(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4987142号

(P4987142)

(45) 発行日 平成24年7月25日(2012.7.25)

(24) 登録日 平成24年5月11日(2012.5.11)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 3 4

請求項の数 8 (全 18 頁)

(21) 出願番号 特願2011-107746 (P2011-107746)

(22) 出願日 平成23年5月13日 (2011.5.13)

(62) 分割の表示 特願2008-1823 (P2008-1823)

の分割

原出願日 平成20年1月9日 (2008.1.9)

(65) 公開番号 特開2011-147830 (P2011-147830A)

(43) 公開日 平成23年8月4日 (2011.8.4)

審査請求日 平成23年5月13日 (2011.5.13)

(73) 特許権者 391010943

株式会社藤商事

大阪府大阪市中央区内本町一丁目1番4号

(74) 代理人 100100376

弁理士 野中 誠一

(72) 発明者 高橋 潤

大阪府大阪市中央区内本町一丁目1番4号

株式会社藤商事内

審査官 増島 稔

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

遊技者に有利な遊技状態を発生させるか否かの抽選処理を実行して、その抽選結果に基づいて遊技動作を中心統括的に制御する主制御部と、

前記主制御部からの指令に基づいて、個別的な制御動作を実行するサブ制御部と、外部から受けた交流電圧に基づいて生成された定常直流電圧と、前記交流電圧が遮断された後も所定期間は所定レベルを維持するバックアップ直流電圧とを、前記主制御部、及び/又は、前記サブ制御部に供給する電源部と、を有して構成され、

前記電源部には、前記交流電圧を前記定常直流電圧に変換する変換回路と、前記バックアップ直流電圧の電圧異常又は電流異常を検出する異常検出回路と、前記異常検出回路の検出信号を受ける中間回路と、が設けられ、

前記中間回路は、前記定常直流電圧を電源電圧として機能し、これが正常レベルを維持する限りON動作して前記異常検出回路の検出信号を他の回路に伝送しないよう構成されていることを特徴とする遊技機。

## 【請求項 2】

前記中間回路は、前記定常直流電圧が遮断時に、前記中間回路から受ける検出信号を記憶する記憶部が設けられている請求項1に記載の遊技機。

## 【請求項 3】

前記記憶部の記憶データに基づいて、前記変換回路が非動作状態に制御されるよう構成されている請求項1又は2に記載の遊技機。

**【請求項 4】**

前記記憶部の記憶データに基づいて、警報動作が実行されるよう構成されている請求項1～3の何れかに記載の遊技機。

**【請求項 5】**

前記異常検出回路は、前記電源部から外部に出力した前記バックアップ直流電圧の、外部からの帰還電圧に基づいて異常判定をしている請求項1～4の何れかに記載の遊技機。

**【請求項 6】**

前記異常検出回路は、正常な帰還電圧に基づいてON動作するフォトカプラ又はスイッチングトランジスタで構成されている請求項5に記載の遊技機。

**【請求項 7】**

前記異常検出回路は、前記電源部の外部から検出信号を受けることなく、前記電圧異常又は電流異常を検出している請求項1～4の何れかに記載の遊技機。

**【請求項 8】**

前記記憶部の出力電圧を受けるダイオードと、前記ダイオードの出力電圧を受けるコンデンサと、前記コンデンサの出力電圧を受けるドライバ回路とを有する異常報知回路が設けられ、前記ドライバ回路は、前記定常直流電圧を電源電圧としている請求項2に記載の遊技機。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、遊技ホールの営業終了後などに、万一、遊技機が違法改造されても、その事実を素早く検出できて違法遊技を未然に防止できる遊技機に関する。

**【背景技術】****【0002】**

パチンコ機などの弾球遊技機は、遊技盤に設けた図柄始動口と、複数の表示図柄による一連の図柄変動態様を表示する図柄表示部と、開閉板が開閉される大入賞口などを備えて構成されている。そして、図柄始動口に設けられた検出スイッチが遊技球の通過を検出すると入賞状態となり、遊技球が賞球として払出された後、図柄表示部では表示図柄が所定時間変動される。その後、7-7-7などの所定の態様で図柄が停止すると大当たり状態となり、大入賞口が繰返し開放されて、遊技者に有利な利益状態を発生させている。但し、実際には、遊技球の入賞に基づく大当たり抽選処理によって、大当たり状態か否かが予め決定されており、図柄表示部では、専ら遊技者を盛上げるために図柄変動動作を行っている。

**【0003】**

通常、この種の遊技機は、遊技動作を全体統括的に制御する主制御基板と、主制御基板から受ける制御コマンドに基づいて個別的な制御動作を実行するサブ制御基板とで構成されている。そして、主制御基板のコンピュータ回路は、前記した大当たり抽選処理を含む制御プログラムに基づいて動作している。したがって、この制御プログラムを変更すれば、任意に大当たり状態を招来させることも可能となり、そのような違法行為も報告されているところである。

**【0004】**

具体的な違法行為としては、例えば、遊技ホールの営業終了後などに、遊技機の主制御基板を違法改造品と交換することが行われる。そこで、かかる違法行為に対処するべく各種の対策が採られている（例えば、特許文献1）。

**【0005】**

特許文献1に記載の発明では、制御基板の背面に、発光素子と受光素子とを有する反射型のフォトセンサを配置し、そのセンサを作動させるためのバッテリを電源基板とは別に設けている。

**【先行技術文献】****【特許文献】****【0006】**

10

20

30

40

50

【特許文献 1】特開 2005 - 137429 号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記の構成では、制御基板とフォトセンサとの隙間に、発光素子からのセンシング光を反射させる部材を挿入すれば、何の問題もなく制御基板を交換できることになる。また、フォトセンサやバッテリを設ける場所を、別に確保する必要があり、抜本的な機器構成の変更を要し、しかも、遊技機の組立工程も複雑化する。

【0008】

本発明は、上記の問題点に鑑みてなされたものであって、防犯用の追加部材を必要とせず、必要最小限の回路変更だけで、違法改造行為を検出できる遊技機を提供することを目的とする。

10

【課題を解決するための手段】

【0009】

上記の目的を達成するため、本発明は、遊技者に有利な遊技状態を発生させるか否かの抽選処理を実行して、その抽選結果に基づいて遊技動作を中心統括的に制御する主制御部と、前記主制御部からの指令に基づいて、個別的な制御動作を実行するサブ制御部と、外部から受けた交流電圧に基づいて生成された定常直流電圧と、前記交流電圧が遮断された後も所定期間は所定レベルを維持するバックアップ直流電圧とを、前記主制御部、及び／又は、前記サブ制御部に供給する電源部と、を有して構成され、前記電源部には、前記交流電圧を前記定常直流電圧に変換する変換回路と、前記バックアップ直流電圧の電圧異常又は電流異常を検出する異常検出回路と、前記異常検出回路の検出信号を受ける中間回路と、が設けられ、前記中間回路は、前記定常直流電圧を電源電圧として機能し、これが正常レベルを維持する限りON動作して前記異常検出回路の検出信号を他の回路に伝送しないよう構成されている。なお、遊技機としては、弾球遊技機の他に回胴遊技機が典型的である。

20

【発明の効果】

【0010】

上記した通り、本発明によれば、防犯用の追加部材を必要とせず、必要最小限の回路変更だけで、違法改造行為を検出できる遊技機を実現できる。

30

【図面の簡単な説明】

【0011】

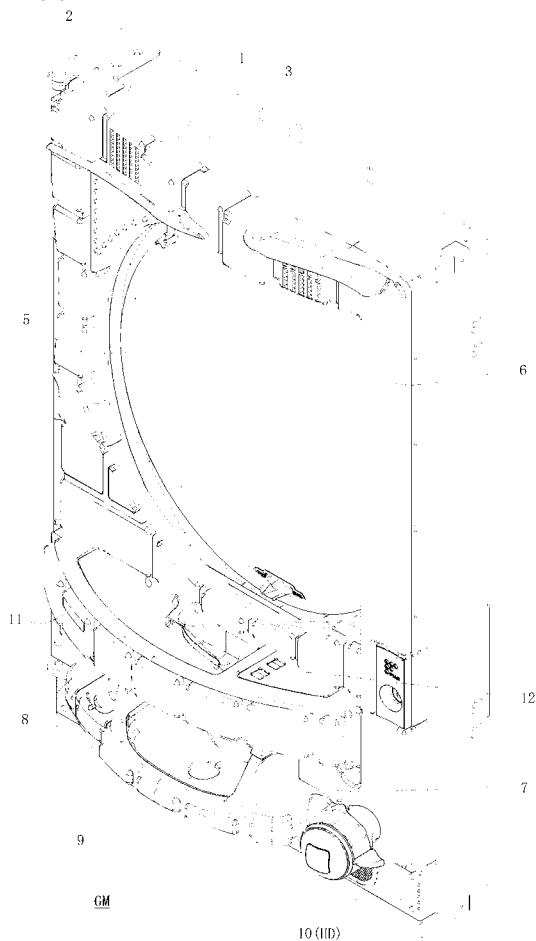

【図1】本発明の実施形態を示すパチンコ機の斜視図である。

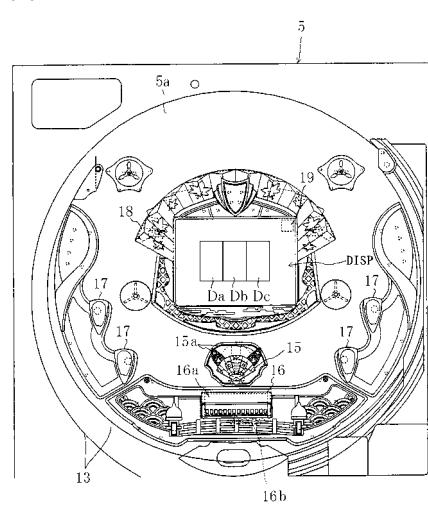

【図2】図1のパチンコ機の遊技盤を詳細に図示した正面図である。

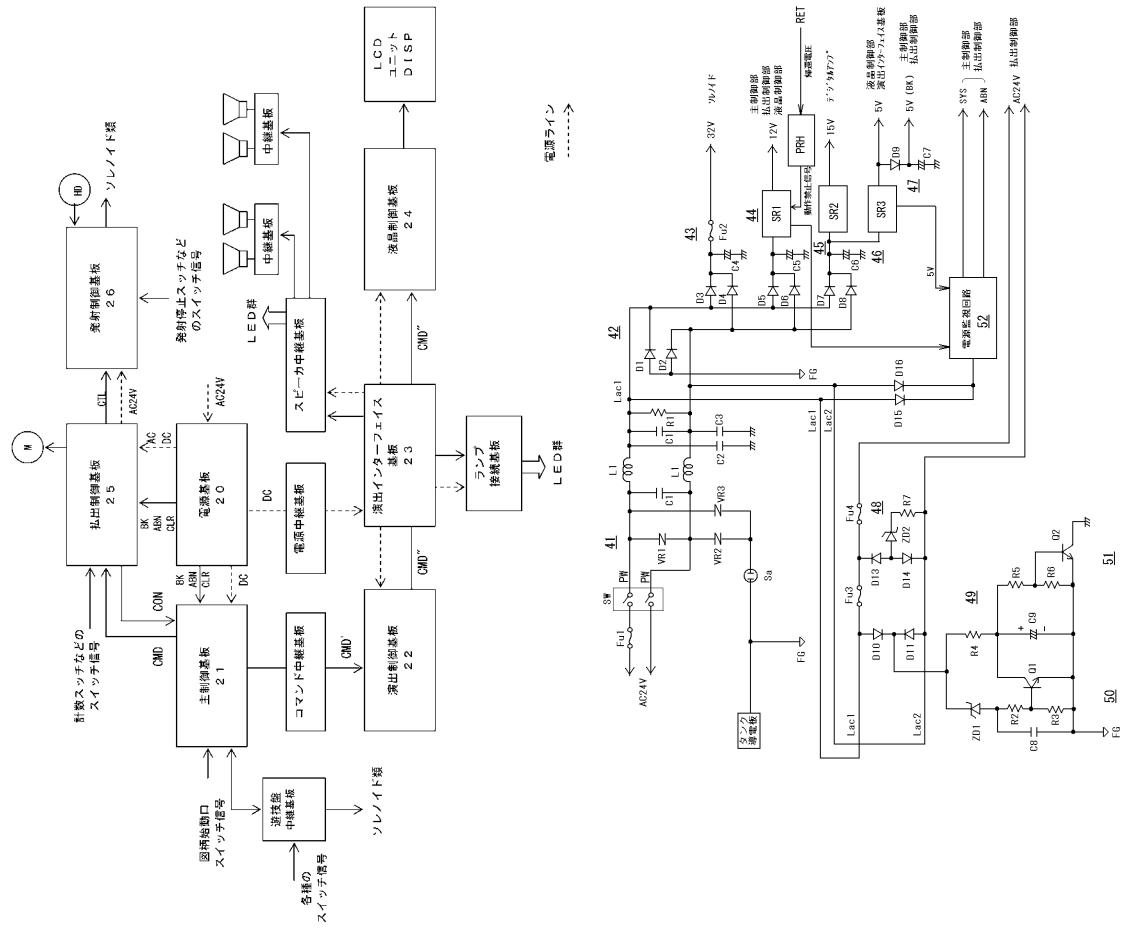

【図3】図1のパチンコ機の全体構成を示すブロック図である。

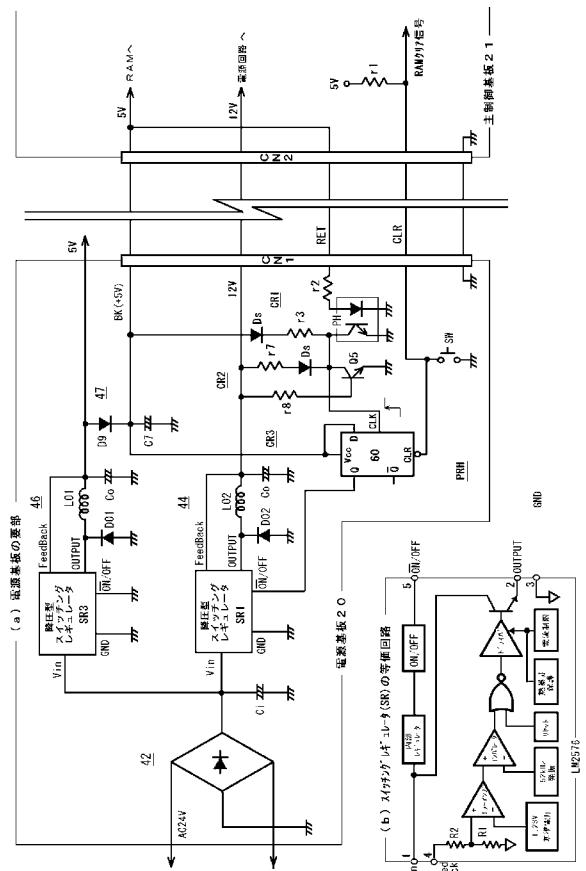

【図4】電源基板の電源回路を示す回路図である。

【図5】図4の一部を詳細に図示した回路図である。

【図6】図5の一部を変形した回路図である。

【図7】図4の一部を詳細に図示した別の回路図である。

40

【図8】シャットダウン機能を活用しない電源回路の回路図である。

【図9】シャットダウン機能を使用しない電源回路の別の回路図である。

【図10】図9の変形回路を示す回路図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態について詳細に説明する。図1は、本実施形態のパチンコ機GMを示す斜視図である。このパチンコ機GMは、島構造体に着脱可能に装着される矩形枠状の木製外枠1と、外枠1に固着されたヒンジ2を介して開閉可能に枢着される前枠3とで構成されている。この前枠3には、遊技盤5が、裏側からではなく、表側から着脱自在に装着され、その前側には、ガラス扉6と前面板7とが夫々開閉自在に枢着されている。

50

## 【0013】

ガラス扉6の外周には、LEDランプなどによる電飾ランプが、略C字状に配置されている。前面板7には発射用の遊技球を貯留する上皿8が装着され、前枠3の下部には、上皿8から溢れ出し又は抜き取った遊技球を貯留する下皿9と、発射ハンドル10(HD)とが設けられている。発射ハンドル10は発射モータと連動しており、発射ハンドル10の回動角度に応じて動作する打撃槌によって遊技球が発射される。

## 【0014】

上皿8の外周面には、チャンスボタン11が設けられている。このチャンスボタン11は、遊技者の左手で操作できる位置に設けられており、遊技者は、発射ハンドル10から右手を離すことなくチャンスボタン11を操作できる。このチャンスボタン11は、通常時には機能していないが、ゲーム状態がボタンチャンス状態となると内蔵ランプが点灯されて操作可能となる。なお、ボタンチャンス状態は、必要に応じて設けられるゲーム状態である。

10

## 【0015】

上皿8の右部には、カード式球貸し機に対する球貸し操作用の操作パネル12が設けられ、カード残額を3桁の数字で表示する度数表示部と、所定金額分の遊技球の球貸しを指示する球貸しスイッチと、ゲーム終了時にカードの返却を指令する返却スイッチとが設けられている。

## 【0016】

図2に示すように、遊技盤5には、金属製の外レールと内レールとからなるガイドレール13が環状に設けられ、その内側の遊技領域5aの略中央には、液晶カラーディスプレイDISPが配置されている。また、遊技領域5aの適所には、図柄始動口15、大入賞口16、複数個の普通入賞口17(大入賞口16の左右に4つ)、2つの通過口であるゲート18が配設されている。これらの入賞口15~18は、それぞれ内部に検出スイッチを有しており、遊技球の通過を検出できるようになっている。

20

## 【0017】

液晶ディスプレイDISPは、大当たり状態に係わる特定図柄を変動表示すると共に背景画像や各種のキャラクタなどをアニメーション的に表示する装置である。この液晶ディスプレイDISPは、中央部に特別図柄表示部Da~Dcと右上部に普通図柄表示部19を有している。そして、特別図柄表示部Da~Dcでは、大当たり状態の招来を期待させるリーチ演出が実行されたり、特別図柄表示部Da~Dc及びその周りでは、当否結果を不確定に報知する予告演出などが実行される。

30

## 【0018】

普通図柄表示部19は普通図柄を表示するものであり、ゲート18を通過した遊技球が検出されると、普通図柄が所定時間だけ変動し、遊技球のゲート18の通過時点において抽出された抽選用乱数値により決定される停止図柄を表示して停止するようになっている。

## 【0019】

図柄始動口15は、左右1対の開閉爪15aを備えた電動式チューリップで開閉されるよう例えれば構成され、普通図柄表示部19の変動後の停止図柄が当たり図柄を表示した場合には、開閉爪15aが所定時間だけ、若しくは、所定個数の遊技球を検出するまで開放されるようになっている。

40

## 【0020】

図柄始動口15に遊技球が入賞すると、特別図柄表示部Da~Dcの表示図柄が所定時間だけ変動し、図柄始動口15への遊技球の入賞タイミングに応じた抽選結果に基づいて決定される停止図柄で停止する。なお、特別図柄表示部Da~Dc及びその周りでは、一連の図柄演出の間に、予告演出が実行される場合がある。

## 【0021】

大入賞口16は、例えば前方に開放可能な開閉板16aで開閉制御されるが、特別図柄表示部Da~Dcの図柄変動後の停止図柄が「777」などの大当たり図柄のとき、「大当

50

リゲーム」と称する特別遊技が開始され、開閉板 16a が開放されるようになっている。

#### 【0022】

大入賞口 16 の開閉板 16a が開放された後、所定時間が経過し、又は所定数（例えば 10 個）の遊技球が入賞すると開閉板 16a が閉じる。このような動作は、最大で例えば 15 回まで特別遊技が継続され、遊技者に有利な状態に制御される。なお、特別図柄表示部 D a ~ D c の変動後の停止図柄が特別図柄のうちの特定図柄であった場合には、特別遊技の終了後のゲームが高確率状態となるという特典が付与される。

#### 【0023】

図 3 は、実施形態に係るパチンコ機の全体回路構成を示すブロック図である。図中の破線は、主に、直流電圧ラインを示している。

10

#### 【0024】

図示の通り、このパチンコ機は、AC 24V を受けて各種の直流電圧やシステムリセット信号（電源リセット信号）SYS や RAMクリア信号 CLRなどを出力する電源基板 20 と、遊技制御動作を中心統括的に担う主制御基板 21 と、主制御基板 21 から受けた制御コマンド CMD' に基づいてランプ演出及び音声演出を実行する演出制御基板 22 と、演出制御基板 22 から受けた信号を各部に伝送する演出インターフェイス基板 23 と、演出インターフェイス基板 23 から受けた制御コマンド CMD" に基づいて液晶ディスプレイ LCD を駆動する液晶制御基板 24 と、主制御基板 21 から受けた制御コマンド CMD に基づいて払出モータ M を制御して遊技球を払い出す払出制御基板 25 と、遊技者による発射ハンドル HD の操作に応答して遊技球を発射させる発射制御基板 26 とを中心に構成されている。

20

#### 【0025】

ここで、主制御基板 21 、演出制御基板 22 、液晶制御基板 24 、及び払出制御基板 25 には、ワンチップマイコンを備えるコンピュータ回路がそれぞれ搭載されている。そこで、主制御基板 21 、演出制御基板 22 、液晶制御基板 24 、及び払出制御基板 25 に搭載された回路、及びその回路によって実現される動作を機能的に総称して、本明細書では、主制御部 21 、演出制御部 22 、液晶制御部 24 、及び払出制御部 25 と言うことがある。又、主制御部 21 を除く全ての制御部又は一部の制御部を総称してサブ制御部と言う。

#### 【0026】

30

主制御部 21 は、払出制御部 25 に対して制御コマンド CMD を一方向に送信する一方、払出制御部 25 からは、遊技球の払出動作を示す賞球計数信号や、払出動作の異常に係わるステータス信号 CON を受信している。ステータス信号 CON には、例えば、補給切れ信号、払出不足エラー信号、下皿満杯信号が含まれる。

#### 【0027】

図示の通り、主制御部 21 と払出制御部 25 には、電源基板 20 から、直流 5V のバックアップ電源 BK が供給されている。したがって、営業終了や停電により交流電源 24V が遮断された後も、ワンチップマイコン内部の RAM のデータは保持される。

#### 【0028】

また、電源基板 20 は、交流電源 24V の遮断時に、主制御部 21 及び払出制御部 25 に、電圧降下信号 ABN を出力するよう構成されている。そして、主制御部 21 及び払出制御部 25 では、フラグセンス方式によって、電圧降下信号 ABN のレベル降下を把握した後、必要なデータを RAM に退避している。そのため、上記したバックアップ電源 BK の作用とあいまって、主制御部 21 と払出制御部 25 では、営業開始時や停電からの復旧時に、電源遮断前の動作を再開できることになる。尚、主制御部 21 にのみバックアップ機能を持たせる、即ち、バックアップ電源 BK や電圧降下信号 ABN を主制御部 21 のみに供給する構成としてもよい。

40

#### 【0029】

更にまた、電源基板 20 は、主制御部 21 と払出制御部 25 に対して、係員のスイッチ操作を示す RAMクリア信号 CLR を出力している。このスイッチ操作は、主に電源投入

50

時に実行されるが、バックアップ電源 B K によって保持されている R A M の記憶内容を消去させるための操作である。したがって、各制御基板 2 1 , 2 5 では、R A M クリア信号 C L R のレベルを判定することによって、係員によるスイッチ操作の有無を把握できることになる。尚、主制御部 2 1 にのみバックアップ機能を持たせた場合、R A M クリア信号 C L R は主制御部 2 1 にのみ供給する。

#### 【 0 0 3 0 】

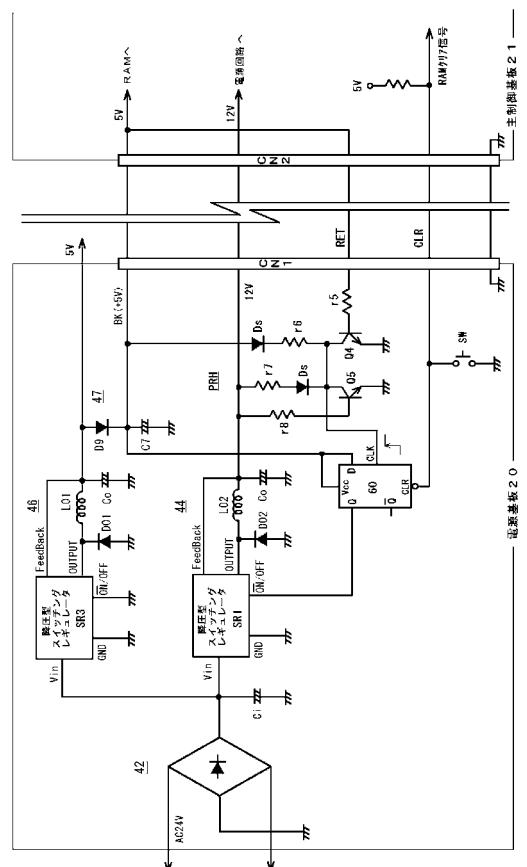

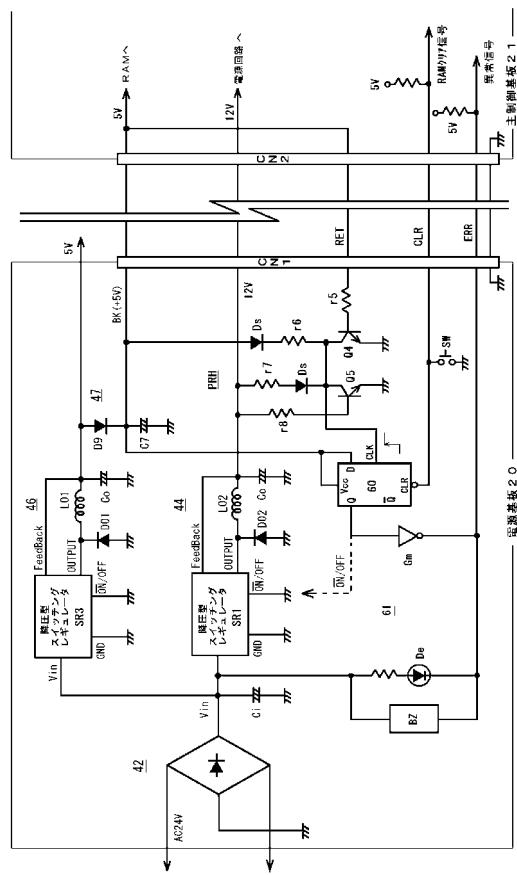

図 4 は、電源基板 2 0 の電源回路を示す回路図である。実施形態の電源回路は、2 4 V の交流電圧を受ける交流入力部 4 1 と、交流入力部 4 1 が output する交流電圧を脈流に変換する整流部 4 2 と、脈流電圧を平滑化する平滑回路 4 3 と、脈流電圧を受けて各種の直流電圧を出力する直流電源部 4 4 ~ 4 6 と、主制御基板 2 1 から受ける帰還電圧 R E T に基づいて直流電源部 4 4 の動作を禁止する電源監視部 P R H と、バックアップ電源を生成する蓄電部 4 7 と、過大な交流電圧を受けると、交流電源ライン L a c を遮断状態にする交流遮断部 4 8 と、交流入力部 4 1 が output する交流電圧を整流する直流生成回路 4 9 と、過大な交流電圧を受けると O N 動作して直流生成回路 4 9 の出力電圧を降下させるレベル監視部 5 0 と、直流生成回路 4 9 の出力電圧レベルに応じて O N / O F F 動作する直流遮断部 5 1 と、電源リセット信号 S Y S と電圧降下信号 A B N を生成する電源監視回路 5 2 とで構成されている。なお、電源リセット信号は、システムリセット信号 S Y S に他ならない。

#### 【 0 0 3 1 】

交流入力部 4 1 は、電源入力ライン P W の一方を溶断させる溶断ヒューズ F u 1 と、電源入力ライン P W , P W を両断する電源スイッチ S W と、機器内部のノイズが外部に漏出することを防止するラインフィルタ ( L 1 , C 1 ~ C 3 , R 1 ) と、遊技球などの静電気を放電する帯電防止部 ( S a , V R 1 ~ V R 3 ) とで構成されている。ラインフィルタは、各電源入力ライン P W , P W に、直列接続される一対のコイル L 1 と、一対のコイル L 1 の両端を接続する一対のコンデンサ C 1 と、各電源入力ライン P W , P W とアース間に接続されるコンデンサ C 2 , C 3 と、電源入力ライン P W , P W の間に接続される抵抗 R 1 とで構成されている。

#### 【 0 0 3 2 】

帯電防止部は、遊技球を蓄える遊技球タンク ( 不図示 ) に設けられた導電板に接続されたサーボアブソーバ S a と、各電源入力ライン P W , P W の間に接続されたバリスタ V R 1 と、各電源入力ライン P W , P W とアース間に接続されたバリスタ V R 2 , V R 3 とで構成されている。なお、タンク導電板とサーボアブソーバ S a の接続点は、フレームグラウンド F G に接続されている。

#### 【 0 0 3 3 】

整流部 4 2 は、ブリッジ型の 3 つの全波整流回路で構成されている。すなわち、ダイオード D 1 , D 2 , D 3 , D 4 で第 1 整流回路が構成され、ダイオード D 1 , D 2 , D 5 , D 6 で第 2 整流回路が構成され、ダイオード D 1 , D 2 , D 7 , D 8 で第 3 整流回路が構成されている。

#### 【 0 0 3 4 】

平滑回路 4 3 は、第 1 整流回路が output する脈流を平滑するコンデンサ C 4 と、直流電源ラインを溶断させる溶断ヒューズ F u 2 とで構成されている。そして、平滑回路 4 3 から出力される + 3 2 V の直流電圧は、主制御基板 2 1 などを経由してソレノイド類に供給される。なお、+ 3 2 V の直流電源ラインに過大な電流が流れると、溶断ヒューズ F u 2 が溶断する。

#### 【 0 0 3 5 】

直流電源部 4 4 は、平滑コンデンサ C 5 と、降圧型のスイッチングレギュレータ S R 1 とで構成され、+ 1 2 V の直流電圧を出力している。そして、+ 1 2 V の直流電圧は、主制御基板 2 1 、拡出制御基板 2 5 、及び液晶制御基板 2 4 に供給されている。

#### 【 0 0 3 6 】

直流電源部 4 5 は、平滑コンデンサ C 6 と、降圧型のスイッチングレギュレータ S R 2

10

20

30

40

50

とで構成され、+15Vの直流電圧を出力している。そして、+15Vの直流電圧は、演出インタフェイス基板23に搭載されたデジタルアンプだけに供給されている。

#### 【0037】

直流電源部46は、平滑コンデンサC6と、降圧型のスイッチングレギュレータSR3とで構成されて+5Vの直流電圧を出力している。そして、+5Vの直流電圧は、液晶制御基板24と演出インタフェイス基板23に供給されている。なお、主制御基板21と派出制御基板25で必要となるDC5Vの電圧については、各制御基板21, 25で受けたDC12Vの電圧を降圧させて生成している。

#### 【0038】

蓄電部47は、ダイオードD9とコンデンサC7とで構成されている。この+5Vの直流電圧は、主制御部21と派出制御部25のワンチップマイコンの内蔵RAMのデータを保持するバックアップ電源となる。

#### 【0039】

交流遮断部48は、交流24Vの交流電源ラインLac1, Lac2に接続された2つのダイオードD13, D14と、ダイオードD13, D14の接続点に接続されたツェナーダイオードZD2及び抵抗R7の直列回路と、ダイオードD13, D14の上流側において、一方側の交流電源ラインLac1に直列接続された溶断ヒューズFu3と、ダイオードD13, D14の下流側において、一方側の交流電源ラインLac1に直列接続された溶断ヒューズFu4とで構成されている。

#### 【0040】

2つのダイオードD13, D14は、交流電源ラインLac1, Lac2から交流電流が侵入しないよう、何れのダイオードD13, D14も、電流の侵入を阻止する方向に直列接続されている。また、ツェナーダイオードZD2は、他方側の交流電源ラインLac2から、ダイオードD13, D14の接続点に向けて、降伏電流が流れる向きに接続されている。

#### 【0041】

ツェナーダイオードZD2は、通常は、OFF状態であるが、交流電源ラインLac1, Lac2に過大な交流電圧（例えばAC100V）が加わると、降伏状態となる。この降伏状態では、交流電源ラインLac2 抵抗R7 ツェナーダイオードZD2 ダイオードD13 交流電源ラインLac1の経路で、ツェナーダイオードZD2の降伏電流が流れるので、溶断ヒューズFu3が溶断される。なお、抵抗R7は、ツェナーダイオードZD2やダイオードD13の破損を防止する保護抵抗である。

#### 【0042】

直流生成回路49は、2つの交流電源ラインLac1, Lac2と、フレームグランドFGとの間に設けられた両波整流回路である。そして、2つの交流電源ラインLac1, Lac2の間に直列接続された2つのダイオードD10, D11と、電流制限抵抗R4と、平滑コンデンサC9と、抵抗R5, R6が直列接続された負荷抵抗とで構成されている。2つのダイオードD10, D11は、各アノード端子が交流電源ラインLac1, Lac2に接続される一方、各カソード端子は、電流制限抵抗R4と、ツェナーダイオードZD1に共通して接続されている。なお、抵抗R4は、レベル監視部50に対する電流制限抵抗であり、また、直列接続された抵抗R5, R6は、スイッチング動作するパワートランジスタQ2のバイアス抵抗でもある。

#### 【0043】

直流生成回路49は、上記の通りに構成されるので、平滑コンデンサC9は、交流電源ラインLac1, Lac2の交流電圧の波高値に近い値まで充電される。また、負荷抵抗として機能する抵抗R5, R6の両端電圧は、平滑された直流電圧となる。

#### 【0044】

レベル監視部50は、バイアス回路(R2, R3, C8)と、スイッチングトランジスタQ1とで構成されて、交流電源ラインLac1, Lac2の何れかが異常レベルでないかを監視している。そして、2つのダイオードD10, D11と、ツェナーダイオードZ

10

20

30

40

50

D 1 と、バイアス抵抗 R 2 , R 3 とが、交流電源ライン L a c 1 , L a c 2 とフレームグランド F G との間に直列接続されている。ダイオード D 1 0 , D 1 1 の接続点には、ツエナーダイオード Z D 1 が、ダイオード D 1 0 , D 1 1 とは逆向きに、つまり、電流を阻止する方向に直列接続されている。

#### 【 0 0 4 5 】

また、直列接続されたバイアス抵抗 R 2 , R 3 の両端には、コンデンサ C 8 が並列接続されている。そして、直列接続されたバイアス抵抗 R 2 , R 3 の接続点に、トランジスタ Q 1 のベース端子が接続されている。また、トランジスタ Q 1 のコレクタ端子は、電流制限抵抗 R 4 と平滑コンデンサ C 9 の接続点に接続され、トランジスタ Q 1 のエミッタ端子は、フレームグランド F G に接続されている。10

#### 【 0 0 4 6 】

一方、直流遮断部 5 1 は、大電流容量のパワートランジスタ Q 2 と、平滑コンデンサ C 9 に並列接続された抵抗 R 5 , R 6 とで構成されている。2つの抵抗 R 5 , R 6 は直列接続されており、その接続点は、パワートランジスタ Q 2 のベース端子に接続されている。なお、抵抗 R 6 は、パワートランジスタ Q 2 のベース端子とエミッタ端子との間に接続されている。これら2つの抵抗 R 5 , R 6 は、パワートランジスタ Q 2 のバイアス抵抗として機能する。またパワートランジスタ Q 2 のコレクタ端子はグランドに接続され、エミッタ端子は、フレームグランド F G に接続されている。

#### 【 0 0 4 7 】

正常状態では、直流生成回路 4 9 の平滑コンデンサ C 9 の両端には、所定レベルの直流電圧が発生している。そのため、パワートランジスタ Q 2 は、ベース端子に十分な正電圧を受けることで O N 状態となり、コレクタ端子とエミッタ端子間は導通状態となる。したがって、フレームグランド F G とアース間も導通状態である。20

#### 【 0 0 4 8 】

トランジスタ Q 2 のコレクタ端子とエミッタ端子は、整流部 4 2 と平滑回路 4 3 など接続する位置に配置されており、トランジスタ Q 2 は O N 状態であることを条件に、平滑回路 4 3 や直流電源部 4 4 ~ 4 6 などが機能することになる。

#### 【 0 0 4 9 】

ここで、交流電源ライン L a c 1 , L a c 2 の何れかと、フレームグランド F G との電位差が、ツエナーダイオード Z D 1 の降伏電圧を超える異常時を想定する。かかる異常時には、ダイオード D 1 0 又はダイオード D 1 1 ツエナーダイオード Z D 1 バイアス抵抗 R 2 , R 3 の向きに電流が流れ、トランジスタ Q 1 のベース電位を上昇させる。そのため、トランジスタ Q 1 は、O F F 状態から O N 状態に遷移して、平滑コンデンサ C 9 の両端電圧を急激に低下させる。30

#### 【 0 0 5 0 】

すると、パワートランジスタ Q 2 のベース電位も低下するので、パワートランジスタ Q 2 が O N 状態から O F F 状態に遷移することになる。そして、パワートランジスタ Q 2 が開放状態となって、平滑回路 4 3 や直流電源部 4 4 ~ 4 6 への給電が停止されて、各回路が非動作状態となる。

#### 【 0 0 5 1 】

実施形態の電源回路では、4つの溶断ヒューズ F u 1 ~ F u 4 に加えて、交流遮断部 4 8 と、直流遮断部 5 1 とを特徴的に備えている。したがって、A C 2 4 V の交流電源ラインに、誤って交流 1 0 0 V を加えてしまう場合でも、I C やその他の電子素子の破損が有效地に防止される。すなわち、A C 1 0 0 V の過大電圧は、バイアス抵抗 R 2 , R 3 を経由してトランジスタ Q 1 を O N 動作させてるので、直ちに、トランジスタ Q 2 が O F F 状態となり、アースラインが切断されて、直流電源部 4 4 ~ 4 6 を保護すると共に、直流電源の供給を受ける各制御基板上の I C や電子素子を保護する。しかも、交流電圧が正常値に戻ると、トランジスタ Q 2 も O N 状態に復帰し、電源回路は正常な動作を再開する。40

#### 【 0 0 5 2 】

図 5 は、図 4 の一部を詳細に図示したものであり、整流部 4 2 と、+ 5 V の電源電圧を50

生成する直流電源部46と、電源遮断後も所定の電圧レベル(+5V)を維持する蓄電部47と、+12Vの電源電圧を生成する直流電源部44と、直流電源部44(スイッチングレギュレータSR1)の出力側の異常を監視する電源監視部PRHとを具体的に図示している。

#### 【0053】

図示の通り、電源基板20と主制御基板21とは、電源基板20のコネクタCN1と、主制御基板21のコネクタCN2とを経由して接続されている。そして、直流5Vのバッカアップ電源BKと、直流12Vと、RAMクリア信号CLRとが、不図示の電源リセット信号SYS及び電圧降下信号ABNと共に、電源基板20から主制御基板21に供給されている。

10

#### 【0054】

RAMクリア信号CLRは、電源基板20に接続されたRAMクリアスイッチSWと、主制御基板21に搭載された電流制限抵抗r1と、主制御基板21の電源回路で12Vから5Vに降圧された電源電圧5Vとで生成される。そして、RAMクリアスイッチSWがON操作された状態では、RAMクリア信号CLRがLレベルとなる。

#### 【0055】

電源基板20から主制御部21に供給されたバックアップ電源BKは、ワンチップマイコンのRAMに供給されるが、このバックアップ電源BKは、帰還電圧RETとして、そのまま電源基板20に戻される。図示の通り、この回路例では、帰還電圧RETは、電流制限抵抗r2を通して、フォトカプラPHのフォトダイオードに供給されている。

20

#### 【0056】

電源監視部PRHは、帰還電圧RETが正常か否かを判定する判定回路(異常検出回路)CR1と、判定回路CR1の出力を受ける中間回路CR2と、判定回路CR1の出力を受けて直流電源部44の動作を禁止する動作禁止回路CR3とで構成されている。ここで、中間回路CR2の電源電圧は、直流電源部44が出力する直流電圧12Vである。一方、判定回路CR1と動作禁止回路CR3は、バックアップ電源BKを受けて動作している。したがって、判定回路CR1と動作禁止回路CR3は、遊技ホールの営業が終了して、電源が遮断された後も、引き続き機能することになる。

#### 【0057】

判定回路CR1は、具体的には、フォトカプラPHで構成され、フォトカプラPHのフォトダイオードとフォトトランジスタには、電流制限抵抗r2,r3と、逆方向電流阻止用のダイオードDsとが接続されている。

30

#### 【0058】

中間回路CR2は、短絡トランジスタQ5と、ベース抵抗r8と、コレクタ抵抗r7と、逆方向電流阻止用のダイオードDsとでスイッチング回路を構成している。中間回路は、直流電源部44が出力する直流電圧12Vで機能するので、電源が投入されて、遊技機が正常に動作を開始した後は、短絡トランジスタQ5は、必ずON状態となる。そのため、遊技動作中、ノイズなどの影響で、仮に、検出トランジスタQ4がON状態からOFF状態に変化しても、検出トランジスタQ4の出力電圧の立ち上がりが、D型フリップフロップ60に伝達されることはない。

40

#### 【0059】

動作禁止回路CR3は、ラッチ回路たるD型フリップフロップ60で構成されている。D型フリップフロップ60は、例えば、汎用デジタルICたるSN7474で構成される。このSN7474は、D入力端子と、クロック端子CLKと、Q出力端子と、クリア端子CLRとを有しており、クロック端子CLKの信号がHレベルに立ち上ると、その時のD入力端子の入力電圧をQ出力端子に出力し、その後はその状態を維持する。一方、クリア端子CLRにLレベルの信号を受けると、Q出力端子はLレベルとなる。

#### 【0060】

図5の回路構成では、D型フリップフロップ60のD入力端子には、Hレベルの電圧が固定的に供給されている。一方、クロック端子CLKは、フォトカプラPHのフォトトラ

50

ンジスタのコレクタ端子に接続されている。そのため、D型フリップフロップ60のクロック端子C L Kへの入力信号、つまり、フォトカプラP Hの出力信号がHレベルに立ち上ると、D型フリップフロップ60のQ出力端子はHレベルとなり、その後は、その状態を維持する。

#### 【0061】

一方、D型フリップフロップ60のクリア端子C L Rには、R A Mクリア信号C L Rが供給されている。したがって、係員によってR A MクリアスイッチS WがON操作されると、D型フリップフロップ60のQ出力端子はLレベルとなり、その後、フォトカプラP Hの出力信号がHレベルに立ち上がらない限り、その状態を維持する。

#### 【0062】

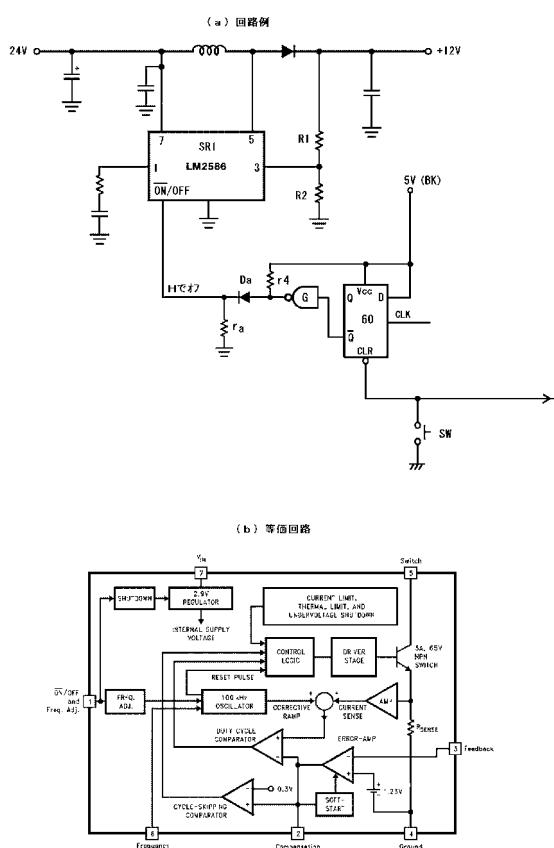

スイッチングレギュレータS R 1, S R 3は、例えば、降圧チョッパ方式の電源I Cで構成され、ここでは、図5(b)に等価回路を示すL M 2 5 7 6が使用される。なお、回路図を簡略化するため、出力電圧が固定タイプのI C(L M 2 5 7 6)を使用し、フィードバック(Feedback)経路に分圧抵抗R 1, R 2を外付けすることなく、各々+12Vと+5Vとを生成している。また、簡易化の観点から、図5(a)には、チョークコイルL 0 1, L 0 2と、ライホールダイオードD 0 1, D 0 2と、出力コンデンサC oだけを図示している。

#### 【0063】

ところで、スイッチングレギュレータS R 1, S R 3(L M 2 5 7 6)は、外部シャットダウン機能を有している。そして、そのON/OFF入力端子にHレベルの電圧を供給すると、スイッチングレギュレータは、スタンバイ状態となり、その後、ON/OFF入力端子にLレベルの電圧を受けるまで、機能を停止するようになっている。

#### 【0064】

そこで、この実施形態では、スイッチングレギュレータS R 1については、動作禁止回路たるD型フリップフロップ60からの信号に基づいて、その外部シャットダウン機能を発揮させている。すなわち、D型フリップフロップ60のQ出力を、スイッチングレギュレータS R 1のON/OFF入力端子に供給して、HレベルのQ出力によって、シャットダウン機能を発揮させて直流電源部44の動作を禁止している。

#### 【0065】

以下、この動作禁止動作について、違法行為に即して説明する。例えば、違法行為者が遊技機を違法改造する場合は、遊技機の電源が遮断された遊技ホールの営業終了後であると思われる。そのような時間帯には、交流入力電圧(A C 2 4 V)が途絶えているので、直流電源部44, 46はともに機能していない。したがって、中間回路C R 2はOFF状態を維持し、他の回路に影響を与えない。

#### 【0066】

一方、バックアップ電源B Kは機能しているので、これを電源電圧とする判定回路C R 1と動作禁止回路C R 3については、主制御部21のR A Mと共に有効に機能している。

#### 【0067】

このような状態で、違法行為者が主制御基板21を交換する場合には、少なくとも、正規の主制御基板21を、コネクタC N 2から取り外す必要がある。なお、正規の主制御基板21は、基板ケースに厳重に封印されているので、違法行為者は、基板ケースごと主制御基板を交換すると思われる。何れにしても、コネクタC N 2が主制御基板21から外されたことによって、それまでフォトカプラP Hに供給されていた帰還電圧R E Tが途絶え、フォトトランジスタの電流も途絶えることになり、フォトカプラの出力電圧は、LレベルからHレベルに立ち上がる。

#### 【0068】

この変化は、D型フリップフロップ60のクロック端子C L Kに伝わるので、その結果、D型フリップフロップ60のQ出力がHレベルに立ち上がる。なお、その後、違法な主制御基板21の接続によって、仮に、帰還電圧R E Tが正常値に復帰したとしても、D型フリップフロップ60のクロック端子C L KがLレベルの立ち下がるだけであり、Hレベ

10

20

30

40

50

ルのQ出力は維持される。また、違法作業時のチャタリングなどによって、繰り返しクロック端子C L Kのレベルが変化したとしても、D型フリップフロップ60のQ出力はHレベルを維持する。

#### 【0069】

このようにして違法改造された遊技機は、その状態のまま翌日の営業開始時を迎える。そして、営業開始に先立って、交流電圧が遊技機に供給されるので、直流電源部45と直流電源部46については、スイッチングレギュレータとしての動作を開始する。しかし、直流電源部44については、そのスイッチングレギュレータSR1のON/OFF端子が、Hレベルに維持されているので、シャットダウン機能が発揮されて、スタンバイ状態のままとなり、+12Vを出力しない。したがって、主制御基板21は動作を開始することができず、この異常事態によって違法行為の事実が判明することになる。なお、万一、電源監視部PRHが誤動作したような場合には、RAMクリアスイッチSWを押すと、D型フリップフロップ60のQ出力がLレベルに戻るので、直流電源部44の動作を開始することができる。10

#### 【0070】

以上の通り、図5の回路構成によれば、違法改造された遊技機が遊技動作を開始することができないので、違法遊技を確実に未然防止することができる。なお、正常の動作を開始した遊技機についても、遊技動作中、常に、帰還電圧RETを受けることになるが、本実施例では、ON動作状態の中間回路CR2が、判定回路CR1の出力を短絡させて、配線ケーブルに重畳するノイズなどが全く問題にならない。20

#### 【0071】

以上、LM2576を使用する回路図について説明したが、使用するICが変われば、電源監視部PRHの回路構成が変更されるのは当然である。図6(a)は、LM2586を使用した回路例であり、LM2586の等価回路(図6(b))も含めて図示している。この回路では、分圧抵抗R1, R2を外付けして、その抵抗比によって+12Vの出力電圧を設定している。また、D型フリップフロップ60のQバー出力が、NOTゲートGを経由して、LM2586のON/OFF入力端子に供給される。なお、この回路構成では、プルアップ抵抗r4と、アイソレーションダイオードDaと、スイッチング周波数を規定する調整抵抗raが必要となるが、その他の回路構成は、図5の場合と同じである。30

#### 【0072】

ところで、図5や図6の回路構成では、交流電圧が遮断された後は、バックアップ電源BKからフォトダイオード及びフォトトランジスタに、継続して電流が流れることになり、コンデンサC7の充電電荷が放電し切ってしまうおそれがある。そこで、そのような場合には、コンデンサC7に代えて、バックアップ電源BKのための充電電池を配置するのが好ましい。

#### 【0073】

また、フォトカプラPHでの消費電流が問題になる場合には、図5や図6の回路構成に代えて、図7の回路構成を探るべきである。図7の電源監視部PRHは、帰還電圧RETの検出トランジスタQ4と、検出トランジスタQ4のコレクタ電圧を短絡させる短絡トランジスタQ5と、D型フリップフロップ60とで構成されている。40

#### 【0074】

そして、検出トランジスタQ4と、ベース抵抗r5と、コレクタ抵抗r6と、電流の逆流を防止するダイオードDsとで、帰還電圧RETが正常か否かを判定する判定回路を構成している。この判定回路は、バックアップ電源BKに基づいて動作しており、検出トランジスタQ4は、正常時には、常にON状態となっている。しかし、この回路構成では、ベース抵抗r5やコレクタ抵抗r6の抵抗値を十分大きく設定することによって、検出トランジスタQ4のON電流を十分小さく抑制することができる。

#### 【0075】

ところで、短絡トランジスタQ5と、ベース抵抗r8と、コレクタ抵抗r7と、電流の50

逆流を防止するダイオード D s とで、もう一つのスイッチング回路（中間回路）を構成している。そして、遊技機が正常に動作を開始した後は、短絡トランジスタ Q 5 は、必ず O N 状態となる。そのため、遊技動作中、ノイズなどの影響で、仮に、検出トランジスタ Q 4 が O N 状態から O F F 状態に変化しても、検出トランジスタ Q 4 の出力電圧の立ち上がりが、D 型フリップフロップ 6 0 に伝達されることはない。

#### 【 0 0 7 6 】

一方、遊技ホールの営業が終了して交流入力電圧が遮断された後は、短絡トランジスタ Q 5 の電源電圧が消滅する。そのため、短絡トランジスタ Q 5 が O N 状態になることはなく、検出トランジスタ Q 4 の出力電圧が、そのまま、D 型フリップフロップ 6 0 に伝達されることになる。

10

#### 【 0 0 7 7 】

このような遊技ホールの営業終了後、もし、主制御基板 2 1 を交換しようとして、正規の主制御基板 2 1 をコネクタ C N 2 から取り外すと、検出トランジスタ Q 4 が O F F 動作する。そして、検出トランジスタ Q 4 のコレクタ電圧の立ち上がりが、そのまま、D 型フリップフロップ 6 0 のクロック端子 C L K に伝達されるので、スイッチングレギュレータ S R 1 の O N / O F F 入力端子が H レベルとなる。そして、この H レベルは、翌日の営業開始までを維持されるので、遊技機への電源投入後は、スイッチングレギュレータ S R 1 がスタンバイ状態となって + 1 2 V を出力しない。したがって、主制御基板 2 1 は動作を開始することができず、この事態によって違法行為の事実が判明することになる。

#### 【 0 0 7 8 】

以上、違法改造時には、正規の主制御基板 2 1 を、基板ケースごとコネクタ C N 2 から取り外されるであろうと想定した。しかし、主制御基板 2 1 の基板ケースに穴を開けて、ワンチップマイコンだけを交換することも考えられる。このような違法行為は、その痕跡が基板ケースに残るので、発生可能性が低いものの、やはり対策は必要である。

20

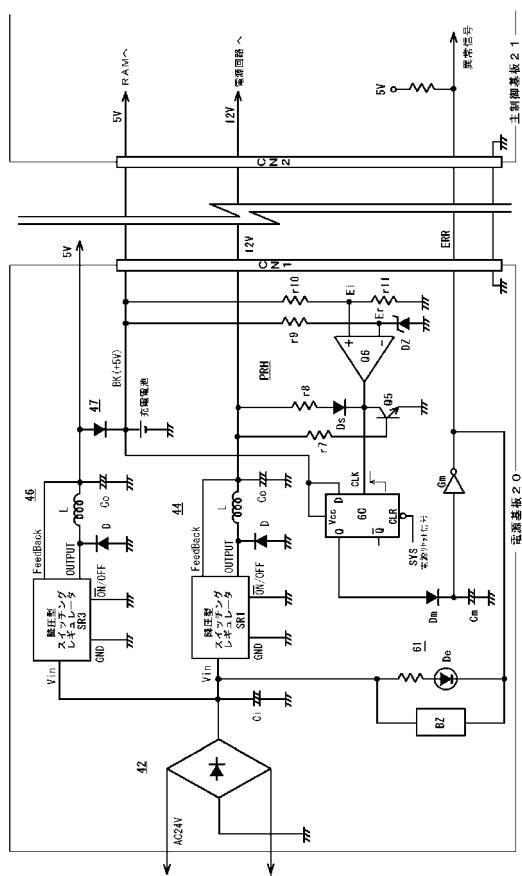

#### 【 0 0 7 9 】

そこで、正規の主制御基板 2 1 が、基板ケースごとコネクタ C N 2 から外されたか否かに拘らず、違法行為を検出するためには、図 8 の回路構成が採用される。図 8 の電源監視部 P R H は、バックアップ電源 B K の電圧上昇を検出するコンパレータ Q 6 と、コンパレータ Q 6 の出力を短絡させる短絡トランジスタ Q 5 と、D 型フリップフロップ 6 0 と、異常報知回路 6 1 とで構成されている。なお、コンパレータ Q 6 には、出力電流制限回路が内蔵されているので、その出力端子が短絡トランジスタ Q 5 によって継続して短絡されても問題は生じない。

30

#### 【 0 0 8 0 】

この電源監視部 P R H では、主制御基板 2 1 がコネクタ C N 2 から取り外されるか、或いは、主制御基板 2 1 のワンチップマイコンが I C ソケットから取り外されると、バックアップ電源 B K の電圧値が微妙に上昇することを利用している。そして、バックアップ電源 B K としては、十分な電流容量を確保するため、好ましくは、充電式の電池が使用される。また、この回路構成では、スイッチングレギュレータ S R 1 のシャットダウン機能を使用しない。これは、図 8 の回路構成では、バックアップ電源 B K の電圧上昇を判定するので、違法行為を誤認する可能性も否定し切れないからである。

40

#### 【 0 0 8 1 】

図示の通り、異常報知回路 6 1 は、D 型フリップフロップ 6 0 の Q 出力端子に接続されたダイオード D m と、ダイオード D m の出力電圧を受けるコンデンサ C m と、コンデンサ C m の両端電圧を受ける N O T ゲート G m と、発光ダイオード D e 及び報知ブザー B Z などで構成されている。

#### 【 0 0 8 2 】

そして、D 型フリップフロップ 6 0 の Q 出力が、ダイオード D m を経由してコンデンサ C m に供給され、異常レベルたる H レベルの Q 出力が、コンデンサ C m に記憶されるようになっている。また、コンデンサ C m の両端電圧は、出力ドライバを兼ねた N O T ゲート G m を経由して、異常信号 E R R として主制御基板 2 1 に伝送される。主制御基板 2 1 は

50

、電源基板 20 から異常信号 E R R を受信した場合、派出制御部 25 に対して派出しを禁止する旨の情報を送信するのが好ましい。又、発射動作を停止させるのも好適である。これらの禁止動作は、例えば、RAMクリア信号 C L R を受信した場合に解除される。

#### 【 0 0 8 3 】

また、NOTゲート G m の出力が L レベルになると、発光ダイオード D e が異常点灯され報知ブザー B Z が鳴るよう構成されている。但し、NOTゲート G m は、スイッチングレギュレータ S R 3 が出力する電源電圧 5 V を受けて動作しており、したがって、遊技機に電源が投入されるまでは機能しない。また、D型フリップフロップ 6 0 のクリア端子 C L R には、RAMクリア信号 C L R に代えて、電源リセット信号 S Y S が供給されている。そのため、遊技機に電源が投入されると、D型フリップフロップ 6 0 の Q 出力端子は、必ず L レベルとなる。したがって、一々、RAMクリアスイッチ S W を操作する必要はない。

10

#### 【 0 0 8 4 】

この電源監視部 P R H では、異常検出回路として、バックアップ電源 B K で動作するコンパレータ Q 6 が配置されている。ここで、コンパレータ Q 6 の非反転入力端子 (+) には、バックアップ電源 B K を分圧抵抗 r 1 0 , r 1 1 で分圧した検出電圧 E i が供給される。一方、反転入力端子 (-) には、ツェナーダイオード D Z の基準電圧 E r が供給される。なお、ツェナーダイオード D Z は、電流制限抵抗 r 9 を経由してバックアップ電源 B K に接続されている。

20

#### 【 0 0 8 5 】

基準電圧 E r は、バックアップ電源 B K が主制御基板 2 1 に給電されている正常時には、検出電圧 E i < 基準電圧 E r となるよう設定されている。そのため、正常時には、コンパレータ Q 6 の出力は常に L レベルであり、短絡トランジスタ Q 5 の O N / O F F 状態に拘らず、D型フリップフロップ 6 0 のクロック入力端子 C L K も L レベルとなる。

#### 【 0 0 8 6 】

このような回路構成を有する遊技機において、交流入力電圧が遮断された後に、主制御基板 2 1 か、そのワンチップマイコンが交換された場合を考える。このような場合には、バックアップ電源 B K からの給電が停止されるタイミングにおいて、バックアップ電源 B K の電圧値が微妙に上昇する。すると、バックアップ電源 B K の電圧値が増加した分だけ検出電圧 E i が増加して、検出電圧 E i > 基準電圧 E r となる。その結果、コンパレータ Q 6 の出力が L レベルから H レベルに変化するので、この変化を、クロック端子 C L K に受ける D型フリップフロップ 6 0 は、その Q 出力が H レベルとなり、この H レベルがダイオード D m を経由してコンデンサ C m に記憶される。なお、このタイミングでは、NOTゲート G m は、電源電圧を受けていないので機能しない。

30

#### 【 0 0 8 7 】

その後、営業開始に先立って交流入力電圧が供給されると、電源リセット信号 S Y S によって、D型フリップフロップ 6 0 の Q 出力は L レベルに戻される。しかし、ダイオード D m が存在する所以コンデンサ C m の充電電圧が直ぐには降下しない。そして、コンデンサ C m の H レベルの両端電圧は、動作を開始した NOTゲートを経由して、主制御基板 2 1 に異常信号 E R R として供給される。また、発光ダイオード D e が異常点灯するとともに、警報ブザー B Z が鳴る。なお、コンデンサ C m の充電電圧は、NOTゲート G m の動作開始と共に徐々に降下するが、数 1 0 秒程度は、H レベルを維持するよう、大容量のコンデンサ C m が使用されており、数 1 0 秒間は警報音が持続する。

40

#### 【 0 0 8 8 】

何れにしても、L レベルの異常信号 E R R を受けた主制御基板 2 1 では、異常事態の発生をホールコンピュータに通報するか、或いは、これに加えて警報表示をするなどの報知動作を実行することになる。この図 8 の回路構成によれば、如何なる場合にも、スイッチングレギュレータ S R 1 をスタンバイモードにしないので、誤動作によって主制御基板 2 1 への給電が停止されるおそれがある。また、図 8 の回路構成では、主制御基板 2 1 から電源基板 2 0 への帰還電圧 R E T が不要であるので、電源基板 2 0 に、全ての回路

50

を収容することができ、したがって、違法行為者の対抗措置を極めて困難にしている。

#### 【0089】

ところで、他の回路基板へ異常信号E R Rを出力する異常報知回路6 1を設けると共に、如何なる場合にも、スイッチングレギュレータS R 1をスタンバイモードに設定しない図8の回路構成は、図5、図6、図7の回路においても、好適に採用できるのは勿論である。この場合、D型フリップフロップ6 0のクリア端子C L Rには、電源リセット信号S Y Sが供給されるのが好適である。

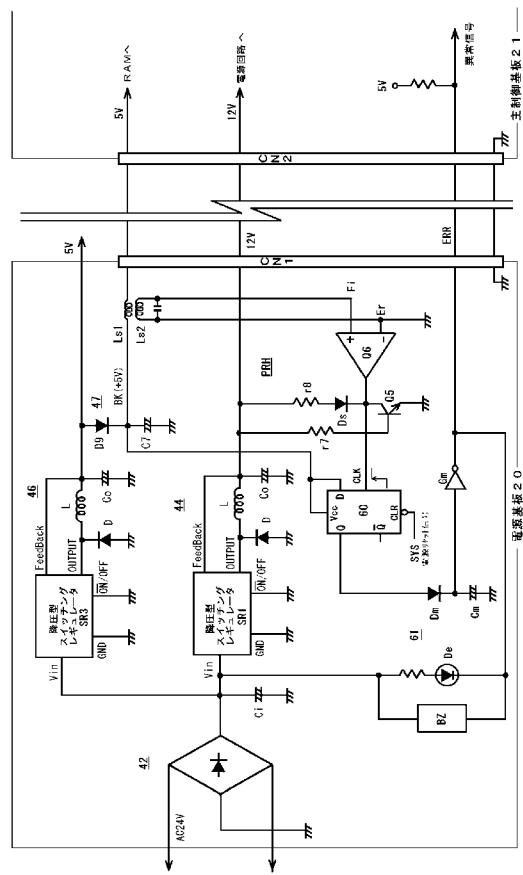

#### 【0090】

また、図8の回路構成では、バックアップ電源B Kの電圧異常を検出する構成を採ったが、これに代えて、バックアップ電源B Kの電源ラインの電流変化を検出する構成を探ることもできる。例えば、図9に示すように、電源ラインに設けた検出一次コイルL s 1と、コンパレータの接続された検出二次コイルL s 2とを密に電磁結合される構成が例示される。この回路構成では、バックアップ電源B Kの電圧降下が問題にならないので充電電池は不要であり大容量のコンデンサC 7で足りる。

#### 【0091】

そして、主制御基板がコネクタC N 2から外されるか、ワンチップマイコンがソケットから外されると、電源ラインの電流が遮断されるので、その変化が検出コイルによって検出されてコンパレータQ 6の出力が立ち上がる。そのため、D型フリップフロップ6 0のQ出力がHレベルとなり、異常事態の発生が翌日まで記憶保持される。

#### 【0092】

以上、本発明の実施形態を具体的に説明したが、具体的な記載内容は何ら本発明を限定するものではなく、各種の改変が可能である。

#### 【0093】

例えば、図8～図10に示す電源監視部P R Hにおいて、D型フリップフロップ6 0のQ出力を、スイッチングレギュレータS R 1のON/OFF入力端子に供給しても良い。但し、この場合には、D型フリップフロップ6 0のクリア端子C L Rには、RAMクリア信号C L Rが供給される。

#### 【0094】

更にまた、スイッチングレギュレータS R 1のシャットダウン機能を活用する図5～図7の回路構成において、図8に示すような異常報知回路6 1を追加するのも好適である。このような場合、図10に示すように、D型フリップフロップ6 0のクリア端子C L Rに、RAMクリア信号C L Rを供給するのであれば、ダイオードD mやコンデンサC mは不要となる。なお、破線で示すように、スイッチングレギュレータS R 1のシャットダウン機能を活用しても良い。

#### 【0095】

なお、上記の説明では、専ら主制御基板2 1の違法改造を問題にしたが、派出制御基板2 5についても違法改造が懸念される場合には、電源基板2 0と派出制御基板2 5との間に、前記した各回路と同様の回路構成が採用される。

#### 【符号の説明】

#### 【0096】

G M 遊技機

2 0 電源基板

B K バックアップ直流電圧

2 1 主制御部

C R 1 異常検出回路

C R 3 動作禁止回路

10

20

30

40

【 四 1 】

【図3】

【 四 2 】

【 図 4 】

【 四 5 】

【 叁 6 】

【 叁 7 】

【 叁 8 】

【 义 9 】

【図10】

---

フロントページの続き

(56)参考文献 特開2005-137429(JP,A)

特開2006-149883(JP,A)

特開2003-180963(JP,A)

(58)調査した分野(Int.Cl., DB名)

A 6 3 F 7 / 0 2