(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6851242号

(P6851242)

(45) 発行日 令和3年3月31日(2021.3.31)

(24) 登録日 令和3年3月11日(2021.3.11)

(51) Int.Cl.

H02M 7/48 (2007.01)

F 1

H02M 7/48

Z

請求項の数 7 (全 17 頁)

(21) 出願番号 特願2017-76718 (P2017-76718)

(22) 出願日 平成29年4月7日 (2017.4.7)

(65) 公開番号 特開2018-182850 (P2018-182850A)

(43) 公開日 平成30年11月15日 (2018.11.15)

審査請求日 令和2年1月16日 (2020.1.16)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100118762

弁理士 高村 順

(72) 発明者 西尾 直樹

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 佐藤 匡

最終頁に続く

(54) 【発明の名称】電力変換装置

## (57) 【特許請求の範囲】

## 【請求項 1】

プリント基板と、

前記プリント基板に設けられる複数のパワーモジュールと、

前記プリント基板に設けられるスナバコンデンサと、

前記プリント基板に設けられる平滑コンデンサと、

を備え、

前記パワーモジュールは、半導体スイッチング素子を有するパッケージと、前記パッケージに設けられた電力側端子と、前記パッケージに設けられた制御側端子とを備え、

前記電力側端子から前記スナバコンデンサまでの距離は、前記制御側端子から前記スナバコンデンサまでの距離よりも短く、

前記プリント基板は、複数の配線レイヤを有し、

前記平滑コンデンサの正側と負側の端子は、前記複数の配線レイヤにおいて互いに異なるレイヤを使用して互いに配線されると共に、前記電力側端子に配線され、

前記パワーモジュールは、直列接続された2つの前記半導体スイッチング素子の半導体スイッチング素子対を複数備え、

複数の前記半導体スイッチング素子対のそれぞれの一端が前記平滑コンデンサの正側に接続され、

複数の前記半導体スイッチング素子対のそれぞれの他端が前記平滑コンデンサの負側に接続され、

10

20

前記電力側端子は、前記直列接続された2つの半導体スイッチング素子の接続点に接続される出力端子を備え、

複数の前記半導体スイッチング素子対のそれぞれを構成する2つの半導体スイッチング素子の前記接続点に接続される前記出力端子が相互に接続され、

複数の前記半導体スイッチング素子対の内、前記平滑コンデンサの正側に接続された複数の前記半導体スイッチング素子を同じタイミングでオン／オフ駆動し、

複数の前記半導体スイッチング素子対の内、前記平滑コンデンサの負側に接続された複数の前記半導体スイッチング素子を同じタイミングでオン／オフ駆動することを特徴とする電力変換装置。

【請求項2】

10

一列に配列される前記複数のパワーモジュールは、一列に配列される前記スナバコンデンサと平行に設けられ、

一列に配列される前記複数のパワーモジュールのそれぞれの前記電力側端子は、一直線上に配列されることを特徴とする請求項1に記載の電力変換装置。

【請求項3】

20

プリント基板と、

前記プリント基板に設けられる複数のパワーモジュールと、

前記プリント基板に設けられるスナバコンデンサと、

前記プリント基板に設けられる平滑コンデンサと、

を備え、

前記パワーモジュールは、半導体スイッチング素子を有するパッケージと、前記パッケージに設けられた電力側端子と、前記パッケージに設けられた制御側端子とを備え、

前記電力側端子から前記スナバコンデンサまでの距離は、前記制御側端子から前記スナバコンデンサまでの距離よりも短く、

前記プリント基板は、複数の配線レイヤを有し、

前記平滑コンデンサの正側と負側の端子は、前記複数の配線レイヤにおいて互いに異なるレイヤを使用して互いに配線されると共に、前記電力側端子に配線され、

一列に配列される前記複数のパワーモジュールは、一列に配列される前記スナバコンデンサと平行に設けられ、

一列に配列される前記複数のパワーモジュールのそれぞれの前記電力側端子は、一直線上に配列されることを特徴とする電力変換装置。

【請求項4】

30

プリント基板と、

前記プリント基板の第2正面に設けられる第1のパワーモジュール、第2のパワーモジュールおよび第3のパワーモジュールと、

前記プリント基板の第1正面に設けられる第1のスナバコンデンサ、第2のスナバコンデンサおよび第3のスナバコンデンサと、

前記プリント基板の前記第1正面に設けられる複数の平滑コンデンサと、

を備え、

前記第1のパワーモジュール、前記第2のパワーモジュールおよび前記第3のパワーモジュールの各々は、半導体スイッチング素子を有するパッケージと、前記パッケージの一方側に設けられた電力側端子と、前記パッケージの他方側に設けられた制御側端子とを備え、

前記プリント基板は、複数の配線レイヤを有し、

前記平滑コンデンサの正側と負側の端子は、前記複数の配線レイヤにおいて互いに異なるレイヤを使用して互いに配線されると共に、前記電力側端子に配線され、

前記第1のパワーモジュール、前記第3のパワーモジュール、前記第1のスナバコンデンサ、前記第2のスナバコンデンサ、および前記第3のスナバコンデンサは、前記第1のパワーモジュール、前記第1のスナバコンデンサ、前記第2のスナバコンデンサ、前記第3のスナバコンデンサ、前記第3のパワーモジュールの順に、前記プリント基板の一辺で

40

50

ある第1辺側から前記第1辺に垂直な前記プリント基板の一辺である第2辺に平行な方向に沿って前記第1辺と対向する第3辺側まで一列に配列され、

前記第2のパワーモジュールは、前記第2のパワーモジュールの前記電力側端子が、第2のパワーモジュールの前記パッケージと前記第2のスナバコンデンサとの間に配置されかつ前記第2のスナバコンデンサと対向するように、前記第2のスナバコンデンサと前記第2辺との間に配置され、

前記第1のパワーモジュールは、前記第1のパワーモジュールの前記電力側端子が、前記第1のパワーモジュールの前記パッケージと前記第1のスナバコンデンサとの間に配置されるように、前記第1のスナバコンデンサと前記第1辺との間に配置され、

前記第3のパワーモジュールは、前記第3のパワーモジュールの前記電力側端子が、前記第3のパワーモジュールの前記パッケージと前記第3のスナバコンデンサとの間に配置されるように、前記第3のスナバコンデンサと前記第3辺との間に配置されることを特徴とする電力変換装置。

#### 【請求項5】

プリント基板と、

前記プリント基板に設けられる複数のパワーモジュールと、

前記プリント基板に設けられるスナバコンデンサと、

前記プリント基板に設けられる平滑コンデンサと、

を備え、

前記パワーモジュールは、半導体スイッチング素子を有するパッケージと、前記パッケージに設けられた電力側端子と、前記パッケージに設けられた制御側端子とを備え、

前記電力側端子から前記スナバコンデンサまでの距離は、前記制御側端子から前記スナバコンデンサまでの距離よりも短く、

前記プリント基板は、複数の配線レイヤを有し、

前記平滑コンデンサの正側と負側の端子は、前記複数の配線レイヤにおいて互いに異なるレイヤを使用して互いに配線されると共に、前記電力側端子に配線され、

前記電力側端子と電気的に接続される出力端子を備え、

前記出力端子は、前記プリント基板の一方の板面側に設けられ、

前記パワーモジュールは、前記プリント基板の他方の板面側に設けられ、

前記出力端子は、前記パワーモジュールを前記プリント基板に向かって投影してなる領域内に設けられることを特徴とする電力変換装置。

#### 【請求項6】

前記パワーモジュールは、直列接続された2つの前記半導体スイッチング素子の半導体スイッチング素子対を複数備え、

複数の前記半導体スイッチング素子対のそれぞれの一端が前記平滑コンデンサの正側に接続され、

複数の前記半導体スイッチング素子対のそれぞれの他端が前記平滑コンデンサの負側に接続され、

前記電力側端子は、前記直列接続された2つの半導体スイッチング素子の接続点に接続される出力端子を備えることを特徴とする請求項5に記載の電力変換装置。

#### 【請求項7】

前記半導体スイッチング素子は、ワイドバンドギャップ半導体で構成されることを特徴とする請求項1から請求項4の何れか一項に記載の電力変換装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体スイッチング素子と半導体スイッチング素子の駆動回路とを同一パッケージに組み込んだ複数のパワーモジュールが配置されるプリント基板を備える電力変換装置に関する。

#### 【背景技術】

10

20

30

40

50

**【0002】**

従来のインバータ又はコンバータの半導体スイッチング素子にはシリコン半導体が使用されていたが、近年では、炭化ケイ素(Silicon Carbide:SiC)及び窒化ガリウム(Gallium Nitride:GaN)といったワイドバンドギャップ半導体の使用が注目されている。ワイドバンドギャップ半導体で構成される半導体スイッチング素子ではスイッチ動作時の電圧変化速度及び電流変化速度が速いため、従来では問題にならなかった電力変換装置の構成部品間の配線インダクタンス又は配線相互間の寄生容量に起因するサージ電圧の発生が無視できなくなっている。

**【0003】**

特許文献1に開示される電力変換装置は、正極導体板及び負極導体板が絶縁シートを介して積層される3層積層構造の積層配線板と、インバータ回路を構成する2つのパワーモジュールと、複数のコンデンサとを備え、2つのパワーモジュールが並列に配置され、複数のコンデンサのそれぞれの正極端子が正極導体板に接続され、複数のコンデンサのそれぞれの負極端子が負極導体板に接続されている。特許文献1に開示される電力変換装置は、複数のコンデンサからパワーモジュールまでの電力配線に積層構造の配線を採用することにより、複数のコンデンサからパワーモジュールまでの配線インピーダンスを同等の値にできる。これにより配線インダクタンスのバラツキに起因して生じるパワーモジュールのサージ電圧を低減している。

10

**【先行技術文献】****【特許文献】**

20

**【0004】**

**【特許文献1】特開2011-19395号公報**

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、特許文献1に開示されるように、平滑コンデンサから半導体素子に至る複数の電流経路のそれぞれの配線インピーダンスが同等の値であっても、ワイドバンドギャップ半導体で構成される半導体スイッチング素子が高速駆動されると、当該電流経路に流れる電流の変化が早い。そのため、配線インピーダンスの両端に発生するサージ電圧が大きくなり、サージ電圧の発生による半導体素子の故障又は電波雑音の増加が問題となる。また、複数の半導体スイッチング素子を1パッケージ化したパワーモジュールを複数使用して機器を構成する場合には、回路全体の面積が増加するため、電流経路が大きくなり電流経路のインピーダンスが大きくなるという課題がある。

30

**【0006】**

本発明は、上記に鑑みてなされたものであって、サージ電圧の発生による半導体素子の故障又は電波雑音の増加を抑制できる電力変換装置を得ることを目的とする。

**【課題を解決するための手段】****【0007】**

上述した課題を解決し、目的を達成するために、本発明の電力変換装置は、プリント基板と、プリント基板に設けられる複数のパワーモジュールと、プリント基板に設けられるスナバコンデンサと、プリント基板に設けられる平滑コンデンサとを備え、パワーモジュールは、半導体スイッチング素子を有するパッケージと、パッケージに設けられた電力側端子と、パッケージに設けられた制御側端子とを備え、電力側端子からスナバコンデンサまでの距離は、制御側端子からスナバコンデンサまでの距離よりも短く、プリント基板は、複数の配線レイヤを有し、平滑コンデンサの正側と負側の端子は、複数の配線レイヤにおいて互いに異なるレイヤを使用して互いに配線されると共に、電力側端子に配線される。パワーモジュールは、直列接続された2つの半導体スイッチング素子の半導体スイッチング素子対を複数備え、複数の半導体スイッチング素子対のそれぞれの一端が平滑コンデンサの正側に接続され、複数の前記半導体スイッチング素子対のそれぞれの他端が平滑コンデンサの負側に接続され、電力側端子は、直列接続された2つの半導体スイッチング素

40

50

子の接続点に接続される出力端子を備える。複数の半導体スイッチング素子対のそれぞれを構成する2つの半導体スイッチング素子の接続点に接続される出力端子が相互に接続され、複数の半導体スイッチング素子対の内、平滑コンデンサの正側に接続された複数の半導体スイッチング素子を同じタイミングでオン／オフ駆動し、複数の半導体スイッチング素子対の内、平滑コンデンサの負側に接続された複数の半導体スイッチング素子を同じタイミングでオン／オフ駆動する。

**【発明の効果】**

**【0008】**

本発明によれば、サージ電圧の発生による半導体素子の故障又は電波雑音の増加を抑制できる、という効果を奏する。

10

**【図面の簡単な説明】**

**【0009】**

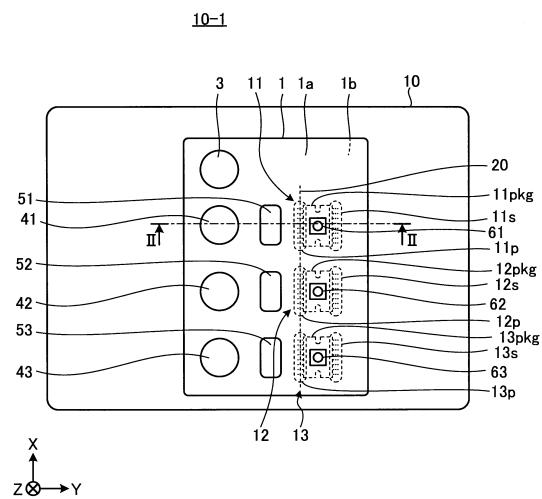

**【図1】**実施の形態1に係る電力変換装置が備えるプリント基板とプリント基板に設けられる部品群とを示す図

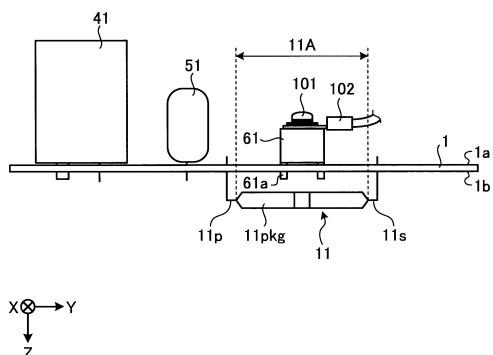

**【図2】**図1に示すII-II矢視断面図

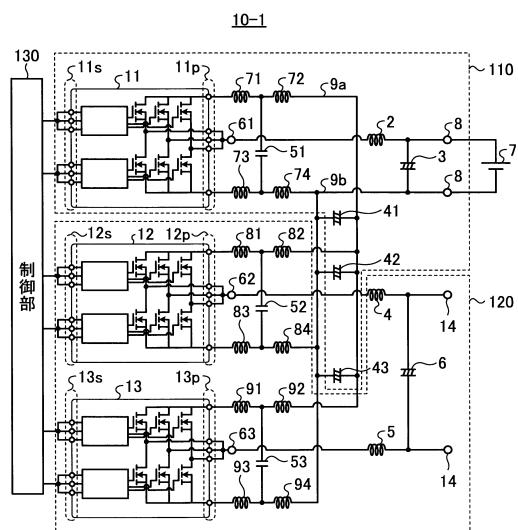

**【図3】**実施の形態1に係る電力変換装置が備える電力変換回路の構成例を示す図

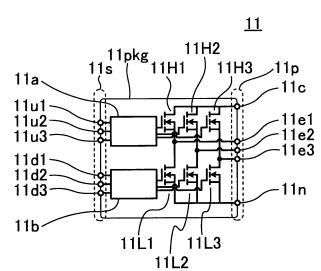

**【図4】**図3に示すパワーモジュールの構成例を示す図

**【図5】**実施の形態1に係る電力変換装置が備えるプリント基板上の配線パターンの一例を示す図

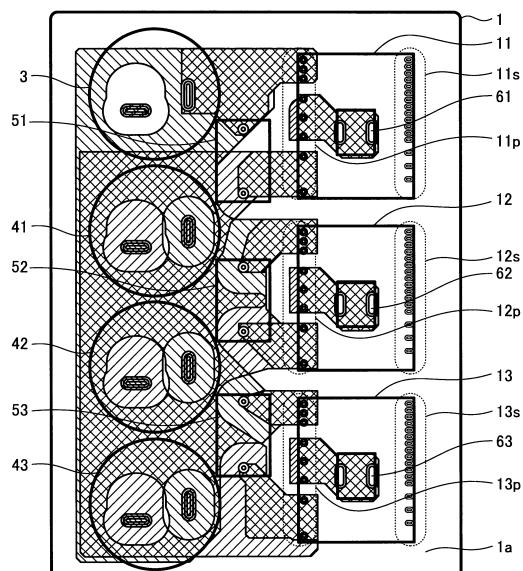

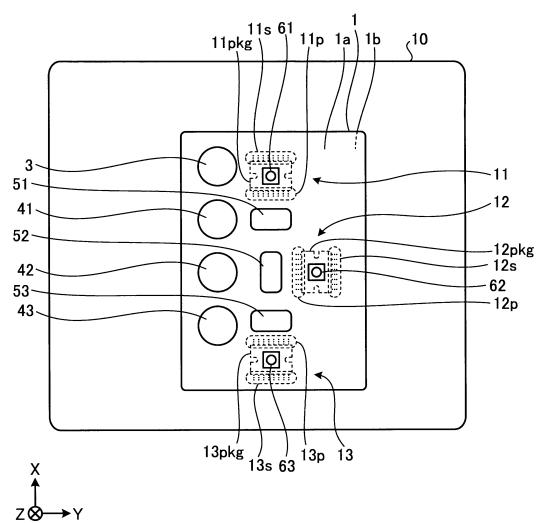

**【図6】**実施の形態2に係る電力変換装置が備えるプリント基板とプリント基板に設けられる部品群とを示す図

20

**【発明を実施するための形態】**

**【0010】**

以下に、本発明の実施の形態に係る電力変換装置を図面に基づいて詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。

**【0011】**

実施の形態1.

図1は実施の形態1に係る電力変換装置が備えるプリント基板とプリント基板に設けられる部品群とを示す図である。図2は図1に示すII-II矢視断面図である。図3は実施の形態1に係る電力変換装置が備える電力変換回路の構成例を示す図である。図4は図3に示すパワーモジュールの構成例を示す図である。

30

**【0012】**

図1に示すように実施の形態1に係る電力変換装置10-1は、電力変換装置10-1の外郭を構成する筐体10と、筐体10の内部に設けられるプリント基板1を備える。プリント基板1は、3つのパワーモジュール11, 12, 13と、入力コンデンサ3と、3つの平滑コンデンサ41, 42, 43と、3つのスナバコンデンサ51, 52, 53と、3つの出力端子61, 62, 63とを備える。

**【0013】**

図1では、プリント基板1上において3つのパワーモジュール11, 12, 13の配列方向をX軸方向とし、プリント基板1上においてX軸方向と直交する方向をY軸方向とし、X軸方向とY軸方向の両者に直交する方向をZ軸方向とする。Z軸方向はプリント基板1の厚み方向、すなわちプリント基板1の一方の板面から他方の板面に向かう方向に等しい。

40

**【0014】**

以下では、3つのパワーモジュール11, 12, 13を「パワーモジュール11, 12, 13」と称し、3つの平滑コンデンサ41, 42, 43を「平滑コンデンサ41, 42, 43」と称し、3つのスナバコンデンサ51, 52, 53を「スナバコンデンサ51, 52, 53」と称し、3つの出力端子61, 62, 63を「出力端子61, 62, 63」と称する場合がある。

**【0015】**

50

図1では、プリント基板1に設けられるパワーモジュール11, 12, 13が3つの例を示しているが、実施の形態1に係る電力変換装置10-1を構成するパワーモジュールの数は、3つに限定されず、2つ以上であればよい。図1では、プリント基板1に設けられる平滑コンデンサ41, 42, 43が3つの例を示しているが、実施の形態1に係る電力変換装置10-1を構成する平滑コンデンサの数は、3つに限定されず、1つ以上であればよい。図1では、プリント基板1に設けられるスナバコンデンサ51, 52, 53が3つの例を示しているが、実施の形態1に係る電力変換装置10-1を構成するスナバコンデンサの数は、3つに限定されず、1つ以上であればよい。

#### 【0016】

図1に示すパワーモジュール11は、複数の半導体スイッチング素子及びスイッチ駆動回路を備えたパッケージ11pkgと、電力側端子11pと、制御側端子11sとを備える。パワーモジュール12は、複数の半導体スイッチング素子及びスイッチ駆動回路を備えたパッケージ12pkgと、電力側端子12pと、制御側端子12sとを備える。パワーモジュール13は、複数の半導体スイッチング素子及びスイッチ駆動回路を備えたパッケージ13pkgと、電力側端子13pと、制御側端子13sとを備える。

10

#### 【0017】

図2に示すようにプリント基板1には符号1a, 1bで示す2つの配線レイヤがあり、2つの配線レイヤにはそれぞれ異なる配線パターンが形成されている。符号1aで示す第1の配線パターンは、プリント基板1のZ軸方向の一方の板面上に形成されている。符号1bで示す第2の配線パターンは、プリント基板1のZ軸方向の他方の板面上に形成されている。図1では、プリント基板1の第1の配線パターン1a側に設けられた部品が実線で示され、プリント基板1の第2の配線パターン1b側に設けられた部品が点線で示される。プリント基板1の第1の配線パターン1a側には、入力コンデンサ3と、平滑コンデンサ41, 42, 43と、スナバコンデンサ51, 52, 53と、出力端子61, 62, 63とが設けられている。プリント基板1の第2の配線パターン1b側には、パワーモジュール11, 12, 13が設けられている。

20

#### 【0018】

図1に示すようにパワーモジュール11, 12, 13は、X軸方向にパワーモジュール11、パワーモジュール12及びパワーモジュール13の順で互いに離間して設けられている。平滑コンデンサ41, 42, 43は、X軸方向に平滑コンデンサ41、平滑コンデンサ42及び平滑コンデンサ43の順で互いに離間して設けられている。スナバコンデンサ51, 52, 53は、X軸方向にスナバコンデンサ51、スナバコンデンサ52及びスナバコンデンサ53の順で互いに離間して設けられている。

30

#### 【0019】

平滑コンデンサ41、スナバコンデンサ51及びパワーモジュール11は、Y軸方向に平滑コンデンサ41、スナバコンデンサ51及びパワーモジュール11の順で互いに離間して設けられている。スナバコンデンサ51は、パワーモジュール11と平滑コンデンサ41との間に設けられている。パワーモジュール11のパッケージ11pkgとスナバコンデンサ51との間には、電力側端子11pが設けられている。パワーモジュール11の制御側端子11sは、パワーモジュール11のY軸方向の電力側端子11pとは反対側に設けられている。プリント基板1のXY平面内において、パワーモジュール11の電力側端子11pからスナバコンデンサ51までの距離は、パワーモジュール11の電力側端子11pから平滑コンデンサ41までの距離よりも短い。

40

#### 【0020】

平滑コンデンサ42、スナバコンデンサ52及びパワーモジュール12は、Y軸方向に平滑コンデンサ42、スナバコンデンサ52及びパワーモジュール12の順で互いに離間して設けられている。スナバコンデンサ52は、パワーモジュール12と平滑コンデンサ42との間に設けられている。パワーモジュール12のパッケージ12pkgとスナバコンデンサ52との間には、電力側端子12pが設けられている。パワーモジュール12の制御側端子12sは、パワーモジュール12のY軸方向の電力側端子12pとは反対側に

50

設けられている。プリント基板1のX Y平面内において、パワーモジュール1 2の電力側端子1 2 pからスナバコンデンサ5 2までの距離は、パワーモジュール1 2の電力側端子1 2 pから平滑コンデンサ4 2までの距離よりも短い。

#### 【0021】

平滑コンデンサ4 3、スナバコンデンサ5 3及びパワーモジュール1 3は、Y軸方向に平滑コンデンサ4 3、スナバコンデンサ5 3及びパワーモジュール1 3の順で互いに離間して設けられている。スナバコンデンサ5 3は、パワーモジュール1 3と平滑コンデンサ4 3との間に設けられている。パワーモジュール1 3のパッケージ1 3 p k gとスナバコンデンサ5 3との間には、電力側端子1 3 pが設けられている。パワーモジュール1 3の制御側端子1 3 sは、パワーモジュール1 3のY軸方向の電力側端子1 3 pとは反対側に設けられている。プリント基板1のX Y平面内において、パワーモジュール1 3の電力側端子1 3 pからスナバコンデンサ5 3までの距離は、パワーモジュール1 3の電力側端子1 3 pから平滑コンデンサ4 3までの距離よりも短い。10

#### 【0022】

図1に示すように、一列に配列されるパワーモジュール1 1, 1 2, 1 3は、一列に配列される平滑コンデンサ4 1, 4 2, 4 3と平行に設けられ、一列に配列されるパワーモジュール1 1, 1 2, 1 3のそれぞれの電力側端子1 1 p, 1 2 p, 1 3 pは、一直線上に配列されている。具体的には、電力側端子1 1 p、電力側端子1 2 p及び電力側端子1 3 pは、図1に示す仮想線2 0上に配列されると共に、互いに離間して配列されている。仮想線2 0は、プリント基板1のX Y平面内においてX軸方向に伸びる仮想的な直線である。このように一列に配列される電力側端子1 1 p、電力側端子1 2 p及び電力側端子1 3 pの近くには、スナバコンデンサ5 1, 5 2, 5 3と平滑コンデンサ4 1, 4 2, 4 3とが設けられている。そして、電力側端子1 1 p, 1 2 p, 1 3 pからスナバコンデンサ5 1, 5 2, 5 3までの距離が、電力側端子1 1 p, 1 2 p, 1 3 pから平滑コンデンサ4 1, 4 2, 4 3までの距離よりも短くなるように、パワーモジュール1 1, 1 2, 1 3とスナバコンデンサ5 1, 5 2, 5 3と平滑コンデンサ4 1, 4 2, 4 3とがプリント基板1上に配列されている。20

#### 【0023】

図2に示すように、出力端子6 1は、プリント基板1の第1の配線パターン1 a側に配置され、パワーモジュール1 1は、プリント基板1の第2の配線パターン1 b側に配置される。出力端子6 1は、パワーモジュール1 1をZ軸方向へプリント基板1に向かって投影してなる領域1 1 A内に設けられている。なお図1に示す出力端子6 2は、パワーモジュール1 2をZ軸方向へプリント基板1に向かって投影してなる領域内に設けられている。また出力端子6 3は、パワーモジュール1 3をZ軸方向へプリント基板1に向かって投影してなる領域内に設けられている。30

#### 【0024】

図2に示すように、出力端子6 1には、ねじ1 0 1によりリード線1 0 2が取り付けられる。リード線1 0 2は、図3に示す直流電力入力部8に接続される。出力端子6 1に設けられた端子6 1 aは、プリント基板1に形成された不図示のスルーホールに挿入され、例えば第2の配線パターン1 bに半田付けされる。パワーモジュール1 1の電力側端子1 1 pは、不図示のスルーホールに挿入されて、例えば第2の配線パターン1 bに半田付けされる。出力端子6 1の端子6 1 aとパワーモジュール1 1の電力側端子1 1 pとは、第2の配線パターン1 bにより電気的に接続される。40

#### 【0025】

図2に示すように、パワーモジュール1 1をZ軸方向へプリント基板1に向かって投影してなる領域1 1 A内に出力端子6 1が設けられることにより、パワーモジュール1 1の電力側端子1 1 pから出力端子6 1の端子6 1 aに至るプリント基板1上の配線パターンを、電力側端子1 1 pのスナバコンデンサ5 1側へ迂回させることなく配線できる。以下では、パワーモジュール1 1の電力側端子1 1 pから出力端子6 1の端子6 1 aに至るプリント基板1上の配線パターンを「第1の基板配線パターン」と称する。50

## 【0026】

第1の基板配線パターンを電力側端子11pのスナバコンデンサ51側へ迂回させた場合、第1の基板配線パターンは、スナバコンデンサ51及び平滑コンデンサ41の周囲に設けられる不図示の複数の配線パターン間に配線しなければならず、第1の基板配線パターンの配線幅を広げることができないという制約が生じる。以下では、スナバコンデンサ51及び平滑コンデンサ41の周囲に設けられる不図示の配線パターンを「第2の基板配線パターン」と称する。第2の基板配線パターンは、例えば、平滑コンデンサ41から電力側端子11pに至る配線パターンや、スナバコンデンサ51から電力側端子11pに至る配線パターンである。図2に示す位置に出力端子61を設けることにより、第1の基板配線パターンを複数の第2の基板配線パターン間に配線する必要がなくなり、第1の基板配線パターンの配線幅を広げることができる。10

## 【0027】

図3に示すように電力変換装置10-1は、直流電圧を特定の値の直流電圧に変換して出力するコンバータ110と、コンバータ110が出力する直流電圧を特定の値の交流電圧に変換して出力するインバータ120と、パワーモジュール11, 12, 13の各々が有する複数の半導体スイッチング素子のオンオフ動作を制御するためのパルス幅変調(Pulse Width Modulation: PWM)信号を生成する制御部130とを備える。直流電源7は、例えば、電力変換装置10-1に直流電力を供給する太陽電池モジュール又は蓄電池といった直流電力供給手段である。電力変換装置10-1は、直流電源7から出力される直流電圧を交流電圧に変換して出力する機能を有し、太陽光発電用又は蓄電池用のパワーコンディショナとして用いられる。20

## 【0028】

制御部130は、例えば、不図示の直流電圧検出部で検出される電圧値と、不図示の交流電圧検出部で検出される電圧値と、不図示の交流電流検出部で検出される電流値とにに基づきPWM信号を生成する。

## 【0029】

コンバータ110は、例えば昇圧チョッパ型の直流 直流変換回路である。コンバータ110は、直流電源7に接続される直流電力入力部8と、パワーモジュール11と、スナバコンデンサ51とを備える。スナバコンデンサ51は、その一端が正極側直流母線9aを介してパワーモジュール11の電力側端子11pに接続され、その他端が負極側直流母線9bを介してパワーモジュール11の電力側端子11pに接続される。30

## 【0030】

またコンバータ110は、入力コンデンサ3と、コンバタリーアクトル2と、出力端子61と、3つの平滑コンデンサ41, 42, 43とを備える。入力コンデンサ3は、その一端が直流電力入力部8の正極に接続され、その他端が直流電力入力部8の負極に接続される。コンバタリーアクトル2は、その一端が入力コンデンサ3の一端に接続されると共に直流電力入力部8の正極に接続される。出力端子61は、コンバタリーアクトル2の他端に接続されると共にパワーモジュール11の電力側端子11pに接続される。3つの平滑コンデンサ41, 42, 43は、それぞれの一端が正極側直流母線9aに接続され、それぞれの他端が負極側直流母線9bに接続される。40

## 【0031】

インバータ120は、パワーモジュール12と、パワーモジュール13と、交流電力出力部14に並列接続されるフィルタコンデンサ6と、一端がフィルタコンデンサ6の一端に接続されると共に交流電力出力部14に接続されるフィルタリーアクトル4と、一端がフィルタコンデンサ6の他端に接続されると共に交流電力出力部14に接続されるフィルタリーアクトル5とを備える。

## 【0032】

またインバータ120は、フィルタリーアクトル4の他端に接続されると共にパワーモジュール12の電力側端子12pに接続される出力端子62と、フィルタリーアクトル5の他端に接続されると共にパワーモジュール13の電力側端子13pに接続される出力端子650

3と、スナバコンデンサ52と、スナバコンデンサ53とを備える。スナバコンデンサ52は、その一端が正極側直流母線9aを介してパワーモジュール12の電力側端子12pに接続され、その他端が負極側直流母線9bを介してパワーモジュール12の電力側端子12pに接続される。スナバコンデンサ53は、その一端が正極側直流母線9aを介してパワーモジュール13の電力側端子13pに接続され、その他端が負極側直流母線9bを介してパワーモジュール13の電力側端子13pに接続される。

#### 【0033】

符号71, 72, 81, 82, 91, 92は、正極側直流母線9aを構成する配線パターンの寄生インダクタンスを表す。符号73, 74, 83, 84, 93, 94は、負極側直流母線9bを構成する配線パターンの寄生インダクタンスを表す。10

#### 【0034】

寄生インダクタンス71は、パワーモジュール11の電力側端子11pからスナバコンデンサ51の一端に至る配線パターンのインダクタンスを表す。寄生インダクタンス73は、パワーモジュール11の電力側端子11pからスナバコンデンサ51の他端に至る配線パターンのインダクタンスを表す。寄生インダクタンス72は、スナバコンデンサ51の一端から平滑コンデンサ41の一端に至る配線パターンのインダクタンスを表す。寄生インダクタンス74は、スナバコンデンサ51の他端から平滑コンデンサ41の他端に至る配線パターンのインダクタンスを表す。

#### 【0035】

寄生インダクタンス81は、パワーモジュール12の電力側端子12pからスナバコンデンサ52の一端に至る配線パターンのインダクタンスを表す。寄生インダクタンス83は、パワーモジュール12の電力側端子12pからスナバコンデンサ52の他端に至る配線パターンのインダクタンスを表す。寄生インダクタンス82は、スナバコンデンサ52の一端から平滑コンデンサ41, 42の一端に至る配線パターンのインダクタンスを表す。寄生インダクタンス84は、スナバコンデンサ52の他端から平滑コンデンサ42, 43の他端に至る配線パターンのインダクタンスを表す。20

#### 【0036】

寄生インダクタンス91は、パワーモジュール13の電力側端子13pからスナバコンデンサ53の一端に至る配線パターンのインダクタンスを表す。寄生インダクタンス93は、パワーモジュール13の電力側端子13pからスナバコンデンサ53の他端に至る配線パターンのインダクタンスを表す。寄生インダクタンス92は、スナバコンデンサ53の一端から平滑コンデンサ43の一端に至る配線パターンのインダクタンスを表す。寄生インダクタンス94は、スナバコンデンサ53の他端から平滑コンデンサ43の他端に至る配線パターンのインダクタンスを表す。30

#### 【0037】

電力変換装置10-1では、直流電力入力部8に印加される直流電圧が、パワーモジュール11及びコンバータリックトル2により特定の値の電圧に昇圧され、昇圧された直流電力が、パワーモジュール12, 13により交流電圧に変換され、変換された交流電圧は、フィルタリックトル4、フィルタリックトル5及びフィルタコンデンサ6で構成されるフィルタにより正弦波の電圧に変換され、交流電力出力部14に接続される不図示の交流負荷に出力される。40

#### 【0038】

このように構成された電力変換装置10-1では、パワーモジュール11, 12, 13のそれぞれが配置される位置により、配線インピーダンスが異なる値となる。特にパワーモジュール11, 12, 13に内蔵される半導体スイッチング素子へ、前述したワイドバンドギャップ半導体が使用されている場合、配線パターンの寄生インダクタンスの値がサージ電圧の発生に大きく影響する。すなわち、ワイドバンドギャップ半導体で構成される半導体スイッチング素子が高速駆動されると、配線パターンに流れる電流の変化が早いため、配線パターン上の寄生インダクタンスが大きくなるほどサージ電圧が大きくなり、サージ電圧の発生による半導体素子の故障又は電波雑音の増加が問題となる。50

## 【0039】

本実施の形態に係る電力変換装置10-1では、図1に示す通り、平滑コンデンサ41, 42, 43とパワーモジュール11, 12, 13の電力側端子11pとの間にスナバコンデンサ51, 52, 53が設けられている。そして、複数のパワーモジュール11, 12, 13の電力側端子11p, 12p, 13pから平滑コンデンサ41, 42, 43までの距離が、パワーモジュール11, 12, 13の制御側端子11s, 12s, 13sから平滑コンデンサ41, 42, 43までの距離よりも短い。また複数のパワーモジュール11, 12, 13の電力側端子11p, 12p, 13pからスナバコンデンサ51, 52, 53までの距離が、パワーモジュール11, 12, 13の電力側端子11p, 12p, 13pから平滑コンデンサ41, 42, 43までの距離よりも短い。

10

## 【0040】

この構成により、パワーモジュール11, 12, 13の電力側端子11p, 12p, 13pとスナバコンデンサ51, 52, 53との間の配線パターンの長さが相対的に短くなり、配線パターンの寄生インダクタンスが低減され、寄生インダクタンスに起因して発生するサージ電圧の値が小さくなり、半導体素子の故障が抑制されると共に電波雑音が抑制される。

## 【0041】

次に、図3に示すパワーモジュール11, 12, 13の内部構成を図4を用いて説明する。なお図4ではパワーモジュール11の内部構成が示されるが、パワーモジュール12, 13の内部構成はパワーモジュール11と同様であるためその説明を割愛する。

20

## 【0042】

図4に示すように、パワーモジュール11は、複数の半導体スイッチング素子11H1, 11L1, 11H2, 11L2, 11H3, 11L3と、上側スイッチ駆動回路11aと、下側スイッチ駆動回路11bとを備える。またパワーモジュール11は、3つの上側スイッチ制御端子11u1, 11u2, 11u3と、3つの下側スイッチ制御端子11d1, 11d2, 11d3とを備える。3つの上側スイッチ制御端子11u1, 11u2, 11u3のそれぞれは、図3に示される制御部130に接続されると共に上側スイッチ駆動回路11aに接続される。3つの下側スイッチ制御端子11d1, 11d2, 11d3のそれぞれは、図3に示される制御部130に接続されると共に下側スイッチ駆動回路11bに接続される。

30

## 【0043】

またパワーモジュール11は、正側端子11cと、負側端子11nと、図3に示される出力端子61に接続される3つの出力端子11e1, 11e2, 11e3とを備える。正側端子11cは、図3に示される正極側直流母線9aに接続されると共に3つの半導体スイッチング素子11H1, 11H2, 11H3のそれぞれのドレインに接続される。負側端子11nは、図3に示される負極側直流母線9bに接続されると共に3つの半導体スイッチング素子11L1, 11L2, 11L3のそれぞれのソースに接続される。

## 【0044】

半導体スイッチング素子11H1のソースには半導体スイッチング素子11L1のドレインが接続される。半導体スイッチング素子11H1から半導体スイッチング素子11L1へ至る経路には、出力端子11e1が接続される。半導体スイッチング素子11H1及び半導体スイッチング素子11L1は、直列に接続された半導体スイッチング素子対を構成する。半導体スイッチング素子対の一端は、正側端子11cを介して図3の正極側直流母線9aに接続され、半導体スイッチング素子対の他端は、負側端子11nを介して図3の負極側直流母線9bに接続される。

40

## 【0045】

半導体スイッチング素子11H2のソースには半導体スイッチング素子11L2のドレインが接続される。半導体スイッチング素子11H2から半導体スイッチング素子11L2へ至る経路には、出力端子11e2が接続される。半導体スイッチング素子11H2及び半導体スイッチング素子11L2は、直列に接続された半導体スイッチング素子対を構

50

成する。半導体スイッチング素子対の一端は、正側端子 11c を介して図 3 の正極側直流母線 9a に接続され、半導体スイッチング素子対の他端は、負側端子 11n を介して図 3 の負極側直流母線 9b に接続される。

#### 【 0 0 4 6 】

半導体スイッチング素子 11H3 のソースには半導体スイッチング素子 11L3 のドレンが接続される。半導体スイッチング素子 11H3 から半導体スイッチング素子 11L3 へ至る経路には、出力端子 11e3 が接続される。半導体スイッチング素子 11H3 及び半導体スイッチング素子 11L3 は、直列に接続された半導体スイッチング素子対を構成する。半導体スイッチング素子対の一端は、正側端子 11c を介して図 3 の正極側直流母線 9a に接続され、半導体スイッチング素子対の他端は、負側端子 11n を介して図 3 の負極側直流母線 9b に接続される。10

#### 【 0 0 4 7 】

図 3 に示すように、3つの上側スイッチ制御端子 11u1, 11u2, 11u3 と3つの下側スイッチ制御端子 11d1, 11d2, 11d3 とは、制御部 130 に接続される。3つの上側スイッチ制御端子 11u1, 11u2, 11u3 には、3つの半導体スイッチング素子 11H1, 11H2, 11H3 のそれぞれをオンオフ駆動するための PWM 信号が入力される。当該 PWM 信号は、上側スイッチ駆動回路 11a により、3つの半導体スイッチング素子 11H1, 11H2, 11H3 のそれぞれをオンオフ駆動する駆動信号に変換される。3つの下側スイッチ制御端子 11d1, 11d2, 11d3 には、3つの半導体スイッチング素子 11L1, 11L2, 11L3 のそれぞれをオンオフ駆動するための PWM 信号が入力される。当該 PWM 信号は、下側スイッチ駆動回路 11b により、3つの半導体スイッチング素子 11L1, 11L2, 11L3 のそれぞれをオンオフ駆動する駆動信号に変換される。20

#### 【 0 0 4 8 】

上側スイッチ駆動回路 11a の3本の入力端子 11u1, 11u2 及び 11u3 は相互に接続され、また下側スイッチ駆動回路 11b の3本の入力端子 11d1, 11d2 及び 11d3 は相互に接続され、出力端子 11e1, 11e2 及び 11e3 は相互に接続される。

#### 【 0 0 4 9 】

上記のように構成することで、パワーモジュール 11、12 及び 13 は、パワーモジュールごとに3組の半導体スイッチング素子を並列接続した出力が得られる構成となり、小容量の半導体スイッチング素子を並列に駆動することにより電流容量の大きなデバイスを実現することができる。30

#### 【 0 0 5 0 】

SiC や GaN といった化合物半導体には、結晶欠陥が僅かに残留しており、例えば均一な欠陥分布のあるウエハから特定のチップ面積の素子を作る場合と、面積がその 1/3 の素子を作る場合とを比較したとき、後者の歩留まりが大きく改善する。すなわち、素子の単位面積当たりの電流値を一定にするように素子の設計を行い所望の電流容量を確保する場合、後者の素子を3つ使用した方が歩留まりが改善され、結果として素子の単位面積当たりの製造コストが低減される。すなわち電流容量の小さいパワーモジュール 11, 12, 13 を並列にして構成した方がコスト的に有利となる。40

#### 【 0 0 5 1 】

その一方で、パワーモジュール 11, 12, 13 を並列接続した場合、個々のパワーモジュールが有する半導体スイッチング素子の特性のばらつきにより、スイッチング波形が振動しやすくなる。このスイッチング波形の振動は、配線パターン上のインダクタンス及びキャパシタンスの共振回路に起因するものである。このような課題に対して実施の形態 1 に係る電力変換装置 10-1 では、平滑コンデンサ 41, 42, 43 とパワーモジュール 11, 12, 13 の電力側端子 11p との間にスナバコンデンサ 51, 52, 53 が設けられているため、配線パターン上の寄生インダクタンスが低減される。従って、個々のパワーモジュールが有する半導体スイッチング素子の特性に僅かなばらつきが存在する場50

合でも、スイッチング波形の振動が抑制される。

#### 【0052】

図5は実施の形態1に係る電力変換装置が備えるプリント基板上の配線パターンの一例を示す図である。図5において、XY平面内において、右下がりの斜線で示されるハッティングは、プリント基板1のZ軸方向の一方の板面上に形成される第1の配線パターン1aを表す。またXY平面内において、左下がりの斜線で示されるハッティングは、プリント基板1のZ軸方向の他方の板面上に形成される第2の配線パターン1bを表す。

#### 【0053】

例えば、平滑コンデンサ41, 42, 43のそれぞれの正側端子は、第1の配線パターン1aに接続され、第1の配線パターン1aを介して電力側端子11pと電気的に接続される。平滑コンデンサ41, 42, 43のそれぞれの負側端子は、第2の配線パターン1bに接続され、第2の配線パターン1bを介して電力側端子11pと電気的に接続される。また、スナバコンデンサ51, 52, 53のそれぞれの正側端子は、第1の配線パターン1aに接続され、第1の配線パターン1aを介して電力側端子11pと電気的に接続される。スナバコンデンサ51, 52, 53のそれぞれの負側端子は、第2の配線パターン1bに接続され、第2の配線パターン1bを介して電力側端子11pと電気的に接続される。

#### 【0054】

このようにプリント基板1に形成される第1の配線パターン1a及び第2の配線パターン1bを用いて部品間を電気的に接続することにより、第1の配線パターン1a及び第2の配線パターン1bの何れか一方のみ用いて部品間を電気的に接続する場合に比べて、パワーモジュール11, 12, 13のスイッチング動作に伴い変化する電流が流れる電流経路の長さが短くなり、配線インピーダンスの値を小さくできる。当該電流経路は、図3に示す正極側直流母線9a及び負極側直流母線9bを構成する配線パターンに等しい。例えば、図3に示す電力側端子11pからスナバコンデンサ51に至る配線パターンと、電力側端子12pからスナバコンデンサ52に至る配線パターンと、電力側端子13pからスナバコンデンサ53に至る配線パターンと、電力側端子11pから平滑コンデンサ41に至る配線パターンと、電力側端子12pから平滑コンデンサ42, 43に至る配線パターンと、電力側端子13pから平滑コンデンサ43に至る配線パターンとが、パワーモジュール11, 12, 13のスイッチング動作に伴い変化する電流が流れる電流経路に相当する。

#### 【0055】

なお実施の形態1のパワーモジュール11, 12, 13には、ワイドバンドギャップ半導体で構成される半導体スイッチング素子が用いられているが、当該半導体スイッチング素子はワイドバンドギャップ半導体で構成されたものに限定されず、シリコン半導体で構成されたものでもよい。ただし、ワイドバンドギャップ半導体で構成された半導体スイッチング素子では、スイッチ動作時の電圧変化速度及び電流変化速度が速いため、配線インピーダンスに発生するサージ電圧の抑制効果がより一層顕著である。

#### 【0056】

以上に説明したように実施の形態1に係る電力変換装置10-1では、平滑コンデンサ41, 42, 43とパワーモジュール11, 12, 13の電力側端子11pとの間にスナバコンデンサ51, 52, 53が設けられているため、パワーモジュール11, 12, 13の電力側端子11p, 12p, 13pとスナバコンデンサ51, 52, 53との間の配線パターンの長さが短くなり、寄生インダクタンスに起因して発生するサージ電圧の値が小さくなり、半導体素子の故障が抑制されると共に電波雑音が抑制される。またワイドバンドギャップ半導体で構成された半導体スイッチング素子を有するパワーモジュール11, 12, 13が用いられている場合でも、電力変換装置10-1では、配線パターンの寄生インダクタンスに起因して発生するサージ電圧の値が小さくなり、半導体素子の安定した動作が実現でき、電波雑音の発生が抑制され、さらにサージ電圧に起因する半導体素子の劣化が抑制される。

10

20

30

40

50

**【0057】**

実施の形態2.

図6は実施の形態2に係る電力変換装置が備えるプリント基板とプリント基板に設けられる部品群とを示す図である。実施の形態2に係る電力変換装置10-2では、3つのパワーモジュール11, 12, 13が、3つのスナバコンデンサ51, 52, 53で構成されるコンデンサ群の周囲を取り囲むように配置されている。具体的には、平滑コンデンサ41, 42, 43は、X軸方向に平滑コンデンサ41、平滑コンデンサ42及び平滑コンデンサ43の順で互いに離間して設けられている。パワーモジュール11、スナバコンデンサ51、スナバコンデンサ52、スナバコンデンサ53及びパワーモジュール13は、X軸方向にパワーモジュール11、スナバコンデンサ51、スナバコンデンサ52、スナバコンデンサ53及びパワーモジュール13の順で互いに離間して設けられている。平滑コンデンサ42、スナバコンデンサ52及びパワーモジュール12は、Y軸方向に平滑コンデンサ42、スナバコンデンサ52及びパワーモジュール12の順で互いに離間して設けられている。10

**【0058】**

パワーモジュール11のパッケージ11pkgとスナバコンデンサ51との間には、電力側端子11pが設けられている。パワーモジュール12のパッケージ12pkgとスナバコンデンサ52との間には、電力側端子12pが設けられている。パワーモジュール13のパッケージ13pkgとスナバコンデンサ53との間には、電力側端子13pが設けられている。パワーモジュール11の制御側端子11sは、パワーモジュール11のX軸方向の電力側端子11pとは反対側に設けられている。パワーモジュール12の制御側端子12sは、パワーモジュール12のY軸方向の電力側端子12pとは反対側に設けられている。パワーモジュール13の制御側端子13sは、パワーモジュール13のX軸方向の電力側端子13pとは反対側に設けられている。20

**【0059】**

このような配置とすることでパワーモジュール11とスナバコンデンサ51の間の距離と、パワーモジュール12とスナバコンデンサ52の間の距離と、パワーモジュール13とスナバコンデンサ53の間の距離と短くしながら、スナバコンデンサ51, 52, 53の相互の距離も短くすることができる。実施の形態2では、パワーモジュール11, 12, 13間を行きかう電流の経路を小さくできるので、外部への高周波雑音の漏洩を抑制できる。30

**【0060】**

また、実施の形態2に係る電力変換装置10-2では、スナバコンデンサ51, 52, 53の互いの距離が短いため、サーボ抑制に必要な静電容量を満足できればスナバコンデンサ51, 52, 53の数を変更することも可能である。また、スナバコンデンサ51, 52, 53を図6のように配置することで、実施の形態1で説明した効果と同等の効果を得られる。詳細については繰り返しとなるため省略する。

**【0061】**

なお実施の形態1, 2のスナバコンデンサ51, 52, 53はコンデンサ及び抵抗の直列回路に置き換えてよい。この直列回路は、パワーモジュール11, 12, 13のスイッチングに伴うサーボ電圧及びスイッチング波形が所望の値となるように構成されているものとする。なお実施の形態1, 2で説明したプリント基板1における部品群の配列方法は、電力変換装置10-1, 10-2をインバータ装置として利用する場合にも同様の効果が得られる。また実施の形態1, 2では、スナバコンデンサ51, 52, 53及び平滑コンデンサ41, 42, 43の数量をパワーモジュール11, 12, 13の数量と等しくした場合の構成例を説明したが、これらの数量は、電力変換装置10-1, 10-2に接続される負荷の容量や、電力変換装置10-1, 10-2の用途に応じて変更してもよい。また実施の形態1, 2では3つのパワーモジュール11, 12, 13に内蔵された3組の半導体スイッチング素子対を3並列した構成例を説明したが、パワーモジュールの並列数は2以上であれば同様の効果が得られる。4050

**【0062】**

また本実施の形態に係る電力変換装置は、複数の半導体スイッチング素子対のそれを構成する2つの半導体スイッチング素子の接続点に接続される出力端子が相互に接続され、複数の半導体スイッチング素子対の内、平滑コンデンサの正側に接続された複数の半導体スイッチング素子を同じタイミングでオン／オフ駆動し、複数の半導体スイッチング素子対の内、平滑コンデンサの負側に接続された複数の半導体スイッチング素子を同じタイミングでオン／オフ駆動するように構成してもよい。このように構成、駆動することで、複数の電流容量の小さい半導体スイッチング素子で、電流容量の大きな半導体スイッチング素子を低コストで実現することが可能となる。

**【0063】**

10

以上の実施の形態に示した構成は、本発明の内容の一例を示すものであり、別の公知の技術と組み合わせることも可能であるし、本発明の要旨を逸脱しない範囲で、構成の一部を省略、変更することも可能である。

**【符号の説明】****【0064】**

1 プリント基板、1a 第1の配線パターン、1b 第2の配線パターン、2 コンバータリアクトル、3 入力コンデンサ、4, 5 フィルタリアクトル、6 フィルタコンデンサ、7 直流電源、8 直流電力入力部、9a 正極側直流母線、9b 負極側直流母線、10 筐体、10-1, 10-2 電力変換装置、11, 12, 13 パワーモジュール、11A 領域、11H1, 11H2, 11H3, 11L1, 11L2, 11L

3 半導体スイッチング素子、11a 上側スイッチ駆動回路、11b 下側スイッチ駆動回路、11c 正側端子、11d1, 11d2, 11d3 下側スイッチ制御端子、11e1, 11e2, 11e3, 61, 62, 63 出力端子、11n 負側端子、11p, 12p, 13p 電力側端子、11pkg, 12pkg, 13pkg パッケージ、11s, 12s, 13s 制御側端子、11u1, 11u2, 11u3 上側スイッチ制御端子、14 交流電力出力部、20 仮想線、41, 42, 43 平滑コンデンサ、51, 52, 53 スナバコンデンサ、61a 端子、71, 72, 73, 74, 81, 82, 83, 84, 91, 92, 93, 94 寄生インダクタンス、101 ねじ、102 リード線、110 コンバータ、120 インバータ、130 制御部。

20

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

10-2

---

フロントページの続き

(56)参考文献 特開2011-250490(JP,A)

特開平11-027959(JP,A)

特開2013-172620(JP,A)

国際公開第2012/098632(WO,A1)

特開2016-195478(JP,A)

特開2010-200433(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 02 M 7 / 48