(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5706674号

(P5706674)

(45) 発行日 平成27年4月22日(2015.4.22)

(24) 登録日 平成27年3月6日(2015.3.6)

(51) Int.Cl.

G05F 3/26 (2006.01)

F 1

G 05 F 3/26

請求項の数 6 (全 11 頁)

|           |                               |           |                                                 |

|-----------|-------------------------------|-----------|-------------------------------------------------|

| (21) 出願番号 | 特願2010-261718 (P2010-261718)  | (73) 特許権者 | 000002325<br>セイコーインスツル株式会社<br>千葉県千葉市美浜区中瀬1丁目8番地 |

| (22) 出願日  | 平成22年11月24日 (2010.11.24)      | (74) 代理人  | 100154863<br>弁理士 久原 健太郎                         |

| (65) 公開番号 | 特開2012-113503 (P2012-113503A) | (74) 代理人  | 100142837<br>弁理士 内野 則彰                          |

| (43) 公開日  | 平成24年6月14日 (2012.6.14)        | (74) 代理人  | 100123685<br>弁理士 木村 信行                          |

| 審査請求日     | 平成25年9月9日 (2013.9.9)          | (72) 発明者  | 小林 裕二<br>千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内       |

|           |                               | (72) 発明者  | 井村 多加志<br>千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内      |

最終頁に続く

(54) 【発明の名称】定電流回路及び基準電圧回路

## (57) 【特許請求の範囲】

## 【請求項 1】

ドレイン端子が電源端子に接続され、互いのゲート端子が接続された第一デプレッションN M O Sトランジスタ及び第二デプレッションN M O Sトランジスタと、

第一入力端子が前記第一デプレッションN M O Sトランジスタのソース端子と接続され、第二入力端子が前記第二デプレッションN M O Sトランジスタのソース端子と接続され、出力端子が前記第一デプレッションN M O Sトランジスタ及び前記第二デプレッションN M O Sトランジスタのゲート端子と接続され、前記第一デプレッションN M O Sトランジスタのソース端子と前記第二デプレッションN M O Sトランジスタのソース端子の電圧を一定に保持する帰還回路と、

前記第一デプレッションN M O Sトランジスタのソース端子及び前記第二デプレッションN M O Sトランジスタのソース端子と接地端子の間に設けられ、少なくとも2つのN M O Sトランジスタと抵抗とを有する定電流生成回路と、

を備えた定電流回路。

## 【請求項 2】

前記帰還回路は差動增幅回路である、ことを特徴とする請求項1に記載の定電流回路。

## 【請求項 3】

前記定電流生成回路は、

ドレイン端子が前記差動增幅回路の反転入力端子に接続され、ソース端子が前記抵抗を介して接地端子に接続された第一N M O Sトランジスタと、

10

20

ゲート端子とドレイン端子が前記差動增幅回路の非反転入力端子及び前記第一N M O Sトランジスタのゲート端子に接続され、ソース端子が接地端子に接続された第二N M O Sトランジスタと、を備えたことを特徴とする請求項2に記載の定電流回路。

【請求項4】

前記定電流生成回路は、

ドレイン端子が前記差動增幅回路の反転入力端子に接続され、ソース端子が接地端子に接続された第一N M O Sトランジスタと、

ゲート端子が前記差動增幅回路の非反転入力端子に接続され、ドレイン端子が前記第一N M O Sトランジスタのゲート端子及び前記抵抗を介して前記差動增幅回路の非反転入力端子に接続され、ソース端子が接地端子に接続された第二N M O Sトランジスタと、を備えたことを特徴とする請求項2に記載の定電流回路。

【請求項5】

請求項1から4のいずれかに記載の定電流回路と、

前記定電流回路の出力端子に設けられた電圧発生回路と、を備えた基準電圧回路。

【請求項6】

前記電圧発生回路は、直列に接続されたP M O Sトランジスタと抵抗とダイオードを備え、

前記電圧発生回路の抵抗と前記定電流生成回路の抵抗は、温度係数が等しいことを特徴とする請求項5に記載の基準電圧回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、定電流回路及びそれを用いた基準電圧回路に関し、より詳しくは定電流回路の安定動作に関する。

【背景技術】

【0002】

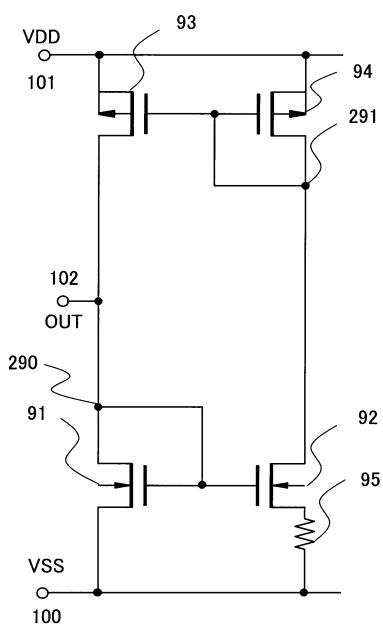

従来の定電流回路について説明する。図9は、従来のK値(駆動能力)の差を用いた定電流回路を示す回路図である。K値は、 $K = W / L \cdot (\mu C_{ox} / 2)$ で求められる。ここで、Wはゲート幅、Lはゲート長、μはキャリアの移動度、C<sub>ox</sub>は単位面積あたりのゲート端子酸化膜容量を示す。

【0003】

従来の定電流回路は、K値の異なるエンハンスマント型N M O Sトランジスタのトランジスタ91及び92と、エンハンスマント型P M O Sトランジスタのトランジスタ93及び94と、抵抗95とからなる。

【0004】

エンハンスマント型N M O Sトランジスタ91は、ソース端子が最低電位の接地端子100に接続され、ドレイン端子とゲート端子がともにエンハンスマント型N M O Sトランジスタ92のゲート端子とエンハンスマント型P M O Sトランジスタ93のドレイン端子に接続されている。エンハンスマント型N M O Sトランジスタ92は、ソース端子が抵抗95を介して接地端子100と接続され、ドレイン端子はエンハンスマント型P M O Sトランジスタ94のゲート端子及びドレイン端子とエンハンスマント型P M O Sトランジスタ93のゲート端子に接続されている。エンハンスマント型P M O Sトランジスタ93及び94のソース端子は、ともに最高電位の電源端子101と接続されている。

【0005】

次に従来の定電流回路の動作について説明する。エンハンスマント型N M O Sトランジスタ91のK値は、エンハンスマント型N M O Sトランジスタ92のK値よりも小さい。エンハンスマント型N M O Sトランジスタ91とエンハンスマント型N M O Sトランジス

10

20

30

40

50

タ92とのゲート端子ソース端子間電圧差が抵抗95に発生し、抵抗95に流れる電流をエンハンスマント型PMOSトランジスタ93及び94でカレントミラーし、バイアス電流を生成する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平3-238513号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、従来の定電流回路は動作点が2つある。一方はバイアス電流が流れる通常の動作点、他方はバイアス電流が0になる動作点である。接続点291の電位が電源端子101になり、接続点290の電位が接地端子100の最低電位になると、バイアス電流が0になる動作点で固定され、定電流回路は動作しなくなる。従って、従来の定電流回路は起動時にスタートアップ回路が別途必要となる、という課題がある。

【0008】

また、電源端子101の上昇に伴い、接続点291の電位が上昇すると、エンハンスマント型NMOSトランジスタ92のチャネル長変調効果の影響で、エンハンスマント型NMOSトランジスタ91及び92の特性が変わり、バイアス電流が変動してしまう。即ち、従来の定電流回路は入力安定度が悪いという課題がある。

【0009】

本発明は、上記の課題に鑑みてなされ、スタートアップ回路を必要とせず、入力安定度の良い定電流回路を提供する。

【課題を解決するための手段】

【0010】

本発明の定電流回路は、上記の課題を解決するために、NMOSトランジスタと抵抗を備えた定電流生成回路と、前記定電流生成回路の電流を流す、互いのゲート端子が接続された、一対のデプレッションNMOSトランジスタで構成されたカレントミラー回路と、前記一対のデプレッションNMOSトランジスタのソース端子の電圧を一定に保持する帰還回路と、を備えた構成とした。

【発明の効果】

【0011】

本発明の定電流回路によれば、カレントミラー回路にデプレッション型NMOSトランジスタを用いることで、チャネルが形成されている状態で起動するので、バイアス電流が0になる動作点で安定することなく確実に起動する。従って、定電流回路はスタートアップ回路を必要としない。また、差動增幅回路を設けたことで、エンハンスマント型NMOSトランジスタのドレイン電圧の変化の帰還が等しく掛かるようになるため、デプレッション型NMOSトランジスタのドレイン電流がW/Lの比のみで決まる様になる。従って、帰還ループのゲイン特性を上げることで、更に入力安定度が改善することが出来る。

【図面の簡単な説明】

【0012】

【図1】本発明の定電流回路を示すブロック図である。

【図2】定電流源ブロック回路の具体例を示した定電流回路の回路図である。

【図3】定電流源ブロック回路の他の具体例を示した定電流回路の回路図である。

【図4】差動增幅回路の具体的な構成例を示した定電流回路の回路図である。

【図5】差動增幅回路の他の構成例を示した定電流回路の回路図である。

【図6】差動增幅回路の他の構成例を示した定電流回路の回路図である。

【図7】差動增幅回路の他の構成例を示した定電流回路の回路図である。

【図8】本発明の定電流回路を用いた基準電圧回の一例を示す回路図である。

【図9】従来の定電流回路の構成例を示す回路図である。

10

20

30

40

50

## 【発明を実施するための形態】

## 【0013】

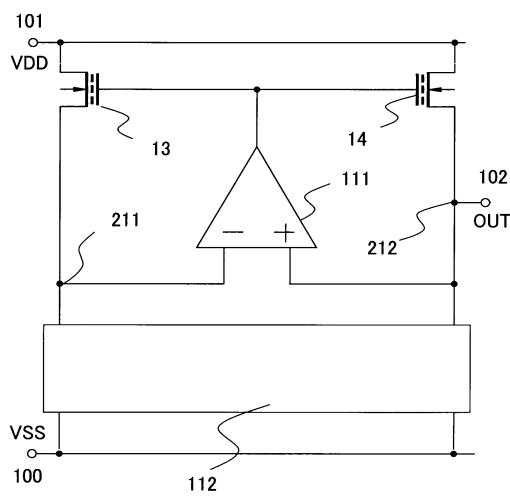

図1は、本発明の定電流回路を示すブロック図である。

本発明の定電流回路は、定電流生成ブロック回路112と、差動增幅回路111と、デブレッショントランジスタ13及び14で構成される。

## 【0014】

差動增幅回路111は、出力端子をデブレッショントランジスタ13及び14のゲート端子に接続され、反転入力端子をデブレッショントランジスタ13のソース端子と定電流生成ブロック回路112に接続され、非反転入力端子をデブレッショントランジスタ14のソース端子と定電流生成ブロック回路112に接続される。定電流生成ブロック回路112は、デブレッショントランジスタ13及び14のソース端子と接地端子100の間に接続される。デブレッショントランジスタ13及び14は、ドレイン端子が電源端子101に接続される。デブレッショントランジスタ14のソース端子が定電流回路の定電流出力端子102に接続される。

10

## 【0015】

定電流生成ブロック回路112は、エンハンスマント型N MOSトランジスタと抵抗で構成される定電流回路である。例えば、図2や図3のような回路で構成される。

## 【0016】

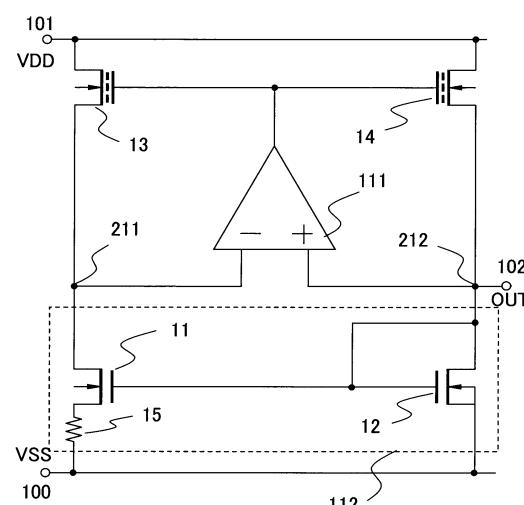

図2の定電流源ブロック回路112は、ゲート端子同士を接続したエンハンスマント型N MOSトランジスタ11及び12と、抵抗15を備えている。エンハンスマント型N MOSトランジスタ11は、ドレイン端子が第一のデブレッショントランジスタ13のソース端子に接続され、ソース端子が抵抗15を介して接地端子100に接続される。エンハンスマント型N MOSトランジスタ12は、ゲート端子とドレイン端子が第二のデブレッショントランジスタ14のソース端子に接続され、ソース端子が接地端子100に接続される。

20

## 【0017】

エンハンスマント型N MOSトランジスタ11に流れる電流は、デブレッショントランジスタ13に流れる電流と等しい。エンハンスマント型N MOSトランジスタ12に流れる電流は、デブレッショントランジスタ14に流れる電流と等しい。また、エンハンスマント型N MOSトランジスタ11のK値とエンハンスマント型N MOSトランジスタ12のK値の比は、デブレッショントランジスタ13のK値とデブレッショントランジスタ14のK値との比と異なる。従って、エンハンスマント型N MOSトランジスタ11のゲート端子ソース端子間電圧とエンハンスマント型N MOSトランジスタ12のゲート端子ソース端子間電圧の差電圧を抵抗に印加することでバイアス電流を生成する。

30

## 【0018】

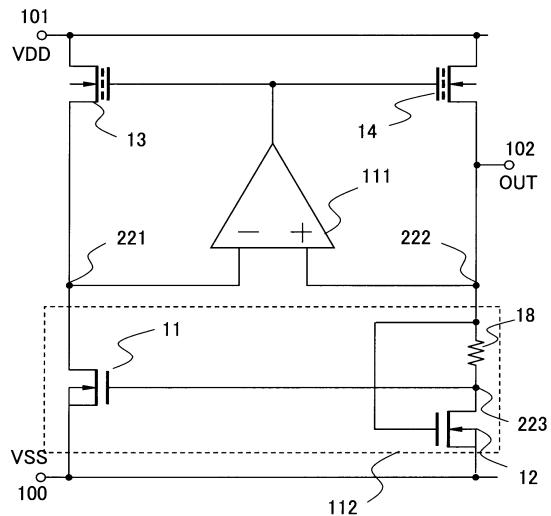

図3の定電流源ブロック回路112は、エンハンスマント型N MOSトランジスタ11及び12と、抵抗18を備えている。エンハンスマント型N MOSトランジスタ11は、ゲート端子がエンハンスマント型N MOSトランジスタ12のドレイン端子に接続され、ドレイン端子が第一のデブレッショントランジスタ13のソース端子に接続され、ソース端子が接地端子100に接続される。エンハンスマント型N MOSトランジスタ12は、ゲート端子が第二のデブレッショントランジスタ14のソース端子に接続され、ドレイン端子が抵抗18を介して第二のデブレッショントランジスタ14のソース端子に接続され、ソース端子が接地端子100に接続される。

40

## 【0019】

図2の定電流源ブロック回路112との違いは、エンハンスマント型N MOSトランジスタ11とエンハンスマント型N MOSトランジスタ12のゲート・ドレイン間電圧差が抵抗18に発生し、バイアス電流を生成する回路構成になった点である。

## 【0020】

50

ここで、エンハンスマント型N M O Sトランジスタ1 1及び1 2は、複数のトランジスタを並列に接続して構成されてもよい。

【0 0 2 1】

次に、本実施形態の定電流回路の動作について説明する。

デプレッショントランジスタ1 3及び1 4は、カレントミラー回路を構成する。デプレッショントランジスタ1 3とデプレッショントランジスタ1 4は、ゲート端子ソース端子間に閾値電圧以上の電圧が掛かると、定電流生成ブロック回路1 1 2にドレイン電流を流す。カレントミラー回路に、デプレッショントランジスタを用いることで、チャネルが形成されている状態で起動するため、バイアス電流が0になる動作点で安定することがなくなる。

10

【0 0 2 2】

また、差動增幅回路1 1 1は、バイアス電流を流すデプレッショントランジスタ1 3及び1 4のソース電圧が等しくなるようにデプレッショントランジスタ1 3のゲート端子に負帰還をかけている。従って、電源端子の電圧変化に伴い、デプレッショントランジスタ1 3のソース電圧が上昇しバイアス電流が増加すると、差動增幅回路1 1 1によって負帰還が掛かり、デプレッショントランジスタ1 3のゲート電圧を下げ、バイアス電流が減少する。つまり、差動增幅回路を用いたことにより、入力安定度を高く保つことができる。

【0 0 2 3】

上述したように、本発明の定電流回路は、カレントミラー回路にデプレッショントランジスタを用いたことで、バイアス電流が0になる動作点で安定することなく、確実に起動することが可能になる。従って、スタートアップ回路を必要としない。また、差動增幅回路1 1 1を用いたことにより、接続点2 1 1と接続点2 1 2の電位は同電位となるので、入力安定度を高く保つことができる。

20

【0 0 2 4】

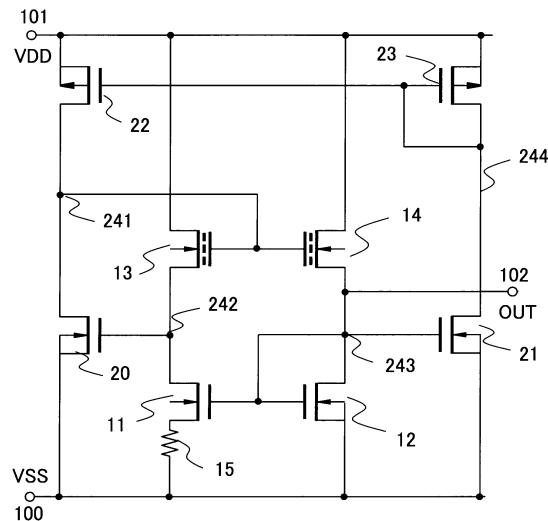

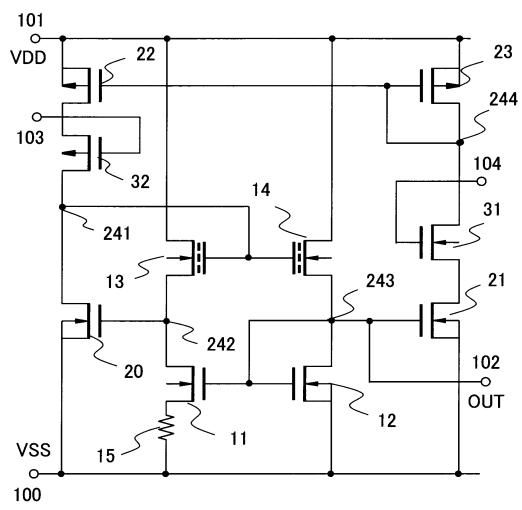

図4は、差動增幅回路1 1 1の具体的な構成例を示した定電流回路の回路図である。

図4の定電流回路は、定電流源ブロック回路1 1 2を構成するエンハンスマント型N M O Sトランジスタ1 1、1 2及び抵抗1 5と、デプレッショントランジスタ1 3及び1 4と、差動增幅回路1 1 1を構成するエンハンスマント型N M O Sトランジスタ2 0及び2 1と、エンハンスマント型P M O Sトランジスタ2 2及び2 3と、を備えている。

30

【0 0 2 5】

定電流源ブロック回路1 1 2は、図2と同じ構成である。差動增幅回路1 1 1は、以下のように構成される。

【0 0 2 6】

エンハンスマント型P M O Sトランジスタ2 2は、ゲート端子がエンハンスマント型P M O Sトランジスタ2 3のゲート端子に接続され、ドレイン端子がエンハンスマント型N M O Sトランジスタ2 0のドレイン端子に接続される。エンハンスマント型P M O Sトランジスタ2 3は、ドレイン端子とゲート端子がエンハンスマント型N M O Sトランジスタ2 1のドレイン端子に接続される。エンハンスマント型N M O Sトランジスタ2 0は、ゲート端子が接続点2 4 2に接続される。エンハンスマント型N M O Sトランジスタ2 1は、ゲート端子が接続点2 4 3に接続される。エンハンスマント型N M O Sトランジスタ2 0及び2 1は、ソース端子と基板が接地端子1 0 0に接続される。エンハンスマント型P M O Sトランジスタ2 2及び2 3は、ソース端子と基板が電源端子1 0 1に接続される。

40

【0 0 2 7】

接続点2 4 1は、差動增幅回路1 1 1の出力端子に対応している。接続点2 4 2は、差動增幅回路1 1 1の反転入力端子に対応している。接続点2 4 3は、差動增幅回路1 1 1の非反転入力端子2 1 2に対応している。エンハンスマント型N M O Sトランジスタ2 0は非反転入力端子段トランジスタ、エンハンスマント型N M O Sトランジスタ2 1は反転入力段トランジスタ、エンハンスマント型P M O Sトランジスタ2 2及び2 3はカレント

50

ミラー回路である。

【0028】

次に、図4の定電流回路の動作について説明する。

電源端子101の電位変動により、反転入力端子の接続点242の電位が上昇すると、エンハンスマント型N MOSトランジスタ20は、ゲート端子ソース端子間電圧が上昇し、ドレイン電流が増加する。これにより、エンハンスマント型N MOSトランジスタ20のドレイン端子と差動増幅回路の出力端子にあたる接続点241の電位が下がり、デプレッショントransistor型N MOSトランジスタ13及び14のゲート電圧を下げる。つまり、デプレッショントransistor型N MOSトランジスタ13及び14に負帰還がかかり、接続点243と接続点242の電位を同電位に保つことができる。

10

【0029】

以上により、図4に示した差動増幅回路を備えたことにより、接続点242と接続点243の電位は同電位となり、入力安定度を高く保つことができる。また、デプレッショントransistor型N MOSトランジスタをカレントミラー回路として用いたため、スタートアップ回路が無くとも、確実に起動することが可能となる。

【0030】

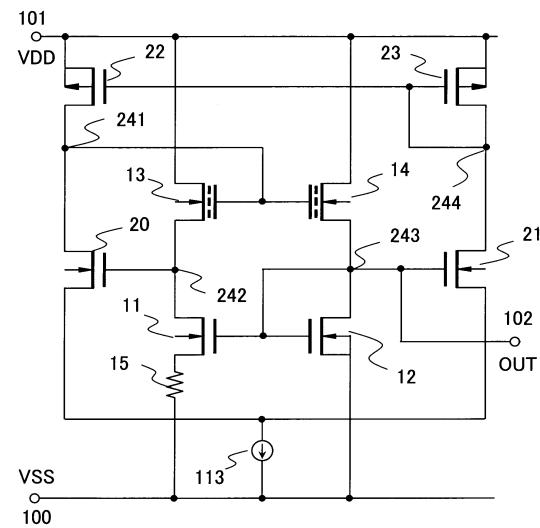

図5は、差動増幅回路111の他の構成例を示した定電流回路の回路図である。

図5の定電流回路は、定電流源ブロック回路112を構成するエンハンスマント型N MOSトランジスタ11、12及び抵抗15と、デプレッショントransistor型N MOSトランジスタ13及び14と、差動増幅回路111を構成するエンハンスマント型N MOSトランジスタ20、21及び31と、エンハンスマント型PMOSトランジスタ22、23及び32と、を備えている。

20

【0031】

定電流源ブロック回路112は、図2と同じ構成である。差動増幅回路111は、図4の差動増幅回路111にエンハンスマント型N MOSトランジスタ31とエンハンスマント型PMOSトランジスタ32のカスコード回路が追加されている。

【0032】

エンハンスマント型PMOSトランジスタ32は、エンハンスマント型PMOSトランジスタ22のドレイン端子とエンハンスマント型N MOSトランジスタ20のドレイン端子の間に設けられ、ゲート端子はPchカスコード端子103に接続されている。エンハンスマント型N MOSトランジスタ31は、エンハンスマント型PMOSトランジスタ23のドレイン端子とエンハンスマント型N MOSトランジスタ21ドレイン端子の間に設けられ、ゲート端子はNチャネルカスコード端子104に接続されている。Pchカスコード端子103には電源電位基準で一定電圧を印加され、Nチャネルカスコード端子104には接地電位基準で一定電圧を印加される。

30

【0033】

次に、図5の定電流回路の動作について説明する。

電源端子101の電位変動により、反転入力端子の接続点242の電位が上昇すると図4の定電流回路と同様の動作をするが、エンハンスマント型PMOSトランジスタ32のカスコード回路によりエンハンスマント型PMOSトランジスタ22のチャネル変調効果が抑えられ、エンハンスマント型N MOSトランジスタ31のカスコード回路によりエンハンスマント型N MOSトランジスタ21のチャネル変調効果が抑えられる。従って、差動増幅回路111のゲイン特性が向上され、図4の定電流回路よりも、入力安定度が改善される。

40

【0034】

図6は、差動増幅回路111の他の構成例を示した定電流回路の回路図である。

図6の定電流回路は、定電流源ブロック回路112を構成するエンハンスマント型N MOSトランジスタ11、12及び抵抗15と、デプレッショントransistor型N MOSトランジスタ13及び14と、差動増幅回路111を構成するエンハンスマント型N MOSトランジスタ20及び21と、エンハンスマント型PMOSトランジスタ22及び23と、定電流源1

50

13を備えている。

【0035】

図4の定電流回路との違いは、差動増幅回路111の入力段のエンハンスマント型NMOSトランジスタ20及び21のソース端子が定電流源113に接続された点である。定電流源113を用いたことにより、差動増幅回路111の消費電流値を制御させることが可能となる。

【0036】

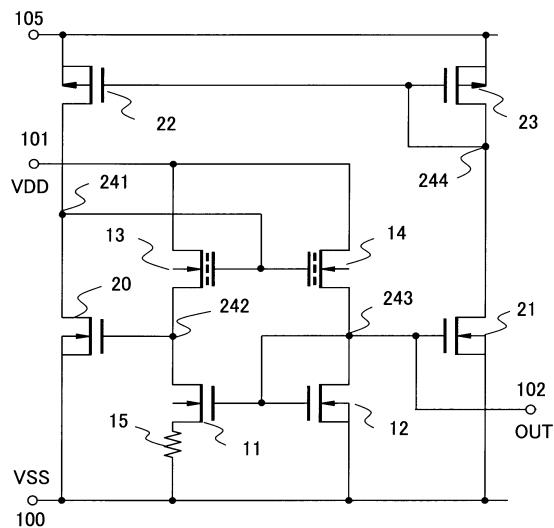

図7は、差動増幅回路111の他の構成例を示した定電流回路の回路図である。

図7の定電流回路は、デプレッション型NMOSトランジスタ13及び14のドレイン端子が電源端子101と接続され、エンハンスマント型PMOSトランジスタ22及び23のソース端子が第二電源端子105に接続されている。

10

【0037】

差動増幅回路111の電源とバイアス電流を生成する回路は、デプレッション型NMOSトランジスタ13及び14のゲート端子ソース端子間電圧にデプレッション型NMOSトランジスタ13及び14の閾値電圧未満の電位が掛からない限り、電源を分けることも可能である。

【0038】

図7のように構成した定電流回路は、電源端子101に対して、第二電源端子105の電位を定電圧化することにより、入力安定度を向上することが可能となる。

【0039】

20

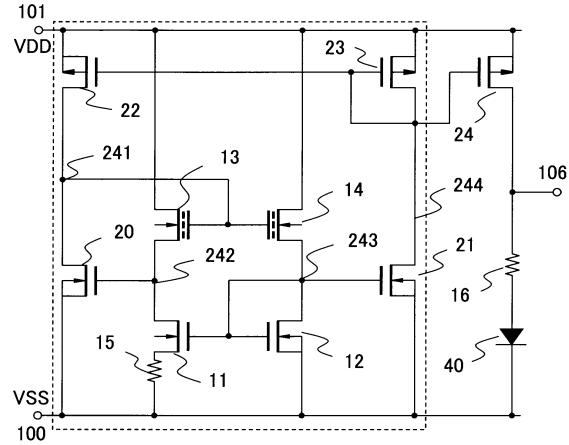

図8は、本発明の定電流回路を用いた基準電圧回路の一例を示す回路図である。図8の基準電圧回路は、図4の定電流回路を用いた回路を例に示している。なお、定電圧回路は他の例に示した回路であってもよい。

【0040】

図8の基準電圧回路は、定電流源ブロック回路112を構成するエンハンスマント型NMOSトランジスタ11、12及び抵抗15と、デプレッション型NMOSトランジスタ13及び14と、差動増幅回路111を構成するエンハンスマント型NMOSトランジスタ20及び21と、エンハンスマント型PMOSトランジスタ22及び23と、エンハンスマント型PMOSトランジスタ24と、抵抗16とダイオード40を備えている。エンハンスマント型PMOSトランジスタ24と、抵抗16及びダイオード40は、電圧発生回路を構成している。

30

【0041】

定電流源ブロック回路112は、図2と同じ構成である。差動増幅回路111は、図4と同じ構成である。

【0042】

エンハンスマント型PMOSトランジスタ23は、ゲート端子を接続点244に接続され、ドレイン端子は基準電圧出力端子106に接続され、ソース端子と基板は電源端子101に接続される。抵抗16は、一方の端子を基準電圧出力端子106に接続され、他方の端子をダイオード40のアノードに接続される。ダイオード40は、カソードは接地端子100に接続される。

40

【0043】

次に、図8の基準電圧回路の動作について説明する。

定電流回路の動作は、図4の説明と同様である。従って、差動増幅回路111により、接続点242と接続点243の電位は同電位となり、入力変動に対する安定性を高く保つことができる。また、カレントミラー回路にデプレッション型NMOSトランジスタ13及び14を用いたため、スタートアップ回路が無くとも、確実に起動することが可能となる。

【0044】

定電流回路のバイアス電流は、エンハンスマント型PMOSトランジスタ24を介して、抵抗16とダイオード40に流れる。ここで、抵抗15を抵抗16と同種の抵抗で構成

50

すると、抵抗の温度係数はキャンセルされる。従って、抵抗 16 の両端には、 $n k T / q$  に比例した正の温度係数を有する電圧が発生する。q は電子の電荷量、k はボルツマン定数、T は温度、n はプロセスによって定まる定数である。

【0045】

一方で、ダイオード 40 の両端の電圧は概ね -2 mV 程度の負の温度係数を有する。ここで、抵抗 16 の両端の電圧の温度係数とダイオード 40 の両端の電圧の温度係数が相殺されるように、抵抗 15 及び抵抗 16 の抵抗比を設定することで、基準電圧出力端子 106 と接地端子 100 の両端からは、温度に依存しない基準電圧を得ることが可能である。

【符号の説明】

【0046】

- 100 接地端子

- 101 電源端子

- 102 定電流出力端子

- 103 P チャネルカスコード端子

- 104 N チャネルカスコード端子

- 105 第二電源端子

- 106 基準電圧出力端子

- 111 差動増幅回路

- 112 定電流生成ブロック回路

- 113 定電流源

10

20

【図 1】

【図 2】

【図3】

【 图 4 】

【図5】

【 四 6 】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 杉浦 正一

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

(72)発明者 五十嵐 敦史

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

審査官 松本 泰典

(56)参考文献 特開2007-140799(JP, A)

特開2007-188245(JP, A)

特開平05-335839(JP, A)

特開平04-111008(JP, A)

特開2010-152510(JP, A)

特開平05-204480(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 05 F 3 / 26