(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4746912号

(P4746912)

(45) 発行日 平成23年8月10日(2011.8.10)

(24) 登録日 平成23年5月20日(2011.5.20)

(51) Int.Cl.

F 1

|             |             |                  |      |      |      |

|-------------|-------------|------------------|------|------|------|

| <b>G09G</b> | <b>5/00</b> | <b>(2006.01)</b> | G09G | 5/00 | 550M |

| <b>G06T</b> | <b>1/60</b> | <b>(2006.01)</b> | G09G | 5/00 | 550P |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> | G09G | 5/00 | 550R |

| <b>G09G</b> | <b>3/22</b> | <b>(2006.01)</b> | G06T | 1/60 | 450C |

| <b>G09G</b> | <b>5/36</b> | <b>(2006.01)</b> | G09G | 3/20 | 631B |

請求項の数 4 (全 15 頁) 最終頁に続く

(21) 出願番号 特願2005-131186 (P2005-131186)

(22) 出願日 平成17年4月28日 (2005.4.28)

(65) 公開番号 特開2005-346044 (P2005-346044A)

(43) 公開日 平成17年12月15日 (2005.12.15)

審査請求日 平成19年6月27日 (2007.6.27)

(31) 優先権主張番号 特願2004-137627 (P2004-137627)

(32) 優先日 平成16年5月6日 (2004.5.6)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100085006

弁理士 世良 和信

(74) 代理人 100100549

弁理士 川口 嘉之

(74) 代理人 100106622

弁理士 和久田 純一

(72) 発明者 井上 健治

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社 内

(72) 発明者 小野 研一郎

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社 内

最終頁に続く

(54) 【発明の名称】 画像信号処理回路および画像表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

順次入力される画像信号をライン単位に格納する第1のメモリ部と、

前記第1のメモリ部から出力される画像信号を複数ライン分格納することができる第2

のメモリ部と、

前記第1のメモリ部および前記第2のメモリ部を制御する制御回路と、を有し、

前記制御回路は、前記第1のメモリ部にライン単位に格納された画像信号のうち、前記

第1のメモリ部の先頭アドレスから任意に設定された列反転位置に対応するアドレスまで

の画像信号を前記第1のメモリ部に入力された第1の順序で前記第2のメモリ部に出力し

た後、前記列反転位置に対応するアドレスから前記先頭アドレスまでの画像信号を前記第

1のメモリ部に入力された順序とは逆の第2の順序で出力し、当該出力された画像信号を

前記第2のメモリ部に順次入力して複数のライン分の画像信号が格納されるように制御す

るとともに、前記第2のメモリ部に複数ライン分格納された画像信号のうち、前記第1の

順序で前記第1のメモリ部から出力された画像信号は前記第2のメモリ部に入力されたラ

イン順で出力するとともに、前記第2の順序で前記第1のメモリ部から出力された画像信

号は前記第2のメモリ部に格納されたライン順とは逆の順序で出力する制御を行う

ことを特徴とする画像信号処理回路。

## 【請求項 2】

請求項1に記載の画像信号処理回路と、

前記画像信号処理回路から出力される画像信号に基づいて表示を実行する表示器とを有

することを特徴とする画像表示装置。

【請求項 3】

順次入力される画像信号をライン単位に格納する第1のメモリ部と、

前記第1のメモリ部から出力される画像信号を複数ライン分格納することが可能な第2のメモリ部と、

前記第1のメモリ部および前記第2のメモリ部を制御する制御回路と、を有し、

前記制御回路は、前記第1のメモリ部にライン単位に格納された画像信号を出力する際、格納された画像信号のうち、前記第1のメモリ部の先頭アドレスから任意に設定された列反転位置に対応するアドレスまでの画像信号を前記第1のメモリ部に入力された第1の順序で前記第2のメモリ部に出力した後、前記列反転位置に対応するアドレスから前記先頭アドレスまでの画像信号を前記第1のメモリ部に入力された順序とは逆の第2の順序で前記第2のメモリ部に出力するように制御し、当該出力された画像信号を前記第2のメモリ部にライン単位に複数ライン分格納する際に、前記第1の順序で前記第1のメモリ部から出力された画像信号は前記第2のメモリ部に入力されたライン順で格納するとともに、前記第2の順序で前記第1のメモリ部から出力された画像信号は前記第2のメモリ部に入力されたライン順とは逆の順序で格納する制御を行う

ことを特徴とする画像信号処理回路。

【請求項 4】

請求項3に記載の画像信号処理回路と、

前記画像信号処理回路から出力される画像信号に基づいて表示を実行する表示器とを有することを特徴とする画像表示装置。

10

20

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、画像信号処理回路および画像表示装置に関し、特に、コンピュータから出力される画像データやテレビジョン信号を、画像表示装置に表示するための画像信号処理回路に適用して好適なものである。

【背景技術】

【0002】

30

従来、画像表示装置に表示する画像としては、コンピュータ画像、デジタルカメラの画像、およびテレビジョン信号の画像などの様々な種類が存在する。そして、これらの画像のフォーマットに関しても多数存在する。

【0003】

これらの画像フォーマットが固定された画像表示装置である場合には、画像フォーマットに合わせた画像表示装置を選択することにより、この画像フォーマットに対応させることができる。ところが、汎用の画像表示装置においては、画像表示装置に画像を表示させるためには、その画像に対しても画像処理を施す必要がある。

【0004】

この画像表示装置における画像処理として、代表的には、IP変換や、フレームレート変換、または解像度変換などがある。これらのうちのIP変換とは、テレビジョン信号のNTSC信号のようなインターレース信号をプログレッシブ信号に変換するものである。また、フレームレート変換とは、画面の切り換えレートの変換である。また、解像度変換とは、横方向の画素数および縦方向の走査線数を変換するものである。

40

【0005】

これらの画像処理を実行する場合において、フレームメモリを用いる構成が知られている。このフレームメモリは、1画面分の画像データを格納しておき、画像処理の必要に応じてデータを読み出して処理を行うものである。そして、このフレームメモリを採用することにより、上述した画像処理のみならず、特殊画像処理を実行することも可能となる。

【0006】

50

また、特許文献 1 には、フレームメモリへの書き込み順序または読み出し順序を制御することによって、画像の反転および回転と拡大および縮小とを行う技術が開示されている。

#### 【 0 0 0 7 】

また、近年、1つの画像表示装置に複数の画面を表示するマルチ画面表示が一般に行われてきている。そして、特許文献 1 および特許文献 2 には、このようなマルチ画面表示に関して、複数のメモリ空間を使用することによりマルチ画面表示を行う手法が開示されている。

#### 【 0 0 0 8 】

また、特許文献 3 においては、S D R A M ( Synchronous DRAM ) のバーストモードを使用して画像の反転、回転などの処理を行う手法が開示されている。この手法においては、画像データを縦横が所定の画素数で構成されたブロックに分割し、ブロック毎にバースト転送を行い、そのブロック内でデータの順番を入れ替えることによってブロック内データの反転、回転などの処理を行い、該当するブロックの書き込み、または読み出し順序を入れ替えることによって画像全体の反転や回転などの処理を実現する。

10

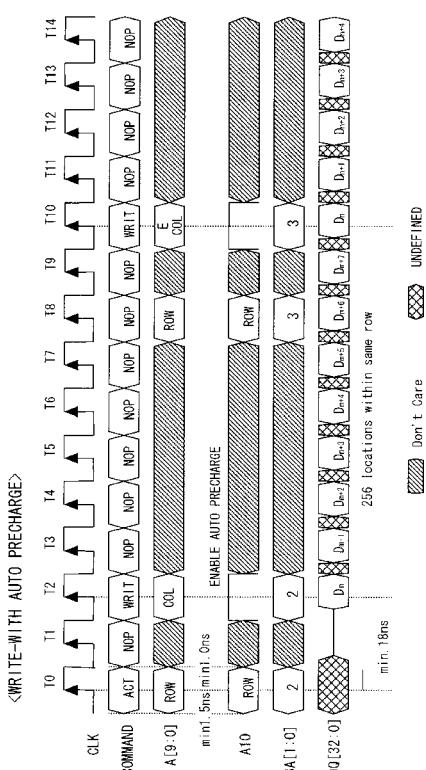

#### 【 0 0 0 9 】

ところで、S D R A M などのフレームメモリを用いてリアルタイム処理を行う場合には、S D R A M のバーストモードを使用するのが好ましい。そして、図 1 1 に示すように、このバーストモードにおいては、パイプライン処理を利用して連続してデータ転送を行うことが可能となる。ただし、バーストモードにおけるアドレスカウントは、シーケンシャルまたはインタリープによるカウントアップとなる。

20

#### 【 0 0 1 0 】

したがって、特許文献 1 および特許文献 2 に記載された技術に対しては、バーストモードを使用することが極めて困難である。具体的には、特許文献 1 および特許文献 2 に記載された方法においては、メモリへの 1 アクセスごとに、ロウアドレスおよびカラムアドレスを指定しなければならない。さらに、動画処理においては、メモリアクセスの処理速度を向上させる必要がある。

【特許文献 1】特開平 7 - 1 5 2 9 0 5 号公報

【特許文献 2】特開平 1 1 - 2 9 6 1 4 5 号公報

【特許文献 3】特開 2 0 0 1 - 3 4 3 9 6 6 号公報

30

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 1 1 】

したがって、この発明の目的は、比較的簡易な回路構成で反転表示を実行可能な画像処理装置およびこの画像処理装置を備えた画像表示装置を提供することにある。

#### 【課題を解決するための手段】

#### 【 0 0 1 2 】

上記目的を達成するために、この発明の第 1 の発明は、

順次入力される画像信号をライン単位に格納する第 1 のメモリ部と、

第 1 のメモリ部から出力される画像信号を複数ライン分格納することができる第 2 のメモリ部と、

40

第 1 のメモリ部および第 2 のメモリ部を制御する制御回路と、を有することを特徴とする画像処理装置である。

制御回路は、第 1 のメモリ部にライン単位に格納された画像信号のうち、第 1 のメモリ部の先頭アドレスから任意に設定された列反転位置に対応するアドレスまでの画像信号を第 1 のメモリ部に入力された第 1 の順序で第 2 のメモリ部に出力した後、列反転位置に対応するアドレスから先頭アドレスまでの画像信号を第 1 のメモリ部に入力された順序とは逆の第 2 の順序で出力し、当該出力された画像信号を第 2 のメモリ部に順次入力して複数のライン分の画像信号が格納されるように制御するとともに、第 2 のメモリ部に複数ライン分格納された画像信号のうち、第 1 の順序で第 1 のメモリ部から出力された画像信号は

50

第2のメモリ部に入力されたライン順で出力するとともに、第2の順序で第1のメモリ部から出力された画像信号は第2のメモリ部に格納されたライン順とは逆の順序で出力する制御を行うことが好ましい。

又は、制御回路は、第1のメモリ部にライン単位に格納された画像信号を出力する際、格納された画像信号のうち、第1のメモリ部の先頭アドレスから任意に設定された列反転位置に対応するアドレスまでの画像信号を第1のメモリ部に入力された第1の順序で第2のメモリ部に出力した後、列反転位置に対応するアドレスから先頭アドレスまでの画像信号を第1のメモリ部に入力された順序とは逆の第2の順序で第2のメモリ部に出力するように制御し、当該出力された画像信号を第2のメモリ部にライン単位に複数ライン分格納する際に、第1の順序で第1のメモリ部から出力された画像信号は第2のメモリ部に入力されたライン順で格納するとともに、第2の順序で第1のメモリ部から出力された画像信号は第2のメモリに入力されたライン順とは逆の順序で格納する制御を行うことが好ましい。

#### 【0013】

また、この発明の第2の発明は、

第1の発明による画像信号処理回路と、

画像信号処理回路から出力される信号に基づいて表示を行う表示器とを有することを特徴とする画像表示装置である。

#### 【発明の効果】

#### 【0014】

この発明による画像信号処理回路および画像処理装置によれば、比較的簡易な回路構成で反転表示を実行することができる。

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、この発明の実施形態について図面を参照しながら説明する。なお、以下の実施形態の全図においては、同一または対応する部分には同一の符号を付す。

#### 【0016】

なお、この発明の実施形態としては、ラインバッファ、フレームメモリの読み出アドレスまたは書き込みアドレスを監視して、ユーザにより任意に設定された値となった段階で「反転処理」を行うようにする場合について説明する。そして、画像データの書き込みおよび読み出しの構成が異なる、3通りの実施形態について説明する。

#### 【0017】

この発明において、1ラインとは、画像データに基づいて表示される画像を構成する一列に対応する画像データをいう。また、画像データに基づいて表示される画像の画素各々に対応する画像信号の集合により構成される。画像信号は、対応する画素の明るさに関する情報を有する信号である。すなわち、画像信号は画素信号ということもできる。また、本発明において、入力順とは逆の順序で第1のメモリ部から出力される画像信号は、1ライン分の画像信号または1ライン分より少ない画像信号であることが好ましい。

#### 【0018】

まず、図1に、以下に説明する実施形態における画像表示装置の全体構成を示す。すなわち、画像処理装置1101から出力される信号に基づいて表示器1102に画像が表示される。この画像処理装置1101は、画像信号処理回路であり、以下のそれぞれの実施形態において詳細に説明する。

#### 【0019】

なお、この発明は、大画面表示装置を平置きにして少人数コラボレーションを行うシステムなどに適用して好適なものであり、表示器を平置きにした際に、上下方向から互いに同じ出力画像を見たときに視認性を向上させた反転マルチ表示が可能となる。このような表示器1102としては、例えばCRT、プラズマディスプレイ、液晶ディスプレイ、ELディスプレイ、または電子放出素子を表示素子1102として用いた、フラットパネルディスプレイを用いることができる。なお、表示器1102を平置きするためには、表示

10

20

30

40

50

器に平置き可能なスタンド等の支持装置が備えられる。なお、平置きとは、表示器 1102 の表示面の中心における法線が表示器 1102 を設置する面の法線と交わる角度が 30° ~ 90° となるように、表示器 1102 が設置されていることをいう。

#### 【0020】

(第1の実施形態)

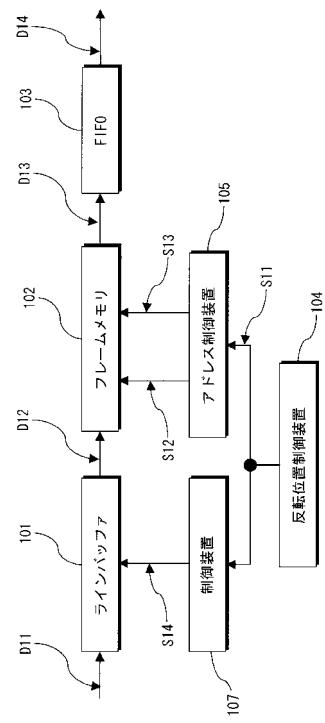

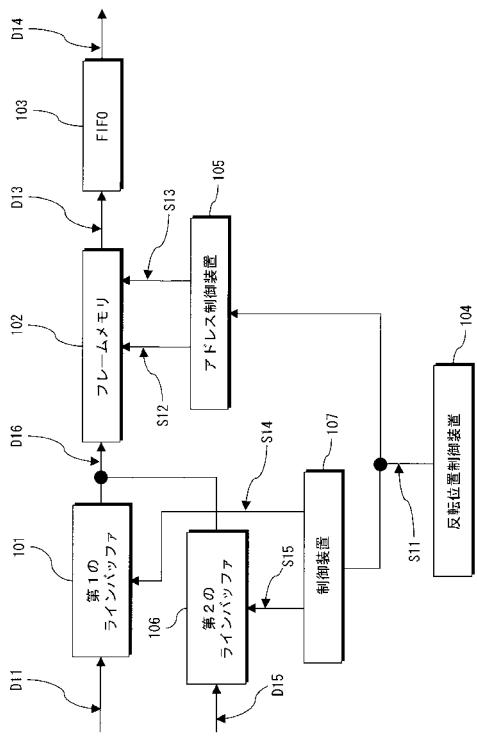

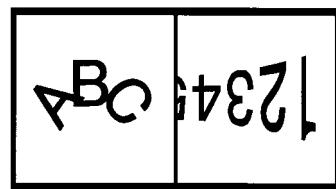

まず、この発明の第1の実施形態による画像処理装置について説明する。図2に、この発明の第1の実施形態による画像処理装置の構成を示す。なお、この第1の実施形態においては、フレームメモリへの画像データの書き込み時または読み込み時にアドレスが制御されて、ライン順反転制御が実行される場合について説明する。

#### 【0021】

図2に示すように、この第1の実施形態による画像処理装置においては、ラインバッファ 101、フレームメモリ 102、FIFO (First-In First-Out) 型バッファ (以下、FIFO) 103、反転位置制御装置 104、アドレス制御装置 105 および制御装置 107 を有して構成されている。第1の実施形態においてラインバッファ 101 が第1のメモリ部、フレームメモリ 102 が第2のメモリ部、制御装置 107 およびアドレス制御装置 105 が制御回路となる。なお、第1のメモリ部としては、列反転処理が可能なメモリであればよく、またハードウェア規模が小さくなるように容量の小さいメモリが好ましい。このようなメモリとしては、好適には、ラインバッファを用いることができる。

#### 【0022】

また、図2中、反転位置制御装置 104 から制御装置 107 およびアドレス制御装置 105 に供給される信号が、列反転位置指示信号 S11 であり、アドレス制御装置 105 からフレームメモリ 102 に供給される信号が、書き込みアドレス S12 および読み出しアドレス S13 である。また、制御装置 107 からラインバッファ 101 に供給される信号が、アドレス指定信号 S14 である。

#### 【0023】

また、この画像処理装置の内部において入出力されるデータとしては、入力画像データ D11、ラインバッファ 101 から読み出された画像データ D12、フレームメモリ 102 から読み出された画像データ D13、および FIFO 103 からの出力画像データ D14 などである。

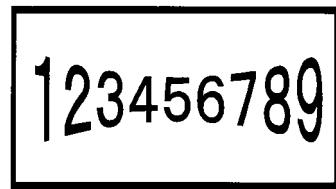

#### 【0024】

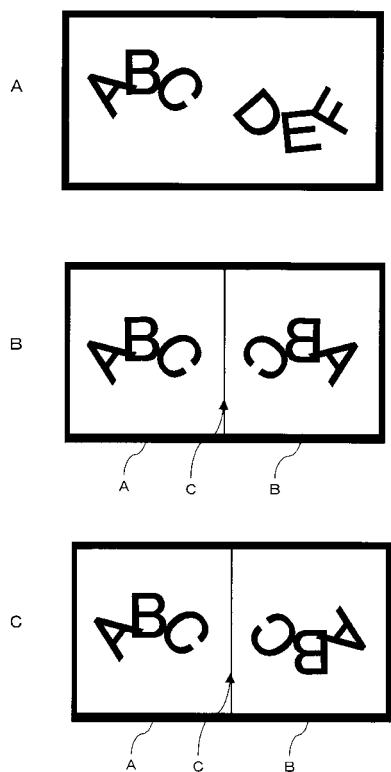

これらのデータのうち、入力画像データ D11 に基づいて、画像表示装置 (図示せず) で表示したときの仮想画像を図3Aに示す。このように表示される入力画像データ D11 は、まず、図2に示すラインバッファ 101 に供給され、ラインごとに格納される。また、ユーザが外部から列反転位置の情報を入力すると、この列反転位置の情報データが反転位置制御装置 104 に入力される。このユーザにより設定された列反転位置の情報に基づいた列反転位置指示信号 S11 が制御装置 107 に供給されることにより、列反転処理のアドレス指定信号 S14 が、制御装置 107 からラインバッファ 101 へ供給される。

#### 【0025】

次に、アドレス指定信号 S14 が供給されたラインバッファ 101 から、あらかじめユーザにより設定された列反転位置まで、画像データが順次カウントアップして出力される。そして、列反転位置になった段階で、ラインバッファ 101 に順次入力された画像データが、入力順とは逆の順序で出力されるようにラインバッファ 101 を制御する。すなわち、1ラインの出力画素数から既に出力した画素数を引いた数の位置を基準として、順次カウントダウンされて出力される。

#### 【0026】

このようにして、ラインバッファ 101 から読み出され、フレームメモリ 102 に供給される画像データ D12 に基づいて、画像表示装置 (図示せず) において表示したときの仮想画像を、図3Bに示す。画像データ D12 をもとに、仮に画像表示装置で表示するすれば、ラインバッファ 101 に入力される画像データに基づいて表示される画像の一部分と、該画像の一部分を画像のラインに対して垂直方向の軸中心で同じ面上に反転させた

10

20

30

40

50

画像とが表示される。

【0027】

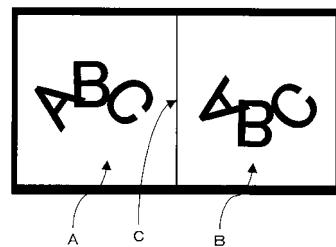

実際には、画像データD12がフレームメモリ102に書き込まれるデータとなるため、複数画素転送が行われたり、一旦非同期 FIFO（いすれも図示せず）に格納されクロック周波数がアップされたりして、フレームメモリ102に転送される。なお、図3Bにおいては、表示画面のほぼ中央が列反転位置となる場合を例として、この図3B中「Aが示す部分」が入力画像データD11の左側の画像、「Bが示す部分」が左側の画像を列反転させた画像、「Cが示す線」が、反転位置制御装置104から入力された列反転位置情報により決定される反転指示位置を示す。

【0028】

他方、図2に示すように、列反転位置指示信号S11は、アドレス制御装置105にも供給される。そして、アドレス制御装置105は、フレームメモリ102に入力される複数ライン分の画像信号のうちの一部分が、入力順で出力され、かつ他の部分がライン順が反転されて出力されるようにフレームメモリ102を制御する。すなわち、アドレス制御装置105は、列反転位置指示信号S11に従って、フレームメモリ102への書き込みアドレスS12および読み出アドレスS13のいすれか一方のアドレスに対して、列反転位置を基準としてライン順反転処理が実行される。

【0029】

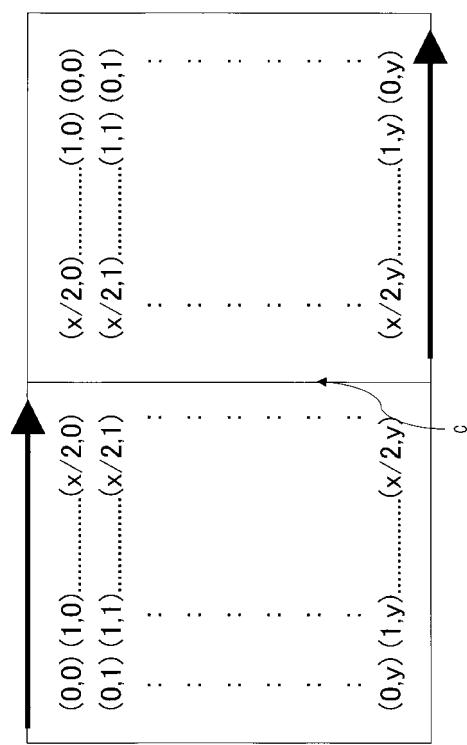

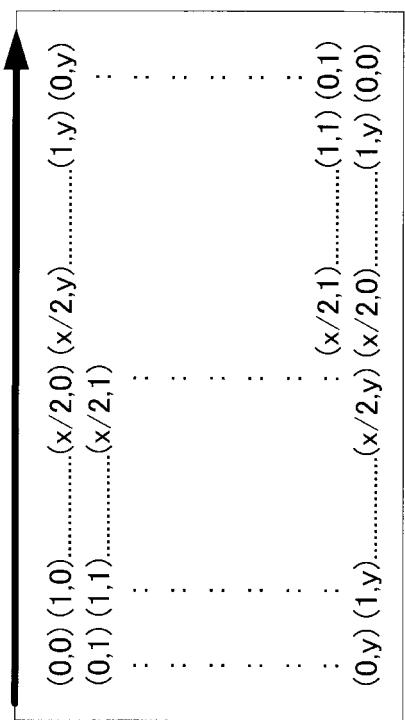

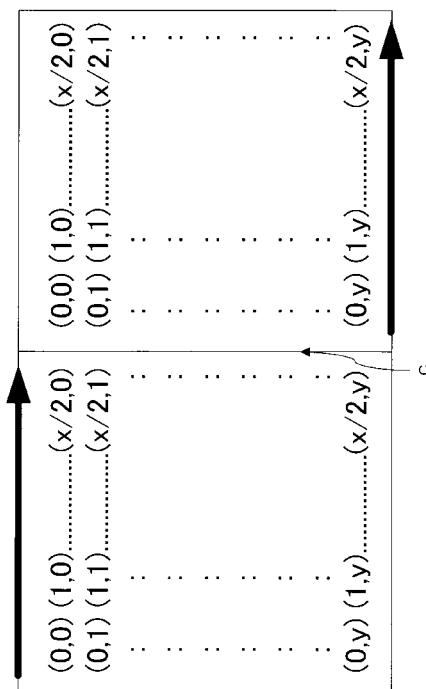

次に、入力画像データD11の左上端の座標を(0, 0)、右下端の座標を(x, y)とした場合における、フレームメモリ102から読み出される画像データD13の画素データの並び方の一例を図4および図5に示す。なお、図4および図5中の矢印は、読み出される順番を示す。図4は、フレームメモリ102への書き込み制御時において、ライン順反転処理を実行することなく、読み出しのときにライン順反転処理を行う場合の例である。

【0030】

すなわち、図4に示す画素データの並びに従うと、座標(0, 0)の位置から矢印の方向に沿って順次データが読み出され、列反転位置Cに達したところでライン順反転が行われる。他方、図5は、フレームメモリ102への書き込み制御時においてライン順反転処理が実行され、読み出し制御時においてライン順反転処理が実行されない場合の読み出し例を示す。すなわち、座標(0, 0)の位置から矢印の方向へ順にデータが読み出され、列反転位置Cに関係なく、そのまま順次データが読み出される。なお、どちらの構成を採用するかは、回路構成によって任意に決定することが可能である。

【0031】

以上のように、ユーザにより決定され、反転位置制御装置104に入力された列反転位置情報に基づき、その列反転位置において、読み込み制御時または書き込み制御時にライン順反転処理が実行される。そして、フレームメモリ102から読み出された画像データD13は、ラインごとに一旦 FIFO103に格納されて、出力のタイミングにあわせて出力されることになる。これにより、画像データD13をもとに、仮に画像表示装置で表示するとすれば、フレームメモリ102に入力される画像データに基づいて表示される画像の一部分と、該画像の一部分を、画像のラインと平行方向の軸を中心に同じ面上に反転した画像とが表示される。

【0032】

そして、出力される出力画像データD14をもとに、画像表示装置（図示せず）において表示されるとすれば、図3Cに示すように、ラインバッファ101に入力される画像データに基づいて表示される画像の一部分が、他の部分に対して同じ面上で回転した状態であって逆の方向に表示される。すなわち、反転マルチ表示とすることが可能となる。

【0033】

（第2の実施形態）

次に、この発明の第2の実施形態による画像処理装置について説明する。図6に、この第2の実施形態による画像処理装置を示す。なお、この第2の実施形態においては、フレ

10

20

30

40

50

ームメモリから画像データを読み出す時にライン順反転処理を実行する場合について説明する。

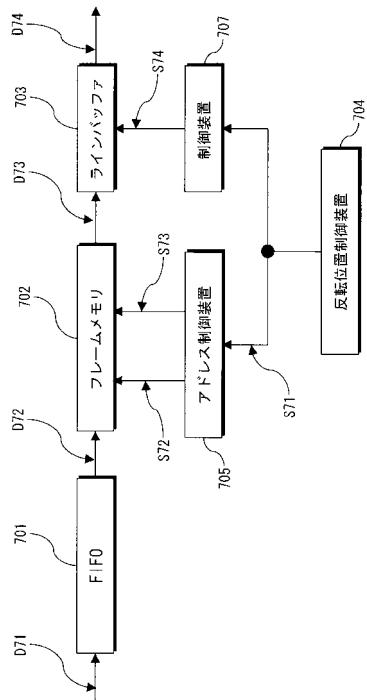

【0034】

図6に示すように、この第2の実施形態による画像処理装置は、FIFO701、フレームメモリ702、ラインバッファ703、反転位置制御装置704、アドレス制御装置705および制御装置707を有して構成されている。この第2の実施形態においては、第1のメモリ部がラインバッファ703、第2のメモリ部がフレームメモリ702、制御回路が制御装置707およびアドレス制御装置705である。

【0035】

また、図6中、外部からFIFO701に入力されるデータが入力画像データD71、このFIFO701から読み出されてフレームメモリ702に供給されるデータが画像データD72、フレームメモリ702から読み出されてラインバッファ703に供給されるデータが画像データD73、および、ラインバッファ703から出力されるデータが出力画像データD74である。また、反転位置制御装置704から列反転位置指示信号S71が出力されて、アドレス制御装置705および制御装置707に供給される。また、アドレス制御装置705から書き込みアドレスS72および読み出アドレスS73が出力されて、フレームメモリ702に供給される。また、制御装置707から列反転処理のアドレス指定信号S74が、ラインバッファ703に供給される。

【0036】

まず、外部から供給される入力画像データD71は、ラインごとに一旦FIFO701に格納される。FIFO701からフレームメモリ702の書き込みタイミングに従って読み出された画像データD72が、アドレス制御装置705から出力される書き込みアドレスS72に従ってフレームメモリ702に格納される。

【0037】

このフレームメモリ702に格納される画像データとしては、図7に示すデータを一例として挙げることができる。この図7に示す例においては、入力画像データD71の列反転位置Cから左側のデータだけがフレームメモリ702に格納される。フレームメモリ702の列反転位置の右側に格納されるデータは、入力画像データD71の列反転位置の左側のデータを2度読むことによって生成され、フレームメモリ702に格納される。

【0038】

そして、アドレス制御装置705は、フレームメモリ702に入力される複数ライン分の画像信号のうちの一部分が、入力順で出力され、かつ他の部分がライン順が反転されて出力されるようにフレームメモリ702を制御する。すなわち、アドレス制御装置705は、列反転位置指示信号S71に従って、フレームメモリ702への読み出アドレスS73のアドレスに対して、列反転位置を基準としてライン順反転処理が実行される。

【0039】

これにより、フレームメモリ702から読み出された画像データD73をもとに、仮に画像表示装置で表示するすれば、フレームメモリ702に入力される画像データに基づいて表示される画像の一部分と、該画像の一部分を、画像のラインと平行方向の軸を中心と同じ面上に反転した画像とが表示される。

【0040】

図8に、以上のようにして読み出された画像データD73に基づき、画像表示装置(図示せず)において表示する際の仮想画像の一例を示す。図8中「Aが示す部分」が入力画像データD71の左側部分を示し、「Bが示す部分」が入力画像データの左側「Aが示す部分」を縦方向に反転させた画像である。なお、「Cが示す部分」は、ユーザにより設定され、反転位置制御装置704に記憶された列反転位置である。

【0041】

そして、フレームメモリ702から読み出された画像データD73が、ラインごとにラインバッファ703に供給されて、格納される。その後、制御装置707から出力されるアドレス指定信号S74により、ラインバッファ703に格納されたデータが、出力のタ

10

20

30

40

50

イミングに従って読み出される。このとき、列反転位置情報を含むアドレス指定信号 S 7 4 に従って、列反転位置まで画像データを順次カウントアップして出力される。そして列反転位置になった段階で、ラインバッファ 7 0 3 に順次入力された画像データが、入力順とは逆の順序で出力されるようにラインバッファ 7 0 3 を制御する。

【 0 0 4 2 】

すなわち、1 ラインの出力画素数の位置を基準として、列反転位置まで順次カウントダウンされて出力される。以上のように、ラインバッファ 7 0 3 の制御装置により列反転処理が実行され、出力画像データ D 7 4 が出力される。

【 0 0 4 3 】

そして、出力される出力画像データ D 7 4 をもとに、画像表示装置において表示されるとすれば、ラインバッファ 7 0 3 に入力される画像データに基づいて表示される画像の一部分と、該画像の一部分を画像のラインに対して垂直方向の軸を中心に反転した画像と同じ面上に表示される。

【 0 0 4 4 】

以上により、出力される出力画像データ D 7 4 をもとに、画像表示装置（図示せず）において表示されるとすれば、図 3 C に示すように、ラインバッファ 1 0 1 に入力される画像データに基づいて表示される画像の一部分が、他の部分に対して同じ面上で回転した状態であって逆の方向に表示される。すなわち、反転マルチ表示が可能なデータとして出力することが可能となる。

【 0 0 4 5 】

（第 3 の実施形態）

次に、この発明の第 3 の実施形態による画像処理装置について説明する。図 9 に、この第 3 の実施形態による画像処理装置を示す。なお、第 1 の実施形態におけると同様の構成要素については、同一の符号を付す。また、この第 3 の実施形態においては、フレームメモリへの画像データの書き込み時においてライン順反転処理を実行する場合について説明する。

【 0 0 4 6 】

図 9 に示すように、この第 3 の実施形態による画像処理装置は、第 1 のラインバッファ 1 0 1、フレームメモリ 1 0 2 および FIFO 1 0 3、反転位置制御装置 1 0 4、アドレス制御装置 1 0 5、第 2 のラインバッファ 1 0 6、および制御装置 1 0 7 を有して構成されている。第 3 の実施形態においては、第 1 のラインバッファ 1 0 1 および第 2 のラインバッファ 1 0 6 が第 1 のメモリ部、フレームメモリ 1 0 2 が第 2 のメモリ部、制御装置 1 0 7 とアドレス制御装置 1 0 5 が制御回路である。

【 0 0 4 7 】

また、図 9 中、第 1 の実施形態におけると同様のデータは、外部から第 1 のラインバッファ 1 0 1 に入力されて格納される第 1 の入力画像データ D 1 1、フレームメモリ 1 0 2 から読み出されて FIFO 1 0 3 に供給される画像データ D 1 3 および、 FIFO 1 0 3 から出力される出力画像データ D 1 4 である。この第 3 の実施形態においては、さらに外部から第 2 の入力画像データ D 1 5 が第 2 のラインバッファ 1 0 6 に入力され、第 1 のラインバッファ 1 0 1 および第 2 のラインバッファ 1 0 6 から読み出されたデータは、画像データ D 1 6 としてフレームメモリ 1 0 2 に供給される。

【 0 0 4 8 】

また、反転位置制御装置 1 0 4 により、制御装置 1 0 7 およびアドレス制御装置 1 0 5 に供給される列反転位置指示信号 S 1 1 は、図 1 0 中「 C が示す部分 」の列反転位置を指示するための命令信号である。また、書き込みアドレス S 1 2、読み出アドレス S 1 3 およびアドレス指定信号 S 1 4、S 1 5 に関しては、第 1 の実施形態におけると同様であるので、その詳細な説明は省略する。

【 0 0 4 9 】

まず、第 1 の入力画像データ D 1 1 が第 1 のラインバッファ 1 0 1 に入力されて格納されるとともに、第 2 の入力画像データ D 1 5 が第 2 のラインバッファ 1 0 6 に入力されて

10

20

30

40

50

格納される。

【0050】

また、反転位置制御装置104から出力される列反転位置指示信号S11が、制御装置107に、第1のラインバッファ101および第2のラインバッファ106のイネーブルおよび読み出し開始位置が制御される。

【0051】

すなわち、第1のラインバッファ101の読み出しイネーブルが可の場合には、第2のラインバッファ106の読み出しイネーブルが不可とされる。他方、第1のラインバッファ101の読み出しイネーブルが不可の場合には、第2のラインバッファ106の読み出しイネーブルが可とされる。また、第2のラインバッファ106からの画像データの読み出し時に列反転処理が実行される。 10

【0052】

具体的には、以下のように第1のラインバッファ101および第2のラインバッファ106から画像データが読み出される。

【0053】

まず、アドレス指定信号S14が供給された第1のラインバッファ101から、あらかじめユーザにより設定された列反転位置まで画像データが順次カウントアップして出力される。そして、列反転位置になった段階で、アドレス指定信号S15により、第2のラインバッファ106に順次入力された画像データが、入力順とは逆の順序で出力される。すなわち、1ラインの出力画素数から既に出力した画素数を引いた数の位置を基準として、第2のラインバッファ106から画像データが順次カウントダウンされて出力される。 20

【0054】

このようにして、第1のラインバッファ101からの出力データと第2のラインバッファ106からの出力データとが切り換えられて合成されたデータが画像データD16として、フレームメモリ102に供給される。

【0055】

これにより、画像データD16をもとに、仮に画像表示装置で表示するとすれば、第1のラインバッファ101と第2のラインバッファ106に入力された画像データに基づいて表示される画像の一部分と、他の画像の一部分を画像のラインに対して垂直方向の軸を中心に同じ面上に反転した画像とが表示される。 30

【0056】

次に、フレームメモリ102への書き込みは、書き込みアドレスS12によって制御される。また、フレームメモリ102からの読み出しへは、読み出アドレスS13によって制御される。また、書き込みアドレスS12と読み出アドレスS13とは、アドレス制御装置105によって生成される。

【0057】

このアドレス制御装置105により反転位置制御装置104から出力される列反転位置指示信号S11に従って、書き込みアドレスS12におけるライン順反転が実行される。アドレス制御装置105は、フレームメモリ102に入力される複数ライン分の画像信号のうちの一部分が、入力順で出力され、かつ他の部分がライン順が反転されて出力されるようにフレームメモリ102を制御する。 40

【0058】

すなわち、アドレス制御装置105は、列反転位置指示信号S11に従って、フレームメモリ102への書き込みアドレスS12に対して、列反転位置を基準としてライン順反転処理が実行される。したがって、フレームメモリ102から順次読み出された画像データD13をもとに、仮に画像表示装置で表示するとすれば、フレームメモリ102に入力された画像データに基づいて表示される画像の一部分と、該画像の一部分を、画像のラインと平行方向の軸を中心に同じ面上に反転した画像と、が表示される。

【0059】

そして、フレームメモリ102から読み出された画像データD13は、FIFO103 50

に格納される。続いて、画像データD13がFIFO103に格納された後、画像表示装置（図示せず）のタイミングにあわせて出力画像データD14として出力される。

【0060】

出力される出力画像データD14をもとに、仮に画像表示装置（図示せず）で表示するすれば、第1のラインバッファ101および第2のラインバッファ106に入力される画像データに基づいて表示される画像の一部分が、他の部分に対して同じ面上で回転する方向で逆の方向に表示される。すなわち、反転マルチ表示とすることが可能となる。

【0061】

ここで、一例として、入力画像データD11に基づいて、画像表示装置（図示せず）で表示したときの仮想画像が図3Aの画像であり、入力画像データD15に基づいて、画像表示装置（図示せず）において表示されたときの仮想画像が図10Aの画像であるとする。このとき、この第3の実施形態による画像処理装置から出力される出力画像データD14に基づいて、不図示の画像表示装置で表示したときの仮想画像は図10Bの画像となる。この図10Bは、それぞれの入力画像データD11、D15をもとにした仮想画像における左端からの表示範囲が設定された例を示す。

【0062】

また、この表示範囲の位置は、ユーザにより設定されて外部から入力された反転位置の指示情報データに従って、アドレス制御装置105および制御装置107に設定された表示範囲のデータに応じて、表示範囲を変えることが可能である。

【0063】

以上、この発明の実施形態について具体的に説明したが、この発明は、上述の実施形態に限定されるものではなく、この発明の技術的思想に基づく各種の変形が可能である。

【0064】

例えば、上述の実施形態において挙げた数値はあくまでも例に過ぎず、必要に応じてこれと異なる数値を用いてもよい。

【0065】

また、例えば上述の第1の実施形態においては、図4および図5において、反転位置Cを、 $\times/2$ としているが、この反転位置Cの列反転座標はあくまで一例であり、他の任意の列反転座標を選択することも可能であり、必ずしも全列反転座標の半分( $\times/2$ )である必要はない。また、図8および図10Bに示す表示例は、あくまでも説明における一例であり、必ずしも表示画面の中央において反転処理が実行されることを示すものではない。

【0066】

また、例えば、上述の実施形態において採用される入力信号としては、インターレース信号とプログレッシブ信号とのいずれの信号であっても良く、必ずしも一方の信号に限定されるものではない。

【0067】

また、例えば上述の実施形態においては、ラインごとの反転処理について説明したが、必ずしも1ライン毎に限定する趣旨ではなく、隣接する2ラインを同時に走査して画像を表示する方式である、いわゆるラインダブルなどの、複数のラインを走査して画像を表示する方式を採用した場合においても、この発明を適用することができ、同様の効果を得ることができる。

【0068】

また、FIFOは、その後段に位置するメモリ部に入力される画像データの転送速度と、メモリ部に画像データを書き込む速度との差を緩和するための一時記憶装置である。したがって、予め画像データの転送速度をメモリ部の画像データ書き込み速度にあわせるよう構成すれば、FIFOを必ずしも用いる必要はない。

【図面の簡単な説明】

【0069】

【図1】この発明の実施形態による画像表示装置の全体の構成を示すブロック図である。

10

20

30

40

50

【図2】この発明の第1の実施形態による画像処理装置の構成を示すブロック図である。

【図3】この発明の第1の実施形態による、入力画像データをもとに表示された仮想画像の一例を示す略線図、ラインバッファから読み出された画像データをもとに表示された仮想画像の一例を示す略線図、および反転マルチ出力画像データをもとに表示された仮想画像の一例を示す略線図である。

【図4】この発明の第1の実施形態による画像処理において、フレームメモリから読み出す順序を説明するための略線図である。

【図5】この発明の第1の実施形態による画像処理において、フレームメモリから読み出す順序を説明するための略線図である。

【図6】この発明の第2の実施形態による画像処理装置の構成を示すブロック図である。10

【図7】この発明の第2の実施形態による画像処理において、フレームメモリから読み出す順序を説明するための略線図である。

【図8】この発明の第2の実施形態による画像処理において、フレームメモリから読み出された画像データをもとに表示された仮想画像を示す略線図である。

【図9】この発明の第3の実施形態による画像処理装置の構成を示すブロック図である。

【図10】この発明の第3の実施形態による入力画像データをもとに表示された仮想画像の一例および出力画像データをもとに表示された仮想画像の一例を示す略線図である。

【図11】従来技術によるSDRAMのバーストモードを説明するためのタイミングチャートである。

【符号の説明】

【0070】

- 101 第1のラインバッファ

- 102, 702 フレームメモリ

- 103, 701 FIFO

- 104 反転位置制御装置

- 105 アドレス制御装置

- 106 第2のラインバッファ

- 107, 707 制御装置

- 703 ラインバッファ

- 704 反転位置制御装置

- 705 アドレス制御装置

- D11, D15, D71 入力画像データ

- D12, D13, D16 画像データ

- D14, D74 出力画像データ

- D72, D73 画像データ

- S11 列反転位置指示信号

- S12, S72 書込アドレス

- S13, S73 読出アドレス

- S14, S15, S74 アドレス指定信号

- S71 列反転位置指示信号

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 四 9 】

【図10】

A

B

【 図 1 1 】

---

フロントページの続き

| (51) Int.Cl.  |       | F I       |        |       |         |

|---------------|-------|-----------|--------|-------|---------|

| <i>G 09 G</i> | 3/30  | (2006.01) | G 09 G | 3/20  | 6 3 1 D |

| <i>G 09 G</i> | 3/36  | (2006.01) | G 09 G | 3/20  | 6 6 0 F |

| <i>G 09 G</i> | 3/28  | (2006.01) | G 09 G | 3/22  | D       |

| <i>H 04 N</i> | 5/262 | (2006.01) | G 09 G | 5/36  | 5 2 0 K |

|               |       |           | G 09 G | 3/30  | H       |

|               |       |           | G 09 G | 3/36  |         |

|               |       |           | G 09 G | 3/28  | R       |

|               |       |           | H 04 N | 5/262 |         |

審査官 長井 真一

(56)参考文献 特開2002-251179 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |                                       |

|--------|---------------------------------------|

| G 09 G | 3 / 2 0 - 3 / 3 6 , 5 / 0 0 - 5 / 3 6 |

| G 06 T | 1 / 6 0                               |

| H 04 N | 5 / 2 6 2                             |