(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-147056

(P2009-147056A)

(43) 公開日 平成21年7月2日(2009.7.2)

(51) Int.Cl.

H01L 27/146 (2006.01)

H01L 31/10 (2006.01)

F 1

H01L 27/14

H01L 31/10

テーマコード(参考)

A 4M118

G 5FO49

審査請求 未請求 請求項の数 4 O L (全 13 頁)

(21) 出願番号

(22) 出願日特願2007-321779 (P2007-321779)

平成19年12月13日 (2007.12.13)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100066980

弁理士 森 哲也

(74) 代理人 100075579

弁理士 内藤 嘉昭

(74) 代理人 100127384

弁理士 坊野 康博

(72) 発明者 北野 洋司

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 4M118 AA10 AB01 BA14 CA03 DD01

DD12 EA01 EA14 FA06

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】一画素の含まれるMOSトランジスタの個数を低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】光信号を電気信号に変換する複数の画素を備えるCMOSイメージセンサであって、P型Si基板に形成されたフォトダイオード1と、フォトダイオード1のカソード上に絶縁膜を介して形成されたSi層と、Si層に形成されたMOSトランジスタ2と、を一画素10内に有し、MOSトランジスタ2のソース又はドレイン(即ち、S/D)の一方は行方向に向かって延びるVDDラインに接続され、MOSトランジスタ2のS/Dの他方は行方向に向かって延びるROWラインに接続され、且つ、MOSトランジスタ2のゲート電極は行方向と交差する列方向に向かって延びるCOLUMNラインに接続されている。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

光信号を電気信号に変換する複数の画素を備える半導体装置であって、

半導体基板に形成されたフォトダイオードと、

前記フォトダイオードのカソード上に絶縁膜を介して形成された半導体層と、

前記半導体層に形成された第1MOSトランジスタと、を一画素内に有し、

前記第1MOSトランジスタのソース又はドレインの一方は一の方向に向かって延びる

電源線に接続され、前記第1MOSトランジスタのソース又はドレインの他方は前記一の

方向に向かって延びる第1信号線に接続され、且つ、前記第1MOSトランジスタのゲート電極は前記一の方向と交差する他の方向に向かって延びる第2信号線に接続されている

ことを特徴とする半導体装置。 10

**【請求項 2】**

前記半導体基板に形成された第2MOSトランジスタを前記一画素内に有し、

前記第2MOSトランジスタのソース又はドレインの一方は前記カソードに接続され、

前記第2MOSトランジスタのソース又はドレインの他方は前記電源線に接続され、且つ、

前記第2MOSトランジスタのゲート電極は前記他の方向に向かって延びる第3信号線に接続されていることを特徴とする請求項1に記載の半導体装置。 20

**【請求項 3】**

光信号を電気信号に変換する複数の画素を備える半導体装置の製造方法であって、

前記画素となる領域の半導体基板にフォトダイオードを形成する工程と、

前記フォトダイオードのカソード上に第1半導体層を形成する工程と、

前記第1半導体層上に第2半導体層を形成する工程と、

前記第2半導体層及び前記第1半導体層をエッチングして、前記第2半導体層及び前記

第1半導体層を貫く第1溝を形成する工程と、

前記第1溝に支持体を形成する工程と、

前記第2半導体層をエッチングして、前記第1半導体層を露出させる第2溝を形成する

工程と、

前記第2溝を介して前記第1半導体層をエッチングすることにより、前記第2半導体層

と前記カソードとの間に空洞部を形成する工程と、

前記空洞部内に絶縁膜を形成して埋め込む工程と、

前記第2半導体層に第1MOSトランジスタを形成する工程と、を含むことを特徴とする

半導体装置の製造方法。 30

**【請求項 4】**

前記画素となる領域の前記半導体基板に第2MOSトランジスタを形成する工程、をさ

らに含み、

前記第2MOSトランジスタを形成する工程では、当該第2MOSトランジスタのソー

ス又はドレインの一方を前記カソードの一部と重なるように形成することを特徴とする請

求項3に記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置及びその製造方法に関し、特に、光信号を電気信号に変換する技

術に関する。

**【背景技術】****【0002】**

これまで主として用いられているCMOSイメージセンサとして、APS(Active

Pixel Sensor)と呼ばれるタイプがある。APS型のイメージセンサは

一画素が受光部であるフォトダイオード(PD)と、3~4個のMOSトランジスタからなる構造を有する。

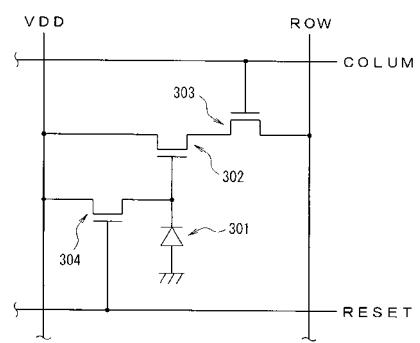

図8は、従来例に係るCMOSイメージセンサの構成例を示す回路図である。 50

## 【0003】

図8に示すCMOSイメージセンサはAPS型であり、行方向に向かって延びる電源線（以下、Vddライン）及び信号線（以下、ROWライン）と、列方向に向かって延びる読み出し線（以下、COLUMNライン）及びリセット線（以下、RESETライン）により囲まれる1画素内に、受光部301と、検出用のMOSトランジスタ302と、読み出し用のMOSトランジスタ303と、リセット用のMOSトランジスタ304と、を含んで構成されている。図8に示すように、受光部はフォトダイオード（PD: Photo Diode）からなり、そのカソードがMOSトランジスタ302のゲート電極に接続されている。

【特許文献1】特開平11-177886号公報 10

【特許文献2】特開平11-317512号公報

【特許文献3】特開2005-354024号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

ところで、図8に示したようなAPS型のイメージセンサでは、1画素内に3～4個のMOSトランジスタを必要とするため、受光部の開口率が低くなり、また受光部の面積が小さくなる。このため、画素の感度が低くなりがちであり、光信号のSN比（Signal to Noise ratio）が低下しやすいという問題があった。

そこで、本発明は、このような事情に鑑みてなされたものであって、一画素の含まれるMOSトランジスタの個数を低減できるようにした半導体装置及びその製造方法の提供を目的とする。 20

## 【課題を解決するための手段】

## 【0005】

〔発明1、2〕 上記問題点を解決するために、発明1の半導体装置は、光信号を電気信号に変換する複数の画素を備える半導体装置であって、半導体基板に形成されたフォトダイオードと、前記フォトダイオードのカソード上に絶縁膜を介して形成された半導体層と、前記半導体層に形成された第1MOSトランジスタと、を一画素内に有し、前記第1MOSトランジスタのソース又はドレインの一方は一の方向に向かって延びる電源線に接続され、前記第1MOSトランジスタのソース又はドレインの他方は前記一の方向に向かって延びる第1信号線に接続され、且つ、前記第1MOSトランジスタのゲート電極は前記一の方向と交差する他の方向に向かって延びる第2信号線に接続されていることを特徴とするものである。ここで、「第1信号線」は例えばROWラインであり、「第2信号線」は例えばCOLUMNラインである。 30

## 【0006】

発明2の半導体装置は、発明1の半導体装置において、前記半導体基板に形成された第2MOSトランジスタを前記一画素内に有し、前記第2MOSトランジスタのソース又はドレインの一方は前記カソードに接続され、前記第2MOSトランジスタのソース又はドレインの他方は前記電源線に接続され、且つ、前記第2MOSトランジスタのゲート電極は前記他の方向に向かって延びる第3信号線に接続されていることを特徴とするものである。ここで、本発明の「第3信号線」は例えばRESETラインである。 40

## 【0007】

発明1、2の半導体装置によれば、受光量に応じて大きさが変化するカソードの電位をバックゲートバイアスとして、第1MOSトランジスタのチャネルとなる領域（以下、チャネル領域）にバックゲートバイアスを印加することができ、受光量に応じて第1MOSトランジスタの閾値をシフトさせることができる。そして、この閾値シフトを第1信号線を介して電流信号として読み出すことにより、光信号を電気信号に変換する（即ち、光電変換する）ことができる。従って、一画素内に形成されるMOSトランジスタの数を従来の3～4個から1～2個に減らすことができ、各画素における開口率の向上、受光部面積の拡大、又は、それらによる画素の高感度化（即ち、光信号のSN比の向上）を図ること

ができる。

また、発明 2 の半導体装置によれば、カソードの電位を電源線の電位に設定する（即ち、カソードに蓄積された電荷を電源線に排出してリセットする）ことができるので、第 1 MOS ランジスタの閾値を直ちに初期状態（即ち、バックゲートバイアスが印加されていない状態）に戻すことができる。

#### 【0008】

〔発明 3、4〕 発明 3 の半導体装置の製造方法は、光信号を電気信号に変換する複数の画素を備える半導体装置の製造方法であって、前記画素となる領域の半導体基板にフォトダイオードを形成する工程と、前記フォトダイオードのカソード上に第 1 半導体層を形成する工程と、前記第 1 半導体層上に第 2 半導体層を形成する工程と、前記第 2 半導体層及び前記第 1 半導体層をエッチングして、前記第 2 半導体層及び前記第 1 半導体層を貫く第 1 溝を形成する工程と、前記第 1 溝に支持体を形成する工程と、前記第 2 半導体層をエッチングして、前記第 1 半導体層を露出させる第 2 溝を形成する工程と、前記第 2 溝を介して前記第 1 半導体層をエッチングすることにより、前記第 2 半導体層と前記カソードとの間に空洞部を形成する工程と、前記空洞部内に絶縁膜を形成して埋め込む工程と、前記第 2 半導体層に第 1 MOS ランジスタを形成する工程と、を含むことを特徴とするものである。ここで、「第 1 半導体層」は例えば単結晶のシリコンゲルマニウム（SiGe）層であり、「第 2 半導体層」は例えば単結晶のシリコン（Si）層である。単結晶の SiGe 層、及び、単結晶の Si 層は例えばエピタキシャル成長法により形成する。

#### 【0009】

発明 4 の半導体装置の製造方法は、発明 3 の半導体装置の製造方法において、前記画素となる領域の前記半導体基板に第 2 MOS ランジスタを形成する工程、をさらに含み、前記第 2 MOS ランジスタを形成する工程では、当該第 2 MOS ランジスタのソース又はドレインの一方を前記カソードの一部と重なるように形成することを特徴とするものである。

#### 【0010】

発明 3 の半導体装置の製造方法によれば、フォトダイオードと、フォトダイオードのカソード上に絶縁膜を介して形成された第 2 半導体層と、第 2 半導体層に形成された第 1 MOS ランジスタと、を一画素内に形成することができ、発明 1 の半導体装置を製造することができる。また、発明 4 の半導体装置の製造方法によれば、上記のフォトダイオード及び第 1 MOS ランジスタに加えて、ソース又はドレインの一方がフォトダイオードのカソードに接続された第 2 MOS ランジスタを一画素内に形成することができ、発明 2 の半導体装置を製造することができる。

#### 【発明を実施するための最良の形態】

#### 【0011】

以下、本発明の実施の形態を添付図面を参照して説明する。なお、以下に説明する各図において、同一部分には同一符号を付し、その重複する説明は省略する。

##### (1) 第 1 実施形態

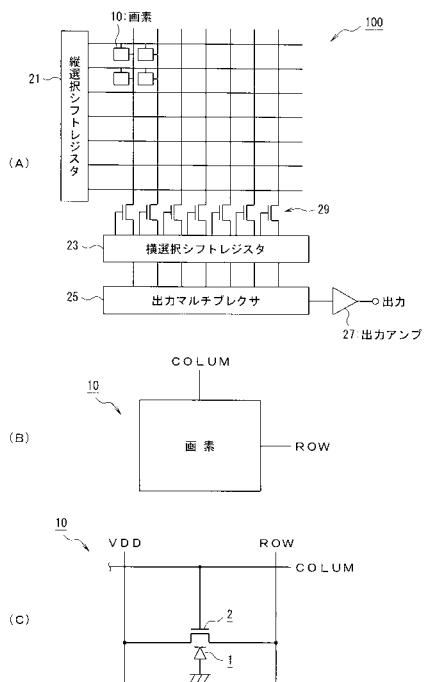

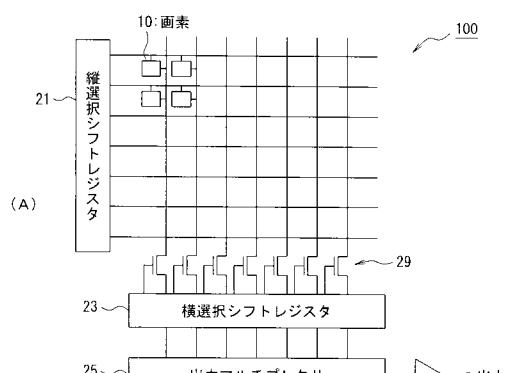

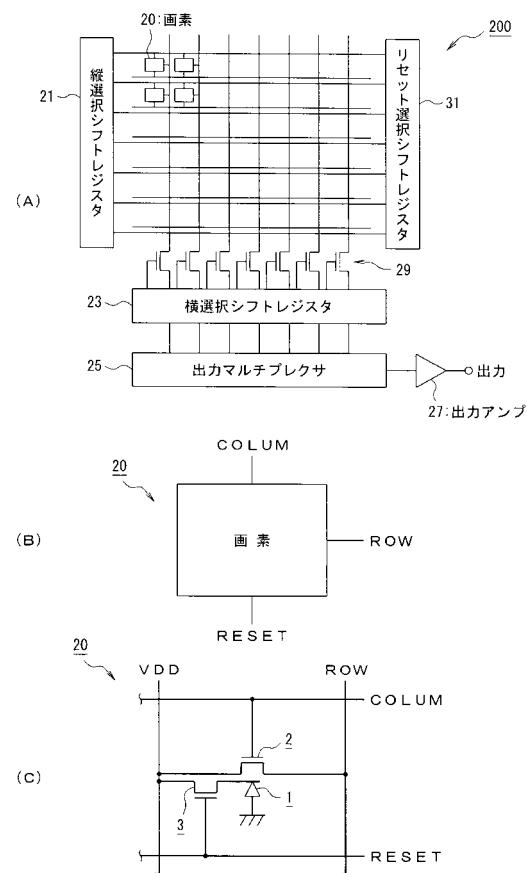

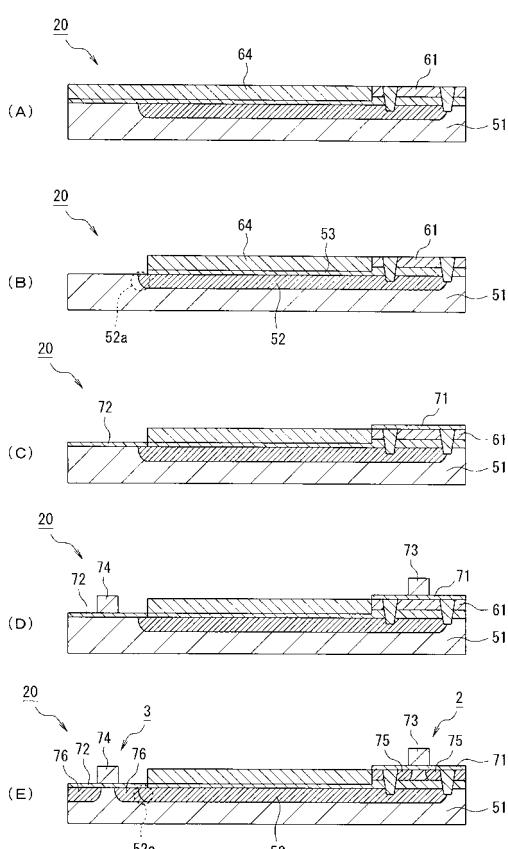

図 1 は本発明の第 1 実施形態に係るイメージセンサ 100 の構成例を示す図であり、図 1 (A) はイメージセンサ 100 の全体構成の一例を示す図、図 1 (B) は画素選択に係る配線（ライン）を示す図、図 1 (C) は画素 10 の構成例を示す図である。

#### 【0012】

図 1 (A) に示すように、このイメージセンサ 100 は、平面視で縦方向及び横方向に一定間隔で配置された（即ち、アレイ状に配置された）複数の画素 10 と、これら複数の画素群（即ち、画素アレイ）の周囲に配置された縦選択シフトレジスタ 21 及び横選択シフトレジスタ 23 と、出力マルチプレクサ 25 と、出力アンプ 27 と、を含んで構成されている。

#### 【0013】

図 1 (B) 及び (C) に示すように、画素アレイに含まれる一つの画素（以下、一画素）10 は、行方向（即ち、平面視で縦方向）に向かって延びる Vdd ライン及び ROW ラ

10

20

30

40

50

インと、列方向（即ち、平面視で横方向）に向かって延びる C O L U M ラインとに隣接しており、一画素 1 0 内に受光部 1 と、受光部 1 で生じた電気信号を読み出すための M O S トランジスタ 2 と、を含んで構成されている。

#### 【 0 0 1 4 】

図 1 ( C ) に示す M O S トランジスタ 2 は例えば N M O S であり、そのソース又はドレン（以下、 S / D ）の一方は R O W ラインに接続され、 S / D の他方は V D D ラインに接続されている。さらに、 M O S トランジスタ 2 のゲート電極は C O L U M ラインに接続されている。また、受光部 1 は例えばフォトダイオード（ P D ）からなり、そのカソードの一部が M O S トランジスタ 2 のチャネル領域の裏面側に配置され、そのアノードが接地電位に接続されている。

10

#### 【 0 0 1 5 】

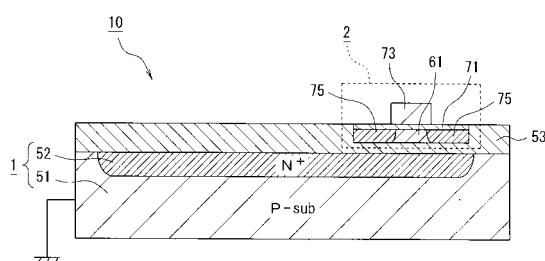

図 2 は、画素 1 0 の断面構成の一例を示す図である。図 2 に示すように、フォトダイオード 1 は例えば p 型 S i 基板 5 1 と、 P 型 S i 基板 5 1 の表面近傍に形成された N 型層 5 2 を含んで構成されている。この P N 接合を含むフォトダイオード 1 では、 P 型 S i 基板 5 1 がアノードで N 型層 5 2 がカソードである。また、 N 型層 5 2 の一部の真上には絶縁膜 5 3 を介して S i 層 6 1 が設けられており、この S i 層 6 1 に M O S トランジスタ 2 が形成されている。図 2 に示すように、この M O S トランジスタ 2 は、 S i 層 6 1 上に形成されたゲート絶縁膜 7 1 と、ゲート絶縁膜 7 1 上に形成されたゲート電極 7 3 と S i 層 6 1 に形成された S / D 層 7 5 と、を含んで構成されており、例えば S O I 構造を有する完全空乏（ F u l l y D e p l e t e d : F D ）型となっている。

20

#### 【 0 0 1 6 】

イメージセンサ 1 0 0 を構成する各々の画素 1 0 では、光がフォトダイオード 1 に照射されることにより電子 - 正孔対が発生し、電子は N 型層 5 2 へ、正孔は P 型 S i 基板 5 1 へそれぞれ移動する。これにより、フォトダイオード 1 の容量成分に電荷がたまり、フォトダイオード 1 の N 型層（即ち、カソード） 5 2 の電位が変化する。そして、この電位の変化により、フォトダイオード 1 上に形成された M O S トランジスタ 2 の閾値がシフトする。この閾値のシフトは、電流信号として読み出すことにより、光信号の電気信号への変換（即ち、光電変換）が行われる。

#### 【 0 0 1 7 】

例えば、 M O S トランジスタ 2 が N M O S の場合、 N 型層 5 2 に電子が蓄積することにより、 N 型層 5 2 の負電位をバックゲートバイアスとして、 M O S トランジスタ 2 のチャネル領域に印加することができ、 M O S トランジスタ 2 の閾値をチャネル領域が反転しにくくなる方向（即ち、電流が流れにくくなる方向）にシフトさせることができる。従って、各画素 1 0 から読み出される電流信号の強度（若しくは、電流信号の有無）を測定することにより、各画素 1 0 における受光量を知ることができる。

30

#### 【 0 0 1 8 】

なお、上記の電流信号の読み出しは、図 1 ( A ) に示した縦選択シフトレジスタ 2 1 及び横選択シフトレジスタ 2 3 による画素選択により、画素 1 0 每に順次行われる。即ち、縦選択シフトレジスタ 2 1 により、複数本の C O L U M ラインの中から任意の一本が選択され、選択された C O L U M ラインに信号 H が印加される。これにより、選択された C O L U M ラインに M O S トランジスタ 2 のゲート電極が繋がる各画素において、電流信号の読み出しが実行される。また、これと同時に、横選択シフトレジスタ 2 3 により、複数本の R O W ラインの中から任意の一本が選択される。この R O W ラインの選択は、例えば R O W ラインと横選択シフトレジスタ 2 3 との間に配置された M O S トランジスタ 2 9 の O N ・ O F F 動作を横選択シフトレジスタ 2 3 が行うことにより実行される。これにより、選択された R O W ラインから出力マルチプレクサ 2 5 に向けて電流信号の送出が行われる。そして、出力マルチプレクサ 2 5 に送出された電流信号は出力アンプ 2 7 を介して外部に出力される。

40

#### 【 0 0 1 9 】

このように、本発明の第 1 実施形態によれば、受光量に応じて大きさが変化するカソ-

50

ド 5 2 の電位をバックゲートバイアスとして、MOSトランジスタ2のチャネル領域にバックゲートバイアスを印加することができ、受光量に応じてMOSトランジスタ2の閾値をシフトさせることができる。そして、この閾値シフトをROWラインを介して電流信号として読み出すことにより、光電変換することができる。従って、一画素内に形成されるMOSトランジスタの数を従来の3～4個から1～2個に減らすことができ、各画素における開口率の向上、受光部面積の拡大、又は、それらによる画素の高感度化（即ち、光信号のSN比の向上）を図ることができる。

#### 【0020】

##### (2) 第2実施形態

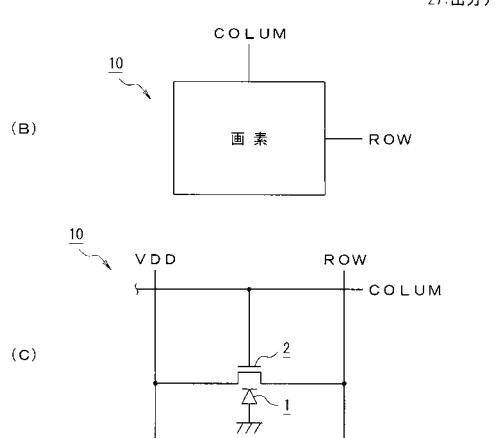

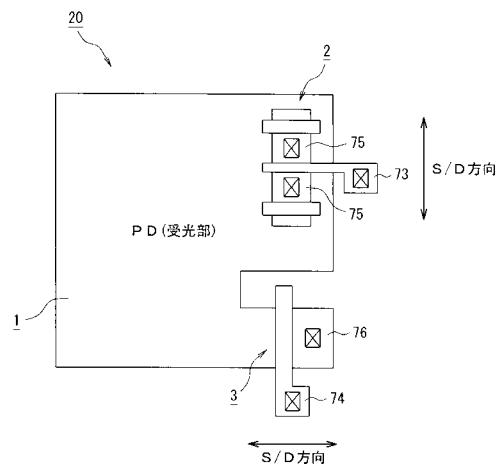

図3は本発明の第2実施形態に係るイメージセンサ200の構成例を示す図であり、図3(A)はイメージセンサ200の全体構成の一例を示す図、図3(B)は画素選択に係る配線(ライン)を示す図、図3(C)は画素20の構成例を示す図である。

図3(A)に示すように、このイメージセンサ200は、平面視で縦方向及び横方向に一定間隔で配置された複数の画素20と、これら複数の画素群（即ち、画素アレイ）の周囲に配置された縦選択シフトレジスタ21、横選択シフトレジスタ23と、出力マルチブレクサ25と、出力アンプ27と、リセット選択シフトレジスタ31と、を含んで構成されている。

#### 【0021】

図3(B)及び(C)に示すように、画素アレイに含まれる一画素20は、行方向に向かって延びるVddライン及びROWラインと、列方向に向かって延びるCOLUMNライン及びRESETラインとにより囲まれてあり、この囲まれた画素20内に受光部（即ち、フォトダイオード）1と、フォトダイオード1で生じた電気信号を読み出すためのMOSトランジスタ2と、フォトダイオード1のカソードをRESETラインに選択的に接続するためのMOSトランジスタ3と、を含んで構成されている。

#### 【0022】

図3(C)に示すように、MOSトランジスタ3は、そのS/Dの一方がVDDラインに接続され、S/Dの他方はフォトダイオードのカソードに接続されている。また、MOSトランジスタ3のゲート電極はRESETラインに接続されている。MOSトランジスタ3は例えばNMOSである。イメージセンサ200を構成する各々の画素20では、MOSトランジスタ3がONすることにより、フォトダイオード1のカソードがVDDラインに接続され、カソードに蓄積された電子がVDDラインに排出される。従って、例えば、上記の電流信号の読み出し後にMOSトランジスタ3をONすることにより、フォトダイオード1の容量成分における電荷の蓄積状態をリセットすることができ、フォトダイオード1の真上に形成されたMOSトランジスタ2の閾値を直ちに初期状態（即ち、バックゲートバイアスが印加されていない状態）に戻すことができる。

#### 【0023】

なお、上記のリセットは、図3(A)に示したリセット選択シフトレジスタ31による画素20選択により、列方向に並ぶ複数の画素毎に順次行われる。即ち、リセット選択シフトレジスタ31により、複数本のRESETラインの中から任意の一本が選択され、選択されたRESETラインに信号Hが印加される。これにより、選択されたRESETラインにMOSトランジスタ3のゲート電極が繋がる各画素20において、上記のリセットが実行される。

このように、本発明の第2実施形態によれば、第1実施形態と同様の効果を得ることができる。さらに、フォトダイオード1のカソード電位をVDD電位に設定する（即ち、カソードに蓄積された電荷をVDDラインに排出してリセットする）ことができ、MOSトランジスタ2の閾値を直ちに初期状態に戻すことができる。

#### 【0024】

##### (3) 第3実施形態

次に、上述したイメージセンサの製造方法について説明する。

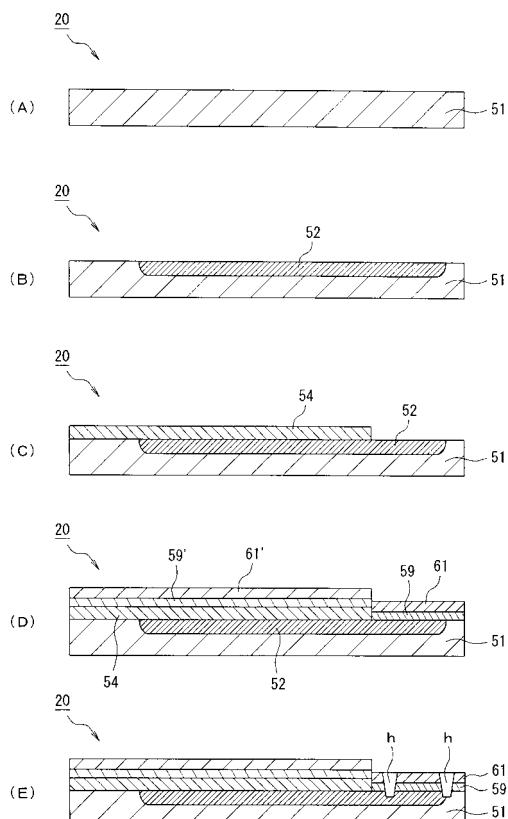

図4(A)～図6(E)は本発明の第3実施形態に係るイメージセンサの製造方法を示

10

20

30

40

50

す工程図である。ここでは、イメージセンサが有する上記画素20をSBSI法を利用して形成する場合について説明する。

#### 【0025】

図4(A)に示すように、まず始めに、単結晶のP型Si基板51を用意する。次に、フォトリソグラフィー及びイオン注入技術により、画素となる領域のP型Si基板51にN型不純物を部分的にイオン注入する。ここで、P型Si基板51に含まれるP型不純物は例えばボロンであり、N型不純物は例えばリン又はヒ素である。次に、N型不純物がイオン注入されたP型Si基板51に熱処理を施して、図4(B)に示すようにN型層52を形成する。これにより、P型Si基板(即ち、アノード)51と、N型層(即ち、カソード)52とからなるフォトダイオード1が完成する。

10

#### 【0026】

次に、図4(C)に示すように、N型層52が形成されたSi基板51上に例えばシリコン酸化(SiO<sub>2</sub>)膜54を形成する。このSiO<sub>2</sub>膜54の形成は例えば熱酸化、又はCVD(Chemical Vapor Deposition)で行う。そして、フォトリソグラフィー及びエッティング技術により、SiO<sub>2</sub>膜54を部分的にエッティングして、MOSトランジスタ2(図3参照。)が形成される領域のSi基板51表面を露出させる。ここでは、MOSトランジスタ2が形成される領域以外のSi基板51上にはSiO<sub>2</sub>膜54を全体的に残しておく。なお、SiO<sub>2</sub>膜54の部分的エッティングは、ウェットエッティング又はドライエッティングのどちらで行っても良い。

20

#### 【0027】

次に、図4(D)に示すように、SiO<sub>2</sub>膜54が部分的にエッティングされたSi基板51上にシリコンゲルマニウム(SiGe)層59、59'を形成し、その上にシリコン(Si)層61、61'を形成する。これらSiGe層59、59'及びSi層61、61'は、例えばエピタキシャル成長法で連続して形成する。エピタキシャル成長法では下地の結晶状態がその上に形成される膜に反映されるため、SiO<sub>2</sub>膜54上のSiGe層59'及びSi層61'は多結晶構造に形成され、N型層52を含むSi基板51上のSiGe層59及びSi層61は単結晶構造に形成される。

20

#### 【0028】

次に、図4(E)に示すように、Si層61及びSiGe層59を順次、部分的にエッティングする。これにより、Si基板51を底面とする支持体穴hを形成する。このエッティング工程では、Si基板51の表面でエッティングを止めるようにしてもよいし、Si基板51をオーバーエッティングして凹部を形成するようにしてもよい。

30

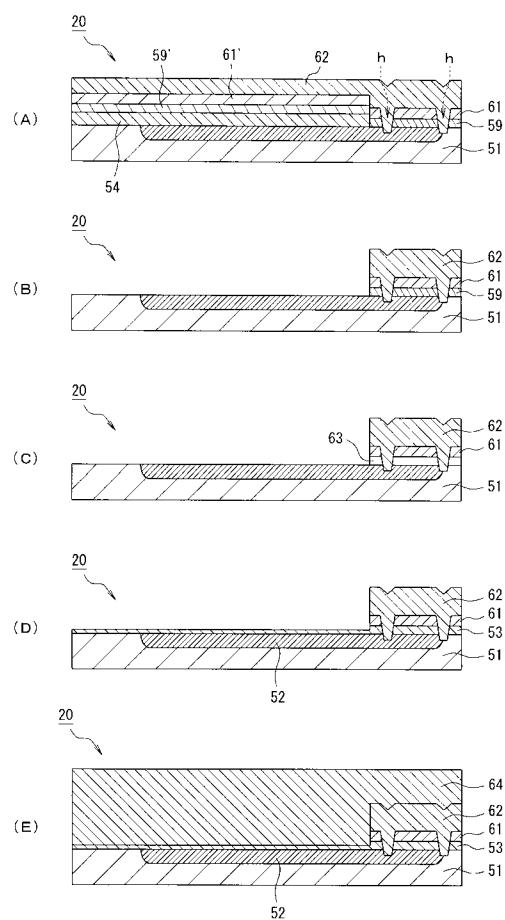

次に、図5(A)に示すように、支持体穴hを埋め込むようにしてSi基板51上の全面に例えばSiO<sub>2</sub>膜62を形成する。このSiO<sub>2</sub>膜62は例えばCVD法で形成する。そして、フォトリソグラフィー及びエッティング技術により、SiO<sub>2</sub>膜62、Si層61、61'、SiGe層59、59'をそれぞれ順次、部分的にエッティングする。これにより、図5(B)に示すように、MOSトランジスタ2が形成される領域以外のSi基板51表面を露出させると共に、紙面の手前側と奥側とにおいて、SiO<sub>2</sub>膜62、Si層61及びSiGe層59の各側面を露出させる溝を形成する。

40

#### 【0029】

次に、上記の溝を介して例えばフッ硝酸溶液を、Si層61及びSiGe層59の各側面に接触させて、SiGe層59を選択的にエッティングして除去する。これにより、図5(C)に示すように、Si層61とSi基板51との間に空洞部63を形成する。フッ硝酸溶液を用いたウェットエッティングでは、Siと比べてSiGeのエッティングレートが大きい(即ち、Siに対するエッティングの選択比が大きい)ので、Si層61を残しつつSiGe層だけをエッティングして除去することが可能である。空洞部63の形成後、Si層61はその上面と側面とがSiO<sub>2</sub>膜62によって支えられることとなる。

#### 【0030】

なお、このSiGe層をエッティングする工程では、フッ硝酸溶液の代わりに、フッ硝酸過水、アンモニア過水、或いはフッ酢酸過水などを用いても良い。過水とは過酸化水素水

50

のことである。この場合も、Siと比べてSiGeのエッティングレートが大きいので、SiGe層を選択的に除去することが可能である。

次に、図5(D)に示すように、例えば熱酸化により、空洞部63内に絶縁膜(例えば、SiO<sub>2</sub>膜)53を形成する。ここでは、空洞部63の内部に面したSi層61の裏面と、N型層52を含むSi基板51の表面とが熱酸化され、熱酸化により上下方向から成長してくるSiO<sub>2</sub>膜53によって空洞部63が埋め込まれる。また、空洞部63以外のSi基板51表面にもSiO<sub>2</sub>膜53が形成される。なお、SiO<sub>2</sub>膜53の形成方法は、熱酸化に限られることではなく、例えばCVD法でも良い。

#### 【0031】

次に、図5(E)に示すように、例えばCVD法により、Si基板51上の全面に例えばSiO<sub>2</sub>膜64を厚く形成する。そして、Si基板51上の全面を覆うSiO<sub>2</sub>膜64と、その下に部分的に残されているSiO<sub>2</sub>膜62とを例えばCMP(Chemical Mechanical Polishing)により平坦化しながら除去して、図6(A)に示すように、Si層61の表面を露出させる。

#### 【0032】

次に、図6(B)に示すように、フォトリソグラフィー及びエッティング技術により、SiO<sub>2</sub>膜を部分的に順次エッティングして、MOSトランジスタが形成される領域のSi基板51表面を露出させる。ここでは、N型層52の端部52aの表面を露出させると共に、MOSトランジスタ3(図3参照。)が形成される領域以外のSi基板51上にSiO<sub>2</sub>膜53、64を残しておく。

#### 【0033】

そして、図6(C)に示すように、Si層61表面にゲート絶縁膜71を形成すると共に、SiO<sub>2</sub>膜53下から露出したSi基板51表面にゲート絶縁膜72を形成する。ゲート絶縁膜71、72は、例えば、熱酸化により形成されるSiO<sub>2</sub>膜若しくはシリコン酸化窒化(SiON)膜、又は、High-k材料膜である。ゲート絶縁膜71、72の形成は同時に行っても良いし、別々に行っても良い。

#### 【0034】

次に、ゲート絶縁膜71、72が形成されたSi基板51上の全面に例えばポリシリコン(poly-Si)膜を形成する。このポリシリコン膜の形成は、例えばCVD法により行う。ここでは、ポリシリコン膜に不純物をイオン注入、又は、in-Situ等で導入して、ポリシリコン膜に導電性を持たせても良い。また、後述するS/D層の形成工程で、ポリシリコン膜に不純物を導入して導電性を持たせても良い。

次に、フォトリソグラフィー及びエッティング技術により、ポリシリコン膜を部分的にエッティングする。これにより、図6(D)に示すように、ゲート絶縁膜71上にゲート電極73を形成すると共に、ゲート絶縁膜72上にゲート電極74を形成する。ゲート電極73、74の形成は同時に行っても良いし、別々に行っても良い。

#### 【0035】

次に、ゲート電極73をマスクにSi層61に不純物をイオン注入すると共に、ゲート電極74をマスクにSi基板51に不純物をイオン注入する。そして、不純物注入後のSi基板51全体に熱処理を施す。これにより、図6(E)に示すように、ゲート電極73の両側のSi層61にS/D層75を形成すると共に、ゲート電極74の両側のSi基板51にS/D層76を形成する。図6(E)に示す工程では、N型層52の端部52aの表面が露出した状態で不純物のイオン注入が行われるので、S/D層75、76の一方はこの端部52aと重なるように形成される。このようなS/D層75、76の形成は同時にあっても良いし、別々に行っても良い。MOSトランジスタ2、3としてNMOSを形成する場合は、例えばリン又はヒ素等のN型不純物をイオン注入してN型のS/D層75、76を形成する。

#### 【0036】

次に、CVD法でSi基板51上の全面に層間絶縁膜(図示せず)を形成する。この層間絶縁膜は例えばSiO<sub>2</sub>膜である。そして、この層間絶縁膜の表面を例えばCMPで平

10

20

30

40

50

坦化する。次に、フォトリソグラフィー技術とエッチング技術とを用いて層間絶縁膜を部分的にエッチングする。これにより、ゲート電極73、74上とS/D層75、76上とにそれぞれコンタクトホールを形成する。

#### 【0037】

その後、コンタクトホール内に図示しないアルミニウム(A1)配線、又は、タンゲステン(W)等の高融点金属からなるプラグ電極を形成することにより、ゲート電極73、74とS/D層75、76とをそれぞれ層間絶縁膜上に引き出す。そして、例えば、プラグ電極と接続するように層間絶縁膜上に配線を形成する。ここで、配線とは、図3(C)等に示したようなVddライン及びROWラインと、COLUMNライン及びRESETラインである。Vddライン及びROWラインに対して、COLUMNライン及びRESETラインを上層又は下層(即ち、異なるレイヤ)に形成することで、これら各ラインを図3(C)等に示すようにショートさせることなく行方向及び列方向にそれぞれ延ばすことができる。

10

#### 【0038】

このように、本発明の第3実施形態によれば、P型Si基板51及びN型層52とからなるフォトダイオード1と、N型層(即ち、カソード)3上にSiO<sub>2</sub>膜53を介して形成されたSi層61と、Si層61に形成されたMOSトランジスタ2と、S/D層76の一方がN型層52に接続されたMOSトランジスタ3とを、一画素内に形成することができる。従って、図3(C)等に示した画素20を形成することができ、当該画素20を有するイメージセンサ200を製造することができる。

20

#### 【0039】

上記の第1～第3実施形態では、P型Si基板51が本発明の「半導体基板」に対応し、SiGe層59が本発明の「第1半導体層」に対応し、Si層61が本発明の「半導体層」又は「第2半導体層」に対応している。また、SiO<sub>2</sub>膜62が本発明の「支持体」に対応している。さらに、MOSトランジスタ2が本発明の「第1MOSトランジスタ」に対応し、MOSトランジスタ2が本発明の「第2MOSトランジスタ」に対応している。また、ROWラインが本発明の「第1信号線」に対応し、COLUMNラインが本発明の「第2信号線」に対応して、RESETラインが本発明の「第3信号線」に対応している。さらに、CMOSイメージセンサ100、200が本発明の「半導体装置」に対応している。

30

#### 【0040】

なお、上記の第1～第3実施形態では、フォトダイオード1がP型Si基板(即ち、P型層)51とN型層52とからなる場合について説明したが、本発明のフォトダイオードはこれに限られることはない。例えば、P型Si基板(即ち、P型層)51と、その上に形成される高純度のI型層と、N型層52とからなる、いわゆるPIN型フォトダイオードであっても良い。このような構成であっても、上記の第1～第3実施形態と同様の効果を得ることができる。

#### 【0041】

また、上記の第3実施形態では、例えば図6(C)に示したように、MOSトランジスタ2のS/D層75と、MOSトランジスタ3のS/D層76とを同一断面に揃えるように形成する場合について説明したが、MOSトランジスタ2、3の位置関係はこれに限られることはない。例えば図7に示すように、MOSトランジスタ2のS/D方向と、MOSトランジスタ3のS/D方向とが平面視で交差するように、MOSトランジスタ2、3をそれぞれ配置しても良い。このような位置関係であっても、画素20を構成することができる。

40

#### 【0042】

さらに、上述の第3実施形態では、第2実施形態で説明した画素20を製造する場合について説明したが、上記の製造方法は、第1実施形態で説明した画素10の製造にも適用可能である。その場合は、例えば、図6(B)に示したSiO<sub>2</sub>膜64の部分的エッチング工程を省くと共に、図6(C)以降の工程で、ゲート絶縁膜72、ゲート電極74及び

50

S / D層 7 6 の形成をそれぞれ省けば良い。これにより、第 1 実施形態で説明した画素 10 を形成することができ、当該画素 10 を有するイメージセンサ 100 を製造することができる。

【図面の簡単な説明】

【0043】

【図 1】本発明の第 1 実施形態に係るイメージセンサ 100 の構成例を示す図。

【図 2】画素 10 の断面構成の一例を示す図。

【図 3】本発明の第 2 実施形態に係るイメージセンサ 200 の構成例を示す図。

【図 4】本発明の第 3 実施形態に係るイメージセンサの製造方法を示す図。

【図 5】本発明の第 3 実施形態に係るイメージセンサの製造方法を示す図。

【図 6】本発明の第 3 実施形態に係るイメージセンサの製造方法を示す図。

【図 7】画素 20 の他の構成例を示す図。

【図 8】従来例を示す図。

【符号の説明】

【0044】

1 受光部（フォトダイオード）、2 （検出用の）MOSトランジスタ、3 （リセット用の）MOSトランジスタ、10、20 画素、21 縦選択シフトレジスタ、23 横選択シフトレジスタ、25 出力マルチプレクサ、27 出力アンプ、29 MOSトランジスタ、31 リセット選択シフトレジスタ、51 P型Si基板、52 N型層、52a (N型層の) 端部、54 SiO<sub>2</sub>膜、59、59' SiGe層、61、61' Si層、53、62、64 SiO<sub>2</sub>膜、71、72 ゲート絶縁膜、73、74 ゲート電極、75 S / D層、100 200 イメージセンサ

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

F ターム(参考) 5F049 MA03 MB03 NA18 NB05 PA10 PA14 QA03 RA02 RA08 SS03

UA01