(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4423458号

(P4423458)

(45) 発行日 平成22年3月3日(2010.3.3)

(24) 登録日 平成21年12月18日(2009.12.18)

(51) Int.Cl.

F 1

H02M 3/28 (2006.01)

H02M 3/335 (2006.01)H02M 3/28

H02M 3/335H

F

請求項の数 5 (全 11 頁)

(21) 出願番号 特願2001-74656 (P2001-74656)

(22) 出願日 平成13年3月15日 (2001.3.15)

(65) 公開番号 特開2002-209381 (P2002-209381A)

(43) 公開日 平成14年7月26日 (2002.7.26)

審査請求日 平成18年4月5日 (2006.4.5)

(31) 優先権主張番号 特願2000-342864 (P2000-342864)

(32) 優先日 平成12年11月10日 (2000.11.10)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 591083244

富士電機システムズ株式会社

東京都品川区大崎一丁目11番2号

(74) 代理人 100075166

弁理士 山口 勝

(74) 代理人 100085833

弁理士 松崎 清

(72) 発明者 野澤 武史

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

(72) 発明者 西川 幸廣

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

審査官 安池 一貴

最終頁に続く

(54) 【発明の名称】 DC／DCコンバータの制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

直流電源の正極と負極間に並列に2つのスイッチ素子の直列回路を接続するとともに、少なくとも1つのコンデンサと変圧器1次巻線との直列回路を前記スイッチ素子の一方に並列に接続し、前記直流電源の正極側に接続したスイッチ素子には前記変圧器の3次巻線からオンオフ信号を与える一方、変圧器の4次巻線は制御回路の電源用として用い、かつ、この制御回路により4次巻線電圧の正負の切替りのタイミングを検出し、そのタイミングで直流電源の負極側に接続したスイッチ素子にオンオフ信号を与えることにより、変圧器の2次巻線に発生する正負の電圧を半波または全波整流して直流出力を得るDC／DCコンバータにおいて、

前記直流電源の負極側に接続したスイッチ素子は、変圧器4次巻線の電圧の正から負または負から正への切替りから短絡防止期間を経た後にオンとし、前記スイッチ素子のオンまたは変圧器4次巻線の電圧の切替りタイミングから時間に比例して増加する参照電圧値を2次側出力電圧検出値と比較し、この電圧検出値に対して前記参照電圧値が上回ったとき、前記スイッチ素子をオフさせることにより、直流出力電圧を一定とするとともに、前記2次側出力電圧検出値が前記参照電圧を上回ったことを検出したときは、或る一定の周波数で発振する矩形波信号の立ち上がりまたは立ち下がりのタイミングで、前記スイッチ素子に駆動信号を与えることにより、前記DC／DCコンバータの誤停止を防止することを特徴とするDC／DCコンバータの制御方法。

## 【請求項 2】

前記参照電圧の最小値が前記 2 次側出力電圧検出値の最小値よりも大きくなるように、一定のオフセットを持たせることを特徴とする請求項 1 に記載の DC / DC コンバータの制御方法。

**【請求項 3】**

直流電源の正極と負極間に並列に 2 つのスイッチ素子の直列回路を接続するとともに、少なくとも 1 つのコンデンサと変圧器 1 次巻線との直列回路を前記スイッチ素子の一方に並列に接続し、前記直流電源の正極側に接続したスイッチ素子には前記変圧器の 3 次巻線からオンオフ信号を与える一方、変圧器の 4 次巻線は制御回路の電源用として用い、かつ、この制御回路により 4 次巻線電圧の正負の切替りのタイミングを検出し、そのタイミングで直流電源の負極側に接続したスイッチ素子にオンオフ信号を与えることにより、変圧器の 2 次巻線に発生する正負の電圧を半波または全波整流して直流出力を得る DC / DC コンバータにおいて、

10

前記変圧器 4 次巻線の電圧の正から負または負から正への切替りの有無を検出し、切替りの無いことを検出したときは、前記直流電源の負極側に接続したスイッチ素子に駆動信号を与えることにより、前記 DC / DC コンバータの誤停止を防止することを特徴とする DC / DC コンバータの制御方法。

**【請求項 4】**

直流電源の正極と負極間に並列に 2 つのスイッチ素子の直列回路を接続するとともに、少なくとも 1 つのコンデンサと変圧器 1 次巻線との直列回路を前記スイッチ素子の一方に並列に接続し、前記直流電源の正極側に接続したスイッチ素子には前記変圧器の 3 次巻線からオンオフ信号を与える一方、変圧器の 4 次巻線は制御回路の電源用として用い、かつ、この制御回路により 4 次巻線電圧の正負の切替りのタイミングを検出し、そのタイミングで直流電源の負極側に接続したスイッチ素子にオンオフ信号を与えることにより、変圧器の 2 次巻線に発生する正負の電圧を半波または全波整流して直流出力を得る DC / DC コンバータにおいて、

20

前記直流電源の負極側に接続したスイッチ素子がオンしている途中で、直流電源の正極側に接続したスイッチ素子がオンすることを変圧器 4 次巻線の電圧から検出したときは、前記直流電源の負極側に接続したスイッチ素子をオフすることにより、アーム短絡を防止することを特徴とする DC / DC コンバータの制御方法。

**【請求項 5】**

30

直流電源の正極と負極間に並列に 2 つのスイッチ素子の直列回路を接続するとともに、少なくとも 1 つのコンデンサと変圧器 1 次巻線との直列回路を前記スイッチ素子の一方に並列に接続し、前記直流電源の正極側に接続したスイッチ素子には前記変圧器の 3 次巻線からオンオフ信号を与える一方、変圧器の 4 次巻線は制御回路の電源用として用い、かつ、この制御回路により 4 次巻線電圧の正負の切替りのタイミングを検出し、そのタイミングで直流電源の負極側に接続したスイッチ素子にオンオフ信号を与えることにより、変圧器の 2 次巻線に発生する正負の電圧を半波または全波整流して直流出力を得る DC / DC コンバータにおいて、

負荷が軽いときは、前記直流電源の負極側に接続したスイッチ素子を、スイッチングを停止する期間と、スイッチングを行なう期間とを設けて間欠発振駆動するものであり、直流電源の負極側に接続したスイッチ素子の、スイッチング停止期間からスイッチング期間への切り替えは、変圧器 4 次巻線の電圧によって、直流電源の正極側に接続したスイッチ素子がオフしていることを検出したときに行なって、アーム短絡を防止することを特徴とする DC / DC コンバータの制御方法。

40

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

この発明は、ハーフブリッジ構成の DC / DC コンバータ、特にその制御方法に関する。

。

**【0002】**

50

**【従来の技術】**

図6に従来例を示す。

**【0003】**

同図に示すように、直流電源10と並列にMOSFET（金属酸化物半導体電界効果トランジスタ）1とMOSFET2との直列回路を接続し、コンデンサ3と変圧器1次巻線5との直列回路とスナバコンデンサ21を、MOSFET2にそれぞれ並列に接続して構成される。変圧器22の2次側には2つの巻線8,9を備え、ダイオード12,13とコンデンサ14からなる整流平滑回路を有している。また、平滑された直流出力電圧を一定に保つため、出力電圧検出回路17と周波数・位相制御回路19を設け、フィードバック制御を行なうようにしている。また、MOSFET1,2の各ゲートを駆動する回路には、高耐圧ドライバIC（集積回路）20が用いられている。10

**【0004】**

図7に図6のタイミングチャートを示す。以下、その動作について図6も参照して説明する。

**【0005】**

まず、期間(1)においてMOSFET1をオンすることにより、直流電源10 コンデンサ3 変圧器1次巻線5 MOSFET1を介して、コンデンサ3と変圧器22の漏れインダクタンスによる共振電流と変圧器22の励磁電流が流れ、コンデンサ3が充電される。このとき、変圧器1次巻線5には直流電源電圧Edとコンデンサ3との差電圧VP1が印加され、変圧器2次巻線8に発生する電圧VS1をダイオード12,コンデンサ14により整流、平滑し負荷に電力を供給する。変圧器2次巻線電圧VS1は、変圧器1次巻線電圧VP1の巻数比に比例した電圧（図7中に点線で示す）で上昇し、出力電圧Voに達するとダイオード12が導通し、出力電圧Voにクランプされる。図中の点線と実線の差電圧は、変圧器22の漏れインダクタンスに印加される。20

**【0006】**

期間(2)において変圧器1次巻線電圧VP1は徐々に低下し、変圧器1次巻線電圧VP1の巻数比に比例した電圧が出力電圧Voよりも下回ると、ダイオード12は阻止状態となり電流が零となる。また、MOSFET1には期間(1)で励磁された変圧器22の励磁電流が継続して流れる。

**【0007】**

期間(3)において、MOSFET1をオフすることにより、変圧器22の励磁電流はスナバコンデンサ21およびMOSFET1,2の出力容量に転流し、MOSFET1,2の電圧は徐々に上昇または下降する。30

**【0008】**

期間(4)において、MOSFET1の電圧が直流電源電圧Edに達すると、変圧器22の励磁電流はMOSFET2の寄生ダイオードに転流する。このとき、MOSFET2をオンすることにより、コンデンサ3 MOSFET2 変圧器1次巻線5を介して共振電流と変圧器22の励磁電流が流れ、コンデンサ3を放電する。また、変圧器1次巻線5には直流電源電圧Edとコンデンサ3との差電圧VP1が印加され、変圧器22はリセットされる。また、このとき変圧器2次巻線9に発生する電圧をダイオード13,コンデンサ14により整流、平滑し負荷に電力を供給する。40

**【0009】**

以下、期間(4)から(6)の動作は期間(1)から(3)と同様なので、説明は省略する。

**【0010】**

こうして、期間(1)から(6)の一連の動作を繰り返すことにより、直流電源10から負荷に電力が供給される。

**【0011】**

次に、軽負荷時の動作を図8を参照して説明する。

**【0012】**

軽負荷時には、スイッチング周波数が増大しないように周波数・位相制御回路19を調整し、変圧器2次側電流ID12, ID13が零になった時点より或る時間が経過してから、MOSFET1またはMOSFET2をオフする。MOSFET1, 2に流れる電流IQ1, 2は、変圧器22の励磁電流にほぼ等しくなる。

#### 【0013】

##### 【発明が解決しようとする課題】

上記の従来例では、各MOSFETは定格負荷から無負荷までデューティ(duty)50%で交互にスイッチングし、負荷の変化に対して出力電圧検出回路および周波数・位相制御回路を用いて、変圧器1次巻線に印加される電圧を調整して負荷に供給する電流を制御することにより、出力電圧を一定にしている。

10

#### 【0014】

しかし、この方法では、定格負荷から無負荷まで変圧器の励磁インダクタンスに流れる励磁電流の値がほとんど変化しないため、この励磁電流が無効電流となり、回路中のインピーダンス(MOSFETのオン抵抗、トランジスタの巻線抵抗など)によって損失が発生し、結果的に軽負荷時の効率が低下するという問題がある。

#### 【0015】

また、直流電源の正極に接続されるMOSFETのソース端子の電位が、直流電源の負極に接続されたMOSFETのソース端子の電位とは異なるため、正極側のMOSFETを駆動する信号はパルストラnsなどで絶縁するか、またはレベルシフト機能を持った高価な高耐圧ドライバICが必要となり、装置の大型化やコストアップを招くことになる。

20

#### 【0016】

したがって、この発明の課題は、無効電流を低く抑え、高価な部品を不要としてコストを低減することにある。

#### 【0017】

##### 【課題を解決するための手段】

このような課題を解決するため、請求項1の発明では、直流電源の正極と負極間に並列に2つのスイッチ素子の直列回路を接続するとともに、少なくとも1つのコンデンサと変圧器1次巻線との直列回路を前記スイッチ素子の一方に並列に接続し、前記直流電源の正極側に接続したスイッチ素子には前記変圧器の3次巻線からオンオフ信号を与える一方、変圧器の4次巻線は制御回路の電源用として用い、かつ、この制御回路により4次巻線電圧の正負の切替りのタイミングを検出し、そのタイミングで直流電源の負極側に接続したスイッチ素子にオンオフ信号を与えることにより、変圧器の2次巻線に発生する正負の電圧を半波または全波整流して直流出力を得るDC/DCコンバータにおいて、

30

前記直流電源の負極側に接続したスイッチ素子は、変圧器4次巻線の電圧の正から負または負から正への切替りから短絡防止期間を経た後にオンとし、前記スイッチ素子のオンまたは変圧器4次巻線の電圧の切替りタイミングから時間に比例して増加する参照電圧値を2次側出力電圧検出値と比較し、この電圧検出値に対して前記参照電圧値が上回ったとき、前記スイッチ素子をオフさせることにより、直流出力電圧を一定とするとともに、前記2次側出力電圧検出値が前記参照電圧を上回ったことを検出したときは、或る一定の周波数で発振する矩形波信号の立ち上がりまたは立ち下がりのタイミングで、前記スイッチ素子に駆動信号を与えることにより、前記DC/DCコンバータの誤停止を防止することを特徴とする。

40

この請求項1の発明においては、前記参照電圧の最小値が前記2次側出力電圧検出値の最小値よりも大きくなるように、一定のオフセットを持たせることができる(請求項2の発明)。

#### 【0018】

請求項3の発明では、直流電源の正極と負極間に並列に2つのスイッチ素子の直列回路を接続するとともに、少なくとも1つのコンデンサと変圧器1次巻線との直列回路を前記スイッチ素子の一方に並列に接続し、前記直流電源の正極側に接続したスイッチ素子には前記変圧器の3次巻線からオンオフ信号を与える一方、変圧器の4次巻線は制御回路の電

50

源用として用い、かつ、この制御回路により 4 次巻線電圧の正負の切替りのタイミングを検出し、そのタイミングで直流電源の負極側に接続したスイッチ素子にオンオフ信号を与えることにより、変圧器の 2 次巻線に発生する正負の電圧を半波または全波整流して直流出力を得る DC / DC コンバータにおいて、

前記変圧器 4 次巻線の電圧の正から負または負から正への切替りの有無を検出し、切替りの無いことを検出したときは、前記直流電源の負極側に接続したスイッチ素子に駆動信号を与えることにより、前記 DC / DC コンバータの誤停止を防止することを特徴とする。

#### 【 0 0 1 9 】

請求項 4 の発明では、直流電源の正極と負極間に並列に 2 つのスイッチ素子の直列回路を接続するとともに、少なくとも 1 つのコンデンサと変圧器 1 次巻線との直列回路を前記スイッチ素子の一方に並列に接続し、前記直流電源の正極側に接続したスイッチ素子には前記変圧器の 3 次巻線からオンオフ信号を与える一方、変圧器の 4 次巻線は制御回路の電源用として用い、かつ、この制御回路により 4 次巻線電圧の正負の切替りのタイミングを検出し、そのタイミングで直流電源の負極側に接続したスイッチ素子にオンオフ信号を与えることにより、変圧器の 2 次巻線に発生する正負の電圧を半波または全波整流して直流出力を得る DC / DC コンバータにおいて、

前記直流電源の負極側に接続したスイッチ素子がオンしている途中で、直流電源の正極側に接続したスイッチ素子がオンすることを変圧器 4 次巻線の電圧から検出したときは、前記直流電源の負極側に接続したスイッチ素子をオフすることにより、アーム短絡を防止することを特徴とする。

#### 【 0 0 2 0 】

請求項 5 の発明では、直流電源の正極と負極間に並列に 2 つのスイッチ素子の直列回路を接続するとともに、少なくとも 1 つのコンデンサと変圧器 1 次巻線との直列回路を前記スイッチ素子の一方に並列に接続し、前記直流電源の正極側に接続したスイッチ素子には前記変圧器の 3 次巻線からオンオフ信号を与える一方、変圧器の 4 次巻線は制御回路の電源用として用い、かつ、この制御回路により 4 次巻線電圧の正負の切替りのタイミングを検出し、そのタイミングで直流電源の負極側に接続したスイッチ素子にオンオフ信号を与えることにより、変圧器の 2 次巻線に発生する正負の電圧を半波または全波整流して直流出力を得る DC / DC コンバータにおいて、

負荷が軽いときは、前記直流電源の負極側に接続したスイッチ素子を、スイッチングを停止する期間と、スイッチングを行なう期間とを設けて間欠発振駆動するものであり、直流電源の負極側に接続したスイッチ素子の、スイッチング停止期間からスイッチング期間への切り替えは、変圧器 4 次巻線の電圧によって、直流電源の正極側に接続したスイッチ素子がオフしていることを検出したときに行なって、アーム短絡を防止することを特徴とする。

#### 【 0 0 2 1 】

##### 【発明の実施の形態】

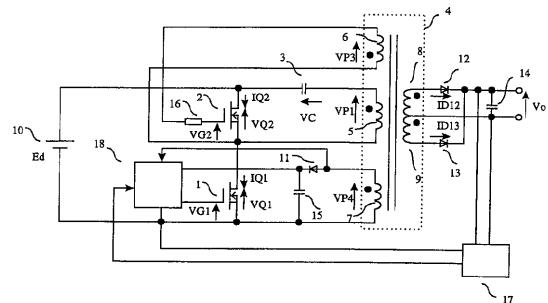

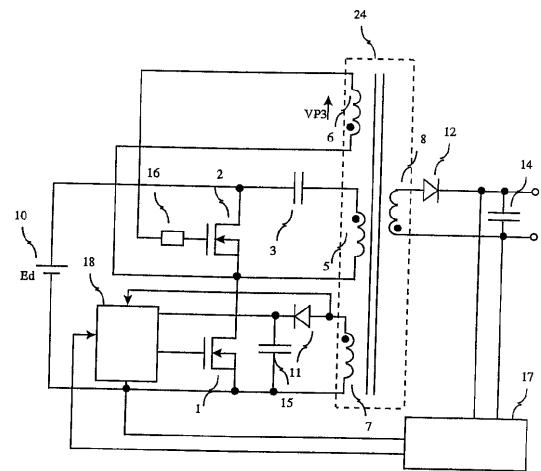

図 1 はこの発明の実施の形態を示す回路図である。

#### 【 0 0 2 2 】

これは、図 6 に示す従来回路の変圧器 2 2 に、変圧器 3 次巻線 6 および 4 次巻線 7 を付加して変圧器 4 とし、変圧器 3 次巻線 6 を MOSFET 2 のゲートに抵抗 1 6 を介して接続し、変圧器 4 次巻線 7 の電圧 V P 4 をダイオード 1 1 およびコンデンサ 1 5 により半波整流して制御回路 1 8 の電源電圧とし、変圧器 4 次巻線 7 をその電圧の切替りを検出するために制御回路 1 8 に接続した点が特徴である。なお、MOSFET 2 と並列に接続されるスナバコンデンサは、ここでは図示を省略した。

#### 【 0 0 2 3 】

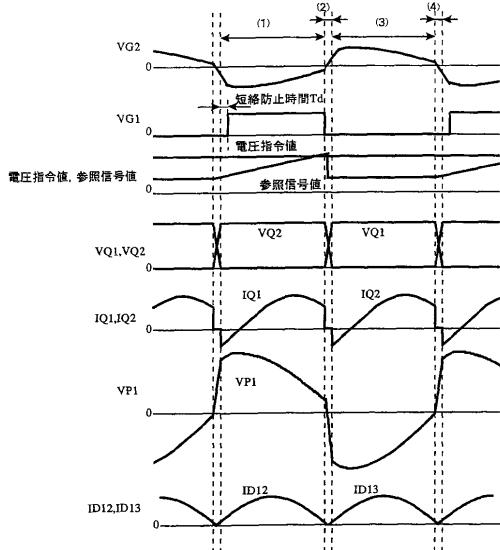

図 2 に図 1 のタイミングチャートを示す。以下、その動作について図 1 も参照して説明する。

#### 【 0 0 2 4 】

10

20

30

40

50

まず、期間(1)においてMOSFET1は、変圧器4次巻線7の電圧VP4が負から正へ切り替わるタイミングから、短絡防止期間Tdを経たのちにオンする。これにより、コンデンサ3と変圧器4の漏れインダクタンスによる共振電流と変圧器4の励磁電流が、直流電源10 コンデンサ3 変圧器1次巻線5 MOSFET1を介して流れ、コンデンサ3が充電される。このとき、変圧器1次巻線5には直流電源電圧Edとコンデンサ3との差電圧VP1が印加され、変圧器2次巻線8に発生する電圧をダイオード12、コンデンサ14により整流、平滑し負荷に電力を供給する。

#### 【0025】

MOSFET1のオフは、変圧器1次巻線の電圧VP1の負より正に切り替わるタイミングから、制御回路18内において、時間に比例して増加する参照信号値と出力電圧検出回路17からの2次側出力電圧検出値（図2では、出力電圧指令値として示す）とを比較し、参照信号値が出力電圧検出値を上回ったときに行なわれる。また、制御回路18は参照信号値が出力電圧検出値を上回る前に、負荷の状態などにより変圧器4次巻線7の電圧VP4が下降した場合（変圧器3次巻線6の電圧VP3は上昇する）、VP4の正から負に切り替わるタイミングを検出して、MOSFET1をオフさせる。これにより、MOSFET1がオンしている途中で、MOSFET2がオンするといったアーム短絡の発生が防止される。MOSFET1がオフすると、変圧器1次巻線5の電圧VP1は正から負に切り替わる。変圧器3次巻線6と変圧器4次巻線7には、変圧器1次巻線5の巻数比に比例した電圧が発生する。その電圧の極性は変圧器3次巻線6の電圧VP3が正で、変圧器4次巻線7の電圧VP4が負となる。MOSFET1がオフするタイミングでは、ダイオード12に流れる電流は零となっており、MOSFET1がオフする電流は変圧器4の励磁電流のみとなる。

10

20

#### 【0026】

期間(2)において、MOSFET1をオフすることにより、変圧器4の励磁電流はMOSFET1, 2の出力容量に転流し、MOSFET1, 2の電圧は徐々に上昇または下降する。

#### 【0027】

期間(3)において、MOSFET1の電圧が直流電源電圧Edに達すると、変圧器4の励磁電流はMOSFET2の寄生ダイオードに転流する。このとき、変圧器3次巻線6の電圧VP3がMOSFET2のゲートしきい値を越えるとMOSFET2がオンし、コンデンサ3 MOSFET2 変圧器1次巻線5を介して共振電流と変圧器4の励磁電流が流れ、コンデンサ3を放電する。また、変圧器1次巻線5には直流電源電圧Edとコンデンサ3との差電圧VP1が印加され、変圧器2次巻線9に発生する電圧をダイオード13、コンデンサ14により整流、平滑し負荷に電力を供給する。共振電流が下降してくると変圧器3次巻線6の電圧VP3が下降し、それがMOSFET2のゲートしきい値以下になると、MOSFET2はオフする。MOSFET2がオフするタイミングでは、ダイオード13に流れる電流は零となっており、MOSFET2がオフする電流は変圧器4の励磁電流のみとなる。

30

#### 【0028】

期間(4)においてMOSFET2がオフすると、変圧器1次巻線5の電圧VP1は負から正になる。変圧器3次巻線6と変圧器4次巻線7には、変圧器1次巻線5の巻数比に比例した電圧が発生する。その電圧の極性は変圧器3次巻線6の電圧VP3が負で、変圧器4次巻線7の電圧VP4が正となる。変圧器4の励磁電流はコンデンサ3およびMOSFET1, 2の寄生容量に転流し、MOSFET1, 2の電圧は徐々に下降または上昇する。期間(1)においてMOSFET2の電圧VQ2が直流電源電圧Edに達すると、変圧器4の励磁電流はMOSFET1の寄生ダイオードに転流する。以後この一連の動作を繰り返すことにより、直流電源10から負荷に電力が供給される。

40

#### 【0029】

なお、出力電圧検出回路17の出力段は、2次側からの信号を電気的に絶縁するためフォトカプラを用いるのが一般的であるが、フォトカプラの2次側はトランジスタ構造とな

50

っているため、出力電圧検出値の最小値はフォトカプラの2次側トランジスタのえん層電圧以下には低下しない。従って、参照電圧信号の最小値が出力電圧検出値の最小値よりも小さい場合、スイッチング周期毎に常にMOSFET 1がオンオフするため、軽負荷時や負荷急変時に2次側出力電圧が設定電圧を越えて過電圧になることがある。

#### 【0030】

この問題に対し、ここでは上記参照電圧信号に対しその最小値が、出力電圧検出回路17からの出力の最小値よりも大きくなるようにオフセットを持たせ、さらに出力電圧検出回路17からの出力値が参照電圧信号の最小値よりも小さくなった場合はMOSFET 1のオンを抑止し、スイッチングを継続しないようにすることで、2次側出力電圧の過電圧を防ぐようしている。

10

#### 【0031】

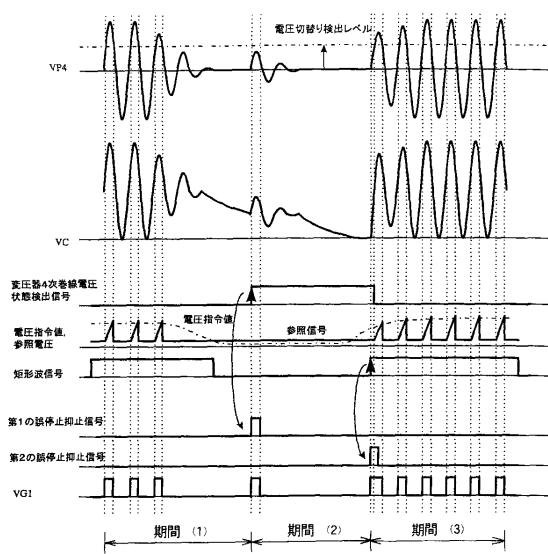

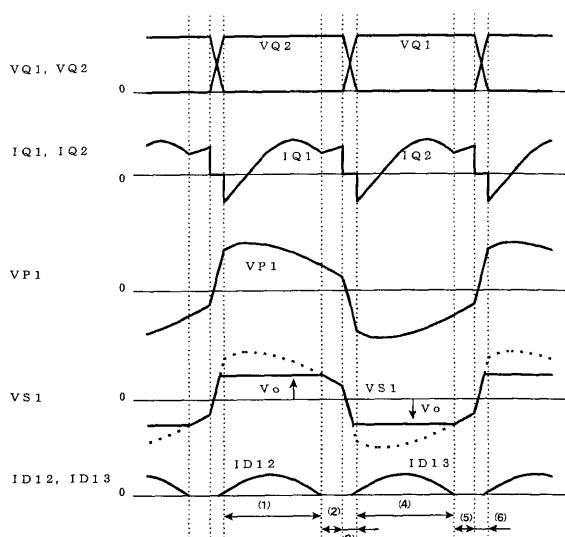

図3を参照して、この発明によるDC/DCコンバータの誤停止を抑止するための制御回路18の動作につき説明する。

#### 【0032】

期間(1)は負荷急変が発生して出力電圧 $V_o$ が上昇し、フィードバック制御により電圧指令値が下降した状態(スイッチング停止)を示す。また、回路の動作状態によりコンデンサ3に電荷が残った状態でMOSFET 1, 2が停止していることを示す。コンデンサ3の電荷は回路中のインピーダンスにより徐々に放電する。期間(2)は、変圧器4次巻線7の電圧切替りが無くなったことを検出して動作する、第1の誤停止抑止回路が動作失敗したときの状態を示す。このとき、コンデンサ3が充分放電していないときには、変圧器1次巻線5に印加される電圧が小さくなり、MOSFET 1に駆動信号を与えることによって、変圧器3次巻線6, 4次巻線7に発生する電圧も小さくなり、スイッチングが継続できない場合がある。

20

#### 【0033】

期間(3)では、出力電圧 $V_o$ が正常値に戻り、電圧指令値が上昇し、さらにコンデンサ3の電荷が充分放電された状態を示す。このとき、或る周波数の矩形波信号の変化(ここでは立ち上がり)のタイミングで、MOSFET 1の駆動信号(第2の誤停止抑止信号)を与えることにより、変圧器3次巻線6, 4次巻線7に充分電圧が発生し、MOSFET 1, 2は繰り返しスイッチングを行なうことができる。なお、コンデンサ3の放電を促進するために、コンデンサ3と並列に放電抵抗を接続することができる。

30

#### 【0034】

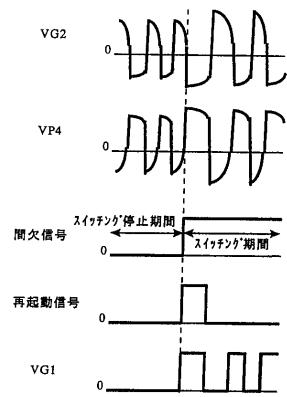

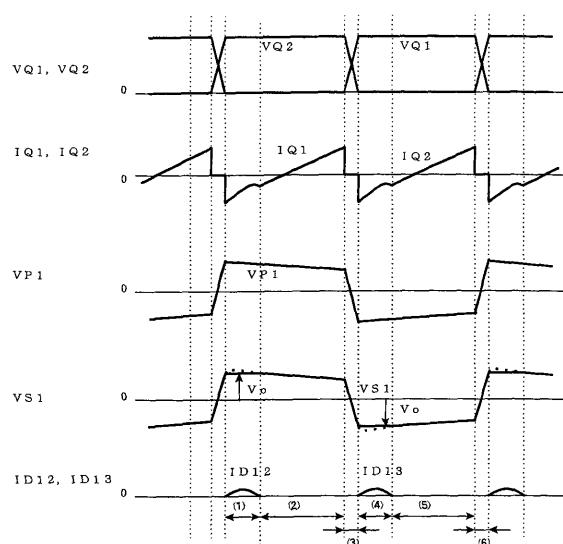

図4にこの発明によるDC/DCコンバータの間欠動作を説明するタイムチャートを示す。

#### 【0035】

この間欠動作は、軽負荷の際に意図的にMOSFETのスイッチングを停止させることで、各部で発生する損失を低減し、入力電力を低く抑えるためのものである。間欠動作時においてスイッチング停止期間が短いと、MOSFET 1のスイッチングを停止させても、変圧器3次巻線6の電圧変化はすぐには停止しないため、MOSFET 2はスイッチングを継続する。スイッチング停止期間が終了しMOSFET 1をオンさせると、MOSFET 2がオンであると直流電源10 MOSFET 2 MOSFET 1の経路で大電流が流れ(アーム短絡)、回路が破壊するおそれがある。従って、制御回路18により変圧器4次巻線7を監視し、MOSFET 2がオフになっている状態のとき(電圧 $V_P 4$ が正電圧または変圧器4次巻線7の電圧の切替わりが停止しているとき)に、再起動信号を出してMOSFET 1をオンするようにする。

40

#### 【0036】

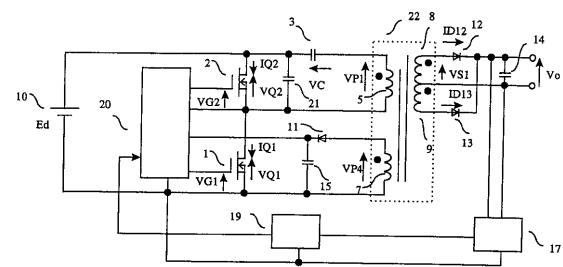

図5はこの発明の第2の実施の形態を示す回路図である。

#### 【0037】

同図からも明らかなように、この例は変圧器24の2次巻線に発生する電圧を半波整流するのにフライバック接続とした点が特徴である。したがって、直流電源10から負荷への電力供給は、MOSFET 1がオフになったときのみ行なわれる。なお、その他は図1

50

と同様なので詳細は省略する。

【0038】

【発明の効果】

この発明によれば、入力電圧や負荷の変化に対し、スイッチング周波数の変化に加えてパルス幅制御を行なうようにしたので、軽負荷時に負極に接続したスイッチ素子のオン時間を狭められるため、無効電流による回路中のインピーダンスで発生する損失を低減でき、軽負荷時の効率低下を抑制することができる。また、高電圧（正極）側のスイッチ素子を駆動するに当たり、比較的高価な高耐圧ドライバICまたはパルストランジスタを不要にできるため、コストの低減と回路の小型化が可能になる、という利点がもたらされる。

【0039】

10

加えて、2次側出力電圧検出値が参照電圧の最小値よりも下回るようにすることで、2次側出力電圧が設定電圧より大きく上昇しようとした場合には、直流電源の負極側のスイッチ素子をオフ状態として不要なスイッチングを抑止するため、スイッチ素子の発生損失が軽減されるとともに2次側出力電圧の過電圧が防止できる。

【0040】

これに対し、2次側出力電圧検出値が参照電圧を上回ったことを検出したときは、或る一定の周波数で発振する矩形波信号の立上がりまたは立下がりのタイミングで、直流電源の負極側に接続したスイッチ素子に駆動信号を与えることにより、DC/DCコンバータの誤停止を防止できるので、信頼性の高い電源を構築できる。

【図面の簡単な説明】

20

【図1】 この発明の第1の実施の形態を示す回路図である。

【図2】 図1の動作を説明するためのタイムチャートである。

【図3】 図1のDC/DCコンバータにおける誤停止の防止動作説明図である。

【図4】 図1における間欠動作時のアーム短絡の防止動作説明図である。

【図5】 この発明の第2の実施の形態を示す回路図である。

【図6】 従来例を示す回路図である。

【図7】 図6の動作を説明するためのタイムチャートである。

【図8】 図6における軽負荷時の動作説明図である。

【符号の説明】

1, 2...MOSFET（金属酸化物半導体電界効果トランジスタ）、3, 14, 15...コンデンサ、4, 22, 24...変圧器、5...変圧器1次巻線、6...変圧器3次巻線、7...変圧器4次巻線、8, 9...変圧器2次巻線、10...直流電源、11, 12, 13...ダイオード、16...抵抗、17...出力電圧検出回路、18...制御回路、19...周波数・位相制御回路、20...高耐圧ドライバIC、21...スナバコンデンサ。

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

---

フロントページの続き

(56)参考文献 独国特許出願公開第03736800(DE, A1)

特開平07-274498(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/28

H02M 3/335