(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-500757

(P2004-500757A)

(43) 公表日 平成16年1月8日(2004.1.8)

(51) Int.Cl.<sup>7</sup>

H03F 3/45

H03G 7/06

F 1

H03F 3/45

H03G 7/06

テーマコード(参考)

5J030

5J066

5J500

審査請求 未請求 予備審査請求 有 (全 50 頁)

(21) 出願番号 特願2001-542460 (P2001-542460)

(86) (22) 出願日 平成12年12月1日 (2000.12.1)

(85) 翻訳文提出日 平成14年6月3日 (2002.6.3)

(86) 國際出願番号 PCT/US2000/032694

(87) 國際公開番号 WO2001/041303

(87) 國際公開日 平成13年6月7日 (2001.6.7)

(31) 優先権主張番号 60/168,280

(32) 優先日 平成11年12月1日 (1999.12.1)

(33) 優先権主張国 米国(US)

(71) 出願人 501263810

トムソン ライセンシング ソシエテ ア

ノニム

Thomson Licensing S

. A.

フランス国、エフ-92100 プロー

ニュ ビヤンクール、ケ アルフォンス

ル ガロ、46番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

最終頁に続く

(54) 【発明の名称】非線形プロセッサ

## (57) 【要約】

シグナルプロセッサは、非線形伝達関数を提供し、プロセッサ出力と、コモンバイアスに参照される非線形の変曲点を提供する。プロセッサ出力と非線形の変曲点は、時変コモンモードの変動に対する阻止を示す。

**【特許請求の範囲】****【請求項 1】**

時変信号とコモンモードバイアスを含む部分的な差動信号を増幅して、前記部分的な差動信号にかかる時変コモンモード信号を阻止するためのプロセッサと、

前記コモンモードバイアスの代表値である閾値レベルを決定するための手段と、

前記時変信号と前記閾値レベルの間に存在する所定の関係に応答して、前記プロセッサの利得を変更するための手段と、

前記時変コモンモード信号が前記所定の関係を変更することを実質的に防ぐための手段と、

、

を備える非線形プロセッサ。

10

**【請求項 2】**

前記利得を変更するための2つ以上の前記手段が設けられ、第1の利得の領域から相対的に高い利得の領域への利得の変更を生成する、

請求項1記載の非線形プロセッサ。

**【請求項 3】**

前記利得を変更するための2つ以上の前記手段が設けられ、第1の利得の領域から相対的に低い利得の領域への利得の変更を生成する、

請求項1記載の非線形プロセッサ。

**【請求項 4】**

前記利得を変更するための3つ以上の前記手段が設けられ、第1の利得の領域から相対的に低い利得の第2の領域への利得の変更、第1の利得の領域から前記第2の領域よりも相対的に高い利得を有する第3の領域への利得の変更を生成する、

請求項1記載の非線形プロセッサ。

20

**【請求項 5】**

前記利得を変更するための3つ以上の前記手段が設けられ、第1の利得の領域から相対的に高い利得の第2の領域への利得の変更、第1の利得の領域から前記第2の領域よりも相対的に低い利得を有する第3の領域への利得の変更を生成する、

請求項1記載の非線形プロセッサ。

**【請求項 6】**

前記閾値は、前記コモンモードバイアスの減衰及び直流変換された代表値である、

請求項1乃至5のいずれか記載の非線形プロセッサ。

30

**【請求項 7】**

1つ以上の前記閾値は、前記コモンモードバイアスの値よりも下に配置される、

請求項6記載の非線形プロセッサ。

**【請求項 8】**

1つ以上の前記閾値は、前記コモンモードバイアスの値よりも上に配置される、

請求項6記載の非線形プロセッサ。

**【請求項 9】**

信号を非線形に処理するための方法であって、

時変信号と部分的な差動信号のためのコモンモードバイアスとを含む部分的な差動信号を

処理して、前記部分的な差動信号にかかる時変コモンモード信号を阻止するステップと、

前記コモンモードバイアスの代表値である閾値レベルを決定するステップと、

前記時変信号と前記閾値レベルの間に存在する所定の関係に応答して、前記部分的な差動

信号の前記処理を非線形に変更するステップと、

前記時変コモンモード信号に応答して、前記所定の関係の変更を防ぐステップと、

を備える方法。

40

**【請求項 10】**

電気信号を非線形に増幅するための装置であって、

第1のトランジスタのベースへの第1の入力と、

第2のトランジスタのベースへの第2の入力と、

50

前記第1のトランジスタのエミッタと前記第2のトランジスタのエミッタとの間に相互接続される第1の抵抗素子と、

前記第1のトランジスタのベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のソースに接続される前記第1のトランジスタのコレクタと、

前記第1のトランジスタのベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のソースに第2の抵抗素子を介して接続される前記第2のトランジスタのコレクタと、前記第2のトランジスタのコレクタと前記第2の抵抗素子の一端からなる接合で、前記第2のトランジスタのコレクタに接続される出力端子と、

前記第1のトランジスタのエミッタと前記第2のトランジスタのエミッタのそれぞれから、直流供給電位の第2のソースに接続される電流源と、

前記第1のトランジスタのエミッタから、第4のトランジスタのコレクタが第4のトランジスタのベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続される、第4のトランジスタのエミッタに接続される第1の2次利得設定抵抗素子と、

閾値電位のソースに接続される前記第4のトランジスタのベースと、

を備える装置。

10

【請求項11】

前記第2のトランジスタのエミッタにその入力が接続され、その出力が前記閾値電位のソースを提供するバッファをさらに含む、

請求項10記載の装置。

20

【請求項12】

前記第2のトランジスタのエミッタにその入力が接続され、1つ以上の分圧点を備える抵抗性ディバイダをその出力が駆動するバッファと、

前記抵抗性ディバイダの一端は前記バッファの出力に接続され、前記抵抗性ディバイダの他端は直流バイアス電位のソースに接続され、

前記閾値電位のソースを提供する前記抵抗性ディバイダのネットワークの第1の分圧点と、

前記バッファの出力と前記第4のトランジスタのベースの間に接続されるバイパスキャパシタと、

をさらに含む請求項10記載の装置。

30

【請求項13】

前記直流バイアス電位のソースは、前記バッファの出力で直流電位よりも低い、

請求項12記載の装置。

30

【請求項14】

前記直流バイアス電位のソースは、前記バッファの出力で直流電位よりも高い、

請求項12記載の装置。

40

【請求項15】

前記第4のトランジスタのベース電位を超える前記第1のトランジスタのベースへの信号入力に応答して、前記第4のトランジスタが導通されるように、前記第4のトランジスタが保持される、

請求項13又は14記載の装置。

40

【請求項16】

前記第2のトランジスタのエミッタから前記第5のトランジスタのエミッタに接続される第2の2次利得設定抵抗素子をさらに備え、

前記第5のトランジスタのコレクタは、前記第5のトランジスタのベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続され、前記第5のトランジスタのベースは、前記抵抗性ディバイダの第2の分圧点に接続され、

前記第5のトランジスタのベース電位を超える前記第1のトランジスタのベースへの前記信号入力に応答して、前記第5のトランジスタが導通されるように、前記第5のトランジスタが保持される、

請求項15記載の装置。

50

**【請求項 17】**

前記第2のトランジスタのエミッタから前記第5のトランジスタのエミッタに接続される第2の2次利得設定抵抗素子をさらに備え、

前記第5のトランジスタのコレクタは、前記第5のトランジスタのベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続され、前記第5のトランジスタのベースは、前記抵抗性ディバイダの第2の分圧点に接続され、

前記第5のトランジスタのベース電位を超える前記第1のトランジスタのベースへの前記信号入力に応答して、前記第5のトランジスタが非導通にされるように、前記第5のトランジスタが保持される、

請求項15記載の装置。 10

**【請求項 18】**

前記第5のトランジスタのベース電位を超える前記第1のトランジスタのベースへの前記信号入力に応答して、前記第4のトランジスタが非導通にされるように、前記第4のトランジスタが保持される、

請求項13又は14記載の装置。

**【請求項 19】**

前記第2のトランジスタのエミッタから前記第5のトランジスタのエミッタに接続される第2の2次利得設定抵抗素子をさらに備え、

前記第5のトランジスタのコレクタは、前記第5のトランジスタのベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続され、前記第5のトランジスタのベースは、前記抵抗性ディバイダの第2の分圧点に接続され、 20

前記第5のトランジスタのベース電位を超える前記第1のトランジスタのベースへの前記信号入力に応答して、前記第5のトランジスタが導通されるように、前記第5のトランジスタが保持される、

請求項18記載の装置。 20

**【請求項 20】**

前記第2のトランジスタのエミッタから前記第5のトランジスタのエミッタに接続される第2の2次利得設定抵抗素子をさらに備え、

前記第5のトランジスタのコレクタは、前記第5のトランジスタのベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続され、前記第5のトランジスタのベースは、前記抵抗性ディバイダの第2の分圧点に接続され、 30

前記第5のトランジスタのベース電位を超える前記第1のトランジスタのベースへの前記信号入力に応答して、前記第5のトランジスタが非導通にされるように、前記第5のトランジスタが保持される、

請求項18記載の装置。 30

**【発明の詳細な説明】****【0001】****[発明の分野]**

本発明は、信号を非線形に処理する信号処理システムに関し、より詳細には、特に、差動構成において信号を非線形に処理するシステムに関する。 40

本出願は、1999年12月1日に提出された米国仮出願第60/168,280号の利点を特許請求するものであり、該出願の全体は、参照により本明細書に組込まれる。

**【0002】****[発明の背景]**

信号処理システムでは、非線形の伝達関数を提供して、差分量によりダイナミックレンジで信号の一部を増幅することが必要とされることがある。この非線形の処理は、1つ以上の理由のために必要とされることがある。たとえば、ビデオ信号処理システムでは、(1)表示されたビデオ画像の主観的な訴えを改善する、(2)カメラ及び表示装置の異なる「ガンマ」特性を補償する、又は(3)カラービデオ表示装置の様々な光出力チャネルの異なる非線形な光出力特性を受け入れるために、非線形処理が使用される場合がある。 50

**【 0 0 0 3 】**

ビデオ信号処理システムにおける共通の問題は、(1)浮遊静電場及び又は電磁場、(2)システムのステージ間のグランド電位差、及び(3)システムのステージ間の供給電位差のための「ノイズ」信号のピックアップである。非線形処理ステージでは、信号についてのバイアス基準と非線形の変曲点の閾値についてのバイアス基準とが異なるかが不確かであり、これにより、「ノイズ」が信号に加わることになる。

**【 0 0 0 4 】**

内部ステージコネクションにおける浮遊静電場及び/又は浮遊電磁場のピックアップを最小にするために、及び/又は信号処理システムにおける回路間のグランド電位差によるグランド誘発ノイズを最小にするために、ツイストペア配線と共に、部分的な差動シグナリング技術が採用される。特に、差動シグナリング1つのコネクションは、部分的な差動ペアの第2のコネクションに伝達される時変信号のために、コモンモードバイアスに伝達する。

10

**【 0 0 0 5 】**

差動増幅器のような後の信号処理は、部分的な差動相互接続にかかるコモンモードの変動を阻止する能力を有するものとして採用される。信号処理の部分は、(東芝社により製造されているTDA6120Q CRTドライバICのような)集積回路のビデオ増幅器に含まれる場合がある。ここでは、電圧利得は、抵抗を減衰させる外部利得設定エミッタを有する差動増幅器により提供される。かかるICを含み、上記された問題を示す特定の信号処理システムの適用の1つの例は、テレビジョンシステムにおけるキネスコープドライバ増幅器である。

20

**【 0 0 0 6 】****[ 発明の概要 ]**

本発明は、上述した問題を認識することに部分的に属し、上記問題を解決する非線形信号処理システムを提供することに部分的に属している。かかるシステムは、時変信号とコモンモードバイアスを含む部分的な差動信号を増幅して、該部分的な差動信号にかかる時変コモンモード信号を阻止するためのプロセッサ、該コモンモードバイアスの代表値である閾値レベルを決定するための手段、該時変信号と該閾値レベルの間に存在する所定の関係に応答して、該プロセッサの利得を変更するための手段、及び該時変コモンモード信号が該所定の関係を変更することを実質的に防ぐための手段を備えている。

30

**【 0 0 0 7 】****[ 発明の実施の形態 ]**

本発明は、添付図面を参照して、以下に記載される詳細な説明により良好に理解されるであろう。図面では、1つの図面以上における同じ参照符号の使用は、同じ又は類似の機能を示している。

本発明は、テレビジョン信号処理に関する例示的な実施の形態の背景で以下に記載される。しかし、本発明は、他のタイプの信号処理システムに適用される場合がある。

**【 0 0 0 8 】**

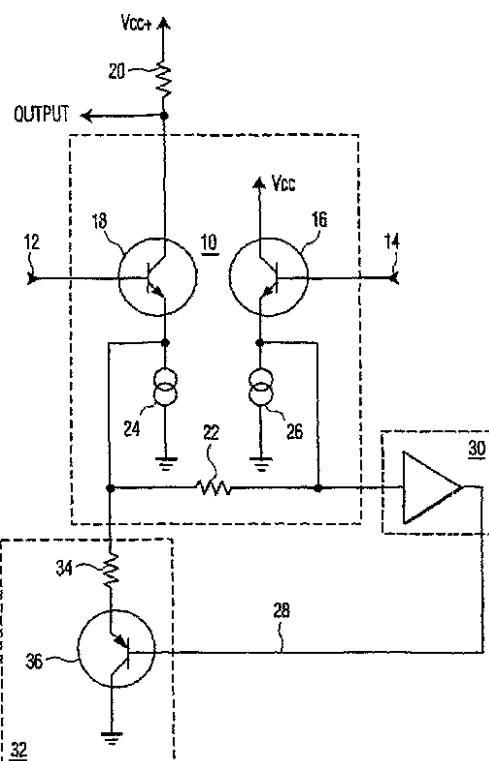

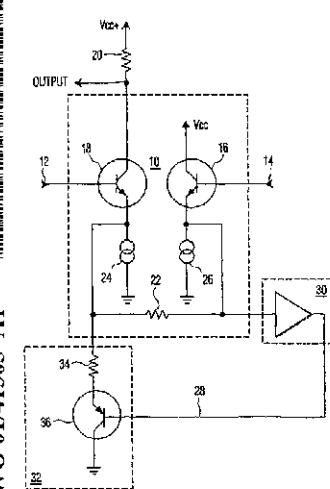

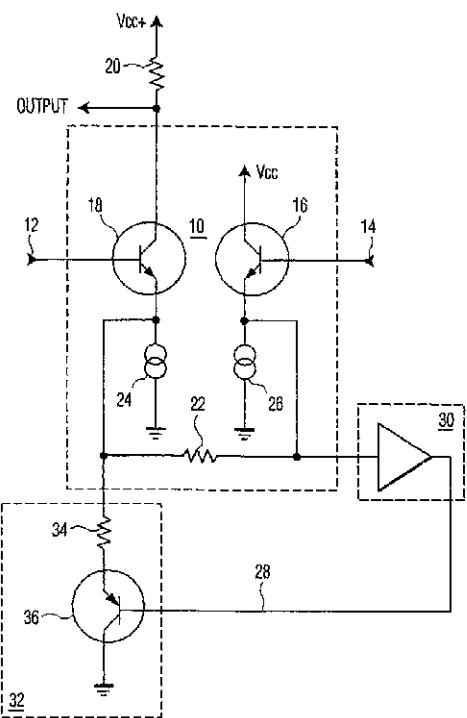

テレビジョン信号処理システムのような信号処理システムは、たとえば、復調された輝度信号又はコンポーネント色信号のいずれかといった電圧信号を増幅するための装置を典型的に含んでいる。増幅器について非線形の利得特性を提供することが望ましい場合がある。図1に示されるように、差動増幅器10が使用され、ここでは、増幅器10への1つの入力が所望の時変信号を含んでおり、他の入力14が増幅器10のためのコモンモードバイアスを提供する。また、時変コモンモード成分がこれら2つの入力信号のそれぞれに存在することが一般的である。

40

**【 0 0 0 9 】**

図1の回路では、コモンモードバイアス14は、トランジスタ16のベースに印加され、時変の入力信号12は、増幅器10のトランジスタ18のベースに印加される。増幅器10の利得は、抵抗素子22に対する抵抗素子20の比により決定される。電流源24及び26は、増幅器10に含まれており、増幅器のための動作電流を供給し、そのコモンモー

50

ド阻止率を改善する。

#### 【0010】

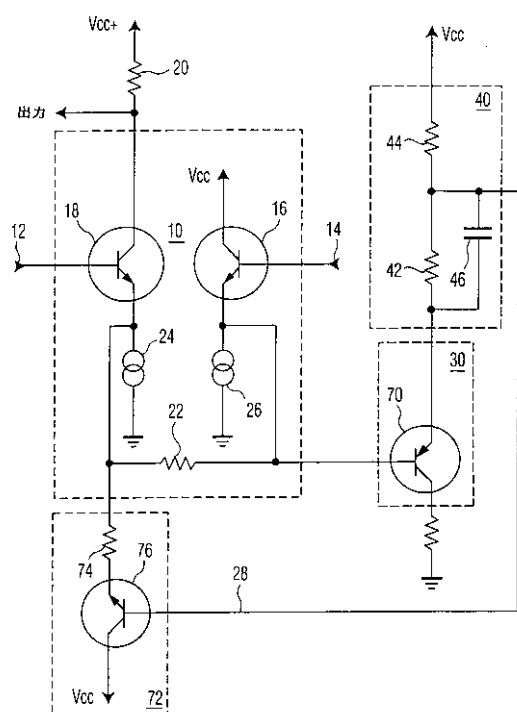

このように構成された増幅器に対して非線形特性を提供することが望まれるとき、一般に、増幅器のための直流バイアスが及び非線形利得を有する回路の両者を提供するためのアプローチが要求される。図2の回路は、バッファ30を通して閾値信号28を導出する。この閾値信号28は、コモンモードバイアスに対する所定の関係を含んでいる。閾値信号28は、コモンモードバイアスに関連する直流成分、及び可能であれば、ある時変のコモンモード成分を備えている。

#### 【0011】

図2に示される回路により生成される閾値信号28は、トランジスタ36及び2次利得設定抵抗素子34を備える非線形ネットワークをバイアスするために使用することができる。非線形ネットワーク32は、トランジスタ18のエミッタとトランジスタ36のベースの間に現れる、増幅器10の入力に印加される時変コモンモード信号をバッファリングする。

#### 【0012】

トランジスタ16に印加されるコモンモードバイアス信号14は、バッファ30によりバッファリングされ、トランジスタ18のエミッタとトランジスタ36のベースの間に現れる。トランジスタ36の条件は、そのベース-エミッタ接合の順バイアスにより決定されるので、トランジスタ36の導通の閾値は、コモンモードバイアス14に対応する入力12のレベルで生じるために決定することができる。

#### 【0013】

閾値信号28以下の時変信号12のレベルでは、トランジスタ36が導通状態にないときに、増幅器10の利得は、抵抗素子22に対する抵抗素子20の比により決定される。閾値信号28以上の時変信号12のレベルでは、トランジスタ36が導通状態にあるとき、増幅器10の利得は、抵抗素子22及び34の並列接続に対する抵抗素子20の比により決定される。

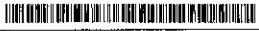

#### 【0014】

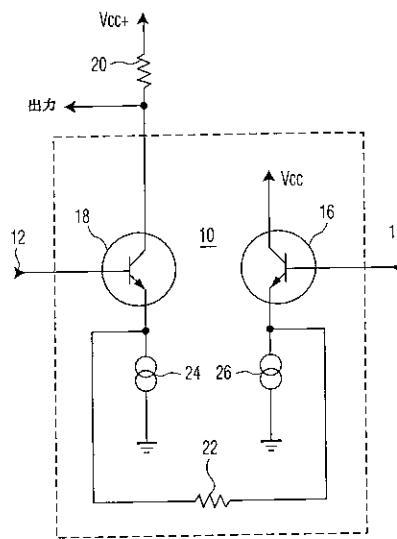

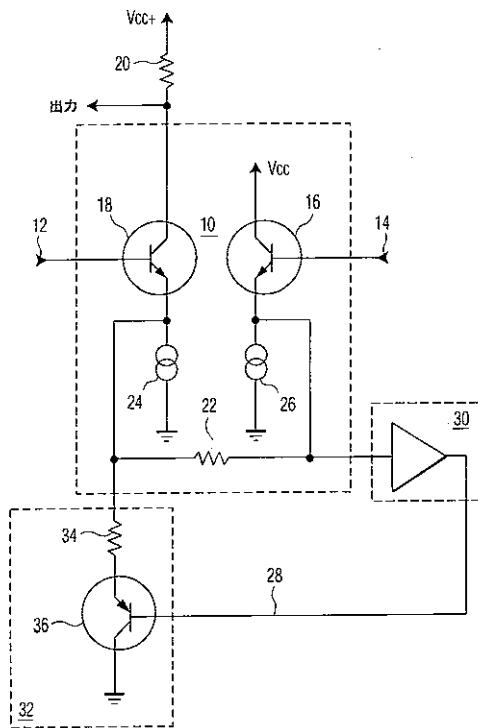

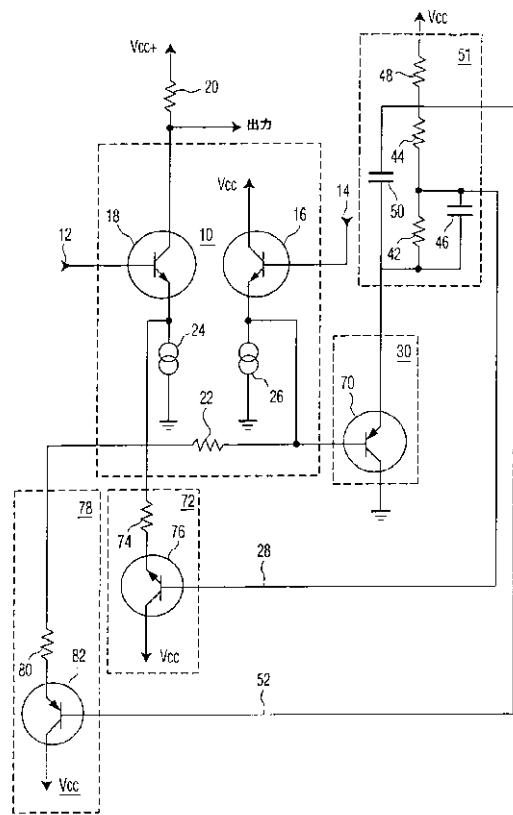

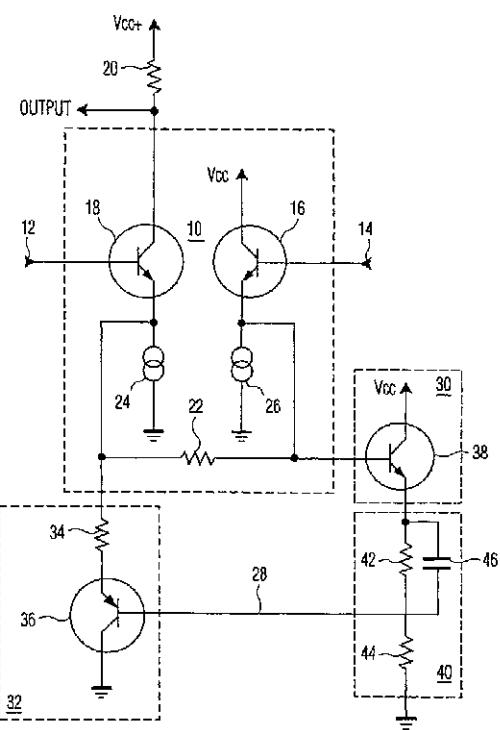

図3に示される実施の形態では、バッファ30は、抵抗素子42及び44並びにバイパスキャパシタ46により構成される抵抗性分圧器を備える分圧器ネットワークを駆動するトランジスタ38を備えるエミッタフォロワステージにより達成される。

#### 【0015】

図3の実施の形態では、閾値信号は、抵抗素子42と抵抗素子44の接続点により構成される分圧器ポイントで駆動される。この回路構成により、閾値は、コモンモードバイアス14の値以下である入力信号の動的なレンジ内のいずれかのレベルで位置される。バイパスキャパシタ46の存在により、時変コモンモード信号は、非線形ネットワーク32の入力28に減衰されることなく生じさせる。

#### 【0016】

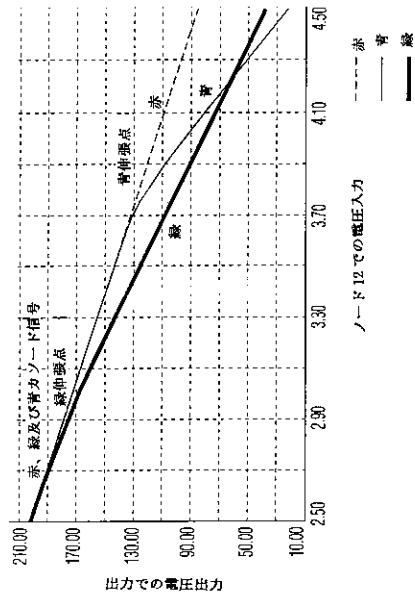

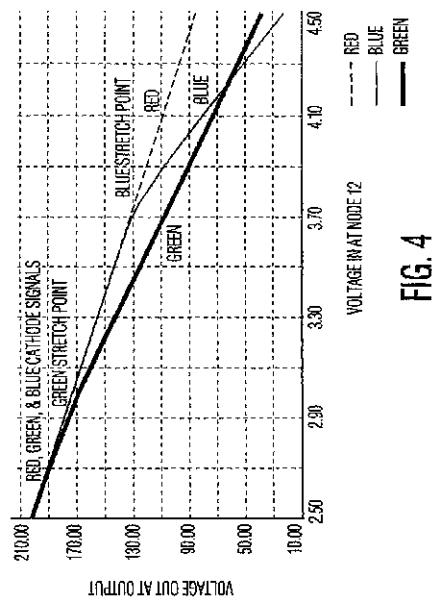

このようにして、図4に示されるような増幅器の伝達関数は、プリセット閾値以上の入力信号について相対的に高い利得を有して得ることができる。なお、図3は、赤、緑及び青のチャネル増幅器のそれぞれについての異なる伝達関数を示す。よく知られているように、増幅器の利得が変化して非線形処理を提供するポイントは、それぞれのチャネルについて異なるプリセットレベルである場合がある。時変コモンモード信号は、トランジスタ36のベースとトランジスタ18のエミッタの間に直接印加されるので、トランジスタ36の導通のための閾値を変更しない。

#### 【0017】

非線形変曲点の基準の1次の温度補償は、トランジスタ36及び38のベース-エミッタ接合の構成により提供される。非線形に関する変曲点が入力コモンモードバイアス14のレベルに非常に近い場合、すなわち、抵抗素子42 << 抵抗素子44である場合、温度補償は、トランジスタ36とトランジスタ38の間の熱整合と同様に良好である。抵抗素子42の値が抵抗素子44に関して増加するにつれて、温度補償は完璧ではなくなるが、ト

10

20

30

40

50

ランジスタ36のベース - エミッタ接合に比較してトランジスタ38のベース - エミッタ接合による好ましい影響をなお有している。

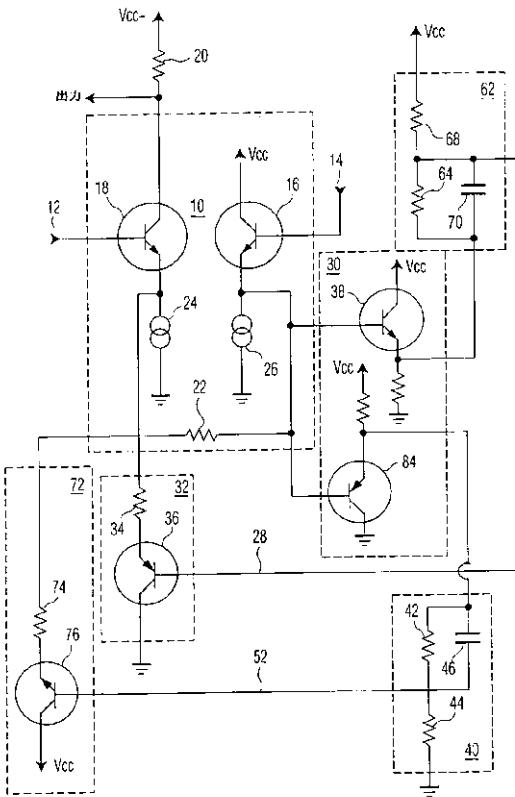

【0018】

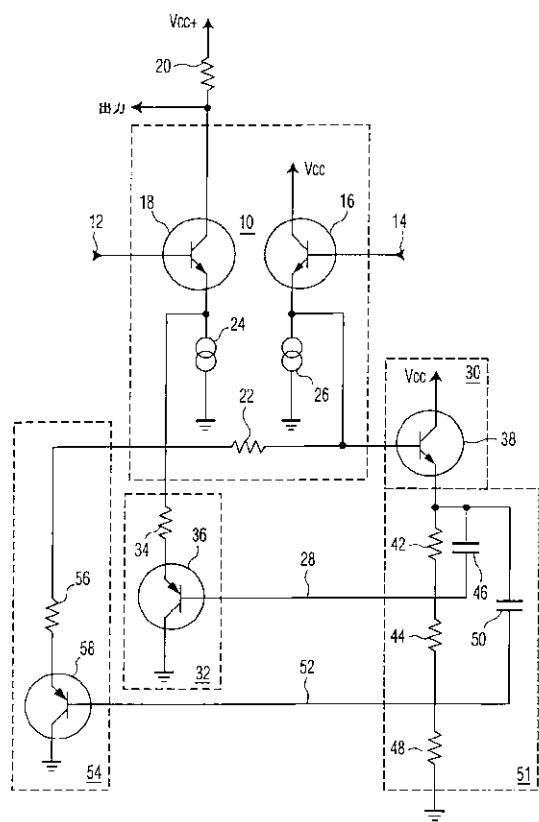

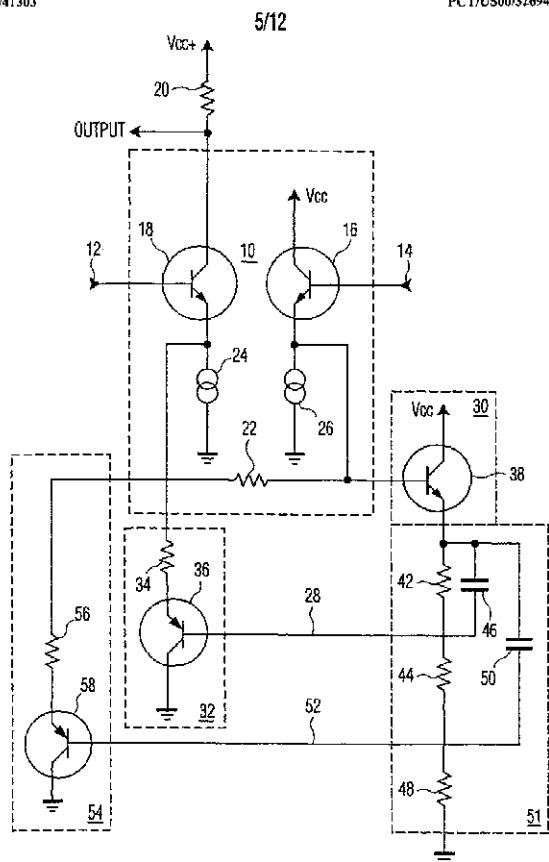

図5は、図3のシステムに類似した信号処理システムの実施の形態を示しているが、2つの非線形に関する変曲点を提供しており、これら変曲点の両者は、入力コモンモードバイアス電圧14のレベルで、又は該レベル以下である。図5に示される回路では、分圧器ネットワーク51が採用され、該ネットワーク51は、抵抗素子44及び48により構成される分圧ポイントで生成される追加の閾値信号52を有している。

【0019】

本実施の形態では、バイパスキャパシタ50が追加され、減衰されていない時変コモンモード信号が、トランジスタ58及び第2の2次利得設定抵抗素子56からなる非線形ネットワーク54への入力で現れることを保証する。

【0020】

図5に関連する3つの利得領域は、以下の場合に生じる。(1)トランジスタ36及びトランジスタ58が導通状態なく、増幅器10の利得が抵抗素子20及び22の比により決定されるとき。(2)トランジスタ58が導通し、増幅器10の利得が抵抗素子56に並列にある抵抗素子22に対する抵抗素子20の比により決定されるとき。及び(3)トランジスタ36及び58が導通し、増幅器10の利得が、抵抗素子22, 34及び56の並列接続に対する抵抗素子20の比により決定されるとき。

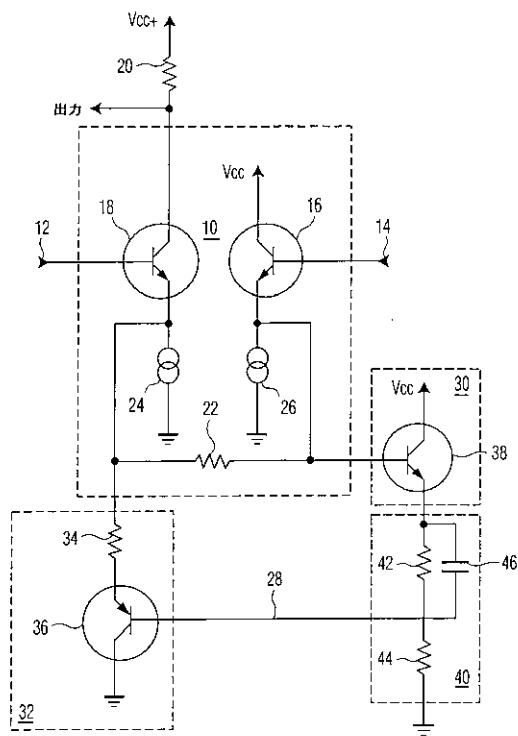

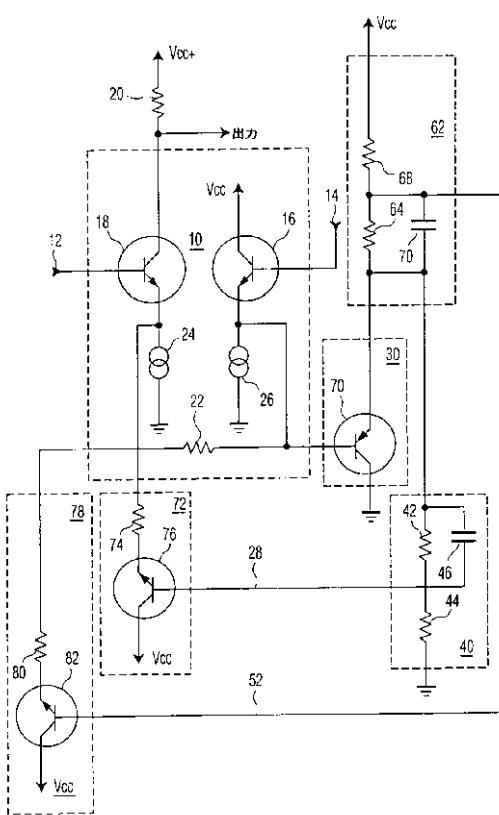

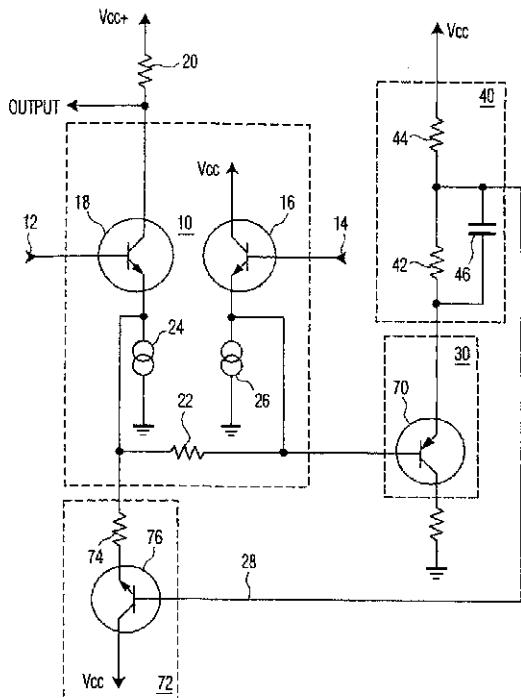

【0021】

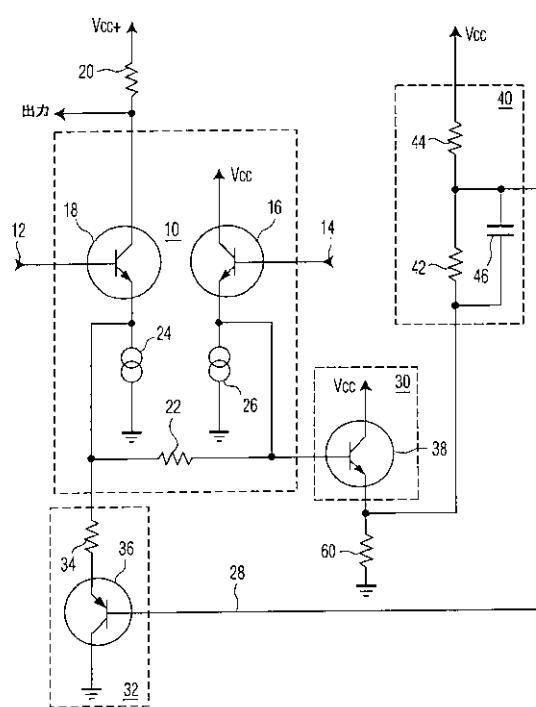

図6における実施の形態は、図3に示される回路の振る舞いに類似した振る舞いを提供するが、入力コモンモードバイアス電圧よりも高い非線形に関する変曲点を有している。図6の回路では、分圧器ネットワーク40は、正の供給電圧が参照され、エミッタ負荷抵抗素子は、トランジスタ38及び分圧器ネットワーク40のバイアス電流を提供するために追加される。2つの利得領域における利得は、図3における回路の記載におけるものと同様に特徴付けられる。

【0022】

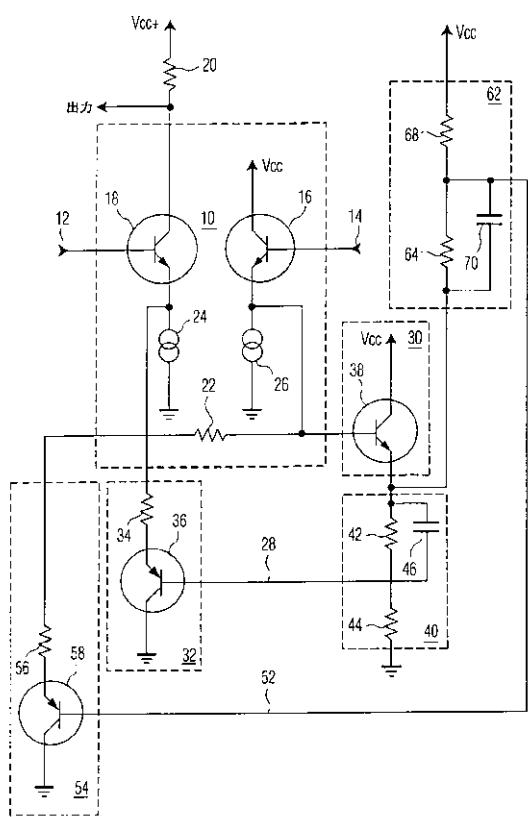

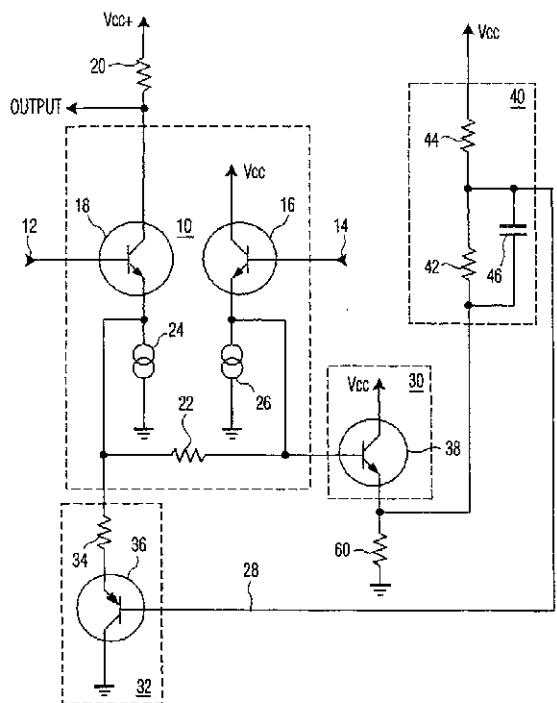

図7の実施の形態は、入力信号レベルの増加について、2つの連続して増加する利得領域を提供し、これら利得領域は、図5の回路の記述において特徴付けられる。

【0023】

図7の回路における変曲点は、入力コモンモードバイアスレベル以上及び以下の両者であり、該バイアスレベル以下の変曲点は、閾値信号28により決定され、該バイアスレベル以上の変曲点は、閾値52により決定され、抵抗素子64及び68からなる追加の分圧器ネットワーク62の分圧器ポイントにより決定される。ここで再び、バイパスキャパシタ70が追加され、減衰されていない時変コモンモードの変動が非線形ネットワーク54への入力52で現れることを保証する。

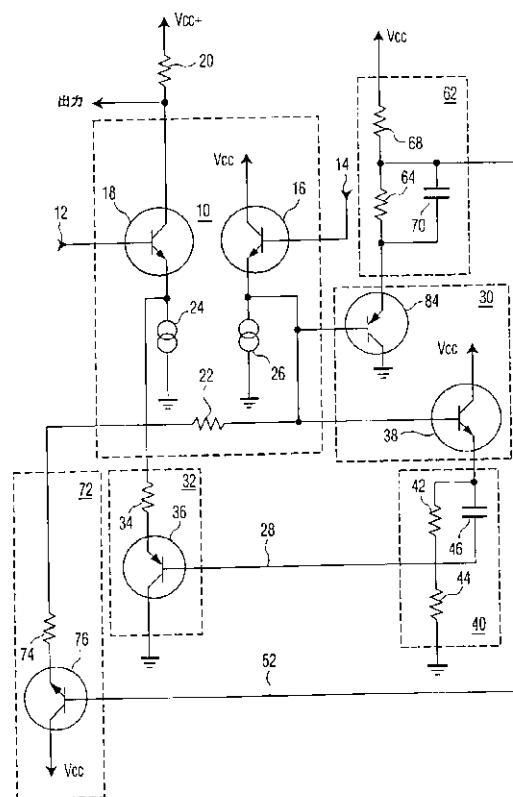

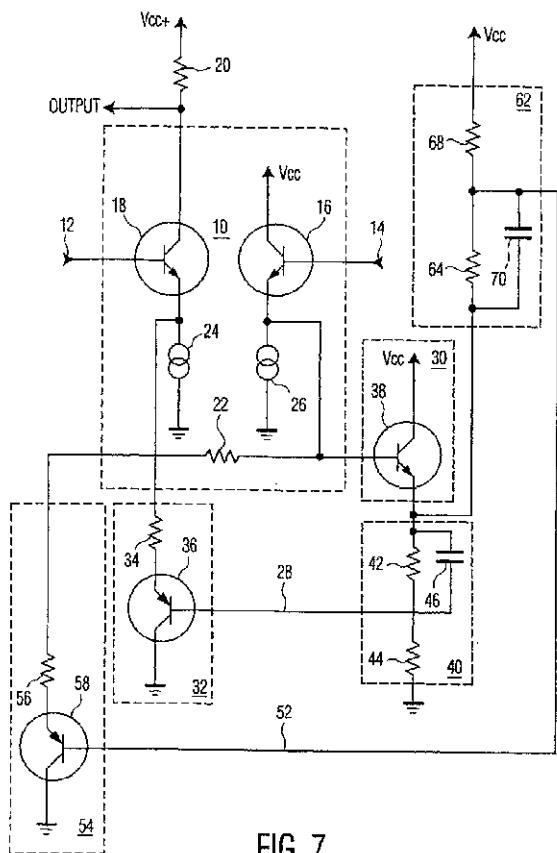

【0024】

図8に示されている信号処理システムは、入力コモンモード電圧のレベル以上である1つの変曲点を有する非線形特性を提供する。この場合、NPNトランジスタ76を備える非線形ネットワーク72が使用され、バッファ30は、PNPトランジスタ70を使用して、非線形ネットワーク72への閾値信号28を提供する。動作は、トランジスタ76が入力時変信号電圧の低いレベルで導通にバイアスされる点を除き、前の例と同じであり、これにより、抵抗素子22及び74の並列接続に対する抵抗素子20の比により決定される利得が増幅器10に提供される。

【0025】

分圧器ネットワーク40により設定される閾値28を超えて入力信号が増加するとき、トランジスタ76は、バイアスが解除され、増幅器10の利得は、抵抗素子22に対する抵抗素子20の比により決定される。このようにして、入力コモンモードバイアスレベル、又は該レベルよりも高い閾値を超える入力信号について、減少された利得を有する非線形特性が決定される。

10

20

30

40

50

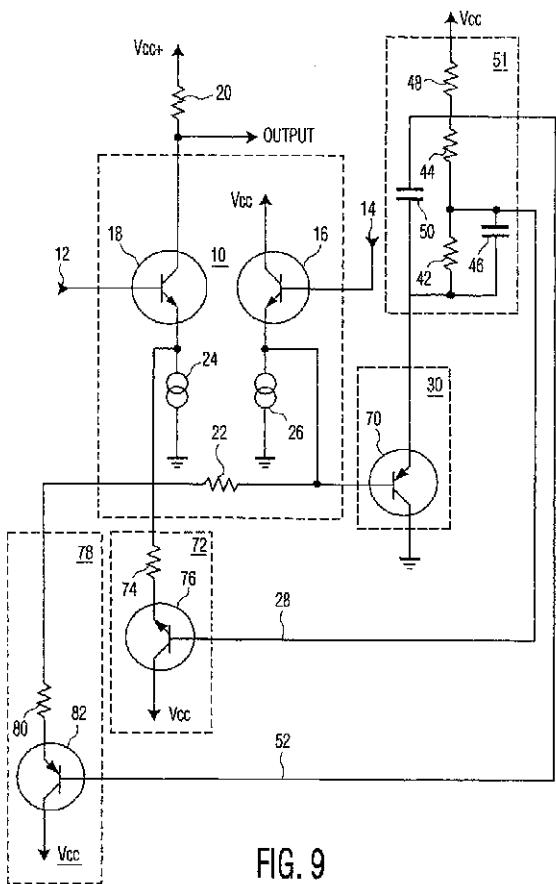

## 【0026】

上述された実施の形態と同様なやり方で、図9に示される実施の形態は、2つの連続的に減少された利得領域を提供し、その利得領域の両者は、入力コモンモードバイアス電圧のレベルを超えて生じる。時変電圧入力の最低の値について、トランジスタ76及び82の両者は導通し、増幅器10の利得は、抵抗素子22, 74及び80の並列接続に対する抵抗素子20の比により決定される。閾値信号28を超える時変信号12のレベルでは、トランジスタ76は、非導通状態にあり、増幅器10の利得は、抵抗素子22及び80の並列接続に対する抵抗素子20の比により決定される。閾値52により決定される時変信号12のなお高いレベルでは、トランジスタ82は非導通となり、増幅器10の利得は、抵抗素子20及び22の比により決定されるようになる。

10

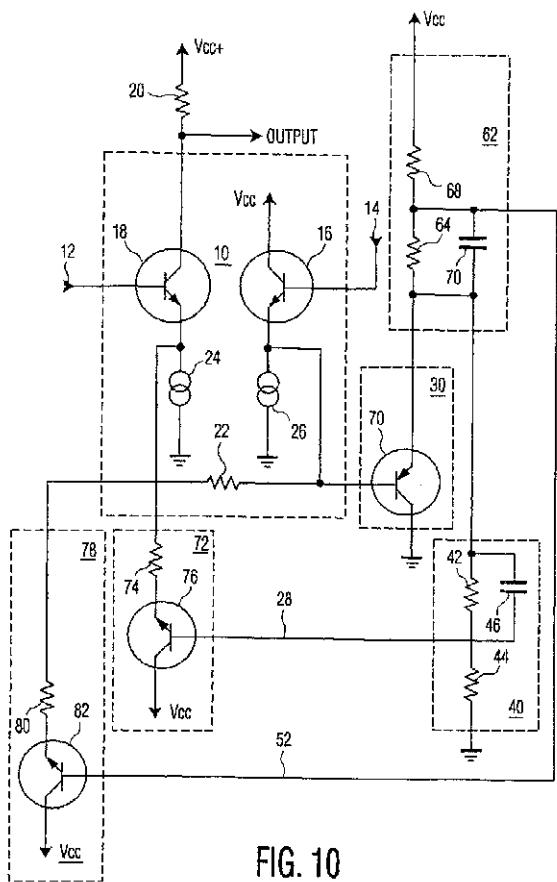

## 【0027】

図10に示される実施の形態は、2つの連続的に減少される利得領域を提供するものであり、一方は、閾値信号28により決定される入力コモンモードバイアスレベル以下で開始し、他方は、閾値信号52により決定される入力コモンモードバイアスレベル以上で開始する。

## 【0028】

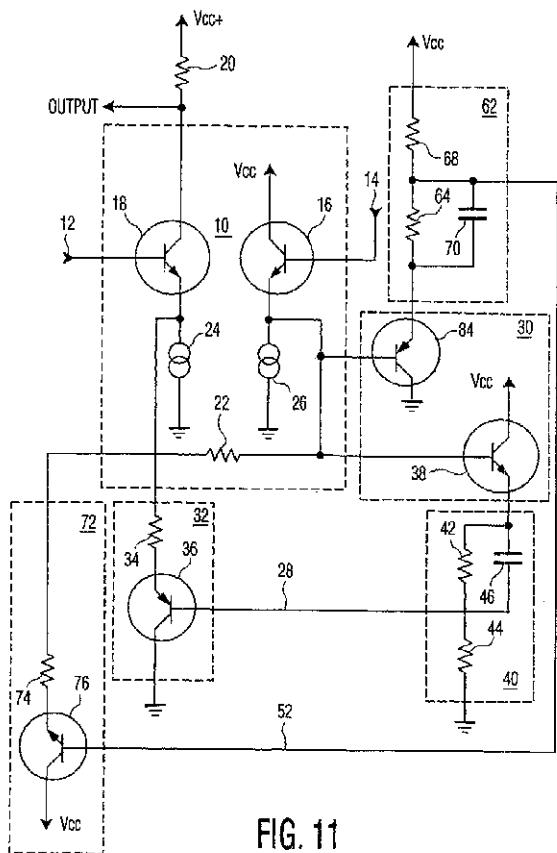

図11の実施の形態は、入力コモンモードバイアス電圧以下であり、相対的に低い利得の領域から相対的に高い利得の領域への遷移を提供する、閾値信号28により決定される変曲点と、入力コモンモードバイアス電圧以上であり、相対的に高い利得の領域から相対的に低い利得の領域への遷移を提供する、閾値信号52により決定される第2の変曲点とを提供する。

20

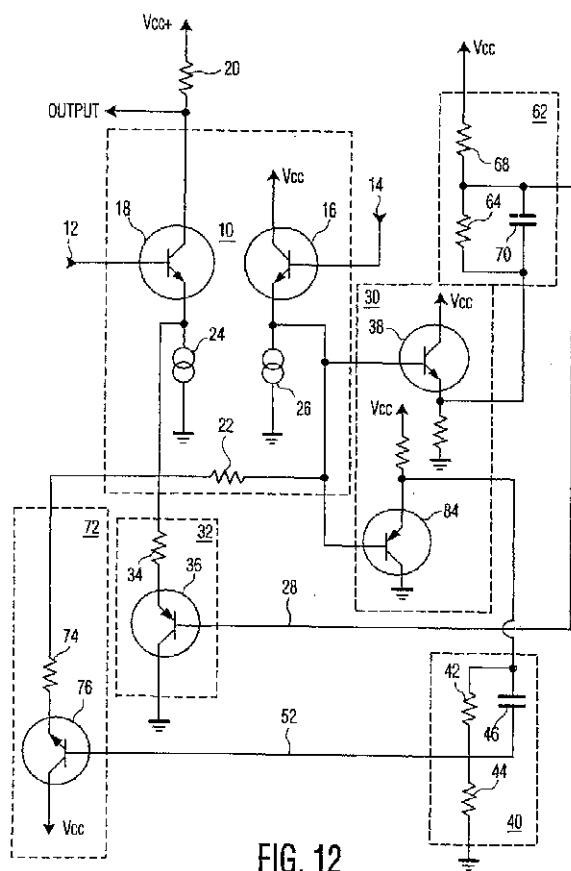

## 【0029】

図12に示される実施の形態は、入力コモンモードバイアス電圧以下であり、トランジスタ76を非導通にすることによる第1の利得の領域から相対的に低い利得の領域への遷移を提供する、閾値信号52により決定される変曲点と、入力コモンモードバイアス電圧以上であり、トランジスタ36の導通により決定される相対的に高い利得の領域への遷移を提供する、閾値信号28により決定される第2の変曲点とを提供する。

30

## 【0030】

第1及び第3の領域における利得は、抵抗素子74及び34のそれぞれの値により、独立に設定される場合がある。図示される全ての他の例示的な実施の形態におけるように、最適な温度トラッキングは、バッファ及びその対応する非線形トランジスタのPNP/NPNペアの使用により、それぞれの非線形に関する変曲点について維持される。

## 【0031】

発明の実施の形態で記載されたように、本発明の概念を実施する信号処理システムは、差動増幅処理により後続される内部ステージの伝達のための部分的な差動シグナリングを提供する。かかる処理は、記載された非線形の特性を生成するための手段を組んでいる。信号増幅及び非線形の閾値決定のためにコモンモードバイアスの使用により、多くのノイズ源が除去される。半導体のタイプ及び回路構成の選択は、非線形閾値の温度に関連する変動の大幅な減少又は除去に寄与する。

40

## 【0032】

また、非線形の変曲点の基準は、ビデオ信号がバイアスされるコモンモード成分を追跡する。また、かかるシステムは、発生された変曲点の基準について1次の温度補償、時変コモンモード増幅器の入力信号によるこれら変曲点の基準の変動の除去、異なる量の電圧利得を有する信号のダイナミックレンジの1つ以上の領域を提供する。

## 【0033】

1つ又は2つの非線形の変曲点を提供する回路の明示的な記載が与えられたが、記載された概念は、入力信号のダイナミックレンジ内のいずれかに位置される変曲点を有するいずれかの数の増加された利得の領域、及び減少された利得の領域を提供するために拡張することができる。

## 【0034】

50

また、テレビジョン信号処理システムの背景において記載されているが、本発明の記載された概念は、非線形処理を含んだ他のタイプの信号処理システムに対して適用可能であることは、当業者には明らかである。

【図面の簡単な説明】

【図 1】

差動増幅器の実施の形態の概念的な回路図である。

【図 2】

入力コモンモードバイアスポイントでの変曲点と、第1の領域における利得よりも高い第2の利得領域における利得とによる2つの利得領域を有する信号処理システムの概念的な回路図である。 10

【図 3】

入力コモンモードバイアスポイント以下の変曲点と、第1の領域における利得よりも高い第2の利得領域における利得とによる2つの利得領域を有する信号処理システムの概念的な回路図である。

【図 4】

図3に示されるようなシステムに典型的な特性応答のグラフを示す図である。

【図 5】

共に入力コモンモードバイアスポイント以下の2つの変曲点と、第1の領域における利得よりもそれぞれ連続的に高い第2及び第3の利得領域における利得とによる3つの利得領域を有する信号処理システムの概念的な回路図である。 20

【図 6】

入力コモンモードバイアスポイント以上の変曲点と、第1の領域における利得よりも高い第2の利得領域における利得とによる2つの利得領域を有する信号処理システムの概念的な回路図である。

【図 7】

入力コモンモードバイアスポイント以上及び以下の変曲点と、第1の領域における利得よりもそれぞれ連続的に高い第2及び第3の利得領域における利得とによる3つの利得領域を有する信号処理システムの概念的な回路図である。

【図 8】

入力コモンモードバイアスポイント以上の変曲点と、第1の領域における利得よりも低い第2の利得領域における利得とによる2つの利得領域を有する信号処理システムの概念的な回路図である。 30

【図 9】

共に入力コモンモードバイアスポイント以上の2つの変曲点と、第1の領域における利得よりもそれぞれ連続的に低い第2及び第3の利得領域における利得とによる3つの利得領域を有する信号処理システムの概念的な回路図である。

【図 10】

入力コモンモードバイアスポイント以上及び以下の変曲点と、第1の領域における利得よりもそれぞれ連続的に低い第2及び第3の利得領域における利得とによる3つの利得領域を有する信号処理システムの概念的な回路図である。 40

【図 11】

入力コモンモードバイアスポイント以上及び以下の変曲点と、第3又は第1の領域のいずれかにおける利得よりも高い第2の利得領域における利得とによる3つの利得領域を有する信号処理システムの概念的な回路図である。

【図 12】

入力コモンモードバイアスポイント以上及び以下の変曲点と、第3又は第1の領域のいずれかにおける利得よりも低い第2の利得領域における利得とによる3つの利得領域を有する信号処理システムの概念的な回路図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【 図 6 】

【図7】

【 図 8 】

【図9】

【図10】

【図11】

【図12】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

7 June 2001 (07.06.2001)

PCT

(10) International Publication Number

**WO 01/41303 A1**(51) International Patent Classification: **H03G 7/06** Del, Frank [US/US]; 5204 Mosswood Court, Indianapolis, IN 46254 (US).(21) International Application Number: **PCT/IL00/032694**

(22) International Filing Date: 1 December 2000 (01.12.2000)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/168,280 1 December 1999 (01.12.1999) US

(31) Applicant (for all designated States except US): THOMSON LICENSING S.A. [FR/FR], 46, quai Alphonse le Gallo, F-92348 Nanterre Cedex (FR).

(72) Inventor; and

(75) Inventor/Applicant (for US only): GRIEPENTROG,

(74) Agents: TRIPOLI, Joseph, S. et al.; Thomson Multimedia Licensing Inc., P.O. Box 5312, Princeton, NJ 08540 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CR, CU, CZ, DE, DK, DM, DZ, ER, ES, FI, GH, GI, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, NG, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TI, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TI, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE,

{Continued on next page}

(54) Title: NON-LINEAR SIGNAL PROCESSOR

(57) Abstract: A signal processor which provides non-linear transfer functions provides a processor output and non-linear inflection points that are referenced to a common bias. The processor output and the non-linear inflection points each exhibit rejection to time variant common-mode variations.

**WO 01/41303 A1**

**WO 01/41303 A1**

IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

**Published:**

- *With international search report.*

- *Before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments.*

WO 01/41303

PCT/US00/32694

1

## NON-LINEAR SIGNAL PROCESSOR

5

Field of the Invention

The present invention relates generally to signal processing systems that process signals non-linearly and, more particularly, to systems that non-linearly process signals in a 10 partially differential configuration.

Background of the Invention

In a signal processing system it is often necessary to provide a non-linear transfer function to amplify portions of the signal dynamic range by different amounts. This non- 15 linear processing is often necessary for one or more reasons. For example, in a video signal processing system, non-linear processing may be used: (1) to improve the subjective appeal of a displayed video image, (2) to compensate for different "gamma" characteristics of cameras and display devices, or (3) to accommodate differing non-linear light output characteristics of the various light output channels of a color video display device.

20 A common problem in video signal processing systems is pick-up of "noise" signals due to (1) stray electrostatic and / or electromagnetic fields, (2) ground potential differences between stages of the system and (3) supply voltage differences between stages of the system. In a non-linear processing stage, it is also problematic if the bias reference for the signal and the bias reference for the non-linear inflection point thresholds are different, which also adds a 25 form of "noise" to the signal.

WO 01/41363

PCT/US00/32694

2

In order to minimize stray electrostatic and or electromagnetic pickup in inter-stage connections and / or to minimize ground induced noise due to ground potential differences between circuits in a signal processing system it is often the case that partially differential signaling techniques will be employed, often in connection with twisted pair wiring. In 5 partially differential signaling, one connection will communicate the common-mode bias for the time variant signal communicated on the second connection of the partially differential pair. Subsequent signal processing, such as differential amplifiers, having the capability to reject common-mode variations imposed on the partially differential interconnections, will be employed. It is often the case that portions of the signal processing will be included in an 10 integrated circuit video amplifier (such as the TDA6120Q CRT Driver IC manufactured by Toshiba) wherein the voltage gain is provided by a differential amplifier having an external gain setting emitter degenerating resistor. One example of a particular signal processing system application that may include such an IC and exhibit the described problems is a kinescope driver amplifier in a television system.

15

Summary of the Invention

The invention resides, in part, in recognizing the problems described above and, in part, in providing a non-linear signal processing system that solves the problem. Such a system comprises a processor for amplifying a partially differential signal, the partially differential 20 signal comprising a time-variant signal and a common-mode bias, and for rejecting a time-variant common-mode signal imposed upon the partially differential signal; means for establishing a threshold level representative of the common-mode bias; means for altering the gain of said processor in response to a predetermined relationship existing between the time-variant signal and the threshold level; and means for substantially preventing the time-variant 25 common-mode signal from modifying the predetermined relationship.

Brief Description of the Drawing

The invention may be better understood by considering the drawing along with the detailed description below. In the drawing:

- 5       Figure 1 shows, in schematic diagram form, an embodiment of a differential amplifier;

- Figure 2 shows, in schematic diagram form, a signal processing system having two gain regions with an inflection point at the input common-mode bias point and the gain in the second gain region being higher than the gain in the first region;

- 10      Figure 3 shows, in schematic diagram form, a signal processing system having two gain regions with an inflection point below the input common-mode bias point and the gain in the second gain region being higher than the gain in the first region;

- 15      Figure 4 shows a graph of a characteristic response typical of a system such as that shown in Figure 3.

- Figure 5 shows, in schematic diagram form, a signal processing system having three gain regions with two inflection points both below the input common-mode bias point and the gain in the second and third gain regions each being successively higher gain than in the first region;

- 20      Figure 6 shows, in schematic diagram form, a signal processing system having two gain regions with an inflection point above the input common-mode bias point and the gain in the second gain region being higher than the gain in the first region'

- Figure 7 shows, in schematic diagram form, a signal processing system having three gain regions with inflection points above and below the input common-mode bias point and the gain in the second and third gain regions each being successively higher gain than the gain in the first region;

WO 01/41303

PCT/US00/32694

4

Figure 8 shows, in schematic diagram form, a signal processing system having two gain regions with an inflection point above the input common-mode bias point and the gain in the second gain region being lower than the gain in the first region;

5 Figure 9 shows, in schematic diagram form, a signal processing system having three gain regions with two inflection points both above the input common-mode bias point and the gain in the second and third gain regions each being successively lower than the gain in the first region;

10 Figure 10 shows, in schematic diagram form, a signal processing system having three gain regions with inflection points above and below the input common-mode bias point and the gain in the second and third gain regions each being successively lower than the gain in the first region;

15 Figure 11 shows, in schematic diagram form, a signal processing system having three gain regions with inflection points above and below the input common-mode bias point and the gain in the second region being higher than the gains in either the third or the first regions; and

Figure 12 shows, in schematic diagram form, a signal processing system having three gain regions with inflection points above and below the input common-mode bias point and the gain in the second region being lower than the gains in either the third or the first regions.

20 In the Drawing, the use of an identical reference designator in more than one Figure indicates the same or similar features in the Figures.

WO 01/41303

PCT/US00/32694

5

Detailed Description

The invention is described below in the context of an exemplary embodiment involving a television signal processing system. However, the invention may be applicable to other types of signal processing systems.

5       A signal processing system such as television signal processing system typically includes apparatus for amplifying voltage signals, for example either a demodulated luminance signal or component color signals. Providing a non-linear gain characteristic for the amplifier is often desirable. As shown in figure 1, it is often the case that a differential amplifier 10 is used, wherein one input 12 to amplifier 10 contains the desired time variant 10 signal and the other input 14 provides the common-mode bias for amplifier 10. It is also common that a time variant common-mode component will reside on each of these two input signals. In the circuit of figure 1 the common-mode bias 14 is applied to the base of transistor 16, and the time variant input signal 12 is applied to the base of transistor 18 of amplifier 10. The gain of amplifier 10 is determined by the ratio of resistor 20 to resistor 22. Current 15 sources 24 and 26 are included in amplifier 10 to provide operating current for the amplifier and to improve its common-mode rejection ratio.

When it is desired to provide a non-linear characteristic to an amplifier so constructed, an approach to providing, in common, both a DC bias for the amplification and the non-linear gain circuitry is required. The circuit of figure 2 derives a threshold value signal 28 through 20 buffer 30, the threshold value signal 28 bearing a predetermined relationship to the common-mode bias. The threshold value signal 28 comprises a DC component related to the common-mode bias and possibly some time variant common-mode component. The threshold value signal 28 produced by the circuit shown in Figure 2 can be used to bias a non-linear network 32 comprising transistor 36 and secondary gain setting resistor 34. Non-linear network 32 is 25 configured such that the time variant common-mode signal which is applied to the inputs of

WO 01/41303

PCT/US00/32694

6

amplifier 10 is buffered and appears between the emitter of transistor 18 and the base of

transistor 36. The common-mode bias signal 14 applied to transistor 16 is buffered by buffer

30 and also appears between transistor 18 emitter and transistor 36 base. Because conduction

of transistor 36 is determined by forward bias of its base to emitter junction, the threshold of

5 conduction of transistor 36 can be determined to occur at the level of input 12 that

corresponds to common-mode bias 14. At levels of time variant signal 12 below threshold

value signal 28, when transistor 36 is not conductive, the gain of amplifier 10 is determined

by the ratio of resistor 20 to resistor 22. At levels of time variant signal 12 above threshold

value signal 28, when transistor 36 is conductive the gain of 10 is determined by the ratio of

10 resistor 20 to the parallel combination of resistors 22 and 34.

In the embodiment shown in figure 3, buffer 30 is accomplished with the emitter

follower stage comprising transistor 38 which drives divider network 40, comprising a

resistive divider formed by resistors 42 and 44 and bypass capacitor 46. In the embodiment of

Figure 3, the threshold value signal is derived at the divider point formed by the junction of

15 resistors 42 and 44. This circuit configuration allows the threshold value to be located at any

level within the input signal dynamic range which is below the value of common-mode bias

14. The presence of bypass capacitor 46 causes the time variant common-mode signal to

appear un-attenuated at input 28 of non-linear network 32. In this way an amplifier transfer

function such as shown in figure 4, having relatively higher gain for input signals above a

20 preset threshold, can be obtained. Note that Figure 3 shows a different transfer function for

each of the red, green, and blue channel amplifiers. As is well known, the point at which the

amplifier gain changes to provide non-linear processing may be at a different preset level for

each channel. Because the time variant common-mode signal is applied directly between

transistor 36 base and transistor 18 emitter, it does not alter the conduction threshold of

25 transistor 36. First order temperature compensation of the non-linear inflection point

WO 01/41303

PCT/US00/32694

7 reference is provided by the configuration of the base-emitter junctions of transistors 36 and 38. If the non-linear inflection point is very close to the input common-mode bias 14 level, i.e., resistor 42 << resistor 44, the temperature compensation will be as good as the thermal match between transistors 36 and 38. As the value of resistor 42 increases with respect to 5 resistor 44, the temperature compensation will be less than perfect, but will still have a favorable influence due to transistor 38 base-emitter junction variation as compared to those of transistor 36 base-emitter junction.

Figure 5 shows a signal processing system embodiment similar to that of figure 3, but which provides two non-linear inflection points, both of which are at or below the level of the 10 input common-mode bias voltage 14. In the circuit shown in figure 5 a divider network 51 is employed, network 51 having an additional threshold value signal 52 developed at the divider point formed by resistors 44 and 48. In this embodiment bypass capacitor 50 is added to assure that the un-attenuated time variant common-mode signal appears at the input 52 to non-linear network 54 comprised of transistor 58 and a second secondary gain setting resistor 56. 15 The three gain regions associated with figure 5 occur: (1) when neither transistor 36 nor transistor 58 are conducting and the gain of amplifier 10 is determined by the ratio of resistors 20 and 22, (2) when transistor 58 conducts and the gain of amplifier 10 is determined by the ratio of resistor 20 to resistor 22 in parallel with resistor 56, and (3) when both transistors 36 and 58 are conducting and the gain of amplifier 10 is determined by the ratio of resistor 20 to 20 the parallel combination of resistors 22, 34 and 56.

The embodiment in Figure 6 provides a behavior similar to that of the circuit shown in Figure 3, but which has a non-linear inflection point which is higher than the input common-mode bias voltage. In the circuit of figure 6, divider network 40 is referenced to a positive supply voltage and an emitter load resistor 60 is added to provide bias current for transistor 38

WO 01/41303

PCT/US00/32694

8

and divider network 40. The gains in the two gain regions are characterized the same as in the description of the circuit in figure 3.

The embodiment of figure 7 will provide two successively increasing gain regions for increasing input signal levels, these gain regions being as characterized in the description of the circuit of figure 5. The inflection points in the circuit of figure 7 are both above and below the input common-mode bias level, the lower inflection point being determined by the threshold value signal 28 and the higher being determined by the threshold value 52, determined by the divider point of an additional divider network 62 comprised of resistors 64 and 68. Here again bypass capacitor 70 is added to assure the un-attenuated time variant common-mode variation appears at the input 52 to non-linear network 54.

The signal processing system embodiment shown in figure 8 will provide a non-linear characteristic having a single inflection point which is above the level of the input common-mode voltage. In this case, non-linear network 72, comprising an NPN transistor 76, is employed and buffer 30 employs transistor 70, a PNP, to provide threshold value signal 28 to non-linear network 72. Operation is similar to previous examples except that transistor 76 is biased into conduction at lower levels of input time variant signal voltage, thus providing amplifier 10 with a gain determined by the ratio of resistor 20 to the parallel combination of resistors 22 and 74. As the input signal increases beyond the threshold value 28 set by divider network 40, transistor 76 is biased off and the gain of amplifier 10 is determined by the ratio of resistors 20 and 22. In this way a non-linear characteristic is determined which has a reduced gain for input signals above a threshold which is at or higher than the input common-mode bias level.

In a manner similar to the embodiments described above, the embodiment shown in figure 9 provides two successively reduced gain regions, both of which occur above the level of the input common-mode bias voltage. For the lowest values of time variant voltage input

WO 01/41303

PCT/US00/32694

9

both transistors 76 and 82 are conducting and the gain of amplifier 10 is determined by the ratio of resistor 20 to the parallel combination of resistors 22, 74 and 80. At a level of time variant signal 12 above threshold value signal 28 transistor 76 becomes non-conductive and the gain of amplifier 10 is determined by the ratio of resistor 20 to the parallel combination of resistors 22 and 80. At a yet higher level of time variant signal 12 determined by threshold value 52, transistor 82 becomes non-conductive and the gain of amplifier 10 becomes determined by the ratio of resistors 20 and 22.

The embodiment shown in figure 10 provides two successively reduced gain regions, one starting below and one starting above the input common-mode bias level, as determined by threshold value signals 28 and 52 respectively, while the embodiment of figure 11 provides an inflection point, determined by threshold value signal 28, which is below the input common-mode bias voltage and provides a transition from a region of relatively lower gain to a region of relatively higher gain, then a second inflection point, determined by threshold value signal 52, which is above the input common-mode bias level and provides a transition from a region of relatively higher gain to one having a relatively lower gain.

The embodiment shown in figure 12 provides an inflection point, determined by threshold value signal 52, which is below the input common-mode bias voltage and provides a transition from a first gain to a region of relatively lower gain by causing transistor 76 to become non-conductive, then a second inflection point, determined by threshold value signal 28, which is above the input common-mode bias level and provides a transition to a relatively higher gain, this higher gain being determined by conduction of transistor 36. The gains in the first and third regions may be independently set by the values of resistors 74 and 34 respectively. As in all the other exemplary embodiments shown, optimal temperature tracking is maintained for each non-linear inflection point, by use of PNP / NPN pairs for the buffer and its corresponding non-linear transistor(s).

WO 01/41303

PCT/US00/32694

10

As described herein, signal processing systems embodying principles of the invention provide for partially differential signaling for inter-stage communication followed by differential amplifier processing of the signal, such processing incorporating means for generating the described non-linear characteristics. By use of a common bias for the signal amplification and the non-linear threshold determination, many sources of noise are eliminated. Selection of semiconductor types and circuit configurations contributes to substantial reduction or elimination of temperature-related variations of the non-linear threshold. Also, non-linear inflection point references track the common-mode component on which the video signal is biased. Such systems also provide first-order temperature compensation for the developed inflection point references, elimination of variation of these inflection point references due to time variant common-mode amplifier input signals, and one or more regions of the signal dynamic range having differing amounts of voltage gain.

Although explicit descriptions of circuits providing one or two non-linear inflection points have been provided, it should be clear that the concepts described can be expanded to provide any number of regions of increased and decreased gain having inflection points located anywhere within the input signal's dynamic range. Also, although described in the context of television signal processing systems, it will be apparent to one skilled in the art that the described principles of the invention are applicable to other types of signal processing systems that involve non-linear processing.

WO 01/41303

PCT/US00/32694

**11

CLAIMS**

1. A non-linear processor, comprising:

- a processor for amplifying a partially differential signal, said partially differential signal comprising a time-variant signal and a common-mode bias, and for rejecting a time-variant common-mode signal imposed upon said partially differential signal;

- means for establishing a threshold level representative of said common-mode bias;

- means for altering the gain of said processor in response to a predetermined relationship existing between said time-variant signal and said threshold level; and

- means for substantially preventing said time-variant common-mode signal from modifying said predetermined relationship.

2. Non-linear processor as in claim 1, wherein two or more of said means for altering the gain are employed and produce a gain alteration from a first region gain to a region of relatively higher gain.

3. Non-linear processor as in claim 1, wherein two or more of said means for altering the gain are employed and produce a gain alteration from a first region gain to a region of relatively lower gain.

4. Non-linear processor as in claim 1, wherein three or more of said means for altering the gain are employed and produce gain alterations from a first region gain to a second region of relatively lower gain to a third region having relatively higher gain than said second region.

20

WO 01/41303

PCT/US00/32694

12

5. Non-linear processor as in claim 1, wherein three or more of said means for altering the gain are employed and produce gain alterations from a first region gain to a second region of relatively higher gain to a third region having relatively lower gain than said second region.

5 6. Non-linear processor as in claims 1, 2, 3, 4 or 5, wherein said threshold values are attenuated and DC translated representations of said common-mode bias.

7. Non-linear processor as in claim 6, wherein one or more of said threshold values are disposed below the value of said common-mode bias.

10

8. Non-linear processor as in claim 6, wherein one or more of said threshold values are disposed above the value of said common-mode bias.

9. A method for non-linearly processing signals, comprising the steps of:

15 processing a partially differential signal comprising a time-variant signal and a common-mode bias for said partially differential signal, said processing to reject a time-variant common-mode signal imposed upon said partially differential signal; developing a threshold value representative of said common-mode bias; altering non-linearly said processing of said partially differential signal in response to

20 a predetermined relationship existing between said time-variant signal and said threshold level; and preventing alterations of said predetermined relationship in response to said time-variant common-mode signal.

10. Apparatus for non-linearly amplifying electrical signals, comprising:

- a first input to the base of a first transistor;

- a second input to the base of a second transistor;

- 5        a first resistor interconnected between the emitters of said first and said second transistors;

- the collector of said first transistor connected to a source of DC supply potential adequate to reverse bias the base to collector junction of said first transistor;

- the collector of said second transistor connected through a second resistor to a source of DC

- 10      supply potential adequate to reverse bias the base to collector junction of said first transistor;

- an output terminal connected to said second transistor collector at the junction of said second transistor collector and one end of said second resistor;

- current sources connected from each of the emitters of said first and said second transistors to a second source of DC supply potential;

- 15      a first secondary gain setting resistor connected from the emitter of said first transistor to the emitter of a fourth transistor, the collector of said fourth transistor connected to a collector DC supply potential adequate to reverse bias the base to collector junction of said fourth transistor; and

- the base of said fourth transistor connected to a source of threshold potential.

20

11. Apparatus as in claim 10, further including a buffer, the input of said buffer being connected to the emitter of said second transistor with the output of said buffer providing said source of threshold potential.

WO 01/41303

PCT/US00/32694

14

12. Apparatus as in claim 10, further including a buffer, the input of said buffer being connected to the emitter of said second transistor with the output of said buffer driving a resistive divider comprising one or more divider points, one end of said resistive divider being connected to the output of said buffer with the other end of said resistive divider being connected to a source of DC bias potential;

- a first divider point of said divider network providing said source of threshold potential; and

- a bypass capacitor connected between the output of said buffer and the base of said fourth transistor.

10

13. Apparatus as in claim 12, wherein said source of DC bias potential is lower than the DC potential at the output of said buffer.

15

14. Apparatus as in claim 12, wherein said source of DC bias potential is higher than the DC potential at the output of said buffer.

15. Apparatus as in claims 13 or 14, wherein said fourth transistor is poled such that said fourth transistor is rendered conductive in response to said signal input to the base of said first transistor exceeding said fourth transistor base potential.

WO 01/41303

PCT/US00/32694

15

16. Apparatus as in claim 15, further comprising a second secondary gain setting resistor connected from the emitter of said second transistor to the emitter of a fifth transistor, the collector of said fifth transistor being connected to a collector DC supply potential adequate to

5 reverse bias the base to collector junction of said fifth transistor, the base of said fifth transistor being connected to a second divider point of said resistive divider; and

the fifth transistor being poled such that said fifth transistor is rendered conductive in response to said signal input to the base of said first transistor exceeding said fifth transistor base potential.

10

17. Apparatus as in claim 15, further comprising a second secondary gain setting resistor connected from the emitter of said second transistor to the emitter of a fifth transistor, the collector of said fifth transistor being connected to a collector DC supply potential adequate to reverse bias the base to collector junction of said fifth transistor, the base of said fifth

15 transistor being connected to a second divider point of said resistive divider; and

the fifth transistor being poled such that said fifth transistor is rendered non-conductive in response to said signal input to the base of said first transistor exceeding said fifth transistor base potential.

- 20 18. Apparatus as in claims 13 or 14, wherein said fourth transistor is poled such that said fourth transistor is rendered non-conductive in response to said signal input to the base of said first transistor exceeding said fourth transistor base potential.

WO 01/41303

PCT/US00/32694

16

19. Apparatus as in claim 18, further comprising a second secondary gain setting resistor connected from the emitter of said second transistor to the emitter of a fifth transistor, the collector of said fifth transistor being connected to a collector DC supply potential adequate to

5 reverse bias the base to collector junction of said fifth transistor, the base of said fifth transistor being connected to a second divider point of said resistive divider; and

the fifth transistor being poled such that said fifth transistor is rendered conductive in response to said signal input to the base of said first transistor exceeding said fifth transistor base potential.

10

20. Apparatus as in claim 18, further comprising a second secondary gain setting resistor connected from the emitter of said second transistor to the emitter of a fifth transistor, the collector of said fifth transistor being connected to a collector DC supply potential adequate to reverse bias the base to collector junction of said fifth transistor, the base of said fifth

15 transistor being connected to a second divider point of said resistive divider; and

the fifth transistor being poled such that said fifth transistor is rendered non-conductive in response to said signal input to the base of said first transistor exceeding said fifth transistor base potential.

20

FIG. 1

RECTIFIED SHEET (REGEEL 91)

ISA/EP

WO 01/41303

PCT/US00/32694

2/12

FIG. 2

RECTIFIED SHEET (REGEL 91)

ISA/EP

WO 01/41303

PCT/US00/32694

3/12

FIG. 3

RECTIFIED SHEET (REGEI 91)

ISA/EP

WO 01/41303

PCT/US00/32694

4/12

FIG. 4

RECTIFIED SHEET (REGEI 91)

ISA/EP

WO 01/41303

PCT/US00/32694

FIG. 5

RECTIFIED SHEET (REGEI 91)

ISA/EP

WO 01/41303

PCT/US00/32694

6/12

FIG. 6

RECTIFIED SHEET (REGEI 91)

ISA/EP

WO-01/41303

PCT/US00/32694

7/12

FIG. 7

RECTIFIED SHEET (REGEL 91)

ISA/EP

WO 01/41303

PCT/US00/32694

8/12

FIG. 8

RECTIFIED SHEET (REGEL 91)

ISA/EP

WO 01/41303

PCT/US00/32694

9/12

FIG. 9

RECTIFIED SHEET (REGEL 91)

ISA/EP

WO 01/41303

PCT/US00/32694

10/12

FIG. 10

RECTIFIED SHEET (REGEL 91)

ISA/EP

WO 01/41303

PCT/US00/32694

11/12

FIG. 11

RECTIFIED SHEET (REGEL 91)

ISA/EP

WO 01/41303

PCT/US00/32694

12/12

FIG. 12

RECTIFIED SHEET (REGEL 91)

ISA/EP

**【手続補正書】**

【提出日】平成13年12月14日(2001.12.14)

**【手続補正1】**

【補正対象書類名】明細書

【補正対象項目名】特許請求の範囲

【補正方法】変更

**【補正の内容】****【特許請求の範囲】****【請求項1】**

時変信号(12)とコモンモードバイアス(14)を含む部分的な差動信号を増幅して、前記部分的な差動信号にかかる時変コモンモード信号を阻止するためのプロセッサ(10)と、

前記コモンモードバイアス(14)の代表値である閾値レベル(28)を決定するための手段(30)と、

前記時変信号(12)と前記閾値レベル(28)の間に存在する所定の関係に応答して、前記プロセッサの利得を変更するための手段(32)と、

前記時変コモンモード信号が前記所定の関係を変更することを実質的に防ぐための手段(30, 32)と、

を備える非線形プロセッサ。

**【請求項2】**

前記利得を変更するための1つ以上の前記手段(72)が設けられ、第1の利得の領域から相対的に高い利得の領域への利得の変更を生成する、

請求項1記載の非線形プロセッサ。

**【請求項3】**

前記利得を変更するための1つ以上の前記手段(32)が設けられ、第1の利得の領域から相対的に低い利得の領域への利得の変更を生成する、

請求項1記載の非線形プロセッサ。

**【請求項4】**

前記利得を変更するための2つ以上の前記手段(32, 72)が設けられ、第1の利得の領域から相対的に低い利得の第2の領域への利得の変更、第1の利得の領域から前記第2の領域よりも相対的に高い利得を有する第3の領域への利得の変更を生成する、

請求項1記載の非線形プロセッサ。

**【請求項5】**

前記利得を変更するための2つ以上の前記手段(72, 78)が設けられ、第1の利得の領域から相対的に高い利得の第2の領域への利得の変更、第1の利得の領域から前記第2の領域よりも相対的に低い利得を有する第3の領域への利得の変更を生成する、

請求項1記載の非線形プロセッサ。

**【請求項6】**

前記閾値(28, 52)は、前記コモンモードバイアス(14)の減衰及び直流変換された代表値である、

請求項1乃至5のいずれか記載の非線形プロセッサ。

**【請求項7】**

1つ以上の前記閾値(28, 52)は、前記コモンモードバイアス(14)の値よりも下に配置される、

請求項6記載の非線形プロセッサ。

**【請求項8】**

1つ以上の前記閾値(28, 52)は、前記コモンモードバイアス(14)の値よりも上に配置される、

請求項6記載の非線形プロセッサ。

**【請求項9】**

信号を非線形に処理するための方法であって、

時変信号(12)と部分的な差動信号のためのコモンモードバイアス(14)とを含む部分的な差動信号を処理して、前記部分的な差動信号にかかる時変コモンモード信号を阻止するステップと、

前記コモンモードバイアス(14)の代表値である閾値レベル(28)を決定するステップと、

前記時変信号(12)と前記閾値レベル(28)の間に存在する所定の関係に応答して、前記部分的な差動信号の前記処理を非線形に変更するステップと、

前記時変コモンモード信号に応答して、前記所定の関係の変更を防ぐステップと、を備える方法。

#### 【請求項 10】

電気信号を非線形に増幅するための装置であって、

第1のトランジスタ(16)のベースへの第1の入力(14)と、

第2のトランジスタ(18)のベースへの第2の入力(12)と、

前記第1のトランジスタ(16)のエミッタと前記第2のトランジスタ(18)のエミッタとの間に相互接続される第1の抵抗素子(22)と、

前記第1のトランジスタ(16)のベース-コレクタ接合を逆バイアスするのに十分な直流供給電位のソースに接続される前記第1のトランジスタ(16)のコレクタと、

前記第2のトランジスタ(18)のベース-コレクタ接合を逆バイアスするのに十分な直流供給電位のソースに第2の抵抗素子(20)を介して接続される前記第2のトランジスタ(18)のコレクタと、

前記第2のトランジスタ(18)のコレクタと前記第2の抵抗素子(20)の一端からなる接合で、前記第2のトランジスタ(18)のコレクタに接続される出力端子と、

前記第1のトランジスタ(16)のエミッタと前記第2のトランジスタ(18)のエミッタのそれぞれから、直流供給電位の第2のソースに接続される電流源(24, 26)と、

前記第2のトランジスタ(18)のエミッタから、第3のトランジスタ(36)のコレクタが第3のトランジスタ(36)のベース-コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続される、第3のトランジスタ(36)のエミッタに接続される第1の2次利得設定抵抗素子(34)と、

閾値電位(28)のソースに接続される前記第3のトランジスタ(36)のベースと、を備える装置。

#### 【請求項 11】

前記第1のトランジスタ(16)のエミッタにその入力が接続され、その出力が前記閾値電位(28)のソースを提供するバッファ(30)をさらに含む、

請求項10記載の装置。

#### 【請求項 12】

前記第1のトランジスタ(16)のエミッタにその入力が接続され、1つ以上の分圧点を備える抵抗性ディバイダ(40)をその出力が駆動するバッファ(30)と、

前記抵抗性ディバイダ(40)の一端は前記バッファ(30)の出力に接続され、前記抵抗性ディバイダ(40)の他端は直流バイアス電位のソースに接続され、

前記閾値電位(28)のソースを提供する前記抵抗性ディバイダのネットワークの第1の分圧点と、

前記バッファ(30)の出力と前記第3のトランジスタ(36)のベースの間に接続されるバイパスキャパシタ(46)と、

をさらに含む請求項10記載の装置。

#### 【請求項 13】

前記直流バイアス電位のソースは、前記バッファ(30)の出力で直流電位よりも低い、請求項12記載の装置。

#### 【請求項 14】

前記直流バイアス電位のソースは、前記バッファ(30)の出力で直流電位よりも高い、

請求項 1 2 記載の装置。

【請求項 1 5】

前記第3のトランジスタ(36)のベース電位を超える前記第2のトランジスタ(18)のベースへの信号入力(12)に応答して、前記第3のトランジスタ(36)が導通されるように、前記第3のトランジスタ(36)が保持される。

請求項 1 3 又は 1 4 記載の装置。

【請求項 1 6】

前記第2のトランジスタ(18)のエミッタから前記第4のトランジスタ(58)のエミッタに接続される第2の2次利得設定抵抗素子(56)をさらに備え、

前記第4のトランジスタ(58)のコレクタは、前記第4のトランジスタ(58)のベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続され、前記第4のトランジスタ(58)のベースは、前記抵抗性ディバイダ(51)の第2の分圧点に接続され、

前記第4のトランジスタ(58)のベース電位を超える前記第2のトランジスタ(18)のベースへの前記信号入力(12)に応答して、前記第4のトランジスタ(58)が導通されるように、前記第4のトランジスタ(58)が保持される。

請求項 1 5 記載の装置。

【請求項 1 7】

前記第2のトランジスタ(18)のエミッタから前記第4のトランジスタ(58)のエミッタに接続される第2の2次利得設定抵抗素子(56)をさらに備え、

前記第4のトランジスタ(58)のコレクタは、前記第4のトランジスタ(58)のベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続され、前記第4のトランジスタ(58)のベースは、前記抵抗性ディバイダ(51)の第2の分圧点に接続され、

前記第4のトランジスタ(58)のベース電位を超える前記第2のトランジスタのベースへの前記信号入力(12)に応答して、前記第4のトランジスタ(58)が非導通にされるように、前記第4のトランジスタ(58)が保持される、請求項 1 5 記載の装置。

【請求項 1 8】

前記第3のトランジスタ(36)のベース電位を超える前記第2のトランジスタ(18)のベースへの前記信号入力(12)に応答して、前記第3のトランジスタ(36)が非導通にされるように、前記第3のトランジスタ(36)が保持される。

請求項 1 3 又は 1 4 記載の装置。

【請求項 1 9】

前記第2のトランジスタ(18)のエミッタから前記第4のトランジスタ(58)のエミッタに接続される第2の2次利得設定抵抗素子(56)をさらに備え、

前記第4のトランジスタ(58)のコレクタは、前記第4のトランジスタ(58)のベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続され、前記第4のトランジスタ(58)のベースは、前記抵抗性ディバイダ(51)の第2の分圧点に接続され、

前記第4のトランジスタ(58)のベース電位を超える前記第2のトランジスタ(18)のベースへの前記信号入力(12)に応答して、前記第4のトランジスタ(58)が導通されるように、前記第4のトランジスタ(58)が保持される。

請求項 1 8 記載の装置。

【請求項 2 0】

前記第2のトランジスタ(18)のエミッタから前記第4のトランジスタ(58)のエミッタに接続される第2の2次利得設定抵抗素子(56)をさらに備え、

前記第4のトランジスタ(58)のコレクタは、前記第4のトランジスタ(58)のベース - コレクタ接合を逆バイアスするのに十分な直流供給電位のコレクタに接続され、前記第4のトランジスタ(58)のベースは、前記抵抗性ディバイダ(51)の第2の分圧点に接続され、

前記第4のトランジスタ(58)のベース電位を超える前記第2のトランジスタ(18)のベースへの前記信号入力(12)に応答して、前記第4のトランジスタ(58)が非導通にされるように、前記第4のトランジスタ(58)が保持される、

請求項18記載の装置。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                      |                                                                                                                                                                                                                                | Int'l. Appl. No.<br>PCT/US 00/32694                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 H03G/06                                                                                                                                                                                             |                                                                                                                                                                                                                                |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                |                                                                                                                                                                                                                                |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H03G H04N                                                                                                               |                                                                                                                                                                                                                                |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                    |                                                                                                                                                                                                                                |                                                                                |

| Electronic database consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal                                                                                                        |                                                                                                                                                                                                                                |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                           |                                                                                                                                                                                                                                |                                                                                |

| Category                                                                                                                                                                                                                                         | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                             | Relevant to claim No.                                                          |

| A                                                                                                                                                                                                                                                | BLOM H ET AL: "ADAPTIVE HIGHLIGHT COMPRESSION IN TODAY'S CCD CAMERAS" SMPTE JOURNAL, US, SMPTE INC. SCARSDALE, N.Y., vol. 101, no. 3, 1 March 1992 (1992-03-01), pages 135-139, XP000263827 ISSN: 0026-1682 the whole document | 1,9,10                                                                         |

| A                                                                                                                                                                                                                                                | US 5 812 218 A (ELBERT MARK) 22 September 1998 (1998-09-22) the whole document                                                                                                                                                 | 1,9,10                                                                         |

| A                                                                                                                                                                                                                                                | US 3 742 377 A (DOBKIN R) 26 June 1973 (1973-06-26)                                                                                                                                                                            | -/-                                                                            |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                   |                                                                                                                                                                                                                                | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| Special categories of cited documents :                                                                                                                                                                                                          |                                                                                                                                                                                                                                |                                                                                |

| 'A' document defining the general state of the art which is not considered to be of particular relevance                                                                                                                                         |                                                                                                                                                                                                                                |                                                                                |

| 'B' earlier document but published on or after the international filing date                                                                                                                                                                     |                                                                                                                                                                                                                                |                                                                                |

| 'C' document which may throw doubts on priority (claim(s)) or which is cited to establish the publication date of another citation or other special reason (as specified)                                                                        |                                                                                                                                                                                                                                |                                                                                |

| 'D' document referring to an oral disclosure, use, exhibition or other means                                                                                                                                                                     |                                                                                                                                                                                                                                |                                                                                |

| 'E' document published prior to the international filing date but later than the priority date claimed                                                                                                                                           |                                                                                                                                                                                                                                |                                                                                |

| 'F' later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |                                                                                                                                                                                                                                |                                                                                |

| 'G' document of particular relevance, the claimed invention cannot be performed without it and it is not common knowledge in the field, this step where the document is taken alone                                                              |                                                                                                                                                                                                                                |                                                                                |

| 'H' document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |                                                                                                                                                                                                                                |                                                                                |

| 'I' document member of the same patent family                                                                                                                                                                                                    |                                                                                                                                                                                                                                |                                                                                |

| Date of the actual completion of the international search                                                                                                                                                                                        | Date of mailing of the International search report                                                                                                                                                                             |                                                                                |

| 23 March 2001                                                                                                                                                                                                                                    | 29/03/2001                                                                                                                                                                                                                     |                                                                                |

| Name and mailing address of the ISA<br>European Patent Office, P.O. Box 8016 Paterlinckstraat 2<br>B-1024 Brussels<br>Tel. (+31-70) 340-2040, TX. 31 651 epo nl<br>Fax: (+31-70) 340-3016                                                        | Authorised officer<br>Yvonnet, J                                                                                                                                                                                               |                                                                                |

Form PCT/ISA/210 (second sheet) (July 1996)

| INTERNATIONAL SEARCH REPORT                         |                                                                                                                                                                                                                                                                                                          | Int'l Application No<br>PCT/US 00/32694 |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| C(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                          |                                         |

| Category                                            | Citation of document, with indication where appropriate, of the relevant passages                                                                                                                                                                                                                        | Relevant to claim No.                   |

| A                                                   | SANO Y ET AL: "INTEGRATED WIDEBAND<br>AMPLIFIER FOR THREE-CHANNEL VIDEO SIGNALS"<br>ELECTRONICS & COMMUNICATIONS IN JAPAN,<br>PART II - ELECTRONICS, US, SCRIPTA TECHNICA,<br>NEW YORK,<br>vol. 77, no. 6, PART 02,<br>1 June 1994 (1994-06-01), pages 81-89,<br>XP000495292<br>ISSN: 8756-663X<br>----- |                                         |

| 1                                                   |                                                                                                                                                                                                                                                                                                          |                                         |

Form PCT/ISA/216 (continuation of second sheet) (July 1992)

page 2 of 2

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No.

PCT/US 00/32694

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Publication date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| US 5812218 A                           | 22-03-1998       | FR 2726706 A<br>EP 0711034 A<br>JP 8279930 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10-05-1996<br>08-05-1996<br>22-10-1996                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| US 3742377 A                           | 26-06-1973       | GB 1528201 A<br>JP 1285860 C<br>JP 56044209 A<br>JP 60006576 B<br>JP 1211010 C<br>JP 51051274 A<br>JP 58038965 B<br>JP 1228351 C<br>JP 51057273 A<br>JP 58054524 B<br>CA 1072645 A<br>DE 2229399 A<br>DE 2607456 A<br>FR 2145164 A<br>FR 2301963 A<br>GB 1350352 A<br>IT 1058855 B<br>JP 51109753 A<br>US 4078206 A<br>AU 538948 B<br>AU 6237580 A<br>CA 1149474 A<br>DE 3034940 A<br>FR 2466137 A<br>GB 2060301 A,B<br>NL 8005221 A<br>US 4347531 A<br>AU 499482 B<br>AU 8603475 A<br>CA 1034216 A<br>DE 2548906 A<br>FR 2290086 A<br>GB 1494054 A<br>NL 7512679 A<br>US 4015212 A<br>AU 8638075 A<br>CA 1042995 A<br>GB 1500407 A<br>US 4021746 A<br>CA 1029445 A<br>DE 2538362 A<br>FR 2283585 A<br>GB 1521286 A<br>JP 1047229 C<br>JP 51050554 A<br>JP 55041050 B<br>US 3987368 A | 11-10-1978<br>09-10-1985<br>23-04-1981<br>19-02-1985<br>12-06-1984<br>06-05-1976<br>26-08-1983<br>19-09-1984<br>19-05-1976<br>05-12-1983<br>26-02-1980<br>18-01-1973<br>26-08-1976<br>16-02-1973<br>17-09-1976<br>18-04-1974<br>10-05-1982<br>28-09-1976<br>07-03-1978<br>06-09-1984<br>26-03-1981<br>05-07-1983<br>09-04-1981<br>27-03-1981<br>29-04-1981<br>24-03-1981<br>31-08-1982<br>26-04-1979<br>05-05-1977<br>04-07-1978<br>13-05-1976<br>28-05-1976<br>07-12-1977<br>04-05-1976<br>29-03-1977<br>12-05-1977<br>21-11-1978<br>08-02-1978<br>03-05-1977<br>11-04-1978<br>11-03-1976<br>26-03-1976<br>16-08-1978<br>28-05-1981<br>04-05-1976<br>22-10-1980<br>19-10-1976 |

Form PCT/ISA/210 (second edition) (July 1992)

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,CH,CY,DE,DK,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CR,CU,CZ,DE,DK,DM,DZ,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,NO,NZ,PL,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TR,TT,TZ,UA,UG,US,UZ,VN,YU,ZA,ZW

(72)発明者 グリペントロッグ, ダル フランク

アメリカ合衆国 インディアナ州 46254 インディアナポリス モスウッド・コート 52

04

F ターム(参考) 5J030 BA08 BB06 BC02

|       |      |      |      |      |      |      |      |      |      |      |

|-------|------|------|------|------|------|------|------|------|------|------|

| 5J066 | AA01 | AA12 | CA53 | CA81 | FA10 | HA02 | HA08 | HA25 | HA29 | KA02 |

| KA05  | MA21 | MD05 | ND01 | ND23 | ND25 | ND28 | SA09 | TA02 |      |      |

| 5J500 | AA01 | AA12 | AC53 | AC81 | AF10 | AH02 | AH08 | AH25 | AH29 | AK02 |

| AK05  | AM21 | AS09 | AT02 | DM05 | DN01 | DN23 | DN25 | DN28 |      |      |