(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4524269号

(P4524269)

(45) 発行日 平成22年8月11日(2010.8.11)

(24) 登録日 平成22年6月4日(2010.6.4)

(51) Int.Cl.

H01L 27/146 (2006.01)

H01L 21/76 (2006.01)

F 1

H01L 27/14

H01L 21/76A

M

請求項の数 4 (全 12 頁)

(21) 出願番号 特願2006-148898 (P2006-148898)

(22) 出願日 平成18年5月29日 (2006.5.29)

(65) 公開番号 特開2006-339643 (P2006-339643A)

(43) 公開日 平成18年12月14日 (2006.12.14)

審査請求日 平成21年2月24日 (2009.2.24)

(31) 優先権主張番号 10/908885

(32) 優先日 平成17年5月31日 (2005.5.31)

(33) 優先権主張国 米国(US)

早期審査対象出願

前置審査

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国 10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】ドープされた分離構造体側壁を有するピクセル・センサ

## (57) 【特許請求の範囲】

## 【請求項 1】

少なくとも 2 つのピクセル・センサ・セルと、該 2 つのピクセル・センサ・セルを分離する分離構造体を含んだピクセル・センサ・セル・アレイを形成するための方法であって、

a ) 第 1 の導電型の基板を提供するステップと、

b ) 前記基板において、一方の前記ピクセル・センサ・セルの第 1 の導電型のピニング層を有する感光デバイスが形成されるべき位置に隣接する第 1 の側壁と、他方の前記ピクセル・センサ・セルのトランジスタ・デバイスが形成されるべき位置に隣接する第 2 の側壁を有する分離構造体を定めるトレンチを形成するステップと、

c ) 前記ピニング層を前記基板に電気的に結合するように、前記トレンチの第 1 の側壁に沿って、前記第 1 の導電型のドーパント材料領域を選択的に形成するステップであって、前記トレンチの内側にドープされた材料層を形成するステップと、前記ドープされた材料層のうち、ドーパント材料領域が対応するトレンチの側壁および底部に形成されることは望ましくない、前記第 2 の側壁に沿った部分を選択的に除去するステップと、ドーパント材料を前記ドープされた材料層から前記トレンチの前記第 1 の側壁内に外方拡散させて、第 1 の導電型の前記ドーパント材料領域を形成するステップとを含むステップと、を含む方法。

## 【請求項 2】

前記ドーパント材料領域が前記トレンチの底部の一部に沿って形成される、請求項 1 に

記載の方法。

【請求項 3】

前記ドーパント材料が、前記トレンチの底部の一部内に外方拡散されて、前記トレンチの底部に沿って第 1 の導電型の前記ドーパント材料領域を形成する、請求項 1 に記載の方法。

【請求項 4】

前記ドーパント材料を前記ドープされた材料層から前記トレンチの前記第 1 の側壁内に外方拡散させて、第 1 の導電型の前記ドーパント材料領域を形成するステップが、前記トレンチ及びドープされた材料層にアニール処理を実施することを含む、請求項 1 に記載の方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、半導体ピクセル・センサ・アレイの製造に関し、より具体的には、選択的にドープされた側壁を含む新規なピクセル・センサ・セル構造体及びそのためのプロセスに関する。

【背景技術】

【0002】

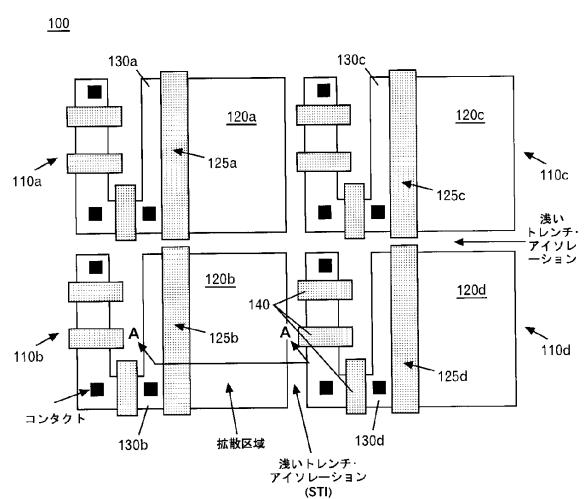

図 1 に示されたように、現在の CMOS イメージ・センサは、ピクセル・センサ・セルのアレイ 100 を含み、図 1 にはそのうちの 110a, ..., 110d と表記された 4 つのピクセル・センサ・セルが図示されている。セル 110a, ..., 110d の各々は、光エネルギーを集めて、読み取り可能な電気信号に変換するために用いられる。各ピクセル・センサ・セル 110 は、基板のドープ領域の上に重なって、下にある部分に光により発生した電荷を蓄積するための、フォト・ダイオード、光ゲート、又は光コンダクタといった感光要素を含む。図 1 に図示された 4 つのピクセル・セル 110a, ..., 110d の群は、それぞれ、コレクション・ウェル即ちフォト・ダイオード・デバイス構造体 120a, ..., 120d のような感光要素を含む。リードアウト回路は、各ピクセル・セルに接続され、リードアウト時に感光要素から電荷を受け取るための拡散領域を含むことがしばしばである。このことは、通例、浮動拡散領域に電気結合されたゲートを有するトランジスタ・デバイスによって達成される。図 1 に図示された 4 つのピクセル・セル 110a, ..., 110d の群は、それぞれの感光要素 120a, ..., 120d からの電荷を、表面チャネルを通してそれぞれの浮動拡散領域 130a, ..., 130d に移送するための、ポリシリコン移送ゲート構造体 125a, ..., 125d をそれぞれ含み、それぞれの浮動拡散領域 130a, ..., 130d は、ピクセル出力信号を選択しゲーティングするための、又は電荷移送に先立ち、浮動拡散領域を所定の電荷レベルにリセットするための、1 つ又はそれ以上のトランジスタ、例えば、細い FET ゲート領域 140 を有する CMOS FET デバイスを含む。

20

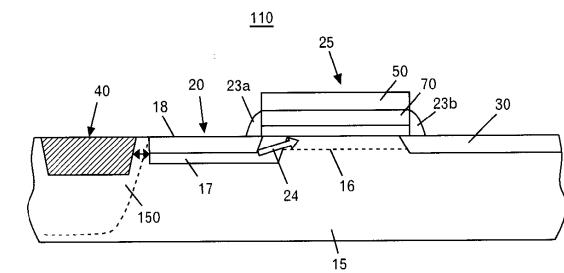

【0003】

図 2 は、図 1 の線 A - A に沿って見た典型的なピクセル・センサ・セル 110 を、より詳細に図示する。図 2 に示されたように、イメージ・センサ・セル 110 は、p+ 型にドープされたピニング層 18 を有するピニングフォト・ダイオード 20 と、下にある軽度にドープされた n 型領域 17 を含む。ピニング・ダイオード 20 は、通例、p 型基板 15 か、或いは p 型エピタキシャル層、又はダイオード・ピニング層 18 より低い p 型濃度を有している p ウェル表面層の上部に形成される。公知のように、表面ピニング層 18 は、基板 15 ( 或いは p 型エピタキシャル層又は p ウェル表面層 ) と電気的に接觸している。従って、フォト・ダイオード 20 は、同一のポテンシャルを有する 2 つの p 型領域 18 及び 15 を有し、それにより、n 型ドープされた領域 17 が、ピニング電圧 ( Vp ) において完全に空乏状態になる。即ち、表面ピニング層 18 は、暗電流をカットダウンするために、基板と電気的に接觸している。ピニングフォト・ダイオードは、フォト・ダイオードが完全に空乏状態になった時に、そのフォト・ダイオードのポテンシャルが一定値 Vp にビ

30

40

50

ニングされることから、「ピニング」と呼ばれる。

【0004】

図2に更に図示されているように、フォト・ダイオード20のn型ドープされた領域17及びp+領域18は、例えば浅いトレンチ・アイソレーション(STI)などの分離構造体40と、薄型スペーサ構造体23a、23bによって囲まれている電荷移送トランジスタ・ゲート25との間に設置される。STI領域40は、セルを隣接するピクセル・セルから分離するために、ピクセル・イメージャ・セルの近傍に配置される。作動中に、ピクセルから発せられた光が、フォト・ダイオード上に合焦され、電子がn型領域17に集まる。移送ゲート25が作動する時、即ち、例えばn型ドープされたポリシリコン層70を含む移送ゲート25に電圧をかけることによってオンにされた時には、光により発生した電荷24が、電荷が蓄積しているドープされたn型ドープ領域17から、移送デバイス表面チャネル16を経由して、例えばn型にドープされた浮動拡散領域30へと移送される。

【0005】

上記のように、各ピクセル・イメージ・セルにおいては、表面ピニング層18は、同じ導電型の基板15に電気的に接触する。現在のところ、ピクセル・センサ・コレクション・ダイオードの(例えばp型ドープされた)表面ピニング層は、コレクション・ダイオード20の一方の縁部に配置された(例えばp型ドープされた)ウェル注入構造体150を経由して基板に接続される。実施の際には、下にある基板ウェル構造体(例えばp-ウェル150)は、フォト・ダイオード及びピニング層構造体と同様にマスク注入技術によって作成され、各々は独立したプロセス・ステップにおいて形成される。

【0006】

ピクセル・センサの暗電流を最小化するためには、コレクション・ダイオードに隣接するSTI側壁上にドープすることも有益である。n型コレクション・ダイオードがSTI側壁と接触した場合には、基板-STI界面に沿ったいかなる表面状態も、コレクション・ダイオードがリセット状態にある時には、空乏状態になったシリコンによってカバーされない。このことは、表面が発生するのに最適な状態であり、ピクセル・センサにおける暗電流に寄与するであろう。コレクション・ダイオードに隣接するSTI側壁がp型にドープされた場合には、正孔が表面をシールドし、表面の発生をなくすことになる。

【0007】

導電性材料の位置合わせの向上、及び、コレクション・ウェル・デバイスの上方の表面ピニング層と下にある基板との間の適切な電気的接触を保証するための1つの技術は、隣接した分離構造体に側壁注入領域を設けることである。

【0008】

STI側壁及び底部をドープして、ピクセル・イメージャ・セルに、基板から表面ピニング層への電気的接続を提供するための角度をつけた注入技術は、例えば、特許文献1において説明されたように、当該技術分野において公知である。フォトレジストの角部を丸めることにより、そのような角度をつけた注入を、精密な配置規則を伴ってマスキングできるようにする更なる方法は、上記の本出願人に譲渡された出願継続中の特許文献2に説明されている。

【0009】

STIの側壁をドープすることは、フォト・ダイオードを囲むSTIの部分のピクセル・センサにおいては有用であるが、アレイの他の部分においては有害な影響を持ちうる。それは、細い電界効果トランジスタ(FET)のSTI側壁におけるより高いドープは、顕著に閾値電圧を上げ、駆動電流強度を下げ、トランジスタの基板電圧の敏感さを増大しかねないからである。更に、拡散部の側壁のドープは、これらのトランジスタのソース・ドレイン拡散を、部分的にカウンタードープすることになる。最終的なドープ量が十分に低い場合には、このことは、電流生成を生じさせかねない。これら全ての影響は、イメージング・セルにおいて望ましいことに反する。よって、従来技術において説明された角度をつけた注入技術によって、細いFETゲート140の近傍の側壁のドープがもたらされ

10

20

30

40

50

た時には、特に寸法が重要視されるイメージ・センサにおいては細いFETのみに注入されることから、全く許容できない状態に至る。

【0010】

従って、FETの近傍の分離構造体側壁領域の注入ドープを引き起こす従来技術を実施した時にもたらされる不利益な影響を避ける目的で、選択的にドープされた側壁を含む、ピクセル・センサ・デバイスを分離するために用いられる分離構造体を提供することが、非常に望ましいであろう。

【0011】

【特許文献1】米国特許出願第2004/0178430号

【特許文献2】米国特許出願第10/905,043号

10

【発明の開示】

【発明が解決しようとする課題】

【0012】

本発明は、特に、ピクセル・センサ構造体、及び、分離構造体側壁内に与えられるドープを調整して、FET近傍の分離構造体側壁をドープする時にもたらされるような潜在的に有害な影響を避けるための改良された技術を含む製造方法に対処するものである。

【課題を解決するための手段】

【0013】

本発明の1つの態様により、特定の側壁及び底部の特定の部分のみをドープされた隣接するピクセル・センサ・セルを離間する、分離構造体が提供される。これは、ピクセル・センサフォト・ダイオードの側壁をドープする一方で、他の構造体の側壁をドープしないことを可能にする。本発明のこの態様により、分離構造体側壁は、堆積された材料からのドーパントが外方拡散されて選択位置における側壁をドープするという拡散プロセスによってドープされる。そうした材料は、側壁の表面上に堆積することが可能である。更なるマスク及びエッチング処理は、ドープが望ましい箇所にのみ材料を残すことが可能である。次いで、アニール・ステップが、いかなる注入が行われることもなしに、シリコンへのドーパントの拡散を生じさせることになる。

20

【0014】

したがって、本発明の1つの態様によれば、ピクセル・センサ・セル構造体を形成するための方法であって、a) 第1の導電型の基板を提供するステップと、b) 第1の導電型の表面ピニング層を有する感光デバイスの位置に隣接して、側壁を有する分離構造体を定めるトレンチを形成するステップと、c) 形成されたピニング層を基板に電気的に結合するようにされたトレンチの第1の側壁に沿って、第1の導電型のドーパント材料領域を選択的に形成するステップと、を含む方法が提供される。

30

【0015】

1つの実施形態においては、ドーパント材料領域を選択的に形成するステップは、トレンチの内側にドープされた材料層を形成するステップと、ドーパント材料をドープされた材料層から分離構造体の第1の側壁内に外方拡散させて、第1の導電型のドーパント材料領域を形成するステップとを含む。

【0016】

40

或いは又はそれに加えて、ドーパント材料領域を選択的に形成するステップは、基板の表面の上にパターン状にフォトレジスト層を形成して、分離構造体の第1の側壁を露出させるステップと、パターン状に形成されたフォトレジスト層の寸法を調整して、分離構造体の露出された第1の側壁におけるドーパント材料のイオン注入を助長するステップと、露出された第1の側壁に沿って、第1の導電型の注入されたドーパント材料を含むドーパント領域を形成するステップと、を含む。

【0017】

本発明の別の態様によれば、少なくとも2つのピクセル・セルを含むピクセル・セル・アレイであって、第2のピクセル・セルに隣接する第1のピクセル・セルと、第1のピクセル・セルと第2のピクセル・セルとを分離し、かつ、側壁を有する第1の分離構造体と

50

、を含み、第1のピクセル・セルに隣接する第1の側壁が、ドーパント材料により選択的にドープされ、第2のピクセル・セルに隣接する第2の側壁が、ドーパント材料により選択的にドープされていない、ピクセル・セル・アレイが提供される。

【0018】

この態様によるピクセル・セル・アレイは、第1のピクセル・セルに隣接する第3のピクセル・セルと、第1のピクセル・セルと第3のピクセル・セルとを分離し、かつ、側壁を有する第2の分離構造体と、をさらに含み、第1のピクセル・セルに隣接する第2の分離構造体の第1の側壁が、ドーパント材料によりドープされ、第3のピクセル・セルに隣接する第2の分離構造体の第2の側壁が、ドーパント材料によりドープされている。

【0019】

本発明の更なる態様によれば、ピクセル・セル・アレイを形成するための方法であって、a) 第2のピクセル・セルに隣接する第1のピクセル・セルを形成するステップと、b) 第1のピクセル・セルと第2のピクセル・セルとの間に、側壁を有する第1の分離構造体を形成して、第1のピクセル・セルと第2のピクセル・セルとを分離するステップと、c) 第1の分離構造体の第1の側壁に沿って、第1の導電型のドーパント材料領域を選択的に形成するステップと、を含む方法が提供される。

【0020】

本発明のこの更なる態様によれば、ドーパント材料領域を選択的に形成するステップは、第1の分離構造体の内側にドープされた材料層を形成するステップと、ドーパント材料をドープされた材料層から第1の分離構造体の第1の側壁内に外方拡散させて、第1の側壁に沿って第1の導電型のドーパント材料領域を形成するステップと、を含む。

【0021】

或いは又はそれに加えて、ドーパント材料領域を選択的に形成するステップは、基板表面上にパターン状にフォトレジスト層を形成して、第1の分離構造体の第1の側壁を露出させるステップと、パターン状に形成されたフォトレジスト層の寸法を調整して、第1の分離構造体の露出された第1の側壁におけるドーパント材料のイオン注入を助長するステップと、第1の分離構造体の露出された第1の側壁に沿って、第1の導電型の注入されたドーパント材料を含むドーパント領域を形成するステップと、を含む。

【0022】

この更なる態様によれば、ピクセル・セル・アレイを形成する方法は、第1のピクセル・セルに隣接する第3のピクセル・セルを形成するステップと、第1のピクセル・セルと第3のピクセル・セルとの間に、側壁を有する第2の分離構造体を形成して、第1のピクセル・セルと第3のピクセル・セルとを分離するステップと、第1のピクセル・セルに隣接する第2の分離構造体の第1の側壁に沿って、第1の導電型のドーパント材料領域を形成するステップと、第3のピクセル・セルに隣接する第2の分離構造体の第2の側壁に沿って、第1の導電型のドーパント材料領域を形成するステップと、を更に含む。

【0023】

コレクション・ウェル・デバイスの表面ピニング層と、本発明の方法により形成された、下にある基板との間に、電気的結合を提供することは、整合の許容度を不要にし、コレクション・ダイオードをより大型にすること、及び光学的効率を増大させることを可能にするという利点を持つ。

【発明を実施するための最良の形態】

【0024】

本発明の目的、特徴、及び利点は、以下の詳細な説明を添付の図面と共に参照することで、当業者には明らかとなるであろう。

【0025】

本発明の1つの態様により、ピクセル・センサ・セルを製造する方法において、分離構造体の角度をつけた注入ドープを行った時に得られる潜在的に有害な影響を回避する一方で、コレクション・ウェル・デバイスの表面ピニング層と下にある基板との間の適切な電気的接続を保証する、改良されたドープ技術が提供される。

10

20

30

40

50

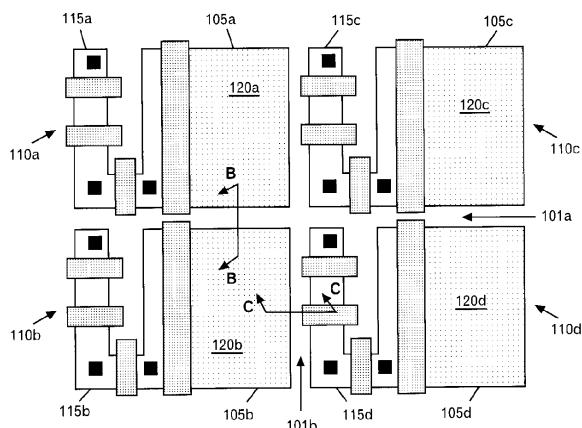

## 【0026】

図3は、本発明により選択的にドープされた側壁を有する分離構造体101a、bによって離間されているピクセル・センサ・セル110a、・・・、110dのアレイ100を含んだ、図1に図示される例示的な現在のピクセル・センサ・デバイスの一部を示す。図3においては、本発明による、それぞれの隣接するコレクション・ウェル・デバイスの表面ピニング層と下にある基板とが確実に電気的に接觸するように有益にドープされる、分離構造体101a、bのそれぞれの側壁105a、・・・、105dと、側壁ドープが回避される分離構造体101a、bのそれぞれの側壁115a、・・・、115dとが図示されている。

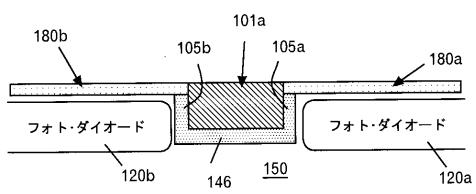

## 【0027】

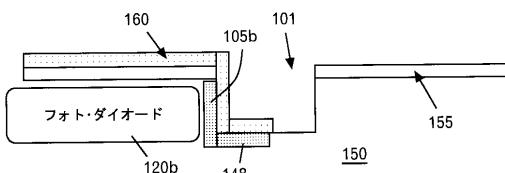

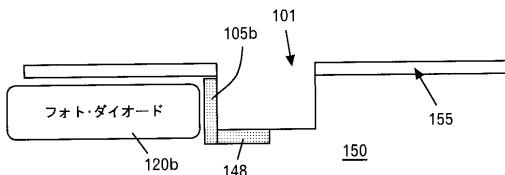

図4は、図3の線B-Bに沿って見た断面を通じて、ピクセル・センサ・セル110a及び110bを離間するドープされた分離構造体101aを示す。図4に図示されたように、ドープされた側壁を有する分離構造体101aは、隣接するセル110a及び110bの2つのフォト・ダイオード領域120a及び120bを離間する。フォト・ダイオード領域120aのドープされた表面ピニング層180a及びフォト・ダイオード領域120bのドープされた表面ピニング層180bと、下にある基板150とが確実に電気的に接続する必要があることから、分離構造体側壁105b及び105aと構造体101aの分離構造体底部146との両方にドーパント材料を与えることは有益である。分離構造体側壁105a及び105b、及び底部146のドーピングは、例えば、本出願人に譲渡された出願継続中の特許文献2に説明されるような角度をつけた注入技術を用いて、又はここにより詳細に説明されるドーパント外方拡散法によって達成することができる。

## 【0028】

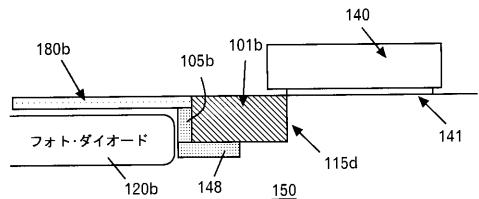

図5は、図3の線C-Cに沿って見た断面を通じて、ピクセル・センサ・セル110b及び110dを離間する部分的にドープされた分離構造体101bを示す。図5に図示されたように、分離構造体101bは、隣接するセル110bのフォト・ダイオード領域120bと、ピクセル・センサ・セル110dに関連付けられた細いFETデバイスのポリシリコン・ゲート140とを離間する。この実施形態においては、フォト・ダイオード領域120bのドープされた表面ピニング層180bと、下にある基板150との間に適切な電気的接続が確実に存在することのみが必要とされる。その結果として、分離構造体側壁105bと、分離構造体101bの下にある底部領域の一部148にのみドーパント材料が与えられることが有益である。分離構造体側壁105b及び底部領域148のドープは、角度をつけた注入技術か、又はここにより詳細に説明されるドーパント外方拡散法によって達成することができる。ここに説明されるように、潜在的に有害な影響を避ける目的で、ドーパント材料は、領域115dに示された分離構造体側壁へは、意図的に与えられない。

## 【0029】

図6-図10は、ドープされた層から不純物（例えばドーパント材料）を外方拡散させて、ピニングフォト・ダイオード120を有するセル110に関連付けられた形成分離構造体の1つ又はそれ以上の側壁にドーパント領域を形成するというステップを含む、センサ・ピクセル・セル製造プロセスにおける方法ステップを示す。外方拡散ステップはまた、分離構造体の底部にドーパント領域を形成するために用いることができる。先で詳細に説明されるように、方法ステップは、トランジスタが形成される区域に近接する分離構造体側壁領域及び底部領域にドーパント材料を選択的に外方拡散しないことにより、潜在的に有害な影響を回避する一方で、ドーパント材料を選択的に分離構造体側壁及び底部領域の中に外方拡散させて、ピニングフォト・ダイオード120の最終的に形成された表面ピニング層が下にある基板150と確実に電気的に接觸するようにするステップを含む。このようなプロセスを用いて、図4に図示されたドープされた分離構造体101a、及び図5に図示されたドープされた分離構造体101bのような、ドープされた分離構造体を形成することができる。

## 【0030】

10

20

30

40

50

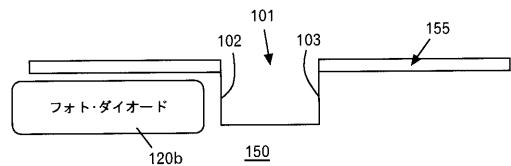

図4及び図5のピクセル・センサ・セル構造体100を形成するプロセスにおいて、例えばSi、SiGe、SiC、SiGeC、GaAs、InP、InAs、及び他の半導体か、或いはシリコン・オン・インシュレータ(SOI)、SiC・オン・インシュレータ(SiCOI)、又はシリコン・ゲルマニウム・オン・インシュレータ(SGOI)のような層状半導体を含むバルク半導体基板150に、最初に分離構造体101が形成される。説明のために、基板150は、例えばボロン又はインジウム(III-V半導体については、ベリリウム又はマグネシウム)などのp型ドーパント材料により、例えば $1 \times 10^{14} \text{ cm}^{-3}$ から $1 \times 10^{16} \text{ cm}^{-3}$ までの標準的な濃度範囲で軽度にドープされた、第1の導電型のSi含有半導体基板である。次いで、標準的なプロセス技術を用いて、側壁102、103を有する分離構造体101が基板150に形成される。即ち、フォトリソグラフィを利用して、犠牲窒化物マスク155(パッド-窒化物)が最初に適用され、パターン形成され、現像されて、分離構造体を形成するための開放領域101を露出する。その後、エッチング処理が実施されて、エッチング済み分離構造体101がもたらされる。図6に図示されたように、図5に示された部分的にドープされた分離構造体の実施形態のために、基板に形成されたエッチング済み分離構造体開口部101に隣接して、ピニングフォト・ダイオード120bが形成されるべき位置が示されている。

### 【0031】

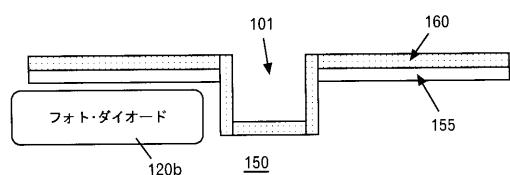

形成ピニングフォト・ダイオード120bの表面ピニング層が、下にある基板150と電気的に接触するようにする目的で、絶縁誘電体材料によりトレンチを充填することに先立ち、ドーパント材料が分離構造体の側壁内に外方拡散される。図7に図示されたように、分離構造体101の側壁及び底部に実質的に適合し、且つ、基板表面に形成された犠牲窒化物マスク155の上部に1つの層を形成する、ドーパント材料を含んだ層160が、このようにして堆積されて存在する。1つの実施形態においては、好ましい分離構造体側壁ドーパント材料は、ボロン又はインジウムといったp型ドーパントを有する、ドープされたガラス(例えばシリコン酸化物)薄膜を含むことができる。層160を構成する例示的なタイプの薄膜は、リンを含有するシリコン酸化物薄膜(PSG)を含むことができ、又は、本発明により外方拡散されるドーパント材料を与えるものとして、ボロンを含有するシリコン酸化物薄膜(例えばボロン-ケイ酸化ガラス即ちBSG)を用いることができる。ドープされたガラス薄膜の堆積は、周知の化学気相堆積法(CVD)技術によって実施することができる。半導体基板の上に薄膜を堆積するのに用いられてきた1つの技術は、低圧化学気相堆積法(LPCVD)である。層160の厚さを正確に制御することを可能にし、同様にして、層160のドーパント濃度を精密に制御するプロセスが実施されることが好ましい。こうした層160の濃度は、低濃度から高濃度の $1 \times 10^{18}$ 原子/ $\text{cm}^3$ までの範囲である。

### 【0032】

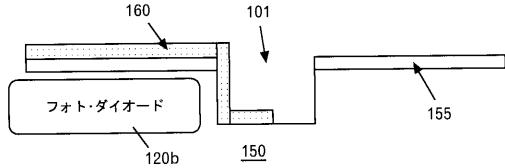

次のステップにおいて、図8に図示されたように、リソグラフィ・マスク(例えばパターン状に形成されたフォトレジスト層を含む)及び指向性即ち非等方性エッチング処理(例えば反応性イオン・エッチング)ステップが実施されて、分離構造体側壁をドープすることが望ましくない領域において、ドープされた材料層160を選択的に除去し、且つ、分離構造体側壁におけるドープが望ましい領域において、ドープされた材料層160のうちの選択部分を残す。次いで、図9に図示されたように、ドープされた層160の選択的に残存する部分を含む図8の構造体は、高温のアニールを十分に受けて、層160の中のドーパント材料を、下にあるシリコン形成外方拡散ドープされた分離構造体側壁105b及び分離構造体底部部分148に追いやる。構造体全体にわたって「キャッピング層」(例えばドープされていない酸化物)が形成され、ドープされた材料層160を閉じ込め、そのことにより、アニール・ステップの間に、ドーパントは、周辺の炉環境に拡散することを防止され、基板に拡散するようにされると理解される。パッド窒化物層155は、拡散障壁として作用する。アニール処理の温度及び時間は、例えばボロンなどのドーパント材料濃度が、選択された分離構造体側壁及び底部領域へ妥当に外方拡散することを保証して、フォト・ダイオード120bの形成された表面ピニング層の上部から下にある軽度に

ドープされた基板 150への導電性を保証するようなものであることが好ましい。例示として、アニール処理は、酸化N<sub>2</sub>環境（例えば約2%以下の酸素と約98%の窒素）において、1-2分間にわたって1120°Cを適用するものとすることができます。付加的に、炉アニールを用いることができる。窒素（SiO生成を避けるために酸素含有量のパーセンテージを下げる）環境においても、酸化環境においても、1000°C-1050°Cの範囲の条件が効果的である。所望の外方拡散の程度、及びこのプロセスと拡散の分離との統合によって、800°Cから1100°Cの炉内で10分-300分間という条件、又は900°Cから1200°Cまでの範囲の温度において約12分を下回る時間での急速アニール熱アニールが効果的であろう。ドープされた領域105b及び148の厚さ及びドーパント濃度は、アニール・ステップの温度及び持続時間によって、非常に精密に制御することが可能であると理解される。最後に、図10に図示されたように、周知の技術を用いて、ドープされた材料層160の残余の部分が除去（剥離）され、図5に示された、部分的にドープされた分離構造体が形成される。図4に示された、ドープされた分離構造体を形成するためには、ドープされた材料層160を選択的に除去するステップ（図8参照）がなくなり、図7に示されたように、ドープされた材料層160上に高温アニールが実施される。

#### 【0033】

ピクセル・センサ・セルフォト・ダイオードのピニング層及びコレクション・ウェルは、分離構造体側壁ドープ形成の前後どちらにおいても形成することができ、また、誘電酸化物（例えばSiO<sub>2</sub>）又は同様の絶縁体材料により分離構造体を充填する前に形成することもできると理解される。

#### 【0034】

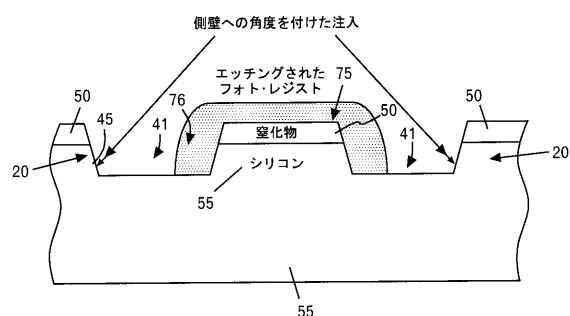

図6-図10に関してここで説明される技術を用いて、図3に図示された分離構造体101a、bの両方のための、選択的にドープされた分離構造体側壁を形成することができると更に理解される。加えて、代替的に、又は上記の方法論と組み合わせて、本出願人に譲渡された出願継続中の特許文献2のような、側壁及び底部部分におけるドーパント原子の角度をつけた注入と組み合わせてフォトマスクが適用されるという、分離構造体を選択的にドープするための方法を利用することができる。より具体的には、図11に図示されたように、基板表面の、後でピクセル・センサ・セル支持デバイスが形成される活性シリコン即ちデバイス領域55の上に形成されている犠牲窒化物マスク層50の上部において、初めは鋭い縁部（図示せず）を持った状態で形成されていたフォトトレジスト・マスク75が、パターン形成されエッチングされる。図11に図示されたように、表面ピニング層18と下にある基板15の間に最終的な電気コンタクトを形成するための適切なドーパント注入濃度を保証するためには、注入レジスト・マスク75の高さと間隔が重要であることが理解される。従って、例えば図11に図示されたような1つのやり方で、1つのエッチング処理が実施されて、フォトトレジスト層75のトポグラフィを調整し、角度をつけた注入を行うことが可能になるように、それを低減する。次いで角度をつけた注入60を実施して、分離構造体41の側壁45にドーパント材料を堆積する。p型ドープされた基板を想定すると、好ましい分離構造体側壁注入ドーパント材料は、ボロン又はインジウムのようなp型ドーパントを含む。

#### 【0035】

レジスト・ブロック・マスクを越えた側壁縁部への角度をつけた注入を容易にする目的で、1)イメージ形成されたフォトトレジストへのスペーサ型エッチングか、又は2)イメージ形成されたフォトトレジストへの角部スパッタ・プロセス、の2通りの方法が提示される。第1のエッチング技術によれば、スペーサ型エッチングは、イメージ形成された材料を引き下げ、同時に、垂直方向のエッチング成分及び水平方向のエッチング成分を持つことにより角部76が両方向から腐食されて、角部の縁が丸められるように実施される。例えば、純粹に物理的であってもよく（例えばスパッタ・エッチング）、又は化学成分を有してもよい（例えば反応性イオン・エッチング即ちRIE）、指向性プロセス又は非等方性プロセスを含むスペーサ型エッチングである。どちらの場合においても、エッチング処

理は、垂直方向エッチング成分を含んで、パターン状に形成されたフォトレジスト層をエッチングし、所望のレジスト層高さをもたらすように、且つ、S i 領域の底部及び上部における水平方向即ち横方向エッチング成分を含んで、図11に図示されたような丸められたプロファイル76を有するフォトレジスト・パターン構造体75をもたらすように選択される。

【0036】

フォトレジスト・マスク75をエッチングする代替的な方法は、パターン状に形成されたレジスト角部を面取りして同様な結果を達成するスパッタ・エッチング技術を提供することである。こうした代替的なプロセスにおいては、フォトレジスト層は、例えばR Fスパッタ・エッチングのような非ケミカル・スパッタ・エッチング処理によって形成されて、図11に見られる丸められたプロファイルをもたらし、分離構造体の側壁へ角度をついた注入ができるようになる。好ましいプロセスは、フォトレジスト層の水平方向部分及び垂直方向部分を除去することが好ましく、また丸められた角部プロファイルを与えることが好ましい。スパッタ・エッチングを用いて、角部におけるレジストの傾きを増加させ、例えば水平軸に対して角度60°又はそれ以下にすることができる。この角部の傾きは、本発明の目的を達成するための角度をつけた注入を可能にするのに十分な程度にされる。

10

【0037】

本発明の好ましい実施形態と見なされるものが図示され、説明されたが、当然ながら、本発明の精神を逸脱することなしに、形態又は詳細における種々の修正及び変更を容易に為し得ることが理解されるであろう。従って、本発明は、説明され図示された形態そのものに限定されることを意図されず、添付の特許請求の範囲内に入るような全ての修正を網羅するように構築されている。

20

【図面の簡単な説明】

【0038】

【図1】従来技術による、ピクセル・センサ・セルのアレイ100を含む例示的な現在のピクセル・センサの一部を示す。

【図2】図1の線A-Aに沿って見た断面を通じて、ピニングフォト・ダイオード20を含む1つのピクセル・センサ・セル110を示す。

【図3】本発明による、選択的にドープされた側壁を有する分離構造体101a、bによって離間されたピクセル・センサ・セルのアレイ100を含む例示的な現在のイメージ・センサの一部を示す。

30

【図4】図3の線B-Bに沿って見た断面を通じて、本発明により形成され、ピクセル・センサ・セル110a及び110bを離間する、ドープされた分離構造体101aを示す。

【図5】図3の線C-Cに沿って見た断面を通じて、本発明により形成され、ピクセル・センサ・セル110b及び110dを離間する、部分的にドープされた分離構造体101bを示す。

【図6】本発明による分離構造体のドープされた側壁部分を選択的に形成するための例示的なプロセスを断面図で示す。

【図7】本発明による分離構造体のドープされた側壁部分を選択的に形成するための例示的なプロセスを断面図で示す。

40

【図8】本発明による分離構造体のドープされた側壁部分を選択的に形成するための例示的なプロセスを断面図で示す。

【図9】本発明による分離構造体のドープされた側壁部分を選択的に形成するための例示的なプロセスを断面図で示す。

【図10】本発明による分離構造体のドープされた側壁部分を選択的に形成するための例示的なプロセスを断面図で示す。

【図11】分離構造体の側壁内に所望の角度をつけた注入ができるようにパターン形成され、エッチングされた、結果として得られるフォトレジスト層構造体75を断面図で示す。

50

## 【符号の説明】

## 【0039】

- 101: 分離構造体

105: 側壁

110: ピクセル・センサ・セル

115: 側壁

120: フォト・ダイオード領域

148: 底部領域の一部

150: 基板

155: 犠牲窒化物マスク

160: ドープされた材料層

10

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 ジェイムズ・ダブリュー・アドキッソン

アメリカ合衆国 05465 バーモント州 エリコ フィールズ・レーン 55

(72)発明者 マーク・ディー・ジャッフェ

アメリカ合衆国 05482 バーモント州 シエルバーン ガバナーズ・レーン 447

(72)発明者 ロバート・ケイ・ライディ

アメリカ合衆国 05401 バーモント州 バーリントン タワー・テラス 11

審査官 柴山 将隆

(56)参考文献 特開2003-188367(JP, A)

特開2003-258229(JP, A)

特開2006-024907(JP, A)

特開2005-317639(JP, A)

特開昭62-219943(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H01L 21/76