(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5555685号

(P5555685)

(45) 発行日 平成26年7月23日(2014.7.23)

(24) 登録日 平成26年6月6日(2014.6.6)

(51) Int.Cl.

F 1

**H01L 27/105 (2006.01)**

**H01L 21/8246 (2006.01)**

**H01L 29/82 (2006.01)**

**H01L 43/08 (2006.01)**

H01L 27/10 447

H01L 29/82 Z

H01L 43/08 Z

請求項の数 15 (全 11 頁)

(21) 出願番号 特願2011-275641 (P2011-275641)

(22) 出願日 平成23年12月16日 (2011.12.16)

(65) 公開番号 特開2012-134495 (P2012-134495A)

(43) 公開日 平成24年7月12日 (2012.7.12)

審査請求日 平成24年7月31日 (2012.7.31)

(31) 優先権主張番号 12/973,536

(32) 優先日 平成22年12月20日 (2010.12.20)

(33) 優先権主張国 米国(US)

(73) 特許権者 500373758

シーゲイト テクノロジー エルエルシー

アメリカ合衆国、95014 カリフォルニア州、クパチーノ、サウス・ディ・アンザ・ブールバード、10200

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 シー・ハイウェン

アメリカ合衆国、95120 カリフォルニア州、サン・ノゼ、チコリ・コート、1111

(72) 発明者 アントワン・コウエアー

アメリカ合衆国、55124 ミネソタ州、アップル・バレー、ドウェラーズ・ウェイ、15578

最終頁に続く

(54) 【発明の名称】磁気スタックおよびメモリセル、ならびにセルを製造する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

磁気スタックであって、下から順番に積層される、下部電極と、合成反強磁性層(SAF)と、磁気トンネル接合と、磁気自由層と、上部電極とを備え、前記磁気トンネル接合、前記磁気自由層および前記上部電極の横方向に配置されて、前記磁気トンネル接合を超えて横方向に伸延する前記SAFのピニング領域との接触を通じて、前記SAFの磁化を固定する反強磁性層(AFM)と、前記磁気自由層および前記上部電極から、前記反強磁性層(AFM)を物理的かつ磁気的に分離するための非磁気スペーサ層とを備えた磁気スタック。

10

## 【請求項 2】

トンネル磁気抵抗効果は、昇温および面内磁場の存在下における焼鈍を通して増加される、請求項1に記載の磁気スタック。

## 【請求項 3】

前記ピニング領域は、焼鈍中に、揮発性AFM原子の拡散を抑制する、請求項1に記載の磁気スタック。

## 【請求項 4】

前記磁気自由層は、第1の幅を有し、

前記磁気トンネル接合は、第2の幅を有し、

前記SAFは、第3の幅を有し、

20

前記ピニング領域は、前記第2の幅と前記第3の幅との差によって定められる、請求項1に記載の磁気スタック。

**【請求項5】**

前記ピニング領域は、前記磁気自由層の横方向の両側に配置される、請求項1に記載の磁気スタック。

**【請求項6】**

磁気スタックであって、

下から順番に積層される、下部電極と、单一の強磁性層と、磁気トンネル接合と、磁気自由層と、上部電極とを備え、

前記磁気トンネル接合、前記磁気自由層および前記上部電極の横方向に配置されて、前記磁気トンネル接合を超えて横方向に伸延する前記单一の強磁性層のピニング領域との接触を通じて、前記单一の強磁性層の磁化を固定する反強磁性層(AFM)と、 10

前記磁気自由層および前記上部電極から、前記反強磁性層(AFM)を物理的かつ磁気的に分離するための非磁気スペーサ層とを備えた磁気スタック。

**【請求項7】**

前記AFMは、マンガン化合物である、請求項1に記載の磁気スタック。

**【請求項8】**

前記マンガン化合物は、IrMnである、請求項7に記載の磁気スタック。

**【請求項9】**

前記磁気スタックは不揮発性であり、スピン偏極電流を用いて前記磁気自由層に論理状態がプログラムされる、請求項1に記載の磁気スタック。 20

**【請求項10】**

下から順番に積層される、下部電極と、合成反強磁性層(SAF)と、磁気トンネル接合と、磁気自由層と、上部電極とを提供するステップと、

前記磁気トンネル接合、前記磁気自由層および前記上部電極の横方向に反強磁性層(AFM)を提供するステップと、

前記磁気自由層および前記上部電極から、前記反強磁性層(AFM)を物理的かつ磁気的に分離するための非磁気スペーサ層を提供するステップと、

前記AFMを用いて、前記磁気トンネル接合を超えて横方向に伸延する前記SAFのピニング領域との接触を通じて、前記SAFの磁化を固定するステップとを備える、方法。 30

**【請求項11】**

前記AFMは、交換バイアス場を用いて前記SAFを固定する、請求項10に記載の方法。

**【請求項12】**

前記SAFは、前記磁気自由層の幅の少なくとも2倍の長さの幅を有する、請求項10に記載の方法。

**【請求項13】**

前記ピニング領域は、前記磁気トンネル接合の側面部を除去することによって形成される、請求項10に記載の方法。

**【請求項14】**

メモリセルであって、

下から順番に積層される、下部電極と、合成反強磁性層(SAF)と、磁気トンネル接合と、磁気自由層と、上部電極とを備え、前記磁気自由層は、第1の幅を有し、前記磁気トンネル接合は、前記第1の幅よりも大きい第2の幅を有し、前記合成反強磁性層(SAF)は、少なくとも前記第1の幅の2倍である第3の幅を有し、

前記磁気トンネル接合、前記磁気自由層および前記上部電極の横方向に配置されて、前記磁気トンネル接合を超えて横方向に伸延する前記SAFのピニング領域との接触を通じて、前記SAFの磁化を固定する反強磁性層(AFM)と、

前記磁気自由層および前記上部電極から、前記反強磁性層(AFM)を物理的かつ磁気的に分離するための非磁気スペーサ層とを備え、 50

前記ピニング領域は、昇温および面内磁場の存在下における焼鈍中に、A F M原子の拡散を抑制する、メモリセル。

**【請求項 15】**

前記A F M原子の拡散の抑制は、前記S A Fの磁気安定性を増加し、

前記焼鈍は、前記メモリセルについてのトンネル磁気抵抗を増加する、請求項14に記載のメモリセル。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

**要約**

本発明のさまざまな実施形態は、概して、横方向磁気ピニング層を用いて構成される不揮発性メモリセルに向けられる。

10

**【発明の概要】**

**【課題を解決するための手段】**

**【0002】**

さまざまな実施形態に従えば、磁気自由層は、非磁気スペーサ層によって反強磁性層(A F M)から横方向に分離されるとともに、磁気トンネル接合によって合成反強磁性層(S A F)から内側に分離される。A F Mは、磁気トンネル接合を超えて横方向に伸延するS A Fのピニング領域との接触を通じてS A Fの磁化を固定する。

**【0003】**

20

本発明のさまざまな実施形態を特徴付けるこれらおよび他の多くの特徴および利点は、以下の詳細な議論および添付の図面に照らして理解することができる。

**【図面の簡単な説明】**

**【0004】**

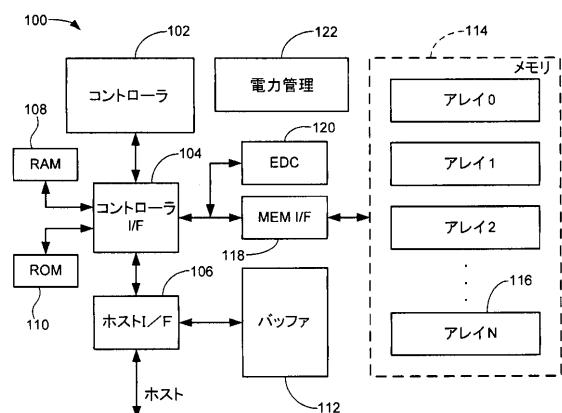

**【図1】**本発明のさまざまな実施形態に従って構築されかつ動作される、例示的なデータ記憶装置の概略機能ブロック図である。

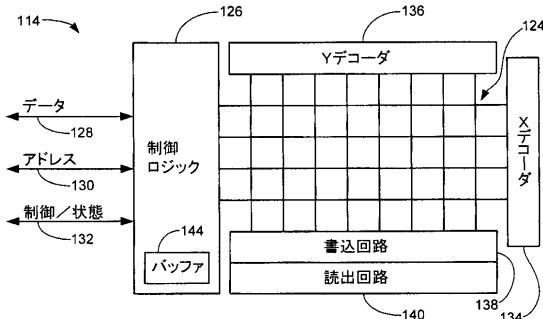

**【図2】**図1の装置のメモリアレイからデータを読み出し、かつデータを書込むために用いられる回路を示す図である。

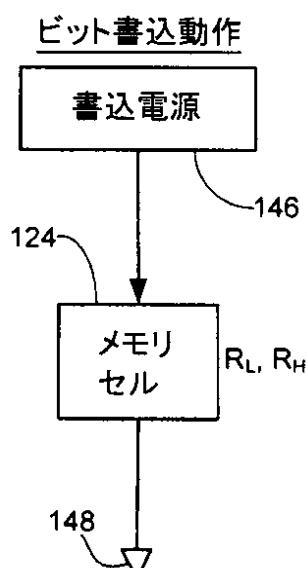

**【図3】**メモリアレイのメモリセルにデータが書き込まれる様子を概略的に示す図である。

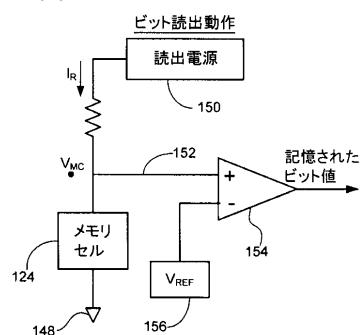

**【図4】**図3のメモリセルからデータが読み出される様子を概略的に示す図である。

30

**【図5】**本発明のさまざまな実施形態に従って構築されかつ動作される例示的なメモリセルを示す図である。

**【図6】**本発明のさまざまな実施形態に従って構築されかつ動作される例示的なメモリセルの等角図である。

**【図7】**メモリセルの例示的な代替構造を示す図である。

**【図8】**本発明のさまざまな実施形態に従って実行される、例示的な「セル製造」ルーチンのフロー図、および、対応する例示的な磁気スタックを示す図である。

**【発明を実施するための形態】**

**【0005】**

**詳細な説明**

40

本開示は、概して、スピントルクランダムアクセスメモリ(S T R A M)セルのような、不揮発性メモリセルに関する。ソリッドステート不揮発性メモリは、フォームファクタを低減しつつ、信頼性のあるデータ記憶および高速データ転送を提供することを狙った、開発中の技術である。しかしながら、低い全体のデータ容量をもたらす大スイッチング電流、低動作マージン、および低面積密度のような、ソリッドステートセルに関連するいくつかの問題は、実際的な用途を抑制する。最近の試みにおいては、高揮発性は、セルのトンネル磁気抵抗(T M R)効果を低下させることによって、ソリッドステートセルをさらに苦しめ、それはセルの読み出可能性(readability)および書き込可能性(writeability)を低減させる。

**【0006】**

50

したがって、磁気自由層に横方向に配置された反強磁性層（A F M）によって磁気的に固定される合成反強磁性（S A F）層を有するソリッドステート不揮発性メモリセルは、読み出可能性および書き込み可能性を強化しながら、揮発性を低減する。A F Mの自由層への横方向の配向は、A F Mからの揮発性原子拡散を通して揮発性を同時に増加することなく、セルのT M Rを増加するための高温焼鈍を可能にする。このようなA F Mの横方向構造は、さまざまなデータ記憶装置における増加された記憶容量をもたらし得る、より小さい全体セル厚さも提供する。

#### 【0007】

図1は、本発明のさまざまな実施形態に従って構築されかつ動作されるデータ記憶装置の概略機能ブロック図を提供する。データ記憶装置は、P C M C I AカードおよびU S B型外部メモリセル装置のような携帯型不揮発性メモリ記憶装置を含むものとして考えられる。しかしながら、装置100のそのような特性は、単に特定の実施形態を示すことを目的としているのであって、主張される課題を限定するものではないことが理解されるであろう。

10

#### 【0008】

装置100の上位制御は、適切なコントローラ102で実行され、それはプログラム可能であってもよいし、またはハードウェアベースのマイクロコントローラであってもよい。コントローラ102は、コントローラインターフェース（I / F）回路104およびホストI / F回路106を介して、ホスト装置と通信する。必要な指令、プログラミング、操作データなどの局部記憶は、ランダムアクセスメモリ（R A M）108および読み取り専用メモリ（R O M）110を介して提供される。バッファ112は、ホスト装置からの入力書き込みデータおよびホスト装置への転送を保留中のリードバックデータを一時的に記憶するように機能する。

20

#### 【0009】

（アレイ0～Nで示される）多くのメモリアレイ116を含むメモリ空間が114に示されるが、必要に応じて、単一のアレイが利用され得ることが理解されるであろう。各アレイ116は、選択された記憶容量の半導体メモリのブロックを含む。コントローラ102とメモリ空間114との間の通信は、メモリ（M E M）I / F118を介して適合される。必要に応じて、オンザフライエラー検出および訂正（E D C）エンコーディング動作およびデコード動作が、データ転送中にE D Cブロック120によって実行される。

30

#### 【0010】

限定しないが、いくつかの実施形態においては、図1に示されるさまざまな回路は、適切な容器、筐体、および相互接続フィーチャ（明確化のために、個別には図示せず）を有する1つまたはより多くの半導体ダイ上に形成される、シングルチップセットとして配列される。装置を動作させる入力電力は、適切な電力管理回路122によって処理され、バッテリ、A C電源入力などのような適当なソースから供給される。電力は、たとえばU S B型インターフェースなどの使用を通して、ホストから装置100へ直接供給されてもよい。

40

#### 【0011】

論理ブロックアドレッシング（L B A）のような、多くのデータ記憶プロトコルおよびデータ転送プロトコルを利用することができます、それによって、データは、（512バイトのユーザデータに加えて、E C C、スペアリング、ヘッダ情報などについてのオーバヘッドバイトのような）固定サイズのブロックに配置されかつ記憶される。ホスト指令は、L B Aごとに発行され、装置100は、対応するL B A - P B A（物理ブロックアドレス）変換を実行して、データが記憶されるべき、または抽出されるべき関連した場所を識別しかつ提供する。

40

#### 【0012】

図2は、図1のメモリ空間114の選択された局面の概略図を提供する。データは、さまざまな行（ワード）ラインおよび列（ビット）ラインによってアクセス可能な、メモリ

50

セル 124 の行および列の配列として記憶される。セルの実際の構造およびそれ上のアクセスラインは、所与の用途の要件に依存する。しかしながら、一般的に、さまざまな制御ラインが、個々のセルの値のそれぞれの書き込みおよび読み出しを、選択的に可能および不可能にするイネーブルラインを一般的に含むことが理解されるであろう。

#### 【0013】

制御ロジック 126 は、マルチラインバス経路 129, 130, 132 に沿って、データ、アドレッシング情報、および制御 / 状態値をそれぞれ受信しあつ転送する。X デコーダ回路 134 および Y デコーダ回路 136 は、適切なセル 124 にアクセスするための、適切な切換えおよび他の機能を提供する。書き回路 138 は、セル 124 へデータを書き込むための書き動作を実行するように動作する要素を表わし、読み回路 140 は、セル 124 からのリードバックデータを取得するように対応して動作する。転送されたデータおよび他の値の局部バッファリングは、1 つまたはより多くの局部レジスタ 144 を介して提供される。この時点において、図 2 の回路は、実際には単に例に過ぎず、多くの代替的な構造が、必要に応じ、所与の用途の要件に応じて容易に採用され得ることが理解されるであろう。10

#### 【0014】

データは、図 3 に概略的に示されるように、個別のメモリセル 124 へ書き込まれる。一般的に、書き電源 146 は、(電流、電圧、磁化などの形態の) 必要な入力を印加して、メモリセル 124 を所望の状態に構成する。図 3 は、ビット書き動作の代表的な図に過ぎないことが理解され得る。書き電源 146、メモリセル 124、および基準ノード 148 の構成は、適切に操作されて、各セルへの選択された論理状態の書き込みを可能とする。20

#### 【0015】

以下に説明されるように、いくつかの実施形態においては、メモリセル 124 は、修正された S T R A M 構造を採用し、その場合においては、書き電源 146 は、メモリセル 124 を通って、接地のような適当な基準ノード 148 へ接続される電流ドライバとして特徴付けられる。書き電源 146 は、メモリセル 124 内の磁気材料を通して動かされることによってスピンドル偏極される電力の流れを提供する。結果として得られる偏極されたスピンドルの回転は、メモリセル 124 の磁気モーメントを変化させるトルクを生成する。

#### 【0016】

磁気モーメントに応じて、セル 124 は、相対的に低い抵抗 ( $R_L$ ) または相対的に高い抵抗 ( $R_H$ ) のいずれかをとり得る。限定しないが、例示的な  $R_L$  の値は、約 100 オーム ( ) くらいの範囲内であり、一方、例示的な  $R_H$  の値は、約 100 K くらいの範囲であり得る。これらの値は、後続の書き動作によって状態が変化されるときまで、個別のセルによって維持される。限定しないが、本実施例においては、高抵抗値 ( $R_H$ ) はセル 124 によって論理 1 の記憶を示し、低抵抗値 ( $R_L$ ) は論理 0 の記憶を示すことが企図される。30

#### 【0017】

各セル 124 に記憶された論理ビット値は、図 4 によって示されるような様式で決定することができる。読み出力 150 が、適切な入力 (たとえば、選択された読み出力電圧) をメモリセル 124 に印加する。セル 124 を流れる読み出力電流  $I_R$  の量は、セルの抵抗 ( $R_L$  または  $R_H$  のそれぞれ) の関数である。メモリセルにわたる電圧降下 (電圧  $V_{MC}$ ) が、経路 152 を介して、比較器 (センスアンプ) 154 の正側 (+) 入力によって検出される。(電圧基準  $V_{REF}$  のような) 適当な基準が、基準源 156 から比較器 154 の負側 (-) 入力へ供給される。40

#### 【0018】

メモリセル 124 にわたる電圧降下  $V_{MC}$  が、セルの抵抗が  $R_L$  に設定されると  $V_{REF}$  値より低くなり、セルの抵抗が  $R_H$  に設定されると電圧降下  $V_{MC}$  が  $V_{REF}$  値より高くなるように、電圧基準  $V_{REF}$  がさまざまな実施形態から選択され得る。このように、比較器 154 の出力電圧レベルは、メモリセル 124 によって記憶された論理ビット値 (0 または 1) を示す。50

## 【0019】

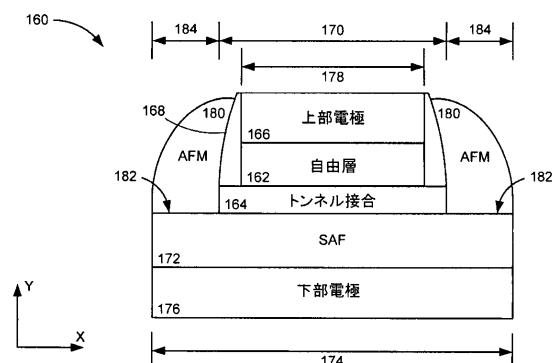

図5は、本発明のさまざまな実施形態に従う不揮発性メモリスタック160を概略的に示す。スタック160は、トンネル接合164、上部電極166、および非磁気スペーサ層168のそれぞれの間に配置された磁気自由層162を有する。トンネル接合164は、幅170で配向され、接触的に隣接する下部電極176によって共有される幅174を有する合成反強磁性(SAF)層172の内側部に取付けられる。

## 【0020】

図示されるように、上部電極166および自由層162の各々は、トンネル接合の幅170より短い幅178を有する。このような幅の差は、X軸に沿って測定されるような、横方向に隣接する反強磁性層(AFM)180から自由層162を分離するスペーサ層168を収容する。AFM180は、トンネル接合幅170とSAF幅174との間の幅の差184によって定められるSAF172のピニング領域182との接触を通してSAF172の磁化を固定する磁気交換バイアスを提供する。ピニング領域182のそのような横方向の配置は、AFM層180が、Y軸に沿って測定されるように、スタック160にいかなる厚みも追加することなく、自由層162の両横側に配置されることを可能にする。

## 【0021】

動作中、自由層162は、正極または負極のような層162における磁化方向を設定する予め定められたプログラミング電流に磁気的に応答する。このような磁化方向は、磁気的に非応答のSAF層172と関連して、スタック160へ記憶されるべき(0または1のような)論理状態を提供するTMR効果を生成するように機能する。トンネル接合164によって、引き続いて、SAF172および自由層162の磁化方向が、プログラムされた論理状態として読み出すことができるTMR効果を生成するように相互作用する。

## 【0022】

スタック160の機能は、TMR効果を増加することによって強化することができ、それは、プログラムされた論理状態と、自由層162の磁化方向を設定および切換えるために必要なより低いプログラミング電流との間における、より大きな磁化の差に対応する。TMR効果は、焼鈍を通じて上昇された温度にさらされることによって増加するし得る。しかしながら、そのような焼鈍はAFM180の原子反強磁性移動(migration)を通して、SAF172および自由層162の磁化の揮発性を増加することによってスタック160に悪影響を及ぼし得る。

## 【0023】

図5のメモリスタック160では、焼鈍は、SAF172および自由層162に対するAFM180の横方向の配置のために、揮発性を増加させることなく生じ得る。つまり、非磁気スペーサ層168によるAFM180と自由層162との分離は、AFM180の横方向取り付けをピニング領域182に沿ってSAF172に結合し、SAF172および自由層162への揮発性AFM原子の移動を低減する。結果として、スタック160は、低磁気揮発性を併用した焼鈍によって、強化されたTMR効果を通して、より大きな読出可能性および書き込み可能性を有し得る。

## 【0024】

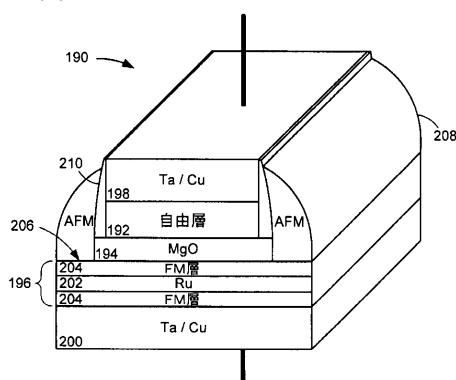

図6は、さまざまな実施形態にしたがって構築された例示的な不揮発性メモリセルの等角図を示す。磁気自由層192が、MgOのトンネル接合194に取付けられ、それは、有利にも、自由層192をSAF3層196により近接させる、低減された厚さを有するTMRを生成することに寄与し得る。自由層192およびSAF3層196の各々は、上部電極198および下部電極200にそれぞれ取付けられ、それらの電極は、限定されないが、TaおよびCuのような、セラ190に電流を伝達することができる、さまざまな電流導通材料であり得る。

## 【0025】

SAF3層196は、示されているように、一対の強磁性層204の間に配置された、Ruのような結合スペーサ層202を有し、それは、NiおよびCoのような金属、Co

10

20

30

40

50

F e および N i F e のような合金、および C o F e B のような高偏極比化合物には限定されない、さまざまな材料であり得る。このような強磁性層 204 は、A F M 208 からの S A F 196 のピニング領域 206 に沿って与えられる交換バイアスに磁気的に応答し、それは、P t M n および I r M n のような、任意の反強磁性的に順序付けられた材料であり得る。

#### 【0026】

しかしながら、マンガンは特に揮発性であり、焼鈍時に原子がセルを通して容易に拡散することが観測された。したがって、A F M 208 からの拡散は、A F M 208 への S A F 196 の制限された取り付けによって抑制される。言い換えれば、ピニング領域 206 の制限された表面積は、マンガン原子がセル 190 を通して拡散すること、および磁気揮発性を増加することを抑制する。拡散は、自由層 192 および上部電極 198 から A F M 208 を物理的および磁気的に分離する非磁気スペーサ層 210 によって、さらに抑制される。10

#### 【0027】

このように、セル 190 は、M n 原子の最小移動を有する T M R 強化焼鈍、および S A F 196 の磁化を固定する交換バイアスを生成する A F M 208 の能力の維持を受ける。読出電流または書き電流がセル 190 を通して伝達されると、薄い M g O トンネル接合 194、横方向 A F M 208 配向、および焼鈍の結合は、より薄いセルにおける高められた T M R 効果を可能とし、それは、データ記憶装置において、論理状態間のより高いマージン、より低いプログラミング電流、および増加された面積密度をもたらす。20

#### 【0028】

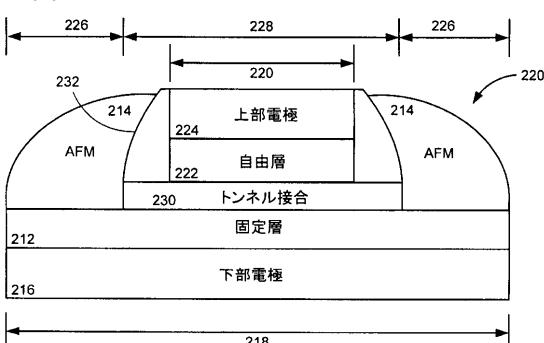

図 7 には、図 6 の S A F の位置に単一の強磁性固定層 212 を有する他の例示的なセル 210 が示される。図 6 のセル 190 の動作と同様に、セル 210 は、横方向に堆積された A F M 層 214 を有する強磁性固定層 212 の磁化を固定する。単一の強磁性固定層 212 の使用によって、セル 210 について、焼鈍中の揮発性原子の拡散を抑止し、かつ増加された T M R 効果を通して読出可能性および書き可能性を強化しながら、セル 190 に対して低減された厚みを有するようにできる。

#### 【0029】

セル 210 は、単に例示に過ぎず、図 7 に示される構成には限定されない。実際に、必要に応じて、セル 210 のサイズ、形状、材料、および動作についてのさまざまな修正が意図され得る。図示されるように、1つのこのような修正は、自由層 222 および上部電極 224 の幅 220 の2倍と等しいまたはより大きい幅 218 への、固定層 212 および下部電極 216 の拡張であり得る。このような構成は、相対的に大きなピニング領域 226 を与え、それは結果として、A F M 層 214 と固定層 212 との間の表面積およびピニング接続を増加する。30

#### 【0030】

さらに、トンネル接合 230 の幅 228 は、A F M 214 と自由層 222 との間の、N i O のような非磁気スペーサ材料 232 の増加された量を提供して、自由層 222 の磁気自由度を保護するように修正され得る。さらに他の修正においては、A F M 214 が除去されるとともに、固定層 212 が、予め定められた磁化方向を個々に維持する非対称 S A F に置き換えられ得る。セル 210 についてのさまざまな修正は、構造および動作を変化させるが、固定層 212 に対する A F M 214 の横方向配向および接続は、焼鈍中の揮発性原子拡散の抑制剤 (inhibitor) を維持し、それは、増加された T M R および改善されたセル 210 機能を可能とする。40

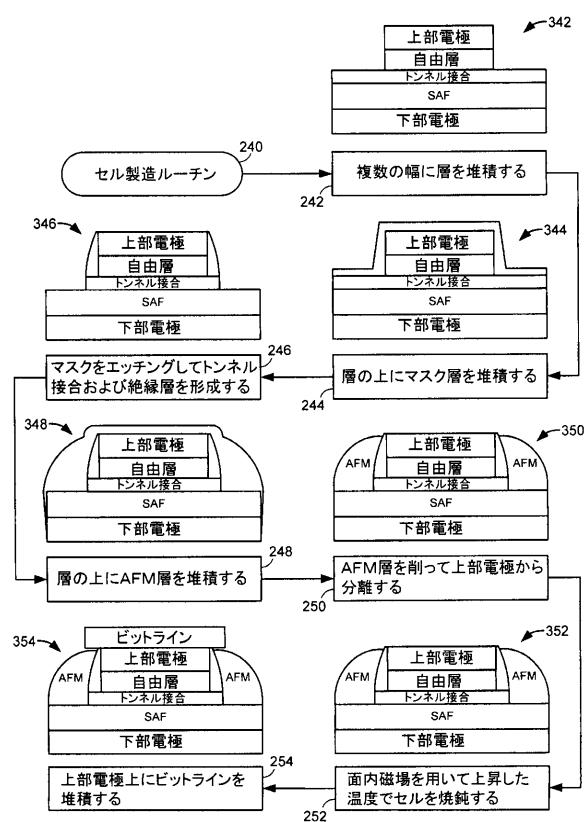

#### 【0031】

本発明のさまざまな実施形態に従う例示的なメモリセルを形成するセル製造ルーチン 240 および対応する図示的表現が、図 8 に概略的に示される。まず、ステップ 242 にて、予め定められた数の層が、少なくとも 2 つの幅で堆積される。さまざまな層の順序、数および厚さは限定されないが、磁気積層 (スタック) 342 は、ステップ 242 からもたらされる例を示しており、それにおいて、下部電極、S A F およびトンネル接合は第 1 の50

幅を有し、一方、自由層および上部電極はより小さい第2の幅を共有する。

#### 【0032】

そして、ステップ244は、前に堆積された層の上にマスク層を堆積し、上部を包み込む。スタック344は、いくつかの実施形態においては、NiOのような絶縁材料である、そのようなマスク層の例を視覚的に提供する。堆積されたマスク層およびトンネル接合は、その後、スタック346に示されるように、自由層について選択された量のマスク層が維持されるような予め定められたパターンで除去される。スタック346は、自由層およびSAFの横側のピニング領域を定めるためにトンネル接合が除去されることも、さらに示している。

#### 【0033】

ステップ248にて、AFM材料が、前で定められたピニング領域上にSAFが少なくとも接触するように、既存の磁気スタック上に堆積される。AFM層の形状および材料は限定されないが、サンプル構成がスタック348によって与えられ、それは、AFM材料がSAFの上面および側面を包み込むことを示している。ルーチン240が進められ、ステップ250にて、AFM材料の一部が、AFMを上部電極から分離する予め定められたパターンで除去される。ステップ250は、AFM材料を除去するための切削動作のために呼び出されるが、スタック350と同様のスタックを製造するために研磨およびエッティングのようなさまざまな処理を用いることができる、このような動作は必要とされずまたは限定されない。

#### 【0034】

形成および成形されたセルのさまざまな要素の層を用いて、ステップ252は、上昇された温度および面内磁場の存在下で、その構造の焼鈍を行なう。上述のように、AFM材料の横配置は、焼鈍中にSAFへの揮発性反強磁性原子の最小拡散を可能とする。スタック352は、焼鈍がセルの以前の構造を維持していることは示すが、焼鈍が、自由層、SAF、およびトンネル接合の間ににおける相互作用のTMR効果を強化することは図示できない。最後に、ステップ254にて、ビットラインが上部電極上に堆積され、セルへの読出電流および書き込み電流を導く導電経路を提供する。ステップ254は、ビットライン材料の堆積または成長のために、上部電極の上表面を準備する複数のサブステップを有し得る。スタック354は、特定の磁化方向にプログラムすることができるとともに、再プログラミングされるまでその方向を維持することができる、ステップ254からの完成したセルを概略的に図示する。

#### 【0035】

製造ルーチン240は、図8に示されたステップ、および対応する例示的な磁気スタックには限定されないことに注意すべきである。必要に応じて、さまざまなステップが、修正または省略でき、一方、新しいステップを追加することができる。例として、ステップ242は、スタック342に示されるSAFに代えて単一の強磁性層の堆積を含むように修正されてもよい。また、ステップ252および対応するスタック352が、データを記憶するためのアレイ内に実装されることが可能な完成したセルであるので、ステップ254は省略してもよい。

#### 【0036】

当業者によって理解されるように、本明細書に示されたさまざまな実施形態は、メモリセル効率および複雑性の双方においての利点を提供する。焼鈍を通してメモリセルのTMR効果を強化する能力は、結果として、動作マージンを増加しながら、より低いプログラミング電流を必要とする。さらに、AFM層の横方向配置は、焼鈍中のAFM原子拡散に関連する磁気揮発性によるエラーの数が低減された、より薄いメモリ装置構造を可能とする。しかしながら、本明細書で言及されたさまざまな実施形態は、多くの潜在的な用途を有し、電子媒体またはデータ記憶装置のタイプの特定の分野に限定されないことが理解されるであろう。

#### 【0037】

本発明のさまざまな実施形態の多くの特徴および利点が、本発明のさまざまな実施形態

10

20

30

40

50

の構造および機能の詳細とともに上記の説明に記載されるけれども、この詳細な説明はほんの例示的なものに過ぎず、詳細において、特に本発明の原理の範囲内で部品の構造および配列の点において、添付の特許請求の範囲に表現された語句の広く一般的な意味によって示される全範囲までの変更がなされても良いことが理解されるべきである。

## 【符号の説明】

[ 0 0 3 8 ]

100 装置、102 コントローラ、104 制御I/F回路、106 ホストI/F回路、112 バッファ、114 メモリ空間、116 メモリアレイ、118 ME M I/F、120 EDCブロック、122 電力管理回路、124, 190, 210 メモリセル、126 制御ロジック、129, 130, 132 マルチラインバス経路、134 Xデコーダ回路、136 Yデコーダ回路、138 書込回路、140 読出回路、144 局部レジスタ、146 書込電源、148 基準ノード、150 読出電源、152 経路、154 比較器、156 基準源、160, 342, 344, 346, 348, 350, 352, 354 メモリストック、162, 192, 222 自由層、164, 194, 230 トンネル接合、166, 198, 224 上部電極、168 スペーサ層、172 SAF層、176, 200, 216 下部電極、180, 214 AFM層、182, 206, 226 ピニング領域、196 SAF3層、202 結合スペーサ層、204 強磁性層、210 非磁気スペーサ層、212 固定層、232 非磁気スペーサ材料。

〔図1〕

【 四 2 】

〔 図 3 〕

【図4】

【図6】

【図5】

【図7】

【図8】

---

フロントページの続き

(72)発明者 ブライアン・リー

アメリカ合衆国、02881 マサチューセッツ州、ボストン、ワシントン・ストリート、131

3、ナンバー・705

(72)発明者 パトリック・ジェイ・ライアン

アメリカ合衆国、55116 ミネソタ州、セント・ポール、シェファー・アベニュー、1249

審査官 境 周一

(56)参考文献 特開2006-059869(JP,A)

特開2004-031605(JP,A)

特開2008-277621(JP,A)

特開2005-150303(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/10 - 27/118

H01L 29/82

G11C 11/00 - 11/16

H01L 43/00 - 43/14