(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5254031号

(P5254031)

(45) 発行日 平成25年8月7日(2013.8.7)

(24) 登録日 平成25年4月26日(2013.4.26)

(51) Int.Cl.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| GO6F 12/08 | (2006.01) | GO6F 12/08 | 501F |

| GO6F 13/38 | (2006.01) | GO6F 13/38 | 340C |

| GO6F 12/00 | (2006.01) | GO6F 12/00 | 597U |

|            |           | GO6F 12/00 | 560B |

|            |           | GO6F 12/08 | 541C |

請求項の数 16 (全 12 頁) 最終頁に続く

(21) 出願番号 特願2008-545888 (P2008-545888)

(86) (22) 出願日 平成18年12月18日 (2006.12.18)

(65) 公表番号 特表2009-520280 (P2009-520280A)

(43) 公表日 平成21年5月21日 (2009.5.21)

(86) 國際出願番号 PCT/US2006/048402

(87) 國際公開番号 WO2007/075668

(87) 國際公開日 平成19年7月5日 (2007.7.5)

審査請求日 平成21年12月18日 (2009.12.18)

(31) 優先権主張番号 11/303,382

(32) 優先日 平成17年12月16日 (2005.12.16)

(33) 優先権主張国 米国(US)

(73) 特許権者 500046438

マイクロソフト コーポレーション

アメリカ合衆国 ワシントン州 9805

2-6399 レッドmond ワン マイ

クロソフト ウェイ

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

(74) 代理人 100096013

弁理士 富田 博行

最終頁に続く

(54) 【発明の名称】メモリの書き込み及び損耗性能の最適化

## (57) 【特許請求の範囲】

## 【請求項 1】

データ記憶速度の階層を有する複数のデータ記憶装置が存在する場合に、データを効率的に記憶する方法であって、

低速データ記憶装置に記憶されるデータを受信するステップ、

高速データ記憶装置内に前記データを記憶するステップ、

特定の低速データ装置向けの好ましい量のデータが記憶されるまで、前記高速データ記憶装置に追加のデータを収集するステップ、

前記低速データ記憶装置をテストし、該低速データ記憶装置にとって好ましい書き込みサイズを求めるステップ、

前記データが前記好ましい書き込みサイズになるまで、前記高速データ記憶装置内に前記データを記憶するステップ、

前記記憶されたデータを、前記高速データ記憶装置よりは低速だが前記低速データ記憶装置よりは高速である追加のデータ記憶装置にバックアップするステップ、及び

前記好ましい書き込みサイズのデータが、前記高速データ記憶装置に記憶されると、前記低速データ記憶装置への書き込みを低システムアクティビティの期間まで待つステップを含む、方法。

## 【請求項 2】

請求項 1 に記載の方法であって、前記データがもはや高速データ記憶装置内で不要であるという判断が下されるまで、前記データを前記高速データ記憶装置内に保持するステッ

プをさらに含む、方法。

【請求項 3】

請求項 1 に記載の方法において、前記低速データ記憶装置は、フラッシュ記憶装置である、方法。

【請求項 4】

請求項 3 に記載の方法において、前記好ましい書き込みサイズは、前記フラッシュ記憶装置の消去ブロックサイズである、方法。

【請求項 5】

請求項 1 に記載の方法であって、前記データが前記低速データ記憶装置にまだ書き込まれなければならないことをユーザに対して警告を発し、前記低速データ記憶装置が取り外される前に前記データを前記高速データ記憶装置から前記低速データ記憶装置に書き込むオプションをユーザに提供するステップをさらに含む、方法。 10

【請求項 6】

請求項 1 に記載の方法であって、前記データが前記高速データ記憶装置から前記低速データ記憶装置へ書き込まれる前に、前記システムから前記低速データ記憶装置が取り外されるときに、前記データが前記低速データ記憶装置にまだ書き込まれなければならないことをユーザに警告するステップをさらに含む、方法。

【請求項 7】

請求項 6 に記載の方法において、前記低速データ記憶装置が取り外される前に、前記高速データ記憶装置から前記低速データ記憶装置へ前記データを書き込むオプションが前記ユーザに提供される、方法。 20

【請求項 8】

請求項 1 に記載の方法であって、前記高速データ記憶装置内の前記データを、前記低速データ記憶装置への前記書き込みがより効率的になるように編成するステップをさらに含む、方法。

【請求項 9】

請求項 1 に記載の方法であって、前記高速データ記憶装置内の前記データを分析し、該データが前記低速データ記憶装置に書き込まれる前に前記データのうちのいずれが新しいデータに置き換えられているか否かを判断するステップをさらに含む、方法。

【請求項 10】

請求項 1 に記載の方法であって、前記高速データ記憶装置内の前記データを分析し、前記低速データ記憶装置に書き込まれる前記データのうちのいずれが重複データであるか否かを判断し、古い方の重複データが前記低速データ記憶装置に書き込まれないようにするステップをさらに含む、請求項 1 に記載の方法。 30

【請求項 11】

請求項 1 に記載の方法であって、前記高速データ記憶装置内のブロックが前記低速データ記憶装置に引き渡される前に書き込み動作がそれらの前記ブロックに影響を与えるとき、該ブロックを無効化するステップをさらに含む、方法。

【請求項 12】

請求項 1 に記載の方法であって、前記低速データ記憶装置に書き込まれるデータのインデックスを前記高速データ記憶装置内に保持するステップ、及び前記低速データ記憶装置に書き込まれることになっている書き込まれる前記データが前記高速データ記憶装置に常駐している場合、前記データが前記低速データ記憶装置に書き込まれているか否かを問わず、前記高速データ記憶装置から、前記データに対する読み取り要求を満足させるステップをさらに含む、方法。 40

【請求項 13】

請求項 1 に記載の方法であって、前記低速データ記憶装置の好ましい消去サイズに関連する好ましい書き込みサイズを計算するステップをさらに含む、方法。

【請求項 14】

データ記憶速度の階層を有する複数のデータ記憶装置が存在する場合に、データを効率

50

的に記憶するためのコンピュータ実行可能命令を有するコンピュータ可読媒体であって、前記コンピュータ命令は、

低速データ記憶装置に記憶されるデータを受信する動作、

高速データ記憶装置内に前記データを記憶する動作、

特定の低速データ記憶装置向けの好ましい量のデータが記憶されるまで、前記高速データ記憶装置に追加のデータを集める動作、

前記低速データ記憶装置をテストし、該低速データ記憶装置にとって好ましい書き込みサイズを求める動作、

前記データが前記好ましい書き込みサイズになるまで、前記高速データ記憶装置内に前記データを記憶する動作、

前記記憶されたデータを、前記高速データ記憶装置よりは低速だが前記低速データ記憶装置よりは高速である追加のデータ記憶装置にバックアップする動作、及び

前記好ましい書き込みサイズのデータが前記高速データ記憶装置に記憶されると、前記低速データ記憶装置への書き込みを低システムアクティビティの期間まで待つ動作を含む、コンピュータ可読媒体。

#### 【請求項 15】

プロセッサと、入出力装置と、データ記憶装置とを備えるコンピュータシステムであって、前記プロセッサはコンピュータ実行可能命令を実行し、前記データ記憶装置はコンピュータ実行可能命令を記憶し、前記コンピュータ実行可能命令は、データ記憶速度の階層を有する複数のデータ記憶装置が存在する場合にデータを効率的に記憶するためのものであり、前記コンピュータ命令は、

低速データ記憶装置に記憶されるデータを受信する動作、

高速データ記憶装置内に前記データを記憶する動作、

特定の低速データ記憶装置向けの好ましい量のデータが記憶されるまで、前記高速データ記憶装置に追加のデータを集める動作、

前記低速データ記憶装置をテストし、該低速データ記憶装置にとって好ましい書き込みサイズを求める動作、

前記データが前記好ましい書き込みサイズになるまで、前記高速データ記憶装置内に前記データを記憶する動作、

前記記憶されたデータを、前記高速データ記憶装置よりは低速だが前記低速データ記憶装置よりは高速である追加のデータ記憶装置にバックアップする動作、及び

前記好ましい書き込みサイズのデータが前記高速データ記憶装置に記憶されると、前記低速データ記憶装置への書き込みを低システムアクティビティの期間まで待つ動作を含む、コンピュータシステム。

#### 【請求項 16】

請求項15に記載のコンピュータシステムであって、前記コンピュータ実行可能命令は、前記低速データ記憶装置に書き込まれるデータのインデックスを前記高速データ記憶装置内に保持する動作、及び前記低速データ記憶装置に書き込まれることになっている書き込まれる前記データが前記高速データ記憶装置に常駐している場合、前記データが前記低速データ記憶装置に書き込まれているか否かを問わず、前記高速データ記憶装置から、前記データに対する読み取り要求を満足させる動作をさらに含む、コンピュータシステム。

#### 【発明の詳細な説明】

##### 【背景技術】

##### 【0001】

メモリ装置は多くのトレードオフを有する。高速のメモリは高価である場合がある。低速のメモリは安価である場合がある。最新のアプリケーションのメモリ要件が消費者のシステムの物理容量を超えると、特にタスク又はユーザ間での切り替えのときに、ハードドライブへのページング動作によって急速にシステム及びアプリケーションが遅く且つ反応が鈍く見えるようになる。理想的なコンピュータでは、全てのメモリは可能な限り高速であろうが、そのようなコンピュータは実現するには費用がかかりすぎるであろう。さらに

、費用が安く長期にわたる記憶のみを必要とするアプリケーションもある。結果として、コンピュータは、プロセッサに近い超高速メモリからディスクベースのメモリのようなより低速のメモリに及ぶ多様なメモリを有する。さらに、コンピュータは、ポータブルハードドライブ、フロッピー（登録商標）ディスク及びフラッシュメモリ装置のようなより多くの且つ異なるタイプのメモリを追加する能力を有する。これらの装置のそれぞれは、最大化することができる性能特性及び損耗特性を有する。

#### 【発明の開示】

##### 【0002】

高速メモリから低速メモリに転送されるメモリの理想的なサイズを求めると共に使用することによって、結果的に、低速メモリへの保存をより高速にすると共に低速メモリの耐用年数をより長くすることができる。例えば、幾つかのフラッシュメモリ装置は、フラッシュメモリに対する消去及び書き込みの回数を最小化するメモリ書き込みサイズを有する。他の低速メモリ装置は、低速メモリ上の大きなブロックが連続するデータを記憶することを可能にする理想的な書き込みサイズを有することができる。さらに、データが低速メモリに送信されるように指示されても、そのデータに高速メモリ内でアクセスすることができる。

10

#### 【発明を実施するための最良の形態】

##### 【0003】

以下の文は、多数の異なる実施形態の詳細な説明を記載するが、この説明の法定の範囲は、本特許の最後に記載される特許請求の範囲の文言によって画定されることを理解されたい。この詳細な説明は、例示としてのみ解釈され、あらゆる可能な実施形態を説明するものではない。これは、あらゆる可能な実施形態を説明することは、不可能ではないとしても、実際的ではないためである。多数の代替の実施形態は、現在の技術、又は本特許の出願日後に開発される技術のいずれかを使用して実施することができ、これは、依然として本特許請求の範囲の範囲内にある。

20

##### 【0004】

また、用語が、「本明細書において使用される場合、用語『...』は本明細書によって、...を意味するように定義される」という文又は同様の文を使用して本特許において明示的に定義されない限り、その用語の意味を、その明白な又は通常の意味を超えて、明示的にも、暗黙的にも限定する意図はなく、そのような用語は、（本特許請求の範囲の文言以外の）本特許の任意の節において述べられる任意の文に基づいて範囲が限定されるものと解釈すべきではない。本特許の最後に記載される特許請求の範囲に記載されるあらゆる用語が単一の意味を有するように本特許において参照される限りにおいては、これは、読者を困惑させないために明瞭さのためにのみ行われ、そのような請求項の用語が、暗示又はその他によってその単一の意味に限定されることは意図されない。最後に、請求項の構成要素が、構造を一切記載せずに単語「手段」及び機能を記載することによって規定されない限り、あらゆる請求項の構成要素の範囲が、米国特許法第112条第6パラグラフの適用に基づいて解釈されることは意図されない。

30

##### 【0005】

図1に、特許請求される方法のステップ及び装置に関するシステムを実装することができる適切なコンピューティングシステム環境100の一例を示す。コンピューティングシステム環境100は、適切なコンピューティング環境の一例に過ぎず、特許請求の範囲に記載の装置の方法の使用又は機能の範囲についていかなる限定をも示唆するようには意図されない。また、コンピューティング環境100は、例示的な動作環境100に示す構成要素のうちの任意の1つ又はそれらの組合せに関連するなんらかの従属関係又は要件を有するものとも解釈すべきでない。

40

##### 【0006】

特許請求される方法のステップ及び装置は、多数の他の汎用又は専用のコンピューティングシステムの環境又は構成と共に動作する。特許請求の範囲に記載の方法又は装置に使用するのに適している可能性がある既知のコンピューティングシステム、コンピューティ

50

ング環境、及び／又はコンピューティング構成の例には、限定はしないが、パーソナルコンピュータ、サーバコンピュータ、ハンドヘルド装置又はラップトップ装置、マルチプロセッサシステム、マイクロプロセッサベースシステム、セットトップボックス、プログラム可能な家電製品、ネットワークPC、ミニコンピュータ、メインフレームコンピュータ、上記のシステム若しくは装置のうちのいずれかを含む分散コンピューティング環境等が含まれる。

#### 【0007】

特許請求される方法のステップ及び装置は、コンピュータによって実行されるプログラムモジュール等のコンピュータ実行可能命令の一般的な文脈で説明することができる。一般に、プログラムモジュールには、特定のタスクを実行するか又は特定の抽象データ型を実装するルーチン、プログラム、オブジェクト、コンポーネント、データ構造等が含まれる。本方法及び本装置は、通信ネットワークを通じてつながれている遠隔の処理装置によってタスクが実行される分散コンピューティング環境で実装することもできる。分散コンピューティング環境では、プログラムモジュールは、メモリ記憶装置を含むローカル及びリモートの両方のコンピュータ記憶媒体に置くことができる。

10

#### 【0008】

図1を参照すると、特許請求される方法のステップ及び装置を実装する例示的なシステムは、コンピュータ110の形態の汎用コンピューティング装置を含む。コンピュータ110の構成要素には、限定はしないが、処理装置120と、システムメモリ130と、システムメモリを含む各種のシステム構成要素を処理装置120に結合するシステムバス121とが含まれ得る。システムバス121は、各種のバスアーキテクチャのうちのいずれかを使用する、メモリバス又はメモリコントローラ、ペリフェラルバス、及びローカルバスを含む数種のバス構造のうちのいずれかとすることができる。限定ではなく例として、そのようなアーキテクチャには、インダストリスタンダードアーキテクチャ(ISA)バス、マイクロチャネルアーキテクチャ(MCA)バス、拡張ISA(EISA)バス、ビデオエレクトロニクススタンダードアソシエーション(VESA)ローカルバス、及び、メザニンバスとしても知られている周辺装置相互接続(PCIE)バスが含まれる。

20

#### 【0009】

コンピュータ110は通常、各種のコンピュータ可読媒体を含む。コンピュータ可読媒体は、コンピュータ110によるアクセスが可能な任意の利用可能媒体とすることができる、揮発性の媒体及び不揮発性の媒体の両方、並びに取り外し可能な媒体及び取り外し不可能な媒体の両方を含む。限定ではなく例として、コンピュータ可読媒体は、コンピュータ記憶媒体と通信媒体とから成ることができる。コンピュータ記憶媒体には、コンピュータ可読命令、データ構造、プログラムモジュール又は他のデータ等の情報を記憶するあらゆる方式又は技術で実装される、揮発性の媒体及び不揮発性の媒体の両方、並びに取り外し可能な媒体及び取り外し不可能な媒体の両方が含まれる。コンピュータ記憶媒体には、限定はしないが、RAM、ROM、EEPROM、フラッシュメモリ、若しくは他のメモリ技術、CD-ROM、デジタル多用途ディスク(DVD)、若しくは他の光ディスク記憶装置、磁気カセット、磁気テープ、磁気ディスク記憶装置、若しくは他の磁気記憶装置、又は必要とする情報を記憶するために使用することができると共にコンピュータ110によるアクセスが可能な他の任意の媒体が含まれる。通信媒体は、通常、コンピュータ可読命令、データ構造、プログラムモジュール、又は他のデータを、搬送波又は他の移送機構等の変調データ信号に具現化するとともに、任意の情報伝達媒体を含むものである。用語「変調データ信号」とは、信号中に情報を符号化するような方式でその特性のうちの1つ又は複数を設定又は変化させた信号を意味する。限定ではなく例として、通信媒体には、有線ネットワーク又は直接配線接続等の有線媒体と、音響、RF、赤外線、及び他の無線媒体等の無線媒体とが含まれる。上記のうちのいずれかの組合せもコンピュータ可読媒体の範囲内に含まれるべきである。

30

#### 【0010】

システムメモリ130は、読み取り専用メモリ(ROM)131及びランダムアクセス

40

50

メモリ (RAM) 132 等の揮発性メモリ及び / 又は不揮発性メモリの形態のコンピュータ記憶媒体を含む。起動中等にコンピュータ 110 内の要素間の情報転送を助ける基本ルーチンを含む基本入出力システム 133 (BIOS) は、通常、ROM 131 に記憶される。RAM 132 は、通常、処理装置 120 から即座にアクセス可能な且つ / 又は処理装置 120 によって現在操作されているデータ及び / 又はプログラムモジュールを保持する。限定ではなく例として、図 1 には、オペレーティングシステム 134、アプリケーションプログラム 135、他のプログラムモジュール 136、及びプログラムデータ 137 が示される。

#### 【0011】

コンピュータ 110 は、他の取り外し可能 / 取り外し不能な、揮発性 / 不揮発性のコンピュータ記憶媒体も含むことができる。例としてのみ、図 1 には、取り外し不能な不揮発性の磁気媒体の読み書きを行うハードディスクドライブ 140 と、取り外し可能な不揮発性の磁気ディスク 152 の読み書きを行う磁気ディスクドライブ 151 と、CD-ROM 又は他の光媒体等の取り外し可能な不揮発性の光ディスク 156 の読み書きを行う光ディスクドライブ 155 が示される。例示的な動作環境で使用することができる他の取り外し可能 / 取り外し不能な、揮発性 / 不揮発性のコンピュータ記憶媒体には、限定はしないが、磁気テープカセット、フラッシュメモリカード、デジタル多用途ディスク、デジタルビデオテープ、ソリッドステート RAM、ソリッドステート ROM 等が含まれる。ハードディスクドライブ 141 は通常、インターフェース 140 等の取り外し不能メモリインターフェースを通じてシステムバス 121 に接続され、磁気ディスクドライブ 151 及び光ディスクドライブ 155 は、通常、インターフェース 150 等の取り外し可能メモリインターフェースによってシステムバス 121 に接続される。

10

20

#### 【0012】

上述され且つ図 1 に示されるドライブとそれに関連するコンピュータ記憶媒体は、コンピュータ可読命令、データ構造、プログラムモジュール、及び他のデータの記憶をコンピュータ 110 に提供する。図 1 では、例えば、ハードディスクドライブ 141 は、オペレーティングシステム 144、アプリケーションプログラム 145、他のプログラムモジュール 146、及びプログラムデータ 147 を記憶しているものとして説明されている。これらのコンポーネントは、オペレーティングシステム 134、アプリケーションプログラム 135、他のプログラムモジュール 136、及びプログラムデータ 137 と同じとすることができるか、又は異なるものとすることに留意されたい。ここでは、それらが最低でも異なるコピーであることを示すために、オペレーティングシステム 144、アプリケーションプログラム 145、他のプログラムモジュール 146、及びプログラムデータ 147 には、異なる参照符号を付している。ユーザは、キーボード 162、及び一般にはマウス、トラックボール又はタッチパッドと称されるポインティング装置 161 等の入力装置を通じてコンピュータ 20 にコマンド及び情報を入力することができる。他の入力装置 (図示せず) としては、マイクロフォン、ジョイスティック、ゲームパッド、衛星受信アンテナ、スキヤナ等を含むことができる。これらの入力装置及び他の入力装置は、多くの場合、システムバスに結合されているユーザ入力インターフェース 160 を通じて処理装置 120 に接続されるが、パラレルポート、ゲームポート、又はユニバーサルシリアルバス (USB) 等の他のインターフェース及びバス構造によって接続することもできる。モニタ 191 又は他のタイプの表示装置も、ビデオインターフェース 190 等のインターフェースを介してシステムバス 121 に接続される。モニタに加えて、コンピュータは、スピーカ 197 及びプリンタ 196 等の他の周辺出力装置も含むことができ、それらの周辺出力装置は、出力周辺インターフェース 190 を通じて接続されることができる。

30

40

#### 【0013】

コンピュータ 110 は、リモートコンピュータ 180 等の 1 つ又は複数のリモートコンピュータとの論理接続を使用するネットワーク環境で動作することができる。リモートコンピュータ 180 は、パーソナルコンピュータ、サーバ、ルータ、ネットワーク PC、ピア装置、又は他の一般的なネットワークノードとすることができます、図 1 にはメモリ記憶装

50

置 181 のみが示されているが、通常は、コンピュータ 110 に関連して上述した要素の多く又はすべてを含む。図 1 に示す論理接続は、ローカルエリアネットワーク (LAN) 171 及びワイドエリアネットワーク (WAN) 173 を含むが、他のネットワークを含むことも可能である。このようなネットワーキング環境は、オフィス、企業内のコンピュータネットワーク、インターネット、及びインターネットで一般的である。

【0014】

LAN ネットワーキング環境で使用される場合、コンピュータ 110 は、ネットワークインターフェース又はアダプタ 170 を通じて LAN 171 に接続される。WAN ネットワーキング環境で使用される場合、コンピュータ 110 は、通常、インターネット等の WAN 173 を通じて通信を確立するモデム 172 又は他の手段を含む。モデム 172 は、内蔵型でも外付け型でもよく、ユーザ入力インターフェース 160 又は他の適切な機構を介してシステムバス 121 に接続することができる。ネットワーク環境では、コンピュータ 110 に関連して図示するプログラムモジュール又はその一部は、遠隔のメモリ記憶装置に記憶することができる。限定ではなく例として、図 1 は、リモートアプリケーションプログラム 185 がメモリ装置 181 にあるように示す。図示されるネットワーク接続は例示的なものであり、コンピュータ間に通信リンクを確立する他の手段を使用することができることは理解されるであろう。

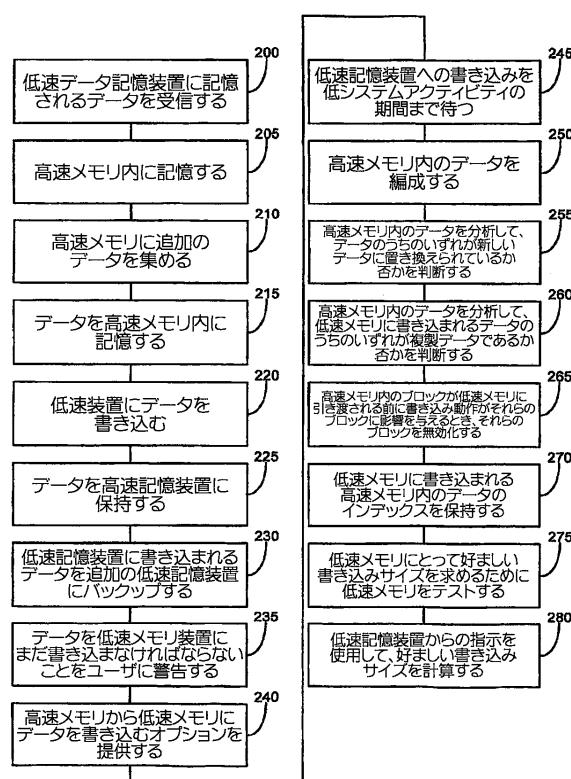

【0015】

図 2 は、データを効率的に記憶する方法を例示するものであり、ここでは、データ記憶速度の階層を有する複数のデータ記憶装置が存在する。メモリ装置は多数のトレードオフを有し得る。高速のメモリは高価である場合がある。低速のメモリは安価である場合がある。理想的なコンピュータでは、全てのメモリは可能な限り高速であろうが、そのようなコンピュータは大多数の使用にとっては費用がかかりすぎるであろう。さらに、費用が安く長期にわたる記憶のみを必要とするアプリケーションもある。結果として、コンピュータは、プロセッサに近い超高速メモリからディスクベースのメモリのようなより低速のメモリに及ぶ多様なメモリを有する。さらに、コンピュータは、ポータブルハードドライブ 140 及びフラッシュメモリ装置 152 のようなより多くの且つ異なるタイプのメモリを追加することができる。これらの装置のそれぞれは、最大化することができる性能特性及び損耗特性を有する。

【0016】

例えば、フラッシュメモリ 152 は 2 つの一般的な形態、すなわち NOR フラッシュ及び NAND フラッシュで作成される。フラッシュメモリ 152 の他の形態も考慮される。フラッシュメモリ 152 の両方のタイプ及び EEPROM は、データを記憶するために使用される電荷蓄積機構周辺の絶縁酸化物層についての損耗に起因して、多数の消去動作の後に損耗してしまう。通常の NOR フラッシュメモリ 152 ユニットは 10000 回～100000 回の消去 / 書き込み動作の後に損耗する可能性があり、通常の NAND フラッシュ 152 メモリは 1000000 回の後に損耗する可能性がある。フラッシュメモリ 152 の 1 つの限界は、フラッシュメモリ 152 が、ランダムアクセスで 1 度に 1 バイト又は 1 ワードで読み取られるか又はプログラムされることができるのにもかかわらず、1 度に 1 つの「ブロック」で消去されなければならないということである。消去されたばかりの 1 つのブロックから始めると、そのブロック内のあらゆるバイトをプログラミングすることができる。しかし、1 バイトがプログラミングされると、ブロック全体が消去されるまでそのバイトは再び変更することができない。ハードディスクドライブ 140 と比較した場合、フラッシュメモリ 152 は、消去 / 書き込みサイクルの回数が有限であるという点で制限されており、その結果、消去 / 書き込みサイクルの回数を最小化するように注意しなければならない。

【0017】

他の装置では、書き込みサイクルの遅さは、好ましい書き込みサイズを求める際の 1 つの因子であり得る。例えば、書き込み機能をセットアップするためにかなりのオーバーヘッド時間が必要とされる場合、書き込まれるデータのサイズを最大化することによって書

き込みの回数を最小化することによって時間を節約することができる。同様に、記憶装置によっては、小規模の保存を繰り返すことによって、結果的にデータが記憶装置にわたって拡散する可能性があり、これによって結果的に、回数のより少ないより大規模な保存という結果を招来し得る、データが隣接して記憶される場合よりも、読み取り時間が長くなるおそれがある。さらに、書き込みサイクルはプロセッサに負担をかけるおそれがあり、プロセッサの使用量が高い期間の間、頻度がより小さくなるような時間間隔でより大きな記憶サイズとして、より少ない頻度で保存することは合理的であり得る。

#### 【0018】

ハードドライブ140を再び参照すると、高速メモリがない場合、ハードディスク140への全ての書き込みがパフォーマンスヒットを伴う可能性があり、その間システムは、ハードディスク140がハードディスク140上の正確な位置にアクセスしてデータを書き込むのを待つ。これは、ほとんどのドライブ上で少なくとも10ミリ秒かかり、この秒数はコンピュータの世界では長い時間であり、システムがハードディスクを待っているときに性能を実際に低下させるおそれがある。

#### 【0019】

RAM132のような高速メモリが利用可能である場合（書き込みキャッシングがイネーブルされるとも呼ばれる）、システムがハードディスク140に書き込みを送信するとき、論理回路はその書き込みを自身のはるかに速いキャッシング、すなわち高速メモリ132に記録し、その直後に基本的に、「終了した」と伝える肯定応答をオペレーティングシステムに返信する。その際システムの残りの部分は、アクチュエータが位置決めされること及びディスクが回転すること等を待つ必要もなく動作し続けることができ、これによって性能が改善される。しかしながら、ディスク140は、実際に終了していないとき、すなわちデータがディスク上に完全になく、キャッシング132内のみにあるときに、返信して「終了した」と伝えることになる。ハードディスク140の論理回路はデータをディスクに書き込み始めるが、これは当然のことながら幾らかの時間がかかる。

#### 【0020】

通常のPC110の使用には、プログラムをロードすること、並びにデータを頻繁にコード及び保存することが必要である。これらの動作の全てはハードディスク140へのアクセスを必要とする場合がある。したがって、ハードディスク140の性能が問題となる。CPU120を待機中に200万の命令を処理するほど速くすることは、その時間中にすべき何かをCPUが有しない限り実際にはユーザにほとんど利益をもたらさない。ハードディスク140の性能問題が最も重要であるアプリケーションは、マルチメディア編集アプリケーション、特に大きなオーディオファイル及びビデオファイルを扱うアプリケーションのような多数の処理を行うアプリケーションではなく、ハードディスク140に対して多数の読み取り及び書き込みを行うアプリケーションである。

#### 【0021】

アクセス時間は、ハードディスク140におけるランダムな性能の位置決め（random performance positioning）を反映する全ての他の仕様の複合を表すメトリックである。最も一般的な定義は以下の通りである：

アクセス時間 = コマンドオーバーヘッド時間 + シーク時間 + 定着時間（Settle time）+ 待ち時間

コマンドオーバーヘッドは、コマンドがハードディスク140に与えられてから、そのコマンドを実行するために何かが実際に起こり始めるまでに経過する時間を指すものとする。ハードディスク140のシーク時間は、読み取り／書き込みヘッドがプラッタの表面にわたってトラック間を移動するのに必要とされる時間を示すものとする。トラック間の切り替えは、ヘッドアクチュエータがヘッドアームを物理的に動かすことを必要とし、これは機械的プロセスであり、特定の時間がかかる。2つのトラックの間で切り替えるのに必要な時間は、そのトラック間の距離によって決まる。しかし、トラックの切り替えには一定量の「オーバーヘッド」が伴う。その結果、関係は線形ではない。トラック1からトラック3に切り替える時間は、トラック1からトラック2に切り替える時間の2倍とはな

10

20

30

40

50

らない可能性がある。

【0022】

シーク時間は通常ミリ秒で表される（一般に「msec」又は「ms」と略される）。当然のことながら、最新のPC110では1ミリ秒は膨大な時間であり、これは、例えばRAM132のような高速システムメモリはナノ秒で測定される速度を有することができるためである（100万倍小さい）。1GHzプロセッサは（理論的には）、1ミリ秒で100万個より多くの命令を実行する。シーク時間のわずかな短縮であっても、システムの残りの部分が多くの場合にハードディスク140を待っているため、結果的に全システム性能を向上することができる。

【0023】

ハードディスク140のプラッタは高速で回転しており、回転速度は、ハードディスク140上でランダムアクセスで読み取り／書き込みヘッドを正確なシリンドラへ動かすプロセスに同期しない可能性がある。したがって、ヘッドが正確なシリンドラに到達するときは、必要とされる実際のセクタはどこにでも存在し得る。アクチュエータアセンブリが正確なトラックに対するシークを完了した後、ドライブ140は、読み取り／書き込みヘッドが位置する所に正確なセクタが回って来るのを待つ場合がある。この時間は待ち時間と呼ばれる。待ち時間はドライブのスピンドル速度に直接関連し、そのようなものはドライブのスピンドル特性によってのみ影響を受ける。したがって、アクセス時間を短縮することができるあらゆる行為は、システム性能に大きな影響を与え得る。

【0024】

利用可能なRAM132の量も、高速メモリ内に記憶することができるデータのサイズに影響を与え得る。例えば、システムが8kの高速RAM132のみを有する場合、単にRAM132が多量のデータを記憶することができないため、システムが512kbの高速RAM132を有する場合よりも頻繁に書き込み動作を行う必要があるであろう。

【0025】

ブロック200において、本方法は、低速データ記憶装置に記憶されるデータを受信することができる。例えば、ワードプロセッシングファイルは、ハードドライブ140に記憶されるように指定することができる。ブロック205において、データを高速メモリ内に記憶することができる。例えば、ワードプロセッシングファイルはRAM132内のキヤッシュに記憶することができる。ブロック210において、本方法は、ハードドライブ140のような特定の低速データ装置向けの好ましい量のデータが記憶されるまで、追加のデータを高速メモリ132に集めることができる。ブロック215において、本方法は、特定の記憶装置に適した書き込みサイズになるまで、データを高速メモリ132に記憶することができる。上述したように、データの好ましい量は装置によって変更することができる。例えば、好ましい書き込みサイズは、128kb、256kb及び512kbのうちの1つのような多様な2の累乗とすることができます。フラッシュメモリの例では、サイズは、フラッシュブロック全体にすぐに記憶できるようになっているときに、フラッシュ装置に書き込むことのみによって消去／書き込み動作が最小限に抑えられるようなフラッシュメモリブロックのサイズとすることができます（多数の消去／書き込み動作を行うのではない）。ブロック220において、特定の装置に適した書き込みサイズのデータは、高速メモリ装置132内に記憶されると、低速装置140に書き込むことができる。

【0026】

ブロック225において、本方法は、データがもはや高速記憶装置132内で不要であるという判断が下されるまで、そのデータを高速記憶装置132内に保持することができる。例えば、システムが余分なRAM132を有する場合、低速メモリ140に既に書き込まれ高速メモリ132内にもあるデータを保持することはシステムに負担をかけない可能性がある。そのデータは、低速メモリ140にすでに記憶されている場合、高速メモリ132内では不要であり得るが、いずれにせよユーザの都合により高速メモリ132内に保持することができる。

【0027】

10

20

30

40

50

ブロック 230において、低速記憶装置 140 に書き込まれるデータが追加の低速記憶装置 140 にバックアップされる請求項 1 の方法。場合によっては、ユーザ又はプログラムは、データを低速記憶装置 140 に記憶するように命令することができる。本方法は、低速メモリに書き込む前に最適な量のデータを待つことができる。その間に、フラッシュメモリユニット 152 のような低速メモリをシステムから取り外すことができる。これらの場合は、データのバックアップを追加の低速記憶装置内に有することができる。有利であり得る。データは、高速メモリ 132 から、高速メモリ 132 よりは低速だが低速メモリよりは高速である追加のメモリに移動させることができる。ブロック 235において、本方法は、データが高速メモリ 132 からフラッシュ 152 のような低速メモリ装置 152 に書き込まれる前に低速メモリ装置がシステムから取り外されたときに、データを低速メモリ装置にまだ書き込まなければならないことをユーザに警告することができる。ブロック 240において、低速メモリ装置が取り外される前にデータを高速メモリ 132 から低速メモリ 152 に書き込むオプションをユーザに提供することができる。ブロック 245において、本方法は、低速記憶装置への書き込みを低システムアクティビティの期間まで待つことができる。10

#### 【0028】

一例として、ユーザ又は方法は、ワードプロセッシングファイルがフラッシュメモリ 152 に記憶されるように指示することができる。本方法は、フラッシュメモリ 152 に最適な書き込みサイズに一致する十分なデータを待つことができ、その結果、ワードプロセッシングファイルのサイズが最適な書き込みサイズ未満である場合に、データがフラッシュメモリ 152 に即座に書き込まれないようにすることができる。フラッシュ 152 が取り外される場合、データをフラッシュメモリ 152 にまだ書き込まなければならないことをユーザに警告することができる。さらに、データは、「中間」速度記憶装置に既にバックアップされていることができ、データが高速記憶装置 132 内にある間に上書きされるのを防ぐためにこのバックアップを使用することができる。20

#### 【0029】

ブロック 250において、本方法は、低速メモリ 140 への書き込みがより効率的であるように高速メモリ 132 内のデータを編成することができる。編成は、低速メモリ 140 への転送がより効率的に進行することができるよう、高速メモリ 132 内のデータを隣接するように再構成するのと同程度に単純であり得る。30

#### 【0030】

ブロック 255において、本方法は、高速メモリ 132 内のデータを分析して、データが低速メモリ 140 に書き込まれる前にデータのうちのいずれが新しいデータに置き換えられているか否かを判断することができる。ブロック 260において、本方法は、高速メモリ 132 内のデータを分析して、低速メモリ 140 に書き込まれるデータのうちのいずれが重複データであるか否かを判断することができ、古い重複データは低速メモリ 140 装置に書き込まれない。ブロック 265において、本方法は、高速メモリ 132 内のブロックが低速装置 140 に引き渡される前に書き込み動作がそれらのブロックに影響を与えるとき、それらのブロックを無効化することができる。40

#### 【0031】

ブロック 270において、本方法は、低速メモリ 140 に書き込まれる高速メモリ 132 内のデータのインデックスを保持することができ、低速装置 140 に書き込まれることになっている書き込まれるデータが高速メモリ 132 に常駐している場合、本方法は、データが低速メモリ 140 に書き込まれているか否かを問わずに、高速メモリ 132 から、データに対する読み取り要求を満足させることができる。

#### 【0032】

ブロック 275において、本方法は、低速メモリ 140 にとって好ましい書き込みサイズを求めるために低速メモリ 140 をテストすることができる。例えば、本方法は、理想的な消去 / 書き込みサイズはいくらであるかについてフラッシュメモリ 152 に問い合わせすることができる。ブロック 280において、本方法は、低速記憶装置 140 からの指示

10

20

30

40

50

を使用して好ましい書き込みサイズを計算することもできる。例えば、フラッシュメモリ 152 の例では、本方法は、ブロックが 1024 バイトの増分で消去されると判断することができ、したがって、本方法は、保存動作が 1024 バイトの増分で生じるべきであると判断することができる。好ましい書き込みサイズは、低速メモリ 152 の好ましい消去サイズに関連することができる。

【 0 0 3 3 】

上記の文は、多数の異なる実施形態の詳細な説明を記載するが、本特許の範囲は、本特許に記載される特許請求の範囲の文言によって画定されることを理解されたい。この詳細な説明は、例示としてのみ解釈されるべきであり、あらゆる可能な実施形態を説明するものではない。これは、あらゆる可能な実施形態を説明することは、不可能ではないとしても、実際的ではないためである。多数の代替の実施形態は、現在の技術、又は本特許の出願日後に開発される技術のいずれかを使用して実施することができ、これは、依然として本特許請求の範囲の範囲内にある。

【 0 0 3 4 】

したがって、多数の変更及び変形を、本特許請求の範囲の精神及び範囲から逸脱することなく、本明細書に記載及び図示される技法及び構造において行うことが可能である。したがって、本明細書に記載される方法及び装置は、単に例示にすぎず、本特許請求の範囲の範囲を限定しないことを理解されたい。

## 【図面の簡単な説明】

〔 0 0 3 5 〕

【図1】図1は、特許請求の範囲に従って動作することができるコンピューティングシステムのブロック図である。

【図2】図2は、特許請求の範囲による方法の図である。

( 四 1 )

〔 図 2 〕

---

フロントページの続き

(51)Int.Cl.

F I

G 0 6 F 12/08 5 0 7 B

(74)代理人 100153028

弁理士 上田 忠

(72)発明者 フォーティン,マイケル・アール

アメリカ合衆国ワシントン州98052,レッドモンド,ワン・マイクロソフト・ウェイ,マイクロソフト コーポレーション,インターナショナル・パテント

(72)発明者 レイナウアー,ロバート・エル

アメリカ合衆国ワシントン州98052,レッドモンド,ワン・マイクロソフト・ウェイ,マイクロソフト コーポレーション,インターナショナル・パテント

審査官 岩間 直純

(56)参考文献 特開平05-282889 (JP, A)

特開2003-196032 (JP, A)

特開2005-044010 (JP, A)

米国特許出願公開第2004/0136259 (US, A1)

元麻布 春男, IEEE1394 岐路に立つ「夢のインターフェイス」, PC USER, 日本, ソフトバンクパブリッシング株式会社, 1999年10月24日, 第6巻, 第18号, pp. 81-85

(58)調査した分野(Int.Cl., DB名)

G 0 6 F 12 / 0 8

G 0 6 F 12 / 0 0

G 0 6 F 13 / 3 8