(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5210710号

(P5210710)

(45) 発行日 平成25年6月12日(2013.6.12)

(24) 登録日 平成25年3月1日(2013.3.1)

(51) Int.Cl.

F 1

H03K 17/08 (2006.01)

H03K 17/08

Z

H03K 17/56 (2006.01)

H03K 17/56

Z

H03K 17/687 (2006.01)

H03K 17/687

A

請求項の数 9 (全 15 頁)

(21) 出願番号

特願2008-136193 (P2008-136193)

(22) 出願日

平成20年5月26日 (2008.5.26)

(65) 公開番号

特開2009-284370 (P2009-284370A)

(43) 公開日

平成21年12月3日 (2009.12.3)

審査請求日

平成23年5月19日 (2011.5.19)

(73) 特許権者 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

(74) 代理人 100085501

弁理士 佐野 静夫

(74) 代理人 100134555

弁理士 林田 英樹

(72) 発明者 柳島 大輝

京都市右京区西院溝崎町21番地 ローム

株式会社内

(72) 発明者 石川 俊行

京都市右京区西院溝崎町21番地 ローム

株式会社内

審査官 栗栖 正和

最終頁に続く

(54) 【発明の名称】ゲート駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

出力トランジスタのゲート電圧を駆動するゲート駆動装置であつて、

前記ゲート電圧と所定の閾値電圧との高低関係を検出する電圧検出回路と、前記電圧検出回路の検出結果に基づいて前記出力トランジスタのゲートと電源電圧の印加端との間を導通／遮断するスイッチと、を有して成り、

前記電圧検出回路は、前記閾値電圧を生成する閾値電圧生成部と、前記ゲート電圧と前記閾値電圧とを比較する電圧比較部と、前記電圧比較部の比較結果に基づいて前記スイッチの制御信号を生成する出力部と、を有して成り、

前記電圧比較部は、カレントミラー回路を形成するトランジスタ対に前記ゲート電圧と前記閾値電圧を印加して、前記カレントミラー回路の出力電流を前記出力部に送出し、前記出力部は、前記出力電流を電圧変換することで前記スイッチの制御信号を生成することを特徴とするゲート駆動装置。

## 【請求項 2】

前記電圧比較部は、前記ゲート電圧及び前記閾値電圧を前記トランジスタ対の各ソースに各々印加することを特徴とする請求項1に記載のゲート駆動装置。

## 【請求項 3】

前記電圧検出回路は、前記ゲート電圧の論理レベルに応じて前記出力トランジスタのゲートと前記電圧比較部のゲート電圧入力端との間を導通／遮断するゲート電圧遮断部を有して成ることを特徴とする請求項1または請求項2に記載のゲート駆動装置。

10

20

**【請求項 4】**

出力トランジスタのゲート電圧を駆動するゲート駆動装置であって、

前記ゲート電圧と所定の閾値電圧との高低関係を検出する電圧検出回路と、前記電圧検出回路の検出結果に基づいて前記出力トランジスタのゲートと電源電圧の印加端との間を導通／遮断するスイッチと、を有して成り、

前記電圧検出回路は、前記閾値電圧を生成する閾値電圧生成部と、前記ゲート電圧と前記閾値電圧とを比較する電圧比較部と、前記電圧比較部の比較結果に基づいて前記スイッチの制御信号を生成する出力部と、を有して成り、

前記電圧検出回路は、前記ゲート電圧の論理レベルに応じて前記出力トランジスタのゲートと前記電圧比較部のゲート電圧入力端との間を導通／遮断するゲート電圧遮断部を有して成ることを特徴とするゲート駆動装置。

10

**【請求項 5】**

前記ゲート電圧遮断部は、前記ゲート電圧を分圧して前記電圧比較部に供給することを特徴とする請求項 3 または請求項 4 に記載のゲート駆動装置。

**【請求項 6】**

前記閾値電圧生成部は、前記電源電圧よりも所定値だけ低い前記閾値電圧を生成し、前記出力部は、前記ゲート電圧が前記閾値電圧以上となったときに前記スイッチを導通することを特徴とする請求項 5 に記載のゲート駆動装置。

**【請求項 7】**

前記ゲート電圧遮断部は、ソースが抵抗を介して前記電源電圧の印加端に接続され、ドレインが前記ゲートの印加端に接続され、ゲートが制御信号の印加端に接続された第 1 トランジスタと；ソースが前記電源電圧の印加端に接続され、ドレインが前記電圧比較部のゲート電圧入力端に接続され、ゲートが第 1 トランジスタのソースに接続された第 2 トランジスタと；ソースが前記電圧比較部のゲート電圧入力端に接続され、ドレインが前記ゲート電圧の印加端に接続され、ゲートが前記制御信号の印加端に接続された第 3 トランジスタと；を有して成ることを特徴とする請求項 6 に記載のゲート駆動装置。

20

**【請求項 8】**

前記閾値電圧生成部は、前記出力トランジスタのソース電圧よりも所定値だけ高い前記閾値電圧を生成し、前記出力部は、前記ゲート電圧が前記閾値電圧以下となったときに前記スイッチを導通することを特徴とする請求項 5 に記載のゲート駆動装置。

30

**【請求項 9】**

前記ゲート電圧遮断部は、ソースが抵抗を介して前記ソース電圧の印加端に接続され、ドレインが前記ゲートの印加端に接続され、ゲートが制御信号の印加端に接続された第 1 トランジスタと；ソースが前記ソース電圧の印加端に接続され、ドレインが前記電圧比較部のゲート電圧入力端に接続され、ゲートが第 1 トランジスタのソースに接続された第 2 トランジスタと；ソースが前記電圧比較部のゲート電圧入力端に接続され、ドレインが前記ゲート電圧の印加端に接続され、ゲートが前記制御信号の印加端に接続された第 3 トランジスタと；を有して成ることを特徴とする請求項 8 に記載のゲート駆動装置。

**【発明の詳細な説明】****【技術分野】**

40

**【0001】**

本発明は、電界効果トランジスタ（FET [Field Effect Transistor]）や絶縁ゲートトランジスタ（IGBT [Insulated Gate Bipolar Transistor]）などのゲート電圧を駆動するゲート駆動装置に関するものである。

**【背景技術】****【0002】**

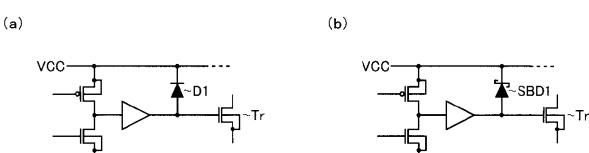

図 5 は、ゲート駆動装置の一従来例を示す回路図である。図中の（a）、（b）で示すように、従来のゲート駆動装置は、出力トランジスタ Tr のゲート電圧をクランプする手段として、出力トランジスタ Tr のゲートと電源電圧 VCC の印加端との間に、ダイオード D1 やショットキーバリアダイオード SBD1 を有する構成とされていた。

50

**【0003】**

なお、上記に関連する従来技術の一例として、特許文献1などを挙げることができる。

【特許文献1】特開平2-298067号公報

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

確かに、図5(a)で示したように、ダイオードD1を用いて出力トランジスタTrのゲート電圧をクランプする構成であれば、ゲート駆動装置を集積化するに際して、ダイオードD1をICに内蔵することができるので、実装スペースや実装コストを抑えることが可能である。しかしながら、図5(a)の従来構成では、ダイオードD1の順方向降下電圧Vfが大きいため、ダイオードD1に流れる電流が大きくなると、出力トランジスタTrのゲート電圧を十分にクランプできなくなり、ゲート駆動装置の定格電圧を超えて破壊に至るおそれがあった。

**【0005】**

一方、図5(b)で示したように、ショットキーバリアダイオードSBD1を用いて出力トランジスタTrのゲート電圧をクランプする構成であれば、ショットキーバリアダイオードSBD1に流れる電流が大きくなった場合でも、出力トランジスタTrのゲート電圧を十分にクランプすることができる。しかしながら、図5(b)の従来構成では、ゲート駆動装置を集積化するに際して、ショットキーバリアダイオードSBD1をICに外付けしなければならず、実装スペースや実装コストの増大が招かれていた。

**【0006】**

本発明は、上記の課題に鑑み、外付け部品を要することなく、出力トランジスタのゲート電圧を適切にクランプすることができるゲート駆動装置を提供することを目的とする。

**【課題を解決するための手段】****【0007】**

上記目的を達成するために、本発明に係るゲート駆動装置は、出力トランジスタのゲート電圧を駆動するゲート駆動装置であって、前記ゲート電圧と所定の閾値電圧との高低関係を検出する電圧検出回路と、前記電圧検出回路の検出結果に基づいて前記出力トランジスタのゲートと電源電圧の印加端との間を導通/遮断するスイッチと、を有して成る構成(第1の構成)とされている。

**【0008】**

なお、上記第1の構成から成るゲート駆動装置において、前記電圧検出回路は、前記閾値電圧を生成する閾値電圧生成部と、前記ゲート電圧と前記閾値電圧とを比較する電圧比較部と、前記電圧比較部の比較結果に基づいて前記スイッチの制御信号を生成する出力部と、を有して成る構成(第2の構成)にするとよい。

**【0009】**

また、上記第2の構成から成るゲート駆動装置において、前記電圧比較部は、カレントミラー回路を形成するトランジスタ対の各ソースに前記ゲート電圧と前記閾値電圧を各々印加して、前記カレントミラー回路の出力電流を前記出力部に送出し、前記出力部は、前記出力電流を電圧変換することで前記スイッチの制御信号を生成する構成(第3の構成)とされている。

**【0010】**

また、上記第2または第3の構成から成るゲート駆動装置において、前記電圧検出回路は、前記ゲート電圧の論理レベルに応じて前記出力トランジスタのゲートと前記電圧比較部のゲート電圧入力端との間を導通/遮断するゲート電圧遮断部を有して成る構成(第4の構成)にするとよい。

**【0011】**

また、上記第4の構成から成るゲート駆動装置において、前記ゲート電圧遮断部は、前記ゲート電圧を分圧して前記電圧比較部に供給する構成(第5の構成)にするとよい。

**【0012】**

10

20

30

40

50

また、上記第5の構成から成るゲート駆動装置にて、前記閾値電圧生成部は、前記電源電圧よりも所定値だけ低い前記閾値電圧を生成し、前記出力部は、前記ゲート電圧が前記閾値電圧以上となったときに前記スイッチを導通する構成（第6の構成）にするとよい。

#### 【0013】

また、上記第6の構成から成るゲート駆動装置において、前記ゲート電圧遮断部は、ソースが抵抗を介して前記電源電圧の印加端に接続され、ドレインが前記ゲートの印加端に接続され、ゲートが制御信号の印加端に接続された第1トランジスタと；ソースが前記電源電圧の印加端に接続され、ドレインが前記電圧比較部のゲート電圧入力端に接続され、ゲートが第1トランジスタのソースに接続された第2トランジスタと；ソースが前記電圧比較部のゲート電圧入力端に接続され、ドレインが前記ゲート電圧の印加端に接続され、ゲートが前記制御信号の印加端に接続された第3トランジスタと；を有して成る構成（第7の構成）にするとよい。10

#### 【0014】

また、上記第5の構成から成るゲート駆動装置において、前記閾値電圧生成部は、前記ソース電圧より所定値だけ高い閾値電圧を生成し、前記出力部は、前記ゲート電圧が前記閾値電圧以下となったときに前記スイッチを導通する構成（第8の構成）にするとよい。

#### 【0015】

また、上記第8の構成から成るゲート駆動装置において、前記ゲート電圧遮断部は、ソースが抵抗を介して前記ソース電圧の印加端に接続され、ドレインが前記ゲートの印加端に接続され、ゲートが制御信号の印加端に接続された第1トランジスタと；ソースが前記ソース電圧の印加端に接続され、ドレインが前記電圧比較部のゲート電圧入力端に接続され、ゲートが第1トランジスタのソースに接続された第2トランジスタと；ソースが前記電圧比較部のゲート電圧入力端に接続され、ドレインが前記ゲート電圧の印加端に接続され、ゲートが前記制御信号の印加端に接続された第3トランジスタと；を有して成る構成（第9の構成）にするとよい。20

#### 【発明の効果】

#### 【0016】

本発明に係るゲート駆動装置であれば、外付け部品を要することなく、出力トランジスタのゲート電圧を適切にクランプすることが可能となる。

#### 【発明を実施するための最良の形態】

#### 【0017】

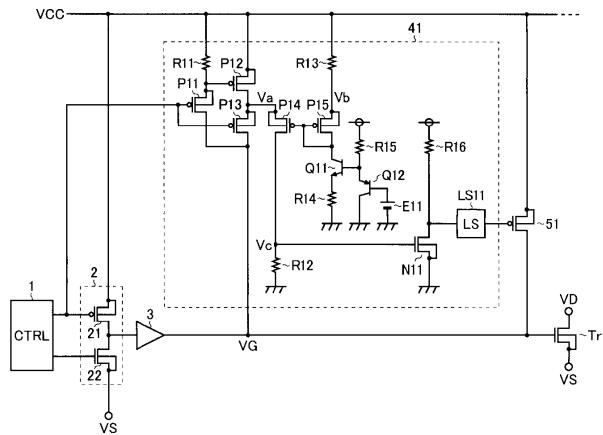

まず、本発明に係るゲート駆動装置の第1実施形態について、図1を参照しながら詳細に説明する。

#### 【0018】

図1は、本発明に係るゲート駆動装置の第1実施形態を示す回路図である。

#### 【0019】

図1に示す通り、本実施形態のゲート駆動装置は、出力トランジスタTr（FETやIGBTなど）のゲート電圧VGを駆動する手段であり、制御部1と、プリドライバ2と、バッファ3と、を有するほか、ゲート電圧VGのクランプ手段として、電圧検出回路41と、スイッチ（Pチャネル型MOS [Metal Oxide Semiconductor] 電界効果トランジスタ）51と、を有して成る。40

#### 【0020】

制御部1は、プリドライバ2を介してゲート電圧VGの駆動制御を行う手段である。例えば、出力トランジスタTrを用いてモータのコイル電流を制御するモータドライバを構成する場合、制御部1は、モータを所望の回転数で駆動するように、プリドライバ2を介してゲート電圧VGの駆動制御を行う。また、出力トランジスタTrを用いてスイッチングレギュレータを構成する場合、制御部1は、所望の出力電圧が生成されるように、プリドライバ2を介してゲート電圧VGの駆動制御を行う。

#### 【0021】

プリドライバ2は、制御部1から入力される制御信号に応じてゲート電圧VGを生成す50

る手段であり、Pチャネル型MOS電界効果トランジスタ21と、Nチャネル型MOS電界効果トランジスタ22と、を有して成る。トランジスタ21のソースは、第1電源電圧VCCの印加端に接続されている。トランジスタ21、22のドレインは互いに接続されており、その接続ノードは、ゲート電圧VGの出力端として、バッファ3の入力端に接続されている。トランジスタ21のバックゲートは、自身のソースに接続されている。トランジスタ21のゲートは、制御部1の第1制御信号出力端に接続されている。トランジスタ22のソースは、所定電圧（例えば、出力トランジスタTrのソース電圧VS）の印加端に接続されている。トランジスタ22のバックゲートは、自身のソースに接続されている。トランジスタ22のゲートは、制御部1の第2制御信号出力端に接続されている。

## 【0022】

10

バッファ3は、プリドライバ2から入力されるゲート電圧VGを緩衝増幅して出力トランジスタTrのゲートに供給する手段である。

## 【0023】

電圧検出回路41は、出力トランジスタTrのゲート電圧VGが所定の閾値電圧（VCC - Vth）以上であるか否かを検出し、その検出結果に応じてスイッチ51のオン／オフ制御を行う手段であり、Pチャネル型MOS電界効果トランジスタP11～P15と、Nチャネル型MOS電界効果トランジスタN11と、抵抗R11～R16と、n-p-n型バイポーラトランジスタQ11と、p-n-p型バイポーラトランジスタQ12と、直流電圧源E11と、レベルシフタLS11と、を有して成る。

## 【0024】

20

トランジスタP11のソースは、抵抗R11を介して、第1電源電圧VCCの印加端に接続されている。トランジスタP11のドレインは、出力トランジスタTrのゲートに接続されている。トランジスタP11のゲートは、制御部1の第1制御信号出力端に接続されている。トランジスタP11のバックゲートは、自身のソースに接続されている。トランジスタP12のソースは、第1電源電圧VCCの印加端に接続されている。トランジスタP12のドレインは、トランジスタP13のソースに接続されている。トランジスタP12のゲートは、トランジスタP11のソースに接続されている。トランジスタP12のバックゲートは、自身のソースに接続されている。トランジスタP13のドレインは、出力トランジスタTrのゲートに接続されている。トランジスタP13のゲートは、制御部1の第1制御信号出力端に接続されている。トランジスタP13のバックゲートは、自身のソースに接続されている。

## 【0025】

30

トランジスタP14のソースは、トランジスタP13のソースに接続されている。トランジスタP14のドレインは、抵抗R12を介して接地端に接続されている。トランジスタP14のゲートは、トランジスタP15のゲート及びドレインに接続されている。トランジスタP14のバックゲートは、自身のソースに接続されている。トランジスタP15のソースは、抵抗R13を介して第1電源電圧VCCの印加端に接続されている。トランジスタP15のドレインは、トランジスタQ11のコレクタに接続されている。トランジスタP15のゲートは、自身のドレインに接続されている。トランジスタP15のバックゲートは、自身のソースに接続されている。

## 【0026】

40

トランジスタQ11のエミッタは、抵抗R14を介して接地端に接続されている。トランジスタQ11のベースは、抵抗R15を介して所定電圧の印加端に接続されている。トランジスタQ12のエミッタは、トランジスタQ11のベースに接続されている。トランジスタQ12のコレクタは、接地端に接続されている。トランジスタQ12のベースは、直流電圧源E11の正極端（基準電圧Vrefの印加端）に接続されている。直流電圧源E11の負極端は、接地端に接続されている。

## 【0027】

トランジスタN11のドレインは、抵抗R16を介して所定電圧の印加端に接続される一方、レベルシフタLS11を介してスイッチ51を形成するトランジスタのゲートにも

50

接続されている。トランジスタN11のソースは、接地端に接続されている。トランジスタN11のゲートは、トランジスタP14のドレインに接続されている。トランジスタN11のバックゲートは、自身のソースに接続されている。

#### 【0028】

レベルシフタLS11は、トランジスタN11のドレインから引き出される電圧信号を適切にレベルシフトすることで、スイッチ51の制御信号（ゲート電圧）を生成する手段である。例えば、電源電圧VCCが高電圧（数百[V]）である場合、スイッチ51をオンするときに、スイッチ51の制御信号を単純にGNDレベルまで落とすと、スイッチ51のゲート・ソース間電圧がスイッチ51の耐圧を超えてしまい、スイッチ51が破壊に至るおそれがある。そこで、レベルシフタLS11では、スイッチ51の破壊を防止すべく、スイッチ51のオン時に供給する制御信号の電圧レベルが適切に設定されている。なお、レベルシフタLS11には、制御信号のレベルシフト機能のほか、必要に応じて制御信号の論理制御機能（例えば論理反転機能）を搭載しても構わない。10

#### 【0029】

スイッチ51は、レベルシフタLS11から入力される制御信号に応じて出力トランジスタTrのゲートと電源電圧VCCの印加端との間を導通／遮断する手段である。なお、図1の例では、スイッチ51としてPチャネル型MOS電界効果トランジスタが用いられており、ゲート駆動装置を集積化する場合には、これをICに内蔵することができる。

#### 【0030】

次に、ゲート電圧VGのクランプ動作について詳細な説明を行う。20

#### 【0031】

上記構成から成るゲート駆動装置において、電圧検出回路41は、閾値電圧生成部（トランジスタQ11、トランジスタQ12、抵抗R13～R15、並びに、直流電圧源E11）と、電圧比較部（トランジスタP14、及び、トランジスタP15）と、出力部（抵抗R12、抵抗R16、トランジスタN11、及び、レベルシフタLS11）と、ゲート電圧遮断部（トランジスタP11～P13、及び、抵抗R11）と、を有して成る。

#### 【0032】

上記のゲート電圧遮断部において、トランジスタP11～P13は、いずれも、制御部1から入力される第1制御信号がローレベルとされたときにオンとなり、第1制御信号がハイレベルとされたときにオフとなる。30

#### 【0033】

すなわち、上記のゲート電圧遮断部は、制御部1から入力される第1制御信号に基づいて、ゲート電圧VGがハイレベルとされるときには、出力トランジスタTrのゲートと電圧比較部のゲート電圧入力端（トランジスタP14のソース）との間を導通し、ゲート電圧VGの分圧電圧Vaを電圧比較部のゲート電圧入力端に印加する一方、ゲート電圧VGがローレベルとされるときには、出力トランジスタTrのゲートと電圧比較部のゲート電圧入力端との間を遮断し、電圧比較部のゲート電圧入力端をオープンとする。

#### 【0034】

このように、上記のゲート電圧遮断部であれば、出力トランジスタTrのゲート電圧VGがローレベルとされるときに、電圧比較部のゲート電圧入力端をオープンとすることができるので、トランジスタP14、P15のゲート酸化物が耐圧破壊されるのを防止することができる。40

#### 【0035】

また、上記のゲート電圧遮断部であれば、出力トランジスタTrのゲート電圧VGを監視する必要のあるとき（ゲート電圧VGがハイレベルとされているとき）にのみ、ゲート電圧VGの分圧経路を導通させることができるので、定常的に電流を浪費せずに済む。

#### 【0036】

ただし、電源電圧VCCの定格電圧がトランジスタP14、P15のゲート耐圧よりも低い場合には、ゲート電圧遮断部を削除し、出力トランジスタTrのゲートを電圧比較部のゲート電圧入力端に直接接続しても構わない。50

## 【0037】

また、上記のゲート電圧遮断部としては、トランジスタP11を削除し、制御部1から入力される第1制御信号をトランジスタP12、P13の各ゲートに直接入力する構成とすることも可能である。ただし、このような構成では、第1制御信号がローレベルとされたとき、先にトランジスタP12がオンし、次いでトランジスタP13がオンする形となる。このように、トランジスタP12、P13のオンタイミングにずれが生じると、分圧電圧Vaは、一旦電源電圧VCC付近まで上昇してしまうため、分圧電圧Vaを電圧比較部に直接入力すると、誤ったクランプ動作が行われてしまう。そのため、トランジスタP11を用いない場合には、分圧電圧Vaの瞬間的な上昇をキャンセルする手段として、何らかのマスク回路が必要となる点に留意すべきである。

10

## 【0038】

これに対して、図1に示すゲート電圧遮断部であれば、トランジスタP11を用いてトランジスタP12がダーリントン接続とされており、第1制御信号がローレベルとされたときには、トランジスタP13がオンし得る状態になってから、トランジスタP12がオンする形となるので、トランジスタP12、P13のオンタイミングを一致させることができ、延いては、分圧電圧Vaの瞬間的な上昇を回避することが可能となる。

## 【0039】

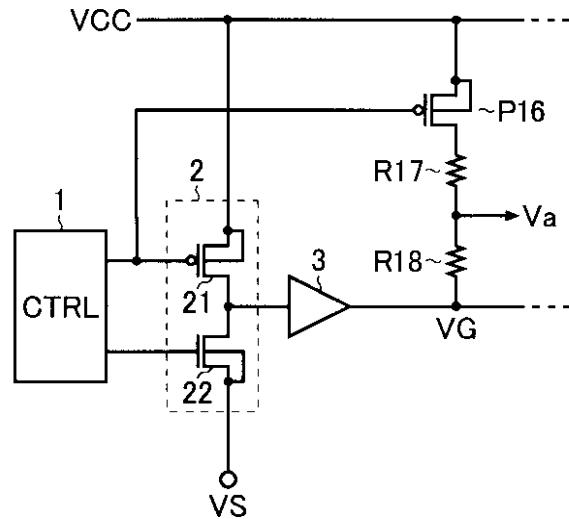

また、上記のゲート電圧遮断部としては、図2に示すように、抵抗R17、R18から成る分圧回路をPチャネル型MOS電界効果トランジスタP16で導通／遮断する構成とすることも可能である。ただし、このような構成を採用する場合には、抵抗R17、R18の抵抗値に比べて、トランジスタP16のオン抵抗値を十分に小さく設定する必要がある。しかしながら、抵抗R17、R18の抵抗値をトランジスタP16のオン抵抗値に比べて十分に大きく設定した場合には、分圧電圧Vaの応答速度が鈍ってしまうため、過渡的な動作が不安定となる。一方、トランジスタP16のオン抵抗値を抵抗R17、R18の抵抗値に比べて十分に小さく設定した場合には、トランジスタP16の占有面積が大きくなる。これに対して、図1に示すゲート電圧遮断部であれば、トランジスタP12、P13のオン抵抗値を必要に小さく設定する必要はなく、上記の課題は生じない。

20

## 【0040】

なお、上記のゲート電圧遮断部で生成される分圧電圧Vaは、電源電圧VCCを基準として、下記(1)式で表される。ただし、(1)式中のパラメータR(P12)、R(P13)は、それぞれ、トランジスタP12、P13のオン抵抗値を表している。

30

## 【0041】

## 【数1】

$$Va = \frac{R(P12)}{\{R(P12) + R(P13)\}} \cdot VG \quad \cdots \quad (1)$$

## 【0042】

上記(1)式からも分かるように、上記のゲート電圧遮断部では、ゲート電圧VGに応じて変動する分圧電圧Vaが生成される。

40

## 【0043】

一方、上記の閾値電圧生成部は、所定の閾値電圧Vbを生成し、これを電圧比較部の閾値電圧入力端(トランジスタP15のソース)に印加する。なお、閾値電圧Vbは、電源電圧VCCを基準として、下記(2)式で表される。ただし、(2)式中のパラメータR13、R14は、それぞれ、抵抗R13、R14の抵抗値を表しており、パラメータVrefは、直流電圧源E11の起電圧を表している。

## 【0044】

## 【数2】

$$V_b = -\frac{R_{13}}{R_{14}} \cdot V_{ref} \cdots (2)$$

## 【0045】

上記(2)式からも分かるように、上記の閾値電圧生成部では、電源電圧VCCよりも所定値だけ低い閾値電圧Vbが生成される。

## 【0046】

また、上記の電圧比較部は、カレントミラー回路を形成するトランジスタP14、P15の各ソースに分圧電圧Vaと閾値電圧Vbを各々印加して、カレントミラー回路の出力電流を出力部に送出する。より具体的に述べると、上記の電圧比較部は、ゲート電圧VGが何らかの原因で上昇して、分圧電圧Vaが閾値電圧Vb以上となったときに、トランジスタP14のドレインから出力電流を出力部に送出する。10

## 【0047】

なお、上記の電圧比較部としては、トランジスタP15を削除して、トランジスタP14のゲートに閾値電圧Vbを直接印加する構成とすることも可能である。ただし、このような構成では、分圧電圧Vaと閾値電圧Vbとの比較動作に、トランジスタP14のオンスレッショルド電圧Vthが関与するため、その製造ばらつきや温度特性の影響により、比較結果に変動を生じるおそれがある点に留意すべきである。これに対して、図1に示す電圧比較部であれば、分圧電圧Vaと閾値電圧Vbとの比較動作に、トランジスタP14のオンスレッショルド電圧が関与しないため、上記の課題は生じない。20

## 【0048】

また、上記の出力部は、電圧比較部の出力電流(トランジスタP14のドレイン電流)を電圧変換することで、スイッチ51の制御信号を生成する。より具体的に述べると、上記の出力部では、電圧比較部の出力電流を抵抗R12で受けることにより電圧信号Vcが生成され、これを用いてトランジスタN11のオン／オフ制御が行われる。すなわち、分圧電圧Vaが閾値電圧Vb以上となり、トランジスタP14のドレインから出力電流が出力部に送出されると、電圧信号Vcがハイレベルとなり、トランジスタN11がオンされる。その結果、スイッチ51の制御信号がローレベルとなってスイッチ51がオンされ、出力トランジスタTrのゲートと電源電圧VCCの印加端との間が導通されるので、ゲート電圧VGは、ほぼ電源電圧VCCにクランプされる。30

## 【0049】

上記したように、本実施形態のゲート駆動装置は、出力トランジスタTrのゲート電圧VG(図1ではゲート電圧VGの分圧電圧Va)と所定の閾値電圧Vbとの高低関係を検出する電圧検出回路41と、電圧検出回路41の検出結果に基づいて出力トランジスタTrのゲートと電源電圧VCCの印加端との間を導通／遮断するスイッチ51と、を有して成る構成とされている。

## 【0050】

このように、出力トランジスタTrのゲートと電源電圧VCCの印加端との間をショートするスイッチ51として、オン抵抗の低いMOS電界効果トランジスタを用いた構成であれば、ダイオードD1を用いた従来構成(図5(a)を参照)と異なり、スイッチ51に大電流が流れても、ゲート電圧VGの上昇を十分に抑えることができるので、出力トランジスタTrの耐圧破壊を防止することができる。また、ショットキーバリアダイオードSBD1を用いた従来構成(図5(b)を参照)と異なり、外付け部品を使用しないので、実装スペースや実装コストの増大を招くこともない。40

## 【0051】

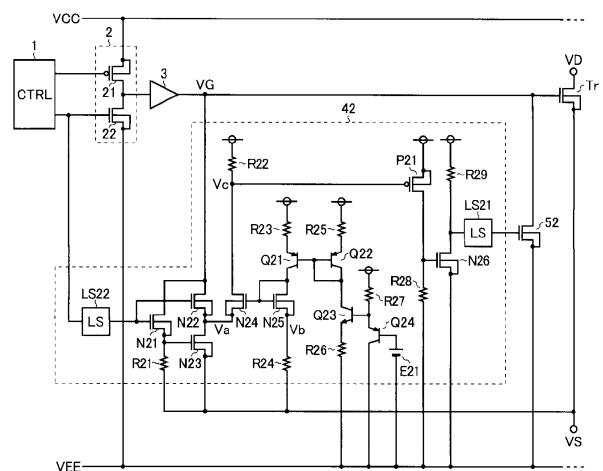

次に、本発明に係るゲート駆動装置の第2実施形態について、図3を参照しながら詳細に説明する。

## 【0052】

図3は、本発明に係るゲート駆動装置の第2実施形態を示す回路図である。

**【0053】**

図3に示す通り、本実施形態のゲート駆動装置は、先述の第1実施形態と同様、制御部1と、プリドライバ2と、バッファ3と、を有するほか、ゲート電圧VGのクランプ手段として、電圧検出回路42と、スイッチ(Nチャネル型MOS電界効果トランジスタ)52と、を有して成る。

**【0054】**

なお、制御部1、プリドライバ2、及び、バッファ3については、プリドライバ2を構成するトランジスタ22のソースが負電源電圧V<sub>EE</sub>(出力トランジスタTrのソース電圧VSよりも低い電源電圧)の印加端に接続されている点以外、第1実施形態と同様であるため、重複した説明は省略し、以下では、本実施形態の特徴部分である電圧検出回路42、及び、スイッチ52について、重点的に説明を行う。

**【0055】**

電圧検出回路42は、出力トランジスタTrのゲート電圧VGが所定の閾値電圧(VS+V<sub>th</sub>)以下であるか否かを検出し、その検出結果に応じてスイッチ52のオン/オフ制御を行う手段であり、Pチャネル型MOS電界効果トランジスタP21と、Nチャネル型MOS電界効果トランジスタN21~N26と、抵抗R21~R29と、pnp型バイポーラトランジスタQ21、Q22、Q24と、npp型バイポーラトランジスタQ23と、直流電圧源E21と、レベルシフタLS21、LS22と、を有して成る。

**【0056】**

トランジスタN21のソースは、抵抗R21を介して、出力トランジスタTrのソースに接続されている。トランジスタN21のドレインは、出力トランジスタTrのゲートに接続されている。トランジスタN21のゲートは、レベルシフタLS22を介して、制御部1の第2制御信号出力端に接続されている。トランジスタN21のバックゲートは、自身のソースに接続されている。トランジスタN22のソースは、トランジスタN23のドレインに接続されている。トランジスタN22のドレインは、出力トランジスタTrのゲートに接続されている。トランジスタN22のゲートは、レベルシフタLS22を介して制御部1の第2制御信号出力端に接続されている。トランジスタN22のバックゲートは自身のソースに接続されている。トランジスタN23のドレインは、出力トランジスタTrのソースに接続されている。トランジスタN23のゲートは、トランジスタN21のソースに接続されている。トランジスタN23のバックゲートは、自身のソースに接続されている。

**【0057】**

トランジスタN24のソースは、トランジスタN22のソースに接続されている。トランジスタN24のドレインは、抵抗R22を介して所定電圧の印加端に接続されている。トランジスタN24のゲートは、トランジスタN25のゲート及びドレインに接続されている。トランジスタN24のバックゲートは、自身のソースに接続されている。トランジスタN25のソースは、抵抗R24を介して、出力トランジスタTrのソースに接続されている。トランジスタN25のドレインは、トランジスタQ21のコレクタに接続されている。トランジスタN25のゲートは、自身のドレインに接続されている。トランジスタN25のバックゲートは、自身のソースに接続されている。

**【0058】**

トランジスタQ21のエミッタは、抵抗R23を介して、所定電圧の印加端に接続されている。トランジスタQ21のベースは、トランジスタQ22のベース及びコレクタに接続されている。トランジスタQ22のエミッタは、抵抗R25を介して、所定電圧の印加端に接続されている。トランジスタQ22のコレクタは、トランジスタQ23のコレクタに接続されている。トランジスタQ23のエミッタは、抵抗R26を介して、負電源電圧V<sub>EE</sub>の印加端に接続されている。トランジスタQ23のベースは、トランジスタQ24のエミッタに接続されている。トランジスタQ24のエミッタは、抵抗R27を介して所定電圧の印加端に接続されている。トランジスタQ24のコレクタは、負電源電圧V<sub>EE</sub>

10

20

30

40

50

の印加端に接続されている。トランジスタQ24のベースは、直流電圧源E21の正極端（基準電圧Vrefの印加端）に接続されている。直流電圧源E21の負極端は、負電源電圧VEEの印加端に接続されている。

#### 【0059】

トランジスタP21のドレインは、抵抗R28を介して負電源電圧VEEの印加端に接続されている。トランジスタP21のソースは、所定電圧の印加端に接続されている。トランジスタP21のゲートは、トランジスタN24のドレインに接続されている。トランジスタP21のバックゲートは、自身のソースに接続されている。トランジスタN26のドレインは、抵抗R29を介して所定電圧の印加端に接続される一方、レベルシフタLS21を介してスイッチ52を形成するトランジスタのゲートにも接続されている。トランジスタN26のソースは、負電源電圧VEEの印加端に接続されている。トランジスタN26のゲートは、トランジスタP21のドレインに接続されている。トランジスタN26のバックゲートは、自身のソースに接続されている。10

#### 【0060】

レベルシフタLS21、LS22は、それぞれ、先述のレベルシフタLS11と同様、入力信号の電圧レベルを適切にレベルシフトして出力する手段である。なお、レベルシフタLS21、LS22には、入力信号のレベルシフト機能のほか、必要に応じて入力信号の論理制御機能（例えば論理反転機能）を搭載しても構わない。

#### 【0061】

スイッチ52は、レベルシフタLS21から入力される制御信号に応じて、出力トランジスタTrのゲートと負電源電圧VEEの印加端との間を導通／遮断する手段である。なお、図3の例では、スイッチ512してNチャネル型MOS電界効果トランジスタが用いられており、ゲート駆動装置を集積化する場合にはこれをICに内蔵することができる。20

#### 【0062】

次に、ゲート電圧VGのクランプ動作について詳細な説明を行う。

#### 【0063】

上記構成から成るゲート駆動装置において、電圧検出回路42は、閾値電圧生成部（トランジスタQ21～Q23、抵抗R23～R27、並びに、直流電圧源E21）と、電圧比較部（トランジスタN24、及び、トランジスタN25）と、出力部（抵抗R22、抵抗R28、抵抗R29、トランジスタP21、トランジスタN26、及び、レベルシフタLS21）と、ゲート電圧遮断部（トランジスタN21～N23、抵抗R21、及び、レベルシフタLS22）と、を有して成る。30

#### 【0064】

上記のゲート電圧遮断部において、トランジスタN21～N23は、いずれも、制御部1から入力される第2制御信号がハイレベルとされたときにオンとなり、第2制御信号がローレベルとされたときにオフとなる。

#### 【0065】

すなわち、上記のゲート電圧遮断部は、制御部1から入力される第2制御信号に基づいて、ゲート電圧VGがローレベルとされるときには、出力トランジスタTrのゲートと電圧比較部のゲート電圧入力端（トランジスタN24のソース）との間を導通し、ゲート電圧VGの分圧電圧Vaを電圧比較部のゲート電圧入力端に印加する一方、ゲート電圧VGがハイレベルとされるときには、出力トランジスタTrのゲートと電圧比較部のゲート電圧入力端との間を遮断し、電圧比較部のゲート電圧入力端をオープンとする。40

#### 【0066】

このように、上記のゲート電圧遮断部であれば、出力トランジスタTrのゲート電圧VGがハイレベルとされるときに、電圧比較部のゲート電圧入力端をオープンとすることができますので、トランジスタN24、N25のゲート酸化物が耐圧破壊されるのを防止することが可能となる。

#### 【0067】

また、上記のゲート電圧遮断部であれば、出力トランジスタTrのゲート電圧VGを監

50

視する必要のあるとき（ゲート電圧  $V_G$  がローレベルとされているとき）にのみ、ゲート電圧  $V_G$  の分圧経路を導通させることができるので、定常的に電流を浪費せずに済む。

#### 【0068】

ただし、電源電圧  $V_{CC}$  の定格電圧がトランジスタ N24、N25 のゲート耐圧よりも低い場合には、ゲート電圧遮断部を削除し、出力トランジスタ Tr のゲートを電圧比較部のゲート電圧入力端に直接接続しても構わない。

#### 【0069】

また、上記のゲート電圧遮断部としては、トランジスタ N21 を削除し、制御部 1 から入力される第 2 制御信号をトランジスタ N22、N23 の各ゲートに直接入力する構成とすることも可能である。ただし、このような構成では、第 2 制御信号がハイレベルとされたとき、先にトランジスタ N23 がオンし、次いでトランジスタ N23 がオンする形となる。このように、トランジスタ N22、N23 のオンタイミングにずれが生じると、分圧電圧  $V_a$  は、一旦出力トランジスタ Tr のソース電圧  $V_S$  付近まで低下してしまうため、分圧電圧  $V_a$  を電圧比較部に直接入力すると、誤ったクランプ動作が行われてしまう。そのため、トランジスタ N21 を用いない場合には、分圧電圧  $V_a$  の瞬間的な低下をキャンセルする手段として、何らかのマスク回路が必要となる点に留意すべきである。10

#### 【0070】

これに対して、図 3 に示すゲート電圧遮断部であれば、トランジスタ N21 を用いてトランジスタ N23 がダーリントン接続とされており、第 2 制御信号がハイレベルとされたときには、トランジスタ N22 がオンし得る状態になってから、トランジスタ N23 がオンする形となるので、トランジスタ N22、N23 のオンタイミングを一致させることができ、延いては、分圧電圧  $V_a$  の瞬間的な低下を回避することが可能となる。20

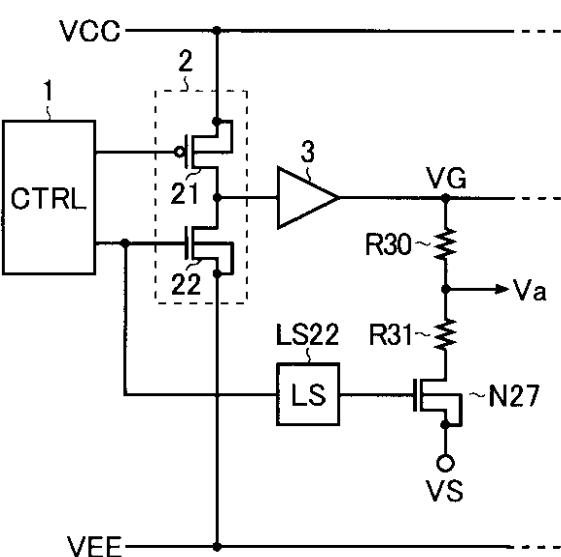

#### 【0071】

また、上記のゲート電圧遮断部としては、図 4 に示すように、抵抗 R30、R31 から成る分圧回路を N チャネル型 MOS 電界効果トランジスタ N27 で導通 / 遮断する構成とすることも可能である。ただし、このような構成を採用する場合には、抵抗 R30、R31 の抵抗値に比べて、トランジスタ N27 のオン抵抗値を十分に小さく設定する必要がある。しかしながら、抵抗 R30、R31 の抵抗値をトランジスタ N27 のオン抵抗値に比べて十分に大きく設定した場合には、分圧電圧  $V_a$  の応答速度が鈍ってしまうため、過渡的な動作が不安定となる。一方、トランジスタ N27 のオン抵抗値を抵抗 R30、R31 の抵抗値に比べて十分に小さく設定した場合には、トランジスタ N27 の占有面積が大きくなる。これに対して、図 3 に示すゲート電圧遮断部であれば、トランジスタ N22、N23 のオン抵抗値を必要に小さく設定する必要はなく、上記の課題は生じない。30

#### 【0072】

なお、上記のゲート電圧遮断部で生成される分圧電圧  $V_a$  は、出力トランジスタ Tr のソース電圧  $V_S$  を基準として、下記(3)式で表される。ただし、(3)式中のパラメータ  $R(N22)$ 、 $R(N23)$  は、それぞれ、トランジスタ N22、N23 のオン抵抗値を表している。

#### 【0073】

#### 【数 3】

$$V_a = \frac{R(N23)}{\{R(N22) + R(N23)\}} \cdot V_G \quad \cdots \quad (3)$$

#### 【0074】

上記(3)式からも分かるように、上記のゲート電圧遮断部では、ゲート電圧  $V_G$  に応じて変動する分圧電圧  $V_a$  が生成される。

#### 【0075】

一方、上記の閾値電圧生成部は、所定の閾値電圧  $V_b$  を生成し、これを電圧比較部の閾値電圧入力端（トランジスタ N25 のソース）に印加する。なお、閾値電圧  $V_b$  は、出力4050

トランジスタ T<sub>r</sub> のソース電圧 V<sub>S</sub> を基準として、下記の(4)式で表される。ただし、(4)式中のパラメータ R<sub>24</sub>、R<sub>26</sub> は、それぞれ、抵抗 R<sub>24</sub>、R<sub>26</sub> の抵抗値を表しており、パラメータ V<sub>ref</sub> は、直流電圧源 E<sub>21</sub> の起電圧を表している。

#### 【0076】

##### 【数4】

$$V_b = \frac{R_{24}}{R_{26}} \cdot V_{ref} \quad \dots \quad (4)$$

#### 【0077】

10

上記(4)式からも分かるように、上記の閾値電圧生成部では、出力トランジスタ T<sub>r</sub> のソース電圧 V<sub>S</sub> よりも所定値だけ高い閾値電圧 V<sub>b</sub> が生成される。

#### 【0078】

また、上記の電圧比較部は、カレントミラー回路を形成するトランジスタ N<sub>24</sub>、N<sub>25</sub> の各ソースに分圧電圧 V<sub>a</sub> と閾値電圧 V<sub>b</sub> を各々印加して、カレントミラー回路の出力電流を出力部に送出する。より具体的に述べると、上記の電圧比較部は、出力トランジスタ T<sub>r</sub> のオフ時にゲート電圧 V<sub>G</sub> をローレベルとする際、分圧電圧 V<sub>a</sub> が閾値電圧 V<sub>b</sub> 以下まで低下したことを検出して、トランジスタ N<sub>24</sub> のドレイン電流を引き込む。

#### 【0079】

20

なお、上記の電圧比較部としては、トランジスタ N<sub>25</sub> を削除して、トランジスタ N<sub>24</sub> のゲートに閾値電圧 V<sub>b</sub> を直接印加する構成とすることも可能である。ただし、このような構成では、分圧電圧 V<sub>a</sub> と閾値電圧 V<sub>b</sub> との比較動作に、トランジスタ N<sub>24</sub> のオンスレッショルド電圧 V<sub>th</sub> が関与するため、その製造ばらつきや温度特性の影響により、比較結果に変動を生じるおそれがある点に留意すべきである。これに対して、図 3 に示す電圧比較部であれば、分圧電圧 V<sub>a</sub> と閾値電圧 V<sub>b</sub> との比較動作に、トランジスタ N<sub>24</sub> のオンスレッショルド電圧が関与しないため、上記の課題は生じない。

#### 【0080】

また、上記の出力部は、電圧比較部の出力電流（トランジスタ N<sub>24</sub> のドレイン電流）を電圧変換することで、スイッチ S<sub>2</sub> の制御信号を生成する。より具体的に述べると、上記の出力部では、電圧比較部の出力電流を抵抗 R<sub>22</sub> で受けることによって電圧信号 V<sub>c</sub> が生成され、これを用いてトランジスタ P<sub>21</sub> のオン／オフ制御、延いては、トランジスタ N<sub>26</sub> のオン／オフ制御が行われる。すなわち、分圧電圧 V<sub>a</sub> が閾値電圧 V<sub>b</sub> 以下となり、トランジスタ N<sub>24</sub> のドレイン電流が引き込まれると、電圧信号 V<sub>c</sub> がローレベルとなり、トランジスタ P<sub>21</sub> がオンされ、引き続いて、トランジスタ N<sub>26</sub> がオンされる。レベルシフタ L<sub>S21</sub> は、トランジスタ N<sub>26</sub> のドレインから引き出されるローレベルの電圧信号を論理反転するとともに、その電圧レベルを適切に調整してスイッチ S<sub>2</sub> の制御信号を生成する。その結果、スイッチ S<sub>2</sub> の制御信号がハイレベルとなってスイッチ S<sub>2</sub> がオンされ、出力トランジスタ T<sub>r</sub> のゲートと負電源電圧 V<sub>EE</sub> の印加端との間が導通されるので、ゲート電圧 V<sub>G</sub> は、ほぼ負電源電圧 V<sub>EE</sub> にクランプされる。

30

#### 【0081】

40

上記したように、本実施形態のゲート駆動装置は、出力トランジスタ T<sub>r</sub> のゲート電圧 V<sub>G</sub>（図 1 ではゲート電圧 V<sub>G</sub> の分圧電圧 V<sub>a</sub>）と所定の閾値電圧 V<sub>b</sub> との高低関係を検出する電圧検出回路 4<sub>2</sub> と、電圧検出回路 4<sub>2</sub> の検出結果に基づいて出力トランジスタ T<sub>r</sub> のゲートと負電源電圧 V<sub>EE</sub> の印加端との間を導通／遮断するスイッチ S<sub>2</sub> と、を有して成る構成とされている。

#### 【0082】

このような構成とすることにより、出力トランジスタ T<sub>r</sub> をオフすべきときには、出力トランジスタ T<sub>r</sub> のゲート電圧 V<sub>S</sub> を負電源電圧 V<sub>EE</sub> に引き落としておくことができる。トランジスタ T<sub>r</sub> のゲート電圧 V<sub>S</sub> にノイズが重畠した場合であっても、出力トランジスタ T<sub>r</sub> の誤オンを防止することができる。

50

**【0083】**

なお、電圧検出回路42としては、負電源電圧V<sub>EE</sub>に対するゲート電圧V<sub>G</sub>を検出することで、スイッチ52のオン／オフ制御を行う構成とすることも可能である。ただし、このような構成では、ゲート電圧V<sub>G</sub>がソース電圧V<sub>S</sub>よりも低くなつてからスイッチ52がオンすることになるため、出力トランジスタTrのオフスピードが遅くなつてしまつ点に留意が必要である。

**【0084】**

これに対して、本実施形態のゲート駆動装置であれば、ソース電圧V<sub>S</sub>に対するゲート電圧V<sub>S</sub>を検出することで、スイッチ52のオン／オフ制御が行われるため、ゲート電圧V<sub>G</sub>がソース電圧V<sub>S</sub>よりも高い状態で、出力トランジスタTrのゲートと負電源電圧V<sub>EE</sub>の印加端との間をショートすることが可能となる。すなわち、本実施形態のゲート駆動装置であれば、負電源電圧V<sub>EE</sub>をどのような電圧レベルに設定した場合でも、スイッチ52がオンするタイミングは、常に出力トランジスタTrのゲート・ソース間電圧で決まるので、出力トランジスタTrを素早くオフすることが可能となる。10

**【0085】**

なお、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。

**【産業上の利用可能性】****【0086】**

本発明は、モータドライバやスイッチングレギュレータに含まれる出力トランジスタのゲート電圧を駆動するゲート駆動装置全般に広く利用可能な技術であり、これを適用可能なアプリケーションとしては、ハイブリッド自動車、電気自動車、家電機器、産業機器などを挙げることができる。20

**【図面の簡単な説明】****【0087】**

【図1】は、本発明に係るゲート駆動装置の第1実施形態を示す回路図である。

【図2】は、ゲート電圧遮断部の一変形例を示す回路図である。

【図3】は、本発明に係るゲート駆動装置の第2実施形態を示す回路図である。

【図4】は、ゲート電圧遮断部の一変形例を示す回路図である。

【図5】は、ゲート駆動装置の一従来例を示す回路図である。30

**【符号の説明】****【0088】**

- |                             |                      |  |  |

|-----------------------------|----------------------|--|--|

| 1                           | 制御部                  |  |  |

| 2                           | プリドライバ               |  |  |

| 2 1                         | Pチャネル型MOS電界効果トランジスタ  |  |  |

| 2 2                         | Nチャネル型MOS電界効果トランジスタ  |  |  |

| 3                           | バッファ                 |  |  |

| 4 1、4 2                     | 電圧検出回路               |  |  |

| 5 1、5 2                     | スイッチ                 |  |  |

| P 1 1 ~ P 1 6、P 2 1         | Pチャネル型MOS電界効果トランジスタ  |  |  |

| N 1 1、N 2 1 ~ N 2 7         | Nチャネル型MOS電界効果トランジスタ  |  |  |

| Q 1 1、Q 2 3                 | n p n型バイポーラトランジスタ    |  |  |

| Q 1 2、Q 2 1、Q 2 2、Q 2 4     | p n p型バイポーラトランジスタ    |  |  |

| R 1 1 ~ R 1 8、R 2 1 ~ R 3 1 | 抵抗                   |  |  |

| E 1 1、E 2 1                 | 直流電圧源                |  |  |

| L S 1 1、L S 2 1、L S 2 2     | レベルシフタ               |  |  |

| T r                         | 出力トランジスタ(FET、IGBTなど) |  |  |

10203040

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開平02-262822(JP,A)

特開平10-224196(JP,A)

特開平02-298067(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00 - 17/70