(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7688965号

(P7688965)

(45)発行日 令和7年6月5日(2025.6.5)

(24)登録日 令和7年5月28日(2025.5.28)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3233(2016.01) | F I | G 0 9 G | 3/3233       |

| G 0 9 F | 9/30 (2006.01)  |     | G 0 9 F | 9/30 3 4 9 C |

| G 0 9 F | 9/302(2006.01)  |     | G 0 9 F | 9/30 3 6 5   |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 F | 9/302 Z      |

|         |                 |     | G 0 9 G | 3/20 6 4 1 D |

請求項の数 7 (全22頁) 最終頁に続く

(21)出願番号 特願2020-125352(P2020-125352)

(22)出願日 令和2年7月22日(2020.7.22)

(65)公開番号 特開2022-21644(P2022-21644A)

(43)公開日 令和4年2月3日(2022.2.3)

審査請求日 令和5年7月19日(2023.7.19)

(73)特許権者 520272868

武漢天馬微電子有限公司

中華人民共和国武漢市東湖新技術開発区

流芳園横路8号

(74)代理人 110001678

藤央弁理士法人

松枝 洋二郎

(72)発明者 神奈川県川崎市幸区鹿島田一丁目1番2号 Tianma Japan 株式会社内

下田 雅通

神奈川県川崎市幸区鹿島田一丁目1番2号 Tianma Japan 株式会社内

(72)発明者 武田 悟

審査官

最終頁に続く

(54)【発明の名称】 表示装置

## (57)【特許請求の範囲】

## 【請求項1】

外部から入力された画像データの画像を表示する、複数の表示画素を含む表示領域と、前記表示領域の外側に配置された複数のダミー画素と、

視認側において前記複数のダミー画素を覆う1又は複数の遮光膜と、

前記表示領域及び前記複数のダミー画素を制御する制御回路と、

を含み、

前記表示領域は、

第1領域と、

表示画素密度が前記第1領域より小さい、第2領域と、

を含み、

前記第2領域の全表示画素のそれぞれは、前記複数のダミー画素の同一色の1つのダミー画素に対応付けられ、

前記複数の表示画素及び前記複数のダミー画素は、それぞれ、駆動電流に応じて発光する発光素子を含み、

前記制御回路は、

画像データの同一階調レベルに対して、前記第2領域の表示画素に対して前記第1領域の表示画素よりも大きい駆動電流を与え、

前記画像データの表示動作において、前記複数のダミー画素の各ダミー画素に、対応付けられた前記第2領域の同一色の表示画素の画像データの駆動電流と同一の駆動電流を与

え、

劣化測定動作において、前記複数のダミー画素の各ダミー画素に、対応付けられた前記第2領域の同一色の表示画素の画像データの駆動電流の値と独立した値を有する、劣化測定のための駆動電流を与えて、前記複数のダミー画素の各ダミー画素の発光素子のアノードとカソードとの間の抵抗値を測定することによって劣化の測定を行い、

前記測定の結果に基づいて、前記複数のダミー画素それぞれに関連づけられている前記第2領域の表示画素へのデータ信号を補正する、

表示装置。

**【請求項2】**

請求項1に記載の表示装置であって、

前記表示領域の視認側に配置されたタッチスクリーンをさらに含み、

前記タッチスクリーンは、透明な電極片を接続する遮光性の導体膜を含み、

前記1又は複数の遮光膜は、前記遮光性の導体膜と同層に形成されている、

表示装置。

**【請求項3】**

請求項1に記載の表示装置であって、

前記複数の遮光膜を含み、

前記複数の遮光膜の各遮光膜は、前記複数のダミー画素における1以上のダミー画素を前記視認側において覆う、

表示装置。

10

**【請求項4】**

請求項1に記載の表示装置であって、

前記複数のダミー画素の各ダミー画素は、前記表示領域の表示画素行を選択する走査線に接続されている、

表示装置。

20

**【請求項5】**

請求項1に記載の表示装置であって、

前記制御回路は、測定対象の1以上のダミー画素の劣化の測定の間、他の全てのダミー画素の発光を停止する、

表示装置。

30

**【請求項6】**

請求項1に記載の表示装置であって、

前記制御回路は、測定対象の1以上のダミー画素の劣化の測定の間、前記測定対象の1以上のダミー画素の画素回路に対して最高輝度を示すデータ信号を与える、

表示装置。

**【請求項7】**

請求項1に記載の表示装置と、

前記第2領域の下に配置された1以上のカメラと、

を含む、端末。

**【発明の詳細な説明】**

40

**【技術分野】**

**【0001】**

本開示は、表示装置に関する。

**【背景技術】**

**【0002】**

OLEO (Organic Light-Emitting Diode) 素子は電流駆動型の自発光素子であるため、バックライトが不要となる上に、低消費電力、高視野角、高コントラスト比が得られるなどのメリットがあり、フラットパネルディスプレイの開発において期待されている。

**【0003】**

50

OLED表示装置の表示領域が、画素密度が異なる領域を含むことがある。例えば、いくつかのスマートフォンやタブレット型コンピュータなどの携帯端末において、表示領域の下に画像撮像用のカメラが配置される。カメラが外部からの光を受光するために、カメラは、周囲よりも画素密度が小さい領域の下に配置される。

【先行技術文献】

【特許文献】

【0004】

【文献】米国特許出願公開第2018/0357952号

【文献】米国特許出願公開第2005/0030214号

【文献】米国特許出願公開第2018/0182816号

10

【発明の概要】

【発明が解決しようとする課題】

【0005】

表示領域における画像の表示品質の低下を抑制するため、相対的に画素密度が小さい領域における画素単位の輝度は、相対的に画素密度が大きい通常領域の画素単位の輝度よりも大きくする必要がある。OLED素子は電流駆動型の素子であるため、画素密度が小さい領域の画素には、画素密度が大きい通常領域の画素よりも多くの電流が供給される。このため、相対的に画素密度が小さい領域の画素の劣化は、相対的に画素密度が大きい領域の画素よりも早く進む。これは、他の電流駆動型素子を使用する表示装置においても同様である。

20

【0006】

表示領域の全ての画素は表示時間の経過と共に劣化する。そのため、表示装置は、画素それぞれの劣化を見積り、それに応じて輝度の補正を行う。しかし、劣化速度が速くなると正確な劣化の見積りはより困難となり、補正精度が低くなる。したがって、相対的に画素密度が小さい領域と大きい領域とを含む表示装置において、表示品質の低下を抑制する技術が望まれる。

【課題を解決するための手段】

【0007】

本開示の一態様の表示装置は、外部から入力された画像データの画像を表示する、複数の表示画素を含む表示領域と、前記表示領域の外側に配置された複数のダミー画素と、視認側において前記複数のダミー画素を覆う1又は複数の遮光膜と、前記表示領域及び前記複数のダミー画素を制御する制御回路と、を含む。前記表示領域は、第1領域と、表示画素密度が前記第1領域よりも小さい、第2領域と、を含む。前記複数のダミー画素の各ダミー画素は、前記第2領域に配置された表示画素に対応付けられる。前記複数の表示画素及び前記複数のダミー画素は、それぞれ、駆動電流に応じて発光する発光素子を含む。前記制御回路は、画像データの同一階調レベルに対して、前記第2領域の表示画素に対して前記第1領域の表示画素よりも大きい駆動電流を与え、前記複数のダミー画素の各ダミー画素に、前記対応付けられた前記第2領域の表示画素と同一のデータ信号を与え、前記複数のダミー画素の各ダミー画素の発光素子の劣化の測定を行い、前記測定の結果に基づいて、前記複数のダミー画素それぞれに関連づけられている前記第2領域の表示画素へのデータ信号を補正する。

30

【発明の効果】

【0008】

本開示の一態様によれば、表示装置の表示品質の低下を抑制することができる。

【図面の簡単な説明】

【0009】

【図1】OLED表示装置の構成例を模式的に示す。

【図2A】画素回路の構成例を示す。

【図2B】画素回路の他の構成例を示す。

【図3】TFT基板の基板、駆動TFT及びOLED素子、並びに、封止構造部の断面構

40

50

造を模式的に示す。

【図4】表示領域及び表示領域外に配置されたダミー画素を模式的に示す。

【図5】図4において一点鎖線で囲まれた領域の詳細を示す。

【図6】図4において一点鎖線で囲まれた領域のダミー画素レイアウトを示す。

【図7】タッチスクリーンに形成されている、遮光パターン及びタッチ電極パターンの例を示す平面図である。

【図8】TFT基板上の制御配線のレイアウトを模式的に示し、

【図9】TFT基板上のアノード電源線及びカソード電極のレイアウトを模式的に示す。

【図10】通常領域及び低密度領域の副画素へのデータ信号電圧と、OLED素子の発光輝度と、の関係を模式的に示すグラフである。

10

【図11】ダミー副画素の画素回路の構成例を示す。

【図12】通常動作におけるダミー副画素に対する信号のタイミングチャートの例を示す。

【図13】ダミー副画素のOLED素子の劣化測定動作における信号のタイミングチャートを示す。

【発明を実施するための形態】

【0010】

以下、添付図面を参照して本開示の実施形態を説明する。本実施形態は本開示を実現するための一例に過ぎず、本開示の技術的範囲を限定するものではないことに注意すべきである。

【0011】

以下の説明において、画素は、表示領域における最小単位であり、単一色の光を発光する要素を示し、副画素とも呼ばれることがある。複数の異なる色の画素、例えば、赤、青及び緑の画素のセットが、一つのカラードットを表示する要素を構成し、主画素と呼ばれることがある。以下において、説明の明確化のために単一色表示を行う要素とカラー表示を行う要素を区別する場合に、それぞれ、副画素及び主画素と呼ぶ。なお、本明細書の特徴は、モノクロ表示を行う表示装置に適用することができ、その表示領域はモノクロ画素で構成されている。

20

【0012】

以下において、表示装置の構成例を説明する。表示装置の表示領域は、相対的に画素密度が小さい第2領域（低密度領域とも呼ぶ）と、相対的に画素密度が大きい第1領域（通常領域とも呼ぶ）とを含む。表示領域における画像の表示品質の低下を抑制するため、同一の画像データの階調レベルに対して、低密度領域における画素の輝度は、通常領域の画素の輝度より大きくなるように制御される。なお、通常領域よりも画素密度が低い複数の低密度領域が配置されてもよく、これらの画素密度が異なっていてもよい。

30

【0013】

以下に説明する例において、画素の発光素子は電流駆動型の素子であり、例えば、OLED (Organic Light-Emitting Diode) 素子である。従って、同一階調レベルの画像データに対して、低密度領域の画素には、通常領域の画素よりも多くの電流が供給される。このため、低密度領域の画素の劣化は、通常領域の画素よりも早く進む。画素は表示時間の経過と共に劣化する。表示装置は、画素それぞれの劣化を見積り、それに応じて輝度の補正を行うことができる。しかし、劣化速度が速くなると、画素の正確な劣化の見積りはより難しくなり、補正精度が低くなり得る。

40

【0014】

以下に説明する表示装置は、低密度領域内の画素に対応し、表示領域外に配置された、ダミー画素を含む。ダミー画素は、対応する画素と同様の輝度で発光するように制御される。ダミー画素は、視認側において、遮光膜に覆われている。これにより、ダミー画素がユーザに視認されることを防ぐことができる。

【0015】

ダミー画素は、劣化測定用画素である。表示装置は、ダミー画素の発光素子の劣化の度合いを測定し、その測定結果を、低密度領域内の対応画素の輝度の補正制御にフィードバ

50

ックする。画像の表示と関わりのないダミー画素の劣化を測定することで、画像表示への影響を避けつつ、低密度領域内の画素の輝度補正をより適切に行うことができる。

#### 【0016】

##### 【表示装置の構成】

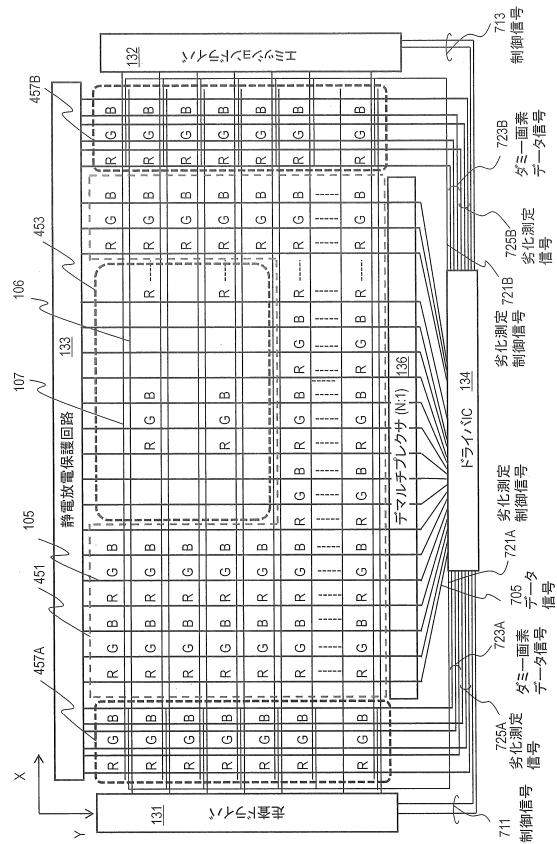

図1を参照して、本実施形態に係る、表示装置の全体構成を説明する。なお、説明をわかりやすくするため、図示した物の寸法、形状については、誇張して記載している場合もある。以下において、表示装置の例として、OLED表示装置を説明する。

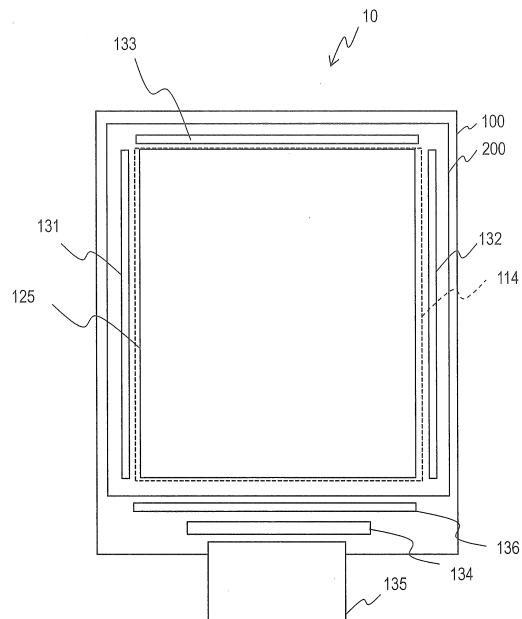

#### 【0017】

図1は、OLED表示装置10の構成例を模式的に示す。OLED表示装置10は、OLED素子(発光素子)が形成されるTFT (Thin Film Transistor) 基板100と、OLED素子を封止する封止構造部200を含んで構成されている。TFT基板100の表示領域125の外側のカソード電極形成領域114の周囲に、制御回路が配置されている。具体的には、走査ドライバ131、エミッションドライバ132、静電気放電保護回路133、ドライバIC134、デマルチプレクサ136が配置されている。

10

#### 【0018】

ドライバIC134は、FPC (Flexible Printed Circuit) 135を介して外部の機器と接続される。走査ドライバ131はTFT基板100の走査線を駆動する。エミッションドライバ132は、エミッショントラニジスタの制御線を駆動して、各画素の発光を制御する。静電気放電保護回路133は、TFT基板における素子の静電破壊を防ぐ。ドライバIC134は、例えば、異方性導電フィルム(ACF: Anisotropic Conductive Film)を用いて実装される。

20

#### 【0019】

ドライバIC134は、走査ドライバ131及びエミッションドライバ132に電源、及び、タイミング信号を含む制御信号を与える。さらに、ドライバIC134は、デマルチプレクサ136に、電源及びデータ信号を与える。デマルチプレクサ136は、ドライバIC134の一つのピンの出力を、d本(dは2以上の整数)のデータ線に順次出力する。デマルチプレクサ136は、ドライバIC134からのデータ信号の出力先データ線を、走査期間内にd回切り替えることで、ドライバIC134の出力ピン数のd倍のデータ線を駆動する。

30

#### 【0020】

##### 【画素回路構成】

TFT基板100上には、複数の副画素のアノード電極にそれぞれ供給する電流を制御する複数の画素回路が形成されている。図2Aは、画素回路の構成例を示す。各画素回路は、駆動トランジスタT1と、選択トランジスタT2と、エミッショントランジスタT3と、保持容量C1とを含む。画素回路は、OLED素子E1の発光を制御する。トランジスタは、TFTである。

#### 【0021】

選択トランジスタT2は副画素を選択するスイッチである。選択トランジスタT2はpチャネル型TFTであり、ゲート端子は、走査線106に接続されている。ソース端子は、データ線105に接続されている。ドレイン端子は、駆動トランジスタT1のゲート端子に接続されている。

40

#### 【0022】

駆動トランジスタT1はOLED素子E1の駆動用のトランジスタ(駆動TFT)である。駆動トランジスタT1はpチャネル型TFTであり、そのゲート端子は選択トランジスタT2のドレイン端子に接続されている。駆動トランジスタT1のソース端子は電源電位VDDを伝送する電源線108に接続されている。ドレイン端子は、エミッショントランジスタT3のソース端子に接続されている。駆動トランジスタT1のゲート端子とソース端子との間に保持容量C1が形成されている。

#### 【0023】

50

エミッショントランジスタT3は、OLED素子E1への駆動電流の供給と停止を制御するスイッチである。エミッショントランジスタT3はpチャネル型TFTであり、ゲート端子はエミッショントランジスタT3のソース端子は駆動トランジスタT1のドレイン端子に接続されている。エミッショントランジスタT3のドレイン端子は、OLED素子E1に接続されている。OLED素子E1のカソードにはカソード電源電位VSSが与えられている。

#### 【0024】

次に、画素回路の動作を説明する。走査ドライバ131が走査線106に選択パルスを出力し、選択トランジスタT2をオン状態にする。データ線105を介してドライバIC134から供給されたデータ電圧は、保持容量C1に格納される。保持容量C1は、格納された電圧を、1フレーム期間を通じて保持する。保持電圧によって、駆動トランジスタT1のコンダクタンスがアナログ的に変化し、駆動トランジスタT1は、発光階調に対応した順バイアス電流をOLED素子E1に供給する。

10

#### 【0025】

エミッショントランジスタT3は、駆動電流の供給経路上に位置する。エミッションドライバ132は、エミッショントランジスタT3のオンオフを制御する。エミッショントランジスタT3がオン状態のとき、駆動電流がOLED素子E1に供給される。エミッショントランジスタT3がオフ状態のとき、この供給が停止される。エミッショントランジスタT3のオンオフを制御することにより、1フレーム周期内の点灯期間（デューティ比）を制御することができる。

20

#### 【0026】

図2Bは、画素回路の他の構成例を示す。当該画素回路は、図2AのエミッショントランジスタT3に代えて、リセットトランジスタT4を有する。リセットトランジスタT4は、基準電圧供給線110とOLED素子E1のアノードとの電気的接続を制御する。リセットトランジスタT4のゲートにリセット制御線109からリセット制御信号が供給されることによりこの制御が行われる。

#### 【0027】

リセットトランジスタT4は、様々な目的で使用することができる。リセットトランジスタT4は、例えば、OLED素子E1間のリーク電流によるクロストークを抑制するために、一旦、OLED素子E1のアノード電極を黒信号レベル以下の十分低い電圧にリセットする目的で使用してもよい。

30

#### 【0028】

図2A及び2Bの画素回路は例であって、画素回路は他の回路構成を有してよい。図2A及び2Bの画素回路はpチャネル型TFTを使用しているが、画素回路はnチャネル型TFTを使用してもよい。

#### 【0029】

##### [OLED表示装置の断面構造]

以下において、OLED表示装置の構造を説明する。図3は、TFT基板100の基板、駆動TFT及びOLED素子、並びに、封止構造部200の断面構造を模式的に示す。基板は例えばフレキシブル基板であり、リジッド基板であってもよい。以下の説明において、上下は、図面における上下を示す。なお、封止構造部200は、封止基板を使用してもよい。

40

#### 【0030】

OLED表示装置は、TFT基板100及び封止構造部200を含む。TFT基板100は、基板202並びにフレキシブル基板上に構成された画素回路（TFTアレイ）及びOLED素子を含む。画素回路及びOLED素子は基板202と封止構造部200との間に構成される。

#### 【0031】

基板202は、有機物層、例えばポリイミド層、及び無機物層、例えばシリコン酸化物層やシリコン窒化物層、を含む複数の層で構成されたフレキシブル基板である。基板20

50

2上に、画素回路（TFTアレイ）及びOLED素子が形成されている。OLED素子は、下部電極（例えば、アノード電極308）と、上部電極（例えば、カソード電極302）と、有機発光多層膜304とを含む。カソード電極302とアノード電極308との間に、有機発光多層膜304が配置されている。複数のアノード電極308は、同一面上（例えば、平坦化膜321の上）に配置され、1つのアノード電極308の上に1つの有機発光多層膜304が配置されている。図3の例において、一つの副画素のカソード電極302は、連続する導体膜の一部である。

#### 【0032】

図3は、トップエミッション型（OLED素子）の画素構造の例である。トップエミッション型の画素構造は、光が出射する側（図面上側及び視認側）に、複数の画素に共通のカソード電極302が配置される。カソード電極302は、表示領域125の全面を覆う形状を有する。トップエミッション型の画素構造において、アノード電極308は光を反射し、カソード電極302は光透過性をもっている。これにより、有機発光多層膜304からの光を封止構造部200に向けて出射させる構成となっている。

10

#### 【0033】

トップエミッション型では、光を基板202側に取り出すボトムエミッション型と比べて、光取り出しのための透過領域を画素領域内に設ける必要がないため、発光部を画素回路や配線の上にも形成することができるといった、画素回路のレイアウトにおいて高い自由度を有する。

20

#### 【0034】

なお、ボトムエミッション型の画素構造は、透明アノード電極と反射カソード電極を有し、基板を介して外部（視認側）に光を出射する。また、アノード電極とカソード電極の双方を光透過性材料で形成することで透明表示装置を実現することもできる。本開示のフレキシブル基板構造は、これらのうちの任意の型のOLED表示装置にも適用でき、さらには、OLEDと異なる発光素子を含む表示装置に適用できる。

30

#### 【0035】

副画素は、フルカラーOLED表示装置において一般に、赤、緑、又は青のいずれかの色を表示する。赤、緑、及び青の副画素により一つの主画素が構成される。複数の薄膜トランジスタを含む画素回路は、対応するOLED素子の発光を制御する。OLED素子は、下部電極であるアノード電極、有機発光層、及び上部電極であるカソード電極で構成される。

30

#### 【0036】

OLED表示装置は、それぞれが複数のスイッチを含む複数の画素回路（TFTアレイ）を有する。複数の画素回路の各々は、フレキシブル基板202とアノード電極308との間に形成され、複数のアノード電極308の各々に供給する電流を制御する。図3に示す駆動TFTは、トップゲート構造を有する。他のTFTも同様に、トップゲート構造を有する。

40

#### 【0037】

ポリシリコン層が、基板202上に存在している。ポリシリコン層にはTFTのトランジスタ特性をもたらすチャネル315が、のちにゲート電極314が形成される位置に存在する。その両端には上部の配線層と電気的に接続をとるために高濃度不純物がドープされたソース／ドレイン領域316、317が存在する。

40

#### 【0038】

チャネル315とソース／ドレイン領域316、317の間には、低濃度の不純物をドープされたLDD（Lightly Doped Drain）を形成する場合もある。なお、LDDについては、煩雑になるため図示を省略している。ポリシリコン層の上には、ゲート絶縁膜323を介して、ゲート電極314が形成されている。ゲート電極314の層上に層間絶縁膜322が形成されている。

#### 【0039】

表示領域125内において、層間絶縁膜322上にソース／ドレイン電極310、31

50

2が形成されている。ソース／ドレイン電極310、312は、層間絶縁膜322及びゲート絶縁膜323に形成されたコンタクトホール311、313を介してポリシリコン層のソース／ドレイン領域316、317に接続されている。

#### 【0040】

ソース／ドレイン電極310、312の上に、絶縁性の有機平坦化膜321が形成される。平坦化膜321の上に、アノード電極308が形成されている。アノード電極308は、平坦化膜321のコンタクトホール309を介してソース／ドレイン電極312に接続されている。画素回路のTFTは、アノード電極308の下側に形成されている。

#### 【0041】

アノード電極308は、例えば、中央の反射金属層と反射金属層を挟む透明導電層で構成される。アノード電極308の上に、OLED素子を分離する絶縁性の画素定義層（Pixel Defining Layer: PDL）307が形成されている。OLED素子は、画素定義層307の開口306に形成されている。

10

#### 【0042】

アノード電極308の上に、有機発光多層膜304が形成されている。有機発光多層膜304は、画素定義層307の開口306及びその周囲において、画素定義層307に付着している。RGBの色毎に、有機発光材料を成膜して、アノード電極308上に、有機発光多層膜304が形成される。

#### 【0043】

有機発光多層膜304の成膜は、メタルマスクを使用して、画素に対応する位置に有機発光材料を蒸着させる。有機発光多層膜304は、下層側から、例えば、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層によって構成される。有機発光多層膜304の積層構造は設計により決められる。

20

#### 【0044】

有機発光多層膜304の上にカソード電極302が形成されている。カソード電極302は、光透過性を有する電極である。カソード電極302は、有機発光多層膜304からの可視光の一部を透過させる。カソード電極302の層は、例えば、Al、Mg等の金属又はこれらの金属を含む合金を蒸着して、形成する。カソード電極302の抵抗が高く発光輝度の均一性が損なわれる場合には、さらに、ITO又はIZOなどの透明電極形成用の材料で補助電極層を追加する。

30

#### 【0045】

画素定義層307の開口306に形成された、アノード電極308、有機発光多層膜304及びカソード電極302の積層膜が、OLED素子を構成する。カソード電極302上には、封止構造部200が直接接觸して形成されている。封止構造部（薄膜封止部）200は、下層から、無機絶縁物層301、有機平坦化膜331、無機絶縁物層332を含む。無機絶縁物層301及び332は、それぞれ、信頼性向上のために下層及び上層のパッジベーション層である。

#### 【0046】

封止構造部200上に、下層から、タッチスクリーン333、/4板334、偏光板335、及び樹脂カバーレンズ336が積層されている。/4板334及び偏光板335は、外部から入射した光の反射を抑制する。なお、図3を参照して説明したOLED表示装置の積層構造は一例であり、図3に示す層の一部が省略されてもよく、図3に示されていない層が追加されてもよい。上述のようにタッチスクリーンをTFT基板100に積層することに代えて、TFT基板100と別プロセスで製造されたタッチスクリーンをTFT基板100に位置合わせして貼り合わせてもよい。

40

#### 【0047】

##### [ダミー画素レイアウト]

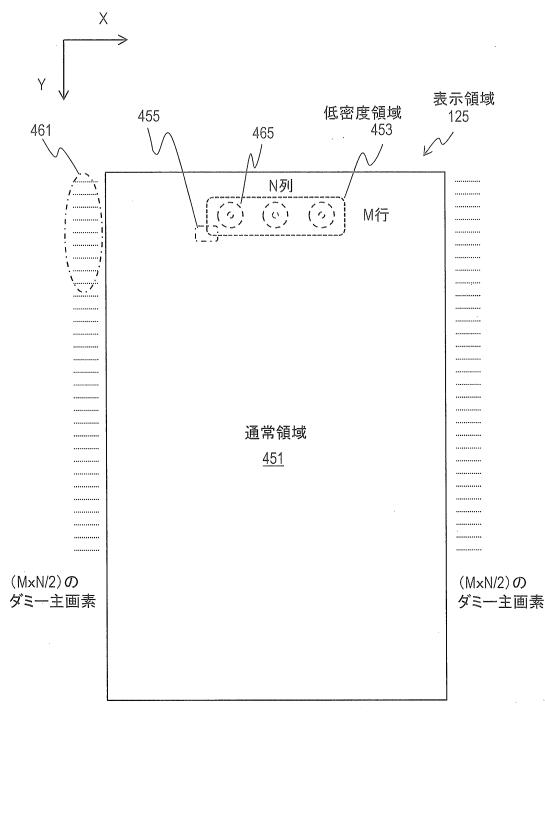

図4は、表示領域125及び表示領域外に配置されたダミー画素を模式的に示す。OLED表示装置10は、例えば、モバイル端末に実装される。表示領域125は、通常の画素密度を有する通常領域451と、通常領域451の画素密度よりも低い画素密度を有す

50

る低密度領域 453 を含む。1又は複数のカメラ 465 が、低密度領域 453 の下に配置されている。図 4 において、複数のカメラのうちの一つが例として符号 465 で指示されている。以下において、表示領域 125 における副画素又は主画素を、表示副画素又は表示主画素と呼ぶことができる。

#### 【0048】

低密度領域 453 はカメラ 465 の視認側に配置されており、カメラ 465 は、低密度領域 453 と通過した光によって視認側の物体を撮影する。カメラ 465 による撮影を妨げないように、低密度領域 453 の画素密度は、周囲の通常領域 451 の画素密度より低い。不図示の制御装置は、例えば、カメラ 465 により撮像した画像のデータを OLE D 表示装置 10 に送信する。なお、図 4 は、低密度領域の例として、カメラがその下に配置されている領域を示すが、本明細書における特徴は、他の目的のために画素密度が相対的に低い領域を含む表示装置に適用できる。

#### 【0049】

低密度領域 453 は、N列M行の主画素で構成されている。主画素列は、図 4 における上下方向である Y 軸に沿って配列された主画素で構成されている。主画素行は、図 4 における左右方向である X 軸に沿って配列された主画素で構成されている。

#### 【0050】

図 4 に示すように、OLE D 表示パネルの表示領域 125 の外側に、ダミー画素（ダミー副画素）が配置されている。後述するように、ダミー副画素は、低密度領域 453 において対応する副画素の劣化を推定するために使用される。ドライバ I C 134 は、ダミー副画素が、低密度領域 453 において対応する副画素と同様の輝度で発光するように制御し、ダミー副画素の劣化を測定する。これにより、対応する副画素の劣化を正確に評価することができる。

#### 【0051】

図 4 の例において、低密度領域 453 の主画素それぞれに対応するダミー主画素が表示領域 125 の外側に配置されている。図 4 の例において、表示領域 125 の左右両側それに、M × N / 2 のダミー主画素が配置されている。なお、低密度領域 453 内の一部の副画素に対するダミー副画素のみが用意されていてもよく、ダミー副画素のレイアウトは、図 4 のレイアウトに限定されず、任意である。

#### 【0052】

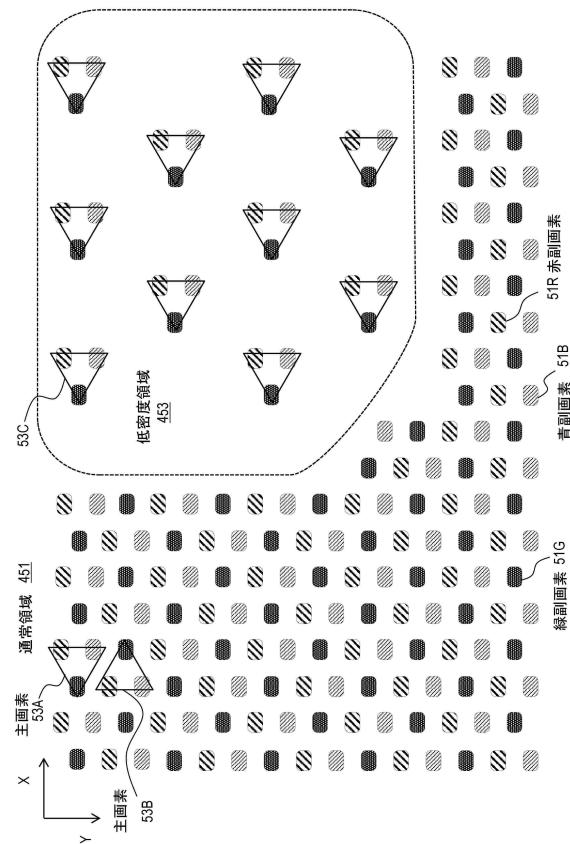

図 5 は、図 4 において一点鎖線で囲まれた領域 455 の詳細を示す。図 5 は、デルタナブラ配置（単にデルタ配置とも呼ぶ）の画素レイアウトを示す。なお、本実施形態における特徴は、他の画素レイアウトを有する表示装置に適用することができる。

#### 【0053】

領域 455 は、通常領域 451 と低密度領域 453 の一部の境界の近傍の領域である。図 5 に示す例において、低密度領域 453 の画素密度は、通常領域 451 の 1 / 4 である。低密度領域 453 の副画素は、同一の画像データに対して、通常領域 451 の副画素の 4 倍の輝度で発光するように制御される。

#### 【0054】

表示領域 125 は、面内に配置されている、複数の赤副画素 51R、複数の緑副画素 51G、及び複数の青副画素 51B で構成されている。図 5 において、一つの赤副画素、一つの緑副画素、及び一つの青副画素が、例として、符号で指示されている。図 5 において、同一のハッチングの（丸い角の）四角は、同一色の副画素を示す。図 5 において、副画素の形状は四角であるが、副画素の形状は任意であって、例えば、六角形又は八角形であってもよい。

#### 【0055】

副画素列は、同一の X 軸位置の副画素からなる、Y 軸に沿って延びる配列である。副画素列において、赤副画素 51R、青副画素 51B 及び緑副画素 51G が、サイクリックに配列されている。例えば、副画素列の副画素は、同一のデータ線に接続される。副画素行は、同一の Y 軸位置の同一色の副画素からなる、X 軸に沿って延びる配列である。例えば

、副画素行の副画素は、同一の走査線に接続される。

【0056】

図5の構成例において、通常領域451は、マトリックス状に配置されている、第1種主画素53A及び第2種主画素53Bの、2種類の主画素を含む。図5において、一つの第1種主画素のみが、例として、符号53Aで指示されている。また、一つの第2種主画素のみが、例として、符号53Bで指示されている。なお、サブピクセルレンダリング技術が使用される場合、外部からの画像データの主画素とパネルの主画素とは一致しない。

【0057】

図5において、第1種主画素53Aは、一つの頂点が左側にあり、二つの頂点が右側にある三角形で示されている。また、第2種主画素53Bは、一つの頂点が右側にあり、二つの頂点が左側にある三角形で示されている。

10

【0058】

第1種主画素53Aにおいて、赤副画素51R及び青副画素51Bは、同一の副画素列において連続して配置されている。緑副画素51Gが含まれる副画素列は、赤副画素51R及び青副画素51Bが含まれる副画素列の左側に隣接している。緑副画素51Gは、Y軸位置において、赤副画素51Rと青副画素51Bの中央に位置している。

【0059】

第2種主画素53Bにおいて、赤副画素51R及び青副画素51Bは、同一の副画素列において連続して配置されている。緑副画素51Gが含まれる副画素列は、赤副画素51R及び青副画素51Bが含まれる副画素列の右側に隣接している。緑副画素51Gは、Y方向において、赤副画素51Rと青副画素51Bの中央に位置している。

20

【0060】

低密度領域453は、第1種主画素53Aと同一構成の主画素53Cで構成されている。図5は、5列4行の主画素53Cを示す。主画素53Cは規則的に配置されており、X軸及びY軸に沿った主画素間距離は一定である。また、隣接する主画素行は、互いに半ピッチだけ離れている。

【0061】

低密度領域453の副画素レイアウトは、通常領域451のレイアウトから一部の副画素を除いた構成を有している。低密度領域453の副画素は、通常領域の副画素と共に副画素行及び副画素列を構成する。低密度領域453の各副画素列は、通常領域451の対応する副画素列と共に一つの副画素列を構成し、同一のデータ線に接続される。低密度領域453の各副画素行は、通常領域451の対応する副画素行と共に一つの副画素行を構成し、同一の走査線線に接続される。

30

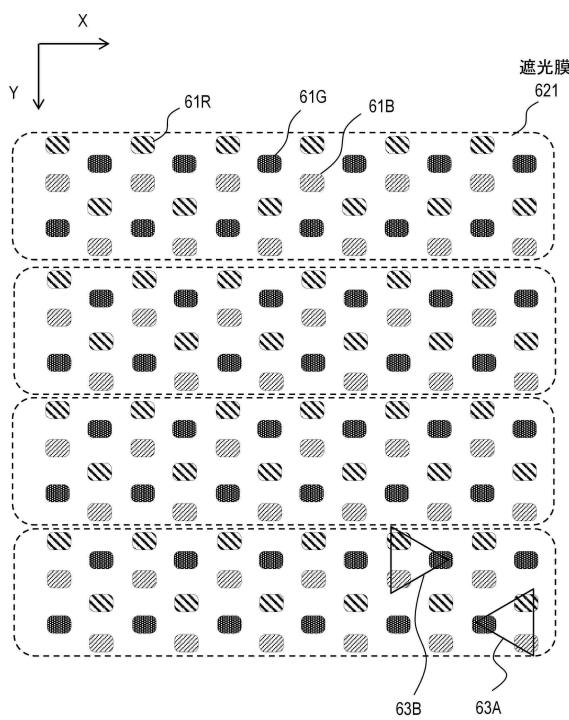

【0062】

図6は、図4において一点鎖線で囲まれた領域461のダミー画素レイアウトを示す。領域461は、表示領域125の外側に配置されたダミー画素の一部を含む。図6は、複数のダミー赤副画素61R、複数のダミー青副画素61B、及び複数のダミー緑副画素61Gを示す。一つのダミー赤副画素、一つのダミー青副画素、及び一つのダミー緑副画素が、例として、符号61R、61B及び61Gで指示されている。

40

【0063】

図6のレイアウト例において、第1種ダミー主画素63A及び第2種ダミー主画素63Bの2種類の主画素が、マトリックス状に配置されている。図6において、一つの第1種ダミー主画素及び一つの第2種ダミー主画素が、それぞれ対応する符号63A及び63Bで指示されている。第1種ダミー主画素63A及び第2種ダミー主画素63Bは、通常領域451における第1種主画素53A及び第2種主画素53Bそれぞれと、同様の構成を有している。

【0064】

各ダミー赤副画素61Rは、低密度領域453における一つの赤副画素51Rに対応付けられている。一例において、それらのOLED素子は同一のサイズ及び構造を有している。異なるダミー赤副画素61Rは、低密度領域453における異なる赤副画素51Rに

50

対応付けられている。――

【 0 0 6 5 】

各ダミー青副画素 6 1 B は、低密度領域 4 5 3 における一つの青副画素 5 1 B に対応付けられている。一例において、それらの O L E D 素子は同一のサイズ及び構造を有している。異なるダミー青副画素 6 1 B は、低密度領域 4 5 3 における異なる青副画素 5 1 B に対応付けられている。

【 0 0 6 6 】

各ダミー緑副画素 6 1 G は、低密度領域 4 5 3 における一つの緑副画素 5 1 G に対応付けられている。一例において、それらの O L E D 素子は同一のサイズ及び構造を有している。異なるダミー緑副画素 6 1 G は、低密度領域 4 5 3 における異なる緑副画素 5 1 G に対応付けられている。

10

【 0 0 6 7 】

図 6 の例において、各第 1 種ダミー主画素 6 3 A は、低密度領域 4 5 3 における一つの主画素 5 3 C に対応付けられている。同様に、各第 2 種ダミー主画素 6 3 B は、低密度領域 4 5 3 における一つの主画素 5 3 C に対応付けられている。異なる第 1 種ダミー主画素 6 3 A 及び第 2 種ダミー主画素 6 3 B は、低密度領域 4 5 3 における異なる主画素 5 3 C に対応付けられている。

【 0 0 6 8 】

対応付けられているダミー主画素と低密度領域 4 5 3 の表示主画素に対して、同一のデータ信号が与えられる。つまり、ダミー副画素は、対応する低密度領域 4 5 3 内の表示副画素と同一のデータ信号が与えられ、対応する副画素と同様の輝度で発光するように制御される。これにより、ダミー副画素の劣化を測定することで、対応する表示副画素の劣化を正確に推定することができる。

20

【 0 0 6 9 】

図 6 の例では各行に 6 つの赤、青、緑のダミー副画素を配置しており、これら 6 つのダミー画素の劣化状態の測定値を平均化して、対応づけられた低密度領域の 4 5 3 の表示種画素の劣化状態を見積もる。このように複数のダミー画素を用いることで、製造ばらつきによる劣化見積もりの誤差を最小化し、より正確な劣化補償が可能となる。なお、ダミー副画素の数は赤、青、緑の最低 1 セットあればよく、ダミー画素を配置できる面積と要求される劣化補償精度のバランスを考慮して、最適なダミー画素数が決定される。

30

【 0 0 7 0 】

図 6 は、互いに分離された複数の不透明な遮光膜 6 2 1 を示す。図 6 において、破線の角丸四角形で示す一つの遮光膜が、例として、符号 6 2 1 で指示されている。複数の遮光膜 6 2 1 を配置することで、一つの遮光膜のサイズを小さくすることができる。これにより、タッチスクリーン 3 3 3 によるタッチ検出への好ましくない影響を低減できる。特に、後述するように遮光膜 6 2 1 をタッチスクリーンのタッチ電極の金属膜と同一層で形成する場合に有効である。

【 0 0 7 1 】

複数の遮光膜 6 2 1 は、それぞれ複数のダミー副画素を視認側から覆うように配置されている。遮光膜 6 2 1 は、その下側の副画素からの光をユーザに視認されないように遮る。図 6 は、視認側から見て左側の一部のダミー副画素を覆う遮光膜 6 2 1 を示すが、左右両側の全てのダミー画素は、遮光膜 6 2 1 に覆われている。

40

【 0 0 7 2 】

遮光膜 6 2 1 が覆う副画素の数は任意であって一つであってもよい。図 6 の例において、遮光膜 6 2 1 は同一層（同一材料及び同一プロセス）に形成されているが、一部の遮光膜 6 2 1 は他の遮光膜 6 2 1 と異なる層に含まれていてもよい。遮光膜 6 2 1 の形状は任意であって、図 6 に示す例に限定されず、異なる遮光膜 6 2 1 が異なる形状を有していてもよい。表示領域 1 2 5 の両側一方又は双方において、全てのダミー副画素が一つの遮光膜 6 2 1 で覆われていてもよい。

【 0 0 7 3 】

50

図6の例において、Y軸に沿って延びるダミー副画素例において、通常領域451と同様に、ダミー赤副画素61R、ダミー青副画素61B及びダミー緑副画素61Gが、サイクリックに配列されている。例えば、ダミー副画素列のダミー副画素は、同一のデータ線に接続される。ダミー副画素行は、同一のY軸位置の同一色のダミー副画素からなる、X軸に沿って延びる配列である。例えば、ダミー副画素行のダミー副画素は、同一の走査線に接続される。

#### 【0074】

ダミー副画素のレイアウトパターンは、通常領域451と異なっていてもよい。例えば、表示主画素に対応するダミー主画素を構成する副画素が隣接しておらず、他の副画素を挟むように離れた位置に配置されていてもよい。例えば、表示領域125の両側のダミー副画素のレイアウトは同一でも異なっていてもよく、ダミー副画素の数も同一でも異なっていてもよい。ダミー副画素の位置は、表示領域125の外側において、特に限定されない。

10

#### 【0075】

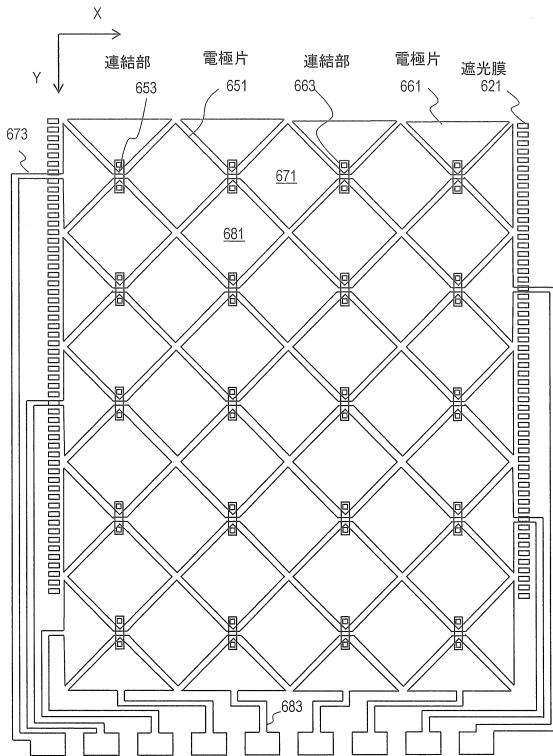

##### 【遮光パターンレイアウト】

図7は、タッチスクリーン333に形成されている、遮光パターン及びタッチ電極パターンの例を示す平面図である。図7は、例として、投影型静電容量方式の電極パターンを示す。タッチスクリーン333は、X軸に沿って延びY軸に沿って配列されたXタッチ電極671と、Y軸に沿って延びX軸に沿って配列されたYタッチ電極681と、を含む。図7は、一つのXタッチ電極及びYタッチ電極を、例として、それぞれ符号671及び681で示している。

20

#### 【0076】

Xタッチ電極671は、菱形又は三角形のX軸に沿って配列された電極片651と、隣接する電極片651の角部をつなぐ、電極片651より細い矩形の連結部653とで構成されている。電極片651及び連結部653は、透明導体、例えば、ITOで形成されている。Xタッチ電極671は連続する透明導体で形成されており、電極片651及び連結部653は同一層に含まれる。

#### 【0077】

Yタッチ電極681は、菱形又は三角形のY軸に沿って配列された電極片661と、隣接する電極片661の角部をつなぐ、661より細い矩形の連結部663とで構成されている。電極片661は、透明導体、例えば、ITOやIZOで形成されている。図7の例において、電極片661、Xタッチ電極671と同一層に含まれる。連結部663は、電極片661より上層に形成されており、遮光性の導体（金属）で形成されている。連結部663は、例えば、AlやMoで形成することができる。

30

#### 【0078】

Xタッチ電極671の電極片651及びYタッチ電極681の電極片661は、マトリックス状に配置されている。ドライバIC134又は不図示の検出回路は、タッチスクリーン333に近づけられた、指やタッチペンなどの指示体によるXタッチ電極671とYタッチ電極681との間の容量変化を、配線673及び683を介して検出する。これにより、タッチ位置が同定される。

40

#### 【0079】

Yタッチ電極の連結部663は、平面視において、Xタッチ電極671の連結部653と交差するように配置されている。連結部663の層と、Xタッチ電極671の層との間には絶縁層（不図示）が形成されている。連結部663と連結部653とは、絶縁膜を介して交差しており、電気的な絶縁が保たれている。

#### 【0080】

タッチスクリーン333は、さらに、複数の遮光膜621からなる遮光膜パターンを含む。遮光膜621は、タッチ電極671及び681が配置されているタッチ検出領域の外側に配置されている。上述のように、遮光膜621は遮光性材料で形成されており、図7の例において、Yタッチ電極の連結部663と同層に、つまり、遮光性金属で形成されて

50

いる。このように、タッチスクリーン 333 の遮光性要素と同層に遮光膜 621 を形成することで、表示装置の製造を効率化できる。複数の遮光膜 621 により、一つの遮光膜のサイズが小さくなり、タッチ検出への好ましくない影響を低減できる。

【0081】

図 7 に示す構成例において、タッチ検出領域の左右両側それぞれに、一つの遮光膜列が配置されている。列数及び列を構成する遮光膜数は任意である。上述のように、遮光膜 621 は、ダミー副画素を覆うようにアライメントされている。なお、遮光膜 621 のパターンは任意であって、例えば、タッチ検出領域の両側のパターン形状（遮光膜 621 の数及び形状）は、異なっていてもよい。なお、遮光膜 621 は、タッチスクリーン 333 に含まれるタッチ電極と異なる他の遮光性要素と同層に形成されてもよく、タッチスクリーン 333 と異なる層に形成されてもよい。タッチスクリーン 333 の方式は任意であり、タッチスクリーン 333 が省略されていてもよい。

10

【0082】

【配線レイアウト】

以下において、OLED 表示装置 10 の配線レイアウト例を説明する。図 8 は、TFT 基板 100 上の制御配線のレイアウトを模式的に示し、図 8 の構成例において、通常領域 451 の画素回路のレイアウトは、ストライプ配置である。具体的には、Y 軸に沿って延びる副画素列は、同一色の副画素で構成されている。X 軸に沿って延びる副画素行は、サイクリックに配置された、赤副画素、緑副画素及び青副画素で構成されている。低密度領域 453 は、通常領域 451 の画素レイアウトから、一部の画素を間引いた構成を有している。低密度領域 453 における空白領域には、OLED 素子を含む画素回路は形成されておらず、配線のみが通過している。

20

【0083】

ダミー画素領域 457A、457B が、それぞれ、表示領域 125 の両側に存在する。図 8 は、ダミー画素領域 457A、457B それぞれにおいて、一つのダミー赤副画素列、一つのダミー緑副画素列及び一つのダミー青副画素列を示すが、劣化補償精度を向上させるために複数のダミー副画素を配置してもよい。

【0084】

複数の走査線 106 が、走査ドライバ 131 から X 軸に沿って延びている。また、複数のエミッショントリガーライン 107 が、エミッショントリガーライン 132 から X 軸に沿って延びている。図 8 は、例として、一つの走査線及び一つのエミッショントリガーラインを、それぞれ符号 106 及び 107 で指示している。

30

【0085】

図 8 に示す構成例において、走査線 106 は、通常領域 451 及び低密度領域 453 に加え、ダミー画素領域 457A、457B の選択信号を伝送する。ダミー副画素が、表示領域 125 内の副画素と共に走査線 106 に接続されていることで、配線数を低減することができる。

【0086】

また、エミッショントリガーライン 107 は、通常領域 451 及び低密度領域 453 に加え、ダミー画素領域 457A、457B のエミッショントリガーライン信号を伝送する。ダミー副画素が、表示領域 125 内の副画素と共にエミッショントリガーライン 107 に接続されていることで、配線数を低減することができる。

40

【0087】

ドライバ IC 134 は、配線 711 によって走査ドライバ 131 に制御信号を送信し、配線 713 によってエミッショントリガーライン 132 に制御信号を送信する。ドライバ IC 134 は、外部からの画像データ（画像信号）に基づき、走査ドライバ 131 から走査信号（選択パルス）及びエミッショントリガーライン 132 のエミッショントリガーライン信号のタイミングを制御する。

【0088】

ドライバ IC 134 は、配線 705 によって、通常領域 451 及び低密度領域 453 の

50

副画素のデータ信号をデマルチプレクサ 136 に与える。図 8 は、1 本の配線を例として、符号 705 で指示している。ドライバ I C 134 は、外部からの画像データ（フレーム）の 1 又は複数の副画素の階調レベルから、通常領域 451 及び低密度領域 453 の各副画素のデータ信号を決定する。デマルチプレクサ 136 は、ドライバ I C 134 の一つの出力を、走査期間内に N 本（N は 2 以上の整数）のデータ線 105 に順次出力する。図 8 において、Y 軸に沿って延びる複数のデータ線のうち、1 本のデータ線が、例として符号 105 で指示されている。

#### 【0089】

ドライバ I C 134 は、さらに、複数の配線 723A を介して、ダミー副画素のデータ信号をダミー画素領域 457A に供給する。ドライバ I C 134 は、複数の配線 723B を介して、ダミー副画素のデータ信号をダミー画素領域 457B に供給する。一つの配線 723A がデータ信号を伝送する全てのダミー副画素は、異なる走査線 106 により選択される。一つの配線 723B がデータ信号を伝送する全てのダミー副画素は、異なる走査線 106 により選択される。

10

#### 【0090】

ドライバ I C 134 は、配線 721A を介して、ダミー画素領域 457A に劣化測定のための制御信号を送信し、配線 721B を介して、ダミー画素領域 457B に劣化測定のための制御信号を送信する。配線 721A は、ダミー画素領域 457A の全てのダミー副画素に接続されている。配線 721B は、ダミー画素領域 457B の全てのダミー副画素に接続されている。劣化測定制御信号の詳細は後述する。

20

#### 【0091】

ドライバ I C 134 は、複数の配線 725A を介して、ダミー画素領域 457A のダミー副画素の劣化測定信号を受信する。図 8 の構成例において、一つの配線 725A が劣化測定信号を伝送する全てのダミー副画素は、異なる走査線 106 により選択される。図 8 の例において、各配線 725A に接続されるダミー副画素のグループは、データ信号を伝送する各配線 723A に接続されているダミー副画素のグループと共通である。

#### 【0092】

ドライバ I C 134 は、複数の配線 725B を介して、ダミー画素領域 457A のダミー副画素の劣化測定信号を受信する。図 8 の構成例において、一つの配線 725B が劣化測定信号を伝送する全てのダミー副画素は、異なる走査線 106 により選択される。ダミー副画素の劣化測定方法の詳細は後述する。

30

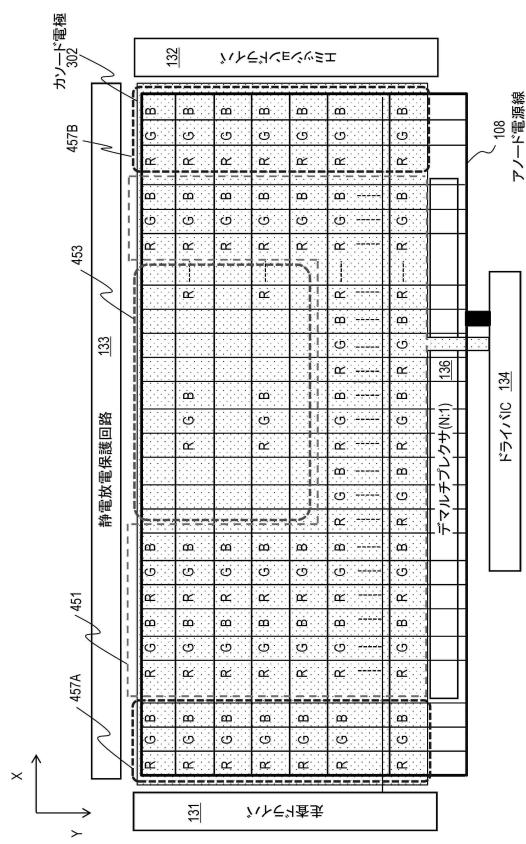

#### 【0093】

図 9 は、TFT 基板 100 上のアノード電源線及びカソード電極のレイアウトを模式的に示す。ドライバ I C 134 は、DC - DC コンバータを含み、複数の異なる電源電位を生成して、OLED 表示パネルに供給する。図 9 に示す構成例において、ドライバ I C 134 は、アノード電源線 108 にアノード電源電位 VDD を出力し、カソード電極 302 にカソード電源電位 VSS を出力する。

#### 【0094】

アノード電源線 108 は網目状であって、通常領域 451、低密度領域 453、及びダミー画素領域 457A、457B の各副画素にアノード電源電位 VDD を伝送する。カソード電極 302 は、シート形状を有し、通常領域 451、低密度領域 453、及びダミー画素領域 457A、457B の全体を覆う。これら領域 451、453、457A、457B の各副画素のカソード電極は、一枚のシート状カソード電極 302 の一部である。

40

#### 【0095】

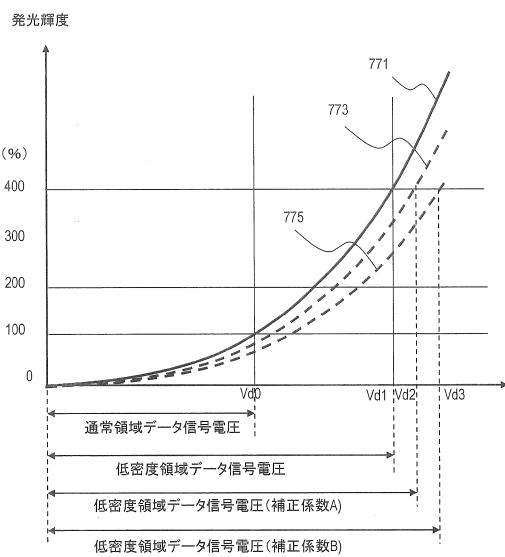

##### 【発光制御方法】

以下において、OLED 表示装置 10 の副画素の発光制御方法を説明する。ドライバ I C 134 は、通常領域 451、低密度領域 453、及びダミー画素領域 457A、457B の副画素それぞれの発光輝度を制御する。図 10 は、通常領域 451 及び低密度領域 453 の副画素へのデータ信号電圧（単にデータ信号とも呼ぶ）と、OLED 素子の発光輝度と、の関係を模式的に示すグラフである。

50

## 【0096】

図10のグラフにおいて、曲線771は、通常領域451の副画素及び低密度領域453の劣化前の副画素の特性を示す。白の階調レベルに対応して、データ信号電圧Vd0が通常領域451の副画素に与えられ、データ信号電圧Vd1が低密度領域453の副画素に与えられる。本例において、低密度領域453の副画素は、通常領域451の副画素の4倍の輝度で発光する。

## 【0097】

発光時間の経過と共に、低密度領域453の副画素(OLED素子)は、通常領域451の副画素と比較して、一桁以上早い速度で劣化する。ここでは、通常領域451の副画素は劣化せずその特性を維持し、低密度領域453の副画素は発光時間の経過と共に劣化するものとする。このようにすることで、最低限の回路構成で表示システムとしては十分な劣化補償性能を実現することができる。

10

## 【0098】

図10のグラフにおいて、曲線773は、低密度領域453の劣化した副画素の特性を示す。劣化前と同一の輝度(400%)で発光するため、データ信号電圧Vd1より大きいデータ信号電圧Vd2が、低密度領域453の副画素に与えられる。データ信号電圧Vd2は、劣化に応じた補正係数Aに基づいて算出される。

## 【0099】

曲線775は、低密度領域453のさらに劣化した副画素の特性を示す。劣化前と同一の輝度(400%)で発光するため、データ信号電圧Vd2より大きいデータ信号電圧Vd3が、低密度領域453の副画素に与えられる。データ信号電圧Vd3は、劣化に応じた補正係数Bに基づいて算出される。後述するように、補正係数A及び補正係数Bは、ダミー副画素の劣化の測定結果に基づき決定される。

20

## 【0100】

通常領域451における副画素の劣化は、低密度領域453の副画素の劣化と比較して遅い。そのため、ドライバIC134は、例えば、通常領域451における副画素のデータ信号を副画素の劣化に応じて補正することなく、出力してもよい。他の例において、ドライバIC134は、通常領域451のデータ信号を劣化に応じて補正してもよい。通常領域451の副画素に対応するダミー副画素は用意されていないため、ドライバIC134は、例えば、副画素のデータ信号の履歴を保持し、予め設定されているルックアップテーブルを参照して、履歴に応じた補正係数を決定することができる。

30

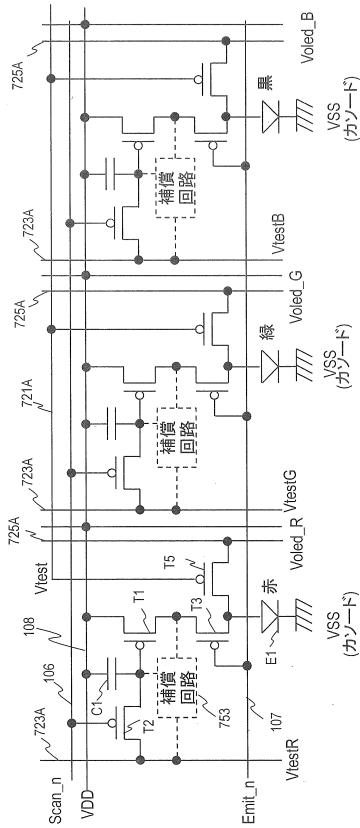

## 【0101】

次に、ダミー副画素の制御方法を説明する。図11は、ダミー副画素の画素回路の構成例を示す。図11は、n行目の、赤、緑、及び青のダミー副画素の画素回路を示す。全てのダミー副画素の画素回路はOLED素子の色を除いて共通である。走査線106は、走査信号SCAN\_nを三つのダミー副画素に同時に伝送する。エミッション制御線107は、エミッション制御信号Emitt\_nを三つのダミー副画素に同時に伝送する。

## 【0102】

異なる配線723Aが、それぞれ、赤、緑、及び青のダミー副画素の画素回路にデータ信号VtestR、VtestG、及びVtestBを伝送する。配線721Aは、劣化測定のための制御信号Vtestを三つのダミー副画素の画素回路に同時に伝送する。異なる配線725Aは、それぞれ、赤、緑、及び青のダミー副画素の劣化測定信号VolRed\_R、VolRed\_G、及びVolRed\_Bを、ドライバIC134に伝送する。

40

## 【0103】

次に、ダミー副画素の画素回路の構成を説明する。異なる色のダミー副画素に、画素回路構成は共通である。図11は、赤のダミー副画素の画素回路の構成要素を、例として符号で指示している。以下において、赤の副画素の画素回路の構成を説明する。図11に示す画素回路は、図2Aに示す画素回路に対して、スイッチトランジスタT5及び閾値電圧補償回路753を追加した構成を有している。なお、表示領域125内の表示副画素の画素回路は、ダミー副画素の画素回路からスイッチトランジスタT5を除いた構成であるこ

50

とができる。

【0104】

閾値電圧補償回路753は、駆動トランジスタT1の閾値電圧を補償する。スイッチトランジスタT5は、OLED素子E1のアノードと配線725Aとに接続されている。具体的には、そのソース／ドレインの一方が、OLED素子E1のアノードとトランジスタT3との間のノードに接続され、ソース／ドレインの他方が配線725Aに接続されている。スイッチトランジスタT5のゲートは配線721Aに接続されている。スイッチトランジスタT5は、劣化測定制御信号Vtestにより、そのON/OFFが制御される。ドライバIC134は、後述するように、通常動作においてスイッチトランジスタT5をOFFに維持し、OLED素子E1の劣化測定を行っている間、スイッチトランジスタT5をONに維持する。

10

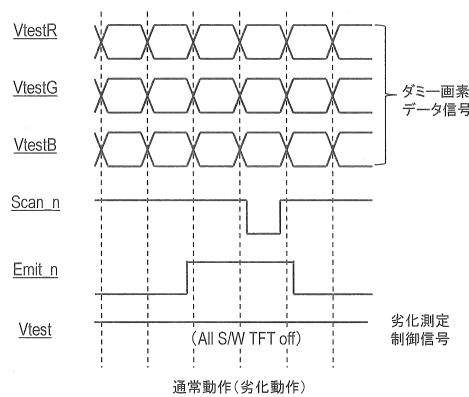

【0105】

次に、通常動作及び劣化測定動作における、ダミー副画素の発光制御を説明する。図12は、通常動作におけるダミー副画素に対する信号のタイミングチャートの例を示す。同時に選択されて発光制御される赤、緑及び青のダミー副画素の信号を示す。これらは、例えば、低密度領域453の主画素に対応するダミー主画素を構成してもよい。

【0106】

VtestR、VtestG、VtestBは、それぞれ、ダミー赤副画素列、ダミー緑副画素列、ダミー青副画素列に与えられるデータ信号を示す。ここでは、図8に示すように、同色のダミー副画素が一つの配線723Aに接続されているとする。ダミー画素データ信号VtestR、VtestG、VtestBは、ダミー副画素が対応する低密度領域453の副画素と同一の値である。

20

【0107】

n行を選択する走査信号SCAN\_nがLowレベルのとき、n行のダミー副画素が選択され、ダミー画素データ信号VtestR、VtestG、VtestBがそれぞれ画素回路に書き込まれる。データ信号の書き込みの間、エミッション制御信号Emit\_nはHighであり、トランジスタT3はOFFである。そのため、OLED素子E1が発光することはない。

【0108】

データ信号書き込みの後、エミッション制御信号Emit\_nはLowに変化して、OLED素子E1が発光する。上述のように、ダミー副画素は、視認側に配置された遮光膜621に覆われているため、ダミー副画素の発光による表示領域125による画像表示への影響は存在しない。通常動作において、劣化測定制御信号Vtestは常にHighであって、全てのダミー副画素の画素回路のスイッチトランジスタT5はOFFに維持される。

30

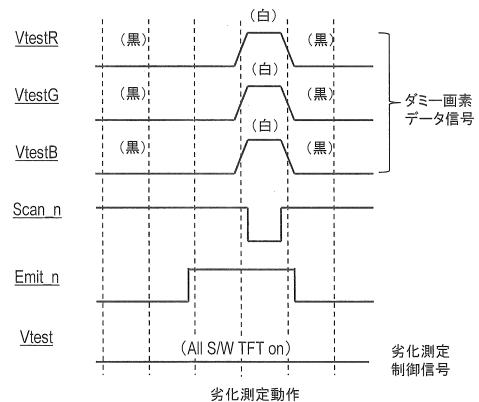

【0109】

次に、ダミー副画素のOLED素子の劣化測定動作を説明する。一例において、ドライバIC134は、外部からの画像データの画像表示期間外（非表示期間）に、ダミー副画素のOLED素子の劣化測定を行う。ドライバIC134は、例えば、OLED表示装置10の電源ONから外部からの画像データに応じた画像表示までの間の起動シーケンスにおいて、又は、電源ONの状態において画像表示を停止するスタンバイモードにおいて、測定を行うことができる。スタンバイモードは、例えば、所定期間を超えて入力画像データが中断している場合に開始する。

40

【0110】

図13は、ダミー副画素のOLED素子E1の劣化測定動作における信号のタイミングチャートを示す。n行目のダミー副画素が、劣化測定対象である。劣化測定動作において、選択した行の劣化測定を行う間、劣化測定制御信号VtestはLowであって、全てのダミー副画素の画素回路のスイッチトランジスタT5はONに維持される。

【0111】

劣化測定信号を伝送する配線725Aに接続されているダミー副画素において、測定対

50

象のダミー副画素以外の全てのダミー副画素に対しては、0（ゼロ）データ信号が書き込まれる。これにより、他のダミー副画素の発光は停止されており、測定対象のダミー副画素の劣化測定のS/N比を向上させることができる。

【0112】

n行を選択する走査信号SCAN\_nがLowレベルのとき、n行のダミー副画素が選択され、劣化測定のためのダミー画素データ信号VtestR、VtestG、VtestBがそれぞれ画素回路に書き込まれる。図13の例において、データ信号は最高輝度を示す。これにより、OLED素子E1の劣化をより正確に測定できる。なお、劣化測定時のデータ信号は異なる値であってもよい。

【0113】

劣化測定のためのデータ信号の書き込みの間、発光制御信号Emitt\_nはHighであり、トランジスタT3はOFFである。データ信号書き込みの後、発光制御信号Emitt\_nはLowに変化して、OLED素子E1が発光する。OLED素子E1からの光は遮光膜621によって遮られる。

【0114】

ドライバIC134は、配線725Aを介して、ダミー副画素それぞれの劣化測定信号Voled\_R、Voled\_G、Voled\_Bを受信する。劣化測定信号Voled\_R、Voled\_G、Voled\_Bは、それぞれ、対応するOLED素子のアノード電位を示す。OLED素子の抵抗は、劣化と共に増加する。

【0115】

従って、一定電流をOLED素子に与えた状態でその電圧（アノードとカソードとの間の電圧）を測定することで、OLED素子の抵抗、つまり劣化度を測定することができる。ドライバIC134は、配線725Aの電位をAD変換して各ダミーサブ画素に対応した表示サブ画素の劣化状態として記録する。なお、OLED素子の劣化測定は、任意の方法を利用することができ、例えば図11において駆動TFTT1を線形動作させてOLED素子に定電圧を印加した状態で電流センスアンプを用いて直接素子に流れる電流値を測定して劣化度を判定することもできる。

【0116】

ドライバIC134は、ダミー副画素の劣化測定結果に基づいて、低密度領域453内の対応する副画素のデータ信号を補正する。例えば、ドライバIC134は、ダミー副画素の抵抗値（劣化度）と補正係数を対応付けるルックアップテーブルを参照して、OLED素子の劣化量を補償するための補正係数を決定する。低密度領域453内の副画素と同じデータ信号パターンで発光したダミー画素の劣化を測定することで、劣化速度が速い当該副画素の劣化を正確に推定でき、OLED表示装置10の表示品質を適切に維持することができる。

【0117】

以上、本開示の実施形態を説明したが、本開示が上記の実施形態に限定されるものではない。当業者であれば、上記の実施形態の各要素を、本開示の範囲において容易に変更、追加、変換することが可能である。ある実施形態の構成の一部を他の実施形態の構成に置き換えることが可能であり、ある実施形態の構成に他の実施形態の構成を加えることも可能である。

【符号の説明】

【0118】

10 OLE D表示装置、51B 青副画素、51G 緑副画素、51R 赤副画素、53A - 53C 主画素、61B ダミー青副画素、61G ダミー緑副画素、61R ダミー赤副画素、100 TFT基板、105 データ線、106 走査線、107 エミッショニ制御線、108 アノード電源線、109 リセット制御線、110 基準電圧供給線、114 カソード電極形成領域、125 表示領域、131 走査ドライバ、132 エミッションドライバ、133 静電気放電保護回路、134 ドライバIC、136 デマルチプレクサ、333 タッチスクリーン、451 通常領域、453 低密度領域、457

10

20

30

40

50

A、457B ダミー画素領域、465 カメラ、621 遮光膜、651、661 電極片、653、663 連結部、705、711、703、721A、721B、723A、723B、725A、725B 配線、753 閾値電圧補償回路、C1 保持容量、E1 OLED 素子、T1 - T5 トランジスタ

【図面】

【図1】

【図4】

【 四 5 】

【図6】

【 四 7 】

【 义 8 】

【図9】

【図10】

### 【図11】

【図 1 2】

【図 1 3】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

| F       | I    |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 4 1 P |

| G 0 9 G | 3/20 | 6 4 2 P |

| G 0 9 G | 3/20 | 6 5 0 M |

| G 0 9 G | 3/20 | 6 7 0 K |

| G 0 9 G | 3/20 | 6 8 0 G |

| G 0 9 G | 3/20 | 6 9 1 D |

## (56)参考文献

米国特許出願公開第 2 0 1 4 / 0 0 9 8 3 0 4 ( U S , A 1 )

中国特許出願公開第 1 1 0 6 1 0 6 8 0 ( C N , A )

韓国公開特許第 1 0 - 2 0 2 0 - 0 0 1 2 5 8 8 ( K R , A )

国際公開第 2 0 1 6 / 0 2 7 4 3 5 ( W O , A 1 )

中国特許出願公開第 1 0 8 7 6 6 3 4 7 ( C N , A )

特開 2 0 0 2 - 3 5 1 4 0 3 ( J P , A )

## (58)調査した分野

(Int.Cl. , D B 名)

|         |           |   |           |

|---------|-----------|---|-----------|

| G 0 9 G | 3 / 0 0   | - | 3 / 3 8   |

| G 0 9 F | 9 / 0 0   | - | 9 / 4 6   |

| H 1 0 K | 5 9 / 0 0 | - | 5 9 / 9 5 |