(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-270076

(P2006-270076A)

(43) 公開日 平成18年10月5日(2006.10.5)

| (51) Int.C1.                  | F 1         | テーマコード (参考) |

|-------------------------------|-------------|-------------|

| <b>HO1L 29/786 (2006.01)</b>  | HO1L 29/78  | 617J 5FO04  |

| <b>HO1L 21/336 (2006.01)</b>  | HO1L 29/78  | 618B 5F110  |

| <b>HO1L 29/78 (2006.01)</b>   | HO1L 29/78  | 301L 5F140  |

| <b>HO1L 21/3065 (2006.01)</b> | HO1L 21/302 | 105B        |

審査請求 未請求 請求項の数 8 O L (全 49 頁)

|              |                            |            |                                        |

|--------------|----------------------------|------------|----------------------------------------|

| (21) 出願番号    | 特願2006-44997 (P2006-44997) | (71) 出願人   | 000153878                              |

| (22) 出願日     | 平成18年2月22日 (2006.2.22)     |            | 株式会社半導体エネルギー研究所                        |

| (31) 優先権主張番号 | 特願2005-51169 (P2005-51169) |            | 神奈川県厚木市長谷398番地                         |

| (32) 優先日     | 平成17年2月25日 (2005.2.25)     | (72) 発明者   | 佐藤 友彦                                  |

| (33) 優先権主張国  | 日本国 (JP)                   |            | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内        |

|              |                            | (72) 発明者   | 物江 滋春                                  |

|              |                            |            | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内        |

|              |                            | F ターム (参考) | 5F004 DA00 DA04 DB07 EA12 EA38<br>EB02 |

最終頁に続く

(54) 【発明の名称】半導体装置、および半導体装置の作製方法

## (57) 【要約】

【課題】フッ素原子を分子中に含むガスでは、SiN膜のエッチングが等方的に進行するため、サイドウォールの幅が小さくなり、LDD領域の幅を大きくすることが困難であった。

【解決手段】ゲート電極上に窒化珪素膜を形成し、エッチングガスとして臭化水素ガスを主に用い、ICP(誘導結合型プラズマ)法などのエッチング方法により、窒化珪素膜のうちゲート電極上の部分と基板表面部のみを除去し、同時にゲート電極の側面部のみに窒化珪素膜を残す。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

半導体膜上にゲート電極を形成し、

前記ゲート電極上に窒化珪素膜を形成し、

臭化水素ガス及び塩素ガスを含む混合ガスを用いて前記窒化珪素膜をドライエッチングすることによって、前記ゲート電極上および前記半導体膜上の前記窒化珪素膜を除去するとともに、前記ゲート電極の側面に前記窒化珪素膜の一部を残すことを特徴とする半導体装置の作製方法。

**【請求項 2】**

半導体膜上にゲート電極を形成し、

前記ゲート電極上に窒化珪素膜を形成し、

臭化水素ガス、塩素ガス及び酸素ガスを含む混合ガスを用いて前記窒化珪素膜をドライエッチングすることによって、前記ゲート電極上および前記半導体膜上の前記窒化珪素膜を除去するとともに、前記ゲート電極の側面に前記窒化珪素膜の一部を残すことを特徴とする半導体装置の作製方法。

**【請求項 3】**

請求項 1 または請求項 2 において、

前記半導体膜は、ガラス、石英、合成樹脂などの絶縁性基板上に形成されていることを特徴とする半導体装置の作製方法。

**【請求項 4】**

半導体基板上にゲート電極を形成し、

前記ゲート電極上に窒化珪素膜を形成し、

臭化水素を含むガスを用いて前記窒化珪素膜をドライエッチングすることによって、前記ゲート電極上および前記半導体基板上の前記窒化珪素膜を除去するとともに、前記ゲート電極の側面に前記窒化珪素膜の一部を残すことを特徴とする半導体装置の作製方法。

**【請求項 5】**

半導体基板上にゲート電極を形成し、

前記ゲート電極上に窒化珪素膜を形成し、

臭化水素および塩素を含むガスを用いて前記窒化珪素膜をドライエッチングすることによって、前記ゲート電極上および前記半導体基板上の前記窒化珪素膜を除去するとともに、前記ゲート電極の側面に前記窒化珪素膜の一部を残すことを特徴とする半導体装置の作製方法。

**【請求項 6】**

請求項 4 または請求項 5 において、

前記半導体基板として、N型またはP型の単結晶シリコン基板、GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、ZnSe基板、貼り合わせ法またはSIMOX (Separation by Implanted Oxygen) 法を用いて作製された基板のいずれかを用いることを特徴とする半導体装置の作製方法。

**【請求項 7】**

請求項 1 乃至請求項 6 のいずれか一項において、

前記混合ガスにおける臭化水素ガスの流量の割合は、混合ガスの総流量に対して 50 % と同じ、若しくはそれ以上とすることを特徴とする半導体装置の作製方法。

**【請求項 8】**

請求項 1 乃至請求項 7 のいずれか一項において、前記半導体装置は、デジタルビデオカメラ、デジタルカメラ、反射型プロジェクター、ディスプレイ、ヘッドマウントディスプレイ、ナビゲーションシステム、音響再生装置、携帯型の情報端末、ゲーム機器、コンピュータ、および記録媒体を備えた画像再生装置の中から選ばれた一であることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】**

10

20

30

40

50

## 【0001】

本発明は、薄膜トランジスタ（TFT）を作製する過程で、ゲート電極の側面に窒化珪素からなるサイドウォールを形成する方法、およびこの処理を行って作製した半導体装置およびその作製方法に関する。

## 【背景技術】

## 【0002】

半導体素子の微細化、高集積化に関して、多くの研究開発が進められている。特に、MOS型トランジスタの微細化技術の進歩はめざましい。MOSとは、Metal-Oxide-Semiconductorの頭文字を取り、「金属-酸化物-半導体」の3種類の材料（物質）を組み合わせた構造を示す。

10

## 【0003】

ここで金属とは、純粋な金属だけを意味するのではなく、十分に導電率の大きな半導体材料や、半導体と金属の合金なども含めた広い意味で使用される。また、酸化物とは、純粋な酸化物だけではなく、窒化物等の十分に抵抗の大きな絶縁性材料が用いられることがある。これらの場合でも慣用的にMOSと呼ばれている。以下、本明細書では窒化物その他の絶縁物をも含めて、このような構造を有する電界効果型素子をMOS型トランジスタと称することとする。

## 【0004】

MOS型トランジスタは、Nチャネル型導電型およびPチャネル型導電型を問わず、一般的にチャネル形成領域、ゲート絶縁膜、ゲート電極、ソース領域、ドレイン領域を有している。このMOS型トランジスタは、高集積化しやすい特徴を持つため、集積回路を有するトランジスタ素子として広く用いられている。

20

## 【0005】

MOS型トランジスタの微細化は、ゲート電極の幅を小さくすることによって行われる。MOS型トランジスタの微細化に伴って、短チャネル効果やホットエレクトロンの発生を防止するために、ドレイン領域のチャネル形成領域側の不純物を低濃度化したLDD（Lightly Doped Drain）構造が用いられている。

30

## 【0006】

LDD構造を用いることによって、ドレイン領域のチャネル形成領域側への不純物の拡散量を低減し、チャネル長の長さを確保することができる。また、チャネル形成領域と不純物領域（ドレイン領域）の境界に形成されるpn接合部の不純物濃度分布の勾配が緩和されるため、この領域の電界集中を緩和させることができる。これによって素子の動作を安定化させることができた。

## 【0007】

LDD領域を形成する際、ゲート電極の両端部にサイドウォールを形成する。窒化珪素（SiN）でサイドウォールを形成する場合、SF<sub>6</sub>やCF<sub>4</sub>などのフッ素系ガスを用いて、RIE（Reactive Ion Etching：反応性イオンエッティング）方式のドライエッティング装置でエッティングを行う。

40

## 【0008】

窒化珪素膜のエッティングには、CF<sub>4</sub>、C<sub>2</sub>F<sub>6</sub>とO<sub>2</sub>の混合ガス、NF<sub>3</sub>、CH<sub>2</sub>F<sub>2</sub>などのフッ素原子を含むガスが従来用いられている。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0009】

半導体装置を作製する際には、構造面および電気的特性面から最適な配置及び寸法を設計する。

構造面に関しては、半導体装置を構成するトランジスタなどの能動素子、抵抗や容量などの受動素子、素子間を電気的に分離するための素子分離、さらには配線などをどのような構造にするかを設計する。この際、それぞれの最小パターン寸法に関するルールなどに従い、寸法を決定する。

50

また、電気的特性に関しては、トランジスタ特性、ゲート電極とソース領域およびゲート電極とドレイン領域のオーバーラップ容量、ゲート電極とソース領域およびゲート電極とドレイン領域の抵抗、ソース領域およびドレイン領域の抵抗、配線の抵抗や寄生容量、コンタクトホールのコンタクト抵抗などを考慮する必要がある。

#### 【0010】

そのため、設計値通りに半導体装置を作製することは、半導体装置の性能を最適にするために必要なことである。

#### 【0011】

ところが、フッ素原子を含むガスを用いて、RIE装置によって窒化珪素膜のエッチングを行うと、窒化珪素膜のエッチングが等方的に進行する。このため、窒化珪素膜をゲート電極の側面だけに、エッチング前の窒化珪素膜の膜厚と同程度の幅に残すことができなかつた。

#### 【0012】

一例を挙げると、厚さが400nmのゲート電極上に窒化珪素膜を300nm形成し、SF<sub>6</sub>とCF<sub>4</sub>の混合ガスを用いてエッチング処理を行うと、サイドウォールの幅は100nm以下になってしまふ。このサイドウォールを用いて作製するLDD領域の幅も小さくなってしまう。

#### 【0013】

本発明の課題は、上述した従来技術の問題点を解決することである。その目的は、窒化珪素膜をエッチングする際にサイドウォールの寸法の変化を抑制し、これによって、LDD領域を形成する際の加工精度を高めることである。

#### 【課題を解決するための手段】

#### 【0014】

そこで、上記の目的を達成するために、本発明は以下の構成を有する。

#### 【0015】

本発明で開示する発明の一つは、半導体膜上にゲート電極を形成し、このゲート電極上に窒化珪素膜を形成し、主に臭化水素(HBr)を含む混合ガスを用いてドライエッチングをすることによって、ゲート電極上および前記半導体膜上の窒化珪素膜を除去するとともに、ゲート電極の側面に窒化珪素からなるサイドウォールを形成することを特徴とする半導体装置の作製方法である。以下に主に臭化水素(HBr)を含む混合ガスの定義を示す。主に臭化水素(HBr)を含む混合ガスとは、混合ガスの総流量に対して臭化水素ガスの流量が50%、若しくはそれ以上の割合であることを指している。

#### 【0016】

また、他の発明の構成は、半導体膜上にゲート電極を形成し、このゲート電極上に窒化珪素膜を形成し、臭化水素(HBr)および塩素(Cl<sub>2</sub>)を含む混合ガスを用いて窒化珪素膜を選択的にエッチングし、ゲート電極の側面に窒化珪素からなるサイドウォールを形成することを特徴とする半導体装置の作製方法である。前記混合ガスは、混合ガスの総流量に対して臭化水素ガスの流量が50%、またはそれ以上の割合である。また、他の発明の構成は、半導体膜上にゲート電極を形成し、このゲート電極上に窒化珪素膜を形成し、ゲート電極の側面に窒化珪素を残すためのエッチングを混合ガスで行う半導体装置の作製方法であり、混合ガスは、臭化水素(HBr)と塩素(Cl<sub>2</sub>)と酸素を含むことを特徴としている。なお、前記混合ガスは、混合ガスの総流量に対して臭化水素ガスの流量が50%、若しくはそれ以上の割合である。

#### 【0017】

なお、上記構成において、半導体膜は絶縁性物質からなる基板に形成されている。絶縁性物質からなる基板の例として、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板、ステンレス基板、またはプラスチックやアクリルなどの合成樹脂からなる基板を挙げることができる。

#### 【0018】

また、他の発明の構成は、半導体膜上にゲート電極を形成し、このゲート電極上に窒化

10

20

30

40

50

珪素膜を形成し、主に臭化水素( HBr )を含む混合ガスを用いてドライエッチングすることによって、ゲート電極上および前記半導体膜上の窒化珪素膜を除去するとともに、ゲート電極の側面に窒化珪素からなるサイドウォールを形成することを特徴とする半導体装置の作製方法である。この主に臭化水素( HBr )を含む混合ガスは塩素( Cl<sub>2</sub> )を含む。

【 0019 】

また、他の発明の構成は、半導体膜上にゲート電極を形成し、このゲート電極上に窒化珪素膜を形成し、臭化水素( HBr )および塩素( Cl<sub>2</sub> )及び酸素( O<sub>2</sub> )を含む混合ガスを用いて窒化珪素膜を選択的にエッチングし、ゲート電極の側面に窒化珪素からなるサイドウォールを形成することを特徴とする半導体装置の作製方法である。なお、前記混合ガスは、混合ガスの総流量に対して臭化水素ガスの流量が 50 %、若しくはそれ以上の割合である。

【 0020 】

なお、上記構成において、半導体膜を形成する基板として( 1 ) 単結晶シリコン基板または化合物半導体基板、( 2 ) S O I ( Silicon on Insulator ) 基板を用いることができる。それぞれ代表的には、( 1 ) N型またはP型の単結晶シリコン基板、G a A s 基板、I n P 基板、G a N 基板、S i C 基板、サファイア基板、Z n S e 基板、( 2 ) 貼り合わせ法またはS I M O X ( Separation by I M p l a n t e d O X y g e n ) 法を用いて作製された基板、などを挙げることができる。

【 0021 】

なお、上記構成において、エッチング方法は、平行平板型 R I E ( 反応性イオンエッチング ) 、マグネットロン型 R I E 、 2 周波型 R I E 、マイクロ波型 R I E 、 E C R ( 電子サイクロトロン共鳴 ) プラズマエッチング、ヘリコン型プラズマエッチング、 I C P ( I n d u c t i v e l y C o u p l e d P l a s m a : 誘導結合型プラズマ ) 型プラズマエッチング等のドライエッチング法を用いることを特徴とする。

【 0022 】

臭化水素を含むガスを用い、上記のエッチング方法を用いると、このガスはプラズマによって分解されたのちに高周波によって加速され、窒化珪素膜の表面に物理的に衝突し、窒化珪素膜と反応する。この反応で生成した四臭化珪素が側壁に付着することによって、横方向のエッチングが阻害される。その結果、異方性エッチングが可能になる。

【 0023 】

また、本発明を用いて薄膜トランジスタ( T F T )を形成し、この T F T を用いた半導体装置としては、代表的には、C P U ( C e n t r a l P r o c e s s i n g U n i t : 中央演算処理装置 ) 、メモリ、I C 、R F I D 素子、画素、ドライバ回路などを挙げることができる。さらに、これらの半導体装置を組み込んで、テレビ、コンピュータ、携帯型の情報処理端末、などのさまざまな電子機器を形成することも可能である。

【 発明の効果 】

【 0024 】

本発明を用いることにより、窒化珪素膜のエッチングにおいて、フッ素原子を含むガスを用いた場合と比較して高い異方性が得られる。そのため、窒化珪素膜のエッチング時にサイドウォールの幅の寸法変化を少なくすることができる。さらには、このサイドウォールに合わせて L D D 領域を良好に形成することが可能となる。

【 発明を実施するための最良の形態 】

【 0025 】

以下に本発明の実施の様態を、図面を用いて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

【 0026 】

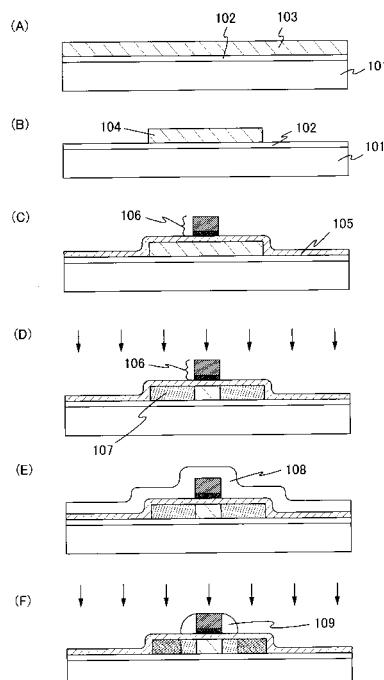

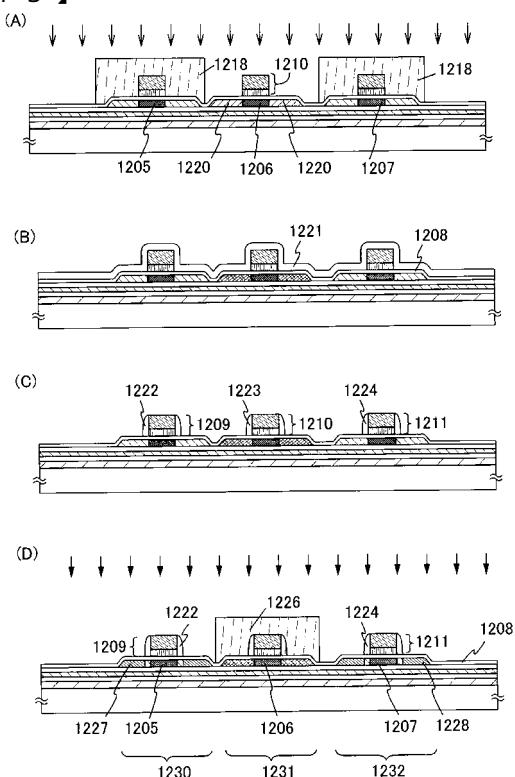

図 1 を用いて本発明の実施の形態を説明する。

10

20

30

40

50

## 【0027】

まず、図1(a)に示すように、絶縁性基板101に珪素を主成分とする絶縁性物質からなる下地膜102を形成する。ここで、絶縁性基板101とは、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミックス基板、ステンレス基板、PET(Polyethylene Terephthalate:ポリエチレンテレフタラート)、PES(Polyether sulfone Resin:ポリエーテルスルホン)、PEN(Polyethylene Naphthalate:ポリエチレンナフタレート)に代表されるプラスチックや、アクリルなどに代表される合成樹脂を原料とする基板を用いることができる。さらに、下地膜102上に非晶質半導体膜103を形成する。

10

## 【0028】

非晶質半導体膜103にレーザ照射を行うことによって結晶性半導体膜とし、この結晶性半導体膜を所定の形状に整形する処理を行うことによって、島状の半導体膜104を形成する。なお、非晶質半導体膜103の結晶化には、レーザ照射だけでなく、電熱炉を用いたファーネスアニール法やランプを用いた高速熱処理法(RTA)などを用いることができる。

## 【0029】

次に、半導体膜104を覆うようにゲート絶縁膜105を形成する。ゲート絶縁膜105はプラズマCVD法またはスパッタ法を用いて、40nm以上150nm以下の膜厚で形成する。その上に、導電膜として窒化タンタル(TaN)とタンゲステン(W)をプラズマCVD法またはスパッタ法を用いて合計400nmになるように形成し、この導電膜を所定の形状に整形することによってゲート電極106を形成する。

20

## 【0030】

次に、Nチャネル型TFTを形成する場合には、半導体膜104にリン(P)をイオン注入し、低濃度のN型領域107を形成する。このとき、ゲート電極106がイオン注入のマスクの役割をするため、N型領域はゲート電極106と自己整合的に形成される。同様に、Pチャネル型TFTを形成する場合には、半導体膜104にホウ素(B)をイオン注入して、低濃度のP型領域を形成する。

## 【0031】

エッチング終了点は、エッチングの時間経過に伴うプラズマの発光スペクトルの波形を観測することによって決定する。すなわち、窒化珪素膜をエッチングする際に、発光するエッチングガスまたは生成する反応生成物の発光強度の変化をとらえてエッチングの終点を決める。

30

## 【0032】

サイドウォール109を形成する場合には、まずゲート電極上や基板上に形成されている窒化珪素膜108が徐々にエッチングされる。この段階では発光スペクトルの強度は一定である。さらにエッチングが進むと、ゲート電極上や基板上の窒化珪素が完全にエッチングされ、窒化珪素膜がゲート電極の側面部に残るだけになる。このような状態になると、発光強度がエッチング開始時より弱くなる。この発光強度の変化をとらえてエッチングの終点が決定される。

40

## 【実施例1】

## 【0033】

半導体素子の作製方法について、図面を参照して説明する。なお、本実施例では、絶縁性基板に半導体膜を形成し、この半導体膜を用いてTFTを作製する場合を示す。

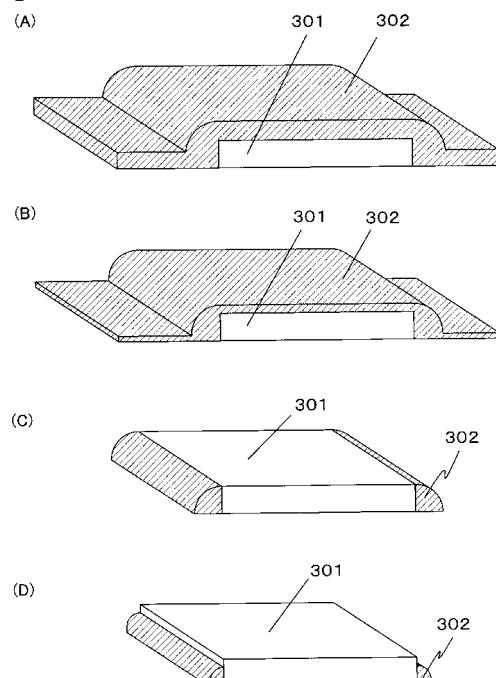

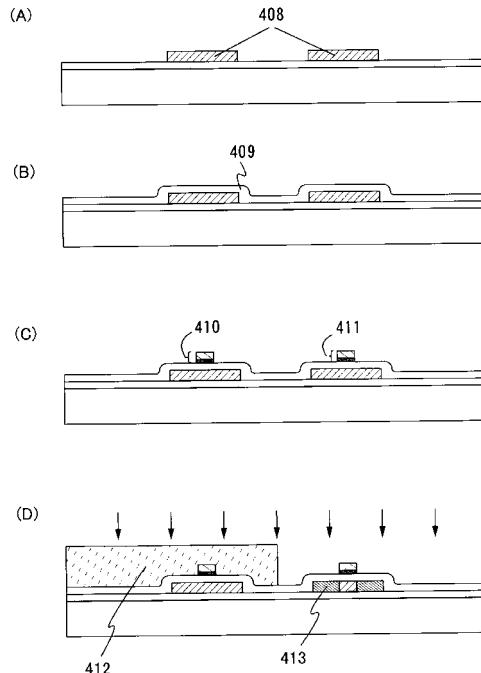

## 【0034】

図4(A)に示すように、絶縁表面を持つ基板401に下地膜402を形成する。本実施例では、基板401としてガラス基板を用いる。なお、ここで用いる基板には、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミックス基板、ステンレス基板などを用いることができる。また、PET(ポリエチレンテレフタラート)、PES(ポリエーテルスルホン)、PEN(ポリエチレンナフタレート)

50

に代表されるプラスチックや、アクリルなどに代表される合成樹脂を原料とする基板は、一般的に他の基板と比較すると耐熱温度が低い傾向であるが、本作製工程の処理温度に耐えることができるものであれば用いることができる。

#### 【0035】

下地膜402は、基板401に含まれるナトリウムなどのアルカリ性金属が半導体中に拡散し、半導体素子の特性に悪影響を及ぼすのを防ぐために用いる。このため、アルカリ金属やアルカリ土類金属の半導体中への拡散を抑えることのできる酸化珪素や窒化珪素、窒化酸化珪素などの絶縁物質を用いて形成する。また、下地膜402は単層または積層構造のいずれでも良い。本実施例では、プラズマCVD法 (Chemical Vapour Deposition: 化学気層成長法) を用いて窒化酸化珪素膜を10nm以上400nm以下の膜厚になるように成膜した。

#### 【0036】

なお、基板401としてガラス基板またはプラスチック基板のようにアルカリ金属やアルカリ土類金属が多少なりとも含まれている基板を用いている場合には、不純物の拡散を防ぐために下地膜を設けることは有効であるが、石英基板など不純物の拡散がさほど問題にならない基板を用いる場合には必ずしも下地膜402を設ける必要はない。

#### 【0037】

次いで、下地膜402上に非晶質半導体膜403を形成する。非晶質半導体膜403は、公知の方法 (スパッタリング法、LPCVD法、プラズマCVD法など) により、10nm以上100nm以下 (好ましくは30nm以上60nm以下) の厚さで形成する。ここで用いる非晶質半導体膜403は、珪素やシリコンゲルマニウムなどを用いることができるが、ここでは珪素を用いる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は0.01atomic%以上4.5atomic%以下の程度であることが好ましい。

#### 【0038】

なお、良好な結晶構造を得るために、非晶質半導体膜403中の酸素、窒素などの不純物元素濃度を $5 \times 10^{18}$ atomic/cm<sup>3</sup>以下に低減させておくと良い。また、大気に曝さずに下地膜402と非晶質半導体膜403とを連続成膜すると、界面汚染を防ぐことができるため好ましい。

#### 【0039】

次に、非晶質半導体膜403上にスピンドローティング法やディップコート法といった方法により、ニッケル(Ni)を代表とする金属元素を含む溶液 (水溶液や酢酸溶液) を一面に塗りつけて、金属元素を含む膜404を形成する。なお、この膜は極めて薄いため膜として観測できない場合もある。本実施例では、スピンドローティング法により、重量換算で1pm以上100ppm以下のニッケルを含む酢酸ニッケル溶液を一面に塗りつける。また、金属元素を含む膜404を形成する方法はこの方法に限らず、プラズマCVD法、スパッタ法、および蒸着法を用いて形成することもできる。

#### 【0040】

このとき、非晶質半導体膜403と酢酸ニッケル溶液との濡れ性を高め、非晶質半導体膜403の表面全体に溶液を行き渡らせるために、酢酸ニッケル溶液を一面に塗りつける前に、酸素雰囲気中の紫外光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水または過酸化水素による処理などを行い、1nm以上5nm以下の厚さの酸化膜を非晶質半導体膜403上に形成するとよい。このようにして薄い酸化膜を形成することにより、金属元素を含む水溶液を均一に非晶質半導体膜403上に塗りつけることができる。

#### 【0041】

なお、本実施例では触媒元素としてニッケル(Ni)を用いているが、その以外にも、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Plt)、銅(Cu)、金(Au)といった元素を用いても良い。

#### 【0042】

10

20

30

40

50

次に、非晶質半導体膜403を結晶化するための加熱処理を行い、第1の半導体膜を形成する。加熱処理の方法は、電熱炉を用いたファーネスアニール法や、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどを用いた瞬間熱アニール法（RTA法）や、ガス加熱式の瞬間熱アニール法（GRTA法）を用いることができる。

【0043】

さらに、第1の半導体膜の結晶性を向上させ、結晶粒内に残される欠陥を補修するために、第1の半導体膜にレーザ光またはレーザ光と同等の強度を持つ強光を照射すると良い。ここでは公知のレーザアニール装置を用いて、第1の半導体膜にレーザを照射する。

【0044】

以上の工程を経て形成された第2の半導体膜405には、金属元素が残存している。そこで、第2の半導体膜405内に存在する触媒元素のゲッタリングを行う。ゲッタリングによって、半導体膜中に存在する金属元素を除去することができるため、オフ電流を低減することが可能である。

【0045】

まず、図4（B）に示すように第2の半導体膜405の表面に酸化膜406を形成する。1nm以上10nm以下程度の膜厚を有する酸化膜406を形成することで、後のエッティング工程において第2の半導体膜405の表面がエッティングにより荒れるのを防ぐことができる。なお、酸化膜406は公知の方法を用いて形成することができる。例えば、硫酸、塩酸、硝酸などと過酸化水素水を混合させた水溶液や、オゾン水で、第2の半導体膜405の表面を酸化することで形成しても良いし、酸素を含む雰囲気中のプラズマ処理や、加熱処理、紫外線照射等により形成しても良い。また酸化膜406を別途、プラズマCVD法やスパッタ法、蒸着法などで形成しても良い。

【0046】

次に、図4（C）に示すように、希ガス元素を $1 \times 10^{20}$ atoms/cm<sup>3</sup>以上の濃度で含むゲッタリング用の半導体膜407を酸化膜406上に、スパッタ法を用いて25nm以上250nm以下の厚さで形成する。半導体膜407は、第2の半導体膜405とエッティングの選択比を大きくするため、第2の半導体膜405よりも膜の密度の低い方がより望ましい。希ガス元素としてはヘリウム（He）、ネオン（Ne）、アルゴン（Ar）、クリプトン（Kr）、キセノン（Xe）から選ばれた一種または複数種を用いる。

【0047】

次に、図4（D）に示すように、ファーネスアニール法やRTA法を用いて加熱処理を施し、ゲッタリングを行う。ファーネスアニール法で行なう場合には、窒素雰囲気中にて450以上600以下で0.5~12時間の加熱処理を行なう。また、RTA法を用いる場合には、加熱用のランプ光源を1~60秒、好ましくは30~60秒点灯させ、それを1~10回、好ましくは2~6回繰り返す。ランプ光源の発光強度は任意なものとするが、第2の半導体膜405が瞬間的には600以上1000以下、好ましくは700以上750以下の程度にまで加熱されるようにする。

【0048】

加熱処理により、第2の半導体膜405内の触媒元素が、拡散により矢印に示すようにゲッタリング用の半導体膜407に移動し、ゲッタリングされる。

【0049】

次に、ゲッタリング用の半導体膜407を選択的にエッティングして除去する。エッティングは、ClF<sub>3</sub>によるプラズマを用いないドライエッティング、或いはヒドラジンや、テトラメチルアンモニウムハイドロオキサイド（（CH<sub>3</sub>）<sub>4</sub>NOH）を含む水溶液などアルカリ溶液によるウェットエッティングで行なうことができる。このとき酸化膜406によって第2の半導体膜405がエッティングされるのを防ぐことができる。

【0050】

次に酸化膜406をフッ酸により除去した後、第2の半導体膜405を所定の形状に整形し、島状の半導体膜408を形成する（図5（A））。ここで形成した半導体膜408

10

20

30

40

50

を用いて TFT に代表される各種の半導体素子を形成することができる。なお、本発明においてゲッタリング工程は、本実施例に示した方法に限定されない。その他の方法を用いて半導体膜中の触媒元素を低減するようにしても良い。

#### 【 0 0 5 1 】

このように形成された結晶性の半導体膜 408 は、金属元素の作用により細長い棒状、または細長い扁平状の結晶となり、各結晶は巨視的に見るとある所定の方向に結晶成長している。

#### 【 0 0 5 2 】

次に、半導体膜 408 にホウ素 (B) を添加する (チャネルドープ)。例えばドーピング法、イオン注入法を用いることができる。この処理により、半導体特性であるしきい値をよりゼロに近づかせることができる。つまり、結晶性半導体膜をより真性に近い状態にすることができる。

#### 【 0 0 5 3 】

続いて、半導体膜 408 を覆うようにゲート絶縁膜 409 を形成する。ゲート絶縁膜 409 はプラズマ CVD 法またはスパッタ法を用いて、40 nm 以上 150 nm 以下の膜厚で形成する。なお、ゲート絶縁膜 409 は、少なくとも酸素または窒素を含む絶縁膜であれば良く、単層でも複層でも良い。本実施例では、プラズマ CVD 法で酸素を含む窒化珪素 (SiNO) と、窒素を含む酸化珪素 (SiON) を連続成膜して、合計膜厚が 115 nm になるように形成した。なお、ゲート絶縁膜 409 はこれらの材料に限らず、高誘電率物質 (high-k 材料ともいう) のタンタル酸化物、酸化ハフニウム (HfO<sub>2</sub>)、窒素添加ハフニウムシリコン酸化物 (HfSiON)、酸化ジリコニウム (ZrO<sub>2</sub>)、酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>)、または酸化ランタン (La<sub>2</sub>O<sub>3</sub>) などの希土類酸化物も用いることができる。

#### 【 0 0 5 4 】

なお、チャネル長の長さが 1 μm 以下であるような TFT (サブミクロン TFT ともいう) を形成する場合、ゲート絶縁膜 409 は 10 nm 以上 50 nm 以下の厚さで形成することが望ましい。

#### 【 0 0 5 5 】

次に、ゲート絶縁膜 409 上に導電膜を形成し、エッチングすることによってゲート電極 410、411 を形成する。その概要は以下の通りになる。ゲート絶縁膜 409 上に形成する導電膜の材料は導電性を有する膜であればよい。本実施例では TaN (窒化タンタル) を 30 nm 形成し、さらに W (タンゲステン) を 370 nm 形成した膜を用いる。この導電膜を加工するためのレジストマスクを形成し、このレジストマスクを基に導電膜を所定の形状に整形してゲート電極 410、411 を形成する。

#### 【 0 0 5 6 】

なお、これに限らず、Al (アルミニウム) と Mo (モリブデン) を用いて Mo、Al、Mo の順に形成した導電膜や、Ti (チタン) と Al を用いて Ti、Al、Ti の順に形成した導電膜を用いても良い。また、金 (Au)、銀 (Ag)、銅 (Cu)、白金 (Pt)、アルミニウム (Al)、モリブデン (Mo)、タンゲステン (W)、チタン (Ti) から選ばれた元素、またはこれらの元素を主成分とする合金材料または化合物材料を用いることができる。さらには、これらの材料の積層物を用いてもよい。特にゲート絶縁膜 409 を先述の高誘電率物質 (high-k 材料) を用いて形成した場合では、上記の金属からなる材料を用いてゲート電極 410、411 を形成すると、ゲート電極 410、411 の空乏化を解消し、大量の電流を流すことができるようになるため、半導体素子の低電力化に貢献する。

#### 【 0 0 5 7 】

ゲート絶縁膜 409 上に導電膜を形成し、さらにこの導電膜をパターン成形するためのレジストマスクを形成する。その工程は、導電膜上にフォトレジストをスピンドルティング法などにより一面に塗りつけ、露光を行う。次に、フォトレジストに対して加熱処理 (プリベーク) を行う。プリベークの温度は 50 ~ 120 ℃ とし、後に行われるポストベー

10

20

30

40

50

クより低い温度で行う。本実施例では、加熱温度は90、加熱時間は90秒とした。

#### 【0058】

フォトレジストを露光させた後、フォトレジストに現像液を滴下するか、あるいはスプレーノズルから現像液をスプレーすることによって、フォトレジストを現像する。

#### 【0059】

その後、現像されたフォトレジストを125、180秒で加熱処理を行ういわゆるポストペークを行い、レジストマスク中に残っている水分などを除去し、同時に熱に対する安定性を高める。以上の工程によってレジストマスクが形成される。このレジストマスクを基に導電膜を加工して、ゲート電極410、411を形成する。

#### 【0060】

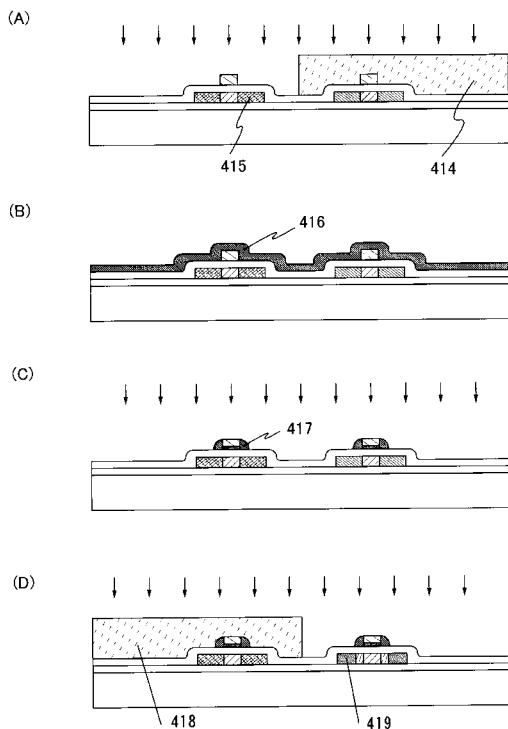

次に、Pチャネル型TFTを形成する部分をレジスト412で覆い、N型不純物のヒ素(A s)やリン(P)を導入し、N型不純物領域413を形成する(図5(D))。本実施例では、ホスフィン(PH<sub>3</sub>)を60～80keVで導入する。また、同様にしてNチャネル型TFTを形成する部分をレジスト414で覆い、P型不純物であるホウ素(B)を導入し、P型不純物領域415を形成する(図6(A))。本実施例では、ジボラン(B<sub>2</sub>H<sub>6</sub>)を30～45keVで導入する。

#### 【0061】

次に、図6(B)に示すように、レジスト414を剥離し、全面に窒化珪素膜416を300nm形成する。窒化珪素膜416の形成はプラズマCVD法などを用いて行うことができる。さらに、図6(C)に示すように、窒化珪素膜416を、臭素を含むガスを用いてドライエッティングを行った。本実施例では、臭化水素、塩素、および酸素の流量を100:44:6の比になるように混合してエッティング用のガスとし、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)装置を用いてドライエッティングを行った。なお、圧力は1.6Pa、ICPの高周波は450W、BIASの高周波は150Wである。ICPに印加する高周波はプロセスガスを分解する役割を持ち、BIASに印加する高周波は、エッティング種(イオン)を加速する役割を持つ。この工程により、ゲート電極410、411の側面にサイドウォール417が形成された。

#### 【0062】

なお、この条件で窒化珪素と酸化珪素のエッティングレートの比は5.04を達成した。このことは、酸化珪素をゲート絶縁膜として、窒化珪素膜を異方性エッティングすることが可能であることを意味している。従って、サイドウォールを窒化珪素膜で形成することが可能となる。

#### 【0063】

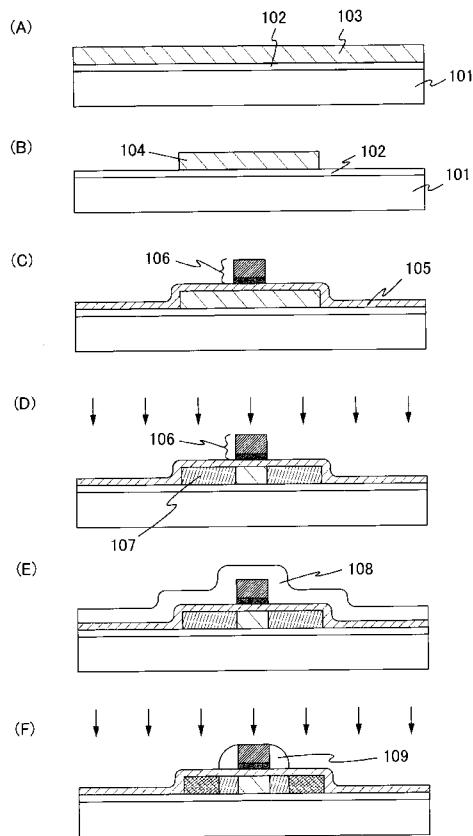

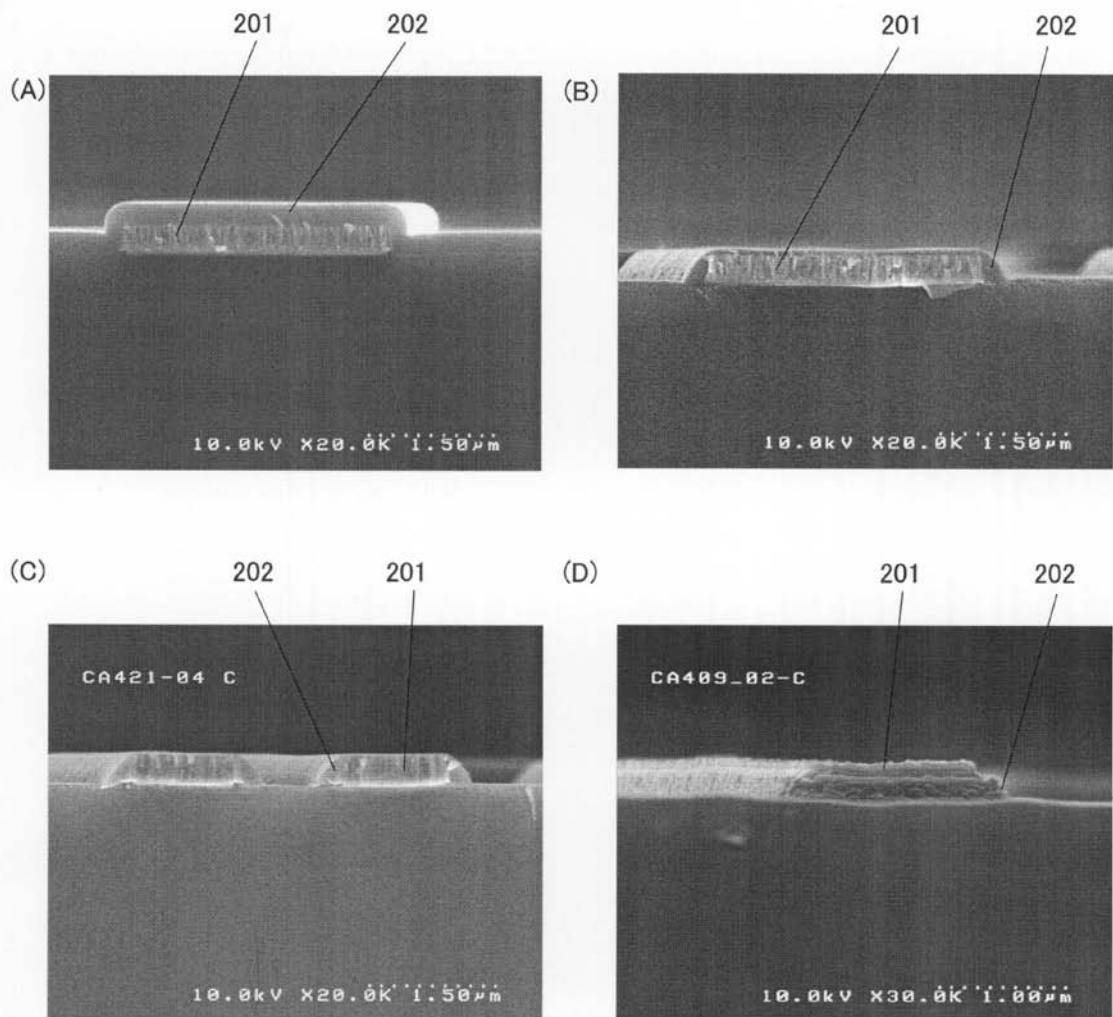

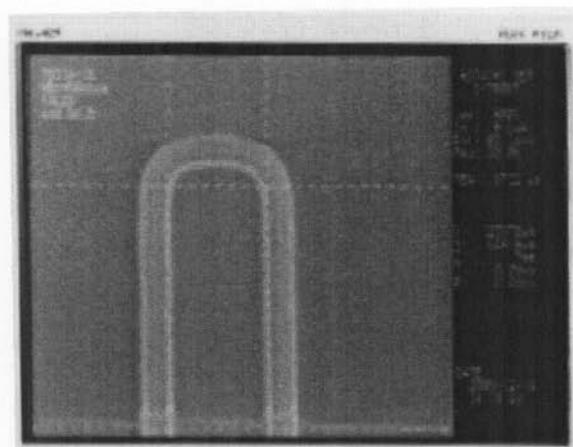

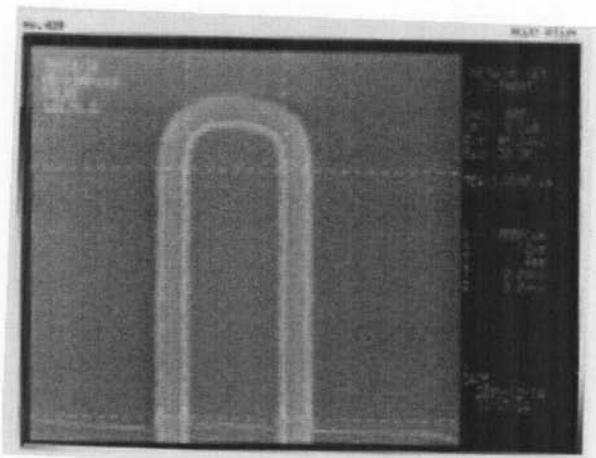

HBrガスを用いてエッティングを行う過程における断面の状態を図2(A)～(D)および図3(A)～(D)に示す。なお、図2は断面の状態を電子顕微鏡で撮影したものであり、図3に対応する図2において、201は半導体膜、202は窒化珪素膜であり、図3において301は半導体膜、302は窒化珪素膜である。

#### 【0064】

図2(A)及び図3(A)は、エッティング処理前、図2(B)及び図3(B)はエッティング開始から200秒経過後、図2(C)及び図3(C)は、エッティング開始から240秒経過後を示す。なお、エッティング開始から240秒後をエッティング終了点とした。また、図2(D)及び図3(D)は、窒化珪素膜202および302が過剰にエッティングされ、半導体膜201および301が露出した状態を示す(エッティング開始から260秒後)。また、処理時間によるサイドウォールの幅を表1に示す。処理開始から240秒後(エッティング終了点)におけるサイドウォールの幅の平均値は236nmであり、エッティング開始前の窒化珪素膜の膜厚とほぼ同程度の幅でサイドウォールが形成される。

## 【表1】

| 塗化珪素のサイドウォール幅 |     | [nm] |      |

|---------------|-----|------|------|

| 処理時間          | 0秒  | 200秒 | 240秒 |

| 基板中央部         | 210 | 259  | 249  |

|               | 240 | 270  | 242  |

| 基板周辺部         |     | 231  | 224  |

|               |     | 231  | 231  |

| 平均            | 225 | 248  | 236  |

## 【0065】

なお、本実施例ではドライエッティングの方法としてICP法を用いているが、この方法には限らない。同様にして、平行平板型RIE（反応性イオンエッティング）、マグネットロング型RIE、2周波型RIE、マイクロ波型RIE、ECR（電子サイクロトロン共鳴）プラズマエッティング、ヘリコン型プラズマエッティングなどのエッティング方法を用いることができる。

## 【0066】

次に、図6(D)に示すように、P型TFTになる部分をレジスト418で覆い、N型の導電性を示すイオンの導入を行い、LDD領域419を形成する、なお、先程よりも高いドーズ量でN型の導電性を示すイオンを導入する。同様にして、図7(A)に示すように、N型TFTになる部分をレジスト420で覆い、P型の導電性を示すイオンの導入を行い、LDD領域421を形成する。こちらも、先程よりも高いドーズ量でP型の導電性を示すイオンを導入する。

## 【0067】

以上のようにして、不純物の導入が終了したら、レーザアニール、ランプアニール、またはファーネスアニールによって処理を行い、導入した不純物の活性化と、不純物の導入に伴う結晶性の損傷を回復させる。

## 【0068】

上記の工程によって、Pチャネル型TFT422とNチャネル型TFT423を同一基板上に形成することができる。

## 【0069】

続いて、図7(B)に示すように、これらの保護膜として絶縁膜424を形成する。この絶縁膜424は、プラズマCVD法またはスパッタ法を用い、塗化珪素膜または塗化酸化珪素膜を単層または積層構造で100nm以上200nm以下の厚さに形成する。塗化酸化珪素膜と酸化珪素膜を組み合わせる場合では、ガスを切り替えることによって連続成膜をすることが可能である。本実施例では、プラズマCVD法により膜厚100nmの酸化珪素膜を形成した。絶縁膜424を設けることにより、酸素や空気中の水分をはじめ、各種イオン性の不純物の侵入を阻止するブロッキング作用を得ることができる。

## 【0070】

次いで、さらに絶縁膜425を形成する。ここでは、SOG(Spin On Glass)法またはスピンドルコート法によって一面に塗りつけたポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリル、シロキサン(-Si-O-Si-)で表される珪素と酸素との結合(シロキサン結合)を構成の基本単位とし、珪素にフッ素、脂肪族炭化水素、または芳香族炭化水素などが結合した構造を持つ物質などの有機樹脂膜、無機層間絶縁膜(塗化珪素、酸化珪素などの珪素を含む絶縁膜)、LOW-K(低誘電率)材料などを用いることができる。絶縁膜425は、ガラス基板上に形成されたTFTによる凹凸を緩和し、平坦化する意味合いが強いため、平坦性に優れた膜が好ましい。

## 【0071】

さらに、フォトリソグラフィ法を用いてゲート絶縁膜409、絶縁膜424および絶縁膜425をパターン加工して、ソース領域426、427、およびドレイン領域428、429に達するコンタクトホールを形成する。

## 【0072】

10

20

30

40

50

次に、導電性材料を用いて導電膜を形成し、この導電膜をパターン加工することによって配線430を形成する。その後、保護膜として絶縁膜431を形成すると、図7(C)に示すような半導体装置が完成する。

#### 【0073】

本発明の半導体装置の作製方法は、上述したTFTの作製工程に限定されない。本実施例では、CMOS型のTFTを作製する過程を示しているが、N型のTFT、P型のTFT、またはこの双方を基板上に形成する際に本発明の半導体装置の作製方法を用いることもできる。

#### 【0074】

また、本発明を用いた半導体装置の作製方法は、ガラスなどの絶縁基板上に形成した半導体膜を用いて作製している。しかし、これだけに限らず、単結晶半導体基板を用いて同様にして作製することもできる。単結晶半導体基板の一例として、貼り合わせ法またはSIMOX (Separation by Implanted Oxygen) 法を用いて作製されたSOI (Silicon on Insulator) 基板、シリコンウエハーなどを用いることができる。

#### 【実施例2】

#### 【0075】

本実施例では、半導体基板を用いてCMOS型のICを作製する過程を、図を用いて説明する。

#### 【0076】

なお、本実施例で用いる半導体基板は、(1)単結晶シリコン基板または化合物半導体基板、(2)SOI (Silicon on Insulator) 基板を指す。(1)、(2)はそれぞれ代表的には、(1)N型またはP型の単結晶シリコン基板、GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、ZnSe基板、(2)貼り合わせ法またはSIMOX (Separation by Implanted Oxygen) 法を用いて作製された基板、などを挙げることができる。SOI基板を用いて半導体素子を作製すると、隣接する素子を完全に分離することができ、リーク電流が流れるのを防ぐことができる。

#### 【0077】

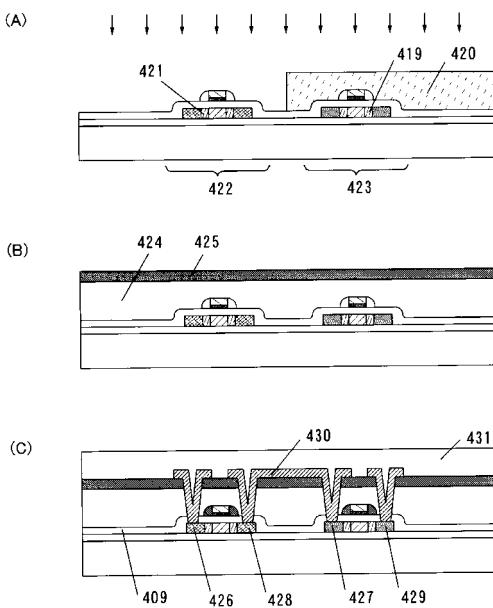

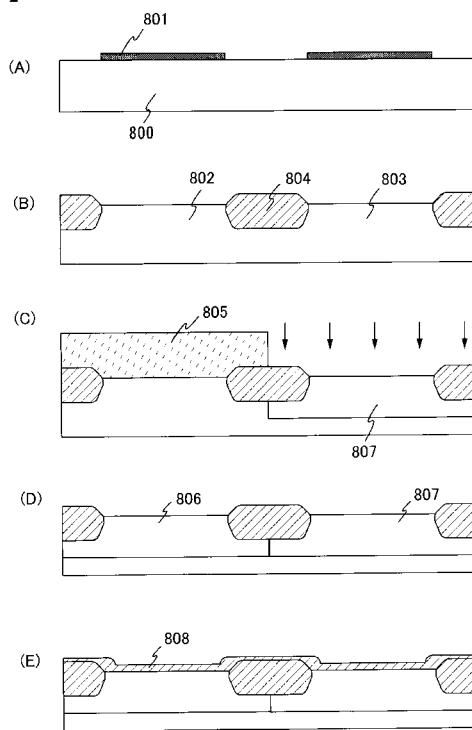

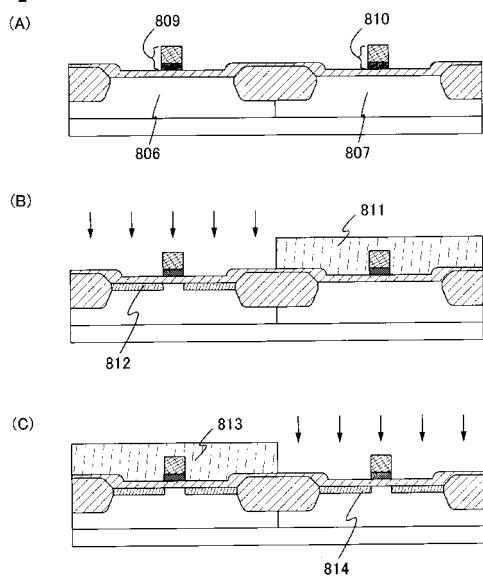

まず、単結晶シリコンからなるシリコン基板800を用意し、公知のLOCOS法またはシャロートレンチ分離法(STI法: Shallow Trench Isolation)を用いて、第1の素子形成領域802と第2の素子形成領域803を形成する。

#### 【0078】

なお、本実施例ではLOCOS法を用いている。具体的には、単結晶シリコン基板800を上に窒化珪素膜801を堆積する。後に活性領域となる部分を残して窒化珪素膜801を除去する(図8(A))。

#### 【0079】

そして、窒化珪素膜801をマスクにして、熱酸化法により厚い分離用の酸化珪素膜(フィールド酸化膜)804を形成する。次に、窒化珪素膜を熱リン酸で除去することによって、フィールド酸化膜804によって分離された第1の素子形成領域802および第2の素子形成領域803が形成される(図8(B))。

#### 【0080】

次に、第1の素子形成領域802にレジスト805で覆い、後にPチャネル型MOSトランジスタが形成される部分である第2の素子形成領域803にリン(P)をイオン注入し、P型ウェル807を形成する。同様にして、後にNチャネル型MOSトランジスタが形成される部分である第1の素子形成領域802にN型ウェル806を形成させる。(図8(C))。

#### 【0081】

次に、レジスト805を剥離し、第1の素子形成領域802、第2の素子形成領域803の表面を露出させる(図8(D))。その後、この表面に熱酸化法で酸化珪素を材料と

10

20

30

40

50

する薄いゲート絶縁膜 808 を形成させる(図8(E))。

【0082】

ゲート絶縁膜 808 の形成方法は、プラズマCVD法やスパッタ法などを用いればよい。例えば、熱酸化法によって得られる膜厚5nmの酸化珪素膜と、CVD法で得られる膜厚10nm以上15nm以下の酸化窒化珪素膜の積層膜を形成してもよい。また、ガスを切り替えることによって連続的に成膜を行うこともできる。

【0083】

なお、ゲート絶縁膜 808 は上記の材料に限らず、(1)酸化珪素膜、窒素を含む酸化珪素膜(SiON)、酸素を含む窒化珪素膜(SiNO)、窒化珪素膜、またはこれらの積層膜、(2)高誘電率物質(high-k材料ともいう)のタンタル酸化物、酸化ハフニウム(HfO<sub>2</sub>)、窒素添加ハフニウムシリコン酸化物(HfSiON)、酸化ジリコニウム(ZrO<sub>2</sub>)、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、または酸化ランタン(La<sub>2</sub>O<sub>3</sub>)などの希土類酸化物を用いることができる。

【0084】

次に、ゲート絶縁膜 808 上に導電膜を形成し、エッチングすることによって、ゲート電極 809、810 を形成する。その概要は以下の通りになる。まず、ゲート絶縁膜 808 上に形成する導電膜の材料は導電性を有する膜であればよい。本実施例ではTaN(窒化タンタル)を30nm形成し、さらにW(タンゲステン)を370nm形成した膜を用いる。この導電膜を加工するためのレジストマスクを形成し、このレジストマスクを基に導電膜をエッチングしてゲート電極 809、810 を形成する。

【0085】

なお、これに限らず、Al(アルミニウム)とMo(モリブデン)を用いてMo、Al、Moの順に形成した導電膜や、Ti(チタン)とAlを用いてTi、Al、Tiの順に形成した導電膜を用いても良い。また、金(Au)、銀(Ag)、銅(Cu)、白金(Pt)、アルミニウム(Al)、モリブデン(Mo)、タンゲステン(W)、チタン(Ti)から選ばれた元素、またはこれらの元素を主成分とする合金材料または化合物材料を用いることができる。さらには、これらの材料の積層物を用いてもよい。特にゲート絶縁膜 808 を先述の高誘電率物質(high-k材料)を用いて形成し、さらに上記の金属からなる材料を用いてゲート電極 809、810 を形成すると、ゲート電極 809、810 の空乏化を解消し、大量の電流を流すことができるようになるため、半導体素子の低電力化に貢献する。

【0086】

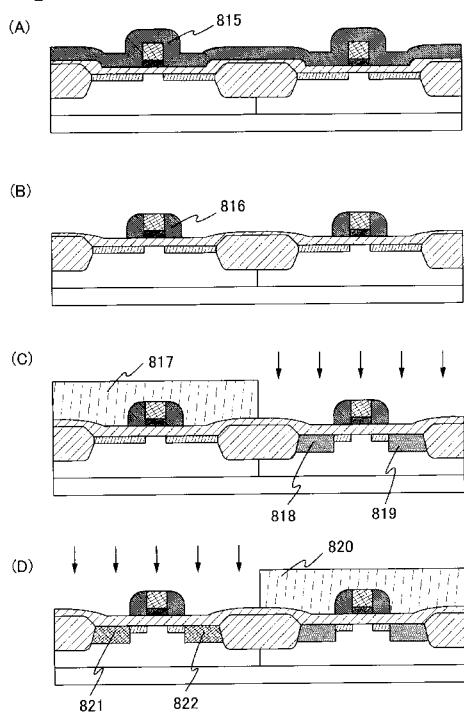

次に、図9(B)に示すように、Pチャネル型TFTを形成する部分をレジスト811で覆い、N型不純物のヒ素(As)やリン(P)を浅く導入し、N型不純物領域812を形成する。続いて、レジスト811を除去し、Nチャネル型TFTを形成する部分をレジスト813で覆い、P型不純物であるホウ素(B)を浅く導入し、P型不純物領域814を形成する(図9(C))。

【0087】

ここで、不純物元素を注入するのと同時に、ゲルマニウム(Ge)や0族の元素(Ar、Kr、Xe、Rnなど)などの質量数の大きい元素を打ち込み、単結晶格子を崩してもよい。この際、打ち込む速度を下げ、20nm程度の深さまで半導体膜をアモルファス化する。不純物の導入と質量数の大きい元素の打ち込みの順番は限定されるものではない。どちらを先にしても良いし、同時にあっても良い。

【0088】

シリコン基板800は原子が整然と配列している。特に<100>面や<111>面の場合では、導入された不純物が結晶の隙間を通り、基板の奥深くまで到達してしまう現象(チャネリング現象)が起きる。そこで、シリコン基板800に対して不純物の導入方向を傾斜させて注入すると、原子間の隙間を少なくすることができるため、導入された不純物が結晶の表面近傍でとどまりやすくなる。

【0089】

10

20

30

40

50

また、ゲート電極 809、810 の周囲には凹凸部分が存在するため、不純物や質量数が大きい元素が導入されない領域が生じやすくなる（シャドー効果という）ため、その防止としてシリコン基板 800 を連続的に回転させながら、導入と回転を交互に行ってよい。シリコン基板 800 に対して不純物や質量数の大きい元素の注入方向を相対的に斜めにし、さらにシリコン基板 800 を回転させながら不純物や質量の大きい元素の注入を行うと、チャネリング現象とシャドー効果の予防ができる。

#### 【0090】

さらに、不純物を導入された部分の活性化、および不純物の導入によって発生した半導体膜の結晶欠陥を回復するために、第1回目の活性化処理を行う。なお、この活性化処理は R T A 法、レーザアニール法などの公知の方法を用いて行うことができる。なお、ここでは浅く不純物を導入するため、パルス幅が小さい（1 フェムト秒以上 10 ピコ秒以下）レーザを用いると、表面から浅い部分のみを良好に活性化させることができる。

10

#### 【0091】

次に、図 10 (A) に示すように、レジスト 813 を除去し、全面に窒化珪素膜 815 を 300 nm 形成する。窒化珪素膜 815 の形成は、プラズマ C V D 法などを用いて行うことができる。さらに、図 10 (B) に示すように、窒化珪素膜 815 を、臭化水素 (HBr) を主とするガスを用いてドライエッチングを行い、サイドウォール 816 を形成した。本実施例では臭化水素、塩素、および酸素の流量を 100 : 44 : 6 の比になるように混合してエッチング用のガスとし、I C P (Inductive Coupled Plasma : 誘導結合型プラズマ) 装置を用いてドライエッチングを行った。この処理により、ゲート電極 809、810 の側面に窒化珪素からなるサイドウォールを良好に形成した。このサイドウォールの幅は、窒化珪素膜 815 の膜厚と同程度の長さである。

20

#### 【0092】

なお、本実施例ではドライエッチングの方法として I C P 法を用いているが、この方法には限らない。同様にして、平行平板型 R I E (反応性イオンエッチング)、マグネットロトン型 R I E、2 周波型 R I E、マイクロ波型 R I E、E C R (電子サイクロトロン共鳴) プラズマエッチング、ヘリコン型プラズマエッチングなどのエッチング方法を用いることができる。

#### 【0093】

次いで、ソース領域およびドレイン領域を形成するために、シリコン基板にイオン注入を行う。C M O S を形成する場合であるので、図 10 (C) に示すように、N チャネル型 T F T を形成する第1の素子形成領域 802 をレジスト 817 で覆い、P 型不純物のホウ素 (B) を第2の素子形成領域 803 に注入することによって、ソース領域 818、ドレイン領域 819 を形成する。また、同様にして P チャネル型 T F T を形成する第2の素子形成領域 803 をレジスト 820 で覆い、N 型不純物のリン (P) やヒ素 (As) を第1の素子形成領域 802 に注入することによって、ソース領域 821、ドレイン領域 822 を形成する (図 10 (D))。

30

#### 【0094】

次に、イオン注入された不純物の活性化およびイオン注入によって発生したシリコン基板の結晶欠陥を回復するために、第2回目の活性化処理を行う。この活性化処理は、R T A 法、レーザアニール法などの公知の方法を用いて行うことができる。

40

#### 【0095】

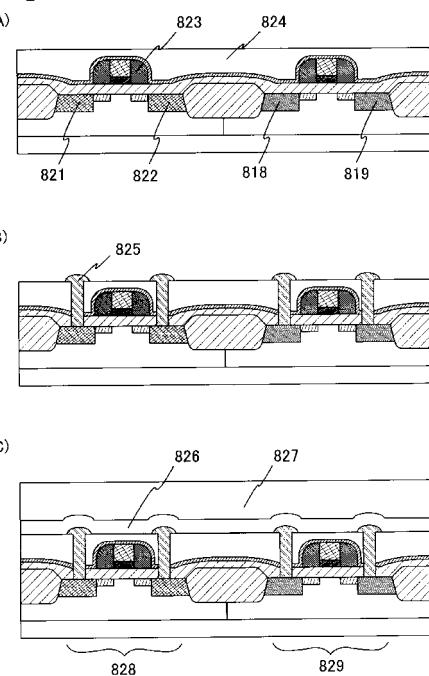

活性化の後、層間絶縁膜や配線などを形成する。図 11 (A) に示すように、第1の層間絶縁膜 823 は、プラズマ C V D 法や減圧 C V D 法を用いて、酸化シリコン膜や酸化窒化シリコン膜などで、100 nm 以上 2000 nm 以下の厚さに形成する。さらに第1の層間絶縁膜 823 の上にリンガラス (PSG)、ボロンガラス (BSG)、またはリンボロンガラス (P B S G) からなる第2の層間絶縁膜 824 を形成する。第2の層間絶縁膜 824 は、平坦性を上げるため、スピンドルコート法や常圧 C V D 法を用いて作製する。

#### 【0096】

続いて、図 11 (B) に示すように、第1の層間絶縁膜 823 および第2の層間絶縁膜

50

824に、それぞれTFTのソース領域およびドレイン領域に達するコンタクトホール(開口)を形成し、配線825をソース領域818、821およびドレイン領域819、822に接続する。ソース領域818、821およびドレイン領域819、822に接続する配線825の材料は、低抵抗材料として通常用いられるアルミニウム(A1)やアルミニウムとチタン(Ti)の積層物などを用いることができる。

#### 【0097】

また、ここでは図示していないが、ソース領域818、821およびドレイン領域819、822を形成するためのコンタクトホールを開口する際に、第1の層間絶縁膜823および第2の層間絶縁膜824に、ゲート電極809、810に達するコンタクトホールも同時に設け、第1の層間絶縁膜823上に設けられている配線と電気的に接続する電極が設けられる。

#### 【0098】

最後に、図11(C)に示すように、パッシベーション膜826と第3の層間絶縁膜827を形成する。図11(C)において、向かって左側がNチャネル型TFT828であり、右側がPチャネル型TFT829である。

#### 【0099】

パッシベーション膜826は、プラズマCVD法で窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜で形成されている。さらに、第3の層間絶縁膜827は、有機樹脂材料で1μm以上2μm以下の厚さに形成する。ここで用いる有機樹脂材料とは、ポリイミド、ポリアミド、アクリル、ベンゾシクロブテン(BCB)などを用いることができる。有機樹脂膜を用いる利点は、膜の形成が容易である点や、比誘電率が低いため寄生容量を低減できる点、膜の平坦化が容易である点などがある。なお、上述した以外の有機樹脂膜を用いてもよい。

#### 【0100】

なお、本実施例は実施の形態および他の実施例と組み合わせて用いることが可能である。

#### 【実施例3】

#### 【0101】

ここでは、本発明を用いて作製する半導体装置の1つの例として、薄膜集積回路、または非接触型薄膜集積回路装置(無線ICタグ、RFID(無線認証、Radio Frequency Identification Identification)とも呼ばれる)を作製する過程を図12～図16を用いて示す。

#### 【0102】

なお、無線ICタグの集積回路に用いられる半導体素子として絶縁分離されたTFTを用いた例を以下に示すが、無線ICタグの集積回路に用いられる半導体素子はTFTに限定されず、あらゆる素子を用いることができる。例えば、TFTの他に、記憶素子、ダイオード、光電変換素子、抵抗素子、コイル、容量素子、インダクタなどが代表的に挙げられる。

#### 【0103】

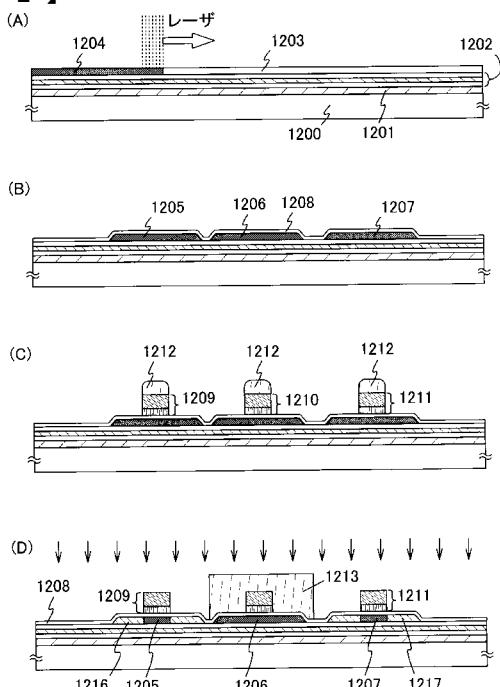

まず、図12(A)に示すように、スパッタ法を用いてガラス基板(第1の基板)1200上に剥離層1201を形成する。剥離層1201は、スパッタ法、減圧CVD法、プラズマCVD法等を用いて形成することができる。本実施例では、膜厚50nm程度の非晶質シリコンを減圧CVD法で形成し、剥離層1201として用いる。なお剥離層1201はシリコンに限定されず、エッチングにより選択的に除去できる材料(例えば、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)など)で形成すれば良く、上記の元素の単体、上記の元素を主成分とする合金材料、または上記の元素の化合物からなる膜を、単層または複数重ねた積層構造で形成する。剥離層1201の膜厚は、50nm以上60nm以下とするのが望ましい。

10

20

30

40

50

## 【0104】

また、剥離層1201を金属膜と金属酸化膜の2層構造で形成する場合には、金属膜と金属酸化膜をそれぞれスパッタ法またはプラズマCVD法で設けることができる。これ以外の方法では、上述の金属膜を形成した後に、酸素雰囲気下でプラズマ処理または加熱処理を行うことによって、金属膜表面上にその金属の酸化物を設けることもできる。なお、プラズマ処理には、高密度プラズマ処理も含まれる。

## 【0105】

高密度プラズマは、マイクロ波、例えば2.45GHzを用いることによって生成される。低電子温度が特徴である高密度プラズマは、活性種の運動エネルギーが低い。そのため、従来のプラズマ処理に比べると、プラズマダメージが少なく欠陥が少ない膜を形成することができる。

10

## 【0106】

また、剥離層1201として、金属酸化膜の他にも、金属窒化物、酸素を含む金属窒化物、窒素を含む金属酸化物を用いてもよい。金属窒化物を形成する場合は、窒素雰囲気下で金属膜にプラズマ処理や加熱処理を行えばよい。また、酸素を含む金属窒化物または窒素を含む金属酸化物を形成する場合には、窒素と酸素を含む雰囲気下で、金属膜にプラズマ処理や加熱処理を行えばよい。成膜される膜の種類は、用いるガスの流量比によって異なる。

20

## 【0107】

剥離層1201を形成するとき、表面に酸化物、窒化物、または窒化酸化物が形成される。これらの化合物はエッチングガス、特に3フッ化塩素(C1F3)との反応速度が高く、簡便かつ短時間に剥離することができる。つまり、エッチングガスによって金属、金属酸化物、金属窒化物、又は金属の窒化酸化物のいずれかが除去されれば、剥離が可能である。

20

## 【0108】

また、剥離層1201の表面に酸化物、窒化物、又は窒化酸化物が形成されるときに、化学的な状態に変化が生じることがある。例えば、タンゲステン(W)を有する酸化膜が形成される場合、酸化タンゲステン(WO<sub>x</sub>(x=2~3))は、価数に変化が生じる。その結果、物理的手段により剥離しやすい状態となる。化学的手段と物理的手段を併用すると、より簡便に、短時間で酸化物、窒化物、又は窒化酸化物を除去することができる。

30

## 【0109】

次いで、剥離層1201上に、下地絶縁膜1202を形成する。下地絶縁膜1202は第1の基板中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、TFTなどの半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。また、下地絶縁膜1202は、後に形成される半導体素子を剥離する工程において、半導体素子を保護する役目も有している。下地絶縁膜1202は単層であっても複数の絶縁膜を積層したものであっても良い。よってアルカリ金属やアルカリ土類金属の半導体膜への拡散を抑えることができる酸化珪素や、窒化珪素、窒素を含む酸化珪素(SiON)、酸素を含む窒化珪素(SiNO)などの絶縁膜を用いて形成する。

40

## 【0110】

次に、下地絶縁膜1202上に半導体膜1203を形成する。半導体膜1203は、下地絶縁膜1202を形成した後、大気に曝さずに形成することが望ましい。半導体膜1203の膜厚は20nm以上200nm以下(望ましくは40nm以上120nm以下、より望ましくは50nm以上150nm以下)とする。

40

## 【0111】

そして、半導体膜1203に対してレーザビームを照射して半導体膜1203を結晶化する。半導体膜1203へのレーザビームの照射により、結晶性半導体膜1204が形成される。なお、結晶性をより良好にするために、ニッケルなどの金属を含む溶液を一面に塗りつけたのちにレーザ照射を行うこともできる。また、レーザビームの照射の代わりに、電熱炉を用いたファーネスアニール法や、ハロゲンランプ、メタルハライドランプ、キ

50

セノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどを用いた瞬間熱アニール法（LRTA法）や、ガス加熱式の瞬間熱アニール法（GRTA法）などを用いてもよい。

【0112】

次いで、図12（B）に示すように、結晶性半導体膜1204を加工して、島状の半導体膜1205～1207を形成した後、ゲート絶縁膜1208を形成する。ゲート絶縁膜1208は、プラズマCVD法又はスパッタリング法などを用い、窒化珪素、酸化珪素、窒素を含む酸化珪素又は酸素を含む窒化珪素を含む膜を、単層で、又は積層させて形成することができる。

【0113】

なお、ゲート絶縁膜1208を形成した後、3%以上100%以下の水素を含む雰囲気中で、300以上450以下で1時間以上12時間以下の熱処理を行ない、島状の半導体膜1205～1207を水素化する工程を行なっても良い。また、水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。

【0114】

次に図12（C）に示すように、ゲート電極1209～1211を形成する。ここでは、TaN（窒化タンタル）膜とW（タンゲステン）膜をスパッタ法やプラズマCVD法で形成した後、レジスト1212をマスクとしてエッチングを行なうことにより、ゲート電極1209～1211を形成した。勿論、ゲート電極1209～1211の導電材料、構造、作製方法は、これに限定されるものではなく、適宜選択することができる。例えば、N型を付与する不純物がドーピングされたSi膜とNiSi（ニッケルシリサイド）膜とを重ねて形成したものや、珪素とタンゲステンとを重ねて形成したものを用いても良い。また、ゲート電極を構成する導電膜を形成する際には、連続成膜をさらに、種々の導電材料を用いて単層で形成しても良い。また、ゲート電極とアンテナとを同時に形成する場合には、それらの機能を考慮して材料を選択すればよい。

【0115】

また、レジストマスクの代わりに、SiO<sub>x</sub>等のマスクを用いてもよい。この場合、材料を加工してSiO<sub>x</sub>、SiON等のマスク（ハードマスクと呼ばれる。）を形成する工程が加わるが、エッチング時におけるマスクの膜減りがレジストよりも少ないため、所望の幅のゲート電極1209～1211を形成することができる。

【0116】

次いで、図12（D）に示すように、Pチャネル型TFTとなる島状の半導体膜1206をレジスト1213で覆い、ゲート電極1209、1211をマスクとして、島状の半導体膜1205、1207に、N型を付与する不純物元素（代表的にはP（リン）又はAs（砒素））を低濃度にドープする。このドーピング工程によって、ゲート絶縁膜1208を介してドーピングがなされ、島状の半導体膜1205、1207に、一対の低濃度不純物領域1216、1217が形成される。なお、このドーピング工程は、Pチャネル型TFTとなる島状の半導体膜1206をレジストで覆わずに行っても良い。

【0117】

次いで、レジスト1213をアッシング等により除去した後、図13（A）に示すように、Nチャネル型TFTとなる半導体膜1205、1207を覆うように、レジスト1218を新たに形成し、ゲート電極1210をマスクとして、半導体膜1206に、P型を付与する不純物元素（代表的にはB（ホウ素））を高濃度にドープする。このドーピング工程によって、ゲート絶縁膜1208を介してドーピングがなされ、島状の半導体膜1206に、一対のP型の高濃度不純物領域1220が形成される。

【0118】

次いで、図13（B）に示すように、レジスト1218をアッシング等により除去した後、ゲート絶縁膜1208及びゲート電極1209～1211を覆うように、窒化珪素膜1221を形成する。窒化珪素膜1221の形成は、プラズマCVD法などを用いて行うことができる。

10

20

30

40

50

## 【0119】

その後、図13(C)に示すように、臭化水素(HBr)を主とするガスを用いて窒化珪素膜1221のドライエッティングを行い、サイドウォール1222～1224を形成する。他の実施例と同様に、臭化水素、塩素、および酸素の流量を100:44:6の比になるように混合してエッティング用のガスとし、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)装置を用いてドライエッティングを行った。圧力は1.6Pa、ICPの高周波は450W、BIASの高周波は150Wである。

## 【0120】

なお、本実施例ではドライエッティングの方法としてICP法を用いているが、この方法には限らない。同様にして、平行平板型RIE(反応性イオンエッティング)、マグネットロン型RIE、2周波型RIE、マイクロ波型RIE、ECR(電子サイクロトロン共鳴)プラズマエッティング、ヘリコン型プラズマエッティングなどのエッティング方法を用いることができる。

## 【0121】

次いで、図13(D)に示すように、Pチャネル型TFTとなる島状の半導体膜1206を覆うように、レジスト1226を新たに形成し、ゲート電極1209、1211及びサイドウォール1222、1224をマスクとして、N型を付与する不純物元素(代表的にはP又はAs)を高濃度にドープする。このドーピング工程によって、ゲート絶縁膜1208を介してドーピングがなされ、島状の半導体膜1205、1207に、一対のN型の高濃度不純物領域1227、1228が形成される。

## 【0122】

次に、レジスト1226をアッティング等により除去した後、不純物領域の熱活性化を行っても良い。例えば、50nmのSiON膜を成膜した後、550、4時間、窒素雰囲気下において、加熱処理を行なえばよい。また、水素を含むSiNx膜を、100nmの膜厚に形成した後、410、1時間、窒素雰囲気下において、加熱処理を行なうことにより、多結晶半導体膜の欠陥を改善することができる。これは、例えば、多結晶半導体膜中に存在するダングリングボンドを終端させるものであり、水素化処理工程などと呼ばれる。

## 【0123】

上述した一連の工程により、Nチャネル型TFT1230、Pチャネル型TFT1231、Nチャネル型TFT1232が形成される。上記作製工程において、エッチバック法の条件を適宜変更し、サイドウォールのサイズを調整することで、チャネル長0.2μm以上2μm以下のTFTを形成することができる。

## 【0124】

さらに、この後、TFT1230～1232を保護するためのパッシベーション膜を形成しても良い。

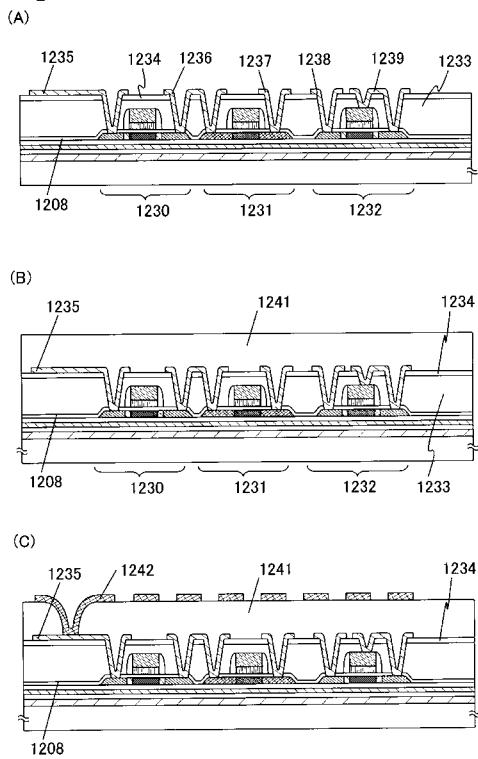

## 【0125】

次いで、図14(A)に示すように、TFT1230～1232を覆うように、第1の層間絶縁膜1233を形成する。

## 【0126】

さらに、第1の層間絶縁膜1233上に、第2の層間絶縁膜1234を形成する。なお、第1の層間絶縁膜1233又は第2の層間絶縁膜1234と、後に形成される配線を構成する導電材料等との熱膨張率の差から生じる応力によって、第1の層間絶縁膜1233又は第2の層間絶縁膜1234の膜剥がれや割れが生じるのを防ぐために、第1の層間絶縁膜1233又は第2の層間絶縁膜1234中にフィラーを混入させておいても良い。

## 【0127】

次いで、第1の層間絶縁膜1233、第2の層間絶縁膜1234及びゲート絶縁膜1208にコンタクトホールを形成し、TFT1230～1232に接続する配線1235～1239を形成する。なお、配線1235、1236はNチャネル型TFT1230の高濃度不純物領域1227に、配線1236、1237はPチャネル型TFT1231の高

10

20

30

40

50

濃度不純物領域 1220 に、配線 1238、1239 は N チャネル型 TFT1232 の高濃度不純物領域 1228 に、それぞれ接続されている。さらに配線 1239 は、N チャネル型 TFT1232 のゲート電極 1211 にも接続されている。N チャネル型 TFT1232 は、乱数 ROM のメモリ素子として用いることができる。

#### 【0128】

次いで、図 14 (B) に示すように、配線 1235 ~ 1239 を覆うように、第 2 の層間絶縁膜 1234 上に第 3 の層間絶縁膜 1241 を形成する。なお、第 3 の層間絶縁膜 1241 は、第 1 の層間絶縁膜 1233 と同様の材料を用いて形成することが可能である。

#### 【0129】

次に、第 3 の層間絶縁膜 1241 上にアンテナ 1242 を形成する。まず、配線 1235 ~ 1239 のいずれかが一部露出するように第 3 の層間絶縁膜 1241 に開口部を形成する。本実施例では、配線 1235 が露出するように開口部を形成している。続いて、アンテナ 1242 を形成する。アンテナ 1242 は、Ag、Au、Cu、Pd、Cr、Mo、Ti、Ta、W、Al、Fe、Co、Zn、Sn、Ni などの金属、金属化合物を 1 つまたは複数有する導電材料を用いることができる。そしてアンテナ 1242 は、配線 1235 と接続されている。

#### 【0130】

なお、図 14 (C) では、アンテナ 1242 が配線 1235 と直接接続されているが、本発明の無線 IC タグはこの構成に限定されない。例えば別途形成した配線を用いて、アンテナ 1242 と配線 1235 とを電気的に接続するようにしても良い。

#### 【0131】

アンテナ 1242 は印刷法、フォトリソグラフィ法、蒸着法または液滴吐出法などを用いて形成することができる。図 14 (C) では、アンテナ 1242 が単層の導電膜で形成されているが、複数の導電膜が積層されたアンテナ 1242 を形成することも可能である。例えば、Ni などで形成した配線に、Cu を無電解めっきでコーティングして、アンテナ 1242 を形成しても良い。

#### 【0132】

なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出して所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。また印刷法にはスクリーン印刷法、オフセット印刷法などが含まれる。印刷法、液滴吐出法を用いることで、露光用のマスクを用いずに、アンテナ 1242 を形成することができる。また、液滴吐出法、印刷法だと、フォトリソグラフィ法と異なり、エッチングにより除去されてしまうような材料の無駄がない。また高価な露光用のマスクを用いなくとも良いので、無線 IC タグの作製に費やされるコストを抑えることができる。

#### 【0133】

液滴吐出法または各種印刷法を用いる場合、例えば、Cu を Ag でコートした導電粒子なども用いることが可能である。なお液滴吐出法を用いてアンテナ 1242 を形成する場合、アンテナ 1242 の密着性が高まるような処理を、第 3 の層間絶縁膜 1241 の表面上に施すことが望ましい。

#### 【0134】

密着性を高めることができる方法として、具体的には、例えば触媒作用により導電膜または絶縁膜の密着性を高めることができる金属または金属化合物を第 3 の層間絶縁膜 1241 の表面に付着させる方法、形成される導電膜または絶縁膜との密着性が高い有機系の絶縁膜、金属、金属化合物を第 3 の層間絶縁膜 1241 の表面に付着させる方法、第 3 の層間絶縁膜 1241 の表面に大気圧下または減圧下においてプラズマ処理を施し、表面改質を行なう方法などが挙げられる。

#### 【0135】

第 3 の層間絶縁膜 1241 に付着させる金属または金属化合物が導電性を有する場合、アンテナの正常な動作が妨げられないように、そのシート抵抗を制御する。具体的には、導電性を有する金属または金属化合物の平均の厚さを、例えば 1 nm 以上 10 nm 以下と

10

20

30

40

50

なるように制御したり、これらの金属または金属化合物を酸化により部分的に、または全体的に絶縁化したりすれば良い。或いは、密着性を高めたい領域以外は、付着した金属または金属化合物をエッティングにより選択的に除去しても良い。また金属または金属化合物を、予め基板の全面に付着させるのではなく、液滴吐出法、印刷法、ゾル・ゲル法などを用いて特定の領域にのみ選択的に付着させても良い。なお金属または金属化合物は、第3の層間絶縁膜1241の表面において完全に連続した膜状である必要はなく、ある程度分散した状態であっても良い。

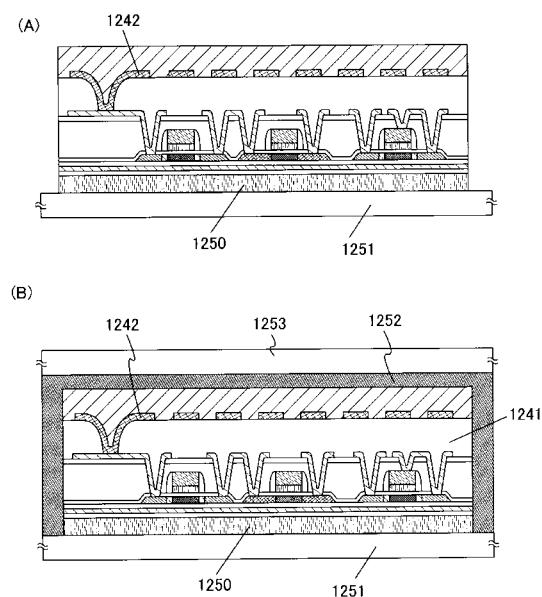

【0136】

そして、図15(A)に示すように、アンテナ1242を形成した後、アンテナ1242を覆うように、第3の層間絶縁膜1241上に保護層1245を形成する。保護層1245は、後に剥離層1201をエッティングにより除去する際に、アンテナ1242を保護することができる材料を用いる。例えば、水またはアルコール類に可溶なエポキシ系、アクリレート系、シリコン系の樹脂を全面に塗りつけることで保護層1245を形成することができる。

【0137】

次いで、図15(B)に示すように、無線ICタグを個別に分離するために溝1246を形成する。溝1246は、剥離層1201が露出する程度であれば良い。溝1246の形成は、ダイシング、スクライビングなどを用いることができる。なお、第1の基板1200上に形成されている無線ICタグを分離する必要がない場合、必ずしも溝1246を形成する必要はない。

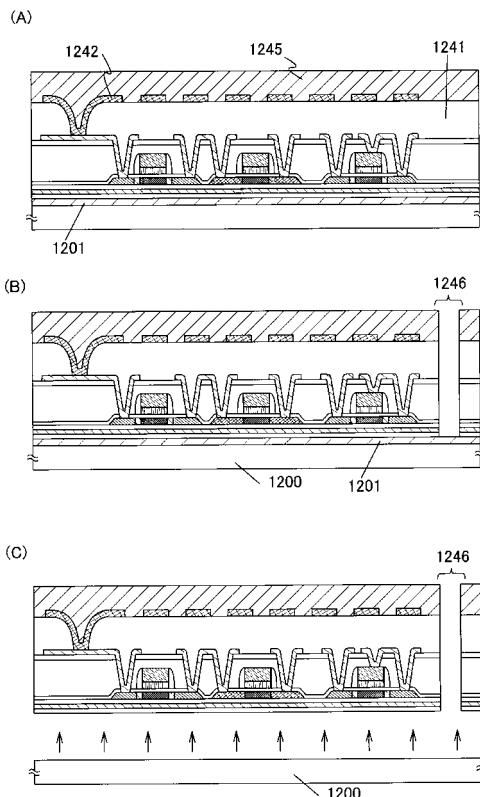

【0138】

次いで、図15(C)に示すように、剥離層1201をエッティングにより除去する。ここでは、エッティングガスとしてフッ化ハロゲンを用い、このガスを溝1246から導入する。例えばC<sub>1</sub>F<sub>3</sub>(三フッ化塩素)を用い、温度を350とし、流量を300sccmとし、気圧を798パスカル(798Pa)とし、処理時間を3時間とした条件で行う。また、C<sub>1</sub>F<sub>3</sub>ガスに窒素を混ぜたガスを用いても良い。C<sub>1</sub>F<sub>3</sub>等のフッ化ハロゲンを用いることで、剥離層1201が選択的にエッティングされ、第1の基板1200よりTFT1230~1232を剥離することができる。なおフッ化ハロゲンは、気体であっても液体であってもどちらでも良い。

【0139】

次に図16(A)に示すように、剥離されたTFT1230~1232及びアンテナ1242を、接着剤1250を用いて第2の基板1251に貼り合わせる。接着剤1250は、第2の基板1251と下地絶縁膜1202とを貼り合わせることができる材料を用いる。接着剤1250は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

【0140】

なお、第2の基板1251として、フレキシブルな紙またはプラスチックなどの有機材料を用いることができる。

【0141】

次いで、図16(B)に示すように、保護層1245を除去した後、アンテナ1242を覆うように接着剤1252を第3の層間絶縁膜1241上に塗りつけ、カバー材1253を貼り合わせる。カバー材1253は第2の基板1251と同様に、フレキシブルな紙またはプラスチックなどの有機材料を用いることができる。接着剤1252の厚さは、例えば10nm以上200μm以下とすれば良い。

【0142】

また接着剤1252は、カバー材1253と第3の層間絶縁膜1241及びアンテナ1242とを貼り合わせることができる材料を用いる。接着剤1252は、例えば反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

【0143】

10

20

30

40

50

上述した各工程を経て、無線ICタグが完成する。上記作製方法によって、トータルの膜厚が0.3μm以上3μm以下、代表的には2μm程度の飛躍的に薄い集積回路を第2の基板1251とカバー材1253との間に形成することができる。

【0144】

なお、集積回路の厚さは、半導体素子自体の厚さのみならず、接着剤1250と接着剤1252との間に形成された各種絶縁膜及び層間絶縁膜の厚さを含めるものとする。また、無線ICタグが有する集積回路の占める面積を、5mm四方(25mm<sup>2</sup>)以下、より望ましくは0.3mm四方(0.09mm<sup>2</sup>)~4mm四方(16mm<sup>2</sup>)程度とすることができる。

【0145】

なお、本実施例では、耐熱性の高い第1の基板1200と集積回路の間に剥離層を設け、エッティングにより剥離層を除去することで基板と集積回路とを剥離する方法について示したが、本発明の無線ICタグの作製方法は、この構成に限定されない。例えば、耐熱性の高い基板と集積回路の間に金属酸化膜を設け、この金属酸化膜を結晶化により脆弱化して集積回路を剥離しても良い。或いは、耐熱性の高い基板と集積回路の間に、水素を含む非晶質半導体膜を用いた剥離層を設け、レーザビームの照射によりこの剥離層を除去することで基板と集積回路とを剥離しても良い。あるいは、集積回路が形成された耐熱性の高い基板を機械的に削除または溶液やガスによるエッティングで除去することで集積回路を基板から切り離しても良い。

【0146】

なお、本実施例では、アンテナを集積回路と同じ基板上に形成している例について説明したが、本発明はこの構成に限定されない。別の基板上に形成したアンテナと集積回路とを、後に貼り合わせることで、電気的に接続するようにしても良い。

【0147】

なお、一般的にRFID(無線認証、Radio Frequency Identification)で用いられている電波の周波数は、13.56MHz、2.45GHzが多く、これらの周波数の電波を検波できるように無線ICタグを形成することが、汎用性を高める上で非常に重要である。

【0148】

本実施例の無線ICタグでは、半導体基板を用いて形成されたRFIDよりも電波が遮蔽されにくく、電波の遮蔽により信号が減衰するのを防ぐことができるというメリットを有している。よって、半導体基板を用いずに済むので、無線ICタグのコストを大幅に低くすることができる。

【0149】

なお、本実施例では、集積回路を剥離して、可撓性を有する基板に貼り合わせる例について説明したが、本発明はこの構成に限定されない。例えばガラス基板のように、集積回路の作製工程における熱処理に耐えうるような、耐熱温度を有している基板を用いる場合、必ずしも集積回路を剥離する必要はない。

【0150】

また、本実施例は、実施の形態や他の実施例と自由に組み合わせることができる。

【実施例4】

【0151】

本発明を用いて作製したTFTを薄膜集積回路、または非接触型薄膜集積回路装置(無線ICタグ、RFID(無線認証、Radio Frequency Identification)とも呼ばれる)として用いることもできる。他の実施例で示した作製方法を用いることにより、薄膜集積回路および非接触型薄膜集積回路は、タグとしての利用やメモリとしての利用が可能である。

【0152】

本発明を用いることによって、従来技術に比較して高い異方性が得られるため、窒化珪素膜のエッティング時にサイドウォールの幅の寸法変化を少なくすることができる。さらに

10

20

30

40

50

は、このサイドウォールに合わせて LDD 領域を良好に形成することが可能となる。従って、本発明を用いて形成した TFT 用いた無線 IC タグは、品質が良好で、品質のばらつきがないものとなる。

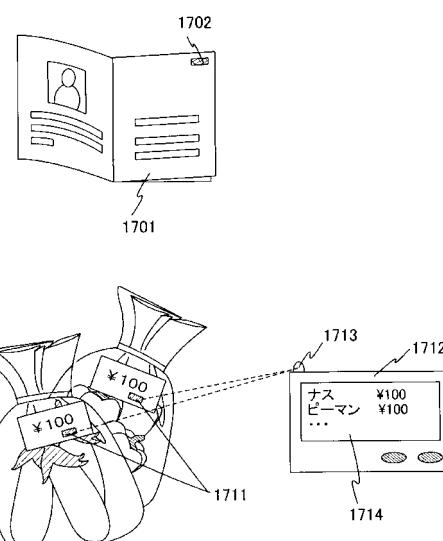

#### 【 0 1 5 3 】

図 17 ( A ) は、パスポート 1701 に無線 IC タグ 1702 を貼り付けている状態を示している。また、パスポート 1701 に無線 IC タグ 1702 を埋め込んでもよい。同様にして、運転免許証、クレジットカード、紙幣、硬貨、証券、商品券、チケット、トラベラーズチェック ( T / C ) 、健康保険証、住民票、戸籍謄本などに無線 IC タグを貼り付けることや埋め込むことができる。この場合、本物であることを示す情報のみを無線 IC タグに入力しておき、不正に情報を読み取ったり書き込んだりできないようにアクセス権を設定する。これは、本発明を用いて形成した TFT を用いることにより実現できる。このように本発明の TFT をタグとして利用することによって、偽造されたものと区別することが可能になる。

#### 【 0 1 5 4 】

このほかに、無線 IC タグをメモリとして用いることも可能である。図 17 ( B ) は、無線 IC タグ 1711 を野菜の包装に貼り付けるラベルに埋め込んだ例を示している。また、包装そのものに無線 IC タグを貼り付けたり埋め込んだりしても構わない。無線 IC タグ 1711 には、生産地、生産者、製造年月日、加工方法などの生産段階のプロセスや、商品の流通プロセス、価格、数量、用途、形状、重量、賞味期限、各種認証情報などを記録することが可能になる。無線 IC タグ 1711 からの情報は、無線式のリーダ 1712 のアンテナ部 1713 で受信して読み取り、リーダ 1712 の表示部 1714 に表示することによって、卸売業者、小売業者、消費者が把握することが容易になる。また、生産者、取引業者、消費者のそれぞれに対してアクセス権を設定することによって、アクセス権を有しない場合は読み込み、書き込み、書き換え、消去ができない仕組みになっている。

#### 【 0 1 5 5 】

また、無線 IC タグは以下のように用いることができる。会計の際に無線 IC タグに会計を済ませたことを記入し、出口にチェック手段を設け、会計済みであることを無線 IC タグに書き込まれているかをチェックする。会計を済ませていないで店を出ようとする、警報が鳴る。この方法によって、会計のし忘れや万引きを予防することができる。

#### 【 0 1 5 6 】

さらに、顧客のプライバシー保護を考慮すると、以下に記す方法にすることも可能である。レジで無線 IC タグから商品情報を読み取り、さらに ( 1 ) 無線 IC タグに入力されているデータを暗証番号などでロックする、( 2 ) 無線 IC タグに入力されているデータそのものを暗号化する、( 3 ) 無線 IC タグに入力されているデータを消去する、( 4 ) 無線 IC タグに入力されているデータを破壊する、のいずれかを行う。これらは、他の実施例にて挙げたメモリを用いることによって実現することができる。そして、出口にチェック手段を設け、( 1 ) ~ ( 4 ) のいずれかの処理が行われたか、または無線 IC タグのデータに何も処理が行われていない状態であるかをチェックすることによって、会計の有無をチェックする。このようにすると、店内では会計の有無を確認することができるし、店外では所有者の意志に反して無線 IC タグの情報を読み取られることを防止することができる。

#### 【 0 1 5 7 】

なお、( 4 ) の無線 IC タグに入力されているデータを破壊する方法をいくつか挙げることができる。例えば、( a ) 無線 IC タグが有する電子データの少なくとも一部に「 0 ( オフ ) 」若しくは「 1 ( オン ) 」、または「 0 」と「 1 」の両方を書き込んでデータのみを破壊する方法や、( b ) 無線 IC タグに電流を過剰に流し、無線 IC タグが有する半導体素子の配線の一部を物理的に破壊する方法などを用いることができる。

#### 【 0 1 5 8 】

他の無線 IC タグの使い方として、無線 IC タグを付いている商品の情報を冷蔵庫や洗

10

20

30

40

50

灌機などの家庭用電化製品が持つリーダで読み取ることにより、商品の品質管理方法や取り扱い方法を自動で調節させることができる。さらに、モニタを家庭用電化製品に付けて、商品情報を表示させることも可能である。

#### 【0159】

例えば、商品（例えば食品）には、保存に適した温度状態や湿度状態がある。また、季節ごとに冷蔵庫内の温度設定を行うことは省エネルギーの観点上、重要なことである。しかし、これを消費者が自力で調節するのは非常に面倒なことである。ところが、調節を怠ると、商品をすぐに傷めてしまうことや、季節によっては必要以上に電力を消費することもある。

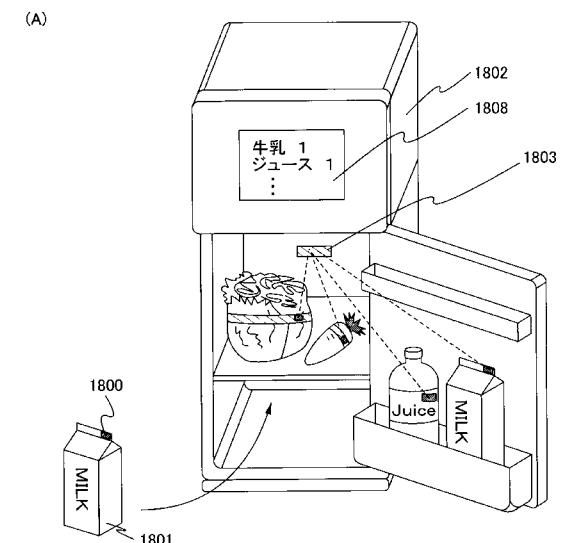

#### 【0160】

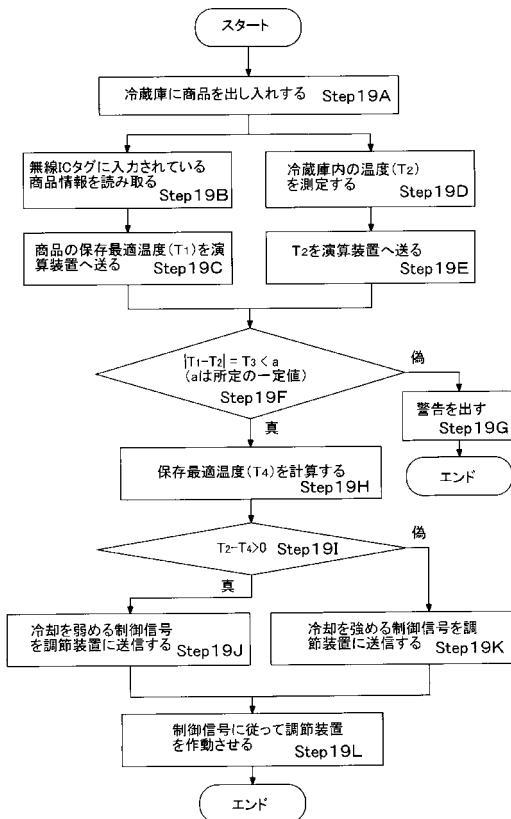

図18（A）は、無線ICタグ1800が付いている商品1801を冷蔵庫1802に出し入れするところを示す。ここで読み取ったデータの流れを図18（B）に示す。また、商品1801の出し入れに伴って冷蔵庫が行う処理の流れ図を図19に示す。

#### 【0161】

まず、図18（A）に示すように、無線ICタグが付いている商品1801を冷蔵庫1802に出し入れする（図19（Step19A））。この際に、出し入れした商品の情報をリーダ1803が読み取る（図19（Step19B））。次に、商品のデータを冷蔵庫1802が有する演算装置1804に送信し（図19（Step19C））、必要に応じて演算装置1804は記憶装置1805に商品のデータを記憶させる。このデータには、商品の種類、保存に最適な温度（ $T_1$ ）、湿度状態、賞味期限などが含まれる。同時に、冷蔵庫1802の温度（ $T_2$ ）、湿度状態を測定し（図19（Step19D））、演算装置1804に送信する（図19（Step19E））。必要に応じて記憶装置1805にこのデータを記憶しておく。なお、以下では温度に注目して述べるが、他の要素に関しても同様に処理を行うことができる。

#### 【0162】

次に、図19（Step19F）に示すように、演算装置1804は、出し入れした商品の保存に最適な温度（ $T_1$ ）と冷蔵庫内の温度（ $T_2$ ）のデータを記憶装置1805から取り出し、 $T_1$ と $T_2$ の差の絶対値（ $T_3$ ）を計算し、 $T_3$ と一定値（a）が以下の式の通りになるか比較する。

$$|T_1 - T_2| = T_3 < a$$

#### 【0163】

$T_3$ が一定値（a）以上である場合、つまり、上の式が偽であるときには、冷蔵庫1802で保存することには不適であるので、音や光などの手段によって消費者に警告を出し（図19（Step19G））、冷蔵庫1802の温度変化を行わない。 $T_3$ が一定値（a）以内の場合、すなわち上の式が真のときには、以下の処理に続く。

#### 【0164】

演算装置1804は、出し入れ後の商品の保存に最適な温度（ $T_4$ ）を計算する（図19（Step19H））。さらに、この温度（ $T_4$ ）と冷蔵庫内の温度（ $T_2$ ）とを比較し（図19（Step19I））、その結果によって冷却の強弱を決定する。 $T_2 > T_4$ の場合では、冷却を弱めるように調節装置1806に制御信号を送信し（図19（Step19J））、 $T_2 < T_4$ の場合では、冷却を強くするように調節装置1806に制御信号を送信する（図19（Step19K））。調節装置1806は、制御信号に従って調節装置1806を作動させ（図19（Step19L））、冷蔵庫1802の温度が $T_4$ になるように調節する。

#### 【0165】

なお、冷蔵庫1802において、リーダ1803、演算装置1804、および記憶装置1805は、制御装置1807によって入出力がコントロールされている。なお、演算装置1804および制御装置1807としてCPUを用いてもよい。

#### 【0166】

他の機能として、冷蔵庫1802に入れている商品の種類や数を把握することによって

10

20

30

40

50

、冷蔵庫 1802 内に商品があまり入っていない場合には冷却を弱め、商品がたくさん入っているときには逆に強くすることも可能になる。さらには、冷蔵庫 1802 内の特定の位置だけ冷却を弱めたり強めたりすることも可能になる。また、冷蔵庫 1802 にモニタ 1808 を設置することにより、冷蔵庫 1802 を開けることなく内部に何が入っているかを確認することができる。

【0167】

また、冷蔵庫内に入れた品物に応じた冷却方法を実行することも可能である。無線 IC タグの情報に従って、急速に冷却するか、またはゆっくり冷却するかを判断する。その判断に従って調節装置 1806 に制御信号を送り、調節装置 1806 は制御信号に従って冷却の調節を行う。

10

【0168】

このように、状況に応じて冷蔵庫内の状態を制御することによって、商品を長時間良好に保存することができ、かつ無駄な電力の消費を少なくすることができる。なお、温度の調整の仕方はここに挙げた方法に限らない。

【0169】

本実施例では食品を保存する冷蔵庫について説明したが、温度、湿度、明るさなどを調節して保存する必要がある品物（例として、（1）化学物質や医薬品、（2）細胞、細菌類、植物、動物などの生体、（3）酵素やDNAなどの生体に由来するもの）であれば、品物の情報を入力した無線 IC タグを容器に付けたり、無線 IC タグを試料自体に付けたりすることにより、同様に用いることが可能である。

20

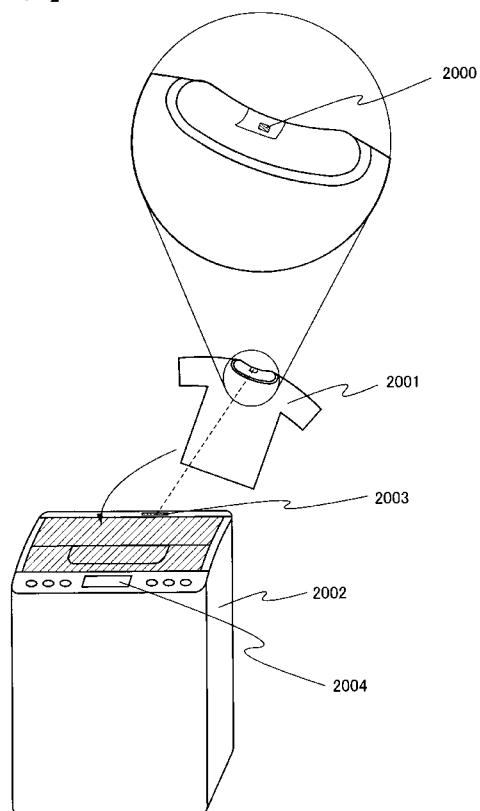

【0170】

洗濯機の場合では、洗濯に適した洗い方、洗剤の種類や量、洗濯に用いる水の量などを設定する必要がある。一般的に、洗濯物は大きさや種類が多様であるため、洗濯の設定は面倒である。近年では、機能がたくさんある洗濯機が数多く市販されているが、消費者が洗濯機の機能を使いこなせていない場合も多い。

【0171】

一般的に市販されている一槽式脱水洗濯機では、洗濯兼脱水槽に洗濯物を入れた後、洗濯兼脱水槽を回すための動力を測定することによって洗濯物の重量を測定し、この洗濯物の重量によって水の量が決められる。従って、同じ重さであっても、シーツのように大きくてかさばるものと、デニム素材のジャケットのように小さいものをそれぞれ洗う場合では、水量も洗い方も全く同じように洗濯が行われてしまう。洗剤の量は洗濯に使う水の量に合わせて設定されるため、上記のような場合では適切な洗剤の量にならないこともある。

30

【0172】

そこで、図 20 に示すように、衣類に無線 IC タグ 2000 が埋め込まれている洗濯物 2001 を洗濯機 2002 に入れる際に、洗濯物の種類、大きさ、重量、素材などの情報を洗濯機に付いているリーダ 2003 が読み取り、その情報を演算装置に送信する。演算装置は、これらの洗濯物の情報から適切な洗濯コース、洗剤の種類と量、水量を判断する。そして、洗濯機に付いているモニタ 2004 に、投入すべき洗剤の種類と量が表示される。消費者はその表示に従って洗剤を投入し、洗濯機のスタートボタンを押せばよい。このようにして、自動的に洗濯に関する設定が行われた後、洗濯が行われる。なお、衣類に埋め込む無線 IC タグ 2000 は、耐水性を有する物質で覆われることが必要である。例えば、耐水性を持つ樹脂、セラミックなどを用いることができる。

40

【実施例 5】

【0173】

本発明を用いて作製した TFT を集積化した CPU、メモリ、IC などとして搭載したり、パネルとして用いたりすることによって、ディスプレイ、反射型プロジェクター、ヘッドマウントディスプレイなどの表示装置、音響再生装置、ナビゲーションシステム、携帯情報端末、ゲーム機、デジタルスチルカメラ、デジタルビデオカメラ、画像や映像を再生する装置などの様々な電子機器を完成させることができる。その具体例を、図 21 を用

50

いて説明する。

【0174】

本発明を用いることによって、従来技術に比較して高い異方性が得られるため、窒化珪素膜のエッチング時にサイドウォールの幅の寸法変化を少なくすることができる。さらには、このサイドウォールに合わせてLDD領域を良好に形成することが可能となる。従って、本発明を用いて形成したTFTを有する電子機器は、品質が良好で、品質のばらつきがないものとなる。

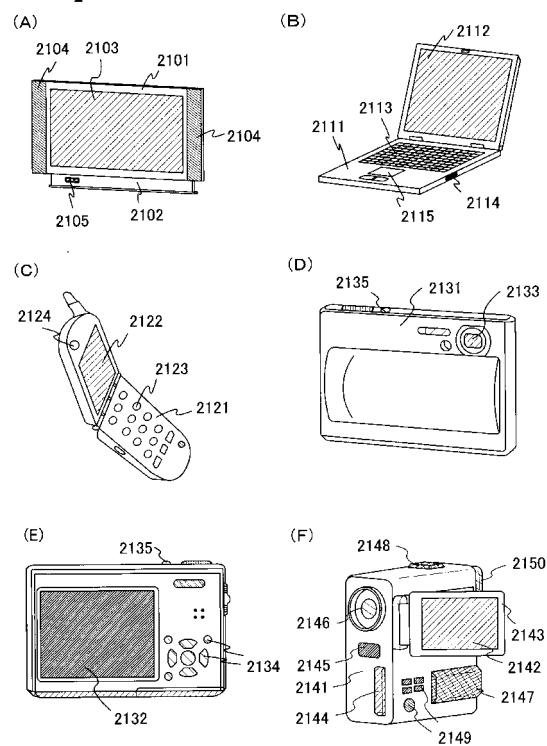

【0175】

図21(A)は表示装置であり、筐体2101、支持台2102、表示部2103、スピーカー部2104、ビデオ入力端子2105などを含む。この表示装置は、他の実施例で示した作製方法により形成したTFTを駆動ICや表示部2103などに用いることにより作製される。なお、表示装置には液晶表示装置、発光表示装置などがあり、具体的にはコンピュータ用、テレビ受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

【0176】

図21(B)はコンピュータであり、筐体2111、表示部2112、キーボード2113、外部接続ポート2114、ポインティングマウス2115などを含む。本発明を用いて形成されたTFTは、表示部2112の画素部だけではなく、表示用の駆動IC、本体内部のCPU、メモリなどの半導体装置にも適用が可能である。

【0177】

また、図21(C)は携帯電話であり、携帯用の情報処理端末の1つの代表例である。この携帯電話は筐体2121、表示部2122、操作キー2123、センサ部2124などを含む。本発明を用いて形成されたTFTは表示部2122の画素部やセンサ部2124だけではなく、表示用の駆動IC、メモリ、音声処理回路などに用いることができる。センサ部2124は光センサ素子を有しており、センサ部2124で得られる照度に合わせて表示部2122の輝度コントロールを行ったり、センサ部2124で得られる照度に合わせて操作キー2123の照明制御を抑えたりすることによって、携帯電話の消費電力を抑えることができる。

【0178】

上記の携帯電話を始めとして、PDA(Personal Digital Assistants、情報携帯端末)、デジタルカメラ、小型ゲーム機などの電子機器に、本発明を用いて形成した半導体材料を用いることもできる。例えば、CPU、メモリ、センサなどの機能回路を形成することや、これらの電子機器の画素部や、表示用の駆動ICにも半導体材料を適用することが可能である。

【0179】

また、図21(D)、(E)はデジタルカメラである。なお、図21(E)は、図21(D)の裏側を示す図である。このデジタルカメラは、筐体2131、表示部2132、レンズ2133、操作キー2134、シャッター2135などを有する。本発明を用いて形成されたTFTは、表示部2132の画素部、表示部2132を駆動する駆動IC、メモリなどに用いることができる。

【0180】

図21(F)はデジタルビデオカメラである。このデジタルビデオカメラは、本体2141、表示部2142、筐体2143、外部接続ポート2144、リモコン受信部2145、受像部2146、バッテリー2147、音声入力部2148、操作キー2149、接眼部2150などを有する。本発明を用いて形成されたTFTは、表示部2142の画素部、表示部2142を制御する駆動IC、メモリ、デジタル入力処理装置などに用いることができる。

【0181】

以上のように、本発明により作製された半導体装置の適用範囲は極めて広く、本発明により作製された半導体装置をあらゆる分野の電子機器に用いることができる。なお、これ

10

20

30

40

50

らの電子機器に使われる表示装置は、大きさや強度、または使用目的に応じて、ガラス基板だけでなく耐熱性のプラスチック基板を用いることも可能である。それによってより一層の軽量化を図ることができる。

【0182】

また、本実施例は実施の形態および他の実施例と組み合わせて用いることが可能である。

【実施例6】

【0183】

本実施例では、臭化水素(HBr)ガスの流量を変えたときに、窒化珪素膜がどのようにエッティングされ、サイドウォールを形成するかを測定した結果を示す。

10

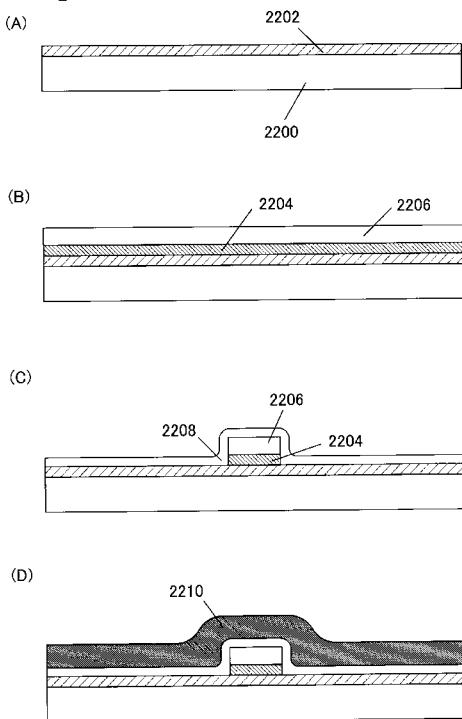

【0184】

エッティングする試料を以下に示すように作製した。まず、図22(A)に示すように、ガラス基板などの絶縁性基板2200を用意する。本実施例では絶縁性基板2200としてガラス基板を用いた。なお、他の実施例に示したように、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス基板、石英基板、セラミックス基板、ステンレス基板などはもちろん、PET(ポリエチレンテレフタラート)、PES(ポリエーテルスルホン)、PEN(ポリエチレンナフタレート)に代表されるプラスチックや、アクリルなどに代表される合成樹脂を原料とする基板も用いることができる。

【0185】

次に、この絶縁性基板2200上に、プラズマCVD法を用いて窒素を含んだ酸化珪素膜を100nmの厚さで形成し、これを下地膜2202とした(図22(A))。一般的に下地膜2202は、絶縁性基板に含まれるナトリウムなどのアルカリ金属やアルカリ土類金属が半導体中に拡散し、半導体素子の特性に悪影響を及ぼすのを防ぐために設けるために用いる。このため、アルカリ金属やアルカリ土類金属の半導体中への拡散を抑えることのできる酸化珪素や窒化珪素、酸素を含む窒化珪素膜などの絶縁膜を用いて形成する。なお、石英基板など不純物の拡散がさほど問題にならない基板を用いる場合には必ずしも下地膜2202を設ける必要はない。本実施例では、サイドウォールの形成状況を観察するだけであるため半導体膜を設けていないが、実際に半導体装置を形成する場合は、他の実施例で示したように半導体膜を形成すればよい。

20

【0186】

次に、図22(B)に示すように、第1の導電膜2204として窒化タンタル(TaN)を30nmの厚さで形成する。さらに、第1の導電膜上に第2の導電膜2206としてタンゲステン(W)を370nmの厚さで形成する。さらに、第1の導電膜2204および第2の導電膜2206をパターン成形するためのレジストマスクを形成し、このレジストマスクをもとに第1の導電膜2204および第2の導電膜2206をエッティング処理し、島状に成形する(図22(C))。この部分がTFTのゲート電極に相当する部分となる。

30

【0187】

次に、下地膜、島状に成形された第1の導電膜2204及び第2の導電膜2206を覆うように、絶縁膜2208としてシリコンオキシナイトライド(SiON:Si<sub>1</sub>Si<sub>0</sub>o<sub>1</sub>xy<sub>1</sub>n<sub>1</sub>tride)を50nmの厚さで成膜する(図22(C))。成膜する方法は、プラズマCVD法やスパッタ法などの公知の方法を用いることができる。本実施例では、絶縁膜2208は後に行うエッティングのストップー膜として用いている。

40

【0188】

次に、図22(D)で示すように、絶縁膜2208を覆うように窒化珪素膜2210を300nmの厚さで形成した。窒化珪素膜の形成は、プラズマCVD法を用いて行ったが、他の公知の方法を用いて形成することもできる。以上の処理を行うことにより、試料を作製した。

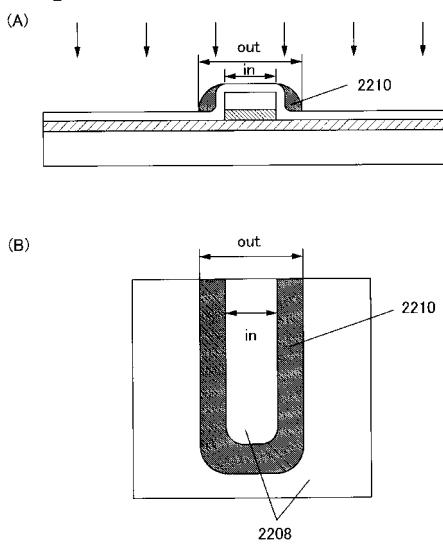

【0189】

ここで、図23(A)に示すように、臭素を含むガスを用いて窒化珪素膜2210のド

50

ライエッチングを行った。エッチングガスは、臭化水素、塩素、酸素の混合ガスを用いた。本実施例では塩素の流量を44 sccm、酸素の流量を6 sccmに固定し、臭化水素の流量を変えて3種類の混合ガスを作った。本実施例で用いた臭化水素の流量は、50 sccm、100 sccm、130 sccmの3種類である。(以下、それぞれ試料1、試料2、試料3と呼ぶ。)これらの混合ガスを用いて、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)装置を用いてドライエッチングを行った。なお、圧力は1.6 Pa、ICPの高周波は450 W、BIAISの高周波は150 W、エッチング装置内の温度は70 °である。ICPに印加する高周波はプロセスガスを分解する役割を持ち、BIAISに印加する高周波は、エッチング種(イオン)を加速する役割を持つ。この工程により、サイドウォールが形成された。

10

## 【0190】

エッチングの終点はプラズマ波形の変化で求めた。試料1、2、3についてそれぞれプラズマ波形を観測すると、それぞれ158秒、180秒、191秒で窒化珪素以外の物質をエッチングし始めたことに由来する波形の変化が見られたため、この時点でサイドウォールが形成されたとした。プラズマ波形の観測時間からは、臭化水素の流量が多い方が長い時間がかかることが分かる。

## 【0191】

この処理を基板上の4点で同時にを行い、それぞれサイドウォールを形成した。サイドウォールの幅は、測長SEMを用いて測定した。図23(B)には、図23(A)の上面図を示す。サイドウォールを含んだ全体の幅(outと呼ぶ)と、サイドウォールを含まない幅(inと呼ぶ)を測定し、サイドウォールの幅を(サイドウォールの幅) = ((out) - (in)) / 2の式で求めた。

20

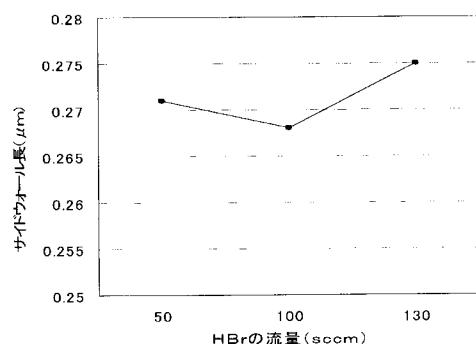

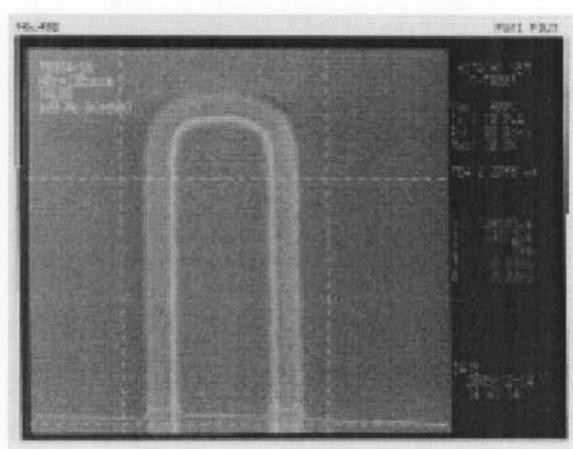

## 【0192】

図24(A)、(B)に示すように、試料1、2、3におけるサイドウォールの幅の平均値は、それぞれ0.271 μm、0.268 μm、0.275 μmとなった。また、試料1、2、3のエッチング終了点におけるSEM写真を図25(A)~(C)に示す。これらの結果より、サイドウォールの幅は臭化水素の流量、すなわち臭化水素の濃度には依存せず、ほぼ同程度の長さで形成されることが分かった。

## 【0193】

以上の結果より、実施の形態や他の実施例においても、塩素の流量を44 sccm、酸素の流量を6 sccmに固定したとき、臭化水素の流量が50 sccm以上130 sccm以下であれば、窒化珪素をエッチング処理して約0.27 μmのサイドウォールを形成することが可能であることが分かった。

30

## 【実施例7】

## 【0194】

本実施例では、本発明を用いて作製する素子の一例として、フォトICおよびその作製例を説明する。

## 【0195】

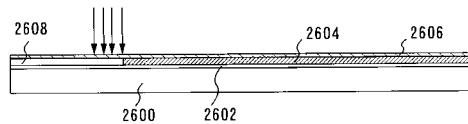

まず、図26(A)において、基板(第1の基板2600)上に素子を形成する。ここでは基板2600として、ガラス基板の一つであるAN100を用いる。

40

## 【0196】

次いで、プラズマCVD法で下地絶縁膜2602となる窒素を含む酸化珪素膜(膜厚100 nm)を形成し、さらに大気にふれることなく、半導体膜を20 nm以上150 nm以下、好ましくは30 nm以上80 nm以下の厚さで積層形成する。本実施例では、非晶質半導体膜2604として、水素を含む非晶質珪素膜を形成する。

## 【0197】

下地絶縁膜2602は酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜を用いて積層してもよい。例えば、下地絶縁膜2602として、酸素を含む窒化珪素膜を50 nm、さらに窒素を含む酸化珪素膜を100 nm積層した膜を形成してもよい。なお、窒素を含む酸化珪素膜や窒化珪素膜は、ガラス基板からのアルカリ金属などの不純物拡散を防止するブ

50

ロッキング層として機能する。

【0198】

次いで、上記非晶質半導体膜2604を固相成長法、レーザ結晶化方法、触媒金属を用いた結晶化方法などにより結晶化させて、結晶構造を有する半導体膜（結晶性半導体膜）の一種として、例えば多結晶珪素膜2608を形成する。

【0199】

本実施例では、触媒元素を用いた結晶化方法を用いて多結晶珪素膜2608を形成する。まず、重量換算で10～100ppmのニッケルを含む溶液、例えば酢酸ニッケルの溶液をスピナーで非晶質半導体膜2604の一部または全面に塗りつける。また、上記のようにスピナーで塗りつける処理の代わりに、スパッタ法でニッケル元素を全面に散布する方法を用いてもよい。そのほかにも、蒸着法やプラズマ処理などを用いてニッケル元素を添加することができる。なお、ここで用いることができる触媒元素はニッケルだけではなく、ゲルマニウム、鉄、パラジウム、スズ、鉛、コバルト、白金、銅、金なども用いることができる。非晶質半導体膜2604の一部または全面に塗りつけた触媒は、図26（A）の2606で示している。

【0200】

なお、半導体膜を結晶化する際に、結晶の成長方向を基板2600の表面に垂直な方向に制御するためには、触媒元素を含む溶液を半導体膜の全面に塗り付ければよい。また、結晶の成長方向を基板2600の表面に平行な方向に制御するためには、触媒元素を含む溶液を半導体膜の一部に塗り付ければよい。

【0201】

次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜（ここでは多結晶珪素膜）を形成する。ここでは熱処理（500、1時間）の後、結晶化のための熱処理（550、4時間）を行う。前者の熱処理によって、非晶質半導体膜2604と触媒元素が反応して、非晶質半導体膜2604と触媒元素が接触した面の表面および表面近傍に化合物を形成する。次の熱処理でこの化合物を核として結晶成長が起きる。結晶化温度の低温化および時短化は、触媒作用のある金属元素の作用によるものである。これらの加熱処理により、多結晶珪素膜を得ることができる。触媒元素を用いると結晶性が向上する。その結果、素子間の移動度、しきい値、およびオン電流のばらつきを抑えることができる。

【0202】

次に、多結晶珪素膜2608表面の酸化膜を希フッ酸等で除去する。その後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザビームの照射を行う。

【0203】

なお、非晶質半導体膜をレーザ結晶化方法で結晶化して結晶性半導体膜を得る場合、もしくは結晶構造を有する半導体膜を得た後に結晶粒内に残される欠陥を補修するためにレーザ照射を行う場合には、CWレーザや発振周波数が高いパルスレーザを用いるとより好ましい。なお、ここで用いるパルスレーザの発振周波数は10MHz以上であるとより好ましい。

【0204】

なお、レーザ照射を大気中、または酸素雰囲気中で行う場合は、レーザビームの照射により表面に酸化膜が形成される。

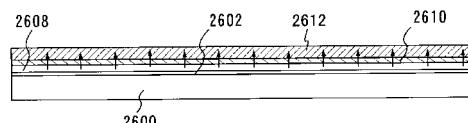

【0205】

次いで、オゾン水で表面を120秒処理して、1～5nmの酸化膜からなるバリア層2610を形成する（図26（B））。なお、大気中または酸素雰囲気中でレーザビームを照射することによって、多結晶珪素膜2608上に酸化膜が形成されている場合では、この処理を行うことによって合計1nm以上5nm以下のバリア層2610を形成する。

【0206】

このバリア層2610は、結晶化させるために添加した触媒元素、例えばニッケル（Ni）を膜中から除去するために形成する。ここではオゾン水を用いてバリア層2610を形成するが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する

10

20

30

40

50

方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマCVD法やスパッタ法や蒸着法などで1～10nm程度の酸化膜を堆積してバリア層2610を形成してもよい。また、バリア層2610を形成する前にレーザビームの照射により形成された酸化膜を除去してもよい。

【0207】

次に、バリア層2610上にスパッタ法にてゲッタリングサイトとなる希ガス元素を含む非晶質珪素膜2612を10nm～400nm、本実施例では膜厚100nmで成膜する(図26(B))。本実施例ではシリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマCVD法を用いてアルゴン元素を含む非晶質珪素膜を形成する場合、成膜条件は、モノシリコンとアルゴンの流量比(SiH<sub>4</sub> : Ar)を1:99とし、成膜圧力を6.665Paとし、RFパワー密度を0.087W/cm<sup>2</sup>とし、成膜温度を350°とする。ここで形成する非晶質珪素膜2612は、多結晶珪素膜2608とエッチングの選択比を大きくするため、多結晶珪素膜2608よりも膜の密度が低い方がより望ましい。希ガス元素としては、ヘリウム(He)、ネオン(Ne)、アルゴン(Ar)、クリプトン(Kr)、キセノン(Xe)から選ばれた一種または複数種を用いることができる。

【0208】

その後、650°に加熱された炉に非晶質珪素膜2612を入れて3分の熱処理を行い、触媒元素を除去(ゲッタリング)する(図26(B))。これにより多結晶珪素膜2608中の触媒元素濃度が低減される。炉に代えてランプアニール装置を用いてもよい。加熱処理によって、多結晶珪素膜2608の触媒元素が、拡散によって矢印に示すようにゲッタリング用の半導体膜、すなわち非晶質珪素膜2612に移動する。

【0209】

次いで、バリア層2610をエッチングストッパーとして、ゲッタリングサイトであるアルゴン元素を含む非晶質珪素膜2612を選択的に除去した後、バリア層2610を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層2610をゲッタリング後に除去することが望ましい。

【0210】

なお、触媒元素を用いて半導体膜の結晶化を行わない場合には、上述したバリア層2610の形成、ゲッタリングサイト(希ガス元素を含む非晶質珪素膜2612)の形成、ゲッタリングのための熱処理、ゲッタリングサイトの除去、バリア層の除去などの工程は不要である。

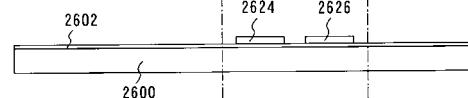

【0211】

次に、得られた結晶構造を有する半導体膜(例えば結晶性珪素膜)の表面にオゾン水で薄い酸化膜を形成し、さらに酸化膜上にレジストを形成し、露光を行うことによって、レジストを材料とするマスクを形成する。さらに、エッチング処理して島状に分離された半導体膜(以下、本明細書では「島状半導体膜」という)2624及び2626を形成する(図26(C)参照)。島状半導体膜2624および2626を形成した後、レジストを材料とするマスクを除去する。

【0212】

次いで、必要があればTFTのしきい値を制御するために微量な不純物元素(ホウ素またはリン)のドーピングを行う。ここでは、ジボラン(B<sub>2</sub>H<sub>6</sub>)を質量分離しないでプラズマ励起したイオンドープ法を用いる。

【0213】

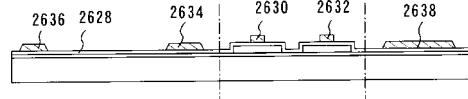

次いで、フッ酸を含むエッチャントで酸化膜を除去すると同時に島状半導体膜2624及び2626の表面を洗浄した後、ゲート絶縁膜2628となる珪素を主成分とする絶縁膜を形成する(図26(D))。ここでは、プラズマCVD法を用いて、窒素を含む酸化珪素膜(組成比Si=32%、O=59%、N=7%、H=2%)を115nmの厚さで形成する。

10

20

30

40

50

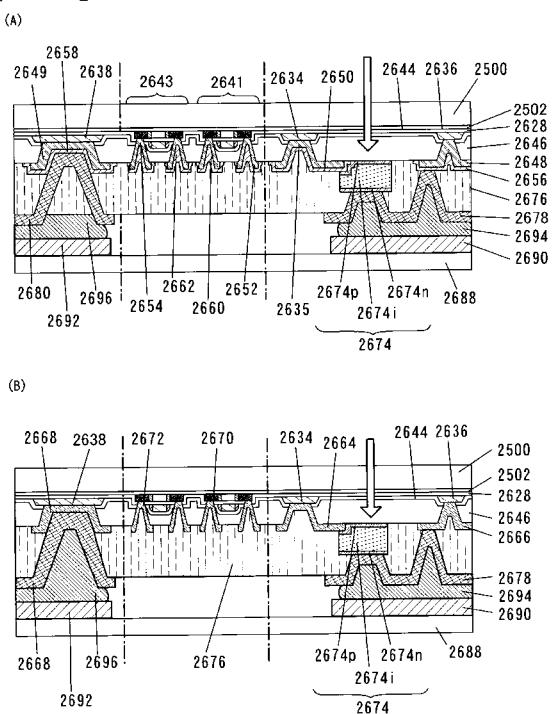

## 【0214】

次いで、ゲート絶縁膜2628上に金属膜を形成した後、第2のフォトマスクを用いて金属膜を所定の形状に形成する処理を行い、ゲート電極2630及び2632、配線2634及び2636、端子電極2638を形成する(図26(D))。この金属膜として、例えば窒化タンタル(TaN)及びタンゲステン(W)をそれぞれ30nm、370nm積層した膜を用いる。

## 【0215】

また、ゲート電極2630及び2632、配線2634及び2636、端子電極2638として、上記以外にもチタン(Ti)、タンゲステン(W)、タンタル(Ta)、モリブデン(Mo)、ネオジウム(Nd)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、白金(Plt)、アルミニウム(Al)、金(Au)、銀(Ag)、銅(Cu)から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物を用いることができる。例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層膜を挙げることができる。

## 【0216】

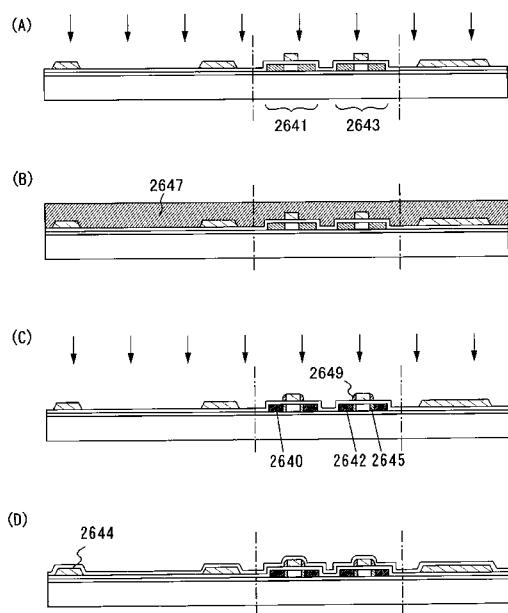

次いで、島状半導体膜2624及び2626への一導電型を付与する不純物の導入を行う。本実施例ではNチャネル型TFT2641、2643を形成するので、N型の不純物、例えばリン(P)、砒素(As)を島状半導体膜2624及び2626に導入する(図27(A)参照)。

## 【0217】

次に、全面に窒化珪素膜2647を300nm形成する(図27(B))。窒化珪素膜2647は、プラズマCVD法などを用いて行うことができる。さらに、窒化珪素膜2647を、臭素を含むガスを用いてエッチング処理する。本実施例では、臭化水素、塩素、および酸素の流量をそれぞれ100:44:6の比になるように混合してエッチング用のガスとし、ICP装置を用いてプラズマエッチング処理を行い、図27(C)に示すようにサイドウォール2649を形成する。なお、このエッチング用のガスに含まれる臭化水素の流量比を変えてよい。具体的には、塩素と酸素の流量比を44:6に固定したとき、臭化水素の流量比は50以上130以下であればよい。この範囲内であれば、臭化水素の流量比に関係なく、一定の大きさでサイドウォールが形成される。

## 【0218】

なお、上記のエッチング処理において、圧力は1.6Pa、ICPの高周波は450W、BIASの高周波は150Wである。ICPに印加する高周波はプロセスガスを分解する役割を持ち、BIASに印加する高周波はエッチング種(イオン)を加速する役割を持つ。

## 【0219】

本実施例ではドライエッチングの方法としてICP法を用いているが、この方法には限らない。同様にして、平行平板型RIE(反応性イオンエッチング)、マグネットロン型RIE、2周波型RIE、マイクロ波型RIE、ECR(電子サイクロトロン共鳴)プラズマエッチング、ヘリコン型プラズマエッチングなどのエッチング方法を用いることができる。

## 【0220】

次に、サイドウォール2649をマスクとして先程よりも高いドーザ量でN型の導電性を示すイオンの導入を行い、TFT2641のソース領域またはドレイン領域2640、及びTFT2643のソース領域またはドレイン領域2642、およびLDD領域2645を形成する。不純物の導入が終了した後、レーザアニール、ランプアニール、またはファーネスアニールによって処理を行い、導入した不純物の活性化と、不純物の導入に伴う結晶性の損傷を回復させる。

## 【0221】

次いで、CVD法により酸化珪素膜を含む第1の層間絶縁膜(図示しない)を50nm形成した後、それぞれの島状半導体膜2624、2626に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法(RTA法)、YAGレーザやエキシマレーザなどのレーザビームを照射する方法、炉を用いた熱処理、またはこれらの方のいずれかを組み合わせた方法によって行う。

#### 【0222】

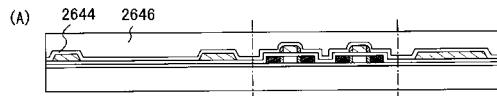

次いで、水素及び酸素を含む窒化珪素膜を含む第2の層間絶縁膜2644を形成する(図27(D))。本実施例ではその一例として、10nmの膜厚で形成する。

#### 【0223】

次いで、第2の層間絶縁膜2644上に絶縁物材料から成る第3の層間絶縁膜2646を形成する(図28(A)参照)。第3の層間絶縁膜2646はCVD法で得られる絶縁膜を用いることができる。本実施例においては密着性を向上させるため、第3の層間絶縁膜2646として、窒素を含む酸化珪素膜を900nmの膜厚で形成する。

#### 【0224】

次に、熱処理(300以上550以下で1時間以上12時間以下の熱処理、例えば窒素雰囲気中410で1時間)を行い、島状半導体膜2624、2626を水素化する。この工程は第2の層間絶縁膜2644に含まれる水素により島状半導体膜2624、2626のダングリングボンドを終端させるために行うものである。ゲート絶縁膜2628の存在に関係なく島状半導体膜2624、2626を水素化することができる。

#### 【0225】

また第3の層間絶縁膜2646として、シロキサンを用いた絶縁膜、及びそれらの積層構造を用いることも可能である。シロキサンは、珪素と酸素との結合(シロキサン結合)で骨格構造が構成され、珪素にフッ素、脂肪族炭化水素、または芳香族炭化水素のうち少なくとも一種が結合した構造を持つ物質である。

#### 【0226】

第3の層間絶縁膜2646としてシロキサンを用いた絶縁膜、及びそれらの積層構造を用いた場合は、第2の層間絶縁膜2644を形成後、島状半導体膜2624、2626を水素化するための熱処理を行い、次に第3の層間絶縁膜2646を形成することもできる。

#### 【0227】

次いで、第3のフォトマスクを用いてレジストからなるマスクを形成し、第1の層間絶縁膜、第2の層間絶縁膜2644第3の層間絶縁膜2646及びゲート絶縁膜2628を選択的にエッチングしてコンタクトホールを形成する。そして、レジストからなるマスクを除去する。

#### 【0228】

なお、第3の層間絶縁膜2646は必要に応じて形成すればよく、第3の層間絶縁膜2646を形成しない場合は、第2の層間絶縁膜2644を形成後に第1の層間絶縁膜、第2の層間絶縁膜2644及びゲート絶縁膜2628を選択的にエッチングしてコンタクトホールを形成する。

#### 【0229】

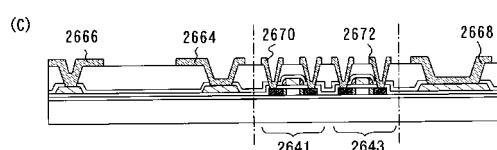

次いで、スパッタ法で金属積層膜を成膜した後、第4のフォトマスクを用いてレジストからなるマスクを形成し、選択的に金属膜をエッチングして、配線2635、接続電極2648、端子電極2651、TFT2641のソース領域またはドレイン領域2640に接続する電極(以後、ソース電極またはドレイン電極と呼ぶ)2652、TFT2643のソース領域またはドレイン領域2642に接続する電極(以後、ソース電極またはドレイン電極と呼ぶ)2654を図28(B)に示すように形成する。そして、レジストからなるマスクを除去する。なお、本実施例の金属膜は、膜厚100nmのTi膜と、膜厚350nmのSiを微量に含むAl膜と、膜厚100nmのTi膜との3層を積層したものとする。

#### 【0230】

10

20

30

40

50

次いで、後に形成される光電変換層（代表的にはアモルファスシリコン）と反応しても合金になりにくい導電性の金属膜（チタン（Ti）またはモリブデン（Mo）など）を成膜した後、第5のフォトマスクを用いてレジストからなるマスクを形成し、選択的に導電性の金属膜をエッチングして配線2634と接続する保護電極2650を形成する（図28（B）参照）。ここではスパッタ法で得られる膜厚200nmのTi膜を用いる。なお、同様に接続電極2648、端子電極2638、TFT2641のソース電極またはドレイン電極2652、TFT2643のソース電極またはドレイン電極2654も導電性の金属膜で覆われ、それぞれ保護電極2656、2658、2660、2662が形成される。従って、導電性の金属膜は、これらの電極における2層目のA1膜が保護電極2650、2656、2658、2660、および2662の側面も覆い、導電性の金属膜は光電変換層へのアルミニウム原子の拡散も防止できる。10

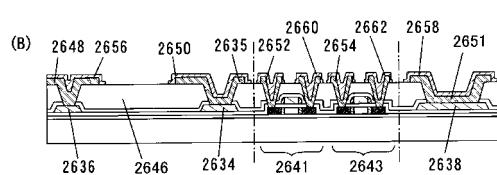

### 【0231】

ただし、配線2634、接続電極2648、端子電極2638、TFT2641のソース電極またはドレイン電極2654、及びTFT2643のソース電極またはドレイン電極2654を、単層の導電膜で形成する場合、すなわち図28（C）で示すように、これらの電極又は配線に代えて、配線2664、接続電極2666、端子電極2668、及びTFT2641のソース電極又はドレイン電極2670、及びTFT2643のソース電極又はドレイン電極2672を形成する場合は、保護電極を形成しなくてもよい。20

### 【0232】

図28（C）のように、配線2664、接続電極2666、端子電極2668、及びTFT2641のソース電極又はドレイン電極2670、及びTFT2643のソース電極又はドレイン電極2672を単層の導電膜により形成する場合は、耐熱性及び導電率等の点からチタン膜（Ti膜）が好ましい。またチタン膜に変えて、タンゲステン（W）、タンタル（Ta）、モリブデン（Mo）、ネオジウム（Nd）、コバルト（Co）、ジルコニウム（Zr）、亜鉛（Zn）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスミウム（Os）、イリジウム（Ir）、白金（Pt）から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。配線2664、接続電極2666、端子電極2668、及びTFT2641のソース電極又はドレイン電極2670、及びTFT2643のソース電極又はドレイン電極2672を単層膜にすることにより、作製工程において成膜回数を減少させることができる。30

### 【0233】

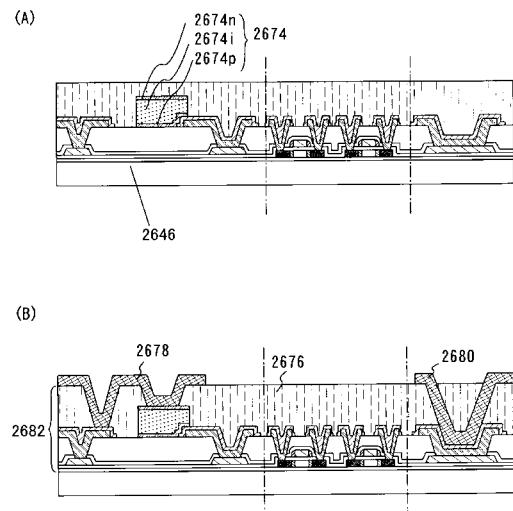

次に、第3の層間絶縁膜2646上に、P型半導体層2674p、i型半導体層2674i及びN型半導体層2674nを含む光電変換層2674を形成する（図29（A））。

### 【0234】

P型半導体層2674pは、13属の不純物元素、例えばホウ素（B）を含んだアモルファスシリコン膜をプラズマCVD法にて成膜して形成すればよい。

### 【0235】

また配線2634及び保護電極2650は光電変換層2674の最下層、本実施例ではP型半導体層2674pと電気的に接続されている。40

### 【0236】

また、図28（C）のように保護電極を形成せず、配線2664、接続電極2666、端子電極2668、及びTFT2641のソース電極又はドレイン電極2670、及びTFT2643のソース電極又はドレイン電極2672を単層の導電膜で形成した場合は、配線2664上に光電変換層2674の最下層が接することとなる。

### 【0237】

P型半導体層2674pを形成したら、さらにi型半導体層2674i及びN型半導体層2674nを順に形成する。これによりP型半導体層2674p、i型半導体層2674i

10

20

30

40

50

4 i 及び N 型半導体層 2674n を有する光電変換層が形成される（図 29（A））。

【0238】

i 型半導体層 2674i としては、例えばプラズマ CVD 法でアモルファスシリコン膜を形成すればよい。また N 型半導体層 2674n としては、15 属の不純物元素、例えばリン（P）を含むアモルファスシリコン膜を形成してもよいし、アモルファスシリコン膜を形成後、15 属の不純物元素を導入してもよい。

【0239】

また P 型半導体層 2674p、i 型半導体層 2674i、N 型半導体層 2674n として、アモルファス半導体膜だけではなく、セミアモルファス半導体膜を用いてもよい。

【0240】

次いで、全面に絶縁物材料（例えば珪素を含む無機絶縁膜）からなる封止層 2676 を厚さ（1 μm ~ 30 μm）で形成する。ここでは絶縁物材料膜として CVD 法により、膜厚 1 μm の窒素を含む酸化珪素膜を形成する。CVD 法で形成した絶縁膜を封止層 2676 に用いることによって、密着性の向上を図っている（図 29（A））。

【0241】

次いで、封止層 2676 をエッティングして開口部を設けた後、スパッタ法により端子電極 2678 及び 2680 を形成する（図 29（B））。端子電極 2678 及び 2680 は、チタン膜（Ti 膜）（100 nm）と、ニッケル膜（Ni 膜）（300 nm）と、金属膜（Au 膜）（50 nm）との積層膜とする。こうして得られる端子電極 2678 及び端子電極 2680 の固着強度は 5 N を超え、端子電極として十分な固着強度を有している。

【0242】

以上の工程で、半田接続が可能な端子電極 2678 及び端子電極 2680 が形成され、図 29（B）に示す構造が得られる。なお、素子形成層 2682 とは、下地絶縁膜 2602 から封止層 2676 までを形成したものとする。

【0243】

次いで、個々に切断して複数の光センサチップを切り出す。1 枚の大面積基板（例えば 600 cm × 720 cm）からは大量の光センサチップ（2 mm × 1.5 mm）を製造することが可能である。

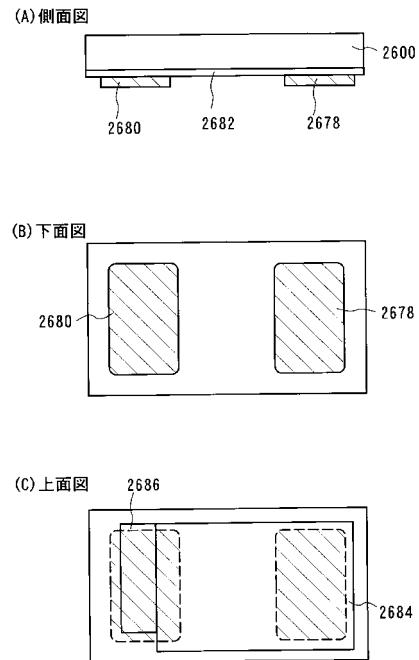

【0244】

切り出した 1 つの光センサチップ（2 mm × 1.5 mm）の断面図を図 30（A）に示し、その下面図を図 30（B）、上面図を図 30（C）に示す。なお、図 30（A）において、基板 2600 と、素子形成層 2682 と、端子電極 2678 及び端子電極 2680 とを含む総膜厚は、0.8 ± 0.05 mm である。

【0245】

また、光センサチップの総膜厚を薄くするために、基板 2600 を CMP 处理等によって削って薄くした後、ダイサーで個々に切断して複数の光センサチップを切り出してもよい。

【0246】

また、図 30（B）において、端子電極 2678 及び 2680 の一つの電極サイズは、0.6 mm × 1.1 mm であり、電極間隔は 0.4 mm である。また、図 30（C）において受光部 2684 の面積は、1.57 mm<sup>2</sup> である。また、增幅回路部 2686 には、約 100 個の TFT が設けられている。

【0247】

最後に、得られた光センサチップを基板 2688 の実装面に実装する。なお、端子電極 2678 と電極 2690、並びに端子電極 2680 と電極 2692 との接続には、それぞれ半田 2694 及び 2696 を用い、予め基板 2600 の電極 2690 及び 2692 上にスクリーン印刷法などによって形成しておき、半田と端子電極を当接した状態にしてから半田リフロー処理を行って基板 2688 に光センサチップを実装する。半田リフロー処理は、例えば不活性ガス雰囲気中、255 ~ 265 程度の温度で約 10 秒行う。また、半田の他に金属（金、銀等）で形成されるバンプ、又は導電性樹脂で形成されるバンプ等

10

20

30

40

50

を用いることができる。また、環境問題を考慮して鉛フリーはんだを用いて実装してもよい。以上の工程によって、図31に示す光センサチップが完成する。光を受光するのは、矢印の部分からである。なお、図31(A)と図31(B)の違いは、保護電極の有無である。

【0248】

本実施例は、実施の形態および他の実施例と組み合わせることが可能である。

【図面の簡単な説明】

【0249】

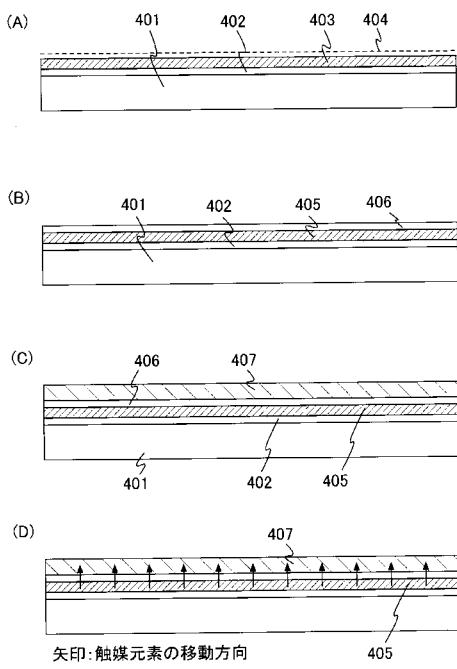

【図1】本発明のエッチング方法を説明する図である。

【図2】本発明のエッチング過程における断面の状態を示す図面代用写真である。

10

【図3】図2の図面代用写真を図面にしたものである。

【図4】本発明を用いた半導体素子の作製過程を示す図である。

【図5】本発明を用いた半導体素子の作製過程を示す図である。

【図6】本発明を用いた半導体素子の作製過程を示す図である。

【図7】本発明を用いた半導体素子の作製過程を示す図である。

【図8】本発明を用いてCMOS型のICを作製する過程を示す図である。

【図9】本発明を用いてCMOS型のICを作製する過程を示す図である。

【図10】本発明を用いてCMOS型のICを作製する過程を示す図である。

【図11】本発明を用いてCMOS型のICを作製する過程を示す図である。

20

【図12】本発明を用いた無線ICタグを作製する過程を示す図である。

【図13】本発明を用いた無線ICタグを作製する過程を示す図である。

【図14】本発明を用いた無線ICタグを作製する過程を示す図である。

【図15】本発明を用いた無線ICタグを作製する過程を示す図である。

【図16】本発明を用いた無線ICタグを作製する過程を示す図である。

【図17】本発明を用いて作製した無線ICタグの使用方法の一例を示す図である。

【図18】本発明を用いて作製した無線ICタグの使用方法の一例を示す図である。

【図19】本発明を用いて作製した無線ICタグの情報処理方法を示す流れ図である。

【図20】本発明を用いて作製した無線ICタグの使用方法の一例を示す図である。

【図21】本発明を用いて作製した電子機器の一例を示す図である。

【図22】臭化水素ガスの濃度を変えて窒化珪素膜をエッチングするための試料を作製する過程を示す図である。

【図23】図22で作製した試料を用いて窒化珪素膜をエッチングする様子を示す図である。

【図24】臭化水素ガスの濃度を変えて窒化珪素膜をエッチングすることによって形成したサイドウォールの幅を示す表とグラフである。

【図25】エッチング終了点における図面代用写真である。

【図26】本発明を用いて作製したフォトICの作製過程を示す図である。

【図27】本発明を用いて作製したフォトICの作製過程を示す図である。

【図28】本発明を用いて作製したフォトICの作製過程を示す図である。

40

【図29】本発明を用いて作製したフォトICの作製過程を示す図である。

【図30】本発明を用いて作製したフォトICの作製過程を示す図である。

【図31】本発明を用いて作製したフォトICの作製過程を示す図である。

【符号の説明】

【0250】

101 絶縁性基板

102 下地膜

103 非晶質半導体膜

104 半導体膜

105 ゲート絶縁膜

106 ゲート電極

50

|       |           |    |

|-------|-----------|----|

| 1 0 7 | N型領域      |    |

| 1 0 8 | 窒化珪素膜     |    |

| 1 0 9 | サイドウォール   |    |

| 2 0 1 | 半導体膜      |    |

| 2 0 2 | 窒化珪素膜     |    |

| 3 0 1 | 半導体膜      |    |

| 3 0 2 | 窒化珪素膜     |    |

| 4 0 1 | 基板        |    |

| 4 0 2 | 下地膜       |    |

| 4 0 3 | 非晶質半導体膜   | 10 |

| 4 0 4 | 膜         |    |

| 4 0 5 | 半導体膜      |    |

| 4 0 6 | 酸化膜       |    |

| 4 0 7 | 半導体膜      |    |

| 4 0 8 | 半導体膜      |    |

| 4 0 9 | ゲート絶縁膜    |    |

| 4 1 0 | ゲート電極     |    |

| 4 1 1 | ゲート電極     |    |

| 4 1 2 | レジスト      |    |

| 4 1 3 | N型不純物領域   | 20 |

| 4 1 4 | レジスト      |    |

| 4 1 5 | P型不純物領域   |    |

| 4 1 6 | 窒化珪素膜     |    |

| 4 1 7 | サイドウォール   |    |

| 4 1 8 | レジスト      |    |

| 4 1 9 | LDD領域     |    |

| 4 2 0 | レジスト      |    |

| 4 2 1 | LDD領域     |    |

| 4 2 2 | Pチャネル型TFT |    |

| 4 2 3 | Nチャネル型TFT | 30 |

| 4 2 4 | 絶縁膜       |    |

| 4 2 5 | 絶縁膜       |    |

| 4 2 6 | ソース領域     |    |

| 4 2 7 | ソース領域     |    |

| 4 2 8 | ドレイン領域    |    |

| 4 2 9 | ドレイン領域    |    |

| 4 3 0 | 配線        |    |

| 4 3 1 | 絶縁膜       |    |

| 8 0 0 | シリコン基板    |    |

| 8 0 1 | 窒化珪素膜     | 40 |

| 8 0 2 | 素子形成領域    |    |

| 8 0 3 | 素子形成領域    |    |

| 8 0 4 | フィールド酸化膜  |    |

| 8 0 5 | レジスト      |    |

| 8 0 6 | N型ウェル     |    |

| 8 0 7 | P型ウェル     |    |

| 8 0 8 | ゲート絶縁膜    |    |

| 8 0 9 | ゲート電極     |    |

| 8 1 0 | ゲート電極     |    |

| 8 1 1 | レジスト      | 50 |

|         |           |    |

|---------|-----------|----|

| 8 1 2   | N型不純物領域   |    |

| 8 1 3   | レジスト      |    |

| 8 1 4   | P型不純物領域   |    |

| 8 1 5   | 窒化珪素膜     |    |

| 8 1 6   | サイドウォール   |    |

| 8 1 7   | レジスト      |    |

| 8 1 8   | ソース領域     |    |

| 8 1 9   | ドレイン領域    |    |

| 8 2 0   | レジスト      |    |

| 8 2 1   | ソース領域     | 10 |

| 8 2 2   | ドレイン領域    |    |

| 8 2 3   | 層間絶縁膜     |    |

| 8 2 4   | 層間絶縁膜     |    |

| 8 2 5   | 配線        |    |

| 8 2 6   | パッシベーション膜 |    |

| 8 2 7   | 層間絶縁膜     |    |

| 8 2 8   | Nチャネル型TFT |    |

| 8 2 9   | Pチャネル型TFT |    |

| 1 2 0 0 | 基板        |    |

| 1 2 0 1 | 剥離層       | 20 |

| 1 2 0 2 | 下地絶縁膜     |    |

| 1 2 0 3 | 半導体膜      |    |

| 1 2 0 4 | 結晶性半導体膜   |    |

| 1 2 0 5 | 半導体膜      |    |

| 1 2 0 6 | 半導体膜      |    |

| 1 2 0 7 | 半導体膜      |    |

| 1 2 0 8 | ゲート絶縁膜    |    |

| 1 2 0 9 | ゲート電極     |    |

| 1 2 1 0 | ゲート電極     |    |

| 1 2 1 1 | ゲート電極     | 30 |

| 1 2 1 2 | レジスト      |    |

| 1 2 1 3 | レジスト      |    |

| 1 2 1 6 | 低濃度不純物領域  |    |

| 1 2 1 7 | 低濃度不純物領域  |    |

| 1 2 1 8 | レジスト      |    |

| 1 2 2 0 | 高濃度不純物領域  |    |

| 1 2 2 1 | 窒化珪素膜     |    |

| 1 2 2 2 | サイドウォール   |    |

| 1 2 2 3 | サイドウォール   |    |

| 1 2 2 4 | サイドウォール   | 40 |

| 1 2 2 6 | レジスト      |    |

| 1 2 2 7 | 高濃度不純物領域  |    |

| 1 2 2 8 | 高濃度不純物領域  |    |

| 1 2 3 0 | Nチャネル型TFT |    |

| 1 2 3 1 | Pチャネル型TFT |    |

| 1 2 3 2 | Nチャネル型TFT |    |

| 1 2 3 3 | 層間絶縁膜     |    |

| 1 2 3 4 | 層間絶縁膜     |    |

| 1 2 3 5 | 配線        |    |

| 1 2 3 6 | 配線        | 50 |

|         |            |    |

|---------|------------|----|

| 1 2 3 7 | 配線         |    |

| 1 2 3 8 | 配線         |    |

| 1 2 3 9 | 配線         |    |

| 1 2 4 1 | 層間絶縁膜      |    |

| 1 2 4 2 | アンテナ       |    |

| 1 2 4 5 | 保護層        |    |

| 1 2 4 6 | 溝          |    |

| 1 2 5 0 | 接着剤        |    |

| 1 2 5 1 | 基板         |    |

| 1 2 5 2 | 接着剤        | 10 |

| 1 2 5 3 | カバー材       |    |

| 1 7 0 1 | パスポート      |    |

| 1 7 0 2 | 無線ICタグ     |    |

| 1 7 1 1 | 無線ICタグ     |    |

| 1 7 1 2 | リーダ        |    |

| 1 7 1 3 | アンテナ部      |    |

| 1 7 1 4 | 表示部        |    |

| 1 8 0 0 | 無線ICタグ     |    |

| 1 8 0 1 | 商品         |    |

| 1 8 0 2 | 冷蔵庫        | 20 |

| 1 8 0 3 | リーダ        |    |

| 1 8 0 4 | 演算装置       |    |

| 1 8 0 5 | 記憶装置       |    |

| 1 8 0 6 | 調節装置       |    |

| 1 8 0 7 | 制御装置       |    |

| 1 8 0 8 | モニタ        |    |

| 2 0 0 0 | 無線ICタグ     |    |

| 2 0 0 1 | 洗濯物        |    |

| 2 0 0 2 | 洗濯機        |    |

| 2 0 0 3 | リーダ        | 30 |

| 2 0 0 4 | モニタ        |    |

| 2 1 0 1 | 筐体         |    |

| 2 1 0 2 | 支持台        |    |

| 2 1 0 3 | 表示部        |    |

| 2 1 0 4 | スピーカー部     |    |

| 2 1 0 5 | ビデオ入力端子    |    |

| 2 1 1 1 | 筐体         |    |

| 2 1 1 2 | 表示部        |    |

| 2 1 1 3 | キー ボード     |    |

| 2 1 1 4 | 外部接続ポート    | 40 |

| 2 1 1 5 | ポインティングマウス |    |

| 2 1 2 1 | 筐体         |    |

| 2 1 2 2 | 表示部        |    |

| 2 1 2 3 | 操作キー       |    |

| 2 1 2 4 | センサ部       |    |

| 2 1 3 1 | 筐体         |    |

| 2 1 3 2 | 表示部        |    |

| 2 1 3 3 | レンズ        |    |

| 2 1 3 4 | 操作キー       |    |

| 2 1 3 5 | シャッター      | 50 |

|         |           |    |

|---------|-----------|----|

| 2 1 4 1 | 本体        |    |

| 2 1 4 2 | 表示部       |    |

| 2 1 4 3 | 筐体        |    |

| 2 1 4 4 | 外部接続ポート   |    |

| 2 1 4 5 | リモコン受信部   |    |

| 2 1 4 6 | 受像部       |    |

| 2 1 4 7 | バッテリー     |    |

| 2 1 4 8 | 音声入力部     |    |

| 2 1 4 9 | 操作キー      |    |

| 2 1 5 0 | 接眼部       | 10 |

| 2 2 0 0 | 絶縁性基板     |    |

| 2 2 0 2 | 下地膜       |    |

| 2 2 0 4 | 導電膜       |    |

| 2 2 0 6 | 導電膜       |    |

| 2 2 0 8 | 絶縁膜       |    |

| 2 2 1 0 | 窒化珪素膜     |    |

| 2 6 0 0 | 基板        |    |

| 2 6 0 2 | 下地絶縁膜     |    |

| 2 6 0 4 | 非晶質半導体膜   |    |

| 2 6 0 6 | 触媒        | 20 |

| 2 6 0 8 | 多結晶珪素膜    |    |

| 2 6 1 0 | バリア層      |    |

| 2 6 1 2 | 非晶質珪素膜    |    |

| 2 6 2 4 | 島状半導体膜    |    |

| 2 6 2 6 | 島状半導体膜    |    |

| 2 6 2 8 | ゲート絶縁膜    |    |

| 2 6 3 0 | ゲート電極     |    |

| 2 6 3 2 | ゲート電極     |    |

| 2 6 3 4 | 配線        |    |

| 2 6 3 5 | 配線        | 30 |

| 2 6 3 8 | 端子電極      |    |

| 2 6 4 0 | ドレイン領域    |    |

| 2 6 4 1 | Nチャネル型TFT |    |

| 2 6 4 2 | ドレイン領域    |    |

| 2 6 4 3 | TFT       |    |

| 2 6 4 4 | 層間絶縁膜     |    |

| 2 6 4 5 | LDD領域     |    |

| 2 6 4 6 | 層間絶縁膜     |    |

| 2 6 4 7 | 窒化珪素膜     |    |

| 2 6 4 8 | 接続電極      | 40 |

| 2 6 4 9 | サイドウォール   |    |

| 2 6 5 0 | 保護電極      |    |

| 2 6 5 1 | 端子電極      |    |

| 2 6 5 2 | ドレイン電極    |    |

| 2 6 5 4 | ドレイン電極    |    |

| 2 6 5 6 | 保護電極      |    |

| 2 6 6 4 | 配線        |    |

| 2 6 6 6 | 接続電極      |    |

| 2 6 6 8 | 端子電極      |    |

| 2 6 7 0 | ドレイン電極    | 50 |

2 6 7 2 ドレイン電極

2 6 7 4 光電変換層

2 6 7 6 封止層

2 6 7 8 端子電極

2 6 8 0 端子電極

2 6 8 2 素子形成層

2 6 8 4 受光部

2 6 8 6 増幅回路部

2 6 8 8 基板

2 6 9 0 電極

2 6 9 2 電極

2 6 9 4 半田

2 6 7 4 i i型半導体層

2 6 7 4 n N型半導体層

2 6 7 4 p P型半導体層

10

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

(A)

| HBrの流量<br>[sccm] | 処理を行った点<br>[μm] | out<br>[μm] | in<br>[μm] | サイドウォール長<br>[μm] | 平均<br>[μm] |

|------------------|-----------------|-------------|------------|------------------|------------|

| 50               | 1               | 1.5663      | 1.0387     | 0.2638           | 0.271      |

|                  | 2               | 1.5444      | 1.0212     | 0.2616           |            |

|                  | 3               | 1.6111      | 1.0475     | 0.2818           |            |

|                  | 4               | 1.6237      | 1.0732     | 0.2753           |            |

| 100              | 1               | 1.5927      | 1.0466     | 0.2731           | 0.268      |

|                  | 2               | 1.5820      | 1.0490     | 0.2665           |            |

|                  | 3               | 1.5757      | 1.0390     | 0.2684           |            |

|                  | 4               | 1.6154      | 1.0855     | 0.2650           |            |

| 130              | 1               | 1.5985      | 1.0284     | 0.2851           | 0.275      |

|                  | 2               | 1.5706      | 1.0356     | 0.2675           |            |

|                  | 3               | 1.5926      | 1.0476     | 0.2725           |            |

|                  | 4               | 1.6379      | 1.0916     | 0.2732           |            |

(B)

【図26】

(A)

(B)

(C)

(D)

【図27】

【図28】

【図29】

【図30】

【図31】

【図2】

【図25】

(A)

50sccmにおけるエッチング終了点

(B)

100sccmにおけるエッチング終了点

(C)

130sccmにおけるエッチング終了点

## フロントページの続き

F ターム(参考) 5F110 AA26 BB04 BB10 BB20 CC02 DD01 DD02 DD03 DD04 DD05

DD13 DD14 DD15 DD17 EE01 EE02 EE03 EE04 EE05 EE06

EE09 EE14 EE15 EE32 EE44 EE45 FF01 FF04 FF09 FF28

FF30 GG01 GG02 GG04 GG07 GG12 GG13 GG25 GG28 GG32

GG43 GG45 GG47 GG51 GG52 HJ01 HJ13 HJ23 HM15 NN03

NN04 NN22 NN23 NN24 NN27 NN34 NN35 NN36 NN71 PP01

PP02 PP03 PP29 PP34 QQ02 QQ04 QQ09 QQ11 QQ16 QQ17

QQ19 QQ23 QQ24 QQ25 QQ28

5F140 AA00 AA26 AB03 AC36 BA01 BA02 BA07 BA08 BA10 BD01

BD04 BD05 BD07 BD09 BD11 BD12 BE07 BE10 BF05 BF07

BF10 BF11 BF15 BF17 BF21 BF27 BG08 BG14 BG37 BG52

BG53 BH15 BH22 BJ01 BJ05 BJ11 BJ17 BK02 BK13 BK21

BK25 CA02 CA03 CB01 CB04 CB08 CC01 CC03 CC05 CC06

CC07 CC08 CC09 CC10 CC12 CC13 CC16 CE18