(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6370929号

(P6370929)

(45) 発行日 平成30年8月8日(2018.8.8)

(24) 登録日 平成30年7月20日(2018.7.20)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

N

請求項の数 20 (全 20 頁)

(21) 出願番号 特願2016-568905 (P2016-568905)

(86) (22) 出願日 平成26年5月22日 (2014.5.22)

(65) 公表番号 特表2017-517235 (P2017-517235A)

(43) 公表日 平成29年6月22日 (2017.6.22)

(86) 国際出願番号 PCT/CN2014/078117

(87) 国際公開番号 WO2015/176269

(87) 国際公開日 平成27年11月26日 (2015.11.26)

審査請求日 平成29年5月12日 (2017.5.12)

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 代理人 100098497

弁理士 片寄 恒三

(72) 発明者 ジミン フー

中華人民共和国 広東省 シェンゼン,

トウエルフス ナンシャン ディストリクト,

ケジ サウス ロード ナンバー2

8, コンカ アールアンドティー ビル

ディング 9階

最終頁に続く

(54) 【発明の名称】デュアルカウンタデジタル積分器を備えるDC - DCコンバータコントローラ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

DC - DCコンバータであって、

スイッチングノードに接続される少なくとも1つのスイッチを含むスイッチング回路と、

コンバータ出力ノードの出力電圧を制御するように前記少なくとも1つのスイッチを選択的に作動および停止させるためにスイッチング制御信号を提供する変調器回路と、

前記出力電圧に少なくとも部分的に基づいてフィードバック電圧信号を提供するため前に記コンバータ出力ノードと結合されるフィードバック回路と、

前記フィードバック電圧信号を受信するように接続される第1のコンパレータ入力と、

補償された基準信号を受信するように接続される第2のコンパレータ入力と、前記フィードバック電圧信号と前記補償された基準信号とに基づいて前記出力電圧をレギュレートするためループコンパレータ出力信号を前記変調器回路に提供するループコンパレータ出力とを備えるループ比較器回路と、

デジタル積分器回路であって、

基準電圧に少なくとも部分的に基づいて積分器基準電圧信号を提供する基準回路と、

前記積分器基準電圧信号を受信するように前記基準回路に結合される第1の入力と、前記フィードバック電圧信号を受信するように前記フィードバック回路に結合される第2の入力と、前記基準電圧信号が前記フィードバック電圧信号よりも大きいかどうかを示すバイナリ比較器出力信号を提供するコンパレータ出力とを含む比較器回路と、

デュアルカウンタ回路と、

を含み、

前記デュアルカウンタ回路が、

積分器回路クロックソースに結合される第1のクロック入力と、前記比較器回路から前記コンパレータ出力信号を受信するように結合される第1のアップ/ダウンカウント入力と、マルチビットの第1のカウンタ出力値を示す信号を提供する複数の第1のカウンタビット出力とを含むマルチビットの第1のカウンタと、

第2のクロック入力と、第2のアップ/ダウンカウント入力と、マルチビットの第2のカウンタ出力値を示す信号を提供する複数の第2のカウンタビット出力とを含むマルチビットの第2のカウンタと、

前記第1のカウンタビット出力が初期に前記第1のカウンタの所定の値を示すことに応答して前記第2のカウンタを初期にインクリメントまたはデクリメントし、その後、前記第1のカウンタビット出力が前記第1のカウンタの全値範囲にわたって一方向に遷移した後に前記第1のカウンタビット出力が再び前記所定の値を示すことに応答して前記第2のカウンタをインクリメントまたはデクリメントするように作用する、論理回路と、

を含む、

前記デジタル積分器回路と、

前記第2のカウンタビット出力に接続される複数の入力と、前記第2のカウンタビット出力と前記基準電圧とに少なくとも部分的に基づいて前記第2のコンパレータ入力に提供される前記補償された基準信号を制御する出力とを備えるデジタル アナログコンバータと、

を含む、DC DCコンバータ。

### 【請求項2】

請求項1に記載のDC DCコンバータであって、

前記論理回路が、前記第1のカウンタに結合される複数の入力と、前記第2のクロック入力に結合される第1の論理出力と、前記第2のアップ/ダウンカウント入力に結合される第2の論理出力を含み、

前記論理回路が、

前記第1のカウンタビット出力が前記第1のカウンタの第1の所定の値を示すことに応答して前記第1の論理出力を第1のバイナリクロック入力状態に設定し、

前記第1のカウンタビット出力が前記第1のカウンタの第2の所定の値を示すことに応答して前記第1の論理出力を第2のバイナリクロック入力状態に設定し、

前記第1のカウンタビット出力が前記第1のカウンタの前記第2の所定の値へ第1の方向に遷移することに応答して前記第2の論理出力を第1のバイナリカウンタ状態に設定し、

前記第1のカウンタビット出力が前記第1のカウンタの前記第2の所定の値へ第2の方向に遷移することに応答して前記第2の論理出力を第2のバイナリカウンタ状態に設定するように、

作用する、DC DCコンバータ。

### 【請求項3】

請求項2に記載のDC DCコンバータであって、

前記デュアルカウンタ回路が、

第1の状態において前記第2のカウンタの前記第2のクロック入力を前記論理回路の前記第1の論理出力に接続するために、第2の状態において前記第2のカウンタの前記第2のクロック入力を前記積分器回路クロックソースに接続するために、制御入力に従って作用する第1のスイッチと、

前記第1の状態において前記第2のカウンタの前記第2のアップ/ダウンカウント入力を前記論理回路の前記第2の論理出力に接続するために、前記第2の状態において前記第2のカウンタの前記第2のアップ/ダウンカウント入力を前記コンパレータ出力に接続するために、前記制御入力に従って作用する第2のスイッチと、

10

20

30

40

50

を更に含む、DC DCコンバータ。

【請求項4】

請求項3に記載のDC DCコンバータであって、

前記第1および第2のカウンタが、第1のモードにおいて対応するクロック入力と対応するアップ/ダウンカウント入力とに従ってそれらのそれぞれのカウンタビット出力を選択的に更新するために、第2のモードにおいてそれらのそれぞれのカウンタビット出力の更新を控えるために、保留制御入力信号に従って個別に動作可能である、DC DCコンバータ。

【請求項5】

請求項2に記載のDC DCコンバータであって、

10

前記第1および第2のカウンタが、第1のモードにおいて対応するクロック入力と対応するアップ/ダウンカウント入力とに従ってそれらのそれぞれのカウンタビット出力を選択的に更新するために、第2のモードにおいてそれらのそれぞれのカウンタビット出力の更新を控えるために、保留制御入力信号に従って個別に動作可能である、DC DCコンバータ。

【請求項6】

請求項1に記載のDC DCコンバータであって、

前記デュアルカウンタ回路が、

第1の状態において前記第2のカウンタの前記第2のクロック入力を前記論理回路に接続するために、第2の状態において前記第2のカウンタの前記第2のクロック入力を前記積分器回路クロックソースに接続するために、制御入力に従って作用する第1のスイッチと、

20

前記第1の状態において前記第2のカウンタの前記第2のアップ/ダウンカウント入力を前記論理回路に接続するために、前記第2の状態において前記第2のカウンタの前記第2のアップ/ダウンカウント入力を前記コンパレータ出力に接続するために、前記制御入力に従って作用する第2のスイッチと、

を更に含む、DC DCコンバータ。

【請求項7】

請求項6に記載のDC DCコンバータであって、

30

前記第1および第2のカウンタが、第1のモードにおいて対応するクロック入力と対応するアップ/ダウンカウント入力とに従ってそれらのそれぞれのカウンタビット出力を選択的に更新するために、第2のモードにおいてそれらのそれぞれのカウンタビット出力の更新を控えるために、保留制御入力信号に従って個別に動作可能である、DC DCコンバータ。

【請求項8】

請求項1に記載のDC DCコンバータであって、

前記第1および第2のカウンタが、第1のモードにおいて対応するクロック入力と対応するアップ/ダウンカウント入力とに従ってそれらのそれぞれのカウンタビット出力を選択的に更新するために、第2のモードにおいてそれらのそれぞれのカウンタビット出力の更新を控えるために、保留制御入力信号に従って個別に動作可能である、DC DCコンバータ。

40

【請求項9】

パルス幅変調(PWM)コントローラであって、

マルチビットデジタル入力と基準電圧とに少なくとも部分的に従って補償された基準信号を提供する基準補償回路と、

フィードバック電圧信号と前記補償された基準信号とに基づいて電力コンバータ出力電圧を制御するためにループコンパレータ出力信号を変調器回路に提供するループ比較器回路と、

基準電圧に少なくとも部分的に基づいて積分器基準電圧信号を提供する基準回路と、基準電圧信号が前記フィードバック電圧信号よりも大きいかどうかを示すバイナリ比較器出

50

力信号を提供する比較器回路と、デュアルカウンタ回路とを含む、デジタル積分器回路と、

を含み、

前記デュアルカウンタ回路が、

前記コンパレータ出力信号と積分器クロック入力信号とを受信し、マルチビットの第1のカウンタ値を提供する、第1のカウンタと、

第2のクロック入力と第2のアップ/ダウンカウント入力とを含み、前記マルチビットデジタル入力を前記基準補償回路に提供する、第2のカウンタと、

前記第1のカウンタ値が所定の値を示すことに基づいて前記第2のカウンタを初期にインクリメントまたはデクリメントし、その後、前記第1のカウンタ値が所定のマルチビットカウント範囲にわたってインクリメントまたはデクリメントすることに応答して第2のカウンタを選択的にインクリメントまたはデクリメントする、論理回路と、

を含む、パルス幅変調コントローラ。

【請求項10】

請求項9に記載のPWMコントローラであって、

前記所定のマルチビットカウント範囲が前記第1のカウンタの全範囲である、PWMコントローラ。

【請求項11】

請求項10に記載のPWMコントローラであって、

第1の状態において前記第2のクロック入力を前記論理回路に接続するため、第2の状態において前記第2のクロック入力を前記積分器クロック入力信号に接続するため、制御入力に従って作用する第1のスイッチと、

前記第1の状態において前記第2のアップ/ダウンカウント入力を前記論理回路に接続するため、前記第2の状態において前記第2のアップ/ダウンカウント入力を前記コンパレータ出力に接続するため、前記制御入力に従って作用する第2のスイッチと、

を更に含む、PWMコントローラ。

【請求項12】

請求項11に記載のPWMコントローラであって、

前記第2のカウンタが、前記基準補償回路に提供される前記マルチビットデジタル入力をフリーズするための保留制御入力を更に含む、PWMコントローラ。

【請求項13】

請求項12に記載のPWMコントローラであって、

過電流制限状況が検出されるときに前記基準補償回路に提供される前記マルチビットデジタル入力をフリーズするため前記第2のカウンタの前記保留制御入力に保留信号を選択的に提供するように作用する過電流制限回路を更に含む、PWMコントローラ。

【請求項14】

請求項9に記載のPWMコントローラであって、

第1の状態において前記第2のクロック入力を前記論理回路に接続するため、第2の状態において前記第2のクロック入力を前記積分器クロック入力信号に接続するため、制御入力に従って作用する第1のスイッチと、

前記第1の状態において前記第2のアップ/ダウンカウント入力を前記論理回路に接続するため、前記第2の状態において前記第2のアップ/ダウンカウント入力を前記コンパレータ出力に接続するため、前記制御入力に従って作用する第2のスイッチと、

を更に含む、PWMコントローラ。

【請求項15】

請求項14に記載のPWMコントローラであって、

前記第2のカウンタが、前記基準補償回路に提供される前記マルチビットデジタル入力をフリーズするための保留制御入力を更に含む、PWMコントローラ。

【請求項16】

請求項15に記載のPWMコントローラであって、

10

20

30

40

50

過電流制限状況が検出されるとき<sub>に</sub>前記基準補償回路に提供される前記マルチビットデジタル入力をフリーズするため<sub>に</sub>前記第2のカウンタの前記保留制御入力に保留信号を選択的に提供するように作用する過電流制限回路を更<sub>に</sub>含む、PWMコントローラ。

【請求項17】

請求項9に記載のPWMコントローラであって、

前記第2のカウンタが、前記基準補償回路に提供される前記マルチビットデジタル入力をフリーズするための保留制御入力を更<sub>に</sub>含む、PWMコントローラ。

【請求項18】

請求項17に記載のPWMコントローラであって、

過電流制限状況が検出されるとき<sub>に</sub>前記基準補償回路に提供される前記マルチビットデジタル入力をフリーズするため<sub>に</sub>前記第2のカウンタの前記保留制御入力に保留信号を選択的に提供するように作用する過電流制限回路を更<sub>に</sub>含む、PWMコントローラ。10

【請求項19】

請求項9に記載のPWMコントローラであって、

前記基準補償回路が、前記マルチビットデジタル入力と前記基準電圧とに少なくとも部分的に従って前記補償された基準信号を提供するため<sub>に</sub>、前記マルチビットデジタル入力に従って動作されるスイッチを備える、スイッチングされる抵抗ディバイダ回路を含む、PWMコントローラ。

【請求項20】

基準電圧信号とフィードバック電圧信号との間の誤差を積分するためのデジタル積分器回路であって、20

前記基準電圧信号が前記フィードバック電圧信号よりも大きいかどうかを示すバイナリ比較器出力信号を提供するコンパレータ出力を含む、比較器回路と、

積分器回路クロックソースに結合される第1のクロック入力と、前記コンパレータ出力信号を受信するように結合される第1のアップ/ダウンカウント入力と、マルチビットの第1のカウンタ出力値を示す信号を提供する複数の第1のカウンタビット出力を含む、第1のカウンタと、

第2のクロック入力と、第2のアップ/ダウンカウント入力と、マルチビットの第2のカウンタ出力値を示す信号を提供する複数の第2のカウンタビット出力と、前記第2のカウンタビット出力をフリーズするための保留制御入力を含む、第2のカウンタと。30

前記第1のカウンタビット出力が初期に所定の値を示すことに応答して前記第2のカウンタを初期にインクリメントまたはデクリメントし、その後、前記第1のカウンタビット出力が前記第1のカウンタの全値範囲にわたって一方向に遷移した後に前記第1のカウンタビット出力が再び前記所定の値を示すことのみに応答して前記第2のカウンタをインクリメントまたはデクリメントするように作用する、論理回路と、

第1の状態において前記第2のカウンタの前記第2のクロック入力を前記論理回路に接続するため<sub>に</sub>、第2の状態において前記第2のカウンタの前記第2のクロック入力を前記積分器回路クロックソースに接続するため<sub>に</sub>、制御入力に従って作用する、第1のスイッチと、40

前記第1の状態において前記第2のカウンタの前記第2のアップ/ダウンカウント入力を前記論理回路に接続するため<sub>に</sub>、前記第2の状態において前記第2のカウンタの前記第2のアップ/ダウンカウント入力を前記コンパレータ出力に接続するため<sub>に</sub>、前記制御入力に従って作用する、第2のスイッチと、

を含む、デジタル積分器回路。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、DC-DCコンバータの制御に関し、より詳細には、デュアルカウンタデジタル積分器回路要素を備えるDC-DCコンバータコントローラ装置に関する。

【背景技術】

10

20

30

40

50

## 【0002】

電圧レギュレータおよびDC DCコンバータは、典型的に、プロセッサ、ASIC、メモリ、および、当時の電子回路におけるその他の構成要素の適正な動作のために、安定したレギュレートされた供給電圧を提供することが必要とされる。コンピュータ、スマートフォン、タブレット、および、その他の電子製品は特に、プロセッサおよび他の内部回路要素の動作のために、高度に正確な供給電圧を必要とする。DC DCコンバータコントローラは、典型的に、初期動、負荷トランジエント、過電流状況、および定常状態動作の間、概ね一定の出力電圧を維持するために、閉ループコンバータ動作を提供する。スイッチングコンバータは、典型的に、パルス幅変調されたスイッチング制御信号により動作される一つまたは複数のスイッチングデバイスを含み、パルス幅変調(PWM)の一般的な形態は、概ね固定のスイッチング周波数を用い、コントローラは、フィードバック信号に従って出力電圧をレギュレートするためにスイッチング制御信号パルスの幅または期間を修正する。しかし、固定周波数DC DC変換は、負荷電流に突然の変化がある状態で、電圧レギュレーション制限を受ける。定常状態動作においてさえ、供給電圧の正確さは、PWM比較器回路要素におけるオフセット、電流信号変動、および、基準ディバイダ誤差によって不利に影響され、システムオフセットを補償するためにアナログ積分器回路がしばしば用いられる。しかし、アナログ積分器は、外部コンデンサを必要とし、集積回路ダイの大部分を占有し、また、高電力消費および有限の時定数を受け、負荷トランジエントの間、出力レギュレーションを不十分なものにする。また、不連続導通モード(DCM)と連続導通モード(CCM)との間の遷移の間アナログ積分器をオフにすると、積分器コンデンサ両端の電圧が経時に放電するので、記憶された積算値としての不安定性がもたらされる。それゆえ、アナログ積分器の解決策は、軽負荷状況におけるアナログ積分器の遮断による負荷効率の犠牲を必要とするか、或いは、システムにおける他の機能ブロックからの電力を削減することにより許容可能な軽負荷効率および正確さを提供し得る。デジタル積分器は、アナログ積分器に比べて占有する領域が小さく使用する電力が少ないが、デジタルアップ/ダウンカウンタを用いるデジタル積分器は、特に負荷トランジエント状況の間、ループ安定性問題に悩まされる。従って、従来のアプローチよりも良好なループ安定性を有する、レギュレーション正確さの改善のための、改善されたパルス幅変調コントローラおよびDC DCコンバータに対する需要がある。

## 【発明の概要】

30

## 【0003】

本開示は、ループ比較器および他のPWM制御回路オフセットを補償するために、一体化した、安定した正確な動作を助長するために有利に用いられる複数のカウンタを用いる新規のデジタル積分器を備える、DC DCコンバータおよびコントローラの実施形態を提供する。

## 【0004】

30

DC DCコンバータが開示される。DC DCコンバータは、スイッチング回路、変調器、フィードバック回路、および、フィードバック電圧信号および補償された基準信号に基づいて出力電圧をレギュレートするために出力信号を変調器に提供する、ループ比較器回路を含む。DC DCコンバータはまた、デジタル積分器回路を含み、デジタル積分器回路は、積分器基準電圧信号を受信するために結合される第1の入力と、フィードバック電圧信号を受信するために結合される第2の入力と、基準電圧がフィードバック電圧よりも大きいかどうかを示す出力信号を提供するコンパレータ出力とを含む比較器回路を備える。デジタル積分器は、第1および第2のマルチビットカウンタを備えるデュアルカウンタ回路を含む。第1のカウンタのクロック入力が、積分器回路クロックソースと結合され、第1のカウンタのアップ/ダウンカウント入力が、コンパレータ出力を受信するよう結合され、第1のカウンタは、マルチビットの第1のカウンタ出力値を示す信号を提供する複数の第1のカウンタビット出力を有する。論理回路が、第1のカウンタビット出力が所定の第1のカウンタ値を初期に示すことに応答して、第2のカウンタを初期にインクリメントまたはデクリメントし、その後、第1のカウンタビット出力が、第1のカウンタ

40

50

の全値範囲にわたって一方向に遷移した後、第1のカウンタビット出力が再び所定の値を示すことに応答して、第2のカウンタをインクリメントまたはデクリメントする。デジタル アナログコンバータ (D A C) が提供される。D A C は、第2のカウンタビット出力に接続される複数の入力と、第2のカウンタビット出力および基準電圧に少なくとも部分的に基づいて第2のコンパレータ入力に提供される補償された基準信号を制御する出力を含む。幾つかの実施形態における、第2のカウンタの制御されたインクリメントおよびデクリメントを有する2つの別個のカウンタの提供が、安定性の向上のために積分器の帯域幅または応答時間を有利に制御するために用いられ得、これにより、安定した正確なD C D C コンバータ動作が向上される。

## 【0005】

10

幾つかの実施形態において、通常または定常状態動作にわたり、第2のカウンタのクロックおよびアップ / ダウンカウント入力を論理回路に選択的に接続するために、および、第2のモードにおいて、第2のカウンタアップ / ダウンカウント入力をコンパレータ出力に代替的に接続し、第2のカウンタのクロック入力を積分器回路クロックソースに接続するために、スイッチが含まれ得る。幾つかの実施形態のこの更なる態様は、D C D C コンバータの始動の間、補償された基準信号の、正確な値への迅速な遷移を促進し得る。

## 【0006】

カウンタの一方または両方が、幾つかの実施形態において、保留制御入力信号を受信するため、ならびに、第1のモードにおいて、対応するクロックおよびアップ / ダウンカウント入力に従ってそれらのそれぞれのカウンタ出力を選択的に更新するように、および、第2のモードにおいて、それらのそれぞれのカウンタビット出力の更新を控えるように機能するために、入力を含み得る。このような実施形態は、過電流制限状況、過電圧状況など、フィードバックが不正確であると知られるかまたは考えられる状況において、積算値をフリーズまたは保留するために有利に用いられ得る。

20

## 【0007】

パルス幅変調 (P W M) コントローラ実施形態が、本開示の更なる態様に従って提供される。P W Mコントローラ実施形態は、マルチビットデジタル入力および基準電圧に少なくとも部分的に従って、補償された基準信号を提供する基準補償回路、ならびに、フィードバック電圧および補償された基準信号に基づいて電力コンバータ出力電圧を制御するためのループ比較器回路、ならびに、デジタル積分器回路を含む。デジタル積分器回路は、基準電圧信号がフィードバック電圧信号よりも大きいかどうかを示すバイナリ比較器出力信号を提供する比較器回路と、第1および第2のカウンタ及び論理回路を備えるデュアルカウンタ回路とを含む。第1のカウンタは、コンパレータ出力信号および積分器クロック入力信号を受信し、マルチビットの第1のカウンタ値を提供し、第2のカウンタは、マルチビットのデジタル入力を基準補償回路に提供する。論理回路は、第1のカウンタ値が所定の値を示すことに基づいて第2のカウンタを初期にインクリメントまたはデクリメントし、その後、第1のカウンタ値が所定のマルチビットカウント範囲にわたってインクリメントまたはデクリメントすることに応答して、第2のカウンタを選択的にインクリメントまたはデクリメントする。

30

## 【0008】

40

幾つかの実施形態における所定のマルチビットカウント範囲は、第1のカウンタの全範囲である。また、幾つかの実施形態において、第1のスイッチが提供され、第1のスイッチは、制御入力に従って、第1の状態において第2のクロック入力を論理回路に接続するように、および、第2の状態において第2のクロック入力を積分器クロック入力信号に接続するように作用し、また、第2のスイッチが提供され、第2のスイッチは、制御入力に従って、第1の状態において第2のアップ / ダウンカウント入力を論理回路に接続するように、および、第2の状態において第2のアップ / ダウンカウント入力をコンパレータ出力に接続するように作用する。幾つかの実施形態における第2のカウンタは、基準補償回路に提供されるデジタル入力をフリーズするための保留制御入力を含む。また、幾つかの実施形態は、過電流制限状況が検出されるとき、基準補償回路に提供されるマルチビット

50

デジタル入力をフリーズするために、第2のカウンタの保留制御入力に保留信号を選択的に提供するように作用する、過電流制限回路を含む。幾つかの実施形態における基準補償回路は、マルチビットデジタル入力および基準電圧に少なくとも部分的に従って、補償された基準信号を提供するため、マルチビットデジタル入力に従って動作されるスイッチを備える、スイッチングされる抵抗ディバイダ回路を含む。

【0009】

基準電圧信号とフィードバック電圧信号との間の誤差を積分するために、本開示の更なる態様に従ってデジタル積分器回路が提供される。デジタル積分器は、基準電圧信号がフィードバック電圧信号よりも大きいかどうかを示すバイナリ比較器出力信号を提供する出力を備える比較器回路、第1および第2のカウンタ、ならびに、論理回路を含む。第1のカウンタは、積分器回路クロックソースに結合される第1のクロック入力と、コンパレータ出力信号を受信するために結合される第1のアップ/ダウンカウント入力と、マルチビットの第1のカウンタ出力値を示す信号を提供する複数の第1のカウンタビット出力を含む。第2のカウンタは、第2のクロック入力と、第2のアップ/ダウンカウント入力と、マルチビットの第2のカウンタ出力値を示す信号を提供する複数の第2のカウンタビット出力と、第2のカウンタビット出力をフリーズするための保留制御入力を含む。論理回路は、第1のカウンタビット出力が初期に所定の値を示すことに応答して第2のカウンタを初期にインクリメントまたはデクリメントするように作用する。その後、論理回路は、第1のカウンタビット出力が第1のカウンタの全値範囲にわたって一方向に遷移した後、第1のカウンタビット出力が再び所定の値を示すことのみに応答して、第2のカウンタをインクリメントまたはデクリメントする。幾つかの実施形態におけるデジタル積分器は、制御入力に従って、第2のカウンタのクロック入力を論理回路に接続するように第1の状態において、および、第2のカウンタの第2のクロック入力を積分器回路クロックソースに接続するように第2の状態において作用する第1のスイッチと、制御入力に従って、第2のアップ/ダウンカウント入力を論理回路に接続するように第1の状態において、および、第2のアップ/ダウンカウント入力をコンパレータ出力に接続するように第2の状態において作用する第2のスイッチとを含む。

【図面の簡単な説明】

【0010】

以下の説明および図面は、本開示の幾つかの例示的な実装を詳細に述べたものであり、本開示の様々な原理が実施され得る幾つかの方法を示す。しかし、例示される例は、本開示の多くの可能な実施形態を網羅するものでない。本開示のその他の目的、利点、および新規の特徴が、図面と共に検討される際に、以下の詳細な説明において述べられる。

【0011】

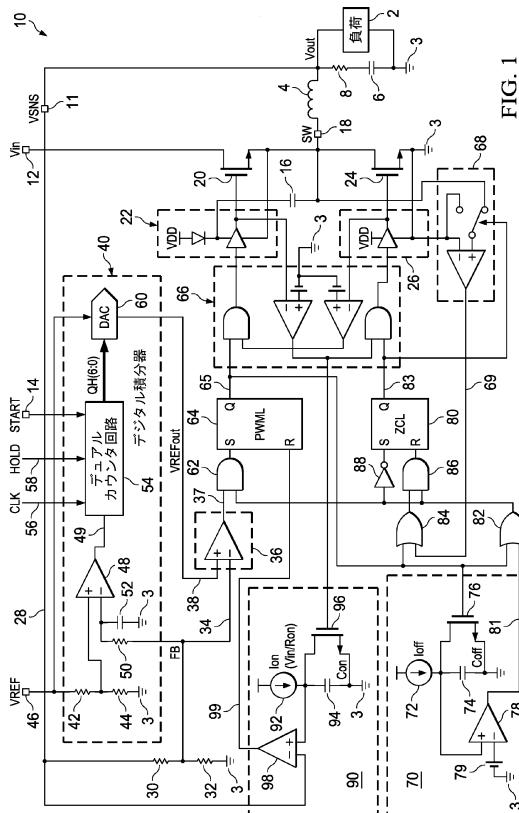

【図1】本開示の一つまたは複数の態様に従った、補償された基準電圧を変調器回路ループコントローラに提供するデュアルカウンタデジタル積分器回路を備えるDC-DCコンバータを図示する概略図である。

【0012】

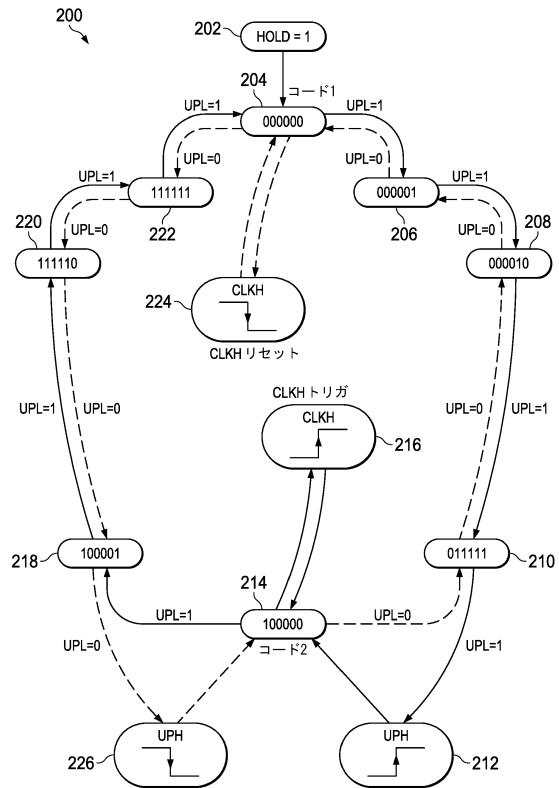

【図2】デジタル積分器におけるデュアルカウンタ回路の更なる詳細を図示する概略図である。

【0013】

【図3】デジタル積分器における論理回路の動作を図示する状態図である。

【0014】

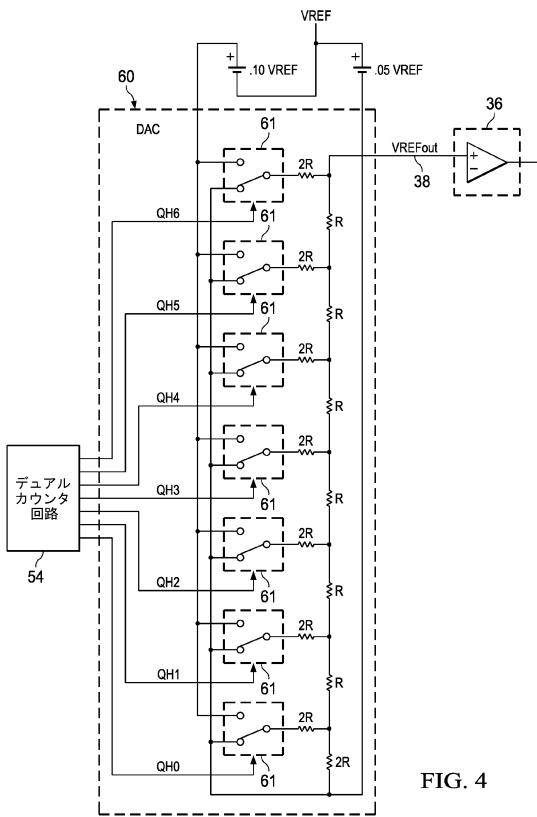

【図4】デジタル積分器におけるスイッチングされる抵抗ディバイダデジタル-アナログコンバータを図示する概略図である。

【0015】

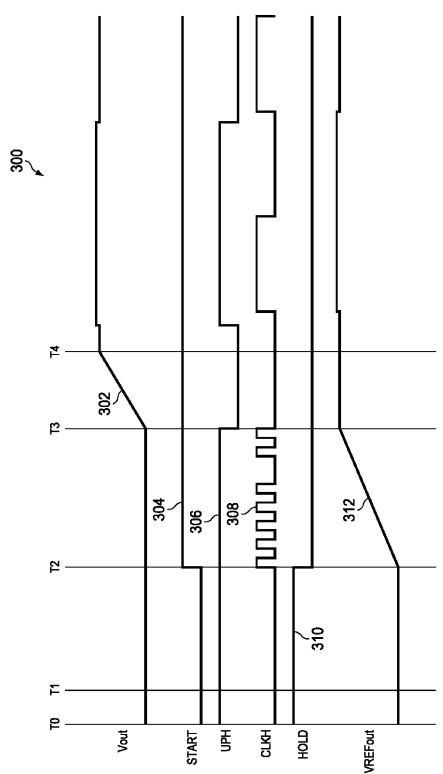

【図5】図1のDC-DCコンバータにおける種々の信号波形を図示する波形図である。

【0016】

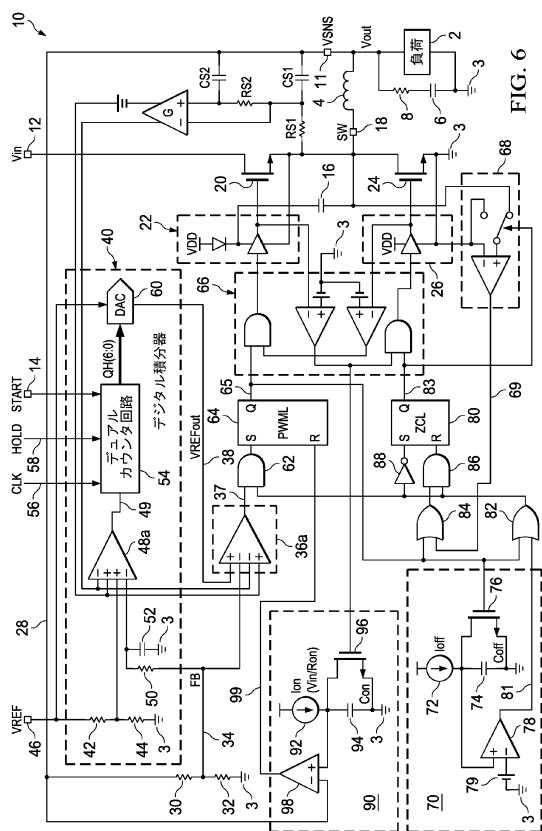

【図6】本開示の一つまたは複数の態様に従った、補償された基準電圧を変調器回路ループコントローラに提供するデュアルカウンタデジタル積分器回路を備える、別のDC-D

10

20

30

40

50

Cコンバータを図示する概略図である。

【0017】

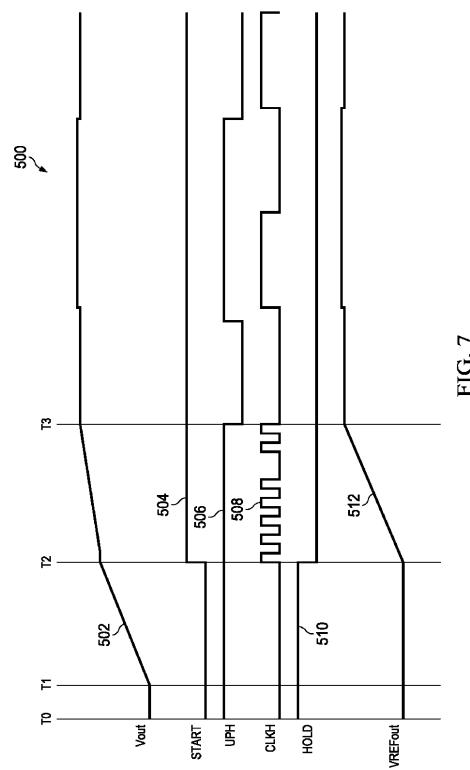

【図7】図6のDC-DCコンバータにおける種々の信号波形を図示する波形図である。

【発明を実施するための形態】

【0018】

一つまたは複数の実施形態または実装が、図面と共に以下で説明される。図面において、同様の参照数字は、全体を通して同様の要素を参照するために用いられ、種々の特徴は必ずしも等倍に描かれていない。

【0019】

図1は、コンバータ出力端子および回路接地3の間に接続される関連する負荷2を駆動するように、出力電圧Voutを提供するためのDC-DCコンバータ10を図示し、この非限定的な例におけるコンバータ10は、スイッチングノードSWおよび出力端子の間に接続される出力インダクタ4を備えるバックコンバータである。関連する等価直列抵抗(ESR)8を有する出力コンデンサ6が、出力端子および回路接地3の間に、駆動負荷2と並列に接続される。図示されるDC-DCコンバータ10は、疑似一定周波数で動作する変調器を提供するが、一定周波数または疑似一定周波数動作は、全ての実施形態の厳格な要件ではない。適切な変調器および関連する回路要素の一般動作は、米国特許番号第6,642,696号、第7,652,461号、および、第8,476,887号において説明されており、これらは参考により全般的に本明細書に組み込まれる。図1におけるDC-DCコンバータ10は、入力供給電圧Vinおよび回路接地3の間に接続される上部および下部電界効果トランジスタ(FET)スイッチングデバイス20および24(この例ではNMOS)を含むスイッチング回路を含み、スイッチ20および24は、スイッチングノードSWで互いに接続される。任意の適切なスイッチング回路要素が、少なくとも一つの対応するスイッチング制御信号に従った選択的動作のためにスイッチングノードに接続される少なくとも一つのスイッチを有して用いられ得る。図示される例において、それぞれ、ハイおよびロードライバ回路22および26が、PWMラッチフリップフロップ64(PWML)からの変調された出力信号65に基づいて、それぞれ、スイッチ20および24にスイッチング制御信号を提供し、ラッチ64は、クロスコンダクション制御回路66に入力信号を提供し、クロスコンダクション制御回路66は、負荷2に提供される出力電圧Voutを制御するように、ハイおよびロースイッチングデバイス20および24の相補パルス幅変調動作のためにドライバ22および26に入力を提供する。

【0020】

幾つかの実施形態において、DC-DCコンバータ10のパルス幅変調制御は、PWMコントローラ集積回路(IC)を介して提供される。PWMコントローラ集積回路(IC)は、必ずしもスイッチ20および24を含まなくてもよく、外部出力インダクタ4の接続のため端子18を提供する。電圧感知(VSNS)入力端子11が、DC-DCコンバータ出力電圧Voutを感知するように、感知された電圧ノード28への接続のために提供され得、入力電圧端子12が、図1に概略的に示されるように、入力電圧Vinを受信するために含まれ得る。スイッチングデバイス20および24、ならびに/または、関連するドライバ22および26が、コントローラICの外にあり得、コントローラICが、そのような構成要素を内部変調器回路要素に接続するための適切な端子を含み得る、その他の実施形態が可能である。また、図示される例は、ハイおよびロードライバ22および26ならびに関連するスイッチングデバイス20および24の両方を含むが、或る実装において、ダイオードがスイッチングノードSWおよび回路接地3の間に接続されることによりローサイドスイッチ24および対応するドライバ26は省略され得る。また、図1におけるDC-DCコンバータ10はバックタイプロンバータであるが、本開示の種々の概念は、DC-DCコンバータまたは電圧レギュレータの任意の適切な形態に関して用いられ得、こういった形態には、バックコンバータ、ブーストコンバータ、バックブーストコンバータ、CUKコンバータ等が含まれるが、これらに限定されない。また、図示される実施形態において、外部から制御可能なSTART信号が、対応する端子14を介してコ

10

20

30

40

50

ントローラ I C に提供され得、または、起動制御信号が、種々の実施形態において、コントローラ I C におけるタイマーまたはその他の回路要素（図示せず）を用いて内部に生成され得る。 PWM 制御回路要素は一般に、基準電圧 V R E F に従って出力電圧 V o u t をレギュレートするために通常モードにおいて動作し、基準電圧 V R E F は、図示される実施形態において、 PWM コントローラ I C に基準電圧端子 4 6 を介して提供される外部入力信号である。

【 0 0 2 1 】

PWM ラッチ 6 4 は、ドライバ 2 2、2 6、任意に含まれるクロスコンダクション制御回路 6 6、およびループ比較器 3 6 と共に、 PWM コントローラの一部として変調器回路を形成する。ループ比較器 3 6 は、 AND ゲート 6 2 を介してラッチ 6 4 のセット入力「 S 」にループコンパレータ出力 3 7 を提供して、以下で更に説明されるように、非反転の第 1 のコンパレータ入力 3 4 に接続されるフィードバック信号 ( F B ) に、および、デジタル積分器 4 0 から非反転ループコンパレータ入力 3 8 に提供される補償された基準信号 V R E F o u t に基づいて、コンバータ出力電圧 V o u t をレギュレートする。この場合のフィードバック信号 F B は、ノード 2 8 の出力電圧感知信号 V S N S と回路接地 3 との間に接続される上部および下部レジスタ 3 0 および 3 2 を含む、抵抗ディバイダフィードバック回路によって提供され、ディバイダ 3 0、3 2 のセンターノードは、感知された出力電圧 V o u t の一部として、ループ比較器回路 3 6 およびデジタル積分器 4 0 にフィードバック電圧信号 F B を提供する。

【 0 0 2 2 】

図示される例において、 PWM ラッチ 6 4 の出力 6 5 ( 「 Q 」 ) は、入力として、クロスコンダクション制御回路 6 6 に、また、最小オフ時間タイマー回路 7 0 に、ならびに、 OR ゲート 8 2 および 8 4 に提供される。タイマー回路 7 0 は、正の供給電圧とオフ時間タイマーコンデンサ 7 4 ( C o f f ) の上部端子との間に接続される電流源 7 2 ( I o f f ) を含み、オフ時間タイマーコンデンサ 7 4 ( C o f f ) の下部端子は回路接地に接続され、 NMOS トランジスタ 7 6 が、 PWM ラッチ出力 6 5 を受信し、これに応じてコンデンサ 7 4 の両端の電圧を選択的に短絡 ( 例えは、放電 ) させる。電流源 7 2 およびコンデンサ 7 4 は、その後、比較器 7 8 の非反転入力に立ち上がり電圧信号を提供し、立ち上がり電圧信号は、比較器 7 8 が OR ゲート 8 2 の入力に出力信号を提供するように、基準電圧 7 9 と比較される。 OR ゲート 8 2 の出力は、 PWM ラッチ 6 4 の S 入力を制御するために、第 2 の入力として AND ゲート 6 2 に提供され、これにより、 PWM ラッチ出力信号 6 5 がオフである時間の最小量を制御する。

【 0 0 2 3 】

図 1 に更に示されるように、ゼロ交差比較器回路 6 8 が、スイッチノード S W の電圧を回路接地と比較し、ゼロ交差信号 6 9 を第 2 の入力として OR ゲート 8 4 に提供する。 OR ゲート 8 2 および 8 4 は、 AND ゲート 8 6 に入力を提供し、 AND ゲート 8 6 の出力が、ゼロ交差ラッチ ( Z C L ) 8 0 へのリセット「 R 」入力を制御し、図示されるように、ゼロ交差ラッチ ( Z C L ) 8 0 は、 OR ゲート 8 2 の出力によりインバータ 8 8 を介して駆動されるセット「 S 」入力を有する。また、図示される実施形態において、クロスコンダクション制御回路 6 6 は、オン時間タイマー回路 9 0 を制御する出力信号を提供するため、ドライバ 2 2 の出力を基準電圧と比較し、オン時間タイマー回路 9 0 は、電流源 9 2 ( I o n : これは、或る実装において、入力電圧 V i n 対外部制御レジスタ R o n の比であるように設定される ) 、タイミングコンデンサ 9 4 ( C o n ) 、制御トランジスタ 9 6 、および、比較器 9 8 を含み、比較器 9 8 は、コンデンサ 9 4 両端の立ち上がり電圧を、感知された出力電圧 2 8 と比較し、ドライバ 2 2 および 2 6 に提供される PWM スイッチング信号のオン時間を制御するため、 PWM ラッチのリセット「 R 」入力に出力信号 9 9 を提供する。このように、 PWM 制御回路要素は、負荷 2 に提供される D C D C コンバータ出力電圧 V o u t を制御するため、閉ループ変調器を提供する。

【 0 0 2 4 】

次に図 1 および図 2 を参照すると、ループ比較器 3 6 は、フィードバック電圧信号 F B

10

20

30

40

50

を受信するように接続される第1の入力34、および、補償された基準信号VREFoutをデジタル積分器回路40から受信するように接続される第2のコンパレータ入力38を有する。例えば、ループ比較器オフセット、レジスタディバイダオフセット等、変調器回路要素におけるオフセットを補償するため、積分器40は、基準信号VREFおよびフィードバック信号FBを受信し、補償された基準信号VREFoutをループ比較器36に提供する。デジタル積分器40は、基準入力VREFと回路接地3との間に互いに直列に接続される上部レジスタ42および下部レジスタ44を備える抵抗ディバイダ基準回路を含み、積分器比較器48の非反転入力に積分器基準信号を提供する。比較器48の反転入力は、図示されるように、レジスタ50およびコンデンサ52を含む任意選択のRCフィルタ回路を介してフィードバック信号FBを受信するように結合される。コンパレータ出力49は、基準電圧信号がフィードバック電圧信号FBよりも大きいかどうかを示すバイナリ比較器出力信号を生成する。コンパレータ出力49は、デュアルカウンタ回路54に入力信号として提供され、デュアルカウンタ回路54は、デジタル アナログコンバータ(DAC)60に、7ビットバイナリコードデジタル出力QH(6:0)を提供する。DAC60は、基準電圧VREFおよびデジタルカウンタ出力を受信し、補償された基準電圧VREFoutをループ比較器36の非反転入力38に提供する。

#### 【0025】

図示される実施形態において、デュアルカウンタ回路54はまた、HOLD制御信号58および積分器クロック信号56(CLK)を受信する。任意の適切なクロックソースが、積分器クロック信号56として用いられ得る。例えば、PWMラッチ64を動作させるために用いられるPWMクロックが用いられ得るが、デジタル積分器40を動作させるために別個のクロックソース56を用いる種々の実装が可能である。一つの可能な実施形態において、HOLD信号58は、図2に示すように、過電流制限(OCL)検出回路47から出力として提供され、回路47は、スイッチングノードSWの電圧および出力電圧感知信号VSENSに基づいて、DCDCコンバータ10における過電流状況を検出する。HOLD信号58は、これに限定されないが過電圧状況等を含む、DCDCコンバータ回路10におけるその他の状況に従って、代替的にまたは組み合わせて提供され得る。特に、HOLD信号58は、有利に、デジタル積分器40の値をフリーズさせ、従って、過電流制限において、および/または、感知された出力電圧及びそれゆえフィードバック信号FBが不正確であると考えられるその他の状況において、有用性を提供する。

#### 【0026】

図2で最もよく分かるように、デュアルカウンタ回路54は、第1のカウンタ100(例えば、この例における低ビットカウンタ)を含み、第1のカウンタ100は、積分器回路クロックソースCLKを受信するクロック入力CLKL、および、比較器48から出力信号49を受信するように結合される第1のアップ/ダウンカウント入力UPLを備える。第1のカウンタ100は、6ビット出力QL(5:0)を提供するが、任意のマルチビットの第1のカウンタ100が、マルチビットの第1のカウンタ出力値を示す信号を提供する2またはそれ以上のバイナリ出力を有して用いられ得る。デュアルカウンタ回路54は更に、論理回路102およびマルチビットの第2のカウンタ104(例えば、高ビットカウンタ)を含み、マルチビットの第2のカウンタ104は、第2のクロック入力CLKH、第2のアップ/ダウンカウント入力UPTH、および、補償された基準電圧VREFoutを生成するために7ビットの第2のカウンタ出力値を示す信号をDAC60に提供する、複数の第2のカウンタビット出力QH(6:0)を備える。図示される実施形態において7ビットの第2のカウンタ104が示されているが、第2のカウンタ104が任意の数のビットのマルチビットカウンタ出力を提供する、その他の実施形態が可能である。

#### 【0027】

また、図3を参照すると、一実施形態における論理回路102は、状態機械を含むか、または、状態機械をその他の方式で実装し、状態機械は、第1のカウンタビット出力QL(5:0)が第1のカウンタ100の所定の値100000を初期に示すことに応答して、第2のカウンタ104を初期にインクリメントまたはデクリメントするように動作する

10

20

30

40

50

。任意の適切な所定の値が用いられ得、値 1 0 0 0 0 0 は一つの非限定的な例に過ぎない。また、所定の値（または第 1 および第 2 の所定の値、ならびに、以下で説明される既定の範囲）は、幾つかの実施形態においてプログラム可能とし得る。この点で、論理回路 102 は、同期回路、フリップフロップ、論理ゲート、レジスタ等、またはそれらの組合せを含む、任意の適切な固定またはプログラム可能な論理回路要素であり得る。論理回路 102 は、第 1 の（低ビット）カウンタ 100 からカウンタ出力を受信するように結合される複数の入力、ならびに、第 2 のクロック入力 C L K H と（例えば、直接的に、または、図 2 に示されるようにスイッチ 106 を介して）結合される第 1 の論理出力（C L K H）、および、第 2 のアップ / ダウンカウント入力 U P H と（例えば、直接的に、または、スイッチ 108 を介して）結合される第 2 の論理出力を有する。以下で更に説明されるように、スイッチ 106 および 108 は、図示されるデュアルカウンタ回路実施形態 54 において、S T A R T 信号 14 に従って通常モードおよび「起動」モードでの選択的動作のために、クロックおよびアップ / ダウンカウンタ入力の、第 2 のカウンタ 104 への接続を選択的に制御するように提供される。

10

#### 【0028】

第 2 のカウンタクロック入力 C L K H がスイッチ 106 を介して論理回路 102 の第 1 の論理出力に接続され、U P H カウンタ入力がスイッチ 108 を介して第 2 の論理出力に接続される通常動作において、且つ、高ビットカウンタ 104 の第 1 の更新の後、第 1 のカウンタビット出力 Q L (5 : 0) が所定の値範囲にわたってアップまたはダウンのいずれかに一方向に遷移した後、第 1 のカウンタビット出力 Q L (5 : 0) が再び所定の値 100000 を示すことに応答して、論理回路 102 は、第 2 のカウンタ 104 を選択的にインクリメントまたはデクリメントする。図示される実施形態において、所定のマルチビットカウンタ範囲は第 1 のカウンタ 100 の全範囲であるが、論理回路 102 は、第 1 のカウンタ 100 の 2 つまたはそれ以上のカウント（アップまたはダウン）を表す任意の所定の範囲を実装するように構成され得る。また、或る実装において、すべての実施形態の厳格な要件ではないが、第 1 のカウンタ 100 が、方向を変えることなく所定の値範囲にわたって一方向の連続的遷移をすることに応答して、論理回路 102 は、第 2 のカウンタ 104 を選択的にインクリメントまたはデクリメントするように作用する。

20

#### 【0029】

図 3 は、論理回路 102 の一実施形態の動作を示す状態図 200 を図示し、アクティブロー - H O L D 信号が、202 に置かれており、また 202 でアクティブ「1」状態である。H O L D 信号 58 が通常動作を開始するためにいったんローになると、論理回路 102 は、初期の第 1 のカウンタ値または状態 204 で、第 1 のカウンタ値またはコード 00000000 (図 3 における C O D E 1) で開始する。第 1 のカウンタ値がこの第 1 の所定の値 00000000 に達する際、論理回路 102 は、スイッチ 106 を介する第 2 のカウンタ 104 へのクロック入力をリセットするために、状態 224 で、第 1 の論理出力 (C L K H) を、第 1 のバイナリクロック入力状態 (L O W) に設定する。初期状態 204 から、第 1 のカウンタ 100 は、低ビットクロック C L K L の各アクティブエッジでカウントアップまたはカウントダウンするために、クロック入力 56 および積分器回路比較器 48 からのアップ / ダウン入力 49 に従って動作し、第 1 のカウンタ 100 は、U P L = 1 では、指定されたクロックエッジでインクリメントまたはカウントアップし（図面では時計回り）、および、U P L = 0 では、デクリメントまたはカウントダウン（反時計回り）する。

30

40

#### 【0030】

初期状態 204 からのアップカウントにより入力される第 1 の状態 206 (000001)、次の上方値または状態 208 (000100) を含め、多くの可能な第 1 のカウンタ値または状態のほんのいくつかが図 3 に図示されており、連続的なインクリメントは状態 210 (011111) に至る。この場合、第 1 のカウンタビット出力 Q L (5 : 0) が第 2 の所定の値 100000 まで上方に遷移することに応答して、論理回路 102 が、状態 212 で、第 2 の論理出力 (U P H) を第 2 のバイナリカウンタ状態 (H I G H) に設定することにより、第 1 のカウンタ 100 (U P L = 1) のそれに続く上方カウントが、

50

論理回路 102 を、状態 212 を介して第 2 の所定の値または状態 214 (カウント値が 100000 である、図 3 における CODE2) に遷移させる。また、この上方カウントの例における論理回路は、第 1 のカウンタ 100 が第 2 の所定の値 100000 までカウントすることに応答して、第 2 のカウンタ 104 のクロック入力をトリガするために、第 1 の論理出力 (CLKH) を、第 2 のバイナリクロック入力状態 (HIGH) 216 に設定する。

### 【0031】

図示されるデジタル積分器 40 において、第 1 のカウンタ 100 のこの上方カウント、及びその後に続く、第 1 のカウンタが所定のカウント値 100000 に達することに応答した第 2 のカウンタ 104 の選択的なトリガが、第 2 のカウンタ 104 をインクリメントし、それゆえ、DAC60 に提供されるカウント値 QH (6:0) をインクリメントし、これにより、補償された基準電圧 VREFout が上昇する。次に、ループ比較器 36 の閉ループ動作が、VREFout をフィードバック信号 FB と比較し、これに従って PWM 制御回路要素の変調を改変し、これにより、DCDC コンバータ出力電圧 Vout が上昇し、入力としてデジタル積分器 40 に提供されるフィードバック信号 FB の上昇がもたらされる。この補償された基準電圧およびコンバータ出力調整の結果は、積分器比較器 48 からのコンバーティ出力 49 を変化させても、変化させなくてもよい。変化させない場合、第 1 のカウンタ 100 は、状態 214 から状態 218 へ上方 (図 3 において時計回り) にカウントし続け、この上方カウント (UPL = 1) が、図示される状態 220 および 222 を介して継続し得、カウンタ 100 は、場合によって、状態 204 で第 1 の所定の値 000000 に再び達し得る。この場合、論理回路 102 は、状態 224 で第 2 のカウンタクロック CLKH をリセットするために、第 1 の論理出力を再びローに設定し、論理回路 102 は、第 1 のカウンタ 100 の任意の更なる上方カウントのために上述の動作を継続する。

### 【0032】

積分器比較器 48 による、基準信号と調整されたフィードバック信号との相対的な比較がコンバーティ出力 49 の状態を変化させる場合、第 1 のカウンタ 100 は、代わりに、下方へカウントし (UPL = 0)、このような下方カウントは、図 3 の状態図 200 において反時計回りの方向で発生する。この場合、状態 218 (第 1 のカウンタ値 100001) から第 2 の所定の値 100000 への下方遷移が、論理回路 102 に、状態 226 で、スイッチ 108 を介して第 2 のカウンタ 104 の UPH 入力へ提供されるアップ/ダウン信号 (LOW) を変化させ、また、カウンタ 100 が状態 214 で下方方向に 100000 値に達することに応答して、論理回路 102 に、状態 216 (ハイに向かうパルスエッジ) で、スイッチ 106 を介して第 2 のカウンタ 104 のクロック入力 CLKH を再びトリガさせ、これにより、第 2 のカウンタ 104 のカウント値をデクリメントする。この例における下方方向の更なるカウントが、状態図 200 を、状態 210、208、および 206 を介して後方に遷移させ、場合によって、204 での第 1 の所定の値 000000 に再び達し、第 1 のカウンタ 100 の下方カウント動作が、上述したような論理回路動作となる。それゆえ、第 2 のカウンタは、所定のカウント範囲 (例えば、この例において全範囲) にわたる一方 (または他方) の第 1 のカウンタ 100 のカウント動作に応答して、通常モード動作において選択的にインクリメントまたはデクリメントされる。

### 【0033】

この動作により、論理回路 102 は、第 2 の (高ビット) カウンタ 104 のインクリメントまたはデクリメントを選択的に制御し、このことが、DAC60 により提供されるカウント値の調整を制御する。このように、デュアルカウンタ回路 54 は、デジタル積分器 40 の応答時間を減少または減速させ、これにより、DCDC コンバータ 10 における安定した動作を促進し、一方で、従来のアナログ積分器回路要素と比較して、デジタル積分器の利点 (例えば、削減された集積回路ダイスペース、削減された電力消費、デジタル積分器値保持等) を促進する。この点で、第 1 のカウンタ 100 が、この場合では第 1 のカウンタ 100 の全範囲である既定のカウント範囲にわたって遷移するまで、第 2 のカウント値が 100000 である、図 3 における CODE2) に遷移させる。

10

20

30

40

50

ンタ 104 の出力は変化されないので、補償された基準電圧  $V_{REFout}$  は安定する。例えば、第 2 のカウンタ 104 の応答を設定するために、第 1 のカウンタ 100 のカウント値の異なる既定の範囲を実装することにより、論理回路 102 のその他の実施形態が、デジタル積分器 40 のための異なる応答時定数を提供するように実装され得る。

#### 【0034】

また、カウント値の既定の範囲が第 1 のカウンタ 100 において継続的に達成される場合に限り第 2 のカウンタ 104 がインクリメントまたはデクリメントされる、論理回路 102 の幾つかの実装が可能である。この点で、このような実施形態は、第 1 のカウンタ 100 が、カウント値の所定の範囲にわたって（如何なる下方カウントもなく）上方に継続的にカウントした後にのみ、第 2 のカウンタ 104 をインクリメントし得、また、第 1 のカウンタ 100 が、所定の範囲にわたって（如何なる上方カウントもなく）下方に継続的にカウントした後にのみ、第 2 のカウンタ 104 をデクリメントし得る。また、幾つかの実施形態において、異なる既定の範囲が上方カウントおよび下方カウントに対して実装され得るが、図示される実施形態のような両方向にカウントするために単一の範囲が用いられてもよい。また、論理回路 102 は、既定の値範囲の選択的な調整のために、（例えば、外部通信を通じて、または PWM コントローラ集積回路の入力ピンを介して等）構築可能またはプログラム可能であり得、これにより、デジタル積分器 40 の応答性の動的な調整を可能にし、または、異なる最終用途において単一の PWM コントローラ集積回路製品を適応または構築することが可能となる。

#### 【0035】

開示されるデジタル積分器 40 の概念は、このように、アナログ積分器アプローチと比較して、削減された集積回路ダイサイズおよび電力消費を有利に促進し、外部積分器コンデンサの必要性をなくす。加えて、積分器 40 におけるデュアルカウンタ回路要素 54 の使用が、従来のアナログ積分器アプローチにおいて見られるループ安定性問題を軽減または防止し、一方で、ループ補償器オフセット等を含め、変調器回路におけるオフセットに関して、閉ループ DC-DC コンバータ制御を補償する。

#### 【0036】

図 4 は、幾つかの実施形態において用いられ得る抵抗ディバイダ DAC 回路 60 を図示する。この実施形態における DAC 60 は 7 個のスイッチ 61 を含み、スイッチ 61 は、対応するレジスタ分岐を、基準電圧  $V_{REF}$  にまたは回路接地 3 に選択的に接続するため、第 2 のカウンタ 104 のバイナリ出力 ( $QH(6:0)$ ) の対応する一つに従って個別に作用する。任意の適切な抵抗値  $R$  および  $2R$  が用いられ得、図示される例はバイナリ重み付けを提供するものであり、幾つかの実施形態は更に、信号安定性および補償された基準電圧  $V_{REFout}$  を促進するために、非反転ループコンバータ入力 38 と回路接地 3 との間に接続される、静電容量（図示せず）を含み得る。図示される例は、7 ビット  $R-2R$  ラダー回路であり、バイナリ重み付けによりループ比較器 36 に提供される補償された基準電圧  $V_{REFout}$  のために  $2^7$  のあり得るアナログ電圧レベルが提供される。また、図示されるスイッチングされる抵抗ディバイダ回路 DAC 60 は一つの可能な実施形態に過ぎず、第 2 のカウンタ 104 からのカウンタ出力 ( $QH(6:0)$ ) および基準電圧  $V_{REF}$  に少なくとも部分的に基づいて、補償された基準電圧  $V_{REFout}$  を提供するように動作する、任意の適切な形態のデジタル アナログコンバータ 60 が用いられ得る。

#### 【0037】

図 2 に更に示されるように、デジタル積分器 40 は更に、起動の間、および / または、デジタル積分器 40 を迅速に応答させ得ることが望ましいその他の状況の間の迅速な動的応答のために、スイッチ 106 および 108 を提供する。第 1 のスイッチ 106 は、端子 14 で受信される START 信号に従って、第 2 のカウンタ 104 の第 2 のクロック入力 CLKH を論理回路 102 の第 1 の論理出力に接続するように第 1 の状態（通常動作）において、および、第 2 のカウンタ 104 の第 2 のクロック入力 CLKH を積分器回路クロックソース 56 (CLK) に接続するように (START 信号がアクティベートされる)

10

20

30

40

50

第2の状態において動作する。また、第2のスイッチ108は、第2のカウンタ104の第2のアップ/ダウンカウント入力UPHを、論理回路102の第2の論理出力に接続するように通常モードにおいて、および、第2のカウンタ104の第2のアップ/ダウンカウント入力UPHをコンパレータ出力49に接続するように(START信号がアクティブである)起動モードにおいて動作する。それゆえ、START信号がアクティベートされるとき、第2のカウンタ104は、DAC60を制御するため、7ビット出力QH(6、0)を提供する単一の7ビットバイナリカウンタとして動作し、これにより、抵抗ディバイダ42、44からの基準信号と、積分器比較器48を介するフィードバック信号FBとの間の大きな差に迅速に応答する。START信号は、図示されるように、外部ソースから端子14を介して提供され得、または、種々の実施形態において、(例えば、PWM制御回路要素の起動の際の動作のため、および/または、その他の検出された動作状況等に基づいて)内部で生成され得、または、それらの組合せであり得る。

10

### 【0038】

図1および図2を再び参照すると、カウンタ100および104の一方または両方がHOLD入力を含み得、外部ソースから、および/または、図2に示されるOCL検出回路47などの内部ソースから、保留制御入力信号58を提供され得る。HOLD入力が、対応するクロック入力CLKL、CLKH、および対応するアップ/ダウンカウント入力UPL、UPHに従って、それらのそれぞれのカウンタビット出力を選択的に更新するためにアクティベートされない場合、図示される例におけるカウンタ100および104は、通常または起動モードにおいて上述したように動作する。HOLD信号がアクティベートされる場合(例えば、一例においてアクティブハイ)、カウンタ100および104は、それらのそれぞれのカウンタビット出力を更新するのを控える(それらは、カウントアップまたはカウントダウンしない)。幾つかの動作状況において、特に、感知される出力電圧およびそれゆえフィードバック信号FBが不正確であることが分かっているかまたは想定される場合、デジタル積分器40の値を本質的に保持または「フリーズ」するこの能力は、PWMコントローラの閉ループ動作における不正確さまたは不安定性を防止または軽減する。例えば、CCMおよびDCM動作間の遷移、(例えば、図2におけるOCL検出回路47により検出される)過電圧状況または過電流制限状況の間、HOLD信号58の作動は、第2のカウンタ104の出力値をフリーズすることによってデジタル積分器40の積分動作を中断し得、これにより、DAC60による補償された基準信号VREFoutの不正確な調整を潜在的に防止し、また、HOLD信号58のディアクティベーションの際のセーブまたはフリーズされたカウンタ値を用いる後続の再開が可能となる。その結果、カウンタ100および104の一方もしくは両方(または少なくとも第2のカウンタ104)の出力値を保持またはフリーズする能力が、システム安定性を向上させる。また、デジタル積分器40を用いることで、アナログ積分器コンデンサの電圧がリークを受けるアナログ積分器回路要素と比較して、より正確な積分器値保持が可能となり、これにより、積分器値は徐々に失われる。通常動作の再開の際、図示される実施形態におけるHOLD信号58は、デジタル積分器40が、積分器出力情報を失うことなく、以前の状態から動作を再開することによって停止され得る。

20

30

40

### 【0039】

図5は、デジタル積分器140が初期化されるまでシステムソフトスタートが遅延される、図1のDCDCコンバータ10の一実施形態の動作における種々の信号波形を図示するグラフ300を提供する。この例において、出力電圧Vout(図5における曲線302)は、時間T1に0Vで始まり、START信号14(曲線304)は初期にアクティブ(ロー)であり、HOLD信号58(図5における曲線310)は初期にアクティブ(ハイ)である。HOLD信号がアクティブである論理回路102の動作において、第2の論理出力(UPH、グラフ306)はハイのままであり、クロックパルス(CLKH)は、START信号14がアクティブである第1の論理出力により第2のクロック104に印加されない。所定の時間の後、または外部制御下で、HOLDおよびSTART信号は、時間T2辺りでディアクティベートされ、第2のカウンタ104(曲線308)が、

50

クロックパルスを受信するために開始し、一方で、対応するアップ／ダウンカウント入力（U P H）信号が、コンパレータ出力 4 9 によりスイッチ 1 0 8 を介してハイに駆動される。このことが、第 2 のカウンタ 1 0 4 のカウンタ出力の上昇をもたらし、これにより、T 2 から T 3 へのデジタル積分器初期化の間、D A C 6 0 の動作を介する補償された基準電圧 V R E F o u t (曲線 3 1 2) が増大される。フィードバック値 F B が、比較器 4 8 により、積分器基準電圧を超えると判定されると、システムソフトスタートが T 3 で開始し、出力電圧 3 0 2 が T 3 から T 4 へランプアップし、時間 T 4 の後の曲線 3 0 6 および 3 0 8 に見られるように、デジタル積分器 4 0 が第 2 のカウンタ 1 0 4 をゆっくりとインクリメントまたはデクリメントする。

## 【0040】

10

それゆえ、図 5 のグラフ 3 0 0 に示すように、補償された基準電圧 V R E F o u t の曲線 3 1 2 は、T 3 の後概して安定しており、デュアルカウンタ回路 5 4 のように相対的にのみ稀に変化し、論理回路 1 0 2 の動作は、P W M 制御変調器回路要素の動作においてループ比較器 3 6 により用いられる補償された基準電圧における過度のジッタを防止または軽減するようにデジタル積分器 4 0 の時定数を効果的に制御する。また、図示される実施形態は、トランジエントの間積分器動作を保持またはフリーズする機能により、定常状態動作の間の安定したループ応答に加えて迅速な初期化も提供する。それゆえ、開示されるデジタル積分器概念は、正確さおよび D C D C 変換の改善のため、また、外部積分器コンデンサの除去に伴う削減された電力消費および集積回路ダイサイズ、ならびに、アナログ積分器設計と比較して改善された安定性および積分器値保持のため、回路オフセットを補償する機能を提供する。

## 【0041】

20

上述したようなデジタル積分器 1 4 0 および変調器を含む D C D C コンバータ 1 0 の別の実施形態が図 6 に示されており、この実施形態において、ループ比較器 3 6 a および積分器比較器 4 8 a に電流ランプ情報を提供するため、電流フィードバックが、レジスタ R S 1 および R S 2 ならびにコンデンサ C S 1 および C S 2 を介し、相互コンダクタンス増幅器 G を介して提供される。この実施形態において、ループ比較器 3 6 a は、基準ディバイダ 4 2 、 4 4 からの信号および R C 回路 5 0 、 5 2 からのフィードバックを受信する第 1 の入力差動対と、相互コンダクタンス増幅器 G からの差動出力を受信する第 2 の入力差動対とを含み、電流情報が、補償された基準信号 V R E F o u t との比較のためにフィードバックに追加される。また、積分器比較器 4 8 a は、第 1 および第 2 の差動対入力を有し、第 1 の差動入力対は、F B 信号および D A C 6 0 から補償された基準信号 V R E F o u t を受信し、第 2 の差動入力対は、相互コンダクタンス増幅器 G から差動出力を受信する。この実施形態において、比較器 3 6 a および 4 8 a に追加された入力は、ループ安定性の向上のために電流ランプ情報を提供する。また、D A C 6 0 の調整範囲は、好みくは、メインループ比較器 3 6 a におけるオフセット、電流ランプ信号 D C 誤差、リップル誤差の半分、および任意のディバイダ比誤差、の補償を可能にするように設定される。

30

## 【0042】

図 7 は、ソフトスタートが終わった後にデジタル積分器 1 4 0 が開始される、図 6 の D C D C コンバータ 1 0 の実施形態の動作における種々の信号波形を図示するグラフ 5 0 0 を示す。システム 1 0 が起動を終えるとき電流ランプ信号が有効であるため、一実施形態において、デジタル積分器 1 4 0 は、ソフトスタートが終わった後（但し、V o u t は負荷に備えている）開始され得る。この例において、出力電圧 V o u t (図 7 における曲線 5 0 2) は、時間 T 1 に 0 V で開始し、T 1 から T 2 へのシステムソフトスタート期間の間ランプアップし、一方で、S T A R T 信号 1 4 (曲線 5 0 4) は、初期にアクティブ（ロー）であり、H O L D 信号 5 8 (図 7 における曲線 5 1 0) は、初期にアクティブ（ハイ）である。H O L D 信号がアクティブである論理回路 1 0 2 の動作において、第 2 の論理出力（U P H、グラフ 5 0 6）はハイのままであり、クロックパルス（C L K H）は、S T A R T 信号 1 4 がアクティブである第 1 の論理出力により第 2 のクロック 1 0 4 に印加されない。所定の時間の後、または外部制御下で、H O L D および S T A R T 信号は

40

50

、時間  $T_2$  辺りでディアクティベートされ、第2のカウンタ104(曲線508)は、クロックパルスを受信するために開始し、一方で、対応するアップ/ダウンカウント入力(UPH)信号は、 $T_2$ から $T_3$ へのデジタル積分器40の初期化の間、コンパレータ出力49によりスイッチ108を介してハイに駆動される。このことが、第2のカウンタ104のカウンタ出力の増加をもたらし、これにより、出力電圧曲線502のランプされた増加と共に、DAC60の動作を介する補償された基準電圧VREFout(曲線512)が増大される。比較器48が、フィードバック値FBが積分器基準電圧を超えると判定すると、デジタル積分器40は、時間 $T_3$ の後の曲線506および508に見られるように、第2のカウンタ104をゆっくりとインクリメントまたはデクリメントする。それゆえ、図7のグラフ500に示されるように、補償された基準電圧VREFout曲線512は、時間 $T_3$ の後概して安定しており、デュアルカウンタ回路54のように相対的にのみ稀に変化し、論理回路102の動作は、デジタル積分器40の時定数を効果的に制御する。

## 【0043】

上記の例は、本開示の種々の態様の幾つかの可能な実施形態を説明するものに過ぎず、同等の変更および/または改変が、本明細書および添付の図面を読んで理解すれば当業者に見いだされる。また、本開示の特定の特徴が、複数の実装の一つのみに関して開示されてきたが、このような特徴は、所望され得るように、また、任意の所与または特定の用途に有利であり得るように、その他の実施形態の一つまたは複数の他の特徴と組み合わされてもよい。また、「含む(including)、(includes)」、「有する(having)、(has)」、「備える(with)」という用語またはそれらの変形が、詳細な説明および/または特許請求の範囲において用いられる限り、このような用語は、「含む(comprising)」という用語と同様に包括的であることが意図される。

【図1】

【 図 3 】

FIG. 3

【 図 4 】

FIG. 4

【 図 5 】

FIG. 5

【 四 6 】

【図7】

FIG. 7

---

フロントページの続き

(72)発明者 立石 哲夫

日本国 458-0805 愛知県名古屋市緑区大清水5-1402

(72)発明者 シュエンイン リー

中華人民共和国 523808 広東省 ドングアン, ソンシャン レイク ハイテク インダストリアル ディベロブメント ゾーン, ナンバー17 ヘッドカウンター ロード 2, エレクトロニック インスティテュート, ルーム エイ506

審査官 小林 秀和

(56)参考文献 米国特許出願公開第2007/0001715(US, A1)

米国特許第07141956(US, B2)

特開2005-210845(JP, A)

米国特許出願公開第2006/0119340(US, A1)

特表2008-522564(JP, A)

米国特許出願公開第2010/0001702(US, A1)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155