**【特許請求の範囲】****【請求項 1】**

基板上に第1の導電膜と第2の導電膜を形成し、

前記第1の導電膜上と前記第2の導電膜上に第1の絶縁膜を形成し、

前記第1の導電膜上に前記第1の絶縁膜を介して電荷蓄積層を選択的に形成し、

前記第1の絶縁膜上と前記電荷蓄積層上に第2の絶縁膜を形成し、

前記第2の絶縁膜上に、前記第1の導電膜と重なる第1の半導体膜と、前記第2の導電膜と重なる第2の半導体膜と、前記第1の導電膜及び前記第2の導電膜と重ならない第3の半導体膜を形成し、

前記第1の半導体膜、前記第2の半導体膜及び前記第3の半導体膜上に第3の絶縁膜を形成し、

10

前記第3の半導体膜の上方に前記第3の絶縁膜を介して第3の導電膜を形成することを特徴とする半導体装置の作製方法。

**【請求項 2】**

基板上に第1の導電膜と第2の導電膜を形成し、

前記第1の導電膜上と前記第2の導電膜上に第1の絶縁膜を形成し、

前記第1の導電膜上に前記第1の絶縁膜を介して電荷蓄積層を選択的に形成し、

前記第1の絶縁膜上と前記電荷蓄積層上に第2の絶縁膜を形成し、

前記第2の絶縁膜上に、前記第1の導電膜と重なる第1の半導体膜と、前記第2の導電膜と重なる第2の半導体膜と、前記第1の導電膜及び前記第2の導電膜と重ならない第3の半導体膜を形成し、

20

前記第1の半導体膜、前記第2の半導体膜及び前記第3の半導体膜上に第3の絶縁膜を形成し、

前記第3の絶縁膜上に、前記第3の半導体膜と重なる第3の導電膜と、前記第1の半導体膜と重なる第4の導電膜と、前記第2の半導体膜と重なる第5の導電膜を形成することを特徴とする半導体装置の作製方法。

**【請求項 3】**

請求項1又は請求項2において、

前記第2の絶縁膜及び前記第3の絶縁膜を、前記第1の絶縁膜の膜厚より薄く形成することを特徴とする半導体装置の作製方法。

30

**【請求項 4】**

基板上に第1の導電膜と第2の導電膜を形成し、

前記第1の導電膜上と前記第2の導電膜上に第1の絶縁膜を形成し、

前記第1の導電膜上に形成された前記第1の絶縁膜を除去し、

前記第1の導電膜上と前記第1の絶縁膜上に第2の絶縁膜を形成し、

前記第1の導電膜上に前記第2の絶縁膜を介して電荷蓄積層を選択的に形成し、

前記電荷蓄積層上にトンネル絶縁膜を選択的に形成し、

前記トンネル絶縁膜上に前記第1の導電膜と重なる第1の半導体膜を形成し、

前記第2の絶縁膜上に、前記第2の導電膜と重なる第2の半導体膜と、前記第1の導電膜及び前記第2の導電膜と重ならない第3の半導体膜を形成し、

40

前記第1の半導体膜、前記第2の半導体膜及び前記第3の半導体膜上に第3の絶縁膜を形成し、

前記第3の半導体膜の上方に前記第3の絶縁膜を介して第3の導電膜を形成することを特徴とする半導体装置の作製方法。

**【請求項 5】**

基板上に第1の導電膜と第2の導電膜を形成し、

前記第1の導電膜上と前記第2の導電膜上に第1の絶縁膜を形成し、

前記第1の導電膜上に形成された前記第1の絶縁膜を除去し、

前記第1の導電膜上と前記第1の絶縁膜上に第2の絶縁膜を形成し、

前記第1の導電膜上に前記第2の絶縁膜を介して電荷蓄積層を選択的に形成し、

50

前記電荷蓄積層上にトンネル絶縁膜を選択的に形成し、

前記トンネル絶縁膜上に前記第1の導電膜と重なる第1の半導体膜を形成し、

前記第2の絶縁膜上に、前記第2の導電膜と重なる第2の半導体膜と、前記第1の導電膜及び前記第2の導電膜と重ならない第3の半導体膜を形成し、

前記第1の半導体膜、前記第2の半導体膜及び前記第3の半導体膜上に第3の絶縁膜を形成し、

前記第3の絶縁膜上に、前記第3の半導体膜と重なる第3の導電膜と、前記第1の半導体膜と重なる第4の導電膜と、前記第2の半導体膜と重なる第5の導電膜を形成することを特徴とする半導体装置の作製方法。

## 【請求項6】

10

請求項4又は請求項5において、

前記トンネル絶縁膜は、プラズマ処理により前記電荷蓄積層を酸化して形成することを特徴とする半導体装置の作製方法。

## 【請求項7】

請求項4乃至請求項6のいずれか一項において、

前記第2の絶縁膜、前記第3の絶縁膜及び前記トンネル絶縁膜を、前記第1の絶縁膜の膜厚より薄く形成することを特徴とする半導体装置の作製方法。

## 【請求項8】

20

請求項1乃至請求項3のいずれか一項において、

前記電荷蓄積層として、タンゲステン、タンタル、チタン、モリブデン、クロム又はシリコンのいずれか一又は複数を有する膜で形成することを特徴とする半導体装置の作製方法。

## 【請求項9】

請求項1乃至請求項7のいずれか一項において、

前記電荷蓄積層として、窒素を含む絶縁膜で形成することを特徴とする半導体装置の作製方法。

## 【請求項10】

基板上に設けられたメモリトランジスタ、第1のトランジスタ及び第2のトランジスタを有し、

前記メモリトランジスタは、前記基板上に設けられた第1の導電膜と、前記第1の導電膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた電荷蓄積層と、前記電荷蓄積層上に設けられた前記第1の絶縁膜より膜厚が薄い第2の絶縁膜と、前記第2の絶縁膜上に設けられた第1の半導体膜とを有し、

前記第1のトランジスタは、前記基板上に設けられた第2の導電膜と、前記第2の導電膜上に設けられた前記第1の絶縁膜と、前記第1の絶縁膜上に設けられた前記第2の絶縁膜と、前記第2の絶縁膜上に設けられた第2の半導体膜とを有し、

前記第2のトランジスタは、前記基板上に前記第1の絶縁膜及び前記第2の絶縁膜を介して設けられた第3の半導体膜と、前記第3の半導体膜上に設けられ、前記第1の絶縁膜より膜厚が薄い第3の絶縁膜と、前記第3の絶縁膜上に設けられた第3の導電膜とを有することを特徴とする半導体装置。

## 【請求項11】

40

基板上に設けられたメモリトランジスタ、第1のトランジスタ及び第2のトランジスタを有し、

前記メモリトランジスタは、前記基板上に設けられた第1の導電膜と、前記第1の導電膜上に設けられた第2の絶縁膜と、前記第2の絶縁膜上に設けられた電荷蓄積層と、前記電荷蓄積層上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた第1の半導体膜とを有し、

前記第1のトランジスタは、前記基板上に設けられた第2の導電膜と、前記第2の導電膜上に設けられた前記第2の絶縁膜より膜厚が厚い第1の絶縁膜と、前記第1の絶縁膜上に設けられた前記第2の絶縁膜と、前記第2の絶縁膜上に設けられた第2の半導体膜とを有

50

し、

前記第2のトランジスタは、前記基板上に前記第1の絶縁膜及び前記第2の絶縁膜を介して設けられた第3の半導体膜と、前記第3の半導体膜上に設けられ、前記第1の絶縁膜より膜厚が薄い第3の絶縁膜と、前記第3の絶縁膜上に設けられた第3の導電膜とを有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置及びその作製方法に関し、特に半導体記憶素子を有する半導体装置及びその作製方法に関する。

10

【背景技術】

【0002】

近年、携帯型コンピュータ、携帯電話といった携帯機器に代表される多機能かつ高機能な小型の半導体装置が急速に普及している。そしてこれに伴い、半導体装置を構成するメモリとして、トランジスタ型の半導体記憶素子（以下、「メモリトランジスタ」とも記す）が注目されている。

【0003】

半導体記憶素子の一つとして、データを電気的に書き換え可能であり、電源を切ってもデータを記憶しておくことのできる不揮発性メモリの市場が拡大している。不揮発性メモリは、MOSトランジスタと類似の構造を有し、電荷を長期間蓄積することができる領域がチャネル形成領域上に設けられているところに特徴がある。フローティングゲート型の不揮発性メモリは、チャネル形成領域上のトンネル絶縁膜を通して電荷蓄積層（フローティングゲート）に電荷を注入して保持させるものである。また、MONOS（Metal-Oxide-Nitride-Oxide Semiconductor）型の不揮発性メモリでは、電荷蓄積層での電荷のトラップ若しくはシリコンクラスタを電荷保持担体として利用している。

20

【0004】

これらの不揮発性メモリを構成するメモリトランジスタにおいては、半導体層と電荷蓄積層との間に形成されるトンネル絶縁膜をできるだけ薄くする必要がある。トンネル絶縁膜はトンネル電流が流れる程度の膜厚にしなければならないためである。

30

【0005】

また、メモリトランジスタと同一基板上に形成されるトランジスタは、設けられる回路毎によって構成が異なる。例えば、ロジック回路に設けられるトランジスタは高速動作が必要とされるためゲート絶縁膜を薄く形成する必要がある。一方で、メモリトランジスタの制御（書き込み、消去、読み出し等）を行う回路に設けられているトランジスタは、メモリトランジスタに加わる電圧と同程度の高電圧が加わるため、トランジスタの破壊を防止するためにゲート絶縁膜を厚く形成する必要がある。

【0006】

引用文献1では、同一基板上に画素部、駆動回路部、メモリ部を一体形成し、メモリトランジスタのゲート絶縁膜を画素部や駆動回路部のゲート絶縁膜よりも薄く形成している。

40

【特許文献1】特開2000-356788号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

メモリトランジスタと周辺回路のトランジスタを同一基板上に形成する場合、メモリトランジスタのトンネル絶縁膜と周辺回路のトランジスタのゲート絶縁膜の構造や膜厚が異なるため、トンネル絶縁膜やゲート絶縁膜の作り分けを行う必要がある。絶縁膜の作り分けにより、半導体膜上に形成された不要な絶縁膜をエッチングして除去する場合、半導体膜の表面がエッチングにより損傷し、特性不良が生じるおそれがある。また、不要な絶縁膜

50

膜の除去に伴い工程が増加する問題がある。

【0008】

本発明は、上記問題に鑑み、同一基板上にメモリトランジスタとトランジスタを設ける場合であっても、工程の簡略化を図ることを課題の一とする。又は、同一基板上にメモリトランジスタとトランジスタを設ける場合であっても、特性不良を抑制することを課題の一とする。又は、同一基板上にメモリトランジスタとトランジスタを設ける場合であっても、特性不良を抑制すると共に、書き込み、消去電圧の低減を図ることを課題の一とする。

【課題を解決するための手段】

【0009】

本発明の半導体装置の作製方法の一は、基板上に第1の導電膜と第2の導電膜を形成し、第1の導電膜上と第2の導電膜上に第1の絶縁膜を形成し、第1の導電膜上に第1の絶縁膜を介して電荷蓄積層を選択的に形成し、第1の絶縁膜上と電荷蓄積層上に第2の絶縁膜を形成し、第2の絶縁膜上に、第1の導電膜と重なる第1の半導体膜と、第2の導電膜と重なる第2の半導体膜と、第1の導電膜及び第2の導電膜と重ならない第3の半導体膜を形成し、第1の半導体膜、第2の半導体膜及び第3の半導体膜上に第3の絶縁膜を形成し、第3の半導体膜の上方に第3の絶縁膜を介して第3の導電膜を形成する。また、第3の導電膜を形成後、第1の半導体膜及び第2の半導体膜上にレジストを形成し、レジスト及び第3の導電膜をマスクとして、第1の半導体膜、第2の半導体膜及び第3の半導体膜に不純物元素を導入することができる。また、第2の絶縁膜及び第3の絶縁膜を、第1の絶縁膜より薄く形成する。

10

20

【0010】

また、本発明の半導体装置の作製方法の一は、基板上に第1の導電膜と第2の導電膜を形成し、第1の導電膜上と第2の導電膜上に第1の絶縁膜を形成し、第1の導電膜上に第1の絶縁膜を介して電荷蓄積層を選択的に形成し、第1の絶縁膜上と電荷蓄積層上に第2の絶縁膜を形成し、第2の絶縁膜上に、第1の導電膜と重なる第1の半導体膜と、第2の導電膜と重なる第2の半導体膜と、第1の導電膜及び第2の導電膜と重ならない第3の半導体膜を形成し、第1の半導体膜、第2の半導体膜及び第3の半導体膜上に第3の絶縁膜を形成し、第3の絶縁膜上に、第3の半導体膜と重なる第3の導電膜と、第1の半導体膜と重なる第4の導電膜と、第2の半導体膜と重なる第5の導電膜を形成する。また、第3の導電膜～第5の導電膜を形成後、第3の導電膜、第4の導電膜及び第5の導電膜をマスクとして、第1の半導体膜、第2の半導体膜及び第3の半導体膜に不純物元素を導入することができる。また、第2の絶縁膜及び第3の絶縁膜を、第1の絶縁膜より薄く形成する。

30

【0011】

また、本発明の半導体装置の作製方法の一は、基板上に第1の導電膜と第2の導電膜を形成し、第1の導電膜上と第2の導電膜上に第1の絶縁膜を形成し、第1の導電膜上に形成された第1の絶縁膜を除去し、第1の導電膜上と第1の絶縁膜上に第2の絶縁膜を形成し、第1の導電膜上に第2の絶縁膜を介して電荷蓄積層を選択的に形成し、電荷蓄積層上にトンネル絶縁膜を選択的に形成し、トンネル絶縁膜上に第1の導電膜と重なる第1の半導体膜を形成し、第2の絶縁膜上に、第2の導電膜と重なる第2の半導体膜と、第1の導電膜及び第2の導電膜と重ならない第3の半導体膜を形成し、第1の半導体膜、第2の半導体膜及び第3の半導体膜上に第3の絶縁膜を形成し、第3の半導体膜の上方に第3の絶縁膜を介して第3の導電膜を形成する。また、第3の導電膜を形成後、第1の半導体膜及び第2の半導体膜上にレジストを形成し、レジスト及び第3の導電膜をマスクとして、第1の半導体膜、第2の半導体膜及び第3の半導体膜に不純物元素を導入することができる。また、第2の絶縁膜及び第3の絶縁膜を、第1の絶縁膜より薄く形成する。

40

【0012】

また、本発明の半導体装置の作製方法の一は、基板上に第1の導電膜と第2の導電膜を形成し、第1の導電膜上と第2の導電膜上に第1の絶縁膜を形成し、第1の導電膜上に形

50

成された第1の絶縁膜を除去し、第1の導電膜上と第1の絶縁膜上に第2の絶縁膜を形成し、第1の導電膜上に第2の絶縁膜を介して電荷蓄積層を選択的に形成し、電荷蓄積層上にトンネル絶縁膜を選択的に形成し、トンネル絶縁膜上に第1の導電膜と重なる第1の半導体膜を形成し、第2の絶縁膜上に、第2の導電膜と重なる第2の半導体膜と、第1の導電膜及び第2の導電膜と重ならない第3の半導体膜を形成し、第1の半導体膜、第2の半導体膜及び第3の半導体膜上に第3の絶縁膜を形成し、第3の絶縁膜上に、第3の半導体膜と重なる第3の導電膜と、第1の半導体膜と重なる第4の導電膜と、第2の半導体膜と重なる第5の導電膜を形成する。また、第3の導電膜～第5の導電膜を形成後、第3の導電膜、第4の導電膜及び第5の導電膜をマスクとして、第1の半導体膜、第2の半導体膜及び第3の半導体膜に不純物元素を導入することができる。また、第2の絶縁膜及び第3の絶縁膜を、第1の絶縁膜より薄く形成する。

10

## 【0013】

本発明の半導体装置の一は、基板上に設けられたメモリトランジスタ、第1のトランジスタ及び第2のトランジスタを有し、メモリトランジスタは、基板上に設けられた第1の導電膜と、第1の導電膜上に設けられた第1の絶縁膜と、第1の絶縁膜上に設けられた電荷蓄積層と、電荷蓄積層上に設けられ第1の絶縁膜より膜厚が小さい第2の絶縁膜と、第2の絶縁膜上に設けられた第1の半導体膜とを有し、第1のトランジスタは、基板上に設けられた第2の導電膜と、第2の導電膜上に設けられた第1の絶縁膜と、第1の絶縁膜上に設けられた第2の絶縁膜と、第2の絶縁膜上に設けられた第2の半導体膜とを有し、第2のトランジスタは、基板上に第1の絶縁膜及び第2の絶縁膜を介して設けられた第3の半導体膜と、第3の半導体膜上に設けられ、第1の絶縁膜より膜厚が小さい第3の絶縁膜と、第3の絶縁膜上に設けられた第3の導電膜とを有する。

20

## 【0014】

また、本発明の半導体装置の一は、基板上に設けられたメモリトランジスタ、第1のトランジスタ及び第2のトランジスタを有し、メモリトランジスタは、基板上に設けられた第1の導電膜と、第1の導電膜上に設けられた第2の絶縁膜と、第2の絶縁膜上に設けられた電荷蓄積層と、電荷蓄積層上に設けられたトンネル絶縁膜と、トンネル絶縁膜上に設けられた第1の半導体膜とを有し、第1のトランジスタは、基板上に設けられた第2の導電膜と、第2の導電膜上に設けられ第2の絶縁膜より膜厚が大きい第1の絶縁膜と、第1の絶縁膜上に設けられた第2の絶縁膜と、第2の絶縁膜上に設けられた第2の半導体膜とを有し、第2のトランジスタは、基板上に第1の絶縁膜及び第2の絶縁膜を介して設けられた第3の半導体膜と、第3の半導体膜上に設けられ、第1の絶縁膜より膜厚が小さい第3の絶縁膜と、第3の絶縁膜上に設けられた第3の導電膜とを有する。

30

## 【発明の効果】

## 【0015】

メモリトランジスタと、ゲート絶縁膜の膜厚が異なる複数の薄膜トランジスタとを同一の基板上に設ける場合において、メモリトランジスタと一部の薄膜トランジスタをボトムゲート型の構造で設け、他の薄膜トランジスタをトップゲート型の構造で設けることにより、作製プロセスの簡略化を図ることができる。

40

## 【0016】

また、メモリトランジスタと、ゲート絶縁膜の膜厚が異なる複数の薄膜トランジスタとを同一の基板上に設ける場合において、ゲート絶縁膜の膜厚に応じて薄膜トランジスタをトップゲート型とボトムゲート型の構造とすることにより、半導体膜上に接して形成された絶縁膜をエッチングにより除去する工程を省略し、トランジスタの特性不良を低減することができる。

## 【0017】

また、メモリトランジスタをボトムゲート型の構造で設け、電荷蓄積層への電子の注入や放出をゲート電極の端部を利用することによって、書き込み、消去電圧を低減することができる。

## 【発明を実施するための最良の形態】

50

## 【0018】

以下、本発明の実施の形態について図面を参照しながら説明する。ただし、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本実施の形態の記載内容に限定して解釈されるものではない。なお、本明細書中の図面において、同一部分または同様な機能を有する部分には同一の符号を付し、その説明は省略する場合がある。

## 【0019】

## (実施の形態1)

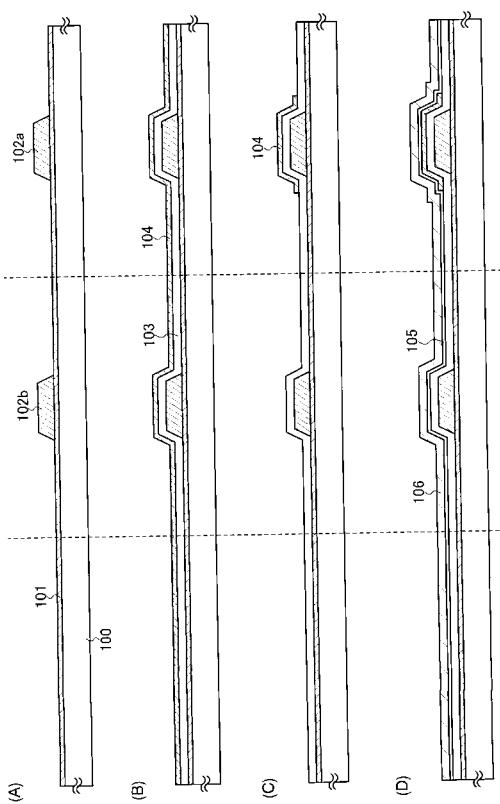

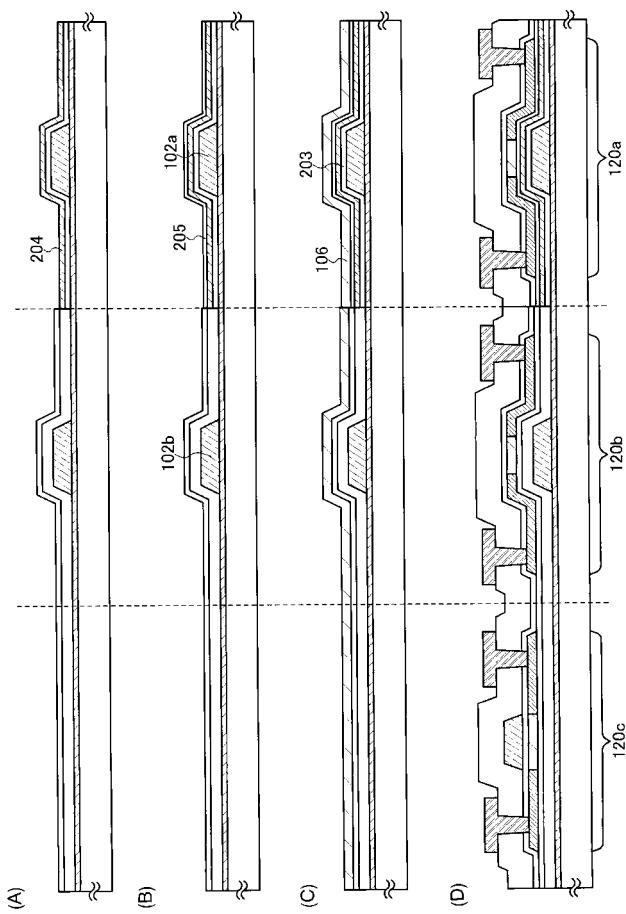

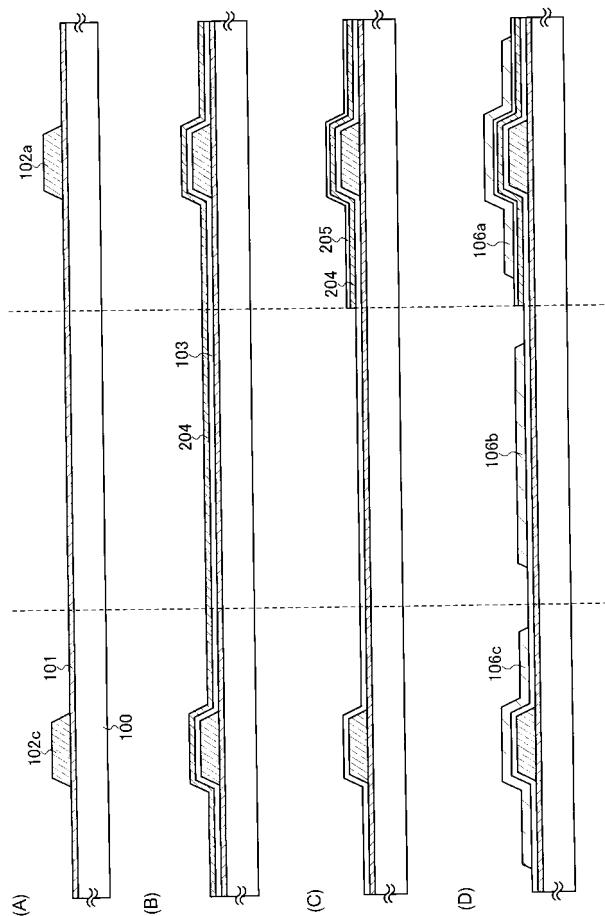

本実施の形態では、メモリトランジスタを具備する半導体装置及びその作製方法の一例に關し図1～図3を参照して説明する。

10

## 【0020】

以下の説明では、メモリトランジスタと、耐圧を要する(高耐圧用)薄膜トランジスタと、高速動作を要する(高速動作用)薄膜トランジスタとを同一基板上に形成する場合に關して説明する。高耐圧用の薄膜トランジスタのゲート絶縁膜は、高速動作用の薄膜トランジスタのゲート絶縁膜より厚く形成する。

## 【0021】

まず、基板100上に絶縁膜101を介して導電膜102a、102bを形成する(図1(A)参照)。

20

## 【0022】

基板100は、ガラス基板、金属基板やステンレス基板、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いるとよい。このような基板であれば、その面積や形状に大きな制限はないため、例えば、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向上させることができる。このような利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。従って、集積回路部を大きく形成した場合であっても、シリコン基板を用いる場合と比較して低コスト化を実現することができる。

## 【0023】

絶縁膜101は、CVD法やスパッタリング法等により、珪素の酸化物または珪素の窒化物を含む膜(例えば、酸化珪素(SiO<sub>x</sub>)膜、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)膜、窒化珪素(SiN<sub>x</sub>)膜、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)膜等)を単層又は積層で形成する。

30

## 【0024】

導電膜102a、102bは、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、ニッケル(Ni)、シリコン(Si)等から選択された元素でなる膜、またはこれらの元素の窒化物でなる膜(代表的には、窒化タンタル膜、窒化タンゲステン膜、窒化チタン膜)、または前記元素を組み合わせた合金膜(代表的にはMo-W合金、Mo-Ta合金)、または前記元素のシリサイド膜(代表的にはタンゲステンシリサイド膜、チタンシリサイド膜、ニッケルシリサイド膜)を用いることができる。また、導電膜102a、102bは、複数の導電膜を積層させた構造で設けてもよく、例えば、膜厚が20nm～100nmの窒化タンタル膜と、膜厚が100nm～400nmのタンゲステン膜を順に積層させた構造で設けることができる。タンゲステンや窒化タンタルは、耐熱性が高いため、導電膜を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、導電膜102a、102bは、絶縁膜101を介さずに基板100上に直接設けてもよい。

40

## 【0025】

なお、導電膜102aはメモリトランジスタのゲート電極として機能し、導電膜102bは高耐圧用の薄膜トランジスタのゲート電極として機能する。

## 【0026】

次に、基板100、導電膜102a、102b上に第1の絶縁膜103を形成し、当該

50

第1の絶縁膜103上に電荷蓄積層104を形成する(図1(B)参照)。

【0027】

第1の絶縁膜103は、CVD法、スパッタリング法等により、珪素の酸化物または珪素の窒化物を含む膜(例えば、酸化珪素膜、酸化窒化珪素膜、窒化珪素膜、窒化酸化珪素膜等)を単層又は積層で形成する。

【0028】

第1の絶縁膜103は、高耐圧用の薄膜トランジスタにおけるゲート絶縁膜の一部、メモリトランジスタにおける電荷蓄積層とゲート電極間に設けられる絶縁膜となる。ここでは、第1の絶縁膜103として酸化珪素膜又は酸化窒化珪素膜を用い、膜厚を20nm~60nm、好ましくは30nm~55nmで設ける。このように、メモリトランジスタと高耐圧用の薄膜トランジスタにおいて、絶縁膜を共有して設けることにより、工程の簡略化を図ることができる。

10

【0029】

電荷蓄積層104は、CVD法、スパッタリング法等により、膜中に電荷をトラップする欠陥を有している絶縁膜、又は導電性粒子又はシリコン等の半導体粒子を含む絶縁膜で形成することができる。例えば、電荷蓄積層104として、窒素を含む絶縁膜、例えば、窒化珪素膜、窒化酸化珪素膜、酸化窒化珪素膜又はこれらの絶縁膜中に導電性粒子や半導体粒子が含まれた膜を利用することができる。このように、電荷蓄積層104として窒素を含む絶縁膜で設けることによって、MONOS型のメモリトランジスタとすることができる。

20

【0030】

なお、メモリトランジスタはMONOS型に限らず、電荷蓄積層104として導電性を有する膜で設けてもよい。例えば、電荷蓄積層104として、タンゲステン(W)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、シリコン(Si)から選ばれた元素でなる膜、または前記元素の窒化物でなる膜(代表的には、窒化タンゲステン膜、窒化タンタル膜、窒化チタン膜)、または前記元素のシリサイド膜(代表的にはタンゲステンシリサイド膜、チタンシリサイド膜)を用いることができる。シリコン膜に対しては、リンやボロンなどの不純物を添加してもよい。このように、電荷蓄積層104として導電性を有する膜で設けることによって、フローティングゲート型のメモリトランジスタとすることができる。

30

【0031】

本実施の形態では、電荷蓄積層104としてタンゲステン(W)を用い、膜厚を5nm~100nm、好ましくは10nm~50nmで設ける。つまり、メモリトランジスタとしてフローティングゲート型で設ける場合を示す。

【0032】

次に、電荷蓄積層104を選択的に除去して一部を残存させる(図1(C)参照)。ここでは、メモリトランジスタを構成する導電膜102a上に設けられた電荷蓄積層を少なくとも残存せしようにエッチングを行う。電荷蓄積層104は、導電膜102aの幅より小さくなるように設けてもよいし、図1(C)に示すように導電膜102aの幅より大きくなるように設けてもよい。

40

【0033】

次に、残存した電荷蓄積層104及び露出した第1の絶縁膜103上に第2の絶縁膜105を形成し、当該第2の絶縁膜105上に半導体膜106を形成する(図1(D)参照)。

【0034】

第2の絶縁膜105は、CVD法、スパッタリング法等を用いて、珪素の酸化物または珪素の窒化物を含む膜(例えば、酸化珪素膜、酸化窒化珪素膜、窒化珪素膜、窒化酸化珪素膜等)を単層又は積層で形成する。

【0035】

第2の絶縁膜105は、メモリトランジスタのトンネル絶縁膜として機能する。ここで

50

は、第2の絶縁膜105として酸化珪素又は酸化窒化珪素を用い、膜厚を5nm～20nm、好ましくは5nm～15nmで設ける。また、第2の絶縁膜105は、高耐圧用の薄膜トランジスタのゲート絶縁膜の一部となる。本実施の形態では、高耐圧の薄膜トランジスタのゲート絶縁膜は第1の絶縁膜103及び第2の絶縁膜105の積層構造となる。このように、メモリトランジスタを構成する絶縁膜と薄膜トランジスタのゲート絶縁膜を共有して設けることにより工程の簡略化を図ることができる。

【0036】

半導体膜106は、スパッタ法、LPCVD法、プラズマCVD法等により、25～200nm(好ましくは30～150nm)の厚さで形成する。半導体膜106としては、例えば、非晶質珪素膜を形成すればよい。

10

【0037】

また非晶質の半導体膜106にレーザー光を照射して結晶化を行ってもよい。なお、レーザー光の照射と、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とを組み合わせた方法等により非晶質の半導体膜106の結晶化を行ってもよい。

【0038】

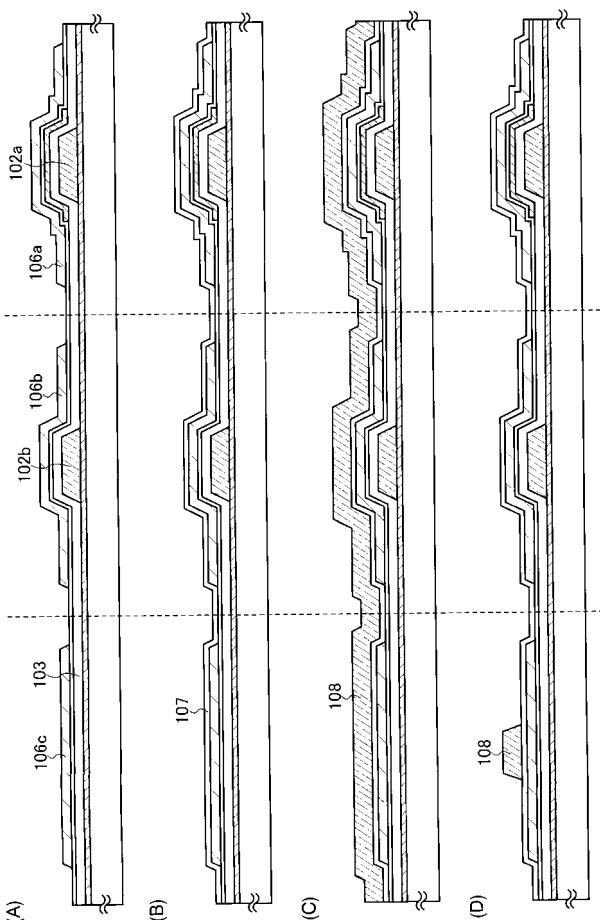

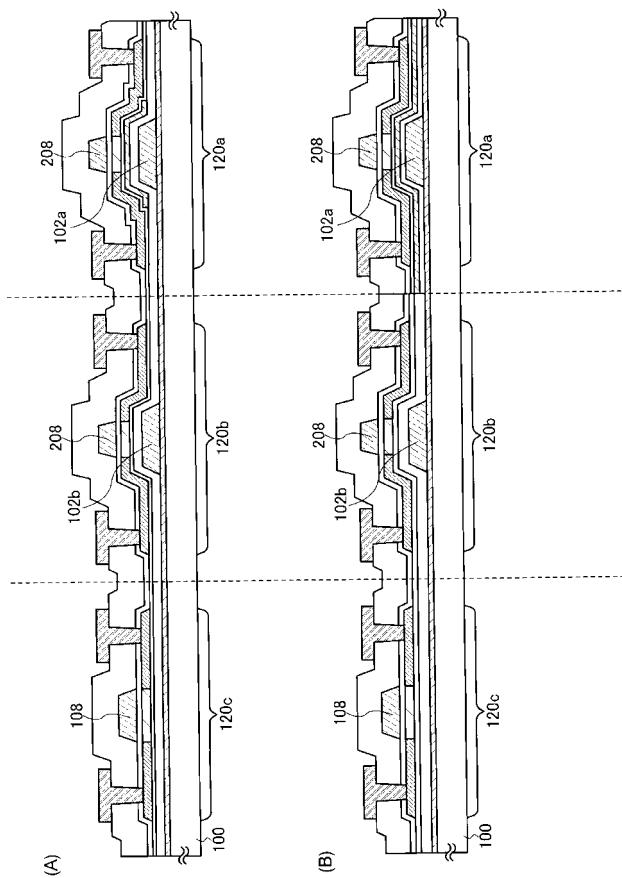

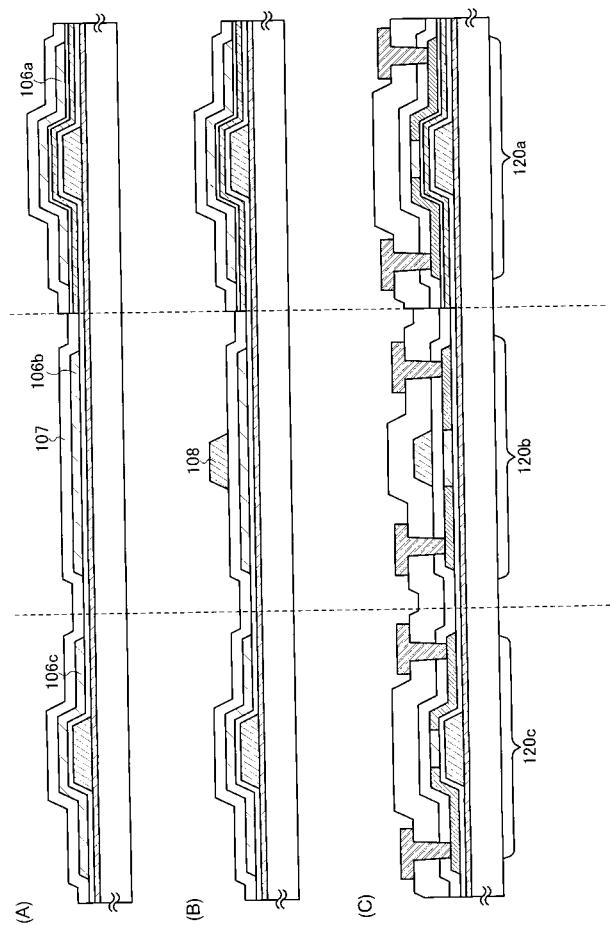

本実施の形態では、半導体膜106の結晶化を行った後に半導体膜106を所望の形状にエッチングして、結晶質の半導体膜106a、106b、106cを形成する(図2(A)参照)。半導体膜106aは導電膜102aと重なるように形成し、半導体膜106bは導電膜102bと重なるように形成し、半導体膜106cは導電膜102a、102bとは重ならないように形成する。

20

【0039】

形成された半導体膜106aはメモリトランジスタのチャネル形成領域を形成し、半導体膜106bは高耐圧用の薄膜トランジスタのチャネル形成領域を形成し、半導体膜106cは高速動作用の薄膜トランジスタのチャネル形成領域を形成する。

【0040】

次に、半導体膜106a～106c上に第3の絶縁膜107を形成する(図2(B)参照)。

【0041】

第3の絶縁膜107は、CVD法、スパッタリング法等を用いて、珪素の酸化物または珪素の窒化物を含む膜(例えば、酸化珪素膜、酸化窒化珪素膜、窒化珪素膜、窒化酸化珪素膜等)を単層又は積層で形成する。又は、プラズマ処理を行い、半導体膜の表面を酸化又は窒化することで形成しても良い。例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスを導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカル(NHラジカルを含む場合もある)によって、半導体膜の表面を酸化又は窒化することができる。また、CVD法、スパッタリング法等を用いて、珪素の酸化物または珪素の窒化物を含む膜を形成した後、当該形成した絶縁膜にプラズマ処理を行ってもよい。

30

【0042】

また、第3の絶縁膜107は、高速動作用の薄膜トランジスタのゲート絶縁膜となる。ここでは、第3の絶縁膜107として酸化珪素膜又は酸化窒化珪素膜を用い、膜厚を3nm～25nm、好ましくは5nm～20nmで設ける。つまり、高耐圧用の薄膜トランジスタのゲート絶縁膜より薄く設ける。

40

【0043】

次に、第3の絶縁膜107上に導電膜108を形成する(図2(C)参照)。

【0044】

導電膜108は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、ニッケル(Ni)、シリコン(Si)

50

等から選択された元素でなる膜、またはこれらの元素の窒化物でなる膜（代表的には、窒化タンタル膜、窒化タンゲステン膜、窒化チタン膜）、または前記元素を組み合わせた合金膜（代表的にはMo-W合金膜、Mo-Ta合金膜）、または前記元素のシリサイド膜（代表的にはタンゲステンシリサイド膜、チタンシリサイド膜、ニッケルシリサイド膜）を単層又は積層して設ける。

【0045】

次に、導電膜108をエッティングして、半導体膜106cの上方に一部を残存させる（図2（D）参照）。残存した導電膜108は、高速動作を要する薄膜トランジスタのゲート電極として機能する。

【0046】

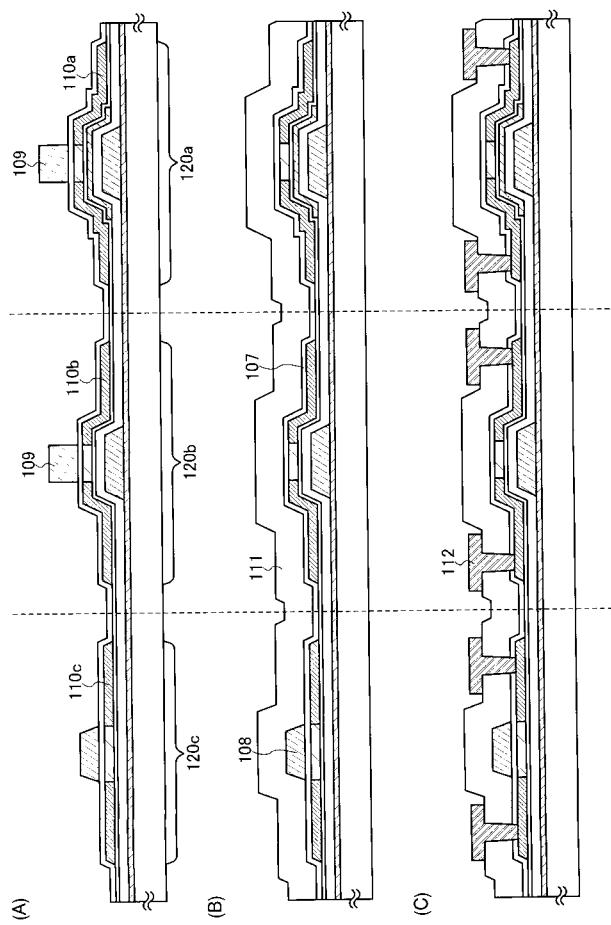

次に、半導体膜106a、半導体膜106bの一部と重なるようにレジスト109を設け、当該レジスト109及び導電膜108をマスクとして半導体膜106a～半導体膜106cに不純物元素を導入してソース領域又はドレイン領域として機能する不純物領域110a～不純物領域110cを形成する（図3（A）参照）。

【0047】

その結果、ボトムゲート型のメモリトランジスタ120a、ボトムゲート型の高耐圧用の薄膜トランジスタ120b、トップゲート型の高速動作用の薄膜トランジスタ120cを形成することができる。

【0048】

導入する不純物元素は、n型の不純物元素又はp型の不純物元素を用いる。n型の不純物元素としては、リン（P）やヒ素（As）等を用いることができる。p型の不純物元素としては、ボロン（B）やアルミニウム（Al）やガリウム（Ga）等を用いることができる。ここでは、半導体膜106a～106cに高濃度のリン（P）を導入し、n型の不純物領域110a～110cを形成する。もちろんボロン（B）を導入して、p型の不純物領域を形成してもよい。

【0049】

半導体膜106cに形成される不純物領域110cは、導電膜108をマスクとして用いることができるため、自己整合的に形成することができる。

【0050】

このように、同一基板上に形成されるメモリトランジスタ及び薄膜トランジスタの一部をボトムゲート型とし、その他の薄膜トランジスタをトップゲート型で設けることによって、メモリトランジスタのトンネル絶縁膜やトランジスタのゲート絶縁膜の膜厚が異なる場合であっても、不要なゲート絶縁膜のエッティング工程を減らし、エッティングによる半導体膜へのダメージを抑制することが可能となる。

【0051】

次に、導電膜108及び第3の絶縁膜107上に層間絶縁膜となる絶縁膜111を形成する（図3（B）参照）。

【0052】

絶縁膜111は、CVD法、スパッタリング法、SOG法、液滴吐出法、スクリーン印刷法等により、シリコンの酸化物やシリコンの窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン系樹脂、アクリルポリマー、エポキシ樹脂等の有機材料やシロキサン材料等により、単層または積層で形成する。例えば、絶縁膜111を、窒化酸化シリコン膜と酸化窒化シリコン膜の2層の積層構造で設けることができる。なお、シロキサン材料とは、Si-O-Si結合を含む材料に相当する。シロキサンは、シリコン（Si）と酸素（O）との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。有機基はフルオロ基含んでも良い。

【0053】

次に絶縁膜111に上にメモリトランジスタ120a、高耐圧用の薄膜トランジスタ120b、高速動作用の薄膜トランジスタ120cのソース電極又はドレイン電極として機

10

20

30

40

50

能しうる導電膜 112 を形成する（図 3（C）参照）。

【0054】

導電膜 112 は、CVD 法やスパッタリング法等により、アルミニウム（Al）、タンゲステン（W）、チタン（Ti）、タンタル（Ta）、モリブデン（Mo）、ニッケル（Ni）、白金（Pt）、銅（Cu）、金（Au）、銀（Ag）、マンガン（Mn）、ネオジム（Nd）、炭素（C）、シリコン（Si）から選択された元素、又はこれらの元素を主成分とする合金若しくは化合物で、単層又は積層で形成する。アルミニウムを主成分とする合金とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素とシリコンの一方又は両方とを含む材料に相当する。

10

【0055】

以上の工程によりメモリトランジスタを具備する半導体装置を得ることができる。

【0056】

なお、本実施の形態において、薄膜トランジスタは、様々な形態のトランジスタを適用させることが出来る。例えば、ゲート電極が 2 個以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすると、形式上チャネル領域が直列に接続されるような構成となるため、複数のトランジスタが直列に接続されたような構成となる。マルチゲート構造にすることにより、オフ電流の低減や、トランジスタの耐圧を向上させることによる信頼性の向上や、飽和領域で動作する時に、ドレインとソース間電圧が変化しても、ドレインとソース間電流があまり変化せず、フラットな特性にすることなどができる。

20

【0057】

また、半導体膜において、チャネル形成領域とソース領域又はドレイン領域となる不純物領域との間に LDD 領域を設けた構成としてもよい。LDD 領域を設けることにより、オフ電流の低減や、トランジスタの耐圧を向上させることによる信頼性の向上や、飽和領域で動作する時に、ドレインとソース間電圧が変化しても、ドレインとソース間電流があまり変化せず、フラットな特性にすることができる。

【0058】

なお、本実施の形態は、本明細書の他の実施の形態で示した半導体装置の構成と適宜組み合わせることができる。

30

【0059】

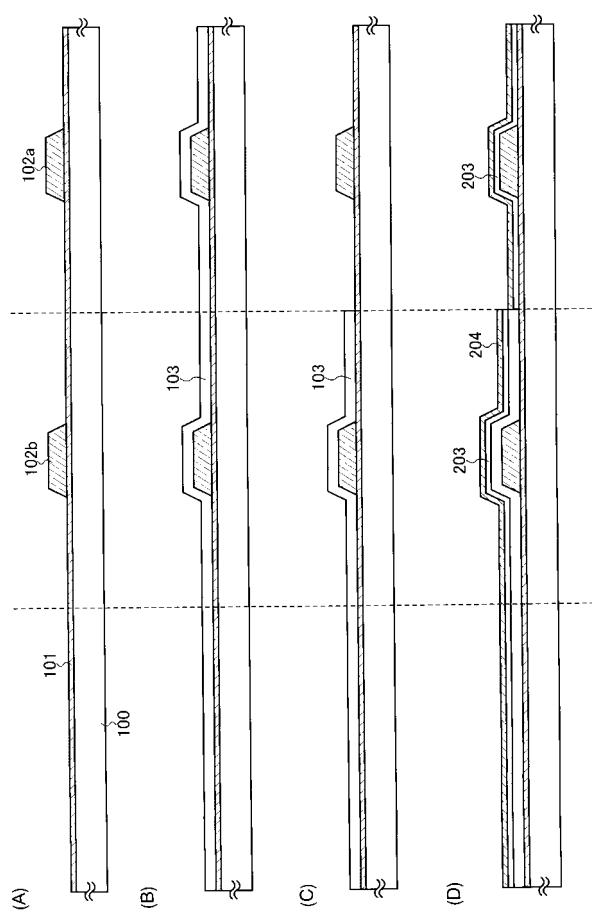

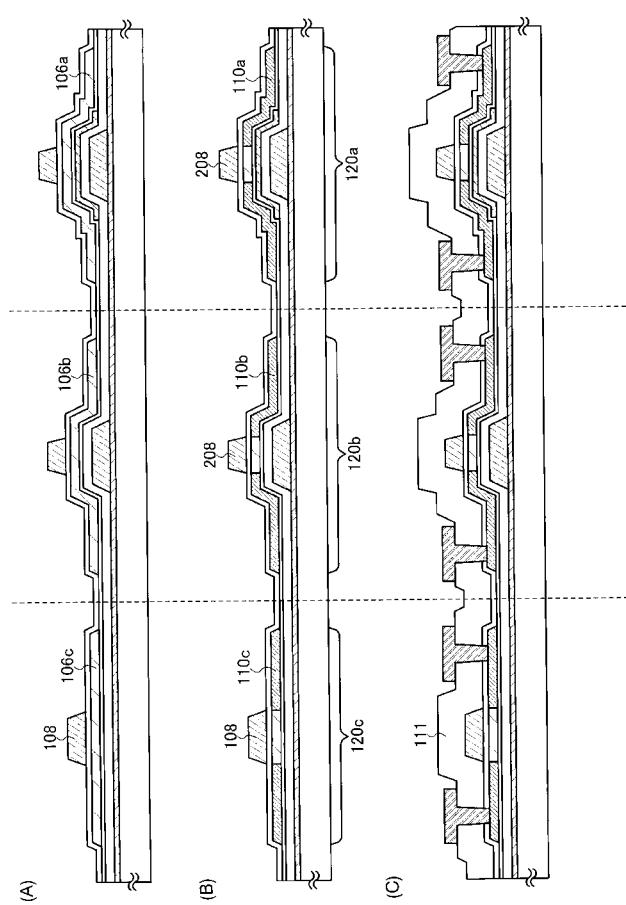

（実施の形態 2）

本実施の形態では、上記実施の形態と異なる半導体装置及びその作製方法について図面を参照して説明する。具体的には、メモリトランジスタの絶縁膜（ゲート電極と電荷蓄積層との間に設けられた絶縁膜）を高耐圧用の薄膜トランジスタのゲート絶縁膜より薄く設ける MONOS 型のメモリトランジスタに関して説明する。

【0060】

まず、基板 100 上に絶縁膜 101 を介して導電膜 102a、102b を形成する（図 4（A）参照）。導電膜 102a はメモリトランジスタのゲート電極となり、導電膜 102b は高耐圧用の薄膜トランジスタのゲート電極となる。

40

【0061】

次に、基板 100、導電膜 102a、102b 上に第 1 の絶縁膜 103 を形成する（図 4（B）参照）。本実施の形態において、第 1 の絶縁膜 103 は、高耐圧用の薄膜トランジスタのゲート絶縁膜の一部となる。ここでは、第 1 の絶縁膜 103 として酸化窒化珪素を用い、膜厚を 10 nm ~ 60 nm、好ましくは 20 nm ~ 40 nm で設ける。

【0062】

次に、導電膜 102a 上に形成された第 1 の絶縁膜 103 を除去する（図 4（C）参照）。

【0063】

次に、導電膜 102a 上及び第 1 の絶縁膜 103 上に第 2 の絶縁膜 203 を形成し、当該第 2 の絶縁膜 203 上に電荷蓄積層 204 を形成する（図 4（D）参照）。電荷蓄積層

50

204は、CVD法、スパッタリング法等により、窒素を含む絶縁膜、例えば、窒化シリコン膜、窒化酸化シリコン膜、酸化窒化シリコン膜又はこれらの絶縁膜中に導電性粒子や半導体粒子が含まれた膜で形成する。本実施の形態では、電荷蓄積層204として窒化シリコンを用い、膜厚を3nm～40nm、好ましくは5nm～20nmで設ける。第2の絶縁膜203は、CVD法、スパッタリング法等により、酸化珪素膜、酸化窒化珪素膜等を用いて単層又は積層で形成する。なお、ここでは、第2の絶縁膜203として酸化窒化シリコンを用い、膜厚を3nm～15nm、好ましくは5nm～10nmで設ける。なお、第2の絶縁膜203は必ずしも設けなくてもよい。第2の絶縁膜203を設けない場合には、MONOS型となる。

## 【0064】

10

次に、電荷蓄積層204を選択的に除去して一部を残存させる(図5(A)参照)。ここでは、メモリトランジスタを構成する導電膜102a上に設けられた電荷蓄積層を少なくとも残存させるようにエッチングを行う。なお、本実施の形態において、電荷蓄積層204は絶縁膜であるため、電荷蓄積層204を除去しない構成としてもよいし、メモリトランジスタ間の電荷蓄積層204を除去してメモリトランジスタ毎に分離してもよい。

## 【0065】

20

次に、少なくとも導電膜102aの上方に絶縁膜205を形成する(図5(B)参照)。絶縁膜205はMONOS型のメモリトランジスタのトンネル絶縁膜となるため、膜厚を小さく形成することが好ましい。ここでは、プラズマ処理を行い、電荷蓄積層204の表面を酸化することで絶縁膜205を形成する。例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素、水素などの混合ガスを導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)によって、電荷蓄積層204の表面を酸化することができる。ここでは、プラズマ処理により、絶縁膜205として酸化珪素膜又は酸化窒化珪素膜を1nm～5nm、好ましくは2nm～4nmで形成する。

## 【0066】

また、プラズマ処理を行うことによって、第2の絶縁膜203の表面を改質することができる。

## 【0067】

30

ここでは、プラズマ処理により絶縁膜205を形成する場合を示したが、もちろん、CVD法やスパッタリング法等により、酸化珪素膜又は窒化珪素膜を形成してもよいし、形成した絶縁膜にプラズマ処理を行ってもよい。

## 【0068】

次に、絶縁膜205及び第2の絶縁膜203上に半導体膜106を形成する(図5(C)参照)。

## 【0069】

40

その後、上記図2(A)～図3(C)まで同様の工程を経ることによって、MONOS型のメモリトランジスタを有する半導体装置を得ることができる(図5(D)参照)。なお、本実施の形態の半導体装置において、メモリトランジスタ120a及び高耐圧用の薄膜トランジスタ120bはボトムゲート型の構造となり、高速動作用の薄膜トランジスタ120cはトップゲート型の構造となる。

## 【0070】

50

本実施の形態では、メモリトランジスタ120aの絶縁膜(導電膜102aと電荷蓄積層204との間に設けられた第2の絶縁膜203)と高耐圧用の薄膜トランジスタ120bのゲート絶縁膜(第1の絶縁膜103と第2の絶縁膜203)の膜厚が異なるため、上記図4(C)において不要なゲート絶縁膜(すなわち、導電膜102a上に形成された第1の絶縁膜103)のエッチングを行っているが、メモリトランジスタ120aをボトムゲート構造とすることにより不要なゲート絶縁膜の除去に伴い半導体膜106へダメージが加わる問題を解消することができる。

## 【0071】

なお、本実施の形態では、メモリトランジスタと高耐圧用の薄膜トランジスタをボトムゲート構造で設け、高速動作用の薄膜トランジスタをトップゲート構造で設けた例を示したがこれに限られない。例えば、メモリトランジスタの絶縁膜（ゲート電極と電荷蓄積層との間に設けられた絶縁膜）と高速動作用の薄膜トランジスタのゲート絶縁膜を共有して設けることができる場合には、メモリトランジスタと高速動作用の薄膜トランジスタをボトムゲート構造で設け、高耐圧用の薄膜トランジスタをトップゲート構造で設けてもよい。この場合の作製方法について、以下に図14、図15を参照して説明する。

## 【0072】

まず、基板100上に絶縁膜101を介して導電膜102a、102cを形成する（図14（A）参照）。導電膜102aはメモリトランジスタのゲート電極となり、導電膜102cは高耐圧用の薄膜トランジスタのゲート電極となる。

10

## 【0073】

次に、基板100、導電膜102a、102c上に第1の絶縁膜103を形成し、当該第1の絶縁膜103上に電荷蓄積層204を形成する（図14（B）参照）。図14、図15において、第1の絶縁膜103は、高速動作用の薄膜トランジスタのゲート絶縁膜、メモリトランジスタの電荷蓄積層とゲート電極間に設けられる絶縁膜となる。

## 【0074】

次に、電荷蓄積層204を導電膜102a上に少なくとも残存させるようにエッティングを行い、残存した電荷蓄積層204上に絶縁膜205を形成する（図14（C）参照）。絶縁膜205は、プラズマ処理により電荷蓄積層204を酸化して形成することができる。なお、電荷蓄積層204のエッティングは必ずしも行う必要はない。

20

## 【0075】

次に、導電膜102aと重なるように絶縁膜205上に半導体膜106aを形成し、導電膜102cと重なるように第1の絶縁膜103上に半導体膜106cを形成し、導電膜102a、102cと重ならないように第1の絶縁膜103上に半導体膜106bを形成する（図14（D）参照）。

## 【0076】

次に、半導体膜106a～106c上に第3の絶縁膜107を形成する（図15（A）参照）。ここでは、第3の絶縁膜107は高耐圧用の薄膜トランジスタのゲート絶縁膜となる。

30

## 【0077】

次に、第3の絶縁膜107上に導電膜108を選択的に形成する（図15（B）参照）。導電膜108は高耐圧用の薄膜トランジスタのゲート電極となる。

## 【0078】

その後、図3（A）～（C）まで同様の工程を経ることによって、ボトムゲート型のメモリトランジスタ120a及び高速動作用の薄膜トランジスタ120cと、トップゲート型の高耐圧用の薄膜トランジスタ120bを得ることができる（図15（C）参照）。

## 【0079】

このように、ゲート絶縁膜の膜厚が異なる薄膜トランジスタを設ける場合であっても、メモリトランジスタ120aの第1の絶縁膜103（ゲート電極102aと電荷蓄積層204との間に設けられた第1の絶縁膜103）と薄膜トランジスタ（ここでは高速動作用の薄膜トランジスタ120c）のゲート絶縁膜103を共有して設けることにより、プロセスの簡略化を図ることができる。また、半導体膜に接して形成される不要な絶縁膜のエッティング工程をなくすことによって、半導体膜へのダメージを抑制することができる。

40

## 【0080】

なお、本実施の形態は、本明細書の他の実施の形態で示した半導体装置の構成と適宜組み合わせることができる。

## 【0081】

（実施の形態3）

50

本実施の形態では、上記実施の形態と異なる半導体装置の構成に関して図面を参照して説明する。具体的には、メモリトランジスタ、高耐圧用の薄膜トランジスタに上部ゲート電極を設けた構成に関して説明する。

【0082】

本実施の形態で示す半導体装置は、上記図3に示した半導体装置において、ボトムゲート型のメモリトランジスタ120a及び高耐圧用の薄膜トランジスタ120bに上部電極となる導電膜208を設けた構成となっている（図6（A）参照）。

【0083】

導電膜208を設けることによって、しきい値の制御が可能となり、高速動作と低消費電力化を任意に可変できる。

10

【0084】

もちろん、上記実施の形態2で示した構成において、メモリトランジスタ120aや高耐圧用の薄膜トランジスタ120bに上部電極となる導電膜208を設けた構成としてもよい（図6（B）参照）。

【0085】

次に、ボトムゲート型のメモリトランジスタ120a及び高耐圧用の薄膜トランジスタ120bに上部ゲート電極を形成する方法に関して図7を参照して説明する。

【0086】

まず、上記実施の形態1で示したように図1（A）～図2（C）まで同様に形成した後、導電膜108を選択的にエッチングして半導体膜106a、106b、106cの上方にゲート電極となる導電膜208、108を形成する（図7（A）参照）。

20

【0087】

次に、導電膜108、導電膜208をマスクとして、半導体膜106a～106cに不純物元素を導入することにより、不純物領域110a～110cを形成し、メモリトランジスタ120a、高耐圧用の薄膜トランジスタ120b、高速動作用の薄膜トランジスタ120cを形成する（図7（B）参照）。

【0088】

次に、導電膜108、208を覆うように層間絶縁膜となる絶縁膜111を形成し、絶縁膜111に上にメモリトランジスタ120a、高耐圧用の薄膜トランジスタ120b、高速動作用の薄膜トランジスタ120cのソース電極又はドレイン電極として機能しうる導電膜112を形成する（図7（C）参照）。

30

【0089】

なお、本実施の形態では、メモリトランジスタ及び高耐圧用の薄膜トランジスタの双方に上部電極を設けた構成を示したが、メモリトランジスタ及び高耐圧用の薄膜トランジスタのいずれか一方に上部電極を設けた構成としてもよい。

【0090】

なお、本実施の形態は、本明細書の他の実施の形態で示した半導体装置の構成と適宜組み合わせることができる。

【0091】

（実施の形態4）

40

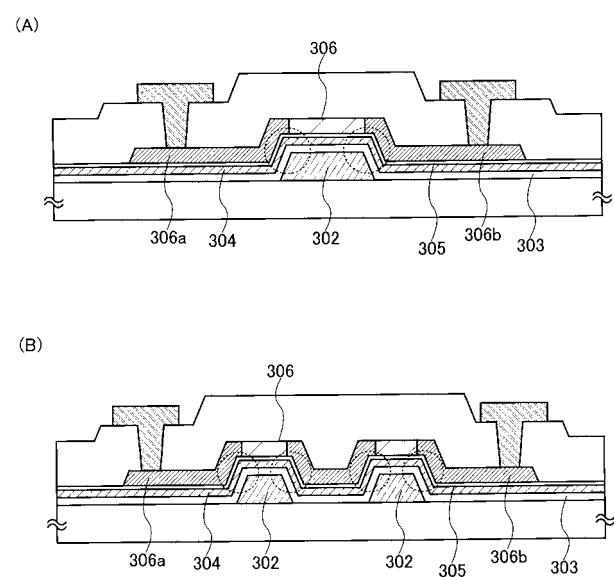

本実施の形態では、上記実施の形態で示したメモリトランジスタの構成に関して説明する。具体的には、ボトムゲート構造で設けられたMONOS型のメモリトランジスタの多値化に関して説明する。

【0092】

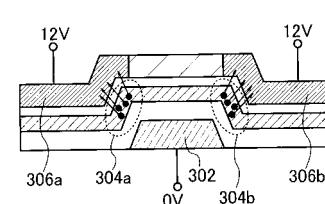

本実施の形態で示すメモリトランジスタは、半導体膜306の下方に設けられたゲート電極302の端部に電界が集中することを利用して、電荷蓄積層304において半導体膜306とゲート電極302の端部との間に設けられた領域に選択的に電荷を注入する（図8（A）参照）。ゲート電極302の両端部への電界の集中を利用することによって、書き込み電圧及び消去電圧を低減することができる。

【0093】

50

以下に、メモリトランジスタの動作について図面を参照して説明する。なお、以下の説明において示す動作電圧の値は、一例であって、その値に限られるわけではない。

【0094】

一般的に、電荷蓄積層304に電子を注入するには、熱電子を利用する方法と、F-N型トンネル電流を利用する方法がある。熱電子を利用する場合には、正の電圧をゲート電極302に印加して、ドレインに高電圧を印加して熱電子を発生させる。それにより、熱電子を電荷蓄積層304に注入することができる。F-N型トンネル電流を利用する場合には、正の電圧をゲート電極302に印加して半導体膜306のチャネル形成領域からF-N型トンネル電流により電荷蓄積層304に電子を注入する。

【0095】

本実施の形態では、ゲート電極302の両端部をそれぞれ利用し、電荷蓄積層304において半導体膜306とゲート電極302の両端部との間に設けられた領域にそれぞれ電子を蓄積させる場合について示す。

【0096】

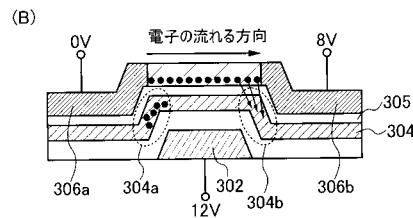

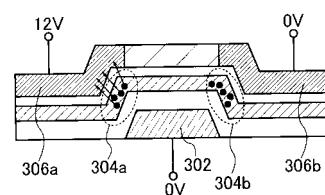

図9(A)は、熱電子により電荷蓄積層304の第1の領域304aに電子を注入するときの印加電圧を示している。例えば、ゲート電極302に正の電圧(8V~14V(ここでは12V))を印加するとともに、半導体膜306の第1の不純物領域306a(ソース領域)は8V、第2の不純物領域306b(ドレイン領域)は0Vとする。その結果、第1の不純物領域306a側に位置するゲート電極302の端部に電界が集中し、半導体膜306のチャネル形成領域を流れる電子は絶縁膜305を介して電荷蓄積層304の第1の領域304aに注入されトラップされる。このように、ゲート電極302の端部への電界の集中を利用することによって、書き込み電圧を低減することができる。

【0097】

電荷蓄積層304の第1の領域304aに電子が保持されている間は、メモリトランジスタのしきい値電圧は正の方向にシフトする。この状態を、第1の状態とすることができる。

【0098】

この第1の状態の検出は、電荷蓄積層304に電荷が保持されていない状態でメモリトランジスタがオンとなるゲート電圧を印加したとき、メモリトランジスタがオンしないことをセンス回路によって検出することで可能である。

【0099】

図9(B)は、熱電子により電荷蓄積層304の第2の領域304bに電子を注入するときの印加電圧を示している。例えば、ゲート電極302に正の電圧(8V~14V(ここでは12V))を印加するとともに、第1の不純物領域306a(ドレイン領域)は0V、第2の不純物領域306b(ソース領域)は8Vとする。その結果、第2の不純物領域306b側に位置するゲート電極302の端部に電界が集中し、半導体膜306のチャネル形成領域を流れる電子は絶縁膜305を介して電荷蓄積層304の第2の領域304bに注入されトラップされる。このように、ゲート電極302の端部への電界の集中を利用することによって、書き込み電圧を低減することができる。

【0100】

電荷蓄積層304の第1の領域304a及び第2の領域304bに電子が保持されている間は、メモリトランジスタのしきい値電圧は図9(A)の状態より正の方向にシフトする。この状態を、第2の状態とすることができる。

【0101】

この第2の状態の検出は、電荷蓄積層304の第1の領域304a、第2の領域304bのいずれか一方に電荷が保持されている状態でメモリトランジスタがオンとなるゲート電圧を印加したとき、メモリトランジスタがオン状態とならないことをセンス回路によって検出することで可能である。

【0102】

図10(A)は、電荷蓄積層304の第1の領域304aから電荷を放出させ、メモリ

10

20

30

40

50

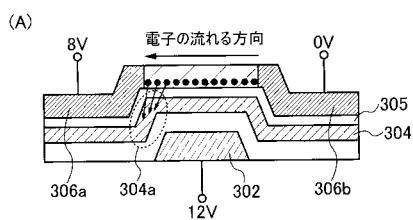

トランジスタからデータを消去する状態を示している。この場合、ゲート電極 302 に 0 V を印加するとともに、半導体膜 306 の第 1 の不純物領域 306a は正の電圧 (8 ~ 14 V)、第 2 の不純物領域 306b は 0 V とする。その結果、第 1 の不純物領域 306a 側に位置するゲート電極 302 の端部に電界が集中し、電荷蓄積層 304 の第 1 の領域 304a に蓄積された電子を第 1 の不純物領域 306a 側に引き抜くことができる。このように、ゲート電極 302 の端部への電界の集中を利用することによって、消去電圧を低減することができる。なお、データを消去する場合には、電荷蓄積層 304 の電子を引き抜くだけでなく、電荷蓄積層 304 へホールを注入することによる電荷の中和も寄与する。

【0103】

また、ゲート電極 302 に 0 V を印加するとともに、半導体膜 306 の第 1 の不純物領域 306a は 0 V、第 2 の不純物領域 306b は正の電圧 (8 ~ 14 V) とすることによって、電荷蓄積層 304 の第 2 の領域 304b から電荷を放出することができる。

【0104】

図 10 (B) は、電荷蓄積層 304 の第 1 の領域 304a 及び第 2 の領域 304b から同時に電荷を放出させ、メモリトランジスタからデータを消去する状態を示している。この場合、ゲート電極 302 に 0 V を印加するとともに、半導体膜 306 の第 1 の不純物領域 306a は正の電圧 (8 ~ 14 V)、第 2 の不純物領域 306b は正の電圧 (8 ~ 14 V) とする。その結果、第 1 の不純物領域 306a 側に位置するゲート電極 302 の端部及び第 2 の不純物領域 306b 側に位置するゲート電極 302 の端部に電界が集中し、電荷蓄積層 304 の第 1 の領域 304a と第 2 の領域 304b に蓄積された電子を第 1 の不純物領域 306a 側、第 2 の不純物領域 306b 側に引き抜くことができる。このように、ゲート電極 302 の端部への電界の集中を利用することによって、消去電圧を低減することができる。

【0105】

上述したように、ボトムゲート構造の MONOS 型のメモリトランジスタにおいて、ゲート電極の端部に集中する電界を利用して電荷蓄積層への電荷の注入、放出を行うことによって、低消費電力化が可能となる。

【0106】

本実施の形態では、メモリトランジスタにおいて 2 値化する場合を示したが、これに限られない。例えば、図 8 (B) に示すようにゲート電極を複数設け、当該ゲート電極の端部の電界集中を利用することにより多値化することが可能となる。

【0107】

なお、本実施の形態は、本明細書の他の実施の形態で示した半導体装置の構成と適宜組み合わせることができる。

【0108】

(実施の形態 5)

本実施の形態では、上記実施の形態で示したメモリトランジスタを備えた非接触でデータの入出力が可能である半導体装置の適用例に関して図面を参照して以下に説明する。非接触でデータの入出力が可能である半導体装置は利用の形態によっては、RFID タグ、ID タグ、IC タグ、IC チップ、RF タグ、無線タグ、電子タグまたは無線チップともよばれる。

【0109】

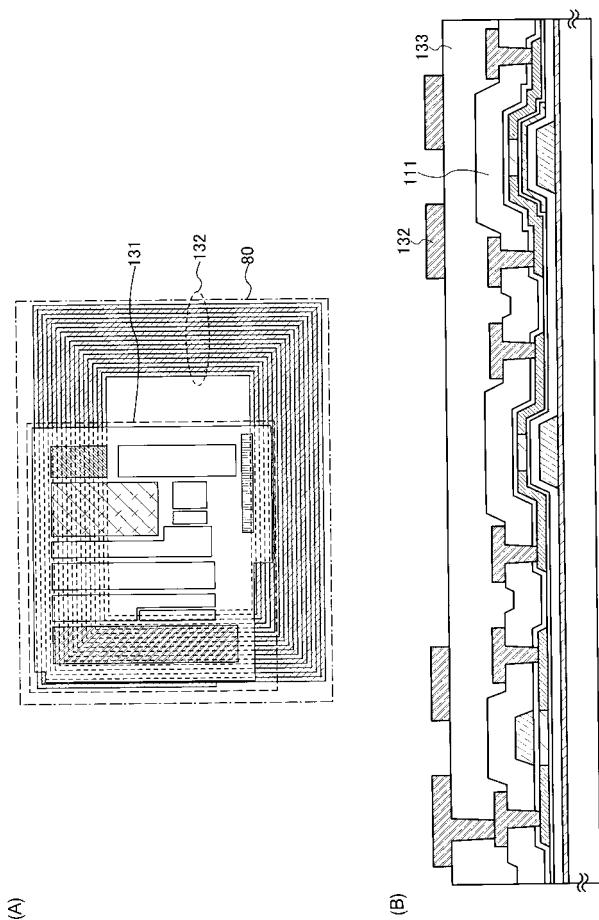

まず、本実施の形態で示す半導体装置の上面構造の一例について、図 11 (A) を参照して説明する。図 11 に示す半導体装置 80 は、上記実施の形態で示したメモリトランジスタや薄膜トランジスタが設けられた薄膜集積回路 131 と、アンテナとして機能する導電膜 132 を含んでいる。アンテナとして機能する導電膜 132 は、薄膜集積回路 131 に電気的に接続されている。

【0110】

また、図 11 (B) に図 11 (A) の断面の模式図を示す。アンテナとして機能する導電膜 132 は、メモリ部を構成するメモリトランジスタやロジック部を構成する薄膜ト

10

20

30

40

50

ンジスタ等の上方に設ければよい。例えば、上記実施の形態で示した構造において、絶縁膜111上に絶縁膜133を介してアンテナとして機能する導電膜132を設けることができる。

#### 【0111】

また、アンテナとして機能する導電膜132は、薄膜集積回路131に対して、重なって設けてもよいし、重ならずに周囲に設ける構造でもよい。また、本実施の形態では、アンテナとして機能する導電膜132をコイル状に設け、電磁誘導方式または電磁結合方式を適用する例を示すが、これに限らずマイクロ波方式を適用することも可能である。マイクロ波方式の場合は、用いる電磁波の波長によりアンテナとして機能する導電膜132の形状を適宜決めればよい。

10

#### 【0112】

半導体装置における信号の伝送方式として、電磁結合方式または電磁誘導方式（例えば13.56MHz帯）を適用する場合には、磁界密度の変化による電磁誘導を利用するため、アンテナとして機能する導電膜を輪状（例えば、ループアンテナ）、らせん状（例えば、スパイラルアンテナ）に形成する。

#### 【0113】

また、半導体装置における信号の伝送方式として、マイクロ波方式（例えば、UHF帯（860～960MHz帯）、2.45GHz帯等）を適用する場合には、信号の伝送に用いる電磁波の波長を考慮してアンテナとして機能する導電膜の長さ等の形状を適宜設定すればよく、例えば、アンテナとして機能する導電膜を線状（例えば、ダイポールアンテナ）、平坦な形状（例えば、パッチアンテナ）またはリボン型の形状等に形成することができる。また、アンテナとして機能する導電膜の形状は線状に限らず、電磁波の波長を考慮して曲線状や蛇行形状またはこれらを組み合わせた形状で設けてもよい。

20

#### 【0114】

アンテナとして機能する導電膜132は、CVD法、スパッタ法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム（Al）、チタン（Ti）、銀（Ag）、銅（Cu）、金（Au）、白金（Pt）ニッケル（Ni）、パラジウム（Pd）、タンタル（Ta）、モリブデン（Mo）から選択された元素、又はこれらの元素を主成分とする合金若しくは化合物で、単層構造又は積層構造で形成する。

30

#### 【0115】

また、アンテナを設ける場合には、1枚の基板上に薄膜集積回路131とアンテナとして機能する導電膜132を直接作り込んで設けてもよいし、薄膜集積回路131とアンテナとして機能する導電膜132を別々の基板上に設けた後に、電気的に接続するように貼り合わせることによって設けてもよい。

#### 【0116】

次に、本実施の形態で示す半導体装置の動作の一例について説明する。

#### 【0117】

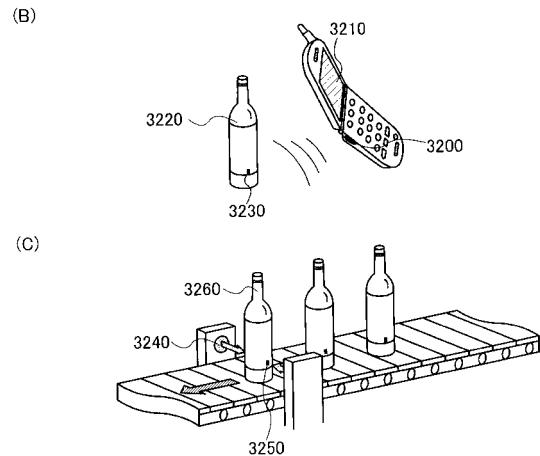

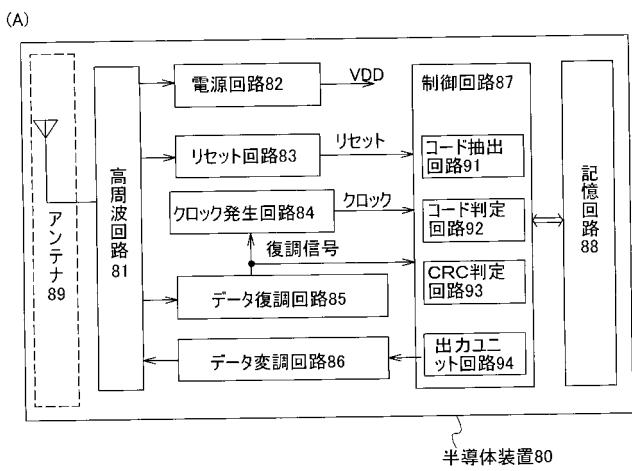

半導体装置80は、非接触でデータを交信する機能を有し、高周波回路81、電源回路82、リセット回路83、クロック発生回路84、データ復調回路85、データ変調回路86、他の回路の制御を行う制御回路87、記憶回路88およびアンテナ89を有している（図12（A））。記憶回路88には、上記実施の形態で示したメモリトランジスタを設けた構成とすることができる。

40

#### 【0118】

高周波回路81はアンテナ89より信号を受信して、データ変調回路86より受信した信号をアンテナ89から出力する回路であり、電源回路82は受信信号から電源電位を生成する回路であり、リセット回路83はリセット信号を生成する回路であり、クロック発生回路84はアンテナ89から入力された受信信号を基に各種クロック信号を生成する回路であり、データ復調回路85は受信信号を復調して制御回路87に出力する回路であり、データ変調回路86は制御回路87から受信した信号を変調する回路である。また、制

50

御回路 8 7 としては、例えばコード抽出回路 9 1、コード判定回路 9 2、C R C 判定回路 9 3 および出力ユニット回路 9 4 が設けられている。なお、コード抽出回路 9 1 は制御回路 8 7 に送られてきた命令に含まれる複数のコードをそれぞれ抽出する回路であり、コード判定回路 9 2 は抽出されたコードとリファレンスに相当するコードとを比較して命令の内容を判定する回路であり、C R C 判定回路 9 3 は判定されたコードに基づいて送信エラー等の有無を検出する回路である。

【 0 1 1 9 】

次に、上述した半導体装置 8 0 の動作の一例について説明する。まず、アンテナ 8 9 により無線信号が受信される。無線信号は高周波回路 8 1 を介して電源回路 8 2 に送られ、高電源電位（以下、V D D と記す）が生成される。V D D は半導体装置 8 0 が有する各回路に供給される。また、高周波回路 8 1 を介してデータ復調回路 8 5 に送られた信号は復調される（以下、復調信号）。さらに、高周波回路 8 1 を介してリセット回路 8 3 およびクロック発生回路 8 4 を通った信号及び復調信号は制御回路 8 7 に送られる。制御回路 8 7 に送られた信号は、コード抽出回路 9 1、コード判定回路 9 2 およびC R C 判定回路 9 3 等によって解析される。そして、解析された信号にしたがって、記憶回路 8 8 内に記憶されている半導体装置 8 0 の情報が出力される。出力された半導体装置 8 0 の情報は出力ユニット回路 9 4 を通って符号化される。さらに、符号化された半導体装置 8 0 の情報はデータ変調回路 8 6 を通って、アンテナ 8 9 を介して送信される。なお、半導体装置 8 0 を構成する複数の回路においては、低電源電位（以下、V S S ）は共通であり、V S S はG N D とすることができる。

10

20

【 0 1 2 0 】

このように、リーダ／ライタから半導体装置 8 0 に信号を送り、当該半導体装置 8 0 から送られてきた信号をリーダ／ライタで受信することによって、半導体装置 8 0 のデータを読み取ることが可能となる。

【 0 1 2 1 】

また、半導体装置 8 0 は、各回路への電源電圧の供給を電源（バッテリー）を搭載せず電磁波により行うタイプとしてもよいし、電源（バッテリー）を搭載して電磁波と電源（バッテリー）により各回路に電源電圧を供給するタイプとしてもよい。

【 0 1 2 2 】

次に、非接触でデータの入出力が可能な半導体装置の使用形態の一例について説明する。表示部 3 2 1 0 を含む携帯端末の側面には、リーダ／ライタ 3 2 0 0 が設けられ、品物 3 2 2 0 の側面には半導体装置 3 2 3 0 が設けられる（図 1 2 ( B )）。品物 3 2 2 0 が含む半導体装置 3 2 3 0 にリーダ／ライタ 3 2 0 0 をかざすと、表示部 3 2 1 0 に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。また、商品 3 2 6 0 をベルトコンベアにより搬送する際に、リーダ／ライタ 3 2 4 0 と、商品 3 2 6 0 に設けられた半導体装置 3 2 5 0 を用いて、該商品 3 2 6 0 の検品を行うことができる（図 1 2 ( C )）。このように、システムに半導体装置を活用することで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。

30

【 0 1 2 3 】

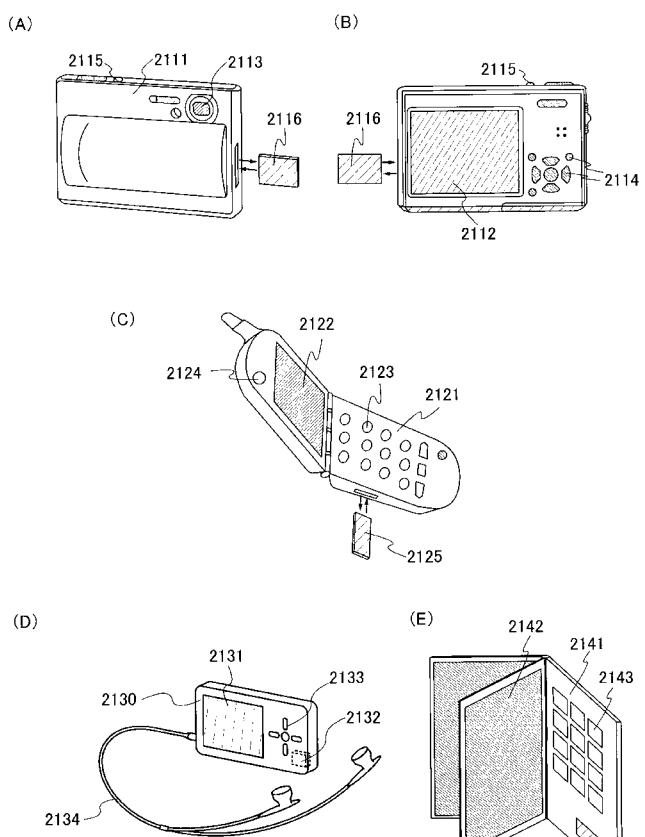

また、上記実施の形態で示したメモリトランジスタを具備する半導体装置は、メモリを具備したあらゆる分野の電子機器に用いることが可能である。例えば、上記実施の形態で示したメモリトランジスタを適用した電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはD V D ( d i g i t a l v e r s a t i l e d i s c ) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。それら電子機器の具体例を図 1 3 に示す。

【 0 1 2 4 】

40

50

図13( A )、( B )は、デジタルカメラを示している。図13( B )は、図13( A )の裏側を示す図である。このデジタルカメラは、筐体2111、表示部2112、レンズ2113、操作キー2114、シャッターボタン2115などを有する。また、取り出し可能な不揮発性メモリ2116を備えており、当該デジタルカメラで撮影したデータをメモリ2116に記憶させておく構成となっている。上記実施の形態で示したメモリトランジスタをメモリ2116に適用することができる。

【0125】

また、図13( C )は、携帯電話を示しており、携帯端末の1つの代表例である。この携帯電話は筐体2121、表示部2122、操作キー2123などを含む。また、携帯電話は、取り出し可能な不揮発性メモリ2125を備えており、当該携帯電話の電話番号等のデータ、映像、音楽データ等をメモリ2125に記憶させ再生することができる。上記実施の形態で示したメモリトランジスタをメモリ2125に適用することができる。

10

【0126】

また、図13( D )は、デジタルプレーヤーを示しており、オーディオ装置の1つの代表例である。図13( D )に示すデジタルプレーヤーは、本体2130、表示部2131、メモリ部2132、操作部2133、イヤホン2134等を含んでいる。なお、イヤホン2134の代わりにヘッドホンや無線式イヤホンを用いることができる。メモリ部2132は、上記実施の形態で示したメモリトランジスタを用いることができる。例えば、記録容量が20～200ギガバイト( GB )のNAND型不揮発性メモリを用い、操作部2133を操作することにより、映像や音声( 音楽 )を記録、再生することができる。なお、表示部2131は黒色の背景に白色の文字を表示することで消費電力を抑えられる。これは携帯型のオーディオ装置において特に有効である。

20

【0127】

また、図13( E )は、電子ブック( 電子ペーパーともいう )を示している。この電子ブックは、本体2141、表示部2142、操作キー2143、メモリ部2144を含んでいる。またモデムが本体2141に内蔵されていてもよいし、無線で情報を送受信できる構成としてもよい。メモリ部2144は、上記実施の形態で示したメモリトランジスタを用いることができる。例えば、記録容量が20～200ギガバイト( GB )のNAND型不揮発性メモリを用い、操作キー2143を操作することにより、映像や音声( 音楽 )を記録、再生することができる。

30

【0128】

以上の様に、上記実施の形態で示したメモリトランジスタの適用範囲は極めて広く、メモリを有するものであればあらゆる分野の電子機器に用いることが可能である。

【0129】

なお、本実施の形態は、本明細書の他の実施の形態と自由に組み合わせて行うことができる。

【図面の簡単な説明】

【0130】

【図1】本発明の半導体装置の作製方法の一例を示す図。

40

【図2】本発明の半導体装置の作製方法の一例を示す図。

【図3】本発明の半導体装置の作製方法の一例を示す図。

【図4】本発明の半導体装置の作製方法の一例を示す図。

【図5】本発明の半導体装置の作製方法の一例を示す図。

【図6】本発明の半導体装置の一例を示す図。

【図7】本発明の半導体装置の作製方法の一例を示す図。

【図8】本発明の半導体装置の一例を示す図。

【図9】本発明の半導体装置の動作の一例を示す図。

【図10】本発明の半導体装置の動作の一例を示す図。

【図11】本発明の半導体装置の使用形態の一例を示す図。

【図12】本発明の半導体装置の使用形態の一例を示す図。

50

【図13】本発明の半導体装置の使用形態の一例を示す図。

【図14】本発明の半導体装置の作製方法の一例を示す図。

【図15】本発明の半導体装置の作製方法の一例を示す図。

【符号の説明】

【0131】

|         |            |    |

|---------|------------|----|

| 8 0     | 半導体装置      |    |

| 8 1     | 高周波回路      |    |

| 8 2     | 電源回路       |    |

| 8 3     | リセット回路     |    |

| 8 4     | クロック発生回路   | 10 |

| 8 5     | データ復調回路    |    |

| 8 6     | データ変調回路    |    |

| 8 7     | 制御回路       |    |

| 8 8     | 記憶回路       |    |

| 8 9     | アンテナ       |    |

| 9 1     | コード抽出回路    |    |

| 9 2     | コード判定回路    |    |

| 9 3     | C R C 判定回路 |    |

| 9 4     | 出力ユニット回路   |    |

| 1 0 0   | 基板         | 20 |

| 1 0 1   | 絶縁膜        |    |

| 1 0 3   | 絶縁膜        |    |

| 1 0 4   | 電荷蓄積層      |    |

| 1 0 5   | 絶縁膜        |    |

| 1 0 6   | 半導体膜       |    |

| 1 0 7   | 絶縁膜        |    |

| 1 0 8   | 導電膜        |    |

| 1 0 9   | レジスト       |    |

| 1 1 1   | 絶縁膜        |    |

| 1 1 2   | 導電膜        | 30 |

| 1 3 1   | 薄膜集積回路     |    |

| 1 3 2   | 導電膜        |    |

| 1 3 3   | 絶縁膜        |    |

| 2 0 3   | 絶縁膜        |    |

| 2 0 4   | 電荷蓄積層      |    |

| 2 0 5   | 絶縁膜        |    |

| 2 0 8   | 導電膜        |    |

| 3 0 1   | ゲート電極      |    |

| 3 0 2   | ゲート電極      |    |

| 3 0 4   | 電荷蓄積層      | 40 |

| 3 0 5   | 絶縁膜        |    |

| 3 0 6   | 半導体膜       |    |

| 1 0 2 a | 導電膜        |    |

| 1 0 2 b | 導電膜        |    |

| 1 0 2 c | 導電膜        |    |

| 1 0 6 a | 半導体膜       |    |

| 1 0 6 b | 半導体膜       |    |

| 1 0 6 c | 半導体膜       |    |

| 1 1 0 a | 不純物領域      |    |

| 1 1 0 c | 不純物領域      | 50 |

|         |           |    |

|---------|-----------|----|

| 1 2 0 a | メモリトランジスタ |    |

| 1 2 0 b | 薄膜トランジスタ  |    |

| 1 2 0 c | 薄膜トランジスタ  |    |

| 2 1 1 1 | 筐体        |    |

| 2 1 1 2 | 表示部       |    |

| 2 1 1 3 | レンズ       |    |

| 2 1 1 4 | 操作キー      |    |

| 2 1 1 5 | シャッター ボタン |    |

| 2 1 1 6 | メモリ       | 10 |

| 2 1 2 1 | 筐体        |    |

| 2 1 2 2 | 表示部       |    |

| 2 1 2 3 | 操作キー      |    |

| 2 1 2 5 | メモリ       |    |

| 2 1 3 0 | 本体        |    |

| 2 1 3 1 | 表示部       |    |

| 2 1 3 2 | メモリ部      |    |

| 2 1 3 3 | 操作部       |    |

| 2 1 3 4 | イヤホン      |    |

| 2 1 4 1 | 本体        |    |

| 2 1 4 2 | 表示部       | 20 |

| 2 1 4 3 | 操作キー      |    |

| 2 1 4 4 | メモリ部      |    |

| 3 0 4 a | 領域        |    |

| 3 0 4 b | 領域        |    |

| 3 0 6 a | 不純物領域     |    |

| 3 0 6 b | 不純物領域     |    |

| 3 2 0 0 | リーダ / ライタ |    |

| 3 2 1 0 | 表示部       |    |

| 3 2 2 0 | 品物        |    |

| 3 2 3 0 | 半導体装置     | 30 |

| 3 2 4 0 | リーダ / ライタ |    |

| 3 2 5 0 | 半導体装置     |    |

| 3 2 6 0 | 商品        |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

【図 1 4】

【図 1 5】

## フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

H 01 L 29/786 (2006.01)

H 01 L 27/08 (2006.01)

F ターム(参考) 5F048 AA07 AA09 AB01 AC01 AC10 BA16 BB01 BB08 BB09 BB10

BB11 BB12 BB16 BB17 BC06 BF07 BF16

5F083 EP02 EP18 EP22 ER02 ER15 HA10 JA04 JA19 JA36 JA37

JA39 JA56 JA58 PR43 PR44 PR45 PR53 PR54 PR55 ZA12

ZA21

5F101 BA01 BA45 BB02 BC02 BC11 BD02 BD30 BE02 BE05 BE07

BF05 BH21

5F110 AA16 BB08 CC01 CC08 DD01 DD02 DD13 DD14 DD15 EE02

EE03 EE04 EE05 EE06 EE09 EE14 EE30 FF02 FF03 FF04

FF09 FF22 FF26 FF28 FF29 GG02 GG13 GG24 GG43 GG45

GG47 HJ01 HL02 HL03 HL04 HL08 HL23 HL24 NN02 NN03

NN22 NN23 NN24 NN33 NN34 NN35 NN78 PP01 PP02 PP03

PP34 QQ11