(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5089336号

(P5089336)

(45) 発行日 平成24年12月5日(2012.12.5)

(24) 登録日 平成24年9月21日(2012.9.21)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

F

H01L 23/12

W

請求項の数 4 (全 8 頁)

(21) 出願番号 特願2007-280695 (P2007-280695)

(22) 出願日 平成19年10月29日 (2007.10.29)

(65) 公開番号 特開2009-111082 (P2009-111082A)

(43) 公開日 平成21年5月21日 (2009.5.21)

審査請求日 平成22年8月9日 (2010.8.9)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100099759

弁理士 青木 篤

(74) 代理人 100077517

弁理士 石田 敏

(74) 代理人 100087413

弁理士 古賀 哲次

(74) 代理人 100111903

弁理士 永坂 友康

(72) 発明者 白石 晶紀

長野県長野市小島田町80番地 新光電気

工業株式会社内

最終頁に続く

(54) 【発明の名称】パッケージ用シリコン基板

## (57) 【特許請求の範囲】

## 【請求項 1】

電子装置チップを収容するキャビティの底面から基板裏面まで貫通する貫通孔が形成されるパッケージ用シリコン基板において、

前記貫通孔に充填される貫通電極であって、キャビティ底面側の端部が前記キャビティの底面よりも低い位置にある貫通電極と、

前記貫通電極のキャビティ底面側の端部に形成される金属層と、

前記金属層から前記キャビティ底面までの前記貫通孔の空間に充填されるワイヤボンディングの充填導体と、

を有することを特徴とするパッケージ用シリコン基板。

10

## 【請求項 2】

前記金属層は、前記キャビティ底面から貫通孔の内壁を介して前記貫通電極のキャビティ底面側の端部まで連続的に形成される薄膜配線である請求項 1 に記載のパッケージ用シリコン基板。

## 【請求項 3】

前記充填導体は、ワイヤボンディングの導体により形成された金パンプである請求項 1 又は請求項 2 に記載のパッケージ用シリコン基板。

## 【請求項 4】

前記充填導体と電子装置チップの電極とを接続するワイヤボンディング配線をさらに有する請求項 1 に記載のパッケージ用シリコン基板。

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、パッケージ用シリコン基板に関し、特に、電子装置チップを収容するためのキャビティを備えたパッケージ用シリコン基板に関する。

**【背景技術】****【0002】**

半導体装置を用いた種々の電子機器の小型化・薄型化を進めるために、半導体装置に用いる半導体パッケージも小型化・薄型化に対応する必要がある。特に薄型化のために、キャビティ付きのパッケージ用シリコン基板が用いられている（例えば特許文献1参照）。すなわち、基板表面からエッティング等により掘り込んだキャビティ内に、レーザダイオード（LD）、フォトダイオード（PD）、発光ダイオード（LED）、マイクロエレクトロメカニカルシステム（MEMS）などの電子装置チップを搭載することで、電子装置チップの高さの一部または全部を基板で吸収し、パッケージを薄型化する。これにより、厚さの選択肢が規格範囲内に限られている市販のシリコンウェーハを用い、顧客の要求仕様に沿って薄型化したパッケージを提供できる。

10

**【0003】**

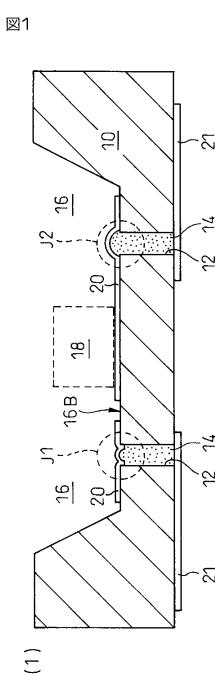

図1(1)に示すように、シリコン基板10を厚さ方向に貫通する貫通孔12をメッキ等により充填して形成された貫通電極14が、キャビティ16内に実装した電子装置チップ18の端子から外部への引き出し線として機能する。キャビティ底面16B上にスパッタや蒸着などで形成した薄膜配線20が貫通電極14との結線部J1、J2を含めてパターニングされている。貫通電極14の外部露出端にはパッケージをマザーボード等に実装するためのパッドを含む裏配線21が形成されている。

20

**【0004】**

図1(2)、図1(3)に示すように、キャビティ16内にメッキ等により形成された貫通電極14の端部T1、T2は、形成プロセスの許容範囲内でキャビティ底面16Bから貫通孔12内へ窪んだり（T1）、逆にキャビティ底面16Bから突き出たり（T2）した状態となる。しかし、キャビティ底面16Bは研磨による平坦化処理を施せないので、貫通電極端部T1、T2の凹凸状態が残ったまま、その上から薄膜配線20を形成せざるを得ない。

30

**【0005】**

図1(2)に示すように、貫通電極端部T1がキャビティ底面16Bから貫通孔12内へ窪んだ状態の結線部J1の場合、端部T1と貫通孔12の側壁とで形成されるコーナー部K1では、スパッタや蒸着による堆積が少ないため、形成される薄膜配線20の膜厚が薄く、断線し易い。

**【0006】**

また、図1(3)に示すように、貫通電極端部T2がキャビティ底面16Bから突き出した状態の結線部J2の場合、端部T2が貫通孔12の開口周縁に傘状に張り出した部分K2では、貫通電極材料とシリコン基板との熱膨張差等による歪が集中し、断線し易い。

40

**【0007】**

このように従来は、キャビティ底面16Bにおける貫通電極14と薄膜配線20との結線部J1、J2で断線が発生し易いという問題があった。

**【0008】**

【特許文献1】特開2007-208041号公報

**【発明の開示】****【発明が解決しようとする課題】****【0009】**

本発明は、キャビティ底面における貫通電極と薄膜配線との断線発生を防止したパッケージ用シリコン基板を提供することを目的とする。

**【課題を解決するための手段】**

50

## 【0010】

上記の目的を達成するために、本発明によれば、電子装置チップを収容するキャビティの底面から基板裏面まで貫通する貫通孔内を充填する貫通電極を備え、貫通電極のキャビティ底面側の端部は、電子装置チップを含む電気回路を構成する配線との結線部を有するパッケージ用シリコン基板において、

(1) 上記配線として薄膜配線を含み、上記結線部は該薄膜配線に接合した導体で補強され、かつ／または

(2) 上記配線としてワイヤボンディング部を含み、上記結線部は貫通電極のキャビティ底面側の端部とのワイヤボンディングにより形成されていることを特徴とするパッケージ用シリコン基板が提供される。 10

## 【発明の効果】

## 【0011】

本発明においては(1)結線部は該薄膜配線に接合した導体で補強され、かつ／または(2)結線部は貫通電極のキャビティ底面側の端部とのワイヤボンディングにより形成されていることにより、結線部での断線を防止することができる。

## 【発明を実施するための最良の形態】

## 【0012】

## 〔実施形態1〕

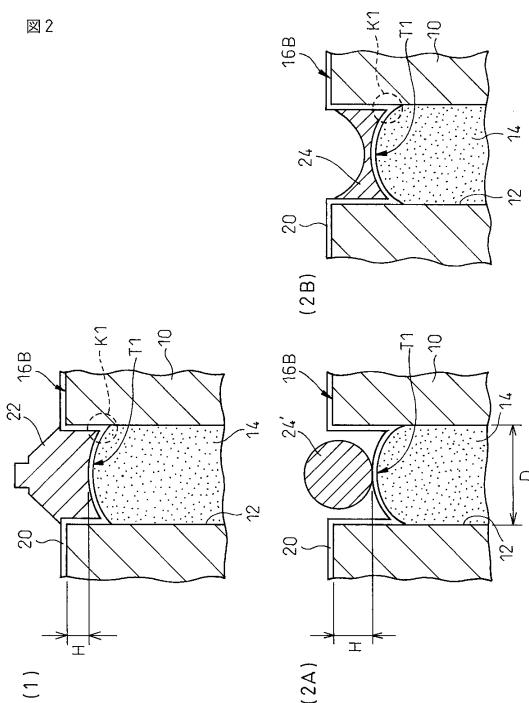

図2に、本発明の一実施形態によるパッケージ用シリコン基板の結線部を示す。図示したシリコン基板10は、図1(1)に示したものと同様にキャビティ16を備えたシリコン基板10であるが、キャビティ16内の貫通電極14と配線との結線部に本発明を適用してある。 20

## 【0013】

図2(1)に示した結線部では、貫通電極14のキャビティ底面16B側の端部T1はキャビティ底面16Bよりも低い位置にある。キャビティ底面16Bから貫通電極端部T1までの深さHは例えば20μm程度である。薄膜配線20がキャビティ底面16Bから貫通孔12の内壁を介して貫通電極14の端部T1までを連続的に覆って形成されている。ワイヤボンディングのファーストボンディングにより形成された金バンプ22が、キャビティ底面16Bから貫通電極端部T1までの貫通孔12内の空間を充填して薄膜配線20に接合して一体の導体を形成し、貫通電極端部T1と薄膜配線20との結線部を補強している。 30

## 【0014】

薄膜配線20はPVD等により製膜された1μm程度あるいはそれ以下の厚さであり、特にコーナー部K1では薄くなるため機械的な強度が極めて低いため、従来はコーナー部K1での断線が発生し易かった。

## 【0015】

図2(1)の結線部は、ファーストボンディングによる金バンプ22が、貫通電極端部T1より上の貫通孔12内を充填しつつ薄膜配線20と強固に接合することにより、薄膜配線20のみから成る従来の結線部(図1(2))に比べて遙かに高い機械的強度が得られるので、特にコーナー部K1でも十分な機械的強度が確保され、断線の発生が防止される。 40

## 【0016】

図2(2A)～(2B)に示した結線部では、図2(1)の結線部と同様に貫通電極14のキャビティ底面16B側の端部T1はキャビティ底面16Bよりも低い位置にあり、薄膜配線20がキャビティ底面16Bから貫通孔12の内壁を介して貫通電極14の端部T1までを連続的に覆って形成されている。ただし、図2(1)の金バンプ22の代わりに、図2(2A)のようにキャビティ底面16Bから貫通電極端部T1までの貫通孔12内の空間にはんだボール24'を配置し、これをリフローして図2(2B)のように形成したはんだリフロー部24が、上記空間を充填して薄膜配線20に接合して一体の導体を形成し、貫通電極端部T1と薄膜配線20との結線部を補強している。はんだボール24 50

’の直径d、貫通孔12の内径D、キャビティ底面16Bから貫通電極端部T1までの深さHは、d < D、H > d / 2の関係にある。

【0017】

図2(2B)の結線部は、はんだリフロー部24が、図2(1)の金パンプと同様に、貫通電極端部T1より上の貫通孔12内を充填しつつ薄膜配線20と強固に接合していることにより、薄膜配線20のみから成る従来の結線部(図1(2))に比べて遙かに高い機械的強度が得られるので、特にコーナー部K1でも十分な機械的強度が確保され、断線の発生が防止される。

【0018】

本実施形態および以下の実施形態において、各部の寸法の一例は下記のとおりである。

10

【0019】

シリコン基板10として、市販のシリコンウェーハを用いると、SEMI規格、JEIDA規格等により厚さが規定されており、例えば6インチ、8インチ、12インチの各ウェーハの厚さは625μm、725μm、775μmと規定されている。

【0020】

このように厚さが規定されている市販ウェーハを用いたシリコン基板10にエッティング等により掘り込むキャビティ16は、実際に用いたウェーハの規格厚さに応じて深さが制限される。また、ウェーハの裏面は梨地状であるため研磨が必要であり、研磨代の分だけ更に薄くなる。例えば8インチウェーハ(規格厚さ725μm)を用いたシリコン基板10の場合、裏面研磨後の厚さは650~675μm程度となるため、キャビティ深さは100~600μm程度の範囲である。

20

【0021】

〔実施形態2〕

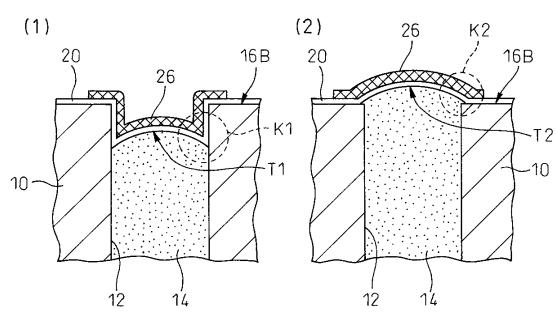

図3に、本発明の一実施形態によるパッケージ用シリコン基板の結線部を示す。図示したシリコン基板10は、図1(1)に示したものと同様にキャビティ16を備えたシリコン基板10であるが、キャビティ16内の貫通電極14と配線との結線部に本発明を適用してある。

【0022】

図3(1)に示した結線部では、貫通電極14のキャビティ底面16B側の端部T1はキャビティ底面16Bよりも低い位置にあり、図3(2)に示した結線部では、貫通電極14のキャビティ底面16B側の端部T2はキャビティ底面16Bよりも高い位置にある。いずれの場合も、貫通電極14のキャビティ底面16B側の端部T1、T2とその周囲の薄膜配線20とを連続的に覆って厚膜配線26が形成されている。厚膜配線26は、薄膜配線20をシード層とする電解めっきにより厚さ5~10μmに形成され、厚さ1μm程度あるいはそれ以下の薄膜配線20と貫通電極端部T1、T2との結線部を補強している。

30

【0023】

厚膜配線26は薄膜配線20と強固に接合しており、薄膜配線20のみから成る従来の結線部(図1(2))に比べて遙かに高い機械的強度が得られるので、コーナー部K1あるいは傘状張り出し部K2においても、十分な機械的強度が確保され、断線が防止される。

40

【0024】

〔実施形態3〕

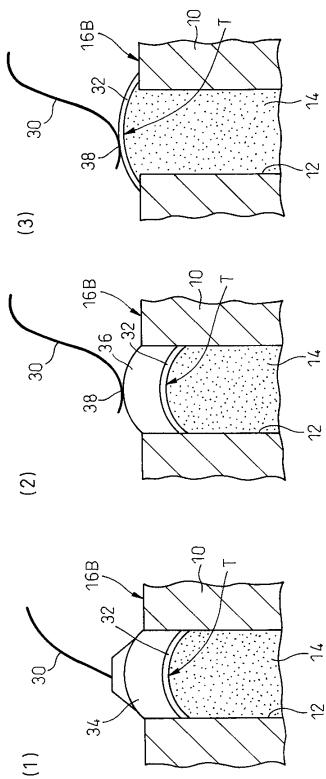

図4に、本発明の一実施形態によるパッケージ用シリコン基板の結線部を示す。図示したシリコン基板10は、図1(1)に示したものと同様にキャビティ16を備えたシリコン基板10であるが、キャビティ16内の貫通電極14と配線との結線部に本発明を適用してある。

【0025】

図4に示した結線部では、上記配線としてワイヤボンディング部30を含み、結線部は貫通電極14のキャビティ底面16B側の端部Tとのワイヤボンディングにより形成され

50

ている。

【0026】

図4(1)の結線部では、貫通電極14のキャビティ底面16B側の端部Tはキャビティ底面16Bよりも低い位置にあり、貫通孔12内の端部Tより上側にある空間を充填し且つ端部Tに接合したファーストボンディング部34により、ワイヤボンディング配線30と端部Tとの結線部が形成されている。ただし、ボンディング前に貫通電極端部T上に基板裏面側端部(図示せず)をシードとする電解めっきによりNi/Au等のメタル層32を形成し、その上にファーストボンディングを行なう。

【0027】

ワイヤボンディング配線30の図示しない他端は一般に電子装置チップの電極に接続されている。

【0028】

図4(1)の結線部は、ファーストボンディングにより、配線30が貫通電極端部Tに強固に接続されており、従来のような断線が発生する虞がない。

【0029】

図4(2)の結線部では、図4(1)と同様に貫通電極14のキャビティ底面16B側の端部Tはキャビティ底面16Bよりも低い位置にある。貫通孔12内の端部Tより上側にある空間を充填する金バンプ36の上端に接合したセカンドボンディング部38により、ワイヤボンディング配線30と端部Tとの結線部が形成されている。金バンプ36の形成は、先ず貫通電極端部T上に基板裏面側端部(図示せず)をシードとする電解めっきによりNi/Au等のメタル層を形成し、このメタル層上に電解金めっきすることにより行なう。

【0030】

ボンディングワイヤ30の図示しない他端は一般に電子装置チップの電極に接続されている。

【0031】

図4(2)の結線部は、電解めっきにより形成されたメタル層32および金バンプ36と、金バンプ36へのセカンドボンディングとにより、配線30が貫通電極端部Tに強固に接続されており、従来のような断線が発生する虞がない。

【0032】

図4(3)の結線部では、貫通電極14のキャビティ底面16B側の端部Tはキャビティ底面16Bより高い位置にあり、端部Tに接合したセカンドボンディング部38により、ワイヤボンディング配線30と端部Tとの結線部が形成されている。ただし、ボンディング前に貫通電極端部T上に基板裏面側端部(図示せず)をシードとする電解めっきによりNi/Au等のメタル層32を形成し、その上にセカンドボンディングを行なう。

【0033】

ボンディングワイヤ30の図示しない他端は一般に電子装置チップの電極に接続されている。

【0034】

図4(3)の結線部は、電解めっきにより形成されたメタル層32と、メタル層32へのセカンドボンディングとにより、配線30が貫通電極端部Tに強固に接続されており、従来のような断線が発生する虞がない。

【産業上の利用可能性】

【0035】

本発明によれば、キャビティ底面における貫通電極と薄膜配線との断線発生を防止したパッケージ用シリコン基板が提供される。

【図面の簡単な説明】

【0036】

【図1】従来のパッケージ用シリコン基板の断面図。

【図2】本発明の実施形態1によるパッケージ用シリコン基板の結線部の断面図。

10

20

30

40

50

【図3】本発明の実施形態2によるパッケージ用シリコン基板の結線部の断面図。

【図4】本発明の実施形態3によるパッケージ用シリコン基板の結線部の断面図。

【符号の説明】

【0037】

10 10 シリコン基板

12 貫通孔

14 貫通電極

16 キャビティ

16B キャビティ底面

18 電子装置チップ

20 薄膜配線

21 裏配線

22 金バンプ

24 はんだリフロー部

24' はんだボール

26 厚膜配線

30 ワイヤボンディング配線

32 メタル層

34 ファーストボンディング部

36 金バンプ

38 セカンドボンディング部

T1、T2、T 貫通電極14のキャビティ底面16B側の端部

J1、J2 結線部

K1 コーナー部

K2 傘状張出部

【図1】

【図2】

【図3】

図3

【図4】

図4

---

フロントページの続き

(72)発明者 村山 啓

長野県長野市小島田町 80 番地 新光電気工業株式会社内

(72)発明者 田口 裕一

長野県長野市小島田町 80 番地 新光電気工業株式会社内

(72)発明者 春原 昌宏

長野県長野市小島田町 80 番地 新光電気工業株式会社内

(72)発明者 東 光敏

長野県長野市小島田町 80 番地 新光電気工業株式会社内

審査官 宮本 靖史

(56)参考文献 特開平04-064254 (JP, A)

特開2007-208041 (JP, A)

特開2002-176070 (JP, A)

特開2005-310934 (JP, A)

特開2002-261204 (JP, A)

特表2006-502564 (JP, A)

特開平09-036168 (JP, A)

特開2002-043456 (JP, A)

特開2002-190544 (JP, A)

特開平05-145230 (JP, A)

特開2005-093513 (JP, A)

特開2006-287085 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| H 01 L | 23 / 12 |

| H 01 L | 21 / 60 |

| H 05 K | 1 / 11  |

| H 05 K | 3 / 40  |