(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2015/200292 A1

(43) International Publication Date

30 December 2015 (30.12.2015)

WIPO | PCT

(51) International Patent Classification:

H04L 25/02 (2006.01)

(21) International Application Number:

PCT/US2015/037132

(22) International Filing Date:

23 June 2015 (23.06.2015)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

14/315,142 25 June 2014 (25.06.2014) US

(71) Applicant: QUALCOMM INCORPORATED [US/US];

Attn: International IP Administration, 5775 Morehouse

Drive, San Diego, CA 92121-1714 (US).

(72) Inventors: PANDEY, Shree, Krishna; 5775 Morehouse

Drive, San Diego, CA 92121-1714 (US). KUNDU, Arun,

Chandra; 5775 Morehouse Drive, San Diego, CA 92121-

1714 (US). WILEY, George, Alan; 5775 Morehouse

Drive, San Diego, CA 92121-1714 (US). LEE, Chulkyu;

5775 Morehouse Drive, San Diego, CA 92121-1714 (US).

(74) Agent: LOZA, Julio; Loza & Loza, LLP, 305 North

Second Avenue #127, Upland, CA 91786 (US).

(81) Designated States (unless otherwise indicated, for every

kind of national protection available): AE, AG, AL, AM,

AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY,

BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM,

DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT,

HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR,

KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG,

MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM,

PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC,

SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN,

TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every

kind of regional protection available): ARIPO (BW, GH,

GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ,

TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU,

TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE,

DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU,

LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK,

SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ,

GW, KM, ML, MR, NE, SN, TD, TG).

#### Declarations under Rule 4.17:

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### Published:

- with international search report (Art. 21(3))

(54) Title: MULTI-WIRE SIGNALING WITH MATCHED PROPAGATION DELAY AMONG WIRE PAIRS

FIG. 4

(57) **Abstract:** In a multi-wire channel that includes at least three wires, each unique wire pair of the multi-wire channel has approximately the same signal propagation time. In this way, jitter can be mitigated in the multi-wire channel for signaling where, for a given data transfer, a differential signal is transmitting on a particular pair of the wires and every other wire is floating. In some implementations, matching of the signal propagation times involves providing additional delay for at least one of the wires. The additional delay is provided using passive signal delay techniques and/or active signal delay techniques.

WO 2015/200292 A1

## MULTI-WIRE SIGNALING WITH MATCHED PROPAGATION DELAY AMONG WIRE PAIRS

### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application claims priority to and the benefit of U.S. non-provisional application no. 14/315,142 filed in the U.S. Patent Office on June 25, 2014, the entire content of which is incorporated herein by reference.

### TECHNICAL FIELD

**[0002]** The following relates generally to electrical signaling and, more specifically, but not exclusively, to multi-wire signaling.

### BACKGROUND

**[0003]** In some electronic systems, signaling between electrical components flows through wires, sometimes referred to as traces, conductors, or electrical paths, on or within printed circuit boards (PCBs), integrated circuits (ICs), or other structures of the electronic system. Conventionally, a signal is carried over a single wire or, for a differential signal, a pair of wires.

**[0004]** Recently, multi-wire signaling schemes (i.e., signaling over more than two wires) have been proposed. For example, C-PHY is a mobile device communication interface for the Mobile Industry Processor Interface (MIPI) Alliance Specification. C-PHY uses a three phase channel (referred to as a “trio”) to transmit data. That is, in contrast with conventional physical interfaces (PHYS) that use a single wire or a differential wire pair for a given channel, a C-PHY channel employs three wires (also referred to as “lanes”). For a given data transmission (e.g., of a bit or symbol), two of the wires are used (active) while the third wire is in a high impedance state (e.g., floating). Over a series of data transmissions, different pairs of the three wires are used to transmit the data.

**[0005]** Multi-wire signaling may be subject to signal transmission issues such as jitter. Jitter is the undesired deviation from true periodicity of an assumed periodic signal in data transmission. For example, over a series of symbol transmissions, there may be timing skew between the symbols when they are received at a receiver. This skew manifests itself as jitter. In view of the above, a need exists for improved circuit

techniques for addressing jitter or other similar transmission issues in wire-based signaling.

### BRIEF SUMMARY OF SOME EXAMPLES

**[0006]** The following summarizes some aspects of the disclosure to provide a basic understanding of such aspects. This summary is not an extensive overview of all contemplated features of the disclosure, and is intended neither to identify key or critical elements of all aspects of the disclosure nor to delineate the scope of any or all aspects of the disclosure. Its sole purpose is to present some concepts of one or more aspects of the disclosure in a summary form as a prelude to the more detailed description that is presented later.

**[0007]** Various aspects of the disclosure provide for multi-wire signaling where each unique wire pair of the n-wires of a multi-wire channel has approximately the same signal propagation time (e.g., within a threshold margin). Here, “n” is three or more.

**[0008]** In accordance with some aspects of the disclosure, matched signal propagation times for different wire pairs are employed in multi-wire signaling where different wire pairs are used for different data transmissions. In such a multi-wire configuration, the distance between one pair of wires can be different from the distance between another pair of wires. Thus, a differential signal on one wire pair may travel at a different velocity than a differential signal on the other wire pair, resulting in jitter at the receiver. However, by matching the signal propagation time for each wire pair in accordance with the teachings herein, signal jitter that could otherwise result from this unequal spacing between wire pairs is mitigated.

**[0009]** The disclosure relates in some aspects to providing additional delay for one or more of the wires of a multi-wire channel. For example, for a multi-wire channel employing three wires that are routed side-by-side, additional delay is provided for the middle wire to balance the signal propagation times for the three unique wire pairs of this channel.

**[0010]** In some implementations, additional delay is provided for a wire by adapting the physical properties for the wire. For example, the wire can have a longer length than the other wires. Other physical properties that could be adapted to provide the desired delay include wire width, wire thickness, dielectric constant, and distance to ground plane.

**[0011]** In some implementations, additional delay is added for a wire by incorporating a delay element into the signaling path. For example, a delay element could be added along the path (e.g., along a wire of a PCB or integrated circuit) or in an I/O circuit (e.g., driver or receiver). Such a delay element can be passive (e.g., a wire of a specified length) or active (e.g., employing transistors).

**[0012]** In implementations that employ an active delay element, the delay can be dynamically adjusted based on initial design criteria and/or based on one or more operating factors. These operating factors can include calibration feedback, signal frequency, signal rise time, signal fall times, or path length.

**[0013]** Further aspects of the disclosure provide an apparatus for multi-wire signaling. The apparatus including: a plurality of wires comprising at least three wires; and at least one delay element coupled to at least one of the wires, each delay element to provide an amount of signal delay such that signal propagation times associated with each wire pair of the plurality of wires are equal to one another within a margin of error.

**[0014]** Examples of other aspects of the disclosure related to the above apparatus follow. In some aspects, each delay element includes a passive delay structure. In some aspects, each delay element includes a wire of a defined length such that an overall length of each of the at least one wires is longer than a length of each of the wires that is not coupled to a delay element. In some aspects, each delay element includes an active delay device. In some aspects, each delay element includes a programmable delay device; and the apparatus further includes a delay controller to generate at least one control signal to control a delay of each delay element.

**[0015]** In some aspects, the at least one control signal controls the delay of each delay element such that the signal propagation times associated with each wire pair of the plurality of wires are equal to one another within the margin of error. In some aspects, the delay controller is further configured to generate the at least one control signal based on lengths of the wires. In some aspects, the delay controller is further configured to generate the at least one control signal based on the signal propagation times associated with the wire pairs. In some aspects, the delay controller is further configured to generate the at least one control signal based on a signal frequency of signals carried by the wires. In some aspects, the delay controller is further configured to generate the at least one control signal based on an application for which signals are transmitted over the wires. In some aspects, the delay controller is further configured to generate the at least one control signal based on a process, voltage, and temperature (PVT) condition.

**[0016]** In some aspects, the apparatus includes a driver circuit coupled to the wires and configured to, for a particular data transfer, drive a particular one of the wire pairs of the plurality of wires, whereby every other wire of the plurality of wires is in a high impedance state. In some aspects, the driver circuit embodies the at least one delay element.

**[0017]** In some aspects, the apparatus includes a receiver circuit coupled to the wires and configured to decode information for a particular data transfer based on a particular one of the wire pairs of the plurality of wires being driven, and every other wire of the plurality of wires being in a high impedance state. In some aspects, the receiver circuit embodies the at least one delay element.

**[0018]** In some aspects, the plurality of wires consists of three wires and three wire pairs. In some aspects, the at least one delay element consists of a delay element coupled to a middle wire of the three wires. In some aspects, the plurality of wires consists of at least four wires including at least two middle wires. In some aspects, the at least one delay element consists of at least two delay elements with each of the delay elements coupled to a respective one of the at least two middle wires.

**[0019]** Further aspects of the disclosure provide an apparatus for multi-wire signaling that includes a memory device and a processing circuit coupled to the memory device. The processing circuit is configured to determine signal propagation times associated with each wire pair of a plurality of wires, the plurality of wires comprising at least three wires; and specify a delay for at least one delay element coupled to at least one of the wires such that the signal propagation times associated with each wire pair of the plurality of wires are equal to one another within a margin of error.

**[0020]** Still further aspects of the disclosure provide a method for communication including determining signal propagation times associated with each wire pair of a plurality of wires, the plurality of wires comprising at least three wires; and specifying a delay for at least one delay element coupled to at least one of the wires such that the signal propagation times associated with each wire pair of the plurality of wires are equal to one another within a margin of error.

**[0021]** Additional aspects of the disclosure provide an apparatus for multi-wire signaling including means for determining signal propagation times associated with each wire pair of a plurality of wires, the plurality of wires comprising at least three wires; and means for specifying a delay for at least one delay element coupled to at least

one of the wires such that the signal propagation times associated with each wire pair of the plurality of wires are equal to one another within a margin of error.

[0022] Other aspects of the disclosure provide a non-transitory machine-readable storage medium having instructions stored thereon which when executed by a processing circuit cause the processing circuit to: determine signal propagation times associated with each wire pair of a plurality of wires, the plurality of wires comprising at least three wires; and specify a delay for at least one delay element coupled to at least one of the wires such that the signal propagation times associated with each wire pair of the plurality of wires are equal to one another within a margin of error.

[0023] Examples of other aspects of the disclosure related to the above apparatuses, method, and medium follow. In some aspects, each delay element has a programmable delay; and the specification of the delay includes controlling the programmable delay of each delay element. In some aspects, a parameter is determined, the parameter including at least one of: lengths of the wires, signal propagation times associated with the wire pairs, a signal frequency of signals carried by the wires, an application for which signals are transmitted over the wires, or a process, voltage, and temperature (PVT) condition; wherein the specification of the delay is based on the parameter. In some aspects, for a particular data transfer, a particular one of the wire pairs of the plurality of wires is driven, whereby every other wire of the plurality of wires is in a high impedance state. In some aspects, for a particular data transfer, information is decoded based on a particular one of the wire pairs of the plurality of wires being driven, and every other wire of the plurality of wires being in a high impedance state. In some aspects, the plurality of wires consists of three wires and three wire pairs. In some aspects, the at least one delay element consists of a delay element coupled to a middle wire of the three wires. In some aspects, the specification of the delay includes specifying a physical characteristic of each delay element. In some aspects, the physical characteristic of each delay element includes a length of a wire segment. In some aspects, the specification of the delay includes generating a circuit description representative of the physical characteristic. In some aspects, the specification of the delay includes generating a circuit embodying the physical characteristic.

[0024] Further aspects of the disclosure provide an apparatus for multi-wire signaling. The apparatus including: a transmitter; a receiver, a plurality of wires comprising at least three wires coupled to the transmitter and the receiver; and at least one delay element coupled to at least one of the wires, each delay element to provide an amount of

signal delay such that signal propagation times associated with wire pairs of the plurality of wires are equal to one another within a margin of error, wherein the transmitter is configured to, for a particular data transfer, drive a particular one of the wire pairs of the plurality of wires, whereby every other wire of the plurality of wires is in a high impedance state.

[0025] Examples of other aspects of the disclosure related to the above apparatus follow. In some aspects, each delay element includes a passive delay structure. In some aspects, each delay element includes an active delay device. In some aspects, each delay element includes a programmable delay device; and the apparatus further includes a delay controller to generate at least one control signal to control a delay of each delay element. In some aspects, the transmitter and/or the receiver embodies the at least one delay element. In some aspects, the receiver is configured to decode information for a particular data transfer based on a particular one of the wire pairs of the plurality of wires being driven, and every other wire of the plurality of wires being in a high impedance state.

[0026] These and other aspects of the disclosure will become more fully understood upon a review of the detailed description, which follows. Other aspects, features, and implementations of the disclosure will become apparent to those of ordinary skill in the art, upon reviewing the following description of specific, exemplary implementations of the disclosure in conjunction with the accompanying figures. While features of the disclosure may be discussed relative to certain implementations and figures below, all implementations of the disclosure can include one or more of the advantageous features discussed herein. In other words, while one or more implementations may be discussed as having certain advantageous features, one or more of such features may also be used in accordance with the various implementations of the disclosure discussed herein. In similar fashion, while exemplary implementations may be discussed below as device, system, or method implementations it should be understood that such exemplary implementations can be implemented in various devices, systems, and methods.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0027] FIG. 1 is a circuit diagram illustrating an example of a three-wire channel.

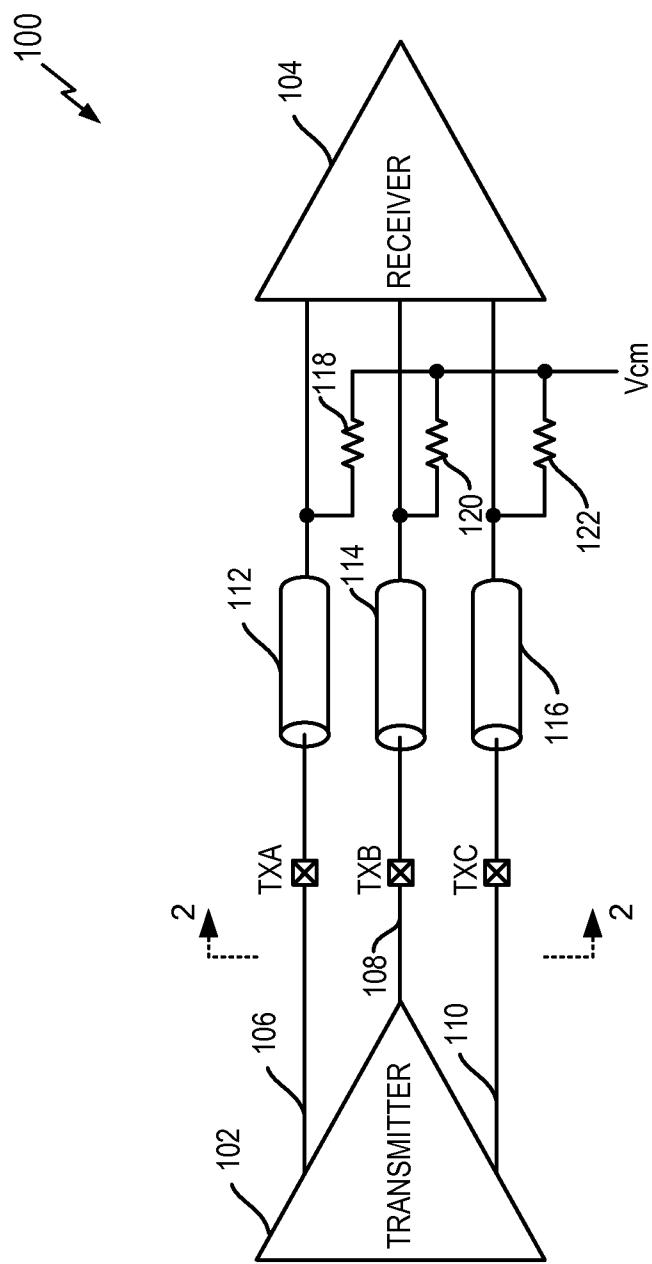

[0028] FIG. 2 is a diagram illustrating an example of wire spacing for a three-wire channel.

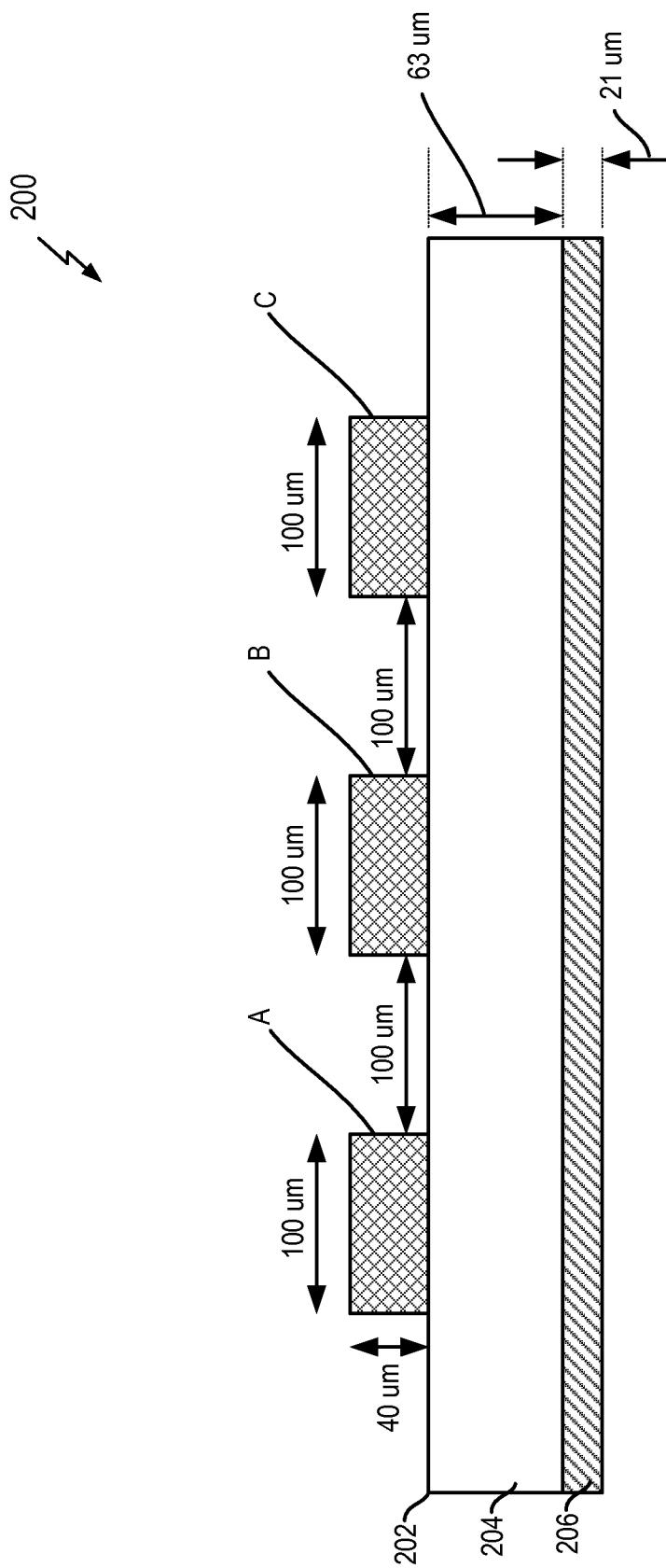

[0029] FIG. 3 is an eye diagram illustrating an example of jitter in a conventional multi-wire channel.

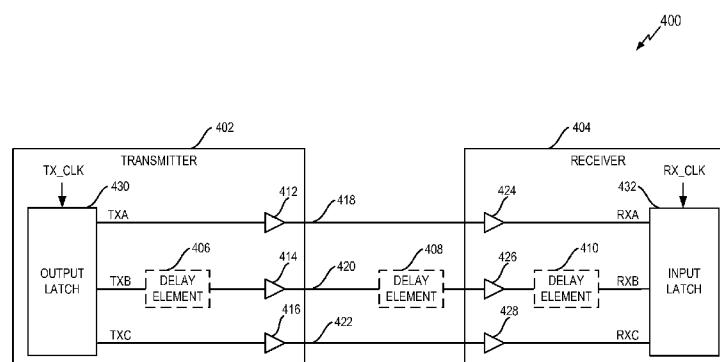

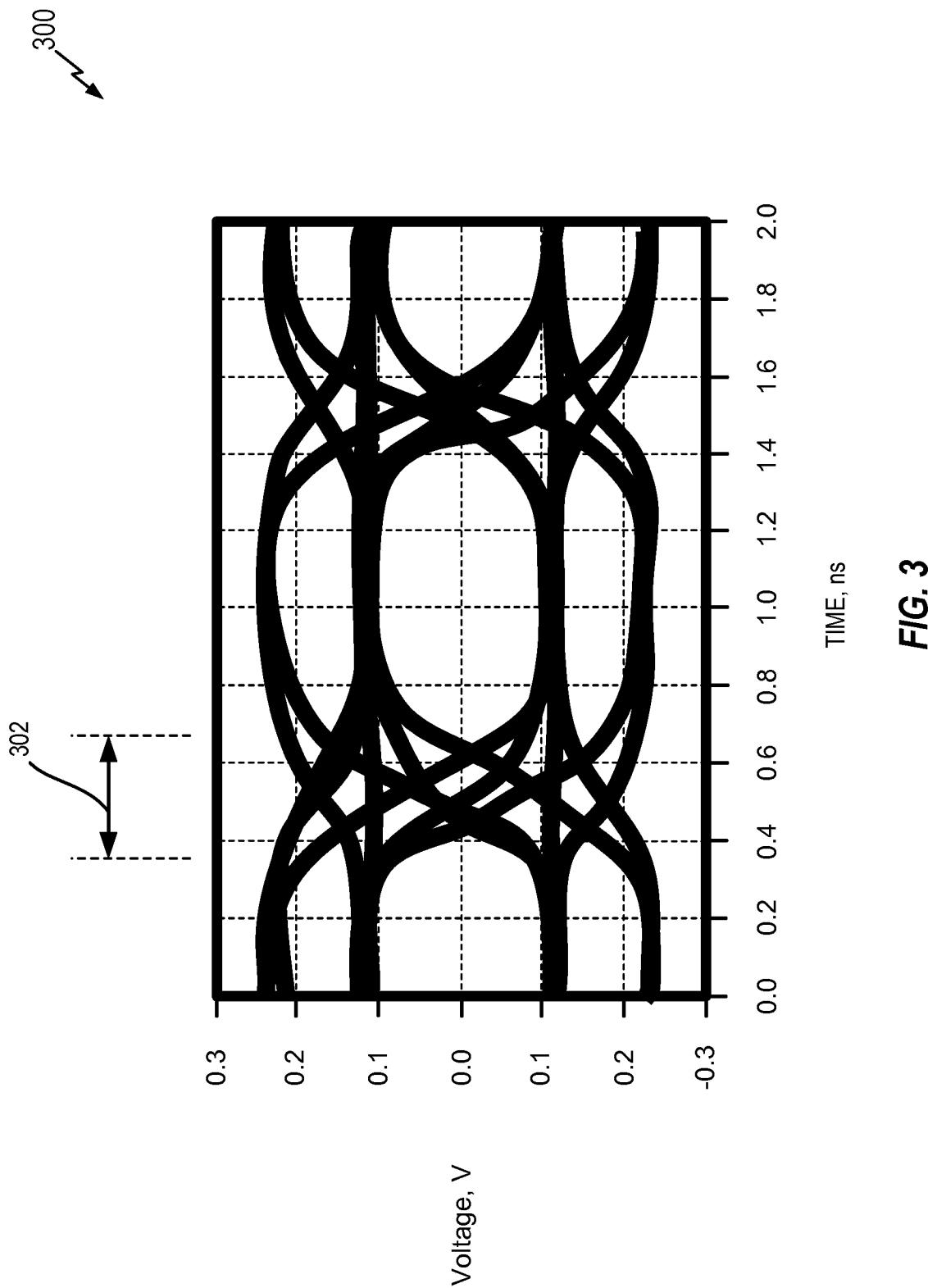

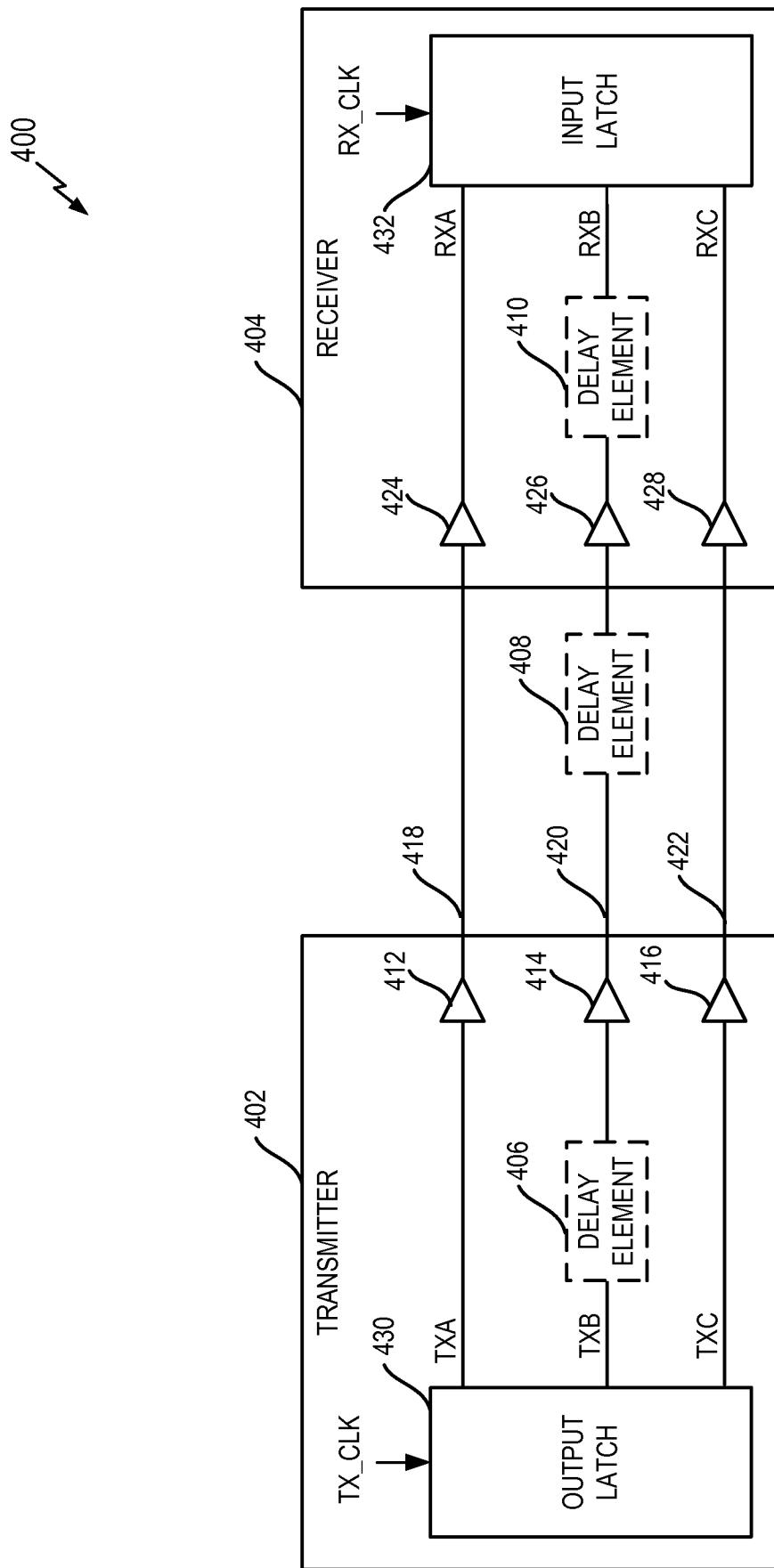

[0030] FIG. 4 is a block diagram illustrating an example of a delay element for a three-wire channel in accordance with some aspects of the disclosure.

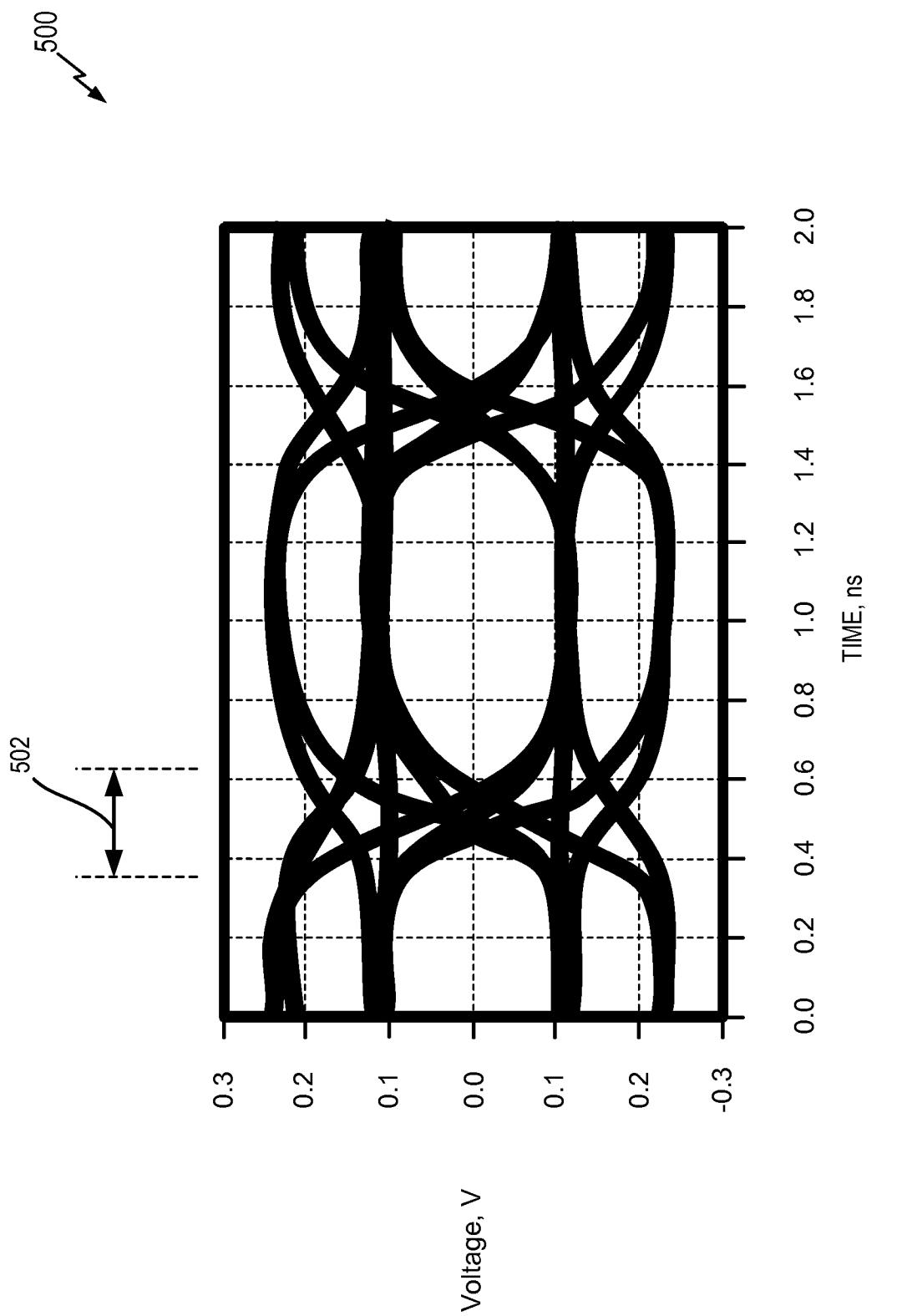

[0031] FIG. 5 is an eye diagram illustrating an example of jitter in a multi-wire channel in accordance with some aspects of the disclosure.

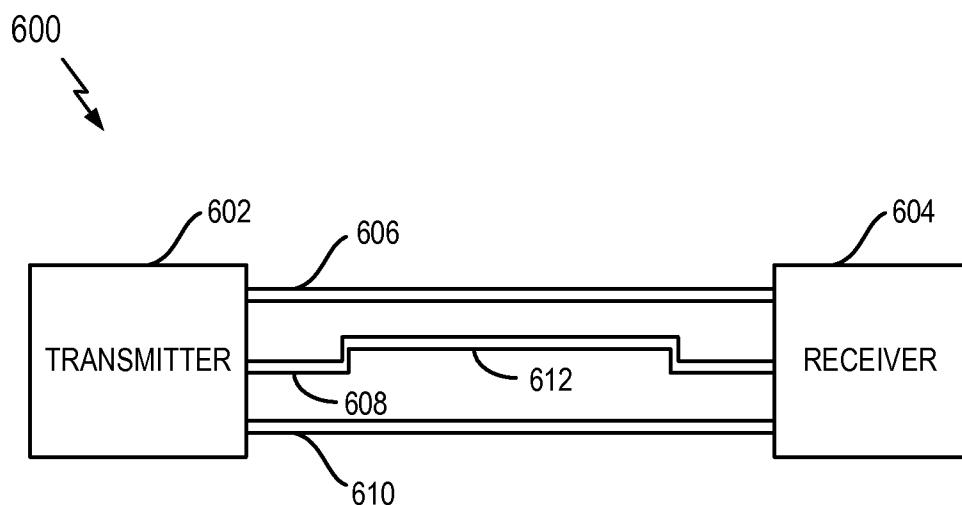

[0032] FIG. 6 is a diagram illustrating an example of a passive delay element in accordance with some aspects of the disclosure.

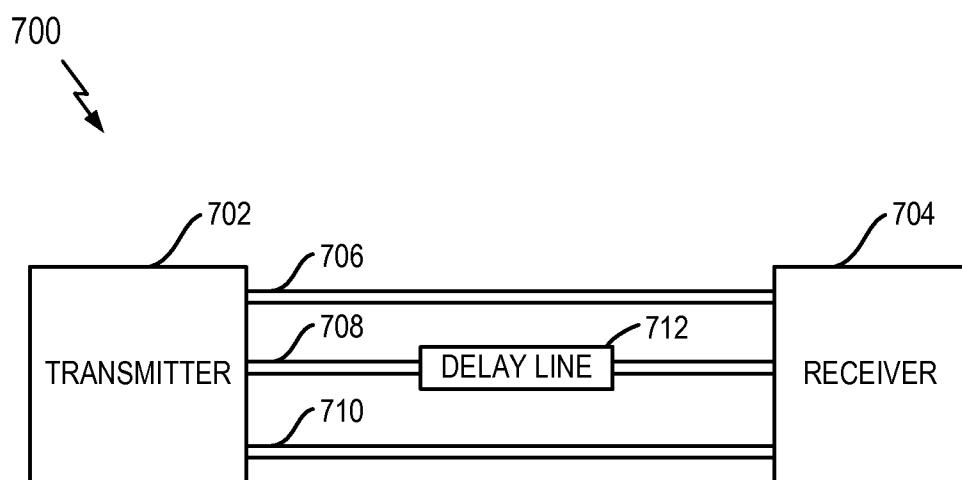

[0033] FIG. 7 is a diagram illustrating an example of a delay line deployed in accordance with some aspects of the disclosure.

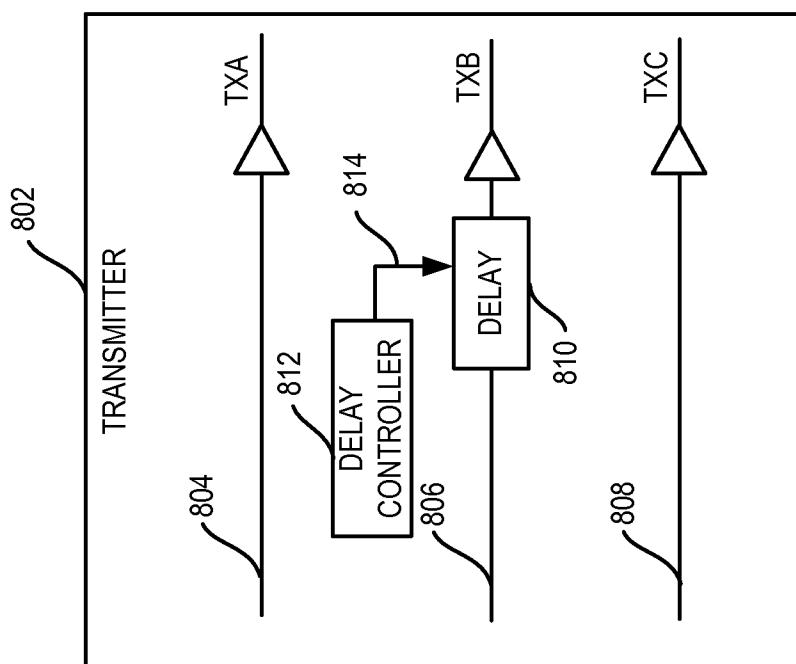

[0034] FIG. 8 is a block diagram illustrating an example of a transmitter including an active delay element in accordance with some aspects of the disclosure.

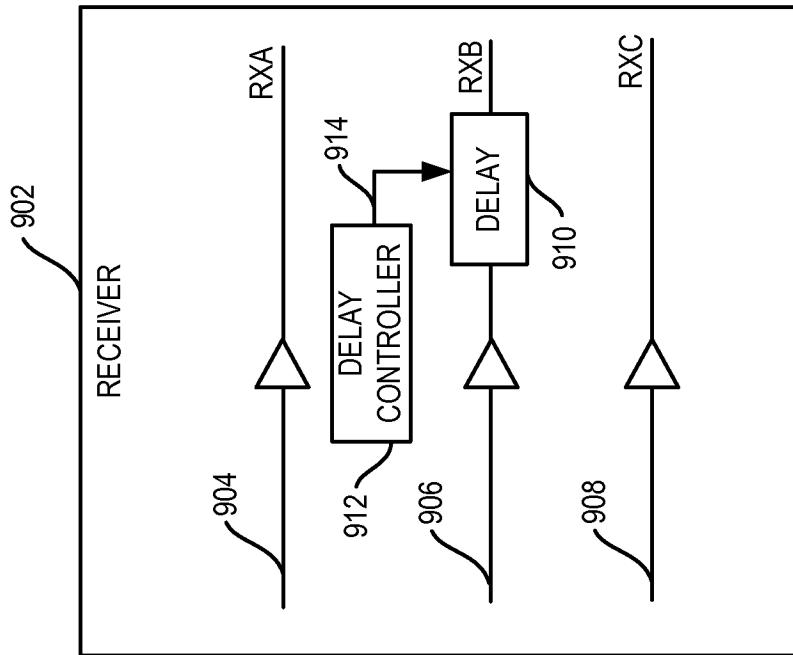

[0035] FIG. 9 is a block diagram illustrating an example of a receiver including a passive delay element in accordance with some aspects of the disclosure.

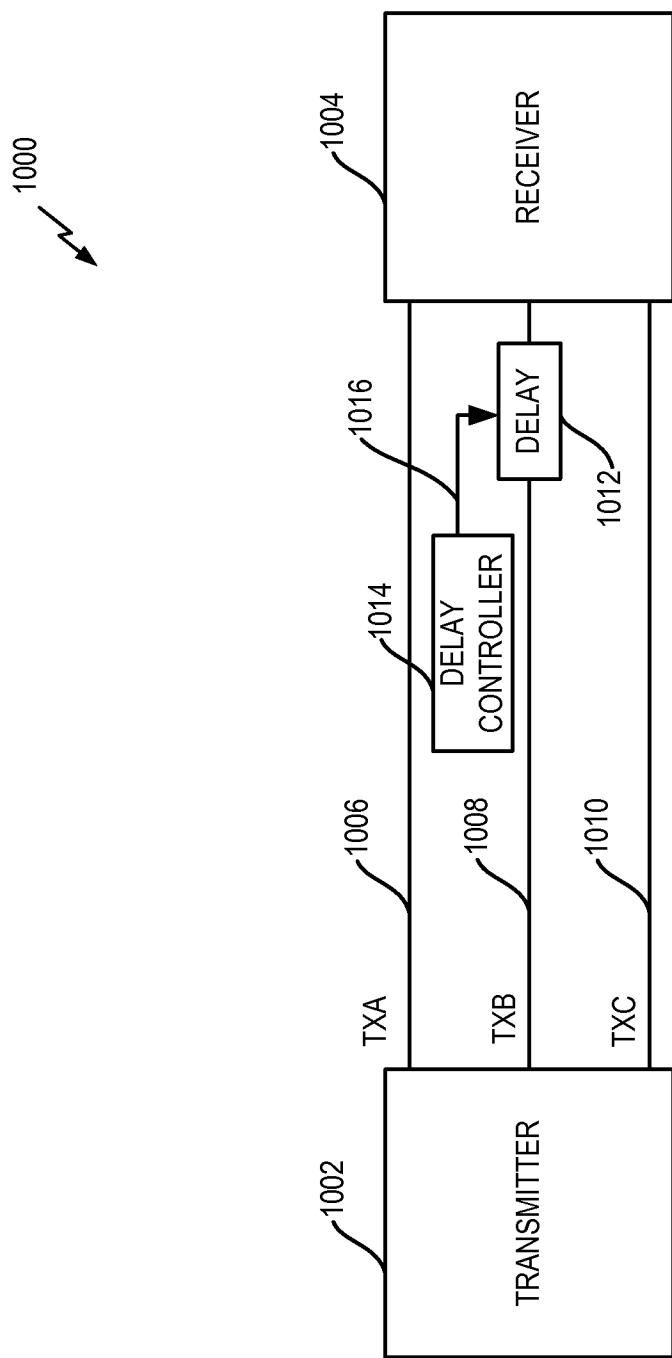

[0036] FIG. 10 is a block diagram illustrating an example of an active delay element deployed in accordance with some aspects of the disclosure.

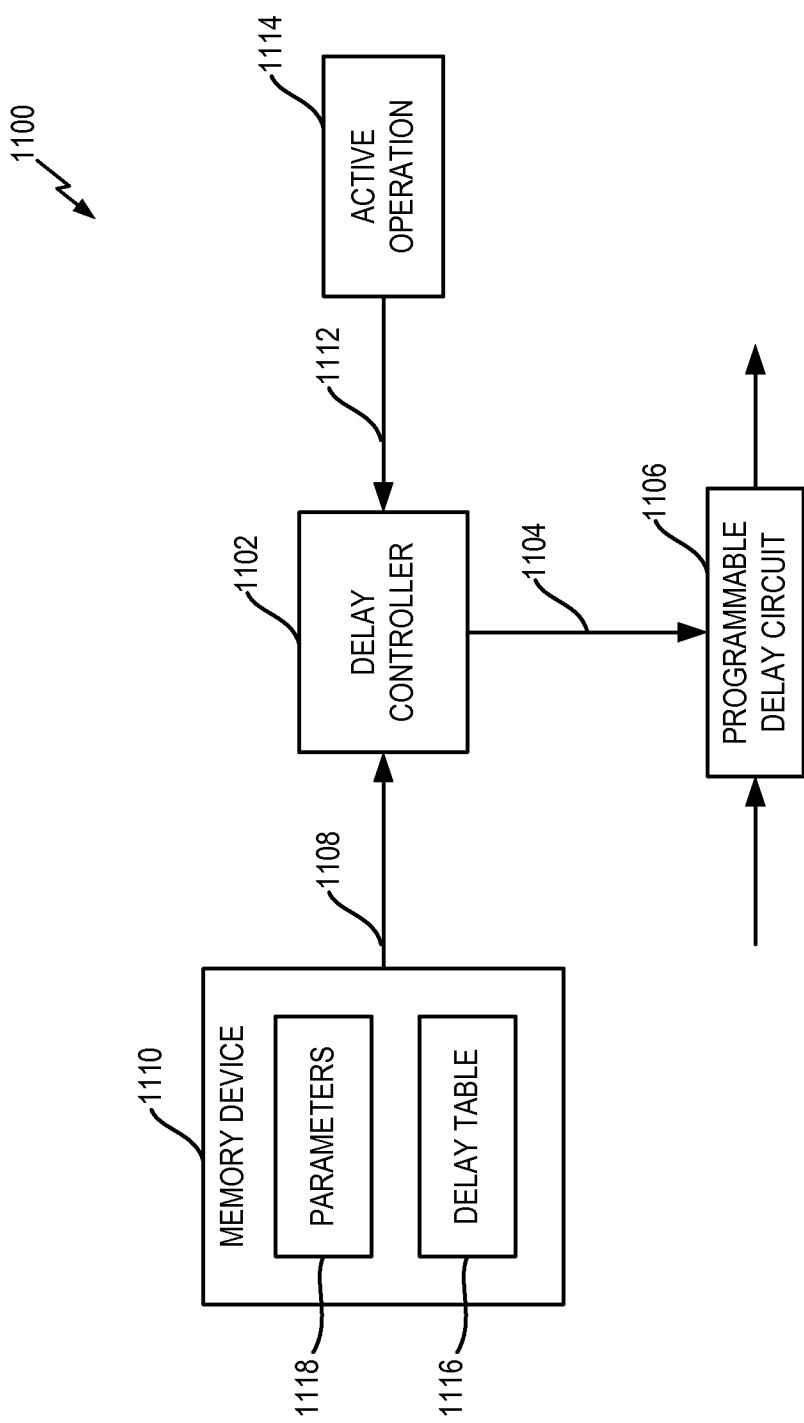

[0037] FIG. 11 is a block diagram illustrating an example of delay controller in accordance with some aspects of the disclosure.

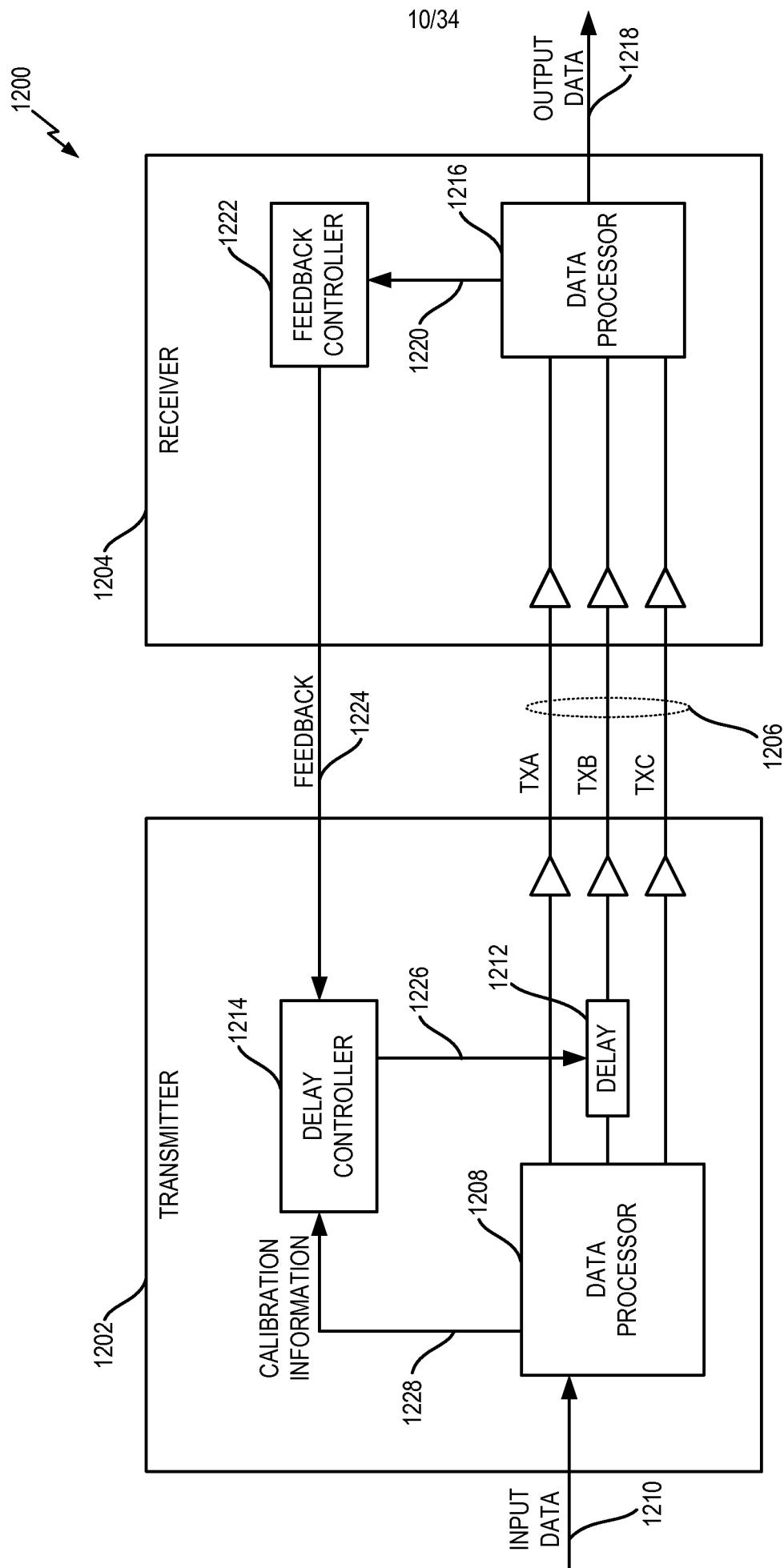

[0038] FIG. 12 is a block diagram illustrating an example of delay calibration in accordance with some aspects of the disclosure.

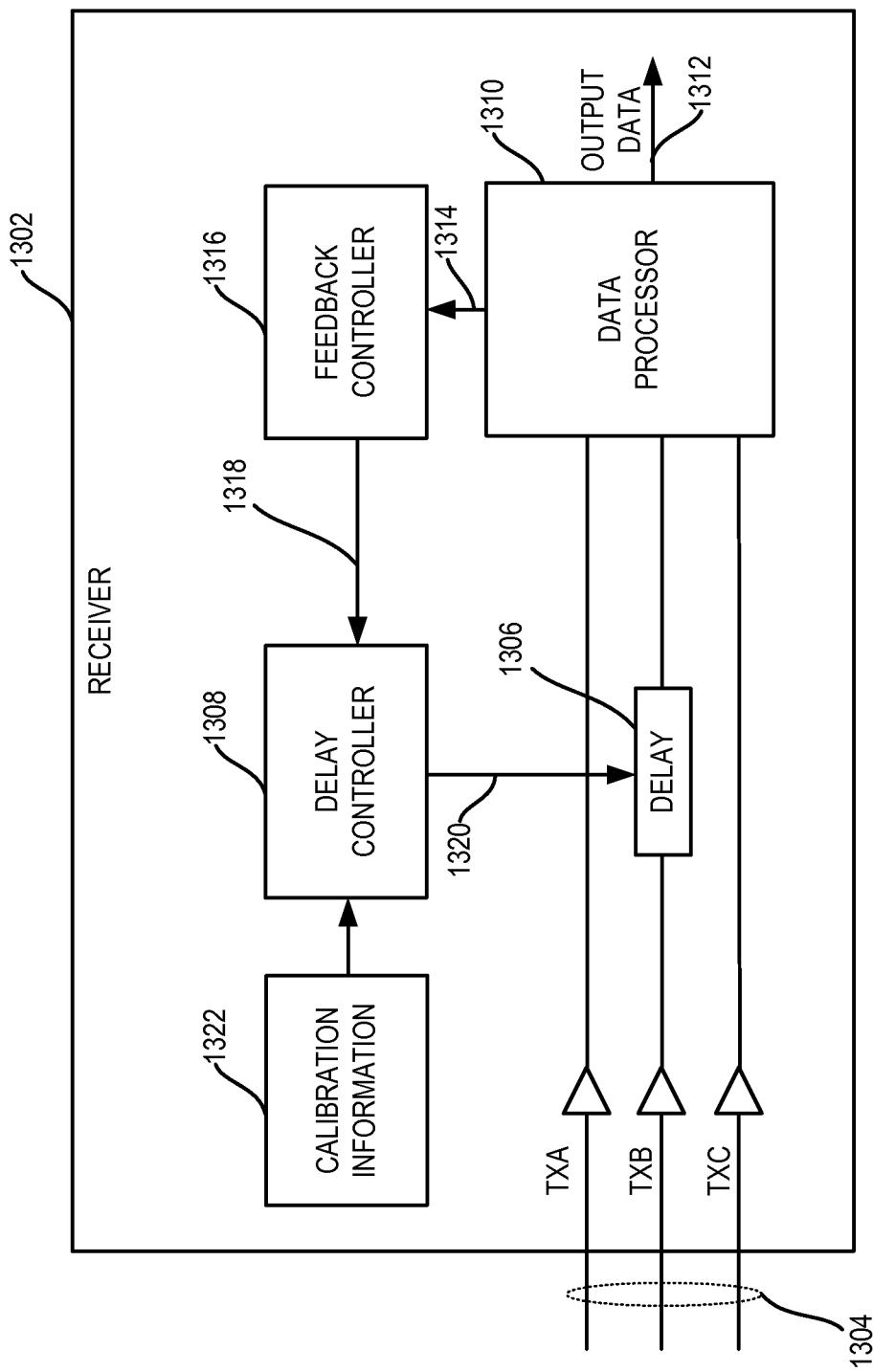

[0039] FIG. 13 is a block diagram illustrating another example of delay calibration in accordance with some aspects of the disclosure.

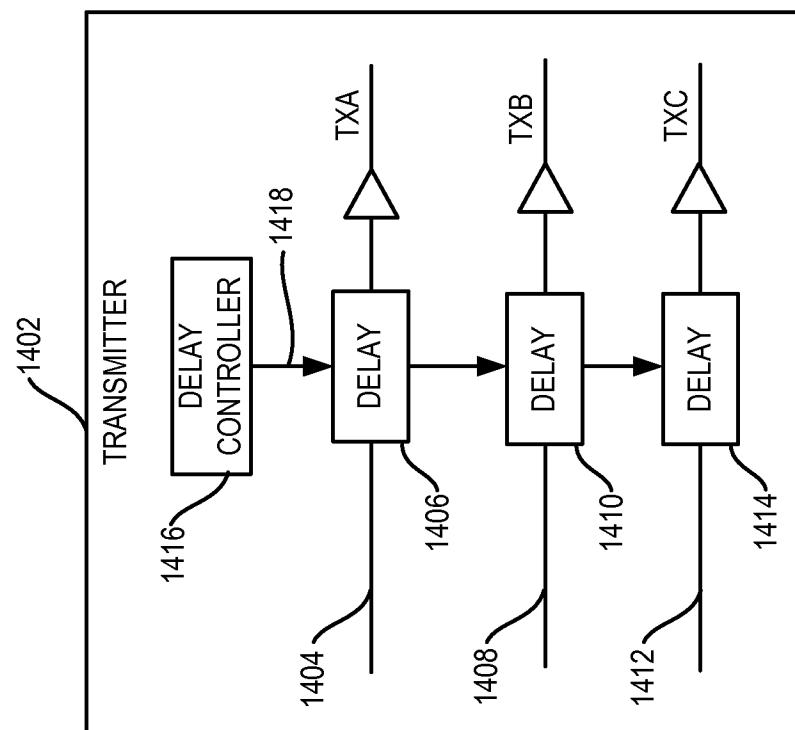

[0040] FIG. 14 is a block diagram illustrating an example of delay elements for a three-wire channel in accordance with some aspects of the disclosure.

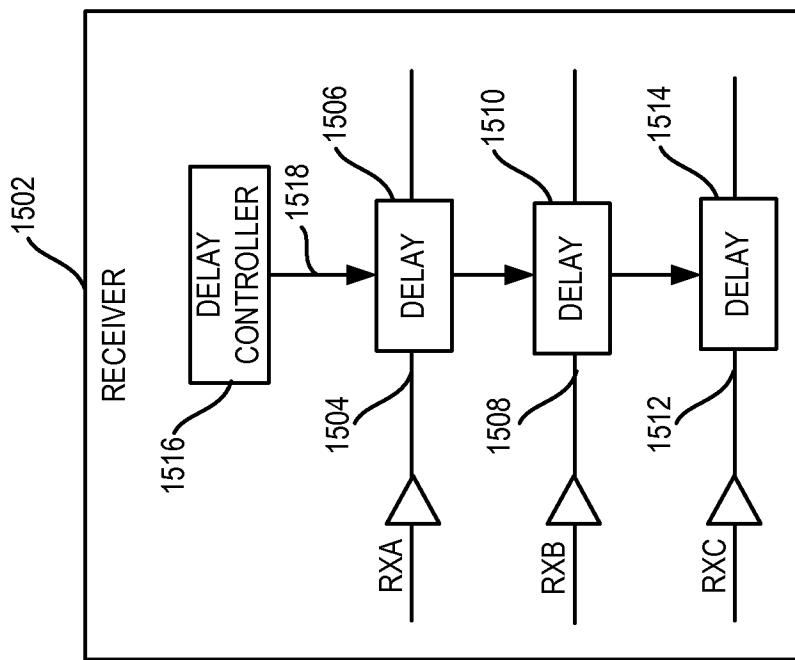

[0041] FIG. 15 is a block diagram illustrating another example of delay elements for a three-wire channel in accordance with some aspects of the disclosure.

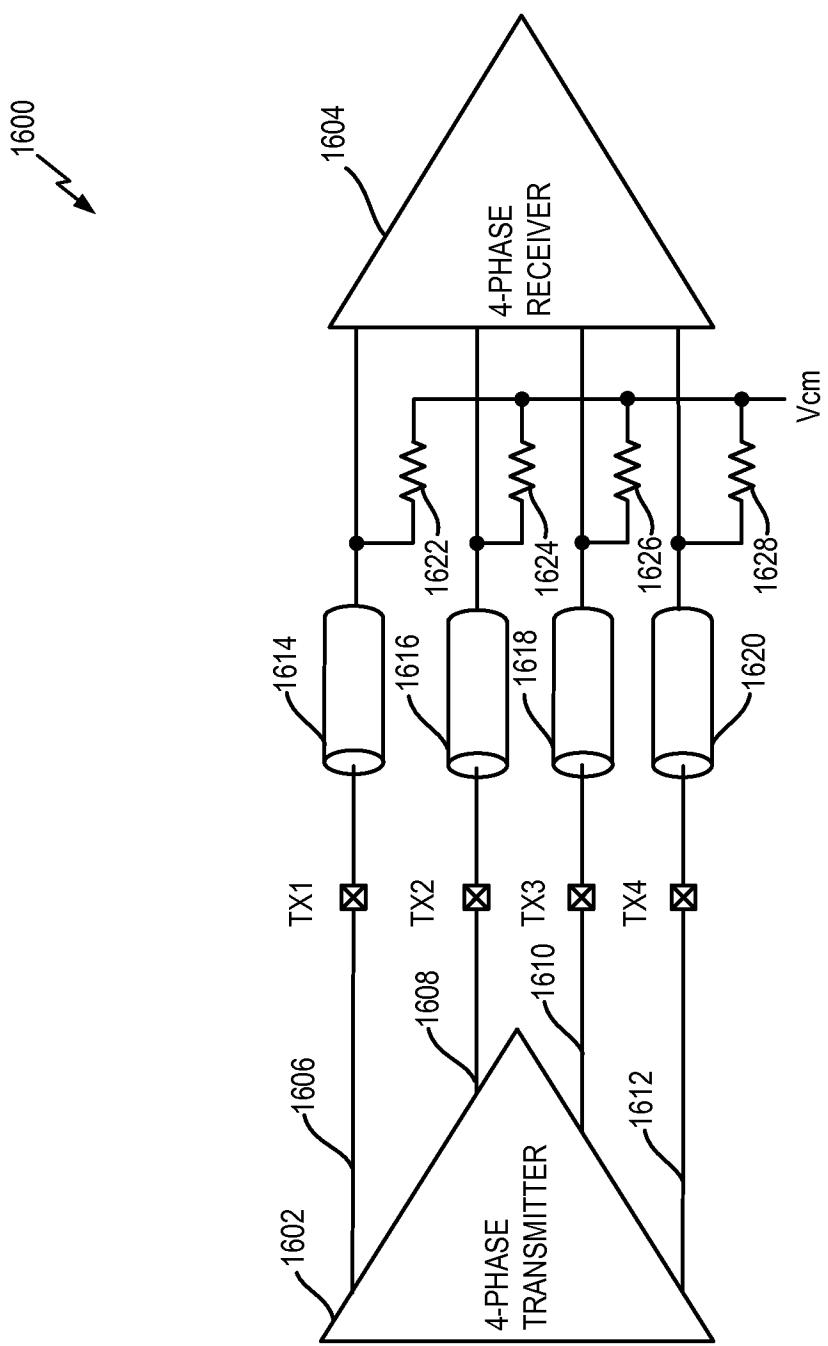

[0042] FIG. 16 is a circuit diagram illustrating an example of a four-wire channel.

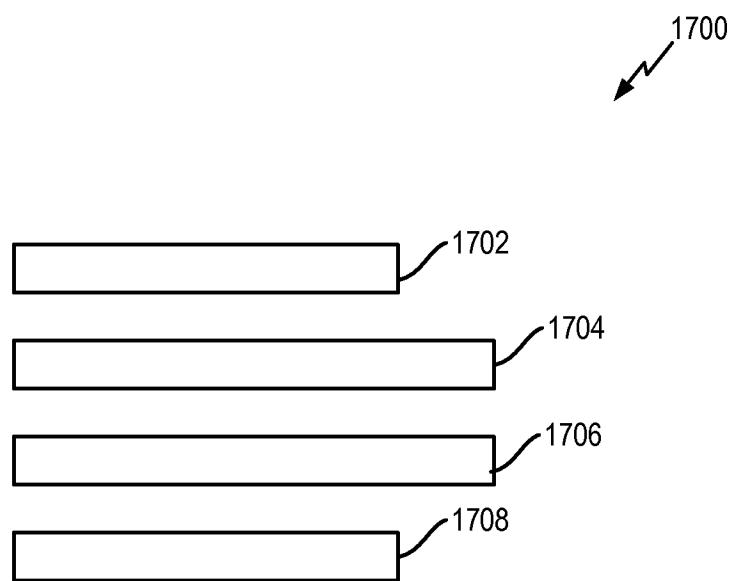

[0043] FIG. 17 is a diagram illustrating an example of wire lengths for a four-wire channel.

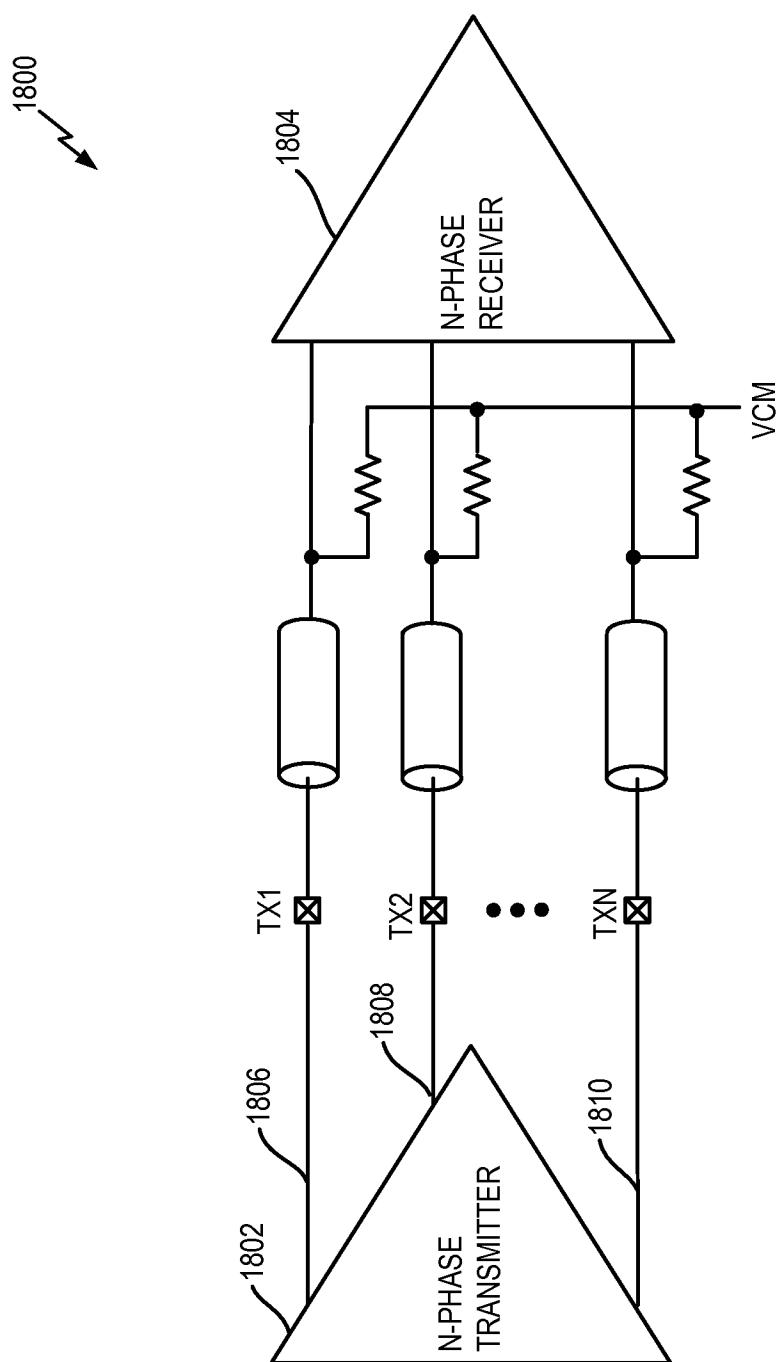

[0044] FIG. 18 is a circuit diagram illustrating an example of an n-wire channel.

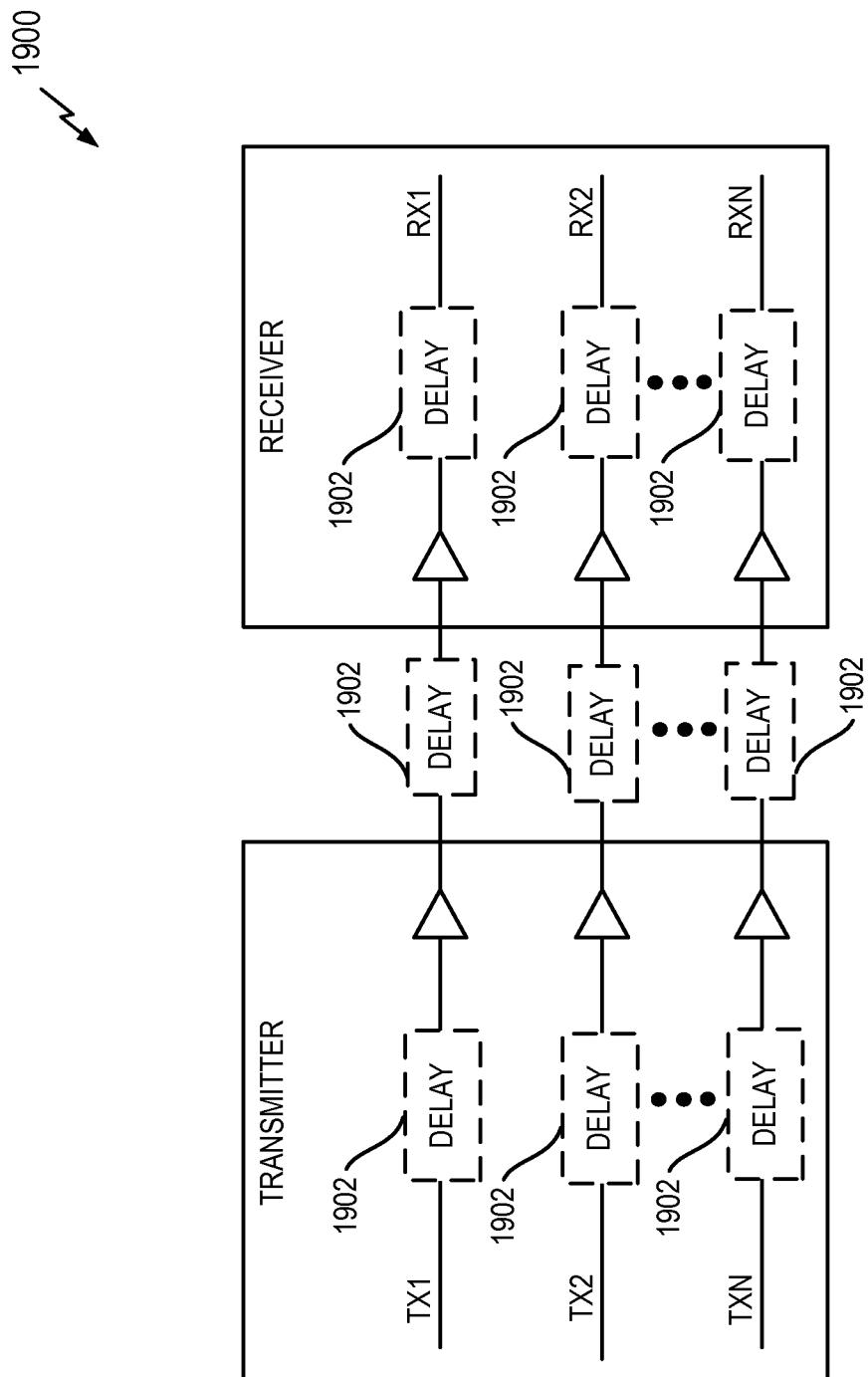

[0045] FIG. 19 is a block diagram illustrating an example of delay elements for an n-wire channel in accordance with some aspects of the disclosure.

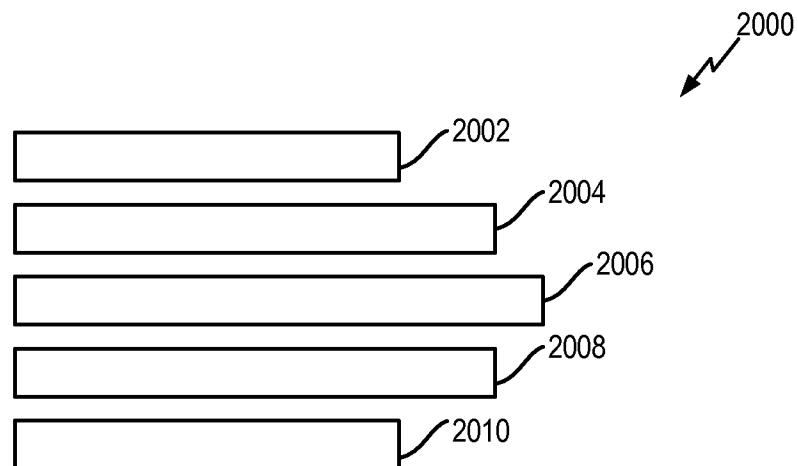

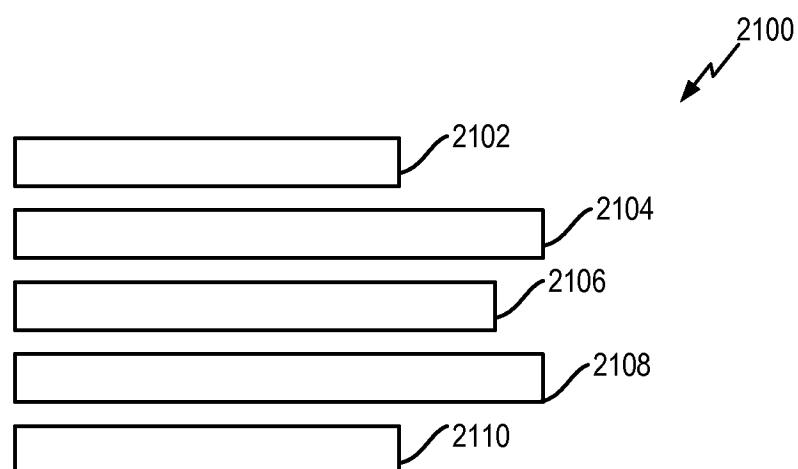

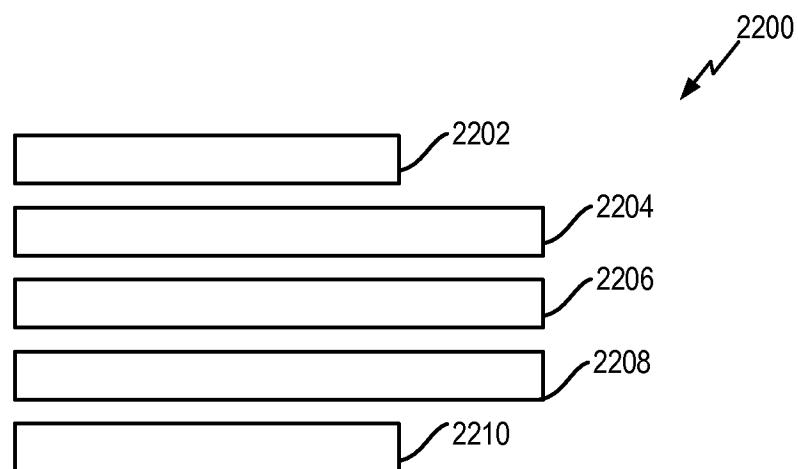

[0046] FIGs. 20 - 22 are diagrams illustrating examples of wire lengths for a five-wire channel.

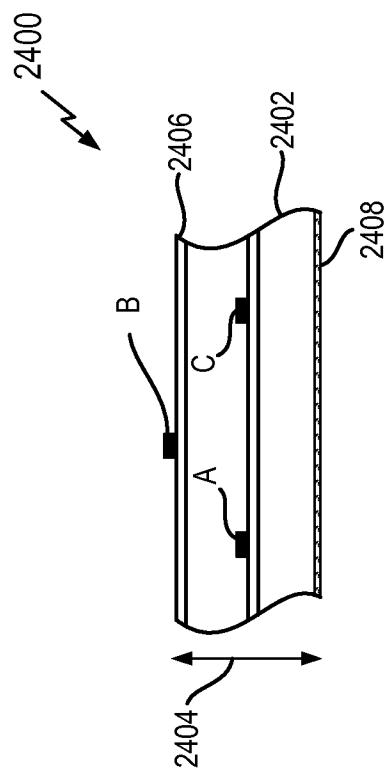

[0047] FIGS. 23 - 26 are cross-sectional views of circuits for improving signal propagation timing in accordance with some aspects of the disclosure.

[0048] FIG. 27 is a circuit diagram illustrating an example of a three-wire channel.

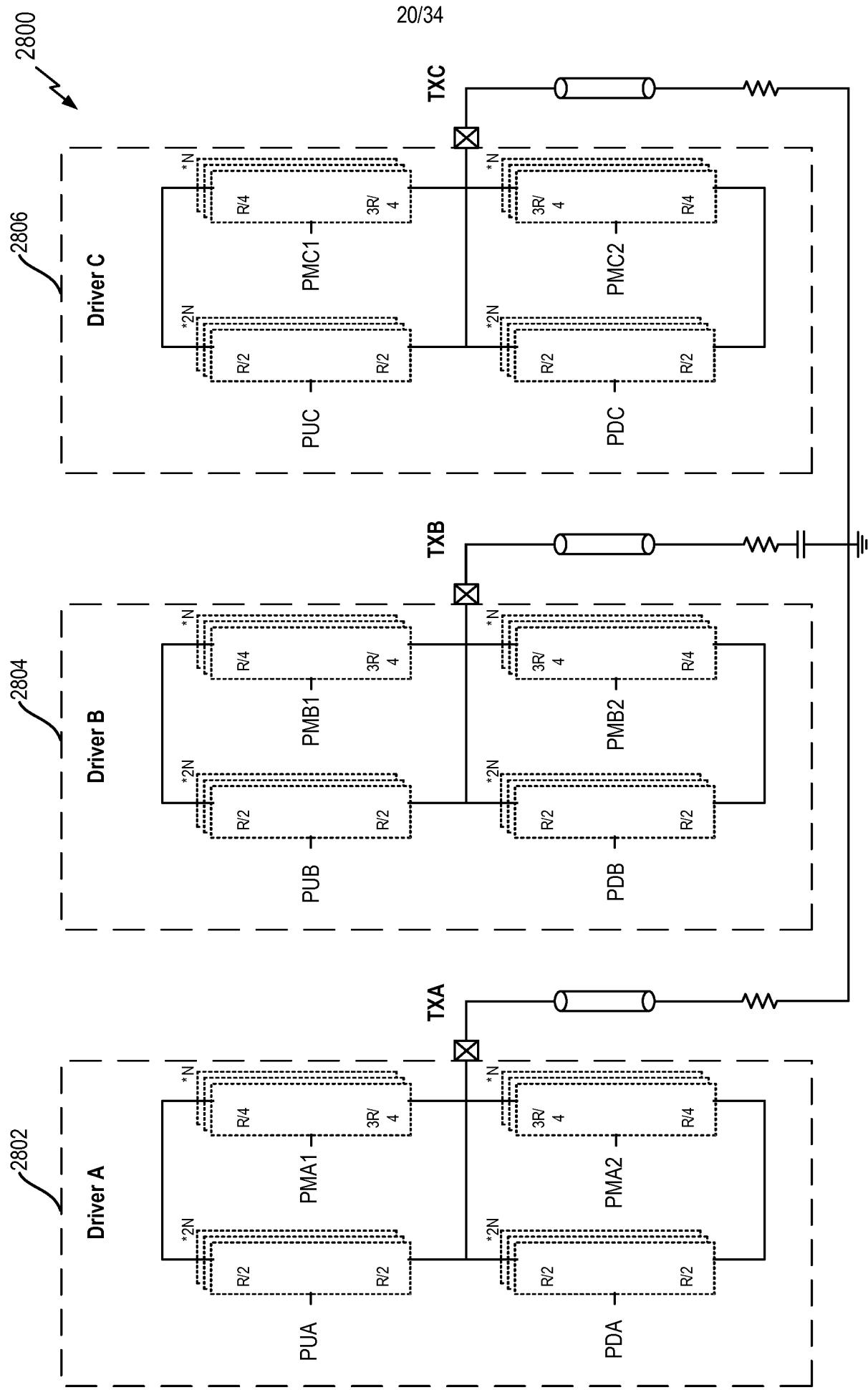

[0049] FIG. 28 is a circuit diagram illustrating an example of a driver circuit for a three-wire channel.

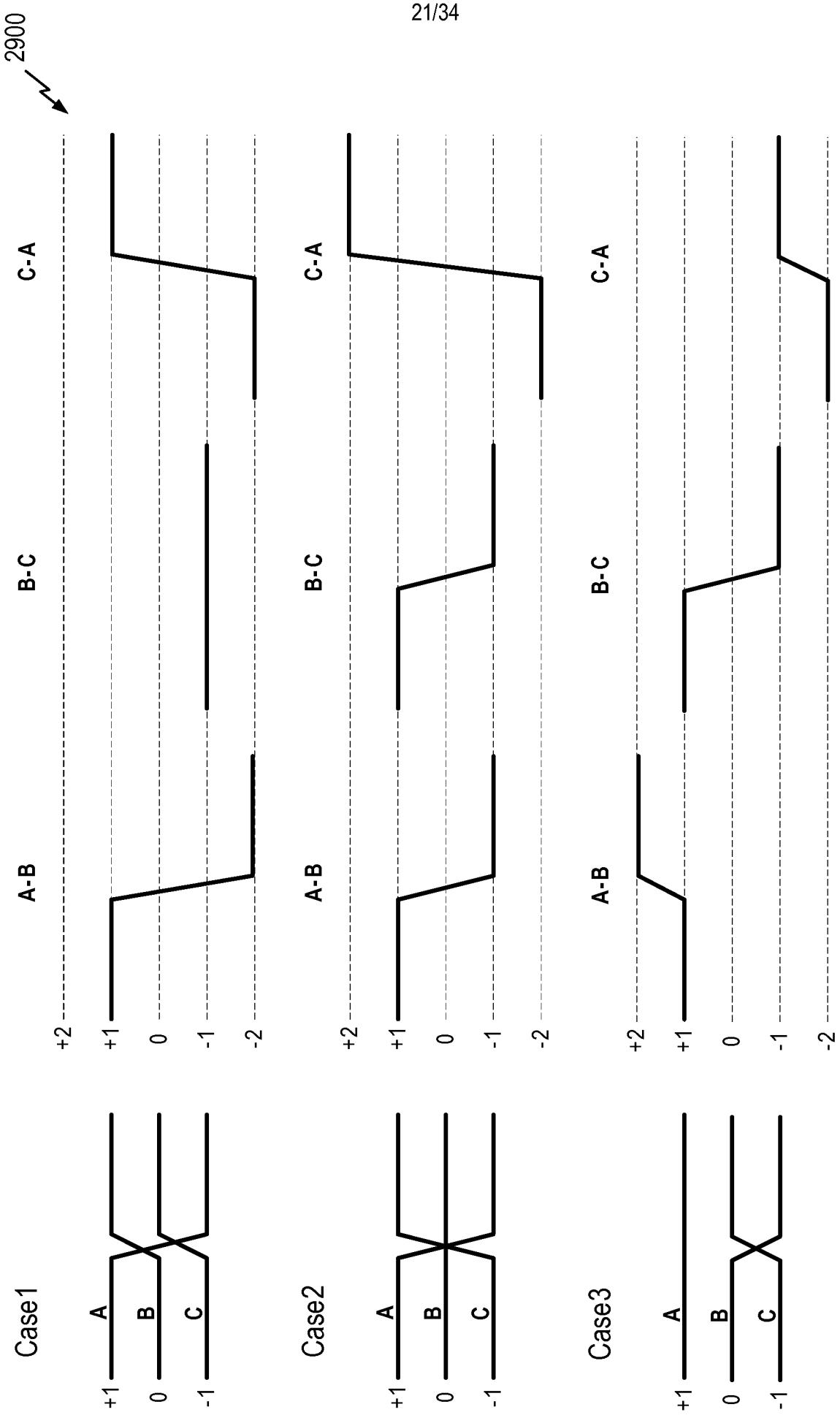

[0050] FIG. 29 is a diagram illustrating an example of signaling for a three-wire channel.

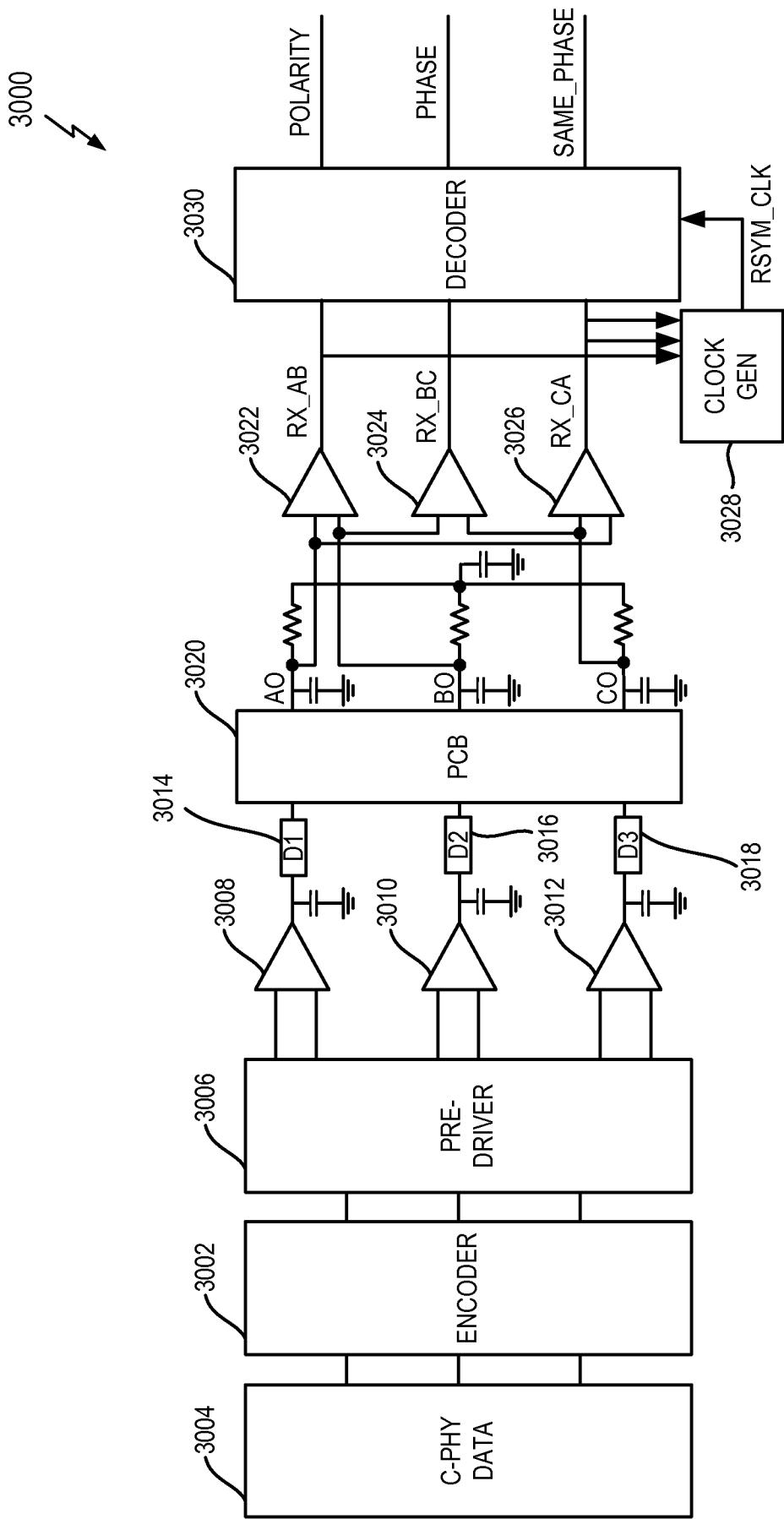

[0051] FIG. 30 is a block diagram illustrating a system employing a three-wire channel.

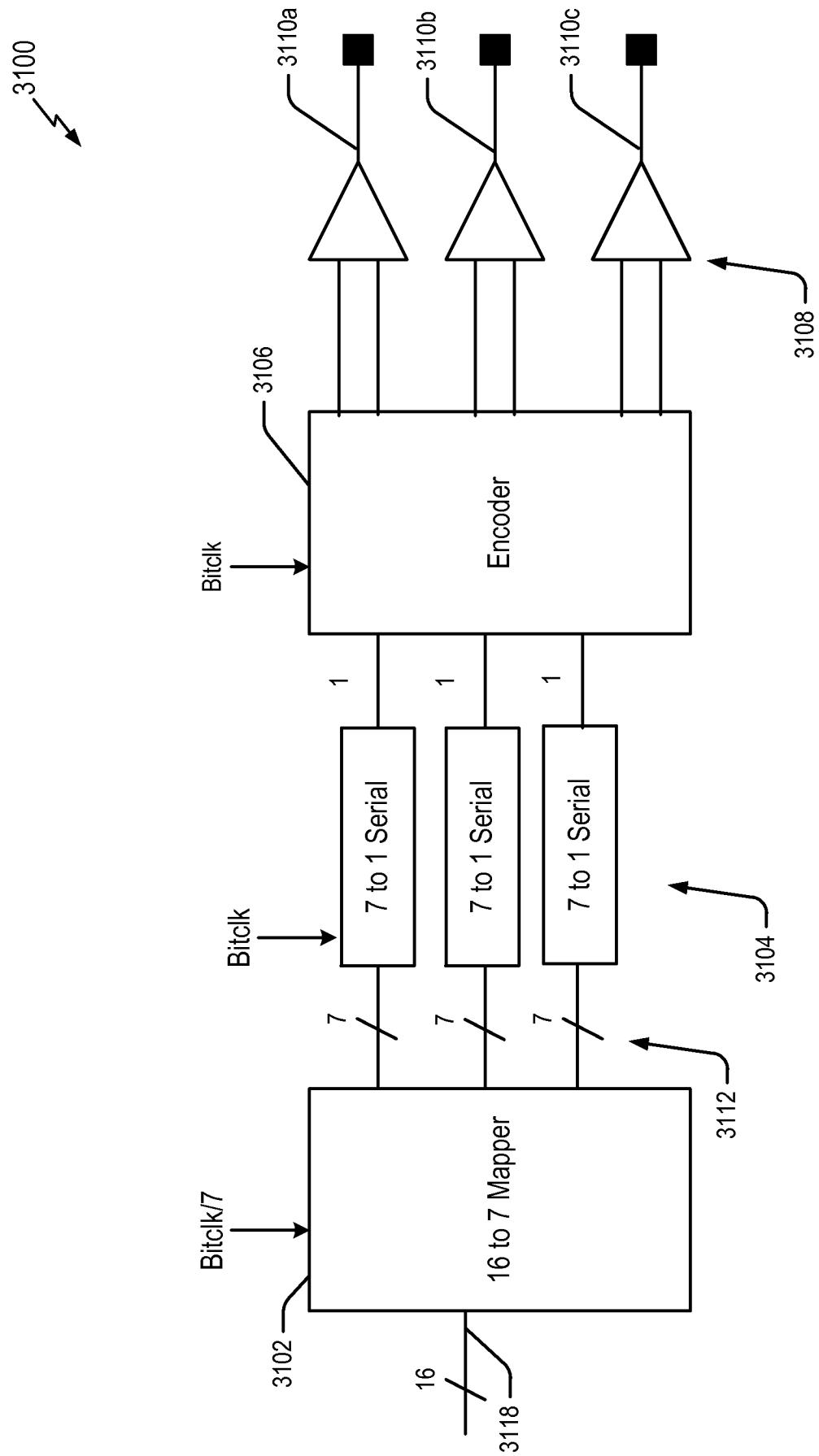

[0052] FIG. 31 is a block diagram illustrating an example of an *N*-Phase polarity data encoder.

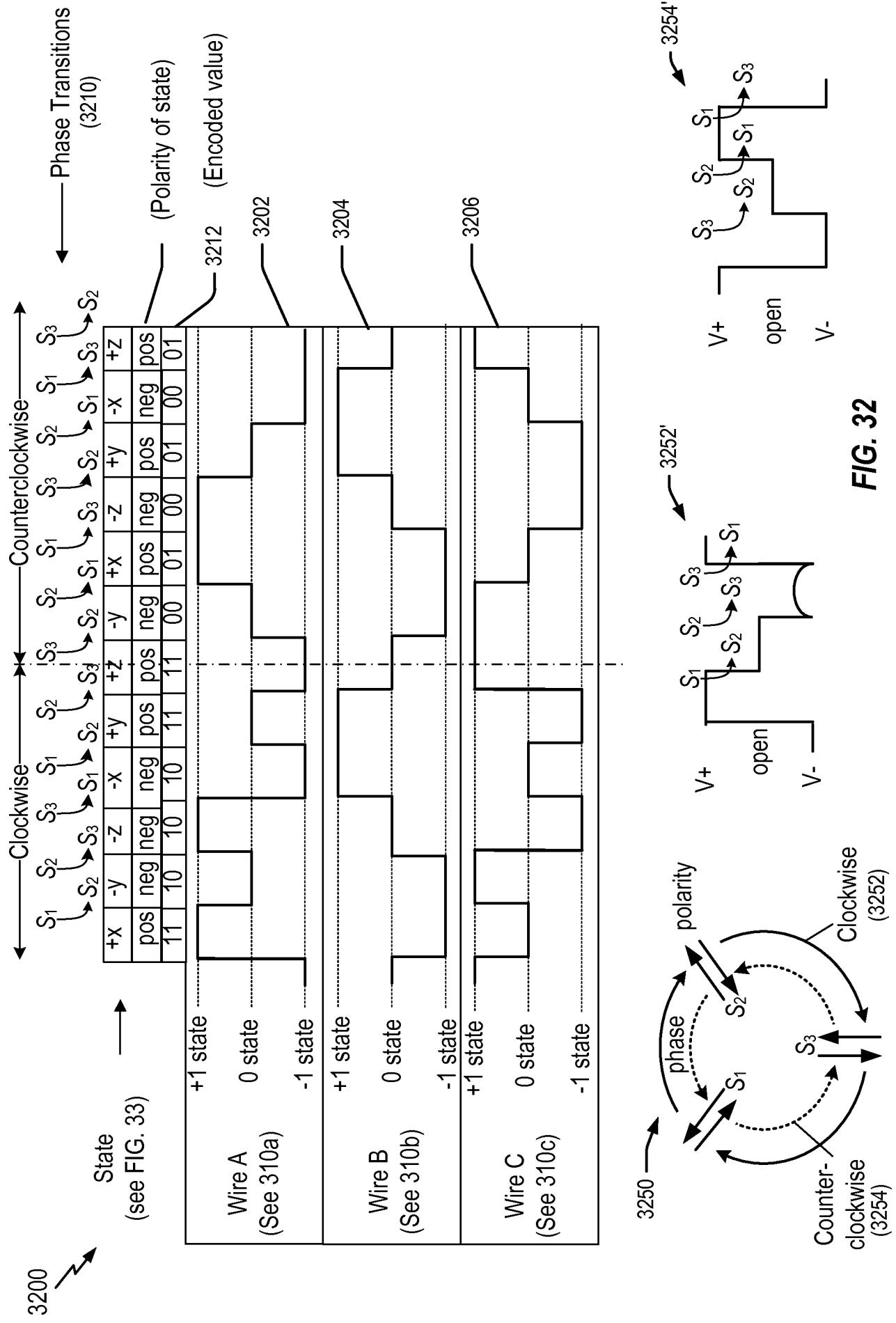

[0053] FIG. 32 is a diagram illustrating signaling in an *N*-Phase polarity encoded interface.

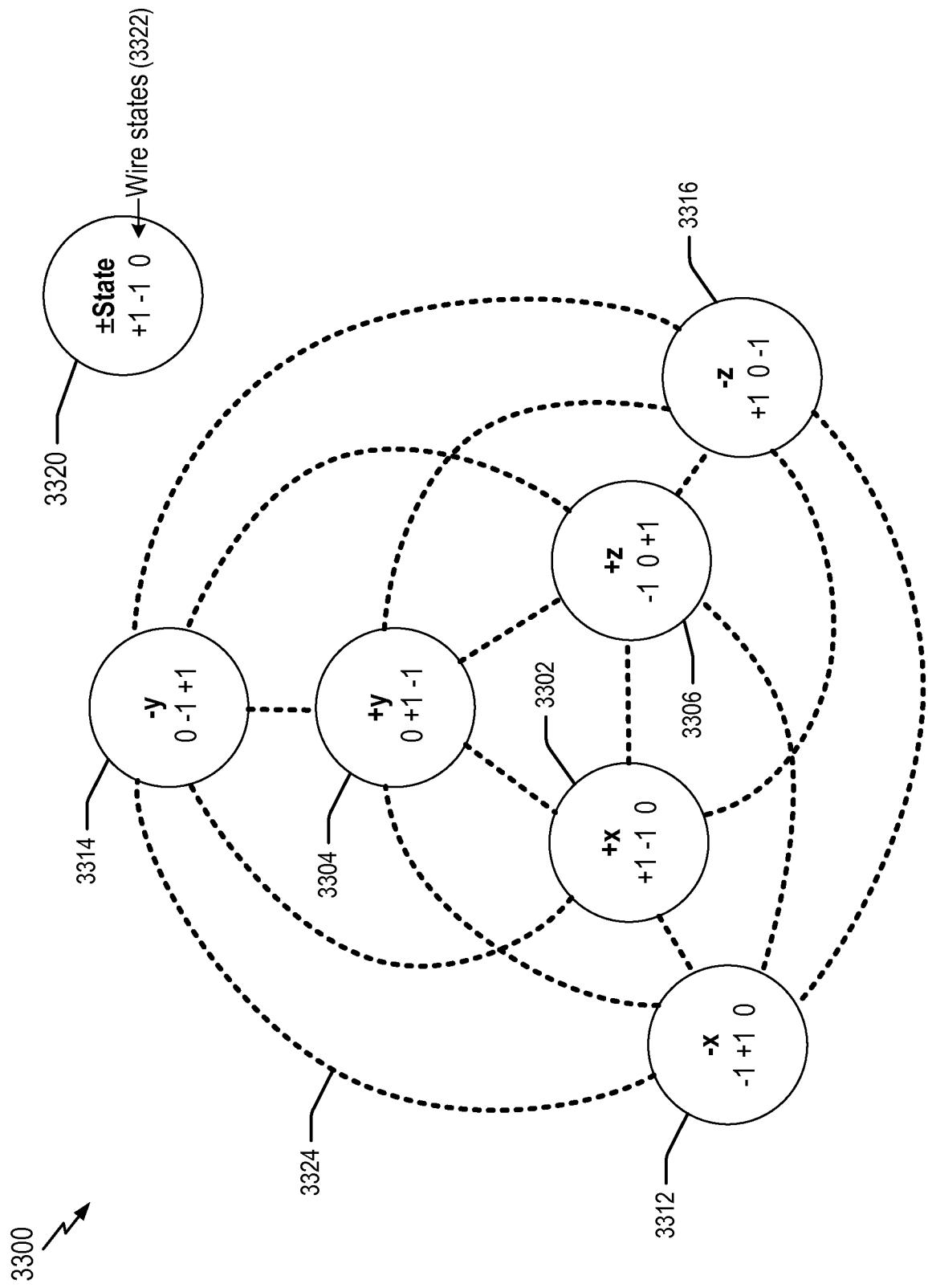

[0054] FIG. 33 is a state diagram illustrating state transitions in the example of a 3-wire, 3-Phase communication link.

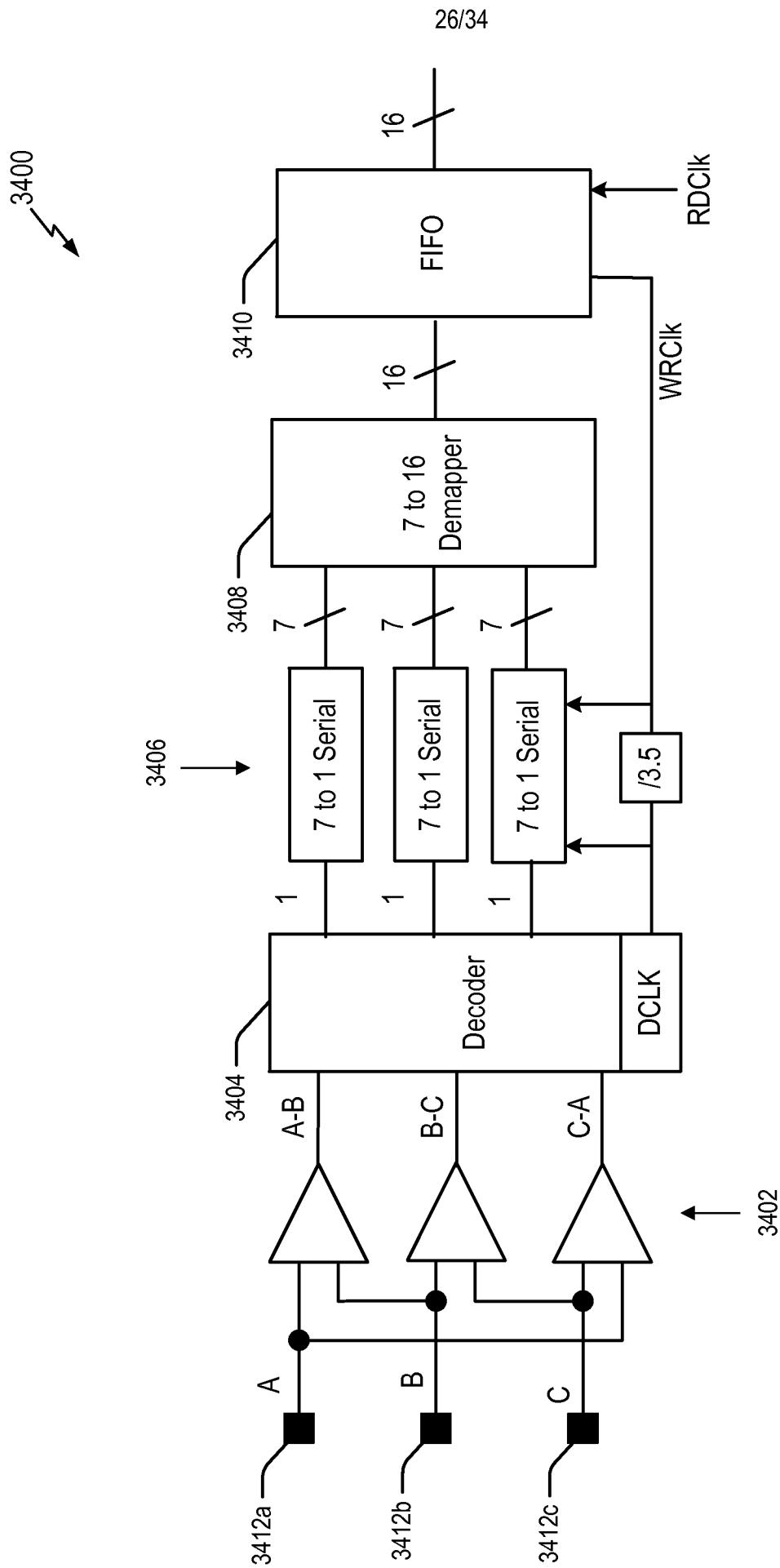

[0055] FIG. 34 is a block diagram illustrating a 3-Phase polarity data decoder.

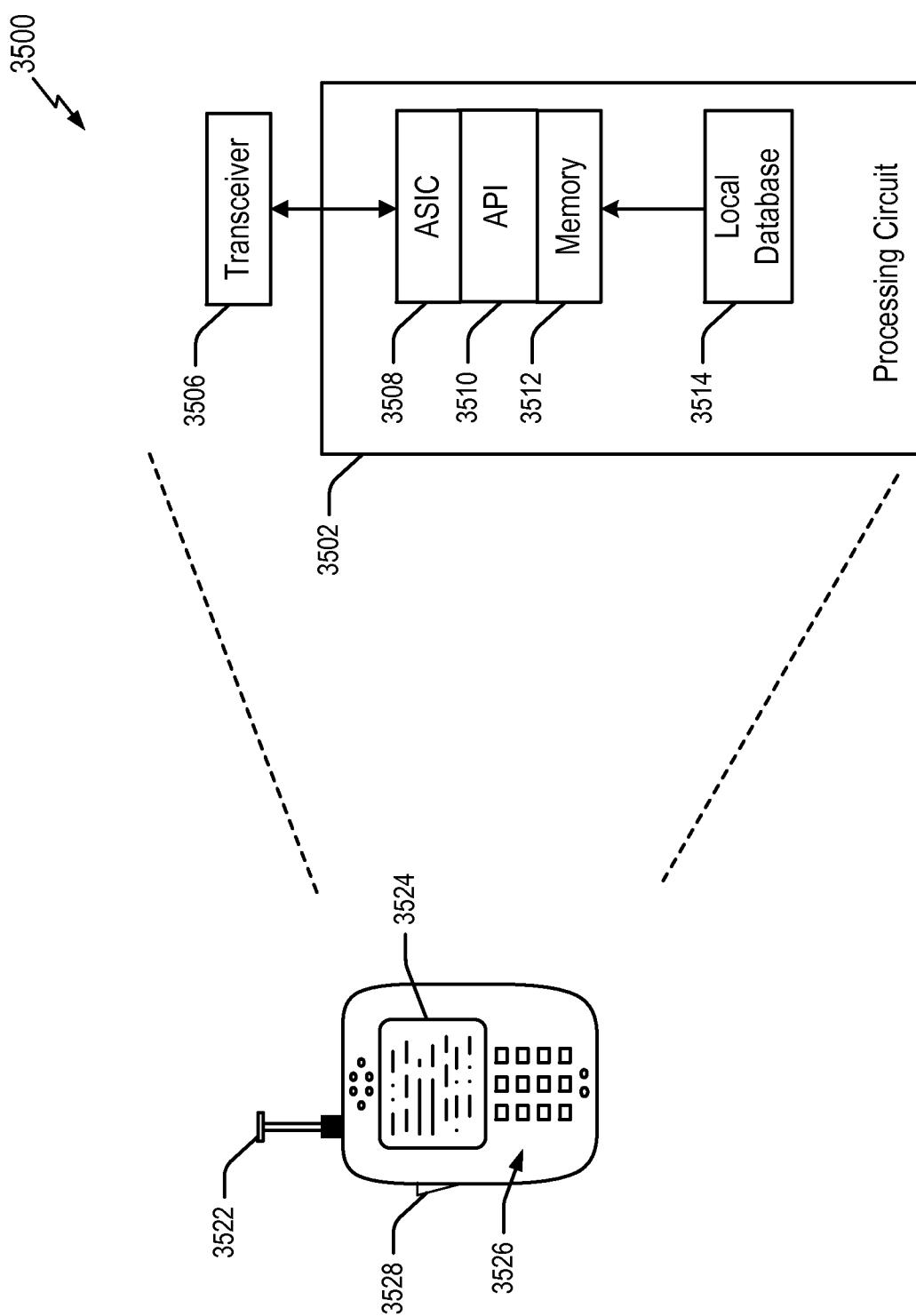

[0056] FIG. 35 is a diagram illustrating an apparatus that employs an *N*-Phase polarity encoded data link between devices within the apparatus in which one or more aspects of the disclosure may find application.

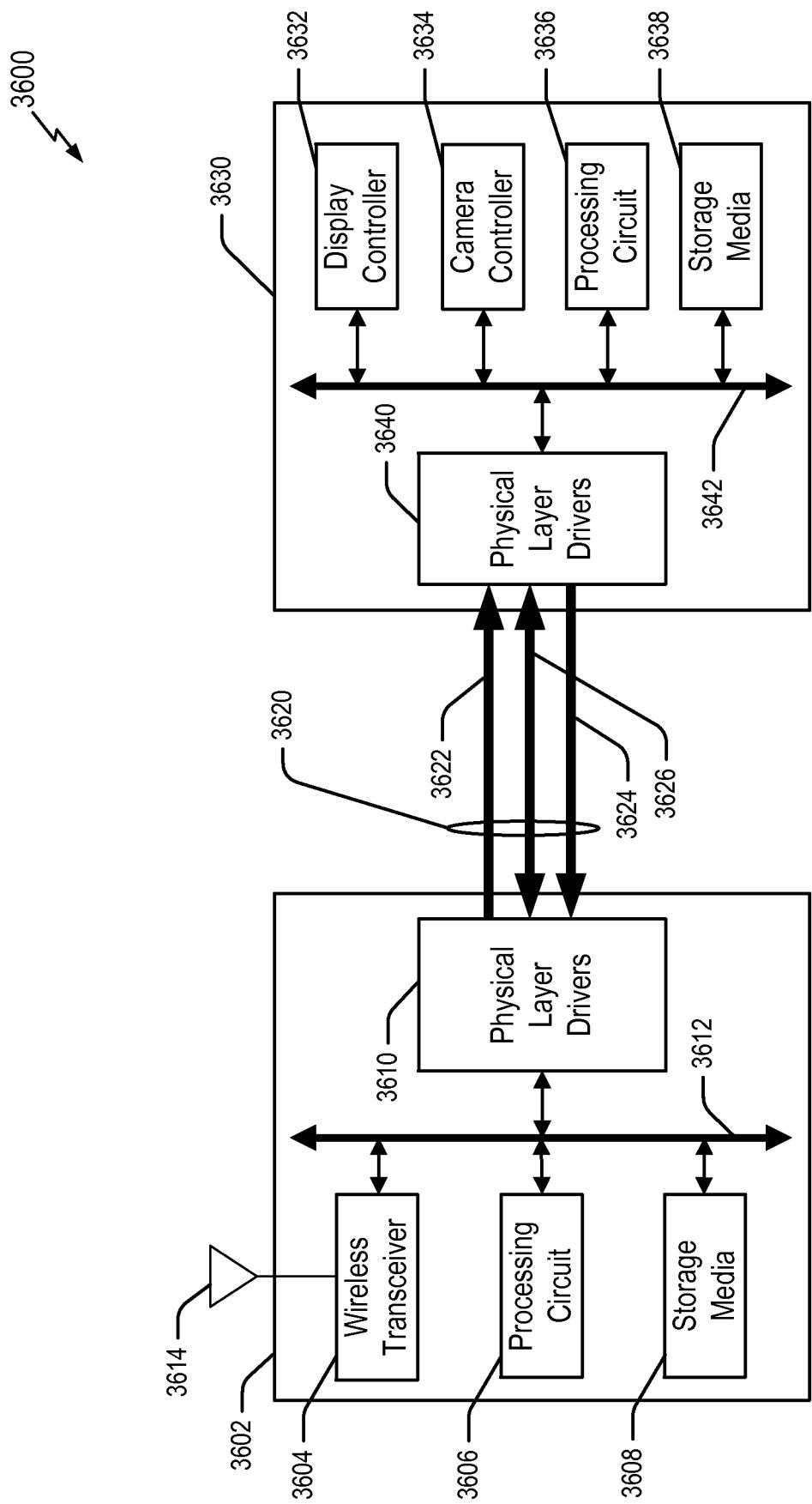

[0057] FIG. 36 is a block diagram illustrating a system architecture for an apparatus employing an *N*-Phase polarity encoded data link in which one or more aspects of the disclosure may find application.

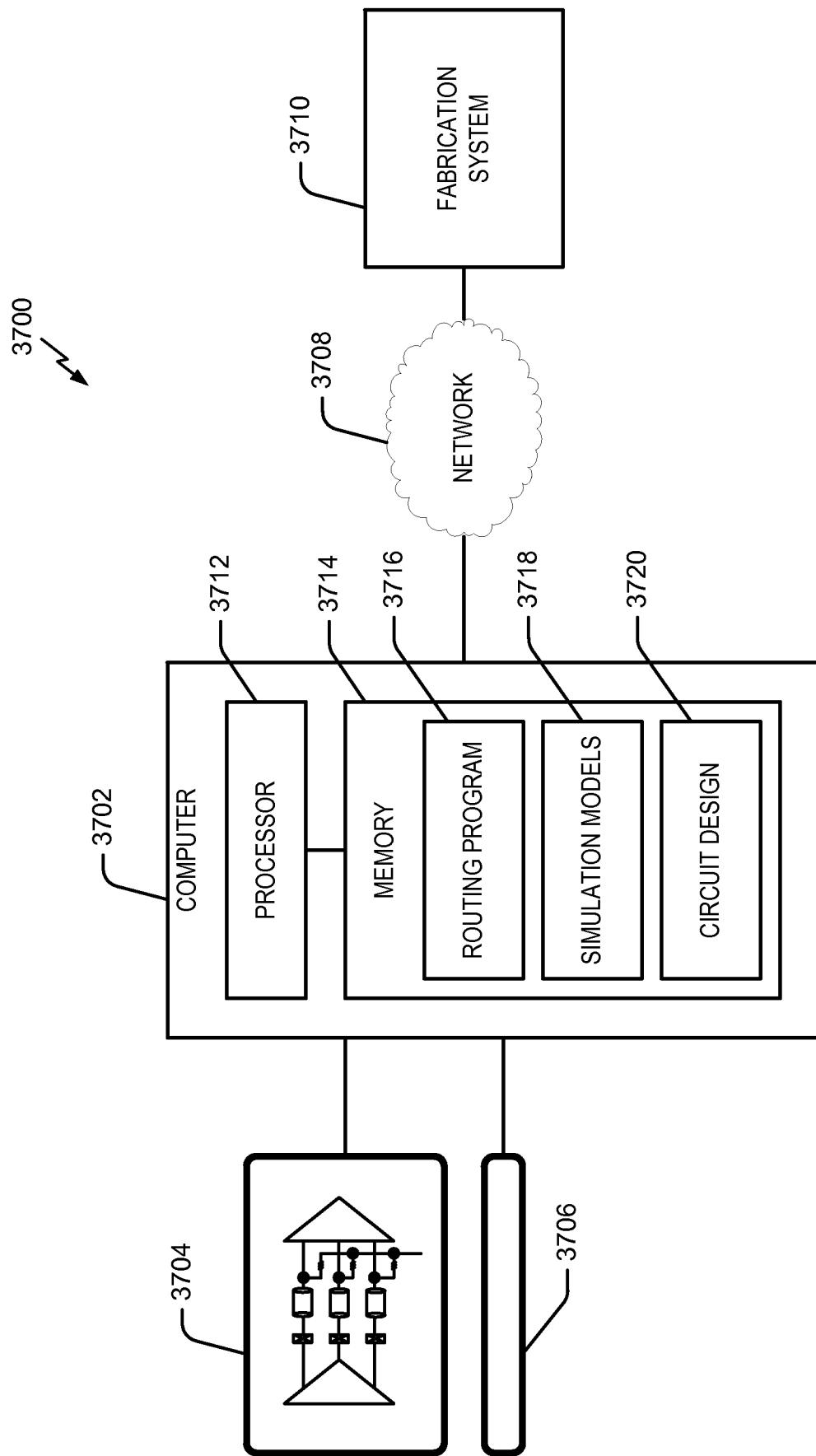

[0058] FIG. 37 is a block diagram illustrating an example of a circuit design system in which one or more aspects of the disclosure may find application.

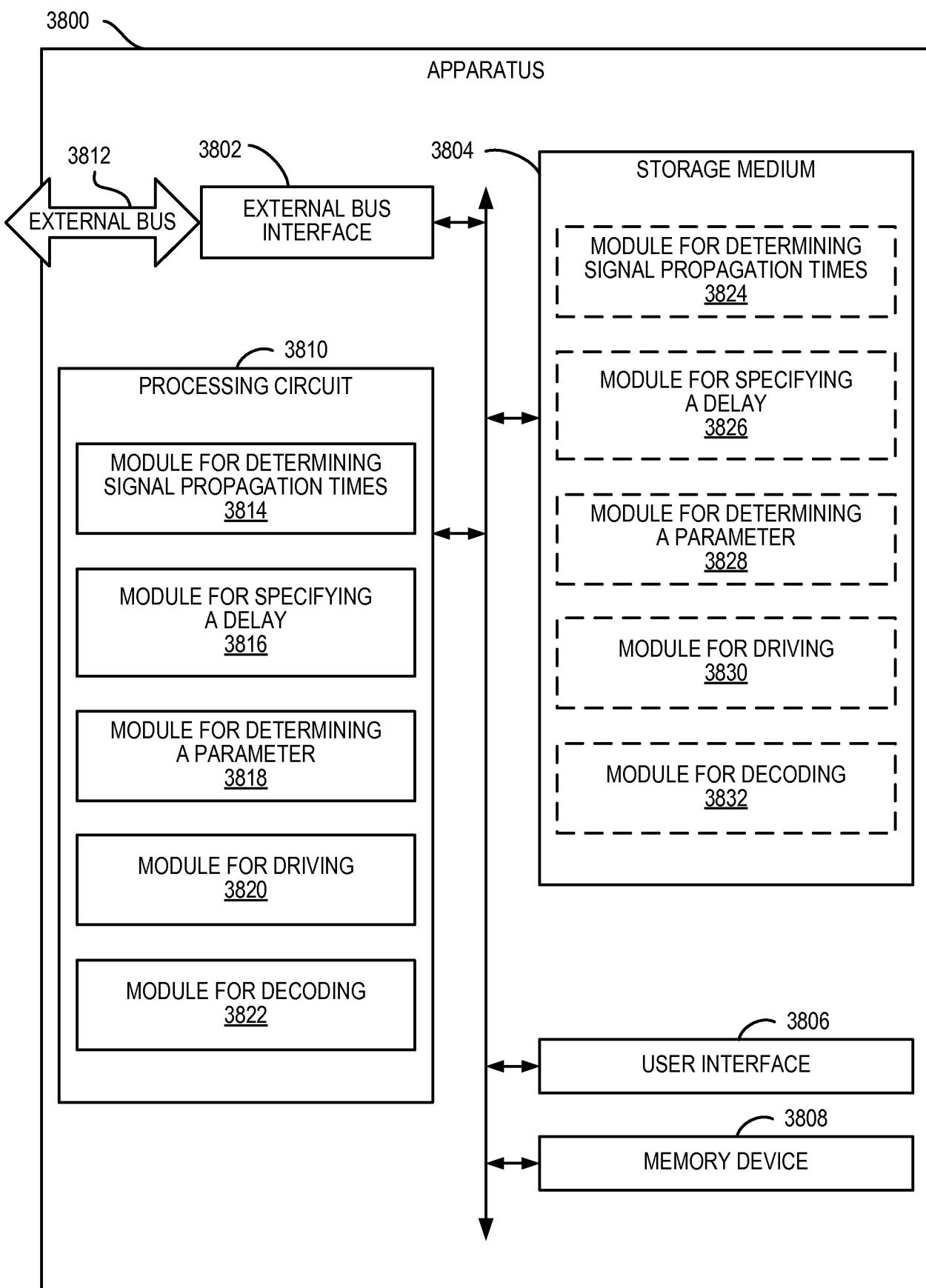

[0059] FIG. 38 is a block diagram illustrating select components of an apparatus configured to provide functionality in accordance with some aspects of the disclosure.

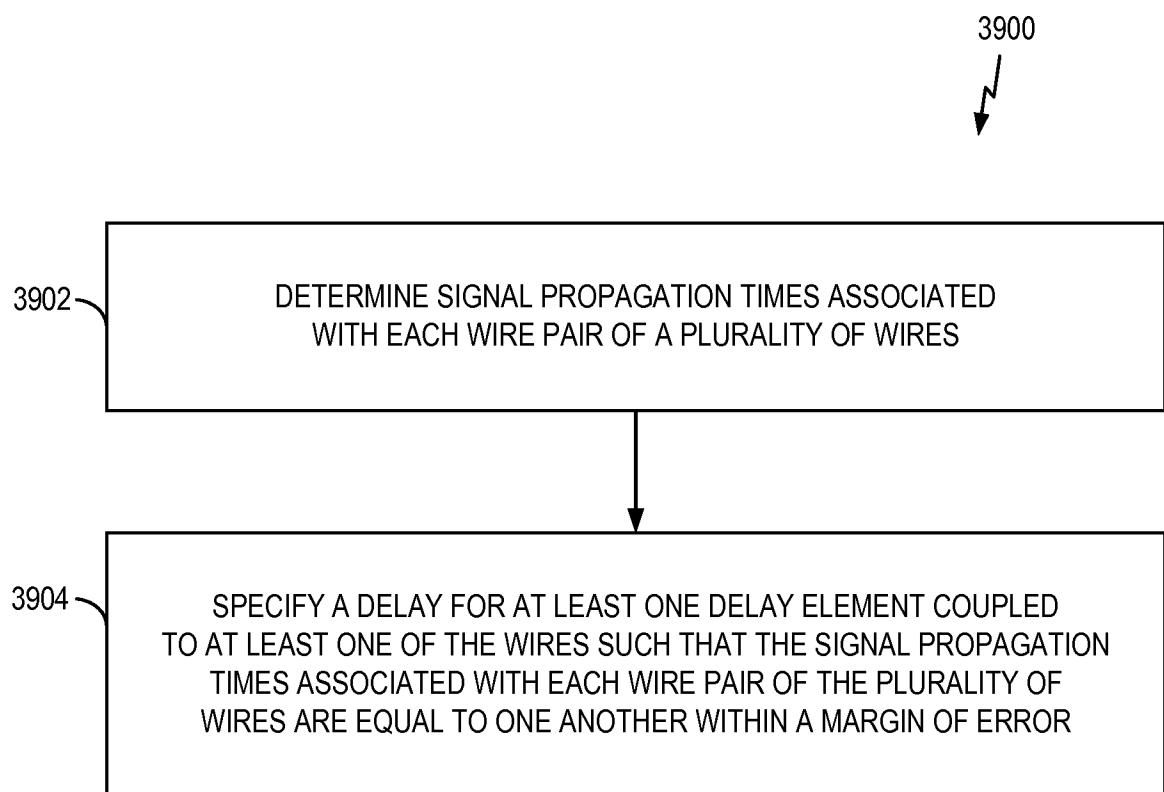

[0060] FIG. 39 is a flowchart illustrating a delay specification method in accordance with some aspects of the disclosure.

[0061] FIG. 40 is a flowchart illustrating a delay specification method in accordance with some aspects of the disclosure.

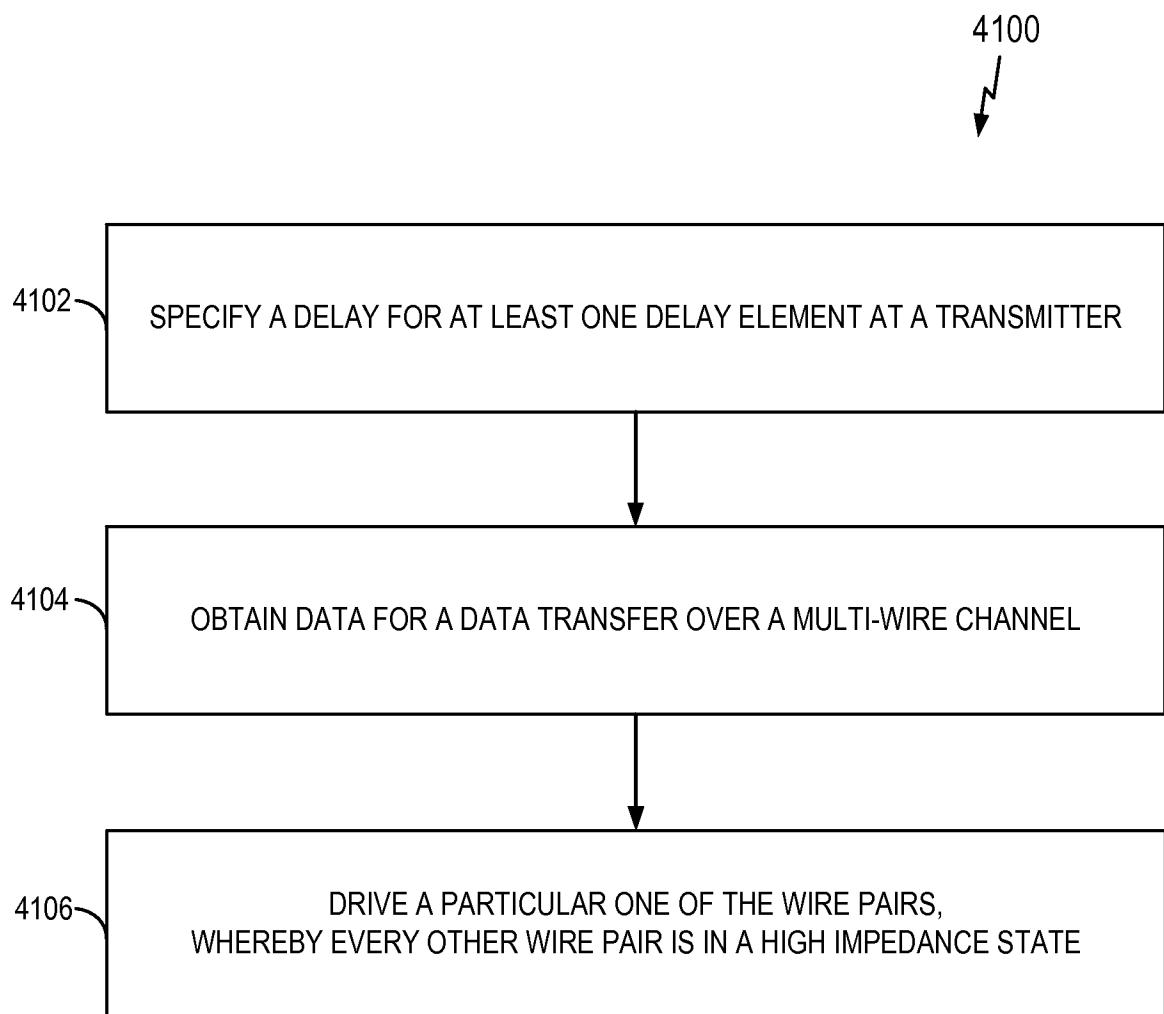

[0062] FIG. 41 is a flowchart illustrating a method for driving a multi-wire channel in accordance with some aspects of the disclosure.

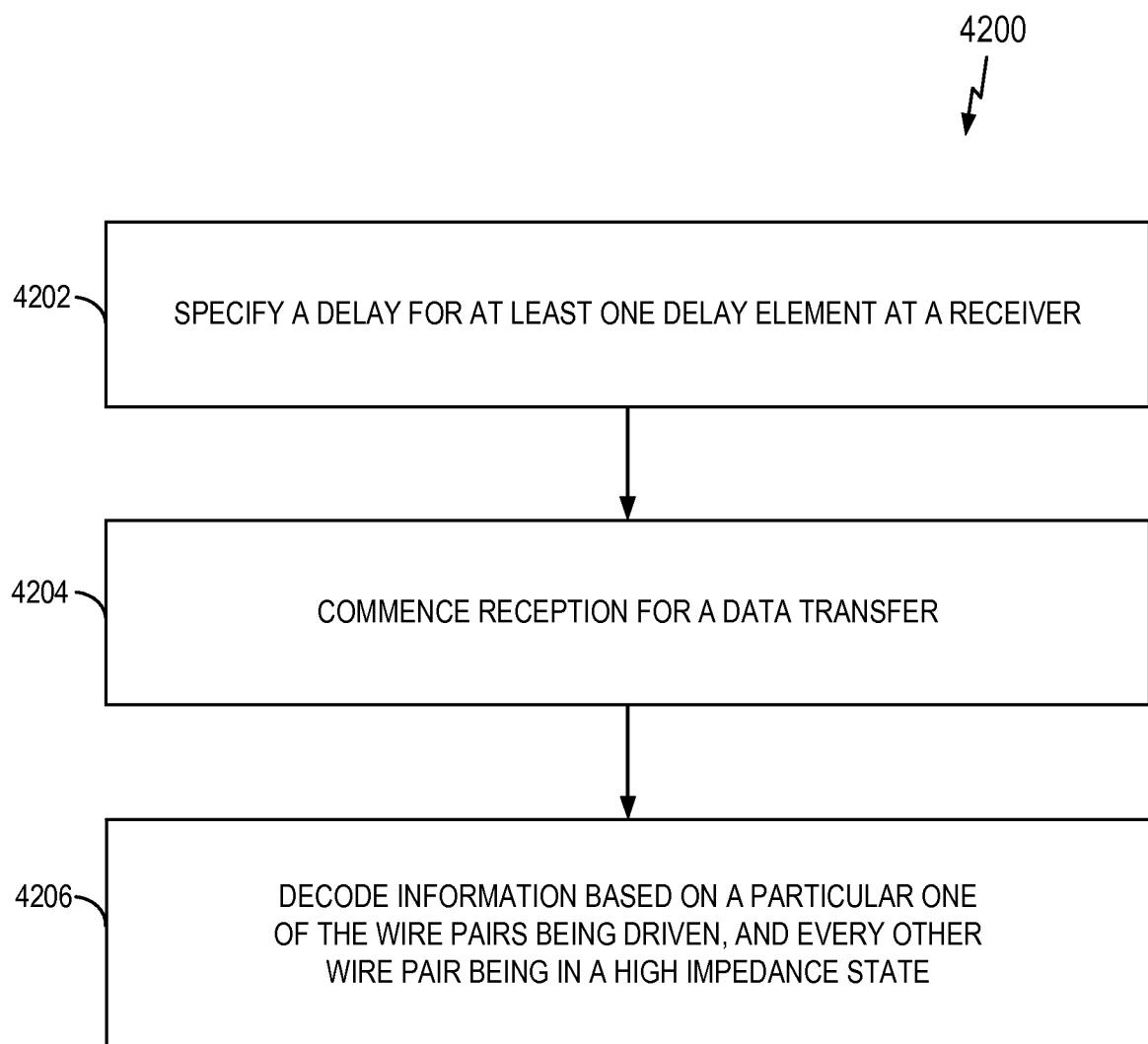

[0063] FIG. 42 is a flowchart illustrating a method for decoding multi-wire channel data in accordance with some aspects of the disclosure.

## DETAILED DESCRIPTION

**[0064]** The detailed description set forth below in connection with the appended drawings is intended as a description of various configurations and is not intended to represent the only configurations in which the concepts described herein may be practiced. The detailed description includes specific details for the purpose of providing a thorough understanding of various concepts. However, it will be apparent to those skilled in the art that these concepts may be practiced without these specific details. In some instances, well known structures and components are shown in block diagram form in order to avoid obscuring such concepts.

**[0065]** For purposes of illustration, various aspects of the disclosure will be discussed in the context of a multi-wire channel that employs three wires. However, the teachings herein are also applicable to multi-wire channels that have more than three wires. For convenience, a multi-wire channel may be referred to herein as an n-wire channel, where n represents three or more.

**[0066]** FIG. 1 illustrates one example of a multi-wire channel 100. In this example, a transmitter 102 sends data to a receiver 104 via a first wire 106, a second wire 108, and a third wire 110. The characteristic impedance of each of the first, second and third wires 106, 108, and 110 is represented by a first characteristic impedance 112, a second characteristic impedance 114, and a third characteristic impedance 116, respectively. The first, second and third wires 106, 108, and 110 are each terminated at the receiver 104 by a first termination resistor 118, a second termination resistor 120, and a third termination resistor 122, respectively, coupled to a common mode voltage  $V_{cm}$ .

**[0067]** Conventionally, the signal propagation time of a wire is calculated based on the length of the wire and other characteristics associated with the wire. For example, the characteristic impedance and the termination resistance of a wire affects the signal propagation times of signals traveling through the wire to some extent. For differential transmissions, precise system timing is maintained by ensuring that the signal propagation times of each wire of the wire pair are equal. In this way, both rails of the differential signal will be received at the receiver at the same time, thereby enabling the receiver to sample a received symbol over a relatively wide timing window.

**[0068]** In contrast, in a multi-wire channel, the conventional approach of ensuring that the signal propagation times for all wires of a channel are equal leads to less than

optimal signaling. This issue will be described in detail with further reference to FIG. 1 and reference to FIGS. 2 and 3.

**[0069]** In a three-wire channel, for a given data transfer (e.g., of a symbol or bit), the transmitter drives two of the wires and leaves the remaining wire in a high impedance state (e.g., floating). For the next data transfer, the transmitter again drives two of the wires and leaves the remaining wire in a high impedance state. However, the pair of wires used for any subsequent data transfer may be different from or the same as the pair of wires used for a previous data transfer. Through the use of such a multi-wire signaling scheme, improved data rates and/or transmission quality may be achieved as compared to a channel that employs a single wire or a differential pair.

**[0070]** Using the designations A, B, and C to refer to the first wire 106, the second wire 108, and the third wire 110 of FIG. 1, a given transmission over the channel 100 can involve wire pair A-B being driven, wire pair B-C being driven, or wire pair A-C being driven. As discussed in more detail below in conjunction with FIGS. 32 and 33, the transmitter 102 can encode data to be transmitted based on which wire pair is used for a given data transfer and any changes in the wire pair used from one data transfer to the next. For example, a transfer over wire pair A-B followed by a transfer over wire pair B-C can represent a certain value (e.g., binary 01). The receiver 104, in turn, is configured to properly interpret signals encoded in this manner and thereby decode the original data that was transmitted.

**[0071]** In practice, the different wire pairs A-B, B-C, and A-C may have different transmission characteristics. For example, the signal propagation time of one wire pair may be different from the signal propagation time of another wire pair. This difference may be due, at least in part, to the physical properties of the wires.

**[0072]** FIG. 2 illustrates a side sectional view 200 of three wires, again designated simply as A, B, and C, implemented on a substrate 202. The substrate 202 includes a dielectric material 204 having a thickness of 63 micrometers (um) and a ground plane 206 having a thickness of 21 um. Each wire is 100 um wide and 40 um thick. Different dimensions may be employed in different implementations.

**[0073]** In some implementations, the wires A, B, and C are conductive paths on a printed circuit board (PCB) and run parallel with one another (into the page in the example of FIG. 2). Thus, the view of FIG. 2 correlates, in some aspects, to the view 2-2 of FIG. 1 (although FIG. 1 is simply in the form a block diagram, and not an actual circuit). The wires A, B, and C can be implemented in other ways in other

implementations. For example, in some implementations, the wires A, B, and C are conductive paths on an integrated circuit (IC) die.

[0074] As indicated in FIG. 2, the distance from the wire A to the wire B is 100 um. Similarly, the distance from the wire B to the wire C is 100 um. However, the distance from the wire A to the wire C is 300 um. Since the signal propagation time of a differential signal traveling over a wire pair depends, at least in part, on the distance between the wires, a differential signal traveling over the wire pair A-B has a different (i.e., shorter) signal propagation time than a differential signal traveling over the wire pair A-C.

[0075] Keeping in mind that different wire pairs are used over a series of data transfers in a multi-wire channel, the symbols (or bits) transmitted over different wire pairs may arrive at the receiver at different times, relative to the receive clock. In other words, signals transmitted via a conventional multi-wire channel may be subject to jitter. Referring to FIG. 2, a differential signal on the wire pair A-C will travel at a slower velocity than a differential signal on the wire pair A-B. Consequently, at the receiver, there will be timing skew between the signals transmitted on the different pairs. Over a series of data transmissions using the different wire pairs, this skew manifests itself as jitter.

[0076] FIG. 3 illustrates, in a simplified manner, an example of an eye pattern 300 (also known as an eye diagram) corresponding to a simulation for a 3-wire channel based on the configuration of FIG. 2. The simulation is further based on a 10 inch long microstrip module, with a dielectric constant (Er) of 3.7, a tangent delta (tanD) of 0.02, a data rate of 1 Gigabit per second (Gbps), a rise/fall time of 100 ps (20% - 80%), a voltage amplitude of 250 millivolts (mV), pad capacitance (C<sub>pad</sub>) of 2 picoFarads (pF), and a common capacitance of 15 pF (see FIG. 30).

[0077] In the eye pattern 300, it may be seen that some of the transitions from one voltage level to another occur later than others. The width 302 of these transitions, collectively, is indicative of the jitter. For example, in this case, the jitter may be on the order of 160 picoseconds (ps).

[0078] In general, it is desirable to reduce the amount of jitter present in a communication system. By reducing jitter, timing margins for the system can be improved since symbols can be sampled over a wider window of time when jitter is low as opposed to when jitter is high.

**[0079]** The disclosure relates in some aspects to mitigating jitter and related timing issues in multi-wire signaling. Jitter is mitigated by ensuring that each unique wire pair of the n-wires in an n-wire channel has approximately the same signal propagation time within a threshold margin (e.g., within a margin of error).

**[0080]** In some aspects, this is achieved by adding delay to at least one of the wires. For example, in a 3-wire system, jitter can be reduced by incorporating additional delay (i.e., positive delay) on the center wire of the trio. Thus, to make the signal propagation time of each wire pair approximately equal (e.g., the propagation delay is the same for the wire pairs A-B, B-C, and A-C), the signal propagation time of the individual wires is made unequal (e.g., by adding delay to one of more of the individual wires).

**[0081]** In general, delay may be added anywhere along a wire to achieve the desired balancing of the signal propagation times between wire pairs. For example, FIG. 4 illustrates a communication system 400 including three-wire transmitter 402 and a three-wire receiver 404 where a first delay element 406 can be incorporated into the transmitter 402, a second delay element 408 can be incorporated into the communication medium between the transmitter 402 and the receiver 404, or a third delay element 410 can incorporated into the receiver 404. Here, the dashed boxes for the first though third delay elements 406 - 410 represent that each delay element is optional. That is, one or more of the first though third delay elements 406 - 410 could be used in a given implementation.

**[0082]** In FIG. 4, the three wires driven by the transmitter 402 are designated as TXA, TXB, and TXC (e.g., corresponding to the wires A, B, and C, of FIG. 2). Similarly, the three wires over which signals are received by the receiver 404 are designated as RXA, RXB, and RXC (e.g., again corresponding to the wires A, B, and C, of FIG. 2).

**[0083]** In implementations that employ the first delay element 406, signals carried by the middle wire TXB are delayed by the delay element 406. The signal carried by the wire TXA, the delayed signal carried by the wire TXB, and the signal carried by the wire TXC are coupled to a first driver 412, a second driver 414, and a third driver 416, respectively, that drive a first wire 418, a second wire 420, and a third wire 422 of an external bus.

**[0084]** In implementations that employ the second delay element 408, signals carried by the second wire 420 are delayed by the delay element 408. The signal carried by the first wire 418, the delayed signal carried by the second wire 420, and the signal carried

by the third wire 422 are coupled to a first receiver circuit 424, a second receiver circuit 426, and a third receiver circuit 428, respectively, of the receiver.

**[0085]** In implementations that employ the third delay element 410, signals output by the second receiver circuit 426 are delayed by the delay element 410. Thus, the signal driven by the first receiver circuit 424, the delayed signal driven by the second receiver circuit 426, and the signal driven by the third receiver circuit 428 are coupled to an input latch 432 of the receiver 404.

**[0086]** In the example of FIG. 4, the signal propagation time of interest for a given wire corresponds to the time that a signal on the wire is clocked out of an output latch 430 at the transmitter 402 (according to a transmit clock TX\_CLK) to the time the signal is clocked into the input latch 432 at the receiver 404 (according to a receive clock RX\_CLK). Thus, in this case, a delay element can be incorporated anywhere along the path of a wire between the output latch 430 and the input latch 432. The delay element may be a stand-alone component or embodied in another component. As an example of the latter case, a delay element can be embodied in an input/output (I/O) circuit such as a driver or receiver circuit.

**[0087]** FIG. 5 illustrates, in a simplified manner, an example of an eye pattern 500 corresponding to a simulation for a 3-wire channel where a 40 ps delay had been added to the center wire (e.g., by adding 4 - 5 millimeters of the length of the wire B of FIG. 2). The other parameters for the simulation are the same as for the simulation of FIG. 3 that does not incorporate this delay. Here, it may be seen that the jitter has been reduced as a result of increasing the delay on the center wire. For example, in this case, the width of the jitter 502 may be on the order of 135 picoseconds (ps), a decrease of 25 ps (approximately 16%).

**[0088]** Table 1 lists several examples of the jitter that results when other delay values are used in the simulation. As indicated, the delay of 40 ps results in the lowest jitter in this scenario.

| Data rate (Gbps) | RT/FT (20% - 80%) (ps) | Delay on Center wire (ps) | Total jitter (ps) | Eye height (mV) |

|------------------|------------------------|---------------------------|-------------------|-----------------|

| 1                | 100                    | 0                         | 160               | 194             |

| 1                | 100                    | +20                       | 160               | 194             |

| 1                | 100                    | +40                       | 135               | 194             |

|   |     |      |     |     |

|---|-----|------|-----|-----|

| 1 | 100 | +60  | 140 | 194 |

| 1 | 100 | +80  | 145 | 194 |

| 1 | 100 | +100 | 220 | 194 |

TABLE 1

[0089] A delay element may take different forms in different implementations. For example, some implementations employ passive delay elements, while other implementations employ active delay elements.

[0090] Examples of passive delay elements include, without limitation, a wire of a defined length and a delay line in the form of a coil of wire of a defined length. A passive delay line also may include capacitors, inductors, or other passive components. In some implementations, a delay element consists of a wire segment that is incorporated into the path of a wire to increase the length of the wire.

[0091] Thus, in some implementations, delay is provided for a wire by defining the physical properties of the wire (e.g., during the design stage). For example, one wire can be configured to have a longer length than another wire. Other physical properties that could be adapted to provide a desired delay include the width of the wire, the thickness of the wire, a dielectric constant of a dielectric upon which the wire rests, and the distance from the wire to a ground plane.

[0092] Examples of active delay elements include, without limitation, fixed delay lines that include active circuitry (e.g., transistors) and programmable delay devices. Thus, in some implementations, a delay element may be adjustable so that the delay imparted on a wire can be changed in the face of changes in operating conditions.

[0093] In implementations that employ an active delay element, the delay can be dynamically adjusted based on initial design criteria and/or based on one or more operating factors. These operating factors may include, without limitation, calibration feedback, signal frequency, signal rise/fall times, or path length.

[0094] FIG. 6 illustrates an example of a multi-wire system 600 that incorporates a passive delay element. A transmitter 602 communicates with a receiver 604 via a first wire 606, a second wire 608, and a third wire 610. The second wire 608 has been configured with a wire segment 612 to increase the overall length of the second wire 608. Thus, the wire segment 612 is a form of passive delay element since the additional length imparts delay on the second wire 608. That is, incorporation of the wire segment 612 increases the overall signal transmission time from one end of the second wire 608 to the other end.

**[0095]** FIG. 7 illustrates an example of a multi-wire system 700 that incorporates a delay line. A transmitter 702 communicates with a receiver 704 via a first wire 706, a second wire 708, and a third wire 710. A delay line 712 is in-line with the second wire 708. The delay line 712 may be passive or active, and imparts additional delay on the second wire 708. Accordingly, incorporation of the delay line 712 increases the overall signal transmission time from one end of the second wire 708 to the other end.

**[0096]** FIG. 8 illustrates an example of a multi-wire transmitter 802 that incorporates a controllable delay element. The transmitter 802 transmits data via a first wire 804, a second wire 806, and a third wire 808. A delay circuit 810 is in-line with the second wire 806. A delay controller 812 generates a control signal 814 that controls the amount of delay imparted on a signal passing through the delay circuit 810. An example of how the delay controller 812 can generate the control signal 814 is described below in conjunction with FIG. 11.

**[0097]** FIG. 9 illustrates an example of a multi-wire receiver 902 that incorporates a controllable delay element. The receiver 902 receives data via a first wire 904, a second wire 906, and a third wire 908. A delay circuit 910 is in-line with the second wire 906. A delay controller 912 generates a control signal 914 that controls the amount of delay imparted on a signal passing through the delay circuit 910. An example of how the delay controller 912 can generate the control signal 914 is described below in conjunction with FIG. 11.

**[0098]** FIG. 10 illustrates an example of a multi-wire communication system 1000 that incorporates a controllable delay element along the wire path between a transmitter 1002 and a receiver 1004. The transmitter 1002 transmits data to the receiver 1004 via a first wire 1006, a second wire 1008, and a third wire 1010. A delay circuit 1012 is in-line with the second wire 1008. A delay controller 1014 generates a control signal 1016 that controls the amount of delay imparted on a signal passing through the delay circuit 1012. An example of how the delay controller 1014 can generate the control signal 1016 will now be described with reference to FIG. 11.

**[0099]** FIG. 11 illustrates a delay control system 1100 where a delay controller 1102 generates at least one control signal 1104 to control a programmable delay circuit 1106. As indicated, the delay controller 1102 can generate the at least one control signal 1104 based on information 1108 that the delay controller 1102 retrieves from a memory device 1110 or based on information 1112 that the delay controller 1102 retrieves from

an active operation 1114. In other implementations, the delay controller 1102 can receive information from other sources.

**[00100]** The memory device 1110 includes a delay table 1116 having a list of delay values (or indications thereof) to be used by the programmable delay circuit 1106 during certain operating conditions. For example, the delay table 1116 can list the delay values to be used for particular data transfer rates, PVT (process, voltage and temperature) conditions, wire lengths, signal propagation times, applications, and so on. The delay table 1116 can be generated, for example, based on empirical studies or based on simulations that identify the optimal delay for each corresponding condition. Accordingly, for a given operating condition or configuration, the delay controller 1102 can select the appropriate delay value from the delay table 1116.

**[00101]** In some aspects, the applications referred to above relate to the type of peer device (e.g., a memory device, a processor, an I/O device, etc.) that is receiving or transmitting data over a multi-wire channel. Here, different applications may correspond to different operating conditions (e.g., data rates, signal propagation times, or wire lengths) that affect how the delay is to be set. Other types of applications could be used to specify desired delay values in other implementations.

**[00102]** The memory device 1110 includes parameters 1118 to be used by the delay controller 1102 to determine a delay value. For example, the parameters 1118 can list the current data transfer rates, PVT (process, voltage and temperature) conditions, wire lengths, signal propagation times, applications, and so on for a multi-wire system that is controlled by the delay controller 1102. In this case, for a given operating condition or configuration, the delay controller 1102 can determine (e.g., calculate using a designated algorithm) the appropriate delay value to be used based on the parameters 1118. The parameters 1118 can be stored in the memory device 1110, for example, during system initialization in the case of static parameters (e.g., wire length) or during active operations in the case of dynamic parameters. As an example of the latter case, a component (e.g., a sensor, a processing circuit, a timing controller, etc.) of a multi-wire system controlled by the delay controller 1102 can generate the parameters 1118 (e.g., current data rate, temperature, etc.) and store the parameters 1118 in the memory device 1110.

**[00103]** In some implementations, an active operation 1114 directly sends the information 1112 about a current operating condition to the delay controller 1102. For example, a component (e.g., a sensor, a processing circuit, a timing controller, etc.) of a

multi-wire system controlled by the delay controller 1102 can generate an indication of an operating condition (e.g., current data rate, temperature, etc.) and send the indication to the delay controller 1102. As discussed above, the delay controller 1102 can then determine an appropriate delay value to be used given the current operating conditions.

**[00104]** A calibration mechanism can also be employed to determine a delay value. FIG. 12 illustrates a communication system 1200 where a transmitter 1202 sends data to a receiver 1204 via a multi-wire channel 1206. A data processor 1208 processes input data 1210 to generate data transmitted via the multi-wire channel 1206. As discussed herein, one of the wires includes a delay element 1212 that is controlled by a delay controller 1214.

**[00105]** At the receiver 1204, a data processor 1216 processes data received via the multi-wire channel 1206 to provide output data 1218. In addition, the data processor 1216 provides information 1220 relating to the received data (e.g., the data itself or some characteristic of the data) to a feedback controller 1222. Based on the information 1220, the feedback controller 1222 sends feedback 1224 to the delay controller 1214 that the delay controller 1214 uses to generate a control signal 1226 for controlling the delay element 1212.

**[00106]** In some implementations, the feedback controller 1222 provides a loopback function. For example, during a calibration operation, the data processor 1208 may send a series of patterns over the multi-wire channel 1206. Through the use of appropriate patterns, the signal propagation times on the multi-wire channel 1206 can be estimated. For example, patterns sent at a relatively high rate may be received with more errors if the jitter associated with the corresponding received signal is high. Consequently, the delay controller 1214 can compare the data that was received by the receiver 1204 (as fed back through the feedback 1224) with the data sent by the transmitter 1202 to determine the error rate. To this end, the data processor 1208 can send calibration information 1228 (e.g., calibration data patterns) to the delay controller 1214. The delay controller 1214 can then adjust the delay value during the calibration operation to determine the delay value that results in the lowest error rate.

**[00107]** A calibration scheme also can be employed at a receiver. FIG. 13 illustrates a receiver 1302 that receives data via a multi-wire channel 1304. As discussed herein, one of the wires includes a delay element 1306 that is controlled by a delay controller 1308. A data processor 1310 processes the received data to provide output data 1312. In addition, the data processor 1310 provides information 1314 relating to the received

data (e.g., the data itself or some characteristic of the data) to a feedback controller 1316. Based on the information 1314, the feedback controller 1316 sends feedback 1318 to the delay controller 1308 that the delay controller 1318 uses to generate a control signal 1320 for controlling the delay element 1306.

**[00108]** In some implementations, the feedback controller 1316 provides a loopback function. Thus, during a calibration operation, a transmitter (not shown) may send a series of patterns over the multi-wire channel 1304. In this case, corresponding calibration information 1322 (e.g., the data patterns) may have been previously provided to the receiver 1302. Consequently, the delay controller 1308 can compare the data that was received by the receiver 1302 (as fed back through the feedback 1318) with the calibration information 1322. Again, the delay controller 1308 can adjust the delay value during the calibration operation to determine the delay value that results in the lowest error rate.

**[00109]** In the previous figures, delay is illustrated as being imparted on a single wire. In practice, delay may be imparted on multiple wires. For example, different delays may be imparted on different wires so that one or more of the wires has a longer signal propagation time as compared to at least one other one of the wires. In this way, the signal propagation times of each of the corresponding wire pairs can be matched in accordance with the teachings herein. FIGS. 14 and 15 illustrate a transmitter 1402 and a receiver 1502, respectively, each of which employs multiple delay elements.

**[00110]** In FIG. 14, signals on a first wire 1404 are delayed by a first delay element 1406, signals on a second wire 1408 are delayed by a second delay element 1410, and signals on a third wire 1412 are delayed by a third delay element 1414. In this case, a delay controller 1416 generates several control signals 1418 that individually control the delay in a given one of the first, second, or third delay elements 1406, 1410, or 1414.

**[00111]** In FIG. 15, signals on a first wire 1504 are delayed by a first delay element 1506, signals on a second wire 1508 are delayed by a second delay element 1510, and signals on a third wire 1512 are delayed by a third delay element 1514. In this case, a delay controller 1516 generates several control signals 1518 that individually control the delay in a given one of the first, second, or third delay elements 1506, 1510, or 1514.

**[00112]** As mentioned above, the teachings herein are applicable to multi-wire channels that employ more than three wires. FIG. 16 illustrates an example of a four-wire channel 1600. A transmitter 1602 sends data to a receiver 1604 via a first wire 1606, a second wire 1608, a third wire 1610, and a fourth wire 1612. The characteristic

impedance of each of the first, second, third, and fourth wires 1606, 1608, 1610, and 1612 is represented by a first characteristic impedance 1614, a second characteristic impedance 1616, and a third characteristic impedance 1618, and a fourth characteristic impedance 1620, respectively. The first, second, third, and fourth wires 1606, 1608, 1610, and 1612 are each terminated at the receiver 1604 by a first termination resistor 1622, a second termination resistor 1624, a third termination resistor 1626, and a fourth termination resistor 1628, respectively, coupled to a common mode voltage  $V_{cm}$ .

**[00113]** In a four-wire channel, for a given data transfer (e.g., of a symbol or bit), the transmitter drives two of the wires and leaves the remaining two wires in a high impedance state (e.g., floating). For the next data transfer, the transmitter again drives two of the wires and leaves the remaining wires in a high impedance state. As with a three-wire channel, the pair of wires used for any subsequent data transfer may be different from or the same as the pair of wires used for a previous data transfer.

**[00114]** Using the designations A, B, C, and D to refer to the first wire 1606, the second wire 1608, the third wire 1610, and the fourth wire 1612, a given transmission over the channel 1600 can involve wire pair A-B being driven, wire pair A-C being driven, wire pair A-D being driven, wire pair B-C being driven, wire pair B-D being driven, or wire pair C-D being driven. Thus, due to the larger number of potential combinations, it may be seen that more information can be transmitted over a four-wire channel as compared to a three-wire channel.

**[00115]** Again, however, the different wire pairs may have different transmission characteristics. For example, the signal propagation time of one wire pair may be different from the signal propagation time of another wire pair due to the different distances that may exist between the corresponding wires for each of the wire pairs. For example, it should be appreciated that for four wires routed in parallel on a substrate, the wire pair consisting of the two outer wires will be even further apart than in the three-wire example of FIG. 2. Thus, jitter may be even more pronounced in this case.

**[00116]** FIG. 17 illustrates, in a simplified manner, a circuit 1700 that includes four wires (e.g., transmission lines) 1702, 1704, 1706, and 1708. As shown in this single layer example, the two center wires 1704 and 1706 are of the same length, but longer than the two outer wires 1702 and 1708. By adding delay to the center wires 1704 and 1706 in this manner, the signal propagation times of each of the six unique wire pairs in the circuit 1700 can be matched in accordance with the teachings herein. It should be appreciated that in other implementations delay can be added to the center wires 1704

and 1706 using one or more of the other techniques described herein (e.g., active delay elements, changing other physical characteristics of the wires, using multiple layers, and so on).

**[00117]** It should be appreciated that jitter issues exists for the general n-wire scenario, where “n” is three or more. FIG. 18 illustrates an example of an n-wire channel 1800. A transmitter 1802 sends data to a receiver 1804 via a first wire 1806, a second wire 1808, and any other wires up to an n-th wire 1810.

**[00118]** In the n-wire channel 1800, for a given data transfer (e.g., of a symbol or bit), the transmitter 1802 drives two of the wires and leaves the remaining wires in a high impedance state (e.g., floating). The pair of wires used for any subsequent data transfer may be different from or the same as the pair of wires used for a previous data transfer. Again, the signal propagation time of one wire pair may be different from the signal propagation time of another wire pair due to the different distances that may exist between the corresponding wires for each of the wire pairs. Thus, jitter may be a significant issue in an n-wire channel.

**[00119]** The techniques described herein can be generally extended to the n-channel scenario. As illustrated in the communication system 1900 of FIG. 19, a delay element 1902 can be incorporated into any of the n-wires, at any appropriate location along each wire. By adding delay to one or more wires, the signal propagation times for each wire pair can be matched. For example, in the absence of an empirical model that precisely describes which wire should be delay and the extent of that delay (e.g., for higher orders of “n”) a trial and error algorithm or a regression-based algorithm may be employed to identify these parameters.

**[00120]** FIGs. 20 - 22 illustrate simplified examples of circuits 2000 - 2200, respectively, that include five wires (e.g., transmission lines). For the five wire scenario utilizing a single layer, the center three wires are longer than the outer two wires. By adding delay to the center wires in this manner, the signal propagation times of each of the unique wire pairs in a given one of the circuits 2000 - 2200 can be matched in accordance with the teachings herein. The exact amount by which the center wires are made longer can be determined, for example, by simulation. It should be appreciated that in other implementations delay can be added to the center wires using one or more of the other techniques described herein (e.g., active delay elements, changing other physical characteristics of the wires, using multiple layers, and so on). FIGs. 20 - 22

illustrate three different examples with different relative lengths added to the center wires.

**[00121]** The circuit 2000 of FIG. 20 includes wires 2002, 2004, 2006, 2008, and 2010. The center wires 2004, 2006, and 2008 are longer than the two outer wires 2002 and 2010. In this case, the center wires 2004 and 2008 are of the same length, but the center wire 2006 has a different length. The two outer wires 2002 and 2010 have the same length.

**[00122]** The circuit 2100 of FIG. 21 includes wires 2102, 2104, 2106, 2108, and 2110. The center wires 2104, 2106, and 2108 are longer than the two outer wires 2102 and 2110. In this case, the center wires 2104 and 2108 are of the same length, but the center wire 2106 has a different length. The two outer wires 2102 and 2110 have the same length.

**[00123]** The circuit 2200 of FIG. 22 includes wires 2202, 2204, 2206, 2208, and 2210. The center wires 2204, 2206, and 2208 are longer than the two outer wires 2202 and 2210. In this case, all of the center wires 2204, 2206, and 2208 are of the same length. The two outer wires 2202 and 2210 have the same length.

**[00124]** As mentioned above, a variety of characteristics may be adjusted to control the signal propagation time associated with wire pairs in a multi-wire channel. FIGS. 23 - 26 illustrate several of these characteristics.

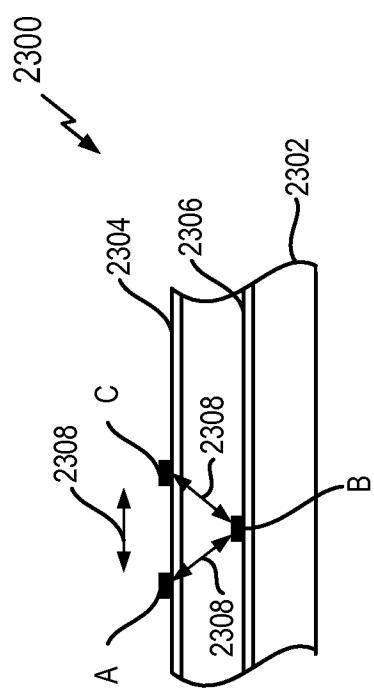

**[00125]** FIG. 23 illustrates that the jitter issue described herein may be mitigated by ensuring that all wires are equidistance from each other. FIG. 23 depicts a side sectional view 2300 of three wires, designated A, B, and C, implemented on different layers of a substrate 2302. Specifically, the first wire A and the third wire C are on a first layer 2304 and the second wire B is on a second layer 2306. As represented by the lines 2308, each wire is equidistance to the other wires.

**[00126]** In practice, routing all wires in the precise manner of FIG. 23 at the circuit design stage may be difficult due to routing constraints. However, such an approach may be employed for at least for a portion of a wire path, whereby the other techniques described herein are used to add any additional delay that may be desired. Advantageously, such a combined approach may reduce the amount of delay that needs to be added to a wire since the timing skews on wires that are at least partially balanced can be expected to be lower.

**[00127]** FIG. 24 illustrates a side sectional view 2400 of three wires, designated A, B, and C, implemented on a substrate 2402. The signal propagation time associated with a

wire depends at least in part on the distance of the wire to a ground plane. Accordingly, at the circuit design stage, the distance 2404 of a metal layer 2406 (and, hence, the wires on that layer) to a ground plane 2408 may be controlled to add delay to any wires (the wire B in this example) on the metal layer 2406. Furthermore, the other techniques described herein may be used in conjunction with the technique of FIG. 24 to add any additional delay that may be desired.

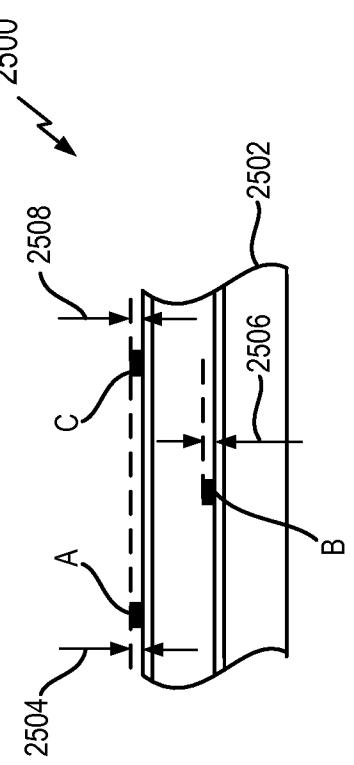

**[00128]** FIG. 25 illustrates a side sectional view 2500 of three wires, designated A, B, and C, implemented on a substrate 2502. The signal propagation time associated with a wire depends at least in part on the thickness of the wire. Accordingly, at the circuit design stage, any one of a thickness 2504 of the first wire A, a thickness 2506 of the second wire B, or a thickness 2508 of the third wire C may be controlled to add delay to the corresponding wire. Furthermore, the other techniques described herein may be used in conjunction with the technique of FIG. 25 to add any additional delay that may be desired.

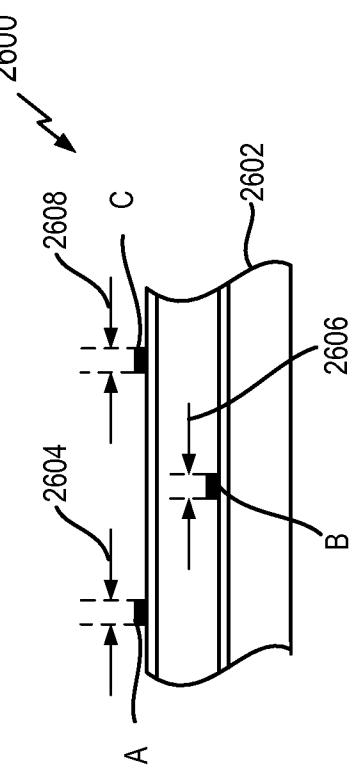

**[00129]** FIG. 26 illustrates a side sectional view 2600 of three wires, designated A, B, and C, implemented on a substrate 2602. The signal propagation time associated with a wire depends at least in part on the width of the wire. Accordingly, at the circuit design stage, any one of a width 2604 of the first wire A, a width 2606 of the second wire B, or a width 2608 of the third wire C may be controlled to add delay to the corresponding wire. Furthermore, the other techniques described herein may be used in conjunction with the technique of FIG. 26 to add any additional delay that may be desired.

**[00130]** The signal propagation time associated with a set of wires also depends at least in part on the spacing between the wires. Accordingly, the spacing between two or more wires may be controlled to add delay to a given wire. Furthermore, the other techniques described herein may be used in conjunction with wire spacing to add any additional delay that may be desired.

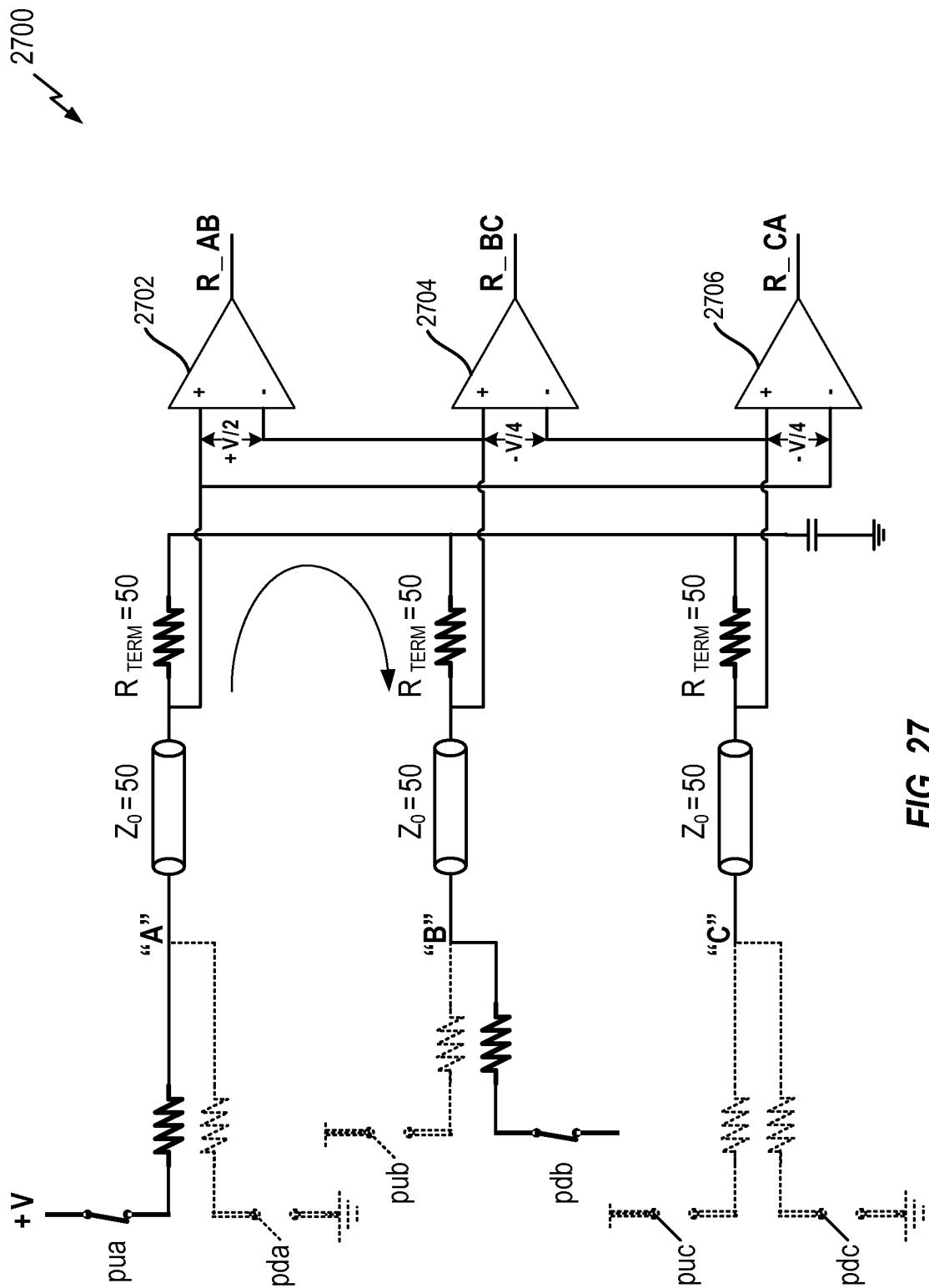

**[00131]** Referring now to FIGS. 27 - 29, additional details of multi-wire signaling will be described in the context of a three-wire channel (e.g., for C-PHY).

**[00132]** FIG. 27 illustrates a system 2700 that uses a trio of wires designated A, B, and C. Through the use of pull-up (pu) switches and pull-down (pd) switches, for each symbol to be transmitted, two of the wires are driven to opposite levels while the third wire is terminated to a mid-level. Specifically, the switches pua and pda are used to pull up or pull down, respectively, the wire A. The switches pub and pdb are used to pull up

or pull down, respectively, the wire B. The switches puc and pdc are used to pull up or pull down, respectively, the wire C.

[00133] At a receiver, three OP amps are coupled to the wires A, B, and C to decode the received symbol information. A first OP amp 2702 generates a signal R\_AB indicative of the difference between the wires A and B. A second OP amp 2704 generates a signal R\_BC indicative of the difference between the wires B and C. A third OP amp 2706 generates a signal R\_CA indicative of the difference between the wires C and A.

[00134] In FIG. 27, the signal propagation times of interest corresponds to the wire path from the switches to the inputs of the OP amps. Thus, a delay element as taught herein may be incorporated into any section of these paths.

[00135] A more detailed driver circuit 2800 is shown in FIG. 28. In general, the pull-up control signals (PUA, PUB, and PUC) correspond to the pull-up control signals (pua, pub, and puc) of FIG. 27. Similarly, the pull-down control signals (PDA, PDB, and PDC) generally correspond to the pull-down control signals (pda, pdb, and pdc) of FIG. 27.

[00136] In some aspects, the driver circuit 2800 is similar to a conventional self-series terminated (SST) driver. Compared to the system 2700 of FIG. 27, an extra series resistor branch (controlled by control signals PM[A,B,C]) is added to maintain the mid-level wire output impedance at 50 ohms. Irrespective of the impedance of any switch MOSFETs, R/2N is set equal to 50 ohm for impedance matching.

[00137] FIG. 29 illustrates three examples of waveforms generated by the system 2700. The left-hand waveforms correspond to the signals driven on the wires A, B, and C for the three cases. The right-hand waveforms correspond to the outputs of the OP amps 2702 - 2706 for each of the three cases.

[00138] The use of such a signaling scheme will be described in more detail in conjunction with the system-level description provided in FIGS. 30 - 36.

[00139] In FIG. 30, a system 3000 illustrates transmitter components, channel components, and receiver components associated with a sample implementation of a three-wire channel. An encoder 3002 encodes C-PHY data 3004 and sends the encoded data to a pre-driver 3006. The pre-driven signals are driven onto an external bus by driver I/O circuits 3008, 3010, and 3012. Corresponding pad capacitances (Cp) are indicated for each wire of the external bus. Delays D1 3014, D2 3016, and D3 3018 correspond to propagation delay times for wires A, B, and C, respectively, of the three-

wire channel. An additional PCB delay 3020 corresponding to the delay imparted on the wires A, B, and C implemented in a PCB is also represented. At the receive section, corresponding pad capacitances ( $C_p$ ) are again indicated for each wire of the bus, as well as the termination resistors and common capacitance ( $C_{comm}$ ) for the termination circuit. Drivers 3022, 3024, and 3026 correspond to the respective OP amps 2702, 2704, and 2706 of FIG. 27. A clock generator 3028 derives a clock signal RSYM\_CLK from the signals output by the drivers 3022, 3024, and 3026. A decoder 3030 then generates signals (POLARITY, PHASE, AND SAME\_PHASE) corresponding to the C-PHY data transmitted by the transmit side. FIGS. 31 and 34 illustrate example of a transmit side and a receive side, respectively, of the system 3000 in more detail.

**[00140]** FIGS. 31 - 34 describe multi-Phase data encoding and decoding methods involving a plurality of wires (i.e.,  $M$  wires). The  $M$  wires typically include three or more wires. The  $M$  wires may include conductive traces on a circuit board or within a conductive layer of a semiconductor integrated circuit (IC) device. The  $M$  wires may be divided into a plurality of transmission groups, each group encoding a portion of a block of data to be transmitted. An  $N$ -Phase encoding scheme is defined in which bits of data are encoded in Phase transitions and polarity changes on the  $M$  wires. In one example, an  $N$ -Phase encoding scheme for a 3-wire system may include three Phase states and two polarities, providing 6 states and 5 possible transitions from each state. Deterministic voltage and/or current changes may be detected and decoded to extract data from the  $M$  wires. Decoding does not rely on independent wires, or pairs of wires and timing information can be derived directly from Phase and/or polarity transitions in the  $M$  wires.  $N$ -Phase polarity data transfer can be applied to any signaling interface, such as electrical, optical and radio frequency (RF) interfaces, for example.

**[00141]** FIG. 31 is a diagram 3100 illustrating an example of an  $M$ -wire,  $N$ -Phase polarity encoding transmitter configured for  $M=3$  and  $N=3$ . The example of 3-wire, 3-Phase encoding is selected solely for the purpose of simplifying descriptions of certain aspects of this disclosure. The principles and techniques disclosed for 3-wire, 3-Phase encoders can be applied in other configurations of  $M$ -wire,  $N$ -Phase polarity encoders.

**[00142]** When  $N$ -Phase polarity encoding is used, connectors such as signal wires 3110a, 3110b and 3110c on an  $M$ -wire bus may be undriven, driven positive, or driven negative. An undriven signal wire 3110a, 3110b or 3110c may be in a high-impedance state. An undriven signal wire 3110a, 3110b or 3110c may be driven to a voltage level that lies substantially halfway between the positive and negative voltage levels provided

on driven signal wires. An undriven signal wire 3110a, 3110b or 3110c may have no current flowing through it. In the example illustrated in FIG. 31, each signal wire 3110a, 3110b and 3110c may be in one of three states (denoted as +1, -1, and 0) using drivers 3108. In one example, drivers 3108 may include unit-level current-mode drivers. In another example, drivers 3108 may drive opposite polarity voltages on two signals 3110a and 3110b while the third signal 3110c is at high impedance and/or pulled to ground. For each transmitted symbol interval, at least one signal is in the undriven (0) state, while the number of signals driven positive (+1 state) is equal to the number of signals driven negative (-1 state), such that the sum of current flowing to the receiver is always zero. For each pair of consecutive symbol transmission intervals, at least one signal wire 3110a, 3110b or 3110c has a different state in the two symbol transmission intervals.

**[00143]** In the example depicted in FIG. 31, 16-bit data 3118 is input to a mapper 3102, which maps the input data 3118 to 7 symbols 3112 for transmitting sequentially over the signal wires 3110a, 3110b and 3110c. The 7 symbols 3112 may be serialized, using parallel-to-serial converters 3104 for example. An *M*-wire, *N*-Phase encoder 3106 receives 7 symbols 3112 produced by the mapper one symbol at a time and computes the state of each signal wire 3110a, 3110b and 3110c for each symbol interval. The encoder 3106 selects the states of the signal wires 3110a, 3110b and 3110c based on the input symbol and the previous states of signal wires 3110a, 3110b and 3110c.

**[00144]** The use of *M*-wire, *N*-Phase encoding permits a number of bits to be encoded in a plurality of symbols where the bits per symbol is not an integer. In the simple example of a 3-wire system, there are 3 available combinations of 2 wires that may be driven simultaneously, and 2 possible combinations of polarity on the pair of simultaneously driven wires, yielding 6 possible states. Since each transition occurs from a current state, 5 of the 6 states are available at every transition. The state of at least one wire is required to change at each transition. With 5 states,  $\log_2(5) \approx 2.32$  bits may be encoded per symbol. Accordingly, a mapper may accept a 16-bit word and convert it to 7 symbols because 7 symbols carrying 2.32 bits per symbol can encode 16.24 bits. In other words, a combination of seven symbols that encodes five states has  $5^7$  (78,125) permutations. Accordingly, the 7 symbols may be used to encode the  $2^{16}$  (65,536) permutations of 16 bits.

**[00145]** FIG. 32 illustrates an example of signaling 3200 employing a 3-Phase modulation data-encoding scheme based on the circular state transition diagram 3250.

According to the data-encoding scheme, a 3-Phase signal may rotate in two directions and may be transmitted on three wires 3110a, 3110b and 3110c. Each of the three signals is independently driven on the wires 3110a, 3110b, 3110c. Each of the three signals includes the 3-Phase signal, with each signal on each wire 3110a, 3110b and 3110c being 120 degrees out of Phase relative to the signals on the other two wires 3110a, 3110b and 3110c. At any point in time, each of the three wires 3110a, 3110b, 3110c is in a different one of the states {+1, 0, -1}. At any point in time, each of the three wires 3110a, 3110b, 3110c in a 3-wire system is in a different state than the other two wires. When more than three wires are used, two or more pairs of wires may be in the same state. The illustrated encoding scheme also encodes information in the polarity of the two wires 3110a, 3110b and/or 3110c that are actively driven to the +1 and -1 states. Polarity is indicated at 3208 for the sequence of states depicted.

**[00146]** At any Phase state in the illustrated three-wire example, exactly two of the wires 3110a, 3110b, 3110c carry a signal which is effectively a differential signal for that Phase state, while the third wire 3110a, 3110b or 3110c is undriven. The Phase state for each wire 3110a, 3110b, 3110c may be determined by voltage difference between the wire 3110a, 3110b or 3110c and at least one other wire 3110a, 3110b and/or 3110c, or by the direction of current flow, or lack of current flow, in the wire 3110a, 3110b or 3110c. As shown in the state transition diagram 3250, three Phase states ( $S_1$ ,  $S_2$  and  $S_3$ ) are defined. A signal may flow clockwise from Phase state  $S_1$  to Phase state  $S_2$ , Phase state  $S_2$  to Phase state  $S_3$ , and/or Phase state  $S_3$  to Phase state  $S_1$  and the signal may flow counter-clockwise from Phase state  $S_1$  to Phase state  $S_3$ , Phase state  $S_3$  to Phase state  $S_2$ , and/or Phase state  $S_2$  to Phase state  $S_1$ . For other values of  $N$ , transitions between the  $N$  states may optionally be defined according to a corresponding state diagram to obtain circular rotation between state transitions.

**[00147]** In the example of a three-wire, 3-Phase communications link, clockwise rotations ( $S_1$  to  $S_2$ ), ( $S_2$  to  $S_3$ ), and/or ( $S_3$  to  $S_1$ ) at a state transition may be used to encode a logic 1, while counter-clockwise rotations ( $S_1$  to  $S_3$ ), ( $S_3$  to  $S_2$ ), and/or ( $S_2$  to  $S_1$ ) at the state transition may be used to encode a logic 0. Accordingly a bit may be encoded at each transition by controlling whether the signal is “rotating” clockwise or counter-clockwise. For example, a logic 1 may be encoded when the three wires 3110a, 3110b, 3110c transition from Phase state  $S_1$  to Phase state  $S_2$  and a logic 0 may be encoded when the three wires 3110a, 3110b, 3110c transition from Phase state  $S_1$  to Phase state  $S_3$ . In the simple three-wire example depicted, direction of rotation may be

easily determined based on which of the three wires 3110a, 3110b, 3110c is undriven before and after the transition.

**[00148]** Information may also be encoded in the polarity of the driven wires 3110a, 3110b, 3110c or direction of current flow between two wires 3110a, 3110b, 3110c. Signals 3202, 3204, and 3206 illustrate voltage levels applied to wires 3110a, 3110b, 3110c, respectively at each Phase state in a three-wire, 3-Phase link. At any time, a first wire 3110a, 3110b, 3110c is coupled to a positive voltage (+V, for example), a second wire 3110a, 3110b, 3110c is coupled to a negative voltage (-V, for example), while the third wire 3110a, 3110b, 3110c may be open-circuited or otherwise undriven. As such, one polarity encoding state may be determined by the current flow between the first and second wires 3110a, 3110b, 3110c or the voltage polarities of the first and second wires 3110a, 3110b, 3110c. In some embodiments, two bits of data may be encoded at each Phase transition 3210. A decoder may determine the direction of signal Phase rotation to obtain the first bit, and the second bit may be determined based on the polarity difference between two of the signals 3202, 3204 and 3206. The decoder having determined direction of rotation can determine the current Phase state and the polarity of the voltage applied between the two active connectors 3110a, 3110b and/or 3110c, or the direction of current flow through the two active wires 3110a, 3110b and/or 3110c.

**[00149]** In the example of the three-wire, 3-Phase link described herein, one bit of data may be encoded in the rotation, or Phase change in the three-wire, 3-Phase link, and an additional bit may be encoded in the polarity of two driven wires. Certain embodiments, encode more than two bits in each transition of a three-wire, 3-Phase encoding system by allowing transition to any of the possible states from a current state. Given three rotational Phases and two polarities for each Phase, 6 states are defined, such that 5 states are available from any current state. Accordingly, there may be  $\log_2(5) \cong 2.32$  bits per symbol (transition) and the mapper may accept a 16-bit word and convert it to 7 symbols.

**[00150]** FIG. 33 is a state diagram 3300 illustrating 6 states and 30 possible state transitions in the example of a 3-wire, 3-Phase communication link. FIG. 33 expands on the state transition diagram 3250 in FIG. 32 by depicting all possible states 3302, 3304, 3306, 3312, 3314 and 3316. These states 3302, 3304, 3306, 3312, 3314 and 3316 include positive polarity and negative polarity versions of the Phase states  $S_1$ ,  $S_2$  and  $S_3$  illustrated in the Phase transition diagram 3250 of FIG. 32. For clarity, the set of Phase/polarity states are labeled alphabetically and includes  $\{+x, -x, +y, -y, +z, -z\}$

where, for example,  $+x$  and  $-x$  represent states with the same Phase state but different polarity. As shown in the model state element 3320, each state 3302, 3304, 3306, 3312, 3314 and 3316 in the state diagram 3300 includes a field 3322 showing the voltage state of signals 3202, 3204 and 3206, which are transmitted on wires 3110a, 3110b and 3110c, respectively. For example, in state 3302 ( $+x$ ) signal 3202 =  $+1$ , signal 3204 =  $-1$  and signal 3206 =  $0$ . Also shown in FIG. 33 are the 5 possible transition paths between the states 3302, 3304, 3306, 3312, 3314 and 3316, including by way of example, the transition path 3324 between  $-x$  state 3312 and  $-y$  state 3314.

**[00151]** FIG. 34 is a block schematic drawing 3400 illustrating an example of a receiver in a 3-Phase PHY. Comparators 3402 and decoder 3404 are configured to provide a digital representation of the state of each of three transmission lines 3412a, 3412b and 3412c, as well as the change in the state of the three transmission lines compared to the state transmitted in the previous symbol period. As can be seen from the illustrated example, the voltage of each connector 3412a, 3412b or 3412c may be compared to the voltages of the other two connectors 3412a, 3412b and/or 3412c to determine the state of each connector 3412a, 3412b or 3412c, such that the occurrence of a transition may be detected and decoded by the decoder 3404 based on the outputs of the comparators 3402. Seven consecutive states are assembled by serial to parallel convertors 3406, which produce sets of 7 symbols to be processed by demapper 3408 to obtain 16 bits of data that may be buffered in the FIFO 3410.

**[00152]** Certain aspects may be applicable to communications links deployed between electronic components, which may include subcomponents of devices such as telephones, mobile computing devices, appliances, automobile electronics, avionics systems, etc. Referring to FIG. 35, for example, an apparatus 3500 employing  $M$ -wire,  $N$ -Phase encoding may include a processing circuit 3502 that is configured to control operation of the apparatus 3500. The processing circuit 3502 may access and execute software applications and control logic circuits and other devices within the apparatus 3500. In one example, the apparatus 3500 may include a wireless communication device that communicates through an RF communications transceiver 3506 with a radio access network (RAN), a core access network, the Internet and/or another network. The communications transceiver 3506 may be operably coupled to a processing circuit 3502. The processing circuit 3502 may include one or more IC devices, such as an application specific IC (ASIC) 3508. The ASIC 3508 may include one or more processing devices, logic circuits, and so on. The processing circuit 3502 may include and/or be coupled to