【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第2区分

【発行日】平成25年7月18日(2013.7.18)

【公開番号】特開2012-13973(P2012-13973A)

【公開日】平成24年1月19日(2012.1.19)

【年通号数】公開・登録公報2012-003

【出願番号】特願2010-150797(P2010-150797)

【国際特許分類】

G 09 G 3/30 (2006.01)

G 09 G 3/20 (2006.01)

【F I】

G 09 G 3/30 J

G 09 G 3/20 6 2 4 B

G 09 G 3/20 6 4 1 D

G 09 G 3/20 6 2 3 C

G 09 G 3/20 6 2 2 D

G 09 G 3/20 6 1 1 H

G 09 G 3/20 6 4 2 A

G 09 G 3/20 6 2 2 C

G 09 G 3/20 6 2 1 A

G 09 G 3/20 6 2 3 D

G 09 G 3/20 6 7 0 J

【手続補正書】

【提出日】平成25年6月4日(2013.6.4)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

発光素子と、該発光素子に対して入力された映像信号電圧に応じた電流印加を行う駆動トランジスタを有する画素回路が、マトリクス状に配置されて成る画素アレイと、

上記画素アレイ上で列状に配設される各信号線に、信号線電圧として、少なくとも映像信号電圧及び基準電圧を供給する信号セレクタと、

上記画素アレイ上で行状に配設される各第1の書き制御線に、上記画素回路への上記信号線電圧の入力制御に用いられる第1の走査パルスを出力する第1の書きスキャナと、

上記画素アレイ上で列状に配設される各第2の書き制御線に、上記第1の走査パルスとともに上記画素回路への上記信号線電圧の入力制御に用いられる第2の走査パルスを出力する第2の書きスキャナと、

を備えた表示装置。

【請求項2】

上記画素回路は、

上記駆動トランジスタが、ドレン・ソース間に駆動電圧が印加されることで上記発光素子に対してゲート・ソース間電圧に応じた電流印加を行う構成とされるとともに、

上記駆動トランジスタのゲート・ソース間に接続され上記信号線から入力される上記映像信号電圧を保持する保持容量と、

上記信号線と上記駆動トランジスタのゲートノードの間に直列接続される第1，第2の

スイッチ素子と、

をさらに備え、

上記第1のスイッチ素子は、上記第1の走査パルスによってオン／オフされ、

上記第2のスイッチ素子は、上記第2の走査パルスによってオン／オフされる請求項1

に記載の表示装置。

【請求項3】

上記第1，第2の走査パルスによって、上記第1，第2のスイッチ素子が共にオンとさ

れることで、上記信号線電圧が上記駆動トランジスタのゲートノードに入力される請求項

2に記載の表示装置。

【請求項4】

上記各画素回路では、

上記信号線電圧が上記映像信号電圧とされている期間に、上記第1，第2の走査パルス

によって上記第1，第2のスイッチ素子が共にオンとされることで、上記映像信号電圧の

入力が行われるとともに、

上記第1の走査パルスによる上記第1のスイッチ素子のオン期間に対して、上記第2の

走査パルスによる上記第2のスイッチ素子のオン期間の長さを調整することで、映像信号

電圧の入力の際に行われる上記駆動トランジスタの移動度補正動作の期間を、画素回路毎

に調整する請求項3に記載の表示装置。

【請求項5】

上記各画素回路では、

上記信号線電圧が上記基準電圧されている期間に、上記第1，第2の走査パルスによ

って、上記第1，第2のスイッチ素子が共にオンとされることで、上記基準電圧が上記駆動

トランジスタのゲートノードに入力され、かつ上記駆動トランジスタへの駆動電圧の印加

が行われることで、上記保持容量に上記駆動トランジスタの閾値電圧を保持させる閾値補

正動作が行われるとともに、

上記第1の走査パルスによる上記第1のスイッチ素子のオン期間に対して、上記第2の

走査パルスによる上記第2のスイッチ素子のオン期間の長さを調整することで、上記閾値

補正動作の実行期間を、画素回路毎に調整する請求項3に記載の表示装置。

【請求項6】

上記各画素回路では、

上記信号線電圧が上記基準電圧されている期間に、上記第1，第2の走査パルスによ

って、上記第1，第2のスイッチ素子が共にオンとされることで、上記基準電圧が上記駆動

トランジスタのゲートノードに入力され、かつ上記駆動トランジスタへの駆動電圧の印加

が行われることで、上記保持容量に上記駆動トランジスタの閾値電圧を保持させる閾値補

正動作が行われるとともに、

上記閾値補正動作の開始直前に、上記駆動トランジスタへの駆動電圧の印加が行われ、

上記第1の走査パルスにより上記第1のスイッチ素子がオンとされ、上記第2の走査パルス

により上記第2のスイッチ素子がオフとされる期間を設けることで、上記駆動トランジ

スタのソース電圧及びゲート電圧を上昇させる請求項3に記載の表示装置。

【請求項7】

上記各画素回路では、

上記信号線電圧が上記映像信号電圧とされている期間に、上記第1，第2の走査パルス

によって上記第1，第2のスイッチ素子が共にオンとされることで、上記映像信号電圧の

入力が行われるとともに、

上記映像信号電圧の入力の際の上記第2の走査パルス波形は、上記第2のスイッチ素子

がオフとなるタイミングが映像信号電圧値に応じて変動する波形とされている請求項3に

記載の表示装置。

【請求項8】

上記各画素回路では、

上記信号線電圧が上記映像信号電圧とされている期間に、上記第1，第2の走査パルス

によって上記第1，第2のスイッチ素子が共にオンとされることで、上記映像信号電圧の入力が行われるとともに、

上記第1のスイッチ素子がオンとなるタイミングより、上記第2のスイッチ素子がオンとなるタイミングが先となるように、上記第1，第2の走査パルスのタイミングが設定されることで、上記第1のスイッチ素子がオンとなるタイミングから、上記映像信号電圧の入力が開始される請求項3に記載の表示装置。

#### 【請求項9】

上記第2の走査パルスのローレベル電圧は、上記第1の走査パルスのローレベル電圧よりも低い電圧とされている請求項3に記載の表示装置。

#### 【請求項10】

発光素子と、

該発光素子に対して、入力された映像信号電圧に応じた電流印加を行う駆動トランジスタと、

上記駆動トランジスタのゲート・ソース間に接続され信号線から入力される上記映像信号電圧を保持する保持容量と、

上記信号線と上記駆動トランジスタのゲートノードの間に直列接続される第1，第2のトランジスタと、

を備え、

上記第1のトランジスタのゲートノードは、行方向に隣接する画素回路の第1のトランジスタのゲートノードと接続され、

上記第2のトランジスタのゲートノードは、列方向に隣接する画素回路の第2のトランジスタのゲートノードと接続される画素回路。

#### 【請求項11】

発光素子と、該発光素子に対して入力された映像信号電圧に応じた電流印加を行う駆動トランジスタを有する画素回路が、マトリクス状に配置されて成る画素アレイと、

上記画素アレイ上で列状に配設される各信号線に、信号線電圧として、少なくとも映像信号電圧及び基準電圧を供給する信号セレクタと、

上記画素アレイ上で行状に配設される各第1の書き制御線に、第1の走査パルスを出力する第1の書きスキャナと、

上記画素アレイ上で列状に配設される各第2の書き制御線に、第2の走査パルスを出力する第2の書きスキャナと、

を備えた表示装置の表示駆動方法として、

上記第1，第2の走査パルスが連携して、各画素回路への上記信号線電圧の入力制御を行い、各画素回路では、入力された上記映像信号電圧及び上記基準電圧を用いて上記発光素子の発光駆動動作を行う表示駆動方法。

#### 【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0006

【補正方法】変更

【補正の内容】

【0006】

また上記各画素回路では、上記信号線電圧が上記映像信号電圧とされている期間に、上記第1，第2の走査パルスによって上記第1，第2のスイッチ素子が共にオンとされることで、上記映像信号電圧の入力が行われるとともに、上記第1の走査パルスによる上記第1のスイッチ素子のオン期間に対して、上記第2の走査パルスによる上記第2のスイッチ素子のオン期間の長さを調整することで、映像信号電圧の入力の際に行われる上記駆動トランジスタの移動度補正動作の期間を、画素回路毎に調整する。

#### 【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0007

【補正方法】変更

【補正の内容】

【0007】

また上記各画素回路では、上記信号線電圧が上記基準電圧されている期間に、上記第1，第2の走査パルスによって、上記第1，第2のスイッチ素子が共にオンとされることで、上記基準電圧が上記駆動トランジスタのゲートノードに入力され、かつ上記駆動トランジスタへの駆動電圧の印加が行われることで、上記保持容量に上記駆動トランジスタの閾値電圧を保持させる閾値補正動作が行われるとともに、上記第1の走査パルスによる上記第1のスイッチ素子のオン期間に対して、上記第2の走査パルスによる上記第2のスイッチ素子のオン期間の長さを調整することで、上記閾値補正動作の実行期間を、画素回路毎に調整する

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0008

【補正方法】変更

【補正の内容】

【0008】

また上記各画素回路では、上記信号線電圧が上記基準電圧されている期間に、上記第1，第2の走査パルスによって、上記第1，第2のスイッチ素子が共にオンとされることで、上記基準電圧が上記駆動トランジスタのゲートノードに入力され、かつ上記駆動トランジスタへの駆動電圧の印加が行われることで、上記保持容量に上記駆動トランジスタの閾値電圧を保持させる閾値補正動作が行われるとともに、上記閾値補正動作の開始直前に、上記駆動トランジスタへの駆動電圧の印加が行われ、上記第1の走査パルスにより上記第1のスイッチ素子がオンとされ、上記第2の走査パルスにより上記第2のスイッチ素子がオフとされる期間を設けることで、上記駆動トランジスタのソース電圧及びゲート電圧を上昇させる。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0072

【補正方法】変更

【補正の内容】

【0072】

このような移動度に起因する閾値補正バラツキを解消するには、移動度の小さい画素回路10については、閾値補正動作を促進することが有効である。

そこで移動度の小さい画素回路10については、図14の様に、期間L T 3 aの1回目の閾値補正時間が短くなるように、第2走査パルスvWSのパルスP1の幅を短くする。

基本的に、1回目の閾値補正動作では、開始前の駆動トランジスタTdのゲート・ソース間電圧Vgsが最も大きく、ソース電圧Vsの上昇も早い。

ここで、移動度小の画素回路について、1回目の閾値補正動作期間を短くするということは、移動度大の画素との関係でみれば、1回目の閾値補正終了時点の駆動トランジスタTdのゲート・ソース間電圧Vgsの差を大きくすることを意味する。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0094

【補正方法】変更

【補正の内容】

【0094】

[9. 变形例]

以上、第1～第6の実施の形態について説明したが、本発明は上記各例に限定されるも

のではない。

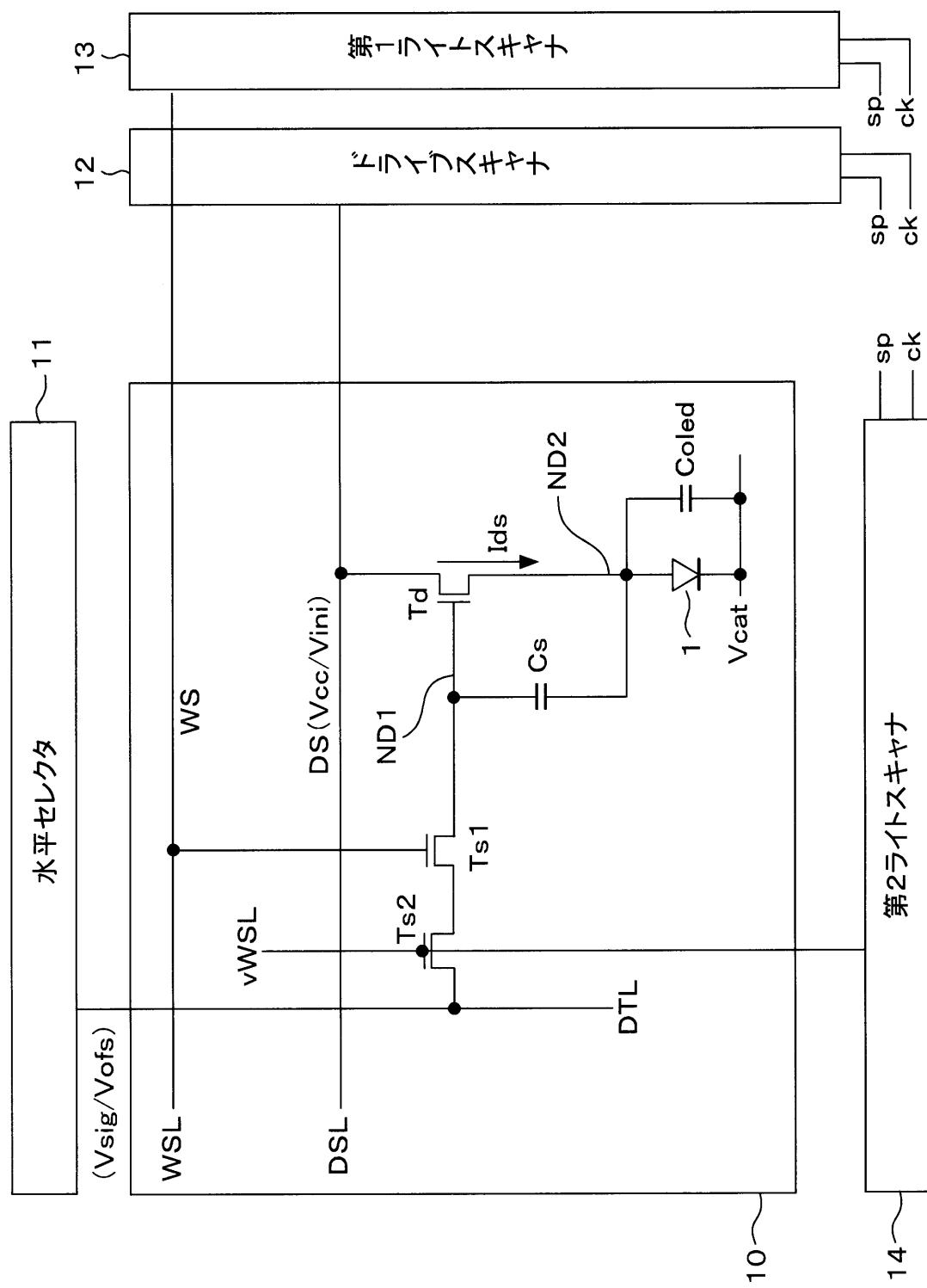

画素回路 1 0 の構成は図 2 に限定されない。例えば図 2 2 の構成でもよい。図 2 の場合は、信号線 D T L 側にサンプリングトランジスタ T s 1、ノード N D 1 側にサンプリングトランジスタ T s 2 を接続した構成であるが、図 2 2 は、逆に、信号線 D T L 側にサンプリングトランジスタ T s 2、ノード N D 1 側にサンプリングトランジスタ T s 1 を接続した構成としている。この回路構成の場合も、上記各例の動作が同様に実現される。

但し、第 2 走査パルス v W S に制御されるサンプリングトランジスタ T s 2 はオン / オフが頻繁に切り替わる。すると、図 2 のようにノード N D 1 側にサンプリングトランジスタ T s 2 を接続すると、ノード N D 1 にカップリングが入りやすく、駆動トランジスタ T d のゲート・ソース間電圧 V g s に影響を与えやすい。この点を考慮する場合は図 2 2 の構成のほうが適切である。

【手続補正 7】

【補正対象書類名】図面

【補正対象項目名】図 2 2

【補正方法】変更

【補正の内容】

【図 2 2】