(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6534557号

(P6534557)

(45) 発行日 令和1年6月26日(2019.6.26)

(24) 登録日 令和1年6月7日(2019.6.7)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 618B |

| HO1L 27/088  | (2006.01) | HO1L 27/088 | 331E |

| HO1L 21/8234 | (2006.01) | HO1L 27/06  | 102A |

| HO1L 27/06   | (2006.01) | HO1L 29/78  | 617U |

| HO1L 21/336  | (2006.01) | HO1L 29/78  | 617N |

請求項の数 7 (全 48 頁) 最終頁に続く

(21) 出願番号

特願2015-85631 (P2015-85631)

(22) 出願日

平成27年4月20日(2015.4.20)

(65) 公開番号

特開2015-216367 (P2015-216367A)

(43) 公開日

平成27年12月3日(2015.12.3)

審査請求日 平成30年4月3日(2018.4.3)

(31) 優先権主張番号 特願2014-91703 (P2014-91703)

(32) 優先日 平成26年4月25日(2014.4.25)

(33) 優先権主張国 日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 肥塚 純一

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

(72) 発明者 島 行徳

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

(72) 発明者 神長 正美

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

酸化物半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第1の絶縁膜と、第2の絶縁膜と、第3の絶縁膜と、を有し、

前記酸化物半導体膜は、第1の領域と、第2の領域と、第3の領域と、第4の領域と、第5の領域と、を有し、

前記第1の領域は、前記第1の導電膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第2の領域は、前記第1の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第3の領域は、前記第3の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第4の領域は、前記第2の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第5の領域は、前記第2の導電膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第1の絶縁膜は、前記第1の導電膜上及び前記酸化物半導体膜上に設けられ、

前記第2の絶縁膜は、前記第2の導電膜上及び前記酸化物半導体膜上に設けられ、

前記第3の絶縁膜は、前記第1の絶縁膜上、前記第2の絶縁膜上及び前記酸化物半導体膜上に設けられ、

10

20

前記第3の導電膜は、前記酸化物半導体膜と前記第3の絶縁膜を介して、重なる領域を有することを特徴とする半導体装置。

【請求項2】

酸化物半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第4の導電膜と、第1の絶縁膜と、第2の絶縁膜と、第3の絶縁膜と、第4の絶縁膜と、を有し、

前記第4の絶縁膜は、前記第4の導電膜上に設けられ、

前記酸化物半導体膜は、前記第4の絶縁膜上に設けられ、

前記酸化物半導体膜は、第1の領域と、第2の領域と、第3の領域と、第4の領域と、第5の領域と、を有し、

前記第1の領域は、前記第1の導電膜と前記酸化物半導体膜とが互いに接する領域を有し、10

前記第2の領域は、前記第1の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第3の領域は、前記第3の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第4の領域は、前記第2の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第5の領域は、前記第2の導電膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第1の絶縁膜は、前記第1の導電膜上及び前記酸化物半導体膜上に設けられ、20

前記第2の絶縁膜は、前記第2の導電膜上及び前記酸化物半導体膜上に設けられ、

前記第3の絶縁膜は、前記第1の絶縁膜上、前記第2の絶縁膜上及び前記酸化物半導体膜上に設けられ、

前記第3の導電膜は、前記酸化物半導体膜と前記第3の絶縁膜を介して、重なる領域を有することを特徴とする半導体装置。

【請求項3】

請求項1または請求項2において、

前記第1の絶縁膜及び前記第2の絶縁膜は、水素を有し、

前記第2の領域は、前記第3の領域よりも、抵抗値が低い領域を有し、

前記第4の領域は、前記第3の領域よりも、抵抗値が低い領域を有することを特徴とする半導体装置。30

【請求項4】

チャネル形成領域を有する、酸化物半導体膜と、

前記酸化物半導体膜と電気的に接続された、ソース電極と、

前記酸化物半導体膜と電気的に接続された、ドレイン電極と、

前記ソース電極の上面、及び前記チャネル形成領域側の側面と重なる領域を有する、第1の絶縁膜と、1

前記ドレイン電極の上面、及び前記チャネル形成領域側の側面と重なる領域を有する、第2の絶縁膜と、

前記酸化物半導体膜、前記第1の絶縁膜及び前記第2の絶縁膜上に設けられた、第3の絶縁膜と、40

前記第3の絶縁膜上の、ゲート電極と、を有し、

前記第1の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第2の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第3の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記ゲート電極は、前記第3の絶縁膜及び前記第1の絶縁膜を介して、前記ソース電極と重なる領域を有し、

前記ゲート電極は、前記第3の絶縁膜及び前記第2の絶縁膜を介して、前記ドレイン電極と重なる領域を有することを特徴とする半導体装置。

【請求項5】

第 1 のゲート電極と、

前記第 1 のゲート電極上の、第 4 の絶縁膜と、

前記第 4 の絶縁膜上の、チャネル形成領域を有する、酸化物半導体膜と、

前記酸化物半導体膜と電気的に接続された、ソース電極と、

前記酸化物半導体膜と電気的に接続された、ドレイン電極と、

前記ソース電極の上面、及び前記チャネル形成領域側の側面と重なる領域を有する、第

1 の絶縁膜と、

前記ドレイン電極の上面、及び前記チャネル形成領域側の側面と重なる領域を有する、

第 2 の絶縁膜と、

前記酸化物半導体膜、前記第 1 の絶縁膜及び前記第 2 の絶縁膜上に設けられた、第 3 の

絶縁膜と、

前記第 3 の絶縁膜上の、第 2 のゲート電極と、を有し、

前記第 1 の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第 2 の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第 3 の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第 2 のゲート電極は、前記第 3 の絶縁膜及び前記第 1 の絶縁膜を介して、前記ソース電極と重なる領域を有し、

前記第 2 のゲート電極は、前記第 3 の絶縁膜及び前記第 2 の絶縁膜を介して、前記ドレイン電極と重なる領域を有することを特徴とする半導体装置。

**【請求項 6】** 20

請求項 1 乃至請求項 5 のいずれか一において、

前記酸化物半導体膜は、第 1 の酸化物半導体膜と、前記第 1 の酸化物半導体膜上の、第

2 の酸化物半導体膜と、前記第 2 の酸化物半導体膜上の、第 3 の酸化物半導体膜と、を有

することを特徴とする半導体装置。

**【請求項 7】** 30

請求項 1 乃至請求項 5 のいずれか一において、

前記酸化物半導体膜は、第 1 の酸化物半導体膜と、前記第 1 の酸化物半導体膜上の、第

2 の酸化物半導体膜と、前記第 2 の酸化物半導体膜上の、第 3 の酸化物半導体膜と、を有

し、

前記第 3 の酸化物半導体膜は、前記第 1 の絶縁膜と前記第 3 の絶縁膜との間に設けられ

た領域を有し、かつ前記第 2 の絶縁膜と前記第 3 の絶縁膜との間に設けられた領域を有す

ることを特徴とする半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、例えば、トランジスタ及び半導体装置、ならびにそれらの製造方法に関する。

または、本発明は、例えば、表示装置、発光装置、照明装置、蓄電装置、記憶装置、プロセッサ、電子機器に関する。または、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の製造方法に関する。または、半導体装置、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の駆動方法に関する。

**【0002】** 40

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。

**【0003】**

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。表示装置、発光装置、照明装置、電気光学装置、半導体回路及び電子機器は、半導体装置を有する場合がある。

**【背景技術】** 50

**【0004】**

近年は、酸化物半導体を用いたトランジスタが注目されている。酸化物半導体は、スパッタリング法などを用いて成膜できるため、大型の表示装置を構成するトランジスタの半導体に用いることができる。また、酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタの生産設備の一部を改良して利用することが可能であるため、設備投資を抑えられるメリットもある。

**【0005】**

また、酸化物半導体を用いたトランジスタは、非導通状態において極めてリーク電流が小さいことが知られている。例えば、酸化物半導体を用いたトランジスタの低いリーク特性を応用した低消費電力のCPUなどが開示されている（特許文献1参照。）。

10

**【先行技術文献】****【特許文献】****【0006】**

【特許文献1】特開2012-257187号公報

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

寄生容量の小さい半導体装置を提供することを課題の一とする。または、電気特性の良好な半導体装置を提供することを課題の一とする。または、電気特性の安定した半導体装置を提供することを課題の一とする。または、オフ時の電流の小さい半導体装置を提供することを課題の一とする。または、新規な半導体装置を提供することを課題の一とする。または、動作速度の速い半導体装置を提供することを課題の一とする。または、該半導体装置を有するモジュールを提供することを課題の一とする。または、該半導体装置、または該モジュールを有する電子機器を提供することを課題の一とする。

20

**【0008】**

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

**【課題を解決するための手段】**

30

**【0009】**

本発明の一態様は、酸化物半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第1の絶縁膜と、第2の絶縁膜と、第3の絶縁膜と、を有し、酸化物半導体膜は、第1の領域と、第2の領域と、第3の領域と、第4の領域と、第5の領域と、を有し、第1の領域は、第1の導電膜と酸化物半導体膜とが互いに接する領域を有し、第2の領域は、第1の絶縁膜と酸化物半導体膜とが互いに接する領域を有し、第3の領域は、第3の絶縁膜と酸化物半導体膜とが互いに接する領域を有し、第4の領域は、第2の絶縁膜と酸化物半導体膜とが互いに接する領域を有し、第5の領域は、第1の導電膜と酸化物半導体膜上に設けられ、第2の絶縁膜は、第2の導電膜上及び酸化物半導体膜上に設けられ、第3の絶縁膜は、第1の絶縁膜上、第2の絶縁膜上及び酸化物半導体膜上に設けられ、第3の導電膜と酸化物半導体膜とは、第3の絶縁膜を介して、互いに重なる領域を有することを特徴とする半導体装置である。

40

**【0010】**

また、本発明の他の一態様は、酸化物半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第4の導電膜と、第1の絶縁膜と、第2の絶縁膜と、第3の絶縁膜と、第4の絶縁膜と、を有し、第4の絶縁膜は、第4の導電膜上に設けられ、酸化物半導体膜は、第4の絶縁膜上に設けられ、酸化物半導体膜は、第1の領域と、第2の領域と、第3の領域と、第4の領域と、第5の領域と、を有し、第1の領域は、第1の導電膜と酸化物半導体膜とが互いに接する領域を有し、第2の領域は、第1の絶縁膜と酸化物半導体膜とが互いに接する領域を有し、第3の領域は、第3の絶縁膜と酸化物半導体膜とが互いに接する領域を有し、第4の領域は、第2の導電膜と酸化物半導体膜上に設けられ、第5の絶縁膜は、第1の絶縁膜上、第2の絶縁膜上及び酸化物半導体膜上に設けられ、第3の導電膜と酸化物半導体膜とは、第3の絶縁膜を介して、互いに重なる領域を有することを特徴とする半導体装置である。

50

互いに接する領域を有し、第3の領域は、第3の絶縁膜と酸化物半導体膜とが互いに接する領域を有し、第4の領域は、第2の絶縁膜と酸化物半導体膜とが互いに接する領域を有し、第5の領域は、第2の導電膜と酸化物半導体膜とが互いに接する領域を有し、第1の絶縁膜は、第1の導電膜上及び酸化物半導体膜上に設けられ、第2の絶縁膜は、第2の導電膜上及び酸化物半導体膜上に設けられ、第3の絶縁膜は、第1の絶縁膜上、第2の絶縁膜上及び酸化物半導体膜上に設けられ、第3の導電膜と酸化物半導体膜とは、第3の絶縁膜を介して、互いに重なる領域を有することを特徴とする半導体装置である。

#### 【0011】

また、上記構成において、第1の絶縁膜及び第2の絶縁膜は、水素を有し、第2の領域は、第3の領域よりも、抵抗値が低い領域を有し、第4の領域は、第3の領域よりも、抵抗値が低い領域を有してもよい。10

#### 【0012】

また、上記構成において、酸化物半導体膜は、第1の酸化物半導体膜と、第2の酸化物半導体膜と、第3の酸化物半導体膜と、を有し、第1の酸化物半導体膜と、第2の酸化物半導体膜と、第3の酸化物半導体膜とが、互いに重なる領域を有してもよい。

#### 【0013】

また、本発明の他の一態様は、上記構成の半導体装置を含むことを特徴とする電子機器である。

#### 【0014】

また、本発明の他の一態様は、酸化物半導体膜を設ける第1の工程と、酸化物半導体膜上に第1の導電膜及び第2の導電膜を設ける第2の工程と、酸化物半導体膜上、第1の導電膜上、及び第2の導電膜上に第1の絶縁膜を設ける第3の工程と、第1の絶縁膜を酸化物半導体膜の一部を露出させるように加工し、第2の絶縁膜及び第3の絶縁膜を設ける第4の工程と、酸化物半導体膜上、第2の絶縁膜上及び第3の絶縁膜上に第4の絶縁膜を設ける第5の工程と、第4の絶縁膜上に酸化物半導体膜と互いに重なる第3の導電膜を設ける第6の工程と、を有することを特徴とする半導体装置の作製方法である。20

#### 【0015】

また、本発明の他の一態様は、酸化物半導体膜を設ける第1の工程と、酸化物半導体膜上に第1の導電膜及び第2の導電膜を設ける第2の工程と、第1の導電膜及び第2の導電膜を酸化または窒化させて、第1の絶縁膜及び第2の絶縁膜を設ける第3の工程と、酸化物半導体膜上、第1の絶縁膜上及び第2の絶縁膜上に第3の絶縁膜を設ける第4の工程と、第3の絶縁膜上に酸化物半導体膜と互いに重なる第3の導電膜を設ける第5の工程と、を有することを特徴とする半導体装置の作製方法である。30

#### 【0016】

なお、本発明の一態様に係る半導体装置において、酸化物半導体膜を他の半導体膜に置き換える構わぬ。

#### 【発明の効果】

#### 【0017】

寄生容量の小さい半導体装置を提供することができる。または、電気特性の良好な半導体装置を提供することができる。または、電気特性の安定した半導体装置を提供することができる。または、オフ時の電流の小さい半導体装置を提供することができる。または、新規な半導体装置を提供することができる。または、動作速度の速い半導体装置を提供することができる。または、該半導体装置を有するモジュールを提供することができる。または、該半導体装置、または該モジュールを有する電子機器を提供することができる。40

#### 【0018】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

#### 【図面の簡単な説明】

## 【0019】

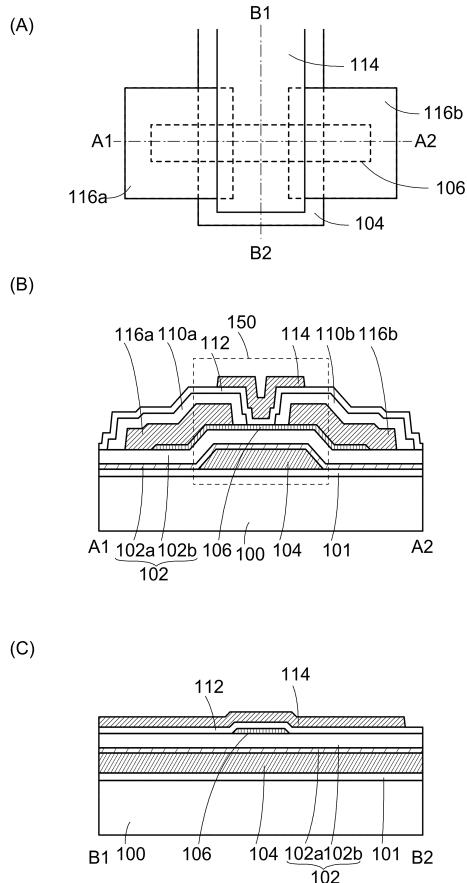

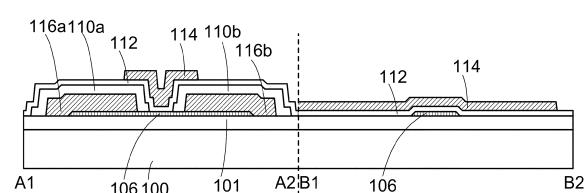

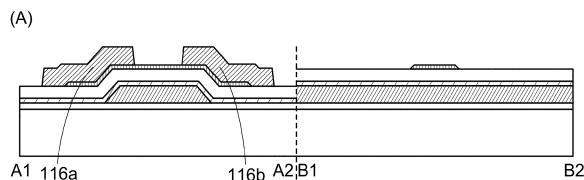

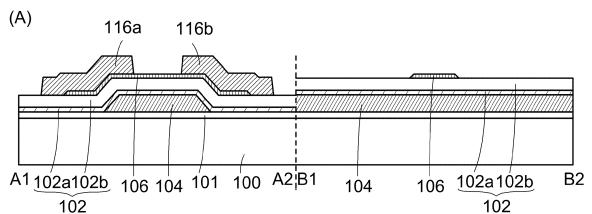

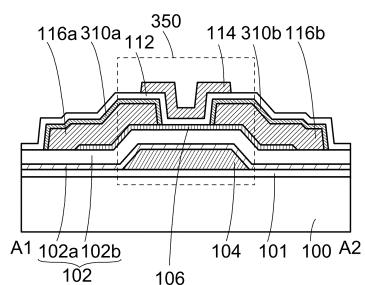

【図1】トランジスタの上面図及び断面図。

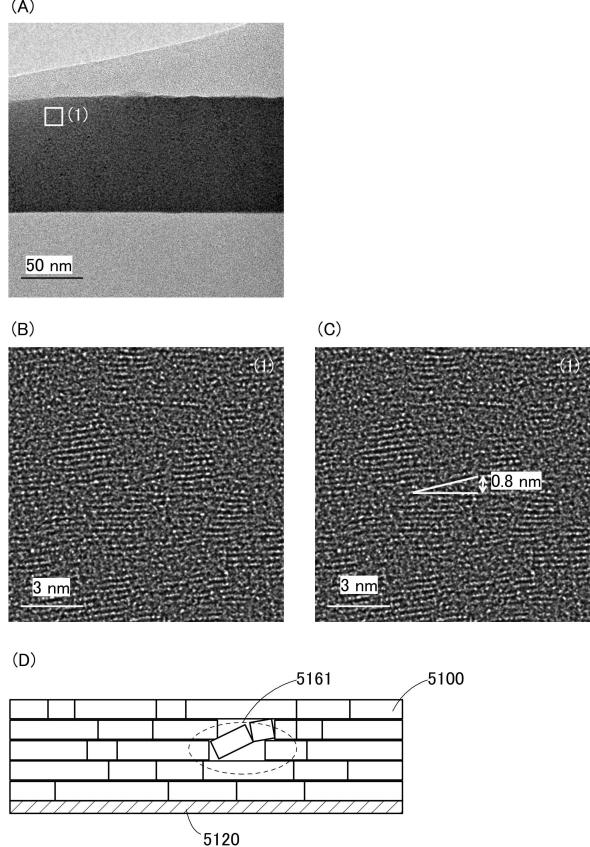

【図2】C A A C - O S の断面におけるC s 補正高分解能T E M像、およびC A A C - O S の断面模式図。

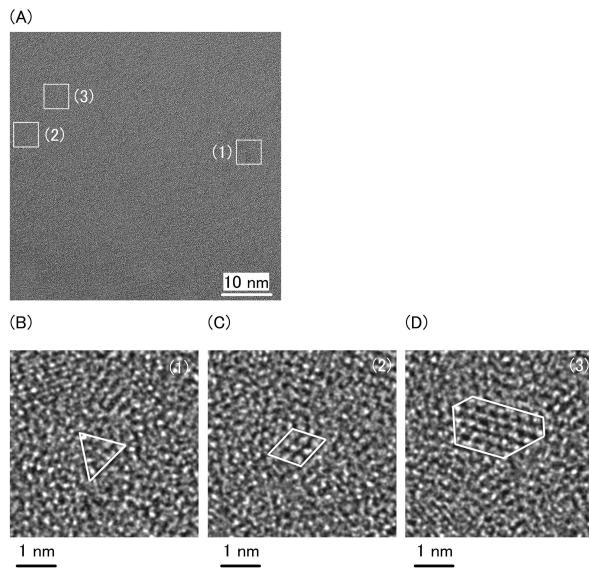

【図3】C A A C - O S の平面におけるC s 補正高分解能T E M像。

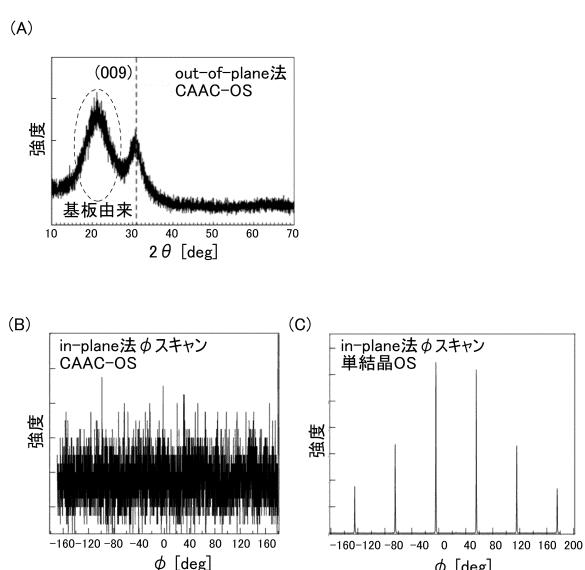

【図4】C A A C - O S および単結晶酸化物半導体のX R Dによる構造解析を説明する図。

【図5】C A A C - O S の電子回折パターンを示す図。

【図6】I n - G a - Z n 酸化物の電子照射による結晶部の変化を示す図。

【図7】トランジスタの一部を示す断面図及びバンド構造を示す図。

10

【図8】トランジスタの断面図。

【図9】トランジスタの作製方法を示す断面図。

【図10】トランジスタの作製方法を示す断面図。

【図11】トランジスタの上面図及び断面図。

【図12】トランジスタの断面図。

【図13】トランジスタの作製方法を示す断面図。

【図14】トランジスタの作製方法を示す断面図。

【図15】トランジスタの上面図及び断面図。

【図16】トランジスタの断面図。

【図17】トランジスタの作製方法を示す断面図。

20

【図18】表示装置の一態様を示す上面図。

【図19】表示装置の一態様を示す断面図。

【図20】表示装置の一態様を示す断面図。

【図21】表示装置を説明するブロック図及び回路図。

【図22】表示モジュールを説明する図。

【図23】電子機器を説明する図。

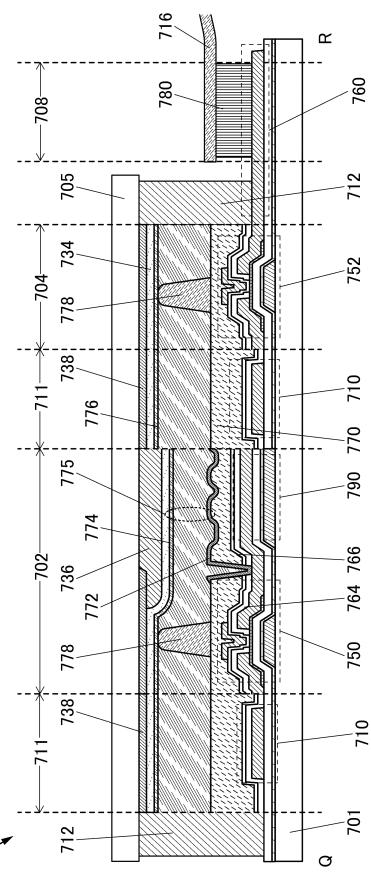

【発明を実施するための形態】

## 【0020】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

30

## 【0021】

なお、図において、大きさ、膜（層）の厚さ、または領域は、明瞭化のために誇張されている場合がある。

## 【0022】

なお、本明細書において、例えば、物体の形状を「径」、「粒径」、「大きさ」、「サイズ」、「幅」などで規定する場合、物体が収まる最小の立方体における一辺の長さ、または物体の一断面における円相当径と読み替えてよい。物体の一断面における円相当径とは、物体の一断面と等しい面積となる正円の直径をいう。

40

## 【0023】

なお、電圧は、ある電位と、基準の電位（例えば接地電位（G N D）またはソース電位）との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。

## 【0024】

なお、第1、第2として付される序数詞は便宜的に用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」又は「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、

50

本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

【0025】

なお、「半導体（または半導体膜）」と表記した場合でも、例えば、導電性が十分低い場合は「絶縁体（または絶縁膜）」としての特性を有する場合がある。また、「半導体」と「絶縁体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「絶縁体」と言い換えることができる場合がある。同様に、本明細書に記載の「絶縁体」は、「半導体」と言い換えることができる場合がある。

【0026】

また、「半導体（または半導体膜）」と表記した場合でも、例えば、導電性が十分高い場合は「導電体（または導電膜）」としての特性を有する場合がある。また、「半導体」と「導電体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「導電体」と言い換えることができる場合がある。同様に、本明細書に記載の「導電体」は、「半導体」と言い換えることができる場合がある。10

【0027】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物である。不純物が含まれることにより、例えば、半導体のDOS (Density of State) が形成されることや、キャリア移動度が低下することや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第14族元素、第15族元素、主成分以外の遷移金属などがあり、特に、例えば、水素（水にも含まれる）、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、例えば水素などの不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。20

【0028】

なお、本明細書において、Aが濃度Bの領域を有する、と記載する場合、例えば、Aのある領域における深さ方向全体が濃度Bである場合、Aのある領域における深さ方向の平均値が濃度Bである場合、Aのある領域における深さ方向の中央値が濃度Bである場合、Aのある領域における深さ方向の最大値が濃度Bである場合、Aのある領域における深さ方向の最小値が濃度Bである場合、Aのある領域における深さ方向の収束値が濃度Bである場合、測定上Aそのものの確からしい値の得られる領域が濃度Bである場合などを含む。30

【0029】

なお、本明細書において、Aが大きさB、長さB、厚さB、幅Bまたは距離Bの領域を有する、と記載する場合、例えば、Aのある領域における全体が大きさB、長さB、厚さB、幅Bまたは距離Bである場合、Aのある領域における平均値が大きさB、長さB、厚さB、幅Bまたは距離Bである場合、Aのある領域における中央値が大きさB、長さB、厚さB、幅Bまたは距離Bである場合、Aのある領域における最大値が大きさB、長さB、厚さB、幅Bまたは距離Bである場合、Aのある領域における最小値が大きさB、長さB、厚さB、幅Bまたは距離Bである場合、Aのある領域における収束値が大きさB、長さB、厚さB、幅Bまたは距離Bである場合、測定上Aそのものの確からしい値の得られる領域が大きさB、長さB、厚さB、幅Bまたは距離Bである場合などを含む。40

【0030】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレイン領域またはドレイン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、50

最小値または平均値とする。

**【0031】**

チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

**【0032】**

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の上面に形成されるチャネル領域の割合に対して、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。

**【0033】**

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためにには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

**【0034】**

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが互いに重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（S C W : S u r r o u n d e d C h a n n e l W i d t h ）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面T E M像などを取得して、その画像を解析することなどによって、値を決定することができる。

**【0035】**

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

**【0036】**

なお、本明細書において、AがBより迫り出した形状を有すると記載する場合、上面図または断面図において、Aの少なくとも一端が、Bの少なくとも一端よりも外側にある形状を有することを示す場合がある。したがって、AがBより迫り出した形状を有すると記載されている場合、例えば上面図において、Aの一端が、Bの一端よりも外側にある形状を有すると読み替えることができる。

**【0037】**

なお、本明細書において、「平行」とは、二つの直線が - 10°以上 10°以下の角度で配置されている状態をいう。したがって、- 5°以上 5°以下の場合も含まれる。また、「略平行」とは、二つの直線が - 30°以上 30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80°以上 100°以下の角度で配置されている状態をいう。したがって、85°以上 95°以下の場合も含まれる。また、「略垂直」と

10

20

30

40

50

は、二つの直線が 60° 以上 120° 以下の角度で配置されている状態をいう。

**【0038】**

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

**【0039】**

(実施の形態 1)

本実施の形態では、本発明の一態様である半導体装置、及びその作製方法について図面を参照して説明する。半導体装置の一例としてトランジスタを用いて説明する。

**【0040】**

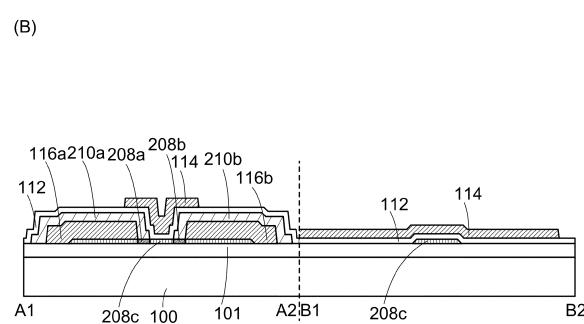

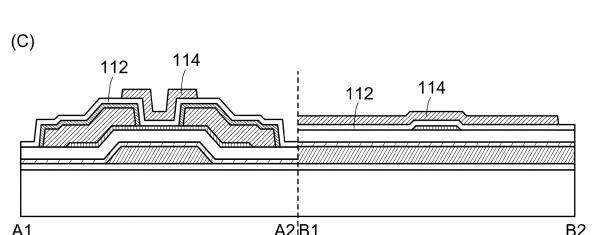

<トランジスタ構造 1>

10

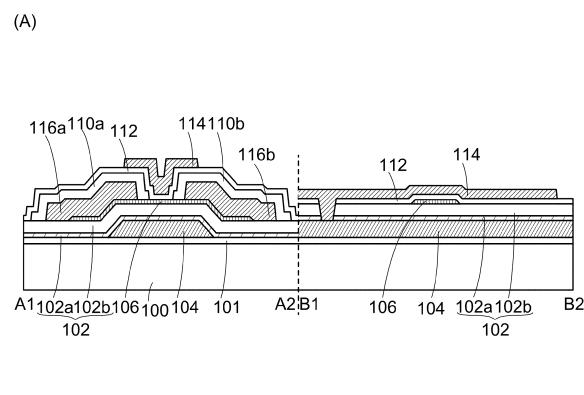

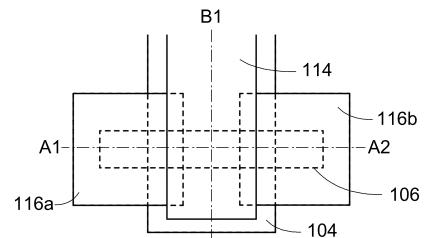

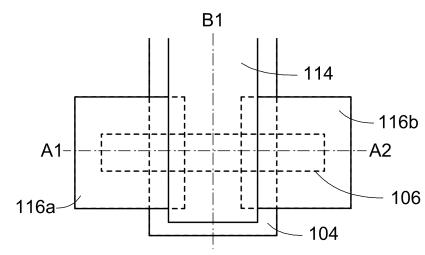

図1(A)、図1(B)及び図1(C)は、本発明の一態様に係るトランジスタ150の上面図及び断面図である。図1(A)は上面図である。図1(B)及び図1(C)は、図1(A)に示す一点鎖線A1-A2、及び一点鎖線B1-B2に対応する断面図である。なお、図1(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

**【0041】**

図1(B)において、トランジスタ150は、基板100上の絶縁膜101と、絶縁膜101上の導電膜104と、導電膜104上の絶縁膜102と、絶縁膜102上の半導体膜106と、半導体膜106の上面及び側面と接する領域を有する導電膜116a及び導電膜116bと、導電膜116aの上面及び側面と接する、半導体膜106上の絶縁膜110aと、導電膜116bの上面及び側面と接する、半導体膜106上の絶縁膜110bと、絶縁膜110a上、絶縁膜110b上、及び半導体膜106上の絶縁膜112と、絶縁膜112上の導電膜114と、を有する。なお、導電膜114と半導体膜106とは互いに重なる領域を有している。

20

**【0042】**

なお、トランジスタ150は、絶縁膜101を有さなくても構わない場合がある。

**【0043】**

トランジスタ150において、絶縁膜101は下地絶縁膜としての機能を有する。また、導電膜104はゲート電極としての機能を有する。また、絶縁膜102はゲート絶縁膜としての機能を有する。また、導電膜116a及び導電膜116bは、ソース電極及びドレイン電極としての機能を有する。また、絶縁膜112はゲート絶縁膜としての機能を有する。また、導電膜114はゲート電極としての機能を有する。したがって、導電膜104または導電膜114に印加する電位によって、トランジスタ150の動作を制御することができる。即ち、導電膜104または導電膜114に印加する電位によって、導電膜116aと導電膜116bとの間の導通・非導通を制御することができる。

30

**【0044】**

また、トランジスタ150の半導体膜106は、導電膜116aと半導体膜106とが互いに接する領域と、絶縁膜110aと半導体膜106とが互いに接する領域と、絶縁膜112と半導体膜106とが互いに接する領域と、絶縁膜110bと半導体膜106とが互いに接する領域と、導電膜116bと半導体膜106とが互いに接する領域と、を有する。トランジスタ150は、導電膜114と導電膜116aとの間、導電膜114と導電膜116bとの間に、それぞれ絶縁膜110a、絶縁膜110b及び絶縁膜112を有することで、絶縁膜の膜厚の合計が大きくなり、結果としてトランジスタ150の動作に係る寄生容量を小さくすることができる。

40

**【0045】**

図1(B)に示すように、半導体膜106の側面は、導電膜116a及び導電膜116bと接する。また、ゲート電極としての機能を有する導電膜114の電界によって、半導体膜106を電気的に取り囲むことができる。ゲート電極の電界によって、半導体膜を電気的に取り囲むトランジスタの構造を、surrounded channel(s-channel)構造とよぶ。そのため、半導体膜106の全体(バルク)にチャネルが形成される場合がある。s-channel構造では、トランジスタのソース・ドレイン間に

50

大電流を流すことができ、導通時の電流（オン電流）を大きくすることができる。また、半導体膜106が、導電膜114の電界によって取り囲まれていることから、非導通時の電流（オフ電流）を小さくすることができる。

#### 【0046】

なお、トランジスタ150を、水素などの不純物及び酸素をブロックする機能を有する絶縁膜で囲うことによって、トランジスタ150の電気特性を安定にすることができる。例えば、絶縁膜101として、水素などの不純物及び酸素をブロックする機能を有する絶縁膜を用いればよい。

#### 【0047】

水素などの不純物及び酸素をブロックする機能を有する絶縁膜としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁膜を、単層で、または積層で用いればよい。10

#### 【0048】

例えば、絶縁膜101としては、酸化アルミニウム、酸化マグネシウム、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。なお、絶縁膜101は、酸化アルミニウムまたは窒化シリコンを有することが好ましい。例えば、絶縁膜101が酸化アルミニウムまたは窒化シリコンを有することで、半導体膜106に水素などの不純物が混入することを抑制することができる。また、たとえば、絶縁膜101が酸化アルミニウムまたは窒化シリコンを有することで、酸素の外方拡散を低減することができる。20

#### 【0049】

絶縁膜101は、基板100からの不純物の拡散を防止する役割を有してもよい。

#### 【0050】

導電膜104としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタル及びタンクステンを一種以上含む導電膜を、単層で、または積層で用いればよい。例えば、合金膜や化合物膜であってもよく、アルミニウムを含む導電膜、銅及びチタンを含む導電膜、銅及びマンガンを含む導電膜、インジウム、スズ及び酸素を含む導電膜、またはチタン及び窒素を含む導電膜などを用いてもよい。30

#### 【0051】

導電膜104は、トランジスタ150の第2のゲート電極（バックゲート電極ともいう。）としての機能を有する。例えば、導電膜104に、ソース電極よりも低い電圧または高い電圧を印加し、トランジスタ150のしきい値電圧をプラス方向またはマイナス方向へ変動させてもよい。例えば、トランジスタ150のしきい値電圧をプラス方向に変動させることで、ゲート電圧が0Vであってもトランジスタ150が非導通状態（オフ状態）となる、ノーマリーオフが実現できる場合がある。なお、導電膜104に印加する電圧は、可変であってもよいし、固定であってもよい。40

#### 【0052】

絶縁膜102としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁膜を、単層で、または積層で用いればよい。例えば、絶縁膜102としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。本実施の形態では、絶縁膜102として基板100側から絶縁膜102a、絶縁膜102bを設ける。絶縁膜102aは、絶縁膜101のような基板100からの不純物の拡散を防止する役割を有50

してもよい。また、半導体膜 106 が酸化物半導体膜である場合、絶縁膜 102b は、半導体膜 106 に酸素を供給する役割を担うことができる。

#### 【0053】

導電膜 116a 及び導電膜 116b としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタル及びタンクステンを一種以上含む導電膜を、単層で、または積層で用いればよい。例えば、合金膜や化合物膜であってもよく、アルミニウムを含む導電膜、銅及びチタンを含む導電膜、銅及びマンガンを含む導電膜、インジウム、スズ及び酸素を含む導電膜、またはチタン及び窒素を含む導電膜などを用いてもよい。

10

#### 【0054】

絶縁膜 110a 及び絶縁膜 110b としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁膜を、単層で、または積層で用いればよい。例えば、絶縁膜 110a 及び絶縁膜 110b としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

20

#### 【0055】

絶縁膜 112 としては、絶縁膜 110a 及び絶縁膜 110b の説明を援用することができる。

#### 【0056】

導電膜 114 としては、導電膜 104 の説明を援用することができる。

#### 【0057】

半導体膜 106 としては、酸化物半導体膜を用いることが好ましい。ただし、シリコン(歪シリコン含む)、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、ガリウムヒ素、アルミニウムガリウムヒ素、インジウムリン、窒化ガリウムまたは有機半導体膜などを用いても構わない場合がある。

30

#### 【0058】

<酸化物半導体の構造>

以下では、酸化物半導体の構造について説明する。

#### 【0059】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、C A A C - O S ( C A x i s A l i g n e d C r y s t a l l i n e O x i d e S e m i c o n d u c t o r )、多結晶酸化物半導体、n c - O S ( n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r )、擬似非晶質酸化物半導体( a - l i k e O S : a m o r p h o u s l i k e O x i d e S e m i c o n d u c t o r )、非晶質酸化物半導体などがある。

40

#### 【0060】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体とに分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、C A A C - O S、多結晶酸化物半導体、n c - O S などがある。

#### 【0061】

非晶質構造の定義としては、一般に、準安定状態で固定化していないこと、等方的であって不均質構造を持たないことなどが知られている。また、結合角度が柔軟であり、短距離秩序性は有するが、長距離秩序性を有さない構造と言い換えることもできる。

#### 【0062】

逆の見方をすると、本質的に安定な酸化物半導体の場合、完全な非晶質( c o m p l e t e l y a m o r p h o u s )酸化物半導体と呼ぶことはできない。また、等方的でない

50

(例えは、微小な領域において周期構造を有する)酸化物半導体を、完全な非晶質酸化物半導体と呼ぶことはできない。ただし、a - like OSは、微小な領域において周期構造を有するものの、鬆(ボイドともいう。)を有し、不安定な構造である。そのため、物性的には非晶質酸化物半導体に近いといえる。

**【0063】**

< C AAC - OS >

まずは、C AAC - OSについて説明する。

**【0064】**

C AAC - OSは、c軸配向した複数の結晶部(ペレットともいう。)を有する酸化物半導体の一つである。

10

**【0065】**

透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって、C AAC - OSの明視野像と回折パターンとの複合解析像(高分解能TEM像ともいう。)を観察すると、複数のペレットを確認することができる。一方、高分解能TEM像ではペレット同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を明確に確認することができない。そのため、C AAC - OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

**【0066】**

以下では、TEMによって観察したC AAC - OSについて説明する。図2(A)に、試料面と略平行な方向から観察したC AAC - OSの断面の高分解能TEM像を示す。高分解能TEM像の観察には、球面収差補正(Spherical Aberration Corrector)機能を用いた。球面収差補正機能を用いた高分解能TEM像を、特にCs補正高分解能TEM像と呼ぶ。Cs補正高分解能TEM像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM - ARM200Fなどによって行うことができる。

20

**【0067】**

図2(A)の領域(1)を拡大したCs補正高分解能TEM像を図2(B)に示す。図2(B)より、ペレットにおいて、金属原子が層状に配列していることを確認できる。金属原子の各層の配列は、C AAC - OSの膜を形成する面(被形成面ともいう。)または上面の凹凸を反映しており、C AAC - OSの被形成面または上面と平行となる。

30

**【0068】**

図2(B)に示すように、C AAC - OSは特徴的な原子配列を有する。図2(C)は、特徴的な原子配列を、補助線で示したものである。図2(B)および図2(C)より、ペレット一つの大きさは1nm以上のものや、3nm以上のものがあり、ペレットとペレットとの傾きにより生じる隙間の大きさは0.8nm程度であることがわかる。したがって、ペレットを、ナノ結晶(nc:nanocrystal)と呼ぶこともできる。また、C AAC - OSを、C ANC(C-Axis Aligned nanocrystals)を有する酸化物半導体と呼ぶこともできる。

**【0069】**

ここで、Cs補正高分解能TEM像をもとに、基板5120上のC AAC - OSのペレット5100の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる(図2(D)参照。)。図2(C)で観察されたペレットとペレットとの間で傾きが生じている箇所は、図2(D)に示す領域5161に相当する。

40

**【0070】**

また、図3(A)に、試料面と略垂直な方向から観察したC AAC - OSの平面のCs補正高分解能TEM像を示す。図3(A)の領域(1)、領域(2)および領域(3)を拡大したCs補正高分解能TEM像を、それぞれ図3(B)、図3(C)および図3(D)に示す。図3(B)、図3(C)および図3(D)より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。

50

**【0071】**

次に、X線回折(XRD: X-Ray Diffraction)によって解析したCAC-OSについて説明する。例えば、InGaZnO<sub>4</sub>の結晶を有するCAC-OSに対し、out-of-plane法による構造解析を行うと、図4(A)に示すように回折角(2θ)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、CAC-OSの結晶がc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

**【0072】**

なお、CAC-OSのout-of-plane法による構造解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、CAC-OS中の一部に、c軸配向性を有さない結晶が含まれることを示している。より好ましいCAC-OSは、out-of-plane法による構造解析では、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さない。

10

**【0073】**

一方、CAC-OSに対し、c軸に略垂直な方向からX線を入射させるin-plane法による構造解析を行うと、2θが56°近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub>の結晶の(110)面に帰属される。CAC-OSの場合は、2θを56°近傍に固定し、試料面の法線ベクトルを軸(a軸)として試料を回転させながら分析(スキャン)を行っても、図4(B)に示すように明瞭なピークは現れない。これに対し、InGaZnO<sub>4</sub>の単結晶酸化物半導体であれば、2θを56°近傍に固定してスキャンした場合、図4(C)に示すように(110)面と等価な結晶面に帰属されるピークが6本観察される。したがって、XRDを用いた構造解析から、CAC-OSは、a軸およびb軸の配向が不規則であることが確認できる。

20

**【0074】**

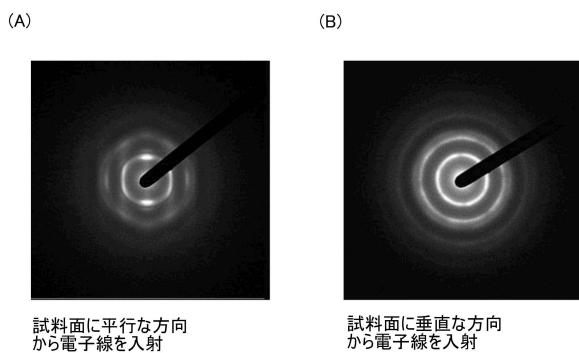

次に、電子回折によって解析したCAC-OSについて説明する。例えば、InGaZnO<sub>4</sub>の結晶を有するCAC-OSに対し、試料面に平行にプローブ径が300nmの電子線を入射させると、図5(A)に示すような回折パターン(制限視野透過電子回折パターンともいう。)が現れる場合がある。この回折パターンには、InGaZnO<sub>4</sub>の結晶の(009)面に起因するスポットが含まれる。したがって、電子回折によても、CAC-OSに含まれるペレットがc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が300nmの電子線を入射させたときの回折パターンを図5(B)に示す。図5(B)により、リング状の回折パターンが確認される。したがって、電子回折によても、CAC-OSに含まれるペレットのa軸およびb軸は配向性を有さないことがわかる。なお、図5(B)における第1リングは、InGaZnO<sub>4</sub>の結晶の(010)面および(100)面などに起因すると考えられる。また、図5(B)における第2リングは(110)面などに起因すると考えられる。

30

**【0075】**

上述したように、CAC-OSは結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、逆の見方をするとCAC-OSは不純物や欠陥(酸素欠損など)の少ない酸化物半導体ともいえる。

40

**【0076】**

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

**【0077】**

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合があ

50

る。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。また、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

#### 【0078】

不純物および酸素欠損の少ない CAAc - OS は、キャリア密度の低い酸化物半導体である。具体的には、 $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上のキャリア密度の酸化物半導体とすることができます。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。CAAc - OS は、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物半導体であるといえる。

10

#### 【0079】

< n c - OS >

次に、n c - OS について説明する。

#### 【0080】

n c - OS は、高分解能 TEM 像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。n c - OS に含まれる結晶部は、1 nm 以上 10 nm 以下、または 1 nm 以上 3 nm 以下の大きさであることが多い。なお、結晶部の大きさが 10 nm より大きく 100 nm 以下である酸化物半導体を微結晶酸化物半導体と呼ぶことがある。n c - OS は、例えば、高分解能 TEM 像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、CAAc - OS におけるペレットと起源を同じくする可能性がある。そのため、以下では n c - OS の結晶部をペレットと呼ぶ場合がある。

20

#### 【0081】

n c - OS は、微小な領域（例えば、1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、n c - OS は、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - OS は、分析方法によっては、a - like OS や非晶質酸化物半導体と区別が付かない場合がある。例えば、n c - OS に対し、ペレットよりも大きい径の X 線を用いた場合、out - of - plane 法による解析では、結晶面を示すピークは検出されない。また、n c - OS に対し、ペレットよりも大きいプローブ径（例えば 50 nm 以上）の電子線を用いる電子回折を行うと、ハローパターンのような回折パターンが観測される。一方、n c - OS に対し、ペレットの大きさと近いかペレットより小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - OS に対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。さらに、リング状の領域内に複数のスポットが観測される場合がある。

30

#### 【0082】

このように、ペレット（ナノ結晶）間では結晶方位が規則性を有さないことから、n c - OS を、RANC (Random Aligned nanocrystals) を有する酸化物半導体、または NANC (Non-Aligned nanocrystals) を有する酸化物半導体と呼ぶこともできる。

40

#### 【0083】

n c - OS は、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、n c - OS は、a - like OS や非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - OS は、異なるペレット間で結晶方位に規則性が見られない。そのため、n c - OS は、CAAc - OS と比べて欠陥準位密度が高くなる。

#### 【0084】

< a - like OS >

a - like OS は、n c - OS と非晶質酸化物半導体との間の構造を有する酸化物半導体である。

50

**【0085】**

a - l i k e OSは、高分解能TEM像において鬆が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。

**【0086】**

鬆を有するため、a - l i k e OSは、不安定な構造である。以下では、a - l i k e OSが、CAAC - OSおよびnc - OSと比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。

**【0087】**

電子照射を行う試料として、a - l i k e OS（試料Aと表記する。）、nc - OS（試料Bと表記する。）およびCAAC - OS（試料Cと表記する。）を準備する。いずれの試料もIn - Ga - Zn酸化物である。10

**【0088】**

まず、各試料の高分解能断面TEM像を取得する。高分解能断面TEM像により、各試料は、いずれも結晶部を有することがわかる。

**【0089】**

なお、どの部分を一つの結晶部と見なすかの判定は、以下のように行えばよい。例えば、InGaZnO<sub>4</sub>の結晶の単位格子は、In - O層を3層有し、またGa - Zn - O層を6層有する、計9層がc軸方向に層状に重なった構造を有することが知られている。これらの近接する層同士の間隔は、(009)面の格子面間隔(d値ともいう。)と同程度であり、結晶構造解析からその値は0.29nmと求められている。したがって、格子縞の間隔が0.28nm以上0.30nm以下の箇所を、InGaZnO<sub>4</sub>の結晶部と見なすことができる。なお、格子縞は、InGaZnO<sub>4</sub>の結晶のa - b面に対応する。20

**【0090】**

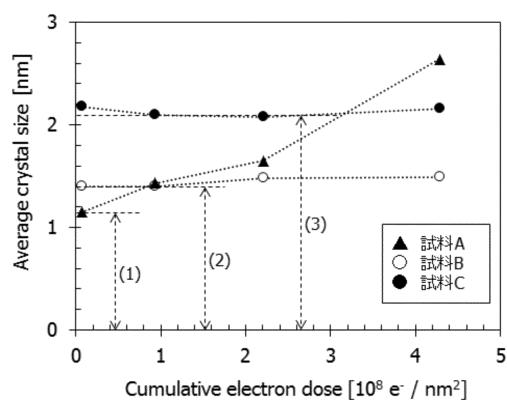

図6は、各試料の結晶部（22箇所から45箇所）の平均の大きさを調査した例である。ただし、上述した格子縞の長さを結晶部の大きさとしている。図6より、a - l i k e OSは、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図6中に(1)で示すように、TEMによる観察初期においては1.2nm程度の大きさだった結晶部（初期核ともいう。）が、累積照射量が $4.2 \times 10^8 e^- / nm^2$ においては2.6nm程度の大きさまで成長していることがわかる。一方、nc - OSおよびCAAC - OSは、電子照射開始時から電子の累積照射量が $4.2 \times 10^8 e^- / nm^2$ までの範囲で、結晶部の大きさに変化が見られないことがわかる。具体的には、図6中の(2)および(3)で示すように、電子の累積照射量によらず、nc - OSおよびCAAC - OSの結晶部の大きさは、それぞれ1.4nm程度および2.1nm程度であることがわかる。30

**【0091】**

このように、a - l i k e OSは、電子照射によって結晶部の成長が見られる場合がある。一方、nc - OSおよびCAAC - OSは、電子照射による結晶部の成長がほとんど見られないことがわかる。即ち、a - l i k e OSは、nc - OSおよびCAAC - OSと比べて、不安定な構造であることがわかる。40

**【0092】**

また、鬆を有するため、a - l i k e OSは、nc - OSおよびCAAC - OSと比べて密度の低い構造である。具体的には、a - l i k e OSの密度は、同じ組成の単結晶の密度の78.6%以上92.3%未満となる。また、nc - OSの密度およびCAAC - OSの密度は、同じ組成の単結晶の密度の92.3%以上100%未満となる。単結晶の密度の78%未満となる酸化物半導体は、成膜すること自体が困難である。

**【0093】**

例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比]を満たす酸化物半導体において、菱面体構造を有する単結晶InGaZnO<sub>4</sub>の密度は6.357g/cm<sup>3</sup>となる。よって、例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比]を満たす酸化物半導体において50

、 a - l i k e O S の密度は 5 . 0 g / cm<sup>3</sup> 以上 5 . 9 g / cm<sup>3</sup> 未満となる。また、例えれば、In : Ga : Zn = 1 : 1 : 1 [原子数比] を満たす酸化物半導体において、n c - OS の密度および C AAC - OS の密度は 5 . 9 g / cm<sup>3</sup> 以上 6 . 3 g / cm<sup>3</sup> 未満となる。

#### 【 0 0 9 4 】

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成における単結晶に相当する密度を見積もることができる。所望の組成の単結晶に相当する密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて見積もればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて見積もることが好ましい。

10

#### 【 0 0 9 5 】

以上のように、酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。なお、酸化物半導体は、例えれば、非晶質酸化物半導体、a - l i k e O S 、n c - OS 、AAC - OS のうち、二種以上を有する積層膜であってもよい。

#### 【 0 0 9 6 】

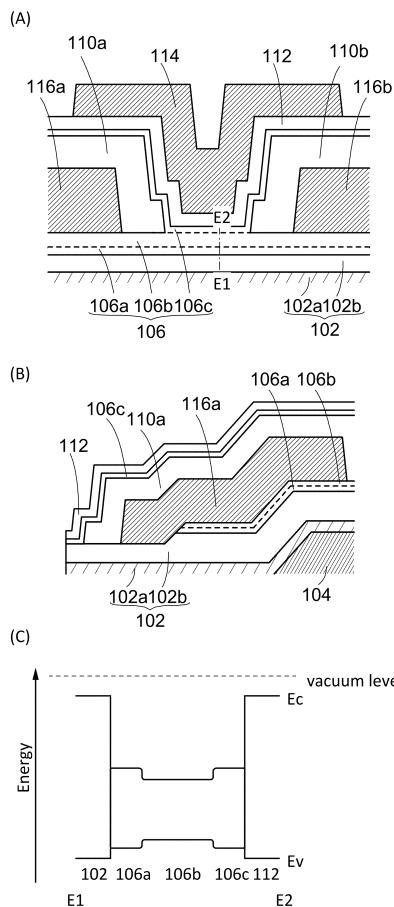

図 7 ( A ) は、トランジスタ 150 の一部を拡大した断面図である。図 7 ( A ) では、半導体膜 106 が、半導体膜 106 a 、半導体膜 106 b 及び半導体膜 106 c が、この順に積層した積層膜である場合を示す。なお、図 7 ( B ) に示すように積層膜を島状に加工する際、積層膜の下の絶縁膜 102 が若干過度にエッティングされてもよい。

#### 【 0 0 9 7 】

半導体膜 106 a 、半導体膜 106 b 、半導体膜 106 c などに適用可能な半導体について説明する。

20

#### 【 0 0 9 8 】

半導体膜 106 b は、例えれば、インジウムを含む酸化物半導体である。半導体膜 106 b は、例えれば、インジウムを含むと、キャリア移動度（電子移動度）が高くなる。また、半導体膜 106 b は、元素 M を含むと好ましい。元素 M は、好ましくは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素 M に適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、イットリウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステンなどがある。ただし、元素 M として、前述の元素を複数組み合わせても構わない場合がある。元素 M は、例えれば、酸素との結合エネルギーが高い元素である。例えれば、酸素との結合エネルギーがインジウムよりも高い元素である。または、元素 M は、例えれば、酸化物半導体のエネルギーギャップを大きくする機能を有する元素である。また、半導体膜 106 b は、亜鉛を含むと好ましい。また、酸化物半導体は、亜鉛を含むと結晶化しやすくなる場合がある。

30

#### 【 0 0 9 9 】

ただし、半導体膜 106 b は、インジウムを含む酸化物半導体に限定されない。半導体膜 106 b は、例えれば、亜鉛スズ酸化物、ガリウムスズ酸化物、酸化ガリウムなどの、インジウムを含まず、亜鉛を含む酸化物半導体、ガリウムを含む酸化物半導体、スズを含む酸化物半導体などであっても構わない。

40

#### 【 0 1 0 0 】

半導体膜 106 b は、例えれば、エネルギーギャップが大きい酸化物を用いる。半導体膜 106 b のエネルギーギャップは、例えれば、2 . 5 eV 以上 4 . 2 eV 以下、好ましくは 2 . 8 eV 以上 3 . 8 eV 以下、さらに好ましくは 3 eV 以上 3 . 5 eV 以下とする。

#### 【 0 1 0 1 】

例えれば、半導体膜 106 a 及び半導体膜 106 c は、半導体膜 106 b を構成する酸素以外の元素一種以上、または二種以上から構成される酸化物半導体である。半導体膜 106 b を構成する酸素以外の元素一種以上、または二種以上から半導体膜 106 a 及び半導体膜 106 c が構成されるため、半導体膜 106 a と半導体膜 106 b との界面、及び半導体膜 106 b と半導体膜 106 c との界面において、界面準位が形成されにくい。

50

## 【0102】

半導体膜106a、半導体膜106b及び半導体膜106cが、インジウムを含む場合について説明する。なお、半導体膜106aがIn-M-Zn酸化物のとき、In及びMの和を100 atomic %としたとき、好ましくはInが50 atomic %以下、Mが50 atomic %以上、さらに好ましくはInが25 atomic %以下、Mが75 atomic %以上とする。また、半導体膜106bがIn-M-Zn酸化物のとき、In及びMの和を100 atomic %としたとき、好ましくはInが25 atomic %以上、Mが75 atomic %以下、さらに好ましくはInが34 atomic %以上、Mが66 atomic %以下とする。また、半導体膜106cがIn-M-Zn酸化物のとき、In及びMの和を100 atomic %としたとき、好ましくはInが50 atomic %以下、Mが50 atomic %以上、さらに好ましくはInが25 atomic %以下、Mが75 atomic %以上とする。なお、半導体膜106cは、半導体膜106aと同種の酸化物を用いても構わない。

## 【0103】

半導体膜106bは、半導体膜106a及び半導体膜106cよりも電子親和力の大きい酸化物を用いる。例えば、半導体膜106bとして、半導体膜106a及び半導体膜106cよりも電子親和力の0.07 eV以上1.3 eV以下、好ましくは0.1 eV以上0.7 eV以下、さらに好ましくは0.15 eV以上0.4 eV以下大きい酸化物を用いる。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。

## 【0104】

なお、インジウムガリウム酸化物は、小さい電子親和力と、高い酸素ブロック性を有する。そのため、半導体膜106cがインジウムガリウム酸化物を含むと好ましい。ガリウム原子の割合[Ga / (In + Ga)]は、例えば、70%以上、好ましくは80%以上、さらに好ましくは90%以上とする。

## 【0105】

ただし、半導体膜106aまたは/及び半導体膜106cが、酸化ガリウムであっても構わない。例えば、半導体膜106cとして、酸化ガリウムを用いると導電膜116aまたは導電膜116bと導電膜114との間に生じるリーク電流を低減することができる。即ち、トランジスタ150のオフ電流を小さくすることができる。

## 【0106】

このとき、導電膜114から半導体膜106にゲート電圧を印加すると、半導体膜106a、半導体膜106b、半導体膜106cのうち、電子親和力の大きい半導体膜106bにチャネルが形成される。

## 【0107】

図7(A)に示す一点鎖線E1-E2に対応するバンド構造を図7(C)に示す。図7(C)には、真空準位(vacuum levelと表記。)、各層の伝導帯下端のエネルギー(Ecと表記。)及び価電子帯上端のエネルギー(Evと表記。)を示す。

## 【0108】

ここで、半導体膜106aと半導体膜106bとの間には、半導体膜106aと半導体膜106bとの混合領域を有する場合がある。また、半導体膜106bと半導体膜106cとの間には、半導体膜106bと半導体膜106cとの混合領域を有する場合がある。混合領域は、界面準位密度が低くなる。そのため、半導体膜106a、半導体膜106b及び半導体膜106cの積層体は、それぞれの界面近傍において、エネルギーが連続的に変化する(連続接合ともいう。)バンド構造となる。

## 【0109】

このとき、電子は、半導体膜106a中及び半導体膜106c中ではなく、半導体膜106b中を主として移動する。つまり、半導体膜106bに電子が埋め込まれる。したがって、半導体膜106a及び半導体膜106bの界面における界面準位密度、半導体膜106bと半導体膜106cとの界面における界面準位密度を低くすることによって、半導体膜106b中で電子の移動が阻害されることが少なく、チャネル抵抗が小さいためトラン

10

20

30

40

50

ジスタ150のオン電流を高くすることができる。

**【0110】**

なお、トランジスタ150がs-channel構造を有する場合、半導体膜106bの全体にチャネルが形成される。したがって、半導体膜106bが厚いほどチャネル領域は大きくなる。即ち、半導体膜106bが厚いほど、トランジスタ150のオン電流を高くすることができる。例えば、10nm以上、好ましくは40nm以上、さらに好ましくは60nm以上、より好ましくは100nm以上の厚さの領域を有する半導体膜106bとすればよい。ただし、トランジスタ150を有する半導体装置の生産性が低下する場合があるため、例えば、300nm以下、好ましくは200nm以下、さらに好ましくは150nm以下の厚さの領域を有する半導体膜106bとすればよい。

10

**【0111】**

また、トランジスタ150のオン電流を高くするためには、半導体膜106cの厚さは小さいほど好ましい。例えば、10nm未満、好ましくは5nm以下、さらに好ましくは3nm以下の領域を有する半導体膜106cとすればよい。一方、半導体膜106cは、チャネルの形成される半導体膜106bへ、隣接する絶縁膜を構成する酸素以外の元素(水素、シリコンなど)が入り込まないようブロックする機能を有する。そのため、半導体膜106cは、ある程度の厚さを有することが好ましい。例えば、0.3nm以上、好ましくは1nm以上、さらに好ましくは2nm以上の厚さの領域を有する半導体膜106cとすればよい。また、半導体膜106cは、絶縁膜102などから放出される酸素の外方拡散を抑制するために、酸素をブロックする性質を有すると好ましい。

20

**【0112】**

また、信頼性を高くするためには、半導体膜106aは厚く、半導体膜106cは薄いことが好ましい。例えば、10nm以上、好ましくは20nm以上、さらに好ましくは40nm以上、より好ましくは60nm以上の厚さの領域を有する半導体膜106aとすればよい。半導体膜106aの厚さを、厚くすることで、隣接する絶縁膜と半導体膜106aとの界面からチャネルの形成される半導体膜106bまでの距離を離すことができる。ただし、トランジスタ150を有する半導体装置の生産性が低下する場合があるため、例えば、200nm以下、好ましくは120nm以下、さらに好ましくは80nm以下の厚さの領域を有する半導体膜106aとすればよい。

30

**【0113】**

例えば、酸化物半導体中のシリコンは、キャリアトラップやキャリア発生源となる場合がある。したがって、半導体膜106bのシリコン濃度は低いほど好ましい。例えば、半導体膜106bと半導体膜106aとの間に、例えば、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)において、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $2 \times 10^{18}$  atoms/cm<sup>3</sup>未満のシリコン濃度となる領域を有する。また、半導体膜106bと半導体膜106cとの間に、SIMSにおいて、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $2 \times 10^{18}$  atoms/cm<sup>3</sup>未満のシリコン濃度となる領域を有する。

40

**【0114】**

また、半導体膜106bの水素濃度を低減するために、半導体膜106a及び半導体膜106cの水素濃度を低減すると好ましい。半導体膜106a及び半導体膜106cは、SIMSにおいて、 $2 \times 10^{20}$  atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下の水素濃度となる領域を有する。また、半導体膜106bの窒素濃度を低減するために、半導体膜106a及び半導体膜106cの窒素濃度を低減すると好ましい。半導体膜106a及び半導体膜106cは、SIMSにおいて、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下の窒素濃度となる領域を有する。

50

## 【0115】

なお、酸化物半導体に銅が混入すると、電子トラップを生成する場合がある。電子トラップは、トランジスタのしきい値電圧をプラス方向へ変動させる場合がある。したがって、半導体膜106bの表面または内部における銅濃度は低いほど好ましい。例えば、半導体膜106bは、銅濃度が $1 \times 10^{19}$ atoms/cm<sup>3</sup>以下、 $5 \times 10^{18}$ atoms/cm<sup>3</sup>以下、または $1 \times 10^{18}$ atoms/cm<sup>3</sup>以下となる領域を有すると好ましい。

## 【0116】

なお、酸化物半導体をチャネルとするトランジスタに安定した電気特性を付与するためには、酸化物半導体中の不純物濃度を低減し、酸化物半導体を真性または実質的に真性にすることが有効である。ここで、実質的に真性とは、酸化物半導体のキャリア密度が、 $1 \times 10^{17}$ /cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$ /cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{13}$ /cm<sup>3</sup>以下、より好ましくは $1 \times 10^{11}$ /cm<sup>3</sup>以下、特に好ましくは $1 \times 10^{10}$ /cm<sup>3</sup>以下であり、 $1 \times 10^{-9}$ /cm<sup>3</sup>以上であることを指す。10

## 【0117】

上述の3層構造は一例である。例えば、半導体膜106aまたは半導体膜106cのない2層構造としても構わない。または、半導体膜106aの上もしくは下、または半導体膜106c上もしくは下に、半導体膜106a、半導体膜106b及び半導体膜106cとして例示した半導体のいずれか一を有する4層構造としても構わない。または、半導体膜106aの上、半導体膜106aの下、半導体膜106cの上、半導体膜106cの下のいずれか二箇所以上に、半導体膜106a、半導体膜106b及び半導体膜106cとして例示した半導体のいずれか一を有するn層構造(nは5以上の整数)としても構わない。20

## 【0118】

基板100としては、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板(イットリア安定化ジルコニア基板など)、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムを材料とした化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えばSOI(Silicon On Insulator)基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてもよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。30

## 【0119】

また、基板100として、可撓性基板を用いてもよい。なお、可撓性基板上にトランジスタを設ける方法としては、非可撓性の基板上にトランジスタを作製した後、トランジスタを剥離し、可撓性基板である基板100に転置する方法もある。その場合には、非可撓性基板とトランジスタとの間に剥離層を設けるとよい。なお、基板100として、繊維を編みこんだシート、フィルムまたは箔などを用いてもよい。また、基板100が伸縮性を有してもよい。また、基板100は、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有してもよい。または、元の形状に戻らない性質を有してもよい。基板100は、例えば、 $5 \mu\text{m}$ 以上 $700 \mu\text{m}$ 以下、好ましくは $10 \mu\text{m}$ 以上 $500 \mu\text{m}$ 以下、さらに好ましくは $15 \mu\text{m}$ 以上 $300 \mu\text{m}$ 以下の厚さとなる領域を有する。基板100を薄くすると、トランジスタ150を有する半導体装置を軽量化することができる。また、基板100を薄くすることで、ガラスなどを用いた場合にも伸縮性を有する場合や、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有する場合がある。そのため、落下などによっ4050

て基板 100 上の半導体装置に加わる衝撃などを緩和することができる。即ち、丈夫な半導体装置を提供することができる。

#### 【0120】

可撓性基板である基板 100 としては、例えば、金属、合金、樹脂もしくはガラス、またはそれらの纖維などを用いることができる。可撓性基板である基板 100 は、線膨張率が低いほど環境による変形が抑制されて好ましい。可撓性基板である基板 100 としては、例えば、線膨張率が  $1 \times 10^{-3} / K$  以下、 $5 \times 10^{-5} / K$  以下、または  $1 \times 10^{-5} / K$  以下である材質を用いればよい。樹脂としては、例えば、ポリエステル、ポリオレフイン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネート、アクリルなどがある。特に、アラミドは、線膨張率が低いため、可撓性基板である基板 100 として好適である。10

#### 【0121】

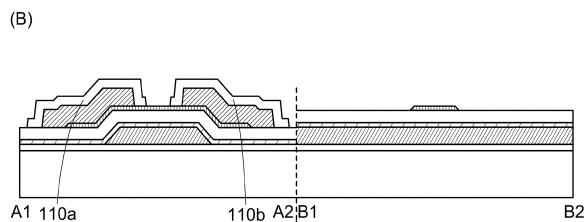

なお、トランジスタ 150 は、図 8 (A) または図 8 (B) に示す断面図の構造であっても構わない。図 8 (A) は、導電膜 114 が導電膜 104 と電気的に接続している点が図 1 (B) に示した構造と異なる。また、図 8 (B) は、導電膜 104 及び絶縁膜 102 を設けない点が図 1 (B) と異なる。

#### 【0122】

<トランジスタ構造 1 の作製方法>

以下では、図 1 に示したトランジスタ 150 の作製方法について説明する。

#### 【0123】

まず、基板 100 を準備する。

#### 【0124】

次に、絶縁膜 101 を成膜する。絶縁膜 101 の成膜は、スパッタリング法、化学気相成長（CVD：Chemical Vapor Deposition）法、分子線エピタキシー（MBE：Molecular Beam Epitaxy）法またはパルスレーザ堆積（PLD：Pulsed Laser Deposition）法、原子層堆積（ALD：Atomic Layer Deposition）法などを用いて行うことができる。

#### 【0125】

なお、CVD 法は、プラズマを利用するプラズマ CVD (PECVD: Plasma Enhanced CVD) 法、熱を利用する熱 CVD (TCVD: Thermal CVD) 法、光を利用する光 CVD (Photo CVD) 法などに分類できる。さらに用いる原料ガスによって金属 CVD (MCVD: Metal CVD) 法、有機金属 CVD (MO-CVD: Metal Organic CVD) 法に分けることができる。30

#### 【0126】

プラズマ CVD 法は、比較的低温で高品質の膜が得られる。また、熱 CVD 法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子（トランジスタ、容量素子など）などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いない熱 CVD 法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、熱 CVD 法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。40

#### 【0127】

また、ALD 法も、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。また、ALD 法も、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

#### 【0128】

CVD 法及び ALD 法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、50

被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、A L D 法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。ただし、A L D 法は、比較的成膜速度が遅いため、成膜速度の速いC V D 法などの他の成膜方法と組み合わせて用いることが好ましい場合もある。

#### 【 0 1 2 9 】

C V D 法及びA L D 法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、C V D 法及びA L D 法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、C V D 法及びA L D 法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間の分、成膜に掛かる時間を短くすることができる。したがって、半導体装置の生産性を高めることができる場合がある。10

#### 【 0 1 3 0 】

次に、導電膜を成膜する。導電膜の成膜は、スパッタリング法、C V D 法、M B E 法またはP L D 法、A L D 法などを用いて行うことができる。

#### 【 0 1 3 1 】

次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜 1 0 4 を形成する（図 9 ( A ) 参照）。20

#### 【 0 1 3 2 】

なお、フォトリソグラフィ法では、まず、フォトマスクを介してレジストを露光する。次に、露光された領域を、現像液を用いて除去または残存させてレジストマスクを形成する。次に、当該レジストマスクを介してエッチング処理することで導電膜、半導体膜または絶縁膜などを所望の形状に加工することができる。例えば、K r F エキシマレーザ光、A r F エキシマレーザ光、E U V ( E x t r e m e U l t r a v i o l e t ) 光などを用いて、レジストを露光することでレジストマスクを形成すればよい。また、基板と投影レンズとの間に液体（例えば水）を満たして露光する、液浸技術を用いてもよい。また、前述した光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、フォトマスクは不要となる。なお、レジストマスクの除去には、アッシングなどのドライエッチング処理またはノンウェットエッチング処理を用いることができる。30

#### 【 0 1 3 3 】

次に、絶縁膜 1 0 2 a 及び絶縁膜 1 0 2 b を成膜する（図 9 ( B ) 参照）。絶縁膜 1 0 2 a 及び絶縁膜 1 0 2 b の成膜は、スパッタリング法、C V D 法、M B E 法またはP L D 法、A L D 法などを用いて行うことができる。なお、絶縁膜 1 0 2 a 及び絶縁膜 1 0 2 b をまとめて絶縁膜 1 0 2 ともいう。

#### 【 0 1 3 4 】

次に、絶縁膜 1 0 2 に酸素を添加する処理を行っても構わない。酸素を添加する処理としては、例えば、イオン注入法、プラズマ処理法などがある。なお、絶縁膜 1 0 2 に添加された酸素は、過剰酸素となる。40

#### 【 0 1 3 5 】

次に、半導体膜を成膜する。半導体膜の成膜は、スパッタリング法、C V D 法、M B E 法またはP L D 法、A L D 法などを用いて行うことができる。

#### 【 0 1 3 6 】

次に、半導体膜に酸素を添加する処理を行っても構わない。酸素を添加する処理としては、例えば、イオン注入法、プラズマ処理法などがある。なお、半導体膜に添加された酸素は、過剰酸素となる。なお、半導体膜が積層膜である場合、図 1 ( A ) の半導体膜 1 0 6 となる半導体に対応する層に酸素を添加する処理を行うと好ましい。

#### 【 0 1 3 7 】

次に、第 1 の加熱処理を行うと好ましい。第 1 の加熱処理は、1 5 0 以上基板の歪み点50

未満、好ましくは 200 以上 480 以下、さらに好ましくは 300 以上 480 以下で行えればよい。第 1 の加熱処理は、不活性ガス雰囲気、または酸化性ガスを 10 ppm 以上、1 % 以上もしくは 10 % 以上含む雰囲気で行う。第 1 の加熱処理は減圧状態で行つてもよい。または、第 1 の加熱処理は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上、1 % 以上または 10 % 以上含む雰囲気で加熱処理を行ってもよい。第 1 の加熱処理によって、半導体膜の結晶性を高めることや、水素や水などの不純物を除去することができる。

## 【0138】

次に、半導体膜をフォトリソグラフィ法などによって加工し、半導体膜 106 を形成する（図 9（C）参照）。 10

## 【0139】

次に、導電膜を成膜する。導電膜の成膜は、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法などを用いて行うことができる。

## 【0140】

次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜 116a 及び導電膜 116b を形成する（図 10（A）参照）。

## 【0141】

次に、絶縁膜を成膜する。絶縁膜の成膜は、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法などを用いて行うことができる。 20

## 【0142】

次に、絶縁膜をフォトリソグラフィ法などによって加工し、絶縁膜 110a 及び絶縁膜 110b を形成する（図 10（B）参照）。

## 【0143】

次に、絶縁膜を成膜する。絶縁膜の成膜は、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法などを用いて行うことができる。

## 【0144】

次に、絶縁膜をフォトリソグラフィ法などによって加工し、絶縁膜 112 を形成する。

## 【0145】

次に、導電膜を成膜する。導電膜の成膜は、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法などを用いて行うことができる。 30

## 【0146】

次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜 114 を形成する。

## 【0147】

なお、導電膜 114 を形成した後に絶縁膜を成膜してもよい。絶縁膜の成膜は、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法などを用いて行うことができる。また、該絶縁膜の成膜より後のタイミングにおいて第 2 の加熱処理を行っても構わない。第 2 の加熱処理を行うことで、絶縁膜 102 などに含まれる過剰酸素が半導体膜 106 まで移動するため、半導体膜 106 の欠陥（酸素欠損）を低減することができる。なお、第 2 の加熱処理は、絶縁膜 102 中の過剰酸素（酸素）が半導体膜 106 まで拡散する温度で行えればよい。例えば、第 1 の加熱処理についての記載を参照しても構わない。または、第 2 の加熱処理は、第 1 の加熱処理よりも低い温度が好ましい。第 1 の加熱処理と第 2 の加熱処理の温度差は、20 以上 150 以下、好ましくは 40 以上 100 以下とする。これにより、絶縁膜 102 から余分に過剰酸素（酸素）が放出することを抑えることができる。なお、第 2 の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてもよい場合がある。 40

## 【0148】

以上のようにして、図 1 に示したトランジスタ 150 を作製することができる。

## 【0149】

トランジスタ 150 は、絶縁膜 110a 及び絶縁膜 110b を設けることにより、導電膜 114 と導電膜 116a との間、及び導電膜 114 と導電膜 116b との間の寄生容量を 50

小さくすることができる。また、寄生容量を削減することにより、当該半導体装置の動作速度を向上させることができる。また、半導体膜 106 の大部分と、導電膜 116a または導電膜 116b とを接触させることにより、寄生抵抗を低減することができる、また、寄生抵抗を低減することにより、オン電流を大きくすることができる。

#### 【0150】

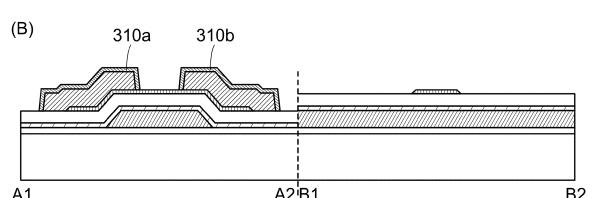

##### <トランジスタ構造2>

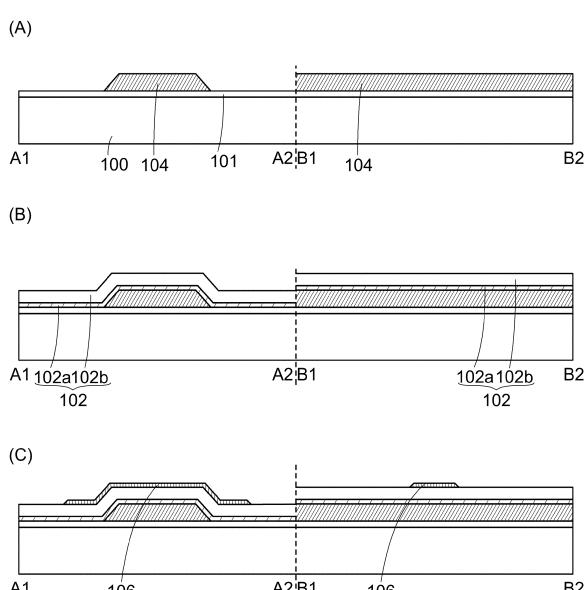

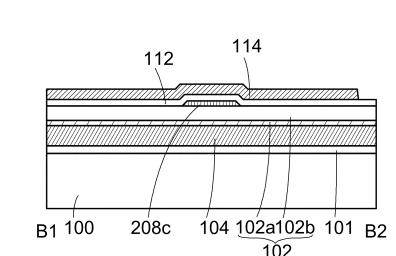

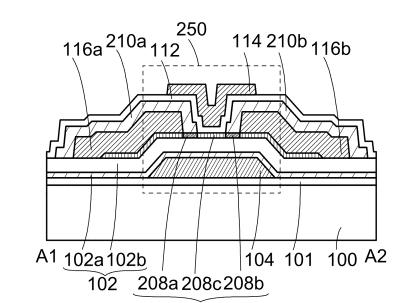

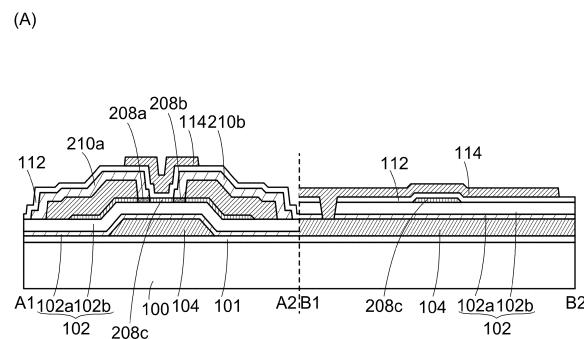

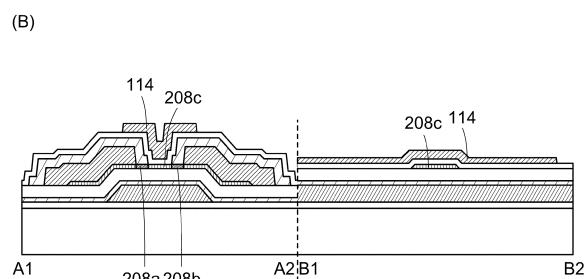

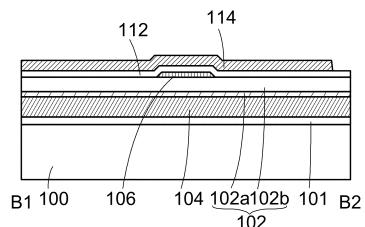

以下では、図1などに示したトランジスタ150とは、異なる構造を有するトランジスタ250について説明する。図11(A)、図11(B)及び図11(C)は、本発明の一態様に係るトランジスタ250の上面図及び断面図である。図11(A)は上面図である。図11(B)及び図11(C)は、図11(A)に示す一点鎖線A1-A2、及び一点鎖線B1-B2に対応する断面図である。なお、図11(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。10

#### 【0151】

図11(B)において、トランジスタ250は、基板100上の絶縁膜101と、絶縁膜101上の導電膜104と、導電膜104上の絶縁膜102と、絶縁膜102上の半導体膜106と、半導体膜106の上面及び側面と接する領域を有する導電膜116a及び導電膜116bと、導電膜116aの上面及び側面と接する、半導体膜106上の絶縁膜210aと、導電膜116bの上面及び側面と接する、半導体膜106上の絶縁膜210bと、絶縁膜210a上、絶縁膜210b上、及び半導体膜106上の絶縁膜112と、絶縁膜112上の導電膜114と、を有する。なお、導電膜114と半導体膜106とは、互いに重なる領域を有している。また、半導体膜106は、低抵抗領域208a、低抵抗領域208b、及びチャネル形成領域208cを有する。20

#### 【0152】

なお、トランジスタ250は、絶縁膜101を有さなくても構わない場合がある。

#### 【0153】

トランジスタ250において、絶縁膜101は下地絶縁膜としての機能を有する。また、導電膜104はゲート電極としての機能を有する。また、絶縁膜102はゲート絶縁膜としての機能を有する。また、導電膜116a及び導電膜116bは、ソース電極及びドレイン電極としての機能を有する。また、絶縁膜112はゲート絶縁膜としての機能を有する。また、導電膜114はゲート電極としての機能を有する。したがって、導電膜104または導電膜114に印加する電位によって、半導体膜106の抵抗を制御することができる。即ち、導電膜104または導電膜114に印加する電位によって、導電膜116aと導電膜116bとの間の導通・非導通を制御することができる。30

#### 【0154】

また、トランジスタ250の半導体膜106は、導電膜116aと半導体膜106とが互いに接する領域と、絶縁膜210aと半導体膜106とが互いに接する領域と、絶縁膜112と半導体膜106とが互いに接する領域と、絶縁膜210bと半導体膜106とが互いに接する領域と、導電膜116bと半導体膜106とが互いに接する領域と、を有する。40

#### 【0155】

なお、絶縁膜210a及び絶縁膜210bが窒化シリコン、窒化酸化シリコンなどの窒化物絶縁膜である場合、窒化物絶縁膜に含まれる水素を、半導体膜106に移動させることができる。この結果、半導体膜106より抵抗値が低い領域である低抵抗領域208a及び低抵抗領域208bを形成することができる。

#### 【0156】

このとき、導電膜116aと、低抵抗領域208aとはエネルギー障壁が十分小さいためオーミック接触となる。また、導電膜116bと、低抵抗領域208bとはエネルギー障壁が十分小さいためオーミック接触となる。したがって、導電膜116a及び導電膜116bと、低抵抗領域208a及び低抵抗領域208bを含む半導体膜106との間で電子の授受がスムーズに行われる。50

**【0157】**

以上に示したように、導電膜 116a 及び導電膜 116b と、半導体膜 106 との間で電子の授受がスムーズに行われ、かつ前述したチャネル抵抗の小さい半導体装置は優れたスイッチング特性を有する。

**【0158】**

トランジスタ 250 は、導電膜 114 と導電膜 116a との間、導電膜 114 と導電膜 116b との間に、それぞれ絶縁膜 210a、絶縁膜 210b 及び絶縁膜 112 を有することで、寄生容量を小さくすることができる。

**【0159】**

なお、トランジスタ 250 は、図 12(A) または図 12(B) に示す断面図の構造であっても構わない。図 12(A) は、導電膜 114 が導電膜 104 と電気的に接続している点が図 11(B) に示した構造と異なる。また、図 12(B) は、導電膜 104 及び絶縁膜 102 を設けない点が図 11(B) と異なる。

**【0160】**

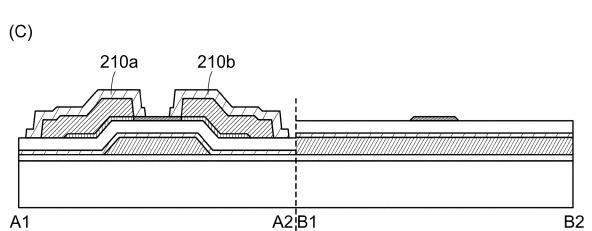

<トランジスタ構造 2 の作製方法>

以下では、図 11 に示したトランジスタ 250 の作製方法について説明する。

**【0161】**

まず、基板 100 を準備する。次に、絶縁膜 101 を成膜する。次に、導電膜を成膜する。次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜 104 を形成する。次に、絶縁膜 102a 及び絶縁膜 102b を成膜する。次に、半導体膜を成膜する。次に、半導体膜をフォトリソグラフィ法などによって加工し、半導体膜 106 を形成する。次に、導電膜を成膜する。次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜 116a 及び導電膜 116b を形成する(図 13(A) 参照)。ここまで工程は、トランジスタ構造 1 の作製方法の図 9(A) 乃至図 10(A) の説明を援用することができる。

**【0162】**

次に、絶縁膜 210 を成膜する。絶縁膜 210 の成膜は、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法などを用いて行うことができる。なお、絶縁膜 210 は窒化物絶縁膜であり、窒化物絶縁膜に含まれる水素を、半導体膜 106 に移動させることができる。この結果、半導体膜 106 に低抵抗領域 208 が形成される(図 13(B) 参照)。

**【0163】**

次に、絶縁膜 210 をフォトリソグラフィ法などによって加工し、絶縁膜 210a 及び絶縁膜 210b を形成する(図 13(C) 参照)。

**【0164】**

次に、絶縁膜を成膜する。絶縁膜の成膜は、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法などを用いて行うことができる。

**【0165】**

次に、絶縁膜をフォトリソグラフィ法などによって加工し、絶縁膜 112 を形成する(図 14(A) 参照)。

**【0166】**

次に、第 2 の加熱処理を行う。第 2 の加熱処理を行うことで、絶縁膜 102 などに含まれる過剰酸素が半導体膜 106 まで移動するため、半導体膜 106 の欠陥(酸素欠損)を低減することができる。つまり、低抵抗領域 208 の絶縁膜 210a 及び絶縁膜 210b と接さない領域に絶縁膜 102 などに含まれる過剰酸素が移動し、チャネル形成領域 208c が形成される。また、低抵抗領域 208 の絶縁膜 210a 及び絶縁膜 210b と接する領域は、絶縁膜 210a 及び絶縁膜 210b に含まれる水素が半導体膜 106 に移動しているため、低抵抗領域 208a 及び低抵抗領域 208b が形成される。なお、第 2 の加熱処理は、絶縁膜 102 中の過剰酸素(酸素)が半導体膜 106 まで拡散する温度で行えばよい。例えば、第 1 の加熱処理についての記載を参照しても構わない。または、第 2 の加

10

20

30

40

50

熱処理は、第1の加熱処理よりも低い温度が好ましい。第1の加熱処理と第2の加熱処理の温度差は、20以上150以下、好ましくは40以上100以下とする。これにより、絶縁膜102から余分に過剰酸素(酸素)が放出することを抑えることができる。なお、第2の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてもよい場合がある。

#### 【0167】

次に、導電膜を成膜する。導電膜の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

#### 【0168】

次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜114を形成する。

10

#### 【0169】

以上のようにして、図11に示したトランジスタ250を作製することができる。

#### 【0170】

トランジスタ250は、窒化物絶縁膜である絶縁膜210a及び絶縁膜210bを設けることにより、低抵抗領域208a及び低抵抗領域208bを形成することができ、導電膜116aと低抵抗領域208aと、及び導電膜116bと低抵抗領域208bとはエネルギー障壁が十分小さいためオーミック接触となる。したがって、導電膜116a及び導電膜116bと、低抵抗領域208a及び低抵抗領域208bを含む半導体膜106との間で電子の授受がスムーズに行われ、かつチャネル抵抗が小さいため優れたスイッチング特性を有することができる。

20

#### 【0171】

また、絶縁膜210a及び絶縁膜210bを設けることにより、導電膜114と導電膜116aとの間、及び導電膜114と導電膜116bとの間の寄生容量を小さくすることができる。また、寄生容量を削減することにより、当該半導体装置の動作速度を向上させることができる。また、半導体膜106の大部分と、導電膜116aまたは導電膜116bとを接触させることにより、寄生抵抗を低減することができる、また、寄生抵抗を低減することにより、オン電流を大きくすることができる。

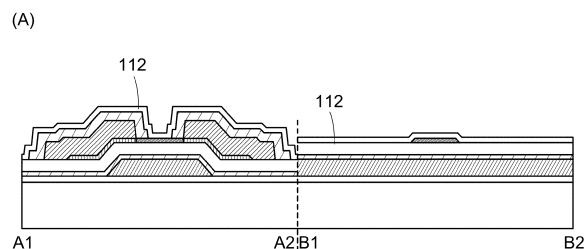

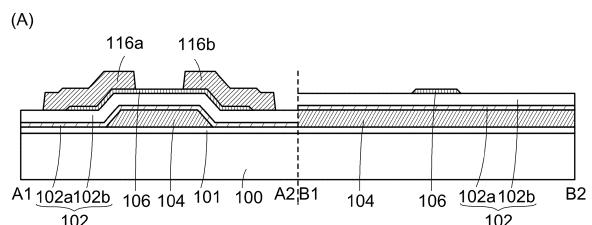

#### 【0172】

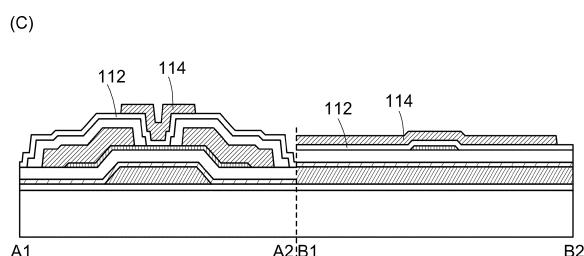

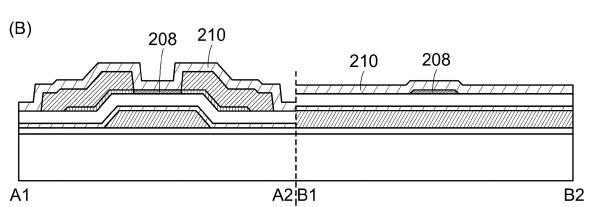

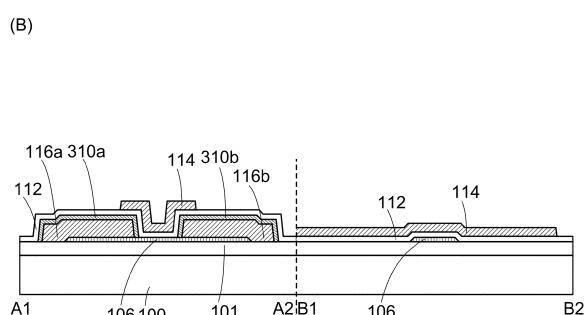

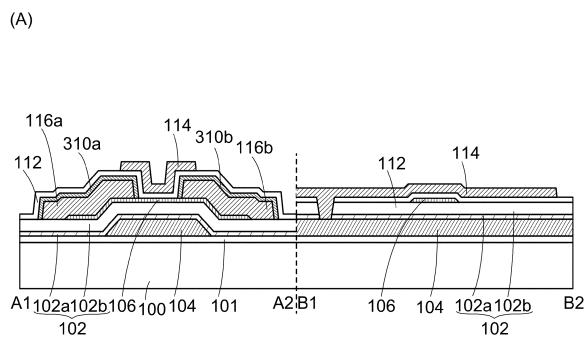

<トランジスタ構造3>

以下では、先に示したトランジスタとは、異なる構造を有するトランジスタ350について説明する。図15(A)、図15(B)及び図15(C)は、本発明の一態様に係るトランジスタ350の上面図及び断面図である。図15(A)は上面図である。図15(B)及び図15(C)は、図15(A)に示す一点鎖線A1-A2、及び一点鎖線B1-B2に対応する断面図である。なお、図15(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

30

#### 【0173】

図15(B)において、トランジスタ350は、基板100上の絶縁膜101と、絶縁膜101上の導電膜104と、導電膜104上の絶縁膜102と、絶縁膜102上の半導体膜106と、半導体膜106の上面及び側面と接する領域を有する導電膜116a及び導電膜116bと、導電膜116aの上面及び側面と接する、半導体膜106上の絶縁膜310aと、導電膜116bの上面及び側面と接する、半導体膜106上の絶縁膜310bと、絶縁膜310a上、絶縁膜310b上、及び半導体膜106上の絶縁膜112と、絶縁膜112上の導電膜114と、を有する。なお、導電膜114と半導体膜106とは、互いに重なる領域を有している。

40

#### 【0174】

なお、トランジスタ350は、絶縁膜101を有さなくても構わない場合がある。

#### 【0175】

トランジスタ350において、絶縁膜101は下地絶縁膜としての機能を有する。また、導電膜104はゲート電極としての機能を有する。また、絶縁膜102はゲート絶縁膜としての機能を有する。また、導電膜116a及び導電膜116bは、ソース電極及びドレ

50

イン電極としての機能を有する。また、絶縁膜 112 はゲート絶縁膜としての機能を有する。また、導電膜 114 はゲート電極としての機能を有する。したがって、導電膜 104 または導電膜 114 に印加する電位によって、半導体膜 106 の抵抗を制御することができる。即ち、導電膜 104 または導電膜 114 に印加する電位によって、導電膜 116a と導電膜 116bとの間の導通・非導通を制御することができる。

#### 【0176】

また、トランジスタ 350 の半導体膜 106 は、導電膜 116a と半導体膜 106 とが互いに接する領域と、絶縁膜 310a と半導体膜 106 とが互いに接する領域と、絶縁膜 112 と半導体膜 106 とが互いに接する領域と、絶縁膜 310b と半導体膜 106 とが互いに接する領域と、導電膜 116b と半導体膜 106 とが互いに接する領域と、を有する。

10

#### 【0177】

絶縁膜 310a 及び絶縁膜 310b は、導電膜 116a 及び導電膜 116b の表面を酸化または窒化させて形成する。導電膜 116a 及び導電膜 116b としては、例えば、ポリシリコン、マグネシウム、アルミニウム、バナジウム、クロム、イットリウム、ジルコニウム、ニオブ、ネオジム、ハフニウム及びタンタルを一種以上含む導電膜を、単層で、または積層で用いればよい。

#### 【0178】

トランジスタ 350 は、導電膜 114 と導電膜 116a との間、導電膜 114 と導電膜 116b との間に、それぞれ絶縁膜 310a、絶縁膜 310b 及び絶縁膜 112 を有することで、寄生容量を小さくすることができる。

20

#### 【0179】

なお、トランジスタ 350 は、図 16(A) または図 16(B) に示す断面図の構造であっても構わない。図 16(A) は、導電膜 114 が導電膜 104 と電気的に接続している点が図 15(B) に示した構造と異なる。また、図 16(B) は、導電膜 104 及び絶縁膜 102 を設けない点が図 15(B) と異なる。

#### 【0180】

<トランジスタ構造 3 の作製方法>

以下では、図 15 に示したトランジスタ 350 の作製方法について説明する。

#### 【0181】

30

まず、基板 100 を準備する。次に、絶縁膜 101 を成膜する。次に、導電膜を成膜する。次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜 104 を形成する。次に、絶縁膜 102a 及び絶縁膜 102b を成膜する。次に、半導体膜を成膜する。次に、半導体膜をフォトリソグラフィ法などによって加工し、半導体膜 106 を形成する。次に、導電膜を成膜する。次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜 116a 及び導電膜 116b を形成する(図 17(A) 参照)。ここまで工程は、トランジスタ構造 1 の作製方法の図 9(A) 乃至図 10(A) の説明を援用することができる。

#### 【0182】

次に、導電膜 116a 及び導電膜 116b の表面を酸化または窒化させて絶縁膜 310a 及び絶縁膜 310b を形成する(図 17(B) 参照)。導電膜 116a 及び導電膜 116b の表面を酸化または窒化させる方法としては、例えば、熱酸化(または熱窒化)、プラズマ酸化(またはプラズマ窒化)、及び酸素イオン注入(または窒素イオン注入)などを用いることができる。

40

#### 【0183】

次に、絶縁膜を成膜する。絶縁膜の成膜は、スパッタリング法、CVD 法、MBE 法または PLD 法、ALD 法などを用いて行うことができる。

#### 【0184】

次に、絶縁膜をフォトリソグラフィ法などによって加工し、絶縁膜 112 を形成する(図 17(C) 参照)。

50

**【0185】**

次に、導電膜を成膜する。導電膜の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

**【0186】**

次に、導電膜をフォトリソグラフィ法などによって加工し、導電膜114を形成する。

**【0187】**

なお、導電膜114を形成した後に絶縁膜を成膜してもよい。絶縁膜の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。また、該絶縁膜の成膜より後のタイミングにおいて第2の加熱処理を行っても構わない。第2の加熱処理を行うことで、絶縁膜102などに含まれる過剰酸素が半導体膜106まで移動するため、半導体膜106の欠陥(酸素欠損)を低減することができる。なお、第2の加熱処理は、絶縁膜102中の過剰酸素(酸素)が半導体膜106まで拡散する温度で行えばよい。例えば、第1の加熱処理についての記載を参照しても構わない。または、第2の加熱処理は、第1の加熱処理よりも低い温度が好ましい。第1の加熱処理と第2の加熱処理の温度差は、20以上150以下、好ましくは40以上100以下とする。これにより、絶縁膜102から余分に過剰酸素(酸素)が放出することを抑えることができる。なお、第2の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてもよい場合がある。

**【0188】**

以上のようにして、図15に示したトランジスタ350を作製することができる。

20

**【0189】**

トランジスタ350は、絶縁膜310a及び絶縁膜310bを設けることにより、導電膜114と導電膜116aとの間、及び導電膜114と導電膜116bとの間の寄生容量を小さくすることができる。また、寄生容量を削減することにより、当該半導体装置の動作速度を向上させることができる。また、半導体膜106の大部分と、導電膜116aまたは導電膜116bとを接触させることにより、寄生抵抗を低減することができる、また、寄生抵抗を低減することにより、オン電流を大きくすることができる。

**【0190】**

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

30

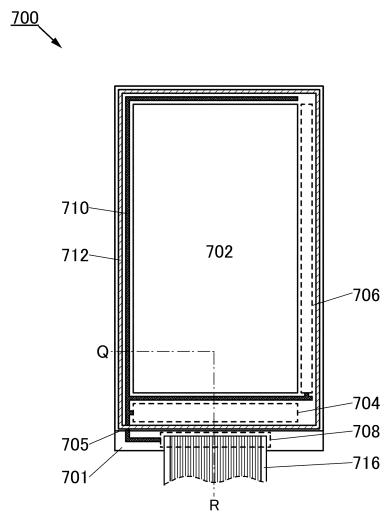

**【0191】****(実施の形態2)**

本実施の形態においては、先の実施の形態で例示したトランジスタを有する表示装置の一例について、図18乃至図20を用いて以下説明を行う。

**【0192】**

図18は、表示装置の一例を示す上面図である。図18に示す表示装置700は、第1の基板701上に設けられた画素部702と、第1の基板701に設けられたソースドライバ回路部704及びゲートドライバ回路部706と、画素部702、ソースドライバ回路部704、及びゲートドライバ回路部706を囲むように配置されるシール材712と、第1の基板701に対向するように設けられる第2の基板705と、を有する。なお、第1の基板701と第2の基板705は、シール材712によって封止されている。すなわち、画素部702、ソースドライバ回路部704、及びゲートドライバ回路部706は、第1の基板701とシール材712と第2の基板705によって封止されている。なお、図18には図示しないが、第1の基板701と第2の基板705の間には表示素子が設けられる。

40

**【0193】**

また、表示装置700は、第1の基板701上のシール材712によって囲まれている領域とは異なる領域に、画素部702、ソースドライバ回路部704、及びゲートドライバ回路部706と電気的に接続されるFPC端子部708(FPC:flexible printed circuit)が設けられる。また、FPC端子部708には、FPC

50

716が接続され、FPC716によって画素部702、ソースドライバ回路部704、及びゲートドライバ回路部706に各種信号等が供給される。また、画素部702、ソースドライバ回路部704、ゲートドライバ回路部706、及びFPC端子部708には、信号線710が各々接続されている。FPC716により供給される各種信号等は、信号線710を介して、画素部702、ソースドライバ回路部704、ゲートドライバ回路部706、及びFPC端子部708に与えられる。

#### 【0194】

また、表示装置700にゲートドライバ回路部706を複数設けてもよい。また、表示装置700としては、ソースドライバ回路部704、及びゲートドライバ回路部706を画素部702と同じ第1の基板701に形成している例を示しているが、この構成に限定されない。例えば、ゲートドライバ回路部706のみを第1の基板701に形成しても良い、またはソースドライバ回路部704のみを第1の基板701に形成しても良い。この場合、ソースドライバ回路またはゲートドライバ回路等が形成された基板（例えば、単結晶半導体膜、多結晶半導体膜で形成された駆動回路基板）を、第1の基板701に実装する構成としても良い。なお、別途形成した駆動回路基板の接続方法は、特に限定されるものではなく、COG（Chip On Glass）方法、ワイヤボンディング方法などを用いることができる。

10

#### 【0195】

また、表示装置700が有する画素部702、ソースドライバ回路部704及びゲートドライバ回路部706は、複数のトランジスタを有しており、本発明の一態様の半導体装置であるトランジスタを適用することができる。

20

#### 【0196】

また、表示装置700は、様々な素子を有することが出来る。該素子の一例としては、液晶素子、EL（エレクトロルミネッセンス）素子（有機物及び無機物を含むEL素子、有機EL素子、無機EL素子）、LED（白色LED、赤色LED、緑色LED、青色LEDなど）、トランジスタ（電流に応じて発光するトランジスタ）、電子放出素子、電子インク、電気泳動素子、グレーティングライトバルブ（GLV）、プラズマディスプレイ（PDP）、MEMS（マイクロ・エレクトロ・メカニカル・システム）を用いた表示素子、デジタルマイクロミラーデバイス（DMD）、DMS（デジタル・マイクロ・シャッター）、MIRASOL（登録商標）、IMOD（インターフェアレンス・モジュレーション）素子、シャッター方式のMEMS表示素子、光干渉方式のMEMS表示素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブを用いた表示素子などの少なくとも一つを有している。これらの他にも、電気的または磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有していても良い。EL素子を用いた表示装置の一例としては、ELディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッショニングディスプレイ（FED）又はSED方式平面型ディスプレイ（SED：Surface-conduction Electron-emitter Display）などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ（透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ）などがある。電子インク又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。なお、半透過型液晶ディスプレイや反射型液晶ディスプレイを実現する場合には、画素電極の一部、または、全部が、反射電極としての機能を有するようすればよい。例えば、画素電極の一部、または、全部が、アルミニウム、銀、などを有するようになればよい。さらに、その場合、反射電極の下に、SRAMなどの記憶回路を設けることも可能である。これにより、さらに、消費電力を低減することができる。

30

#### 【0197】

なお、表示装置700における表示方式は、プログレッシブ方式やインターレース方式等を用いることができる。また、カラー表示する際に画素で制御する色要素としては、RGB（Rは赤、Gは緑、Bは青を表す）の三色に限定されない。例えば、Rの画素とGの画

40

50

素とBの画素とW(白)の画素の四画素から構成されてもよい。または、ペンタイル配列のように、RGBのうちの2色分で一つの色要素を構成し、色要素よって、異なる2色を選択して構成してもよい。またはRGBに、イエロー、シアン、マゼンタ等を一色以上追加してもよい。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。ただし、開示する発明はカラー表示の表示装置に限定されるものではなく、モノクロ表示の表示装置に適用することもできる。

#### 【0198】

また、バックライト(有機EL素子、無機EL素子、LED、蛍光灯など)に白色光(W)を用いて表示装置をフルカラー表示させるために、着色層(カラーフィルタともいう。)を用いてもよい。着色層は、例えば、レッド(R)、グリーン(G)、ブルー(B)、イエロー(Y)などを適宜組み合わせて用いることができる。着色層を用いることで、着色層を用いない場合と比べて色の再現性を高くすることができる。このとき、着色層を有する領域と、着色層を有さない領域と、を配置することによって、着色層を有さない領域における白色光を直接表示に利用しても構わない。一部に着色層を有さない領域を配置することで、明るい表示の際に、着色層による輝度の低下を少なくでき、消費電力を2割から3割程度低減できる場合がある。ただし、有機EL素子や無機EL素子などの自発光素子を用いてフルカラー表示する場合、R、G、B、Y、ホワイト(W)を、それぞれの発光色を有する素子から発光させても構わない。自発光素子を用いることで、着色層を用いた場合よりも、さらに消費電力を低減できる場合がある。

#### 【0199】

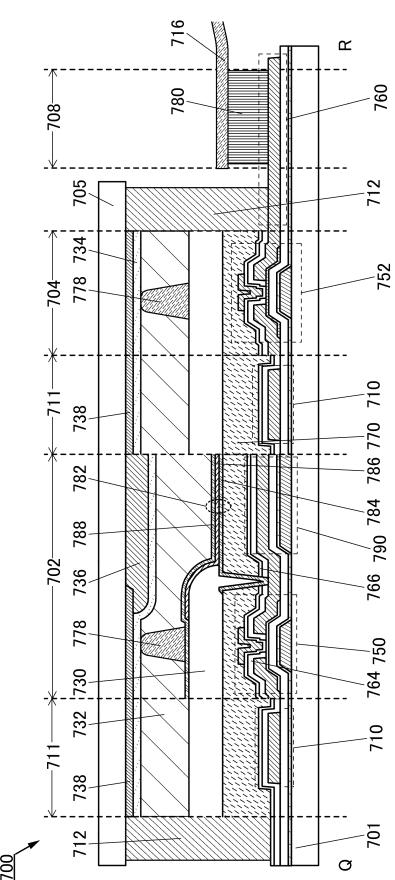

本実施の形態においては、表示素子として液晶素子及びEL素子を用いる構成について、図19及び図20を用いて説明する。なお、図19は、図18に示す一点鎖線Q-Rにおける断面図であり、表示素子として液晶素子を用いた構成である。また、図20は、図18に示す一点鎖線Q-Rにおける断面図であり、表示素子としてEL素子を用いた構成である。

#### 【0200】

まず、図19及び図20に示す共通部分について最初に説明し、次に異なる部分について以下説明する。

#### 【0201】

<表示装置の共通部分に関する説明>

図19及び図20に示す表示装置700は、引き回し配線部711と、画素部702と、ソースドライバ回路部704と、FPC端子部708と、を有する。また、引き回し配線部711は、信号線710を有する。また、画素部702は、トランジスタ750及び容量素子790を有する。また、ソースドライバ回路部704は、トランジスタ752を有する。

#### 【0202】

トランジスタ750及びトランジスタ752は、先に示すトランジスタを用いることができる。

#### 【0203】

本実施の形態で用いるトランジスタは、高純度化し、酸素欠損の形成を抑制した酸化物半導体膜を有する。該トランジスタは、オフ状態における電流値(オフ電流値)を低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

#### 【0204】

また、本実施の形態で用いるトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。例えば、このような高速駆動が可能なトランジスタを液晶表示装置に用いることで、画素部のスイッチングトランジスタと、駆動回路部に使用するドライバトランジスタを同一基板上に形成することができる。すなわち、別途駆動回路として、シリコンウェハ等により形成された半導体装置を用いる必要がないため、半導体装置の

10

20

30

40

50

部品点数を削減することができる。また、画素部においても、高速駆動が可能なトランジスタを用いることで、高画質な画像を提供することができる。

#### 【0205】

容量素子790は、一対の電極間に誘電体を有する構造である。より詳しくは、容量素子790の一方の電極としては、トランジスタ750のゲート電極として機能する導電膜と同一工程で形成された導電膜を用い、容量素子790の他方の電極としては、トランジスタ750のソース電極及びドレイン電極として機能する導電膜を用いる。また、一対の電極間に挟持される誘電体としては、トランジスタ750のゲート絶縁膜として機能する絶縁膜を用いる。

#### 【0206】

また、図19及び図20において、トランジスタ750、トランジスタ752、及び容量素子790上に、絶縁膜764、絶縁膜766、及び平坦化絶縁膜770が設けられている。

#### 【0207】

絶縁膜764、絶縁膜766としては、それぞれ先の実施の形態に示す絶縁膜110a、絶縁膜110b、絶縁膜112と、同様の材料及び作製方法により形成することができる。また、平坦化絶縁膜770としては、ポリイミド樹脂、アクリル樹脂、ポリイミドアミド樹脂、ベンゾシクロブテン樹脂、ポリアミド樹脂、エポキシ樹脂等の耐熱性を有する有機材料を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、平坦化絶縁膜770を形成してもよい。また、平坦化絶縁膜770を設けない構成としてもよい。

#### 【0208】

また、信号線710は、トランジスタ750、トランジスタ752のソース電極及びドレイン電極として機能する導電膜と同じ工程で形成される。なお、信号線710は、トランジスタ750、トランジスタ752のソース電極及びドレイン電極と異なる工程で形成された導電膜、例えばゲート電極として機能する導電膜としてもよい。信号線710として、例えば、銅元素を含む材料を用いた場合、配線抵抗に起因する信号遅延等が少なく、大画面での表示が可能となる。

#### 【0209】

また、FPC端子部708は、接続電極760、異方性導電膜780、及びFPC716を有する。なお、接続電極760は、トランジスタ750、トランジスタ752のソース電極及びドレイン電極として機能する導電膜と同じ工程で形成される。また、接続電極760は、FPC716が有する端子と異方性導電膜780を介して、電気的に接続される。

#### 【0210】

また、第1の基板701及び第2の基板705としては、例えばガラス基板を用いることができる。また、第1の基板701及び第2の基板705として、可撓性を有する基板を用いてもよい。該可撓性を有する基板としては、例えばプラスチック基板等が挙げられる。

#### 【0211】

また、第1の基板701と第2の基板705の間には、構造体778が設けられる。構造体778は、絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、第1の基板701と第2の基板705の間の距離（セルギャップ）を制御するために設けられる。なお、構造体778として、球状のスペーサを用いていても良い。また、本実施の形態においては、構造体778を第1の基板701側に設ける構成について例示したが、これに限定されない。例えば、第2の基板705側に構造体778を設ける構成、または第1の基板701及び第2の基板705双方に構造体778を設ける構成としてもよい。

#### 【0212】

また、第2の基板705側には、ブラックマトリクスとして機能する遮光膜738と、カラーフィルタとして機能する着色膜736と、遮光膜738及び着色膜736に接する絶

10

20

30

40

50

縁膜 734 が設けられる。

【0213】

<表示素子として液晶素子を用いる表示装置の構成例>

図19に示す表示装置700は、液晶素子775を有する。液晶素子775は、導電膜772、導電膜774、及び液晶層776を有する。導電膜774は、第2の基板705側に設けられ、対向電極としての機能を有する。図19に示す表示装置700は、導電膜772と導電膜774に印加される電圧によって、液晶層776の配向状態が変わることによって光の透過、非透過が制御され画像を表示することができる。

【0214】

また、導電膜772は、トランジスタ750が有するソース電極及びドレイン電極として機能する導電膜に接続される。導電膜772は、平坦化絶縁膜770上に形成され画素電極、すなわち表示素子の一方の電極として機能する。また、導電膜772は、反射電極としての機能を有する。図19に示す表示装置700は、外光を利用し導電膜772で光を反射して着色膜736を介して表示する、所謂反射型のカラー液晶表示装置である。

10

【0215】

導電膜772としては、可視光において透光性のある導電膜、または可視光において反射性のある導電膜を用いることができる。可視光において透光性のある導電膜としては、例えば、インジウム(Indium)、亜鉛(Zinc)、錫(Silver)の中から選ばれた一種を含む材料を用いるとよい。可視光において反射性のある導電膜としては、例えば、アルミニウム、または銀を含む材料を用いるとよい。本実施の形態においては、導電膜772として、可視光において、反射性のある導電膜を用いる。

20

【0216】

また、導電膜772として、可視光において反射性のある導電膜を用いる場合、該導電膜を積層構造としてもよい。例えば、下層に膜厚100nmのアルミニウム膜を形成し、上層に厚さ30nmの銀合金膜(例えば、銀、パラジウム、及び銅を含む合金膜)を形成する。上述の構造とすることで、以下の優れた効果を奏する。

【0217】

(1) 下地膜と導電膜772との密着性を向上させることができる。(2) 薬液によってアルミニウム膜と、銀合金膜とを一括してエッチングすることが可能である。(3) 導電膜772の断面形状を良好な形状(例えば、テーパー形状)とすることができます。(3)の理由としては、アルミニウム膜は、銀合金膜よりも薬液によるエッチング速度が遅い、または上層の銀合金膜のエッチング後、下層のアルミニウム膜が露出した場合に、銀合金膜よりも卑な金属、別言するとイオン化傾向の高い金属であるアルミニウムから電子を引き抜くため、銀合金膜のエッチングが抑制され、下層のアルミニウム膜のエッチングの進行が速くなるためである。

30

【0218】

また、図19に示す表示装置700においては、画素部702の平坦化絶縁膜770の一部に凹凸が設けられている。該凹凸は、例えば、平坦化絶縁膜770を有機樹脂膜等で形成し、該有機樹脂膜の表面に凹凸を設けることで形成することができる。また、反射電極として機能する導電膜772は、上記凹凸に沿って形成される。したがって、外光が導電膜772に入射した場合において、導電膜772の表面で光を乱反射することができなり、視認性を向上させることができる。

40

【0219】

なお、図19に示す表示装置700は、反射型のカラー液晶表示装置について例示したが、これに限定されない、例えば、導電膜772を可視光において、透光性のある導電膜を用いることで透過型のカラー液晶表示装置としてもよい。透過型のカラー液晶表示装置の場合、平坦化絶縁膜770に設けられる凹凸については、設けない構成としてもよい。

【0220】

なお、図19において図示しないが、導電膜772、導電膜774の液晶層776と接する側に、それぞれ配向膜を設ける構成としてもよい。また、図19において図示しないが

50

、偏光部材、位相差部材、反射防止部材などの光学部材（光学基板）などは適宜設けてよい。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

#### 【0221】

表示素子として液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

#### 【0222】

また、横電界方式を採用する場合、配向膜を用いないブルー相を示す液晶を用いてもよい。

10 ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転位する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために数重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が短く、光学的等方性であるため、配向処理が不要であり、かつ、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。

#### 【0223】

また、表示素子として液晶素子を用いる場合、TN (Twisted Nematic) モード、IPS (In-Plane-Switching) モード、FFS (Fringing Field Switching) モード、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optical Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) モードなどを用いることができる。

20

#### 【0224】

また、ノーマリーブラック型の液晶表示装置、例えば垂直配向（VA）モードを採用した透過型の液晶表示装置としてもよい。垂直配向モードとしては、いくつか挙げられるが、

30 例えば、MVA (Multi-Domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ASV (Advanced Super View) モードなどを用いることができる。

#### 【0225】

<表示素子として発光素子を用いる表示装置>

図20に示す表示装置700は、発光素子782を有する。発光素子782は、導電膜784、EL層786、及び導電膜788を有する。図20に示す表示装置700は、発光素子782が有するEL層786が発光することによって、画像を表示することができる。

40

#### 【0226】

また、導電膜784は、トランジスタ750が有するソース電極及びドレイン電極として機能する導電膜に接続される。導電膜784は、平坦化絶縁膜770上に形成され画素電極、すなわち表示素子の一方の電極として機能する。導電膜784としては、可視光において透光性のある導電膜、または可視光において反射性のある導電膜を用いることができる。可視光において透光性のある導電膜としては、例えば、インジウム（In）、亜鉛（Zn）、錫（Sn）の中から選ばれた一種を含む材料を用いるとよい。可視光において反射性のある導電膜としては、例えば、アルミニウム、または銀を含む材料を用いるとよい。

#### 【0227】

また、図20に示す表示装置700には、平坦化絶縁膜770及び導電膜784上に絶縁

10

20

30

40

50

膜730が設けられる。絶縁膜730は、導電膜784の一部を覆う。なお、発光素子782はトップエミッション構造である。したがって、導電膜788は透光性を有し、EL層786が発する光を透過する。なお、本実施の形態においては、トップエミッション構造について、例示するが、これに限定されない。例えば、導電膜784側に光を射出するボトムエミッション構造や、導電膜784及び導電膜788の双方に光を射出するデュアルエミッション構造にも適用することができる。

#### 【0228】

また、発光素子782と重なる位置に、着色膜736が設けられ、絶縁膜730と重なる位置、引き回し配線部711、及びソースドライバ回路部704に遮光膜738が設けられている。また、着色膜736及び遮光膜738は、絶縁膜734で覆われている。また、発光素子782と絶縁膜734の間は封止膜732で充填されている。なお、図20に示す表示装置700においては、着色膜736を設ける構成について例示したが、これに限定されない。例えば、EL層786を塗り分けにより形成する場合においては、着色膜736を設けない構成としてもよい。

#### 【0229】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【0230】

(実施の形態3)

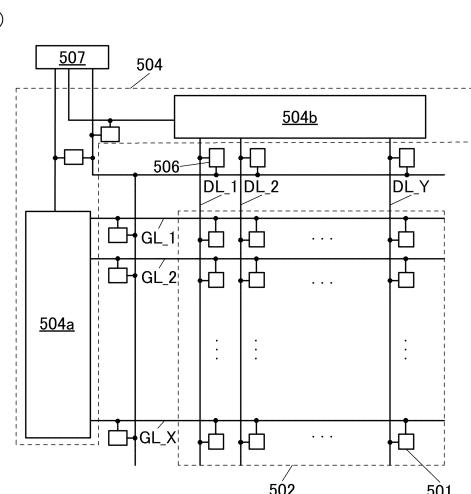

本実施の形態では、本発明の一態様の半導体装置を有する表示装置について、図21を用いて説明を行う。

#### 【0231】

図21(A)に示す表示装置は、表示素子の画素を有する領域(以下、画素部502という)と、画素部502の外側に配置され、画素を駆動するための回路を有する回路部(以下、駆動回路部504という)と、素子の保護機能を有する回路(以下、保護回路506という)と、端子部507と、を有する。なお、保護回路506は、設けない構成としてもよい。

#### 【0232】

駆動回路部504の一部、または全部は、画素部502と同一基板上に形成されていることが望ましい。これにより、部品数や端子数を減らすことが出来る。駆動回路部504の一部、または全部が、画素部502と同一基板上に形成されていない場合には、駆動回路部504の一部、または全部は、COGやTAB(Tape Automated Bonding)によって、実装することができる。

#### 【0233】

画素部502は、X行(Xは2以上の自然数)Y列(Yは2以上の自然数)に配置された複数の表示素子を駆動するための回路(以下、画素回路501という)を有し、駆動回路部504は、画素を選択する信号(走査信号)を出力する回路(以下、ゲートドライバ504aという)、画素の表示素子を駆動するための信号(データ信号)を供給するための回路(以下、ソースドライバ504b)などの駆動回路を有する。

#### 【0234】

ゲートドライバ504aは、シフトレジスタ等を有する。ゲートドライバ504aは、端子部507を介して、シフトレジスタを駆動するための信号が入力され、信号を出力する。例えば、ゲートドライバ504aは、スタートパルス信号、クロック信号等が入力され、パルス信号を出力する。ゲートドライバ504aは、走査信号が与えられる配線(以下、走査線GL\_1乃至GL\_Xという)の電位を制御する機能を有する。なお、ゲートドライバ504aを複数設け、複数のゲートドライバ504aにより、走査線GL\_1乃至GL\_Xを分割して制御してもよい。または、ゲートドライバ504aは、初期化信号を供給することができる機能を有する。ただし、これに限定されず、ゲートドライバ504aは、別の信号を供給することも可能である。

#### 【0235】

10

20

30

40

50

ソースドライバ504bは、シフトレジスタ等を有する。ソースドライバ504bは、端子部507を介して、シフトレジスタを駆動するための信号の他、データ信号の元となる信号（画像信号）が入力される。ソースドライバ504bは、画像信号を元に画素回路501に書き込むデータ信号を生成する機能を有する。また、ソースドライバ504bは、スタートパルス、クロック信号等が入力されて得られるパルス信号に従って、データ信号の出力を制御する機能を有する。また、ソースドライバ504bは、データ信号が与えられる配線（以下、データ線DL\_1乃至DL\_Yという）の電位を制御する機能を有する。または、ソースドライバ504bは、初期化信号を供給することができる機能を有する。ただし、これに限定されず、ソースドライバ504bは、別の信号を供給することも可能である。

10

#### 【0236】

ソースドライバ504bは、例えば複数のアナログスイッチなどを用いて構成される。ソースドライバ504bは、複数のアナログスイッチを順次オン状態にすることにより、画像信号を時分割した信号をデータ信号として出力できる。また、シフトレジスタなどを用いてソースドライバ504bを構成してもよい。

#### 【0237】

複数の画素回路501のそれぞれは、走査信号が与えられる複数の走査線GLの一つを介してパルス信号が入力され、データ信号が与えられる複数のデータ線DLの一つを介してデータ信号が入力される。また、複数の画素回路501のそれぞれは、ゲートドライバ504aによりデータ信号のデータの書き込み及び保持が制御される。例えば、m行n列目の画素回路501は、走査線GL\_m（mはX以下の自然数）を介してゲートドライバ504aからパルス信号が入力され、走査線GL\_mの電位に応じてデータ線DL\_n（nはY以下の自然数）を介してソースドライバ504bからデータ信号が入力される。

20

#### 【0238】

図21（A）に示す保護回路506は、例えば、ゲートドライバ504aと画素回路501の間の配線である走査線GLに接続される。または、保護回路506は、ソースドライバ504bと画素回路501の間の配線であるデータ線DLに接続される。または、保護回路506は、ゲートドライバ504aと端子部507との間の配線に接続することができる。または、保護回路506は、ソースドライバ504bと端子部507との間の配線に接続することができる。なお、端子部507は、外部の回路から表示装置に電源及び制御信号、及び画像信号を入力するための端子が設けられた部分をいう。

30

#### 【0239】

保護回路506は、自身が接続する配線に一定の範囲外の電位が与えられたときに、該配線と別の配線とを導通状態にする回路である。

#### 【0240】

図21（A）に示すように、画素部502と駆動回路部504にそれぞれ保護回路506を設けることにより、ESD（Electro Static Discharge：静電気放電）などにより発生する過電流に対する表示装置の耐性を高めることができる。ただし、保護回路506の構成はこれに限定されず、例えば、ゲートドライバ504aに保護回路506を接続した構成、またはソースドライバ504bに保護回路506を接続した構成とすることもできる。あるいは、端子部507に保護回路506を接続した構成とすることもできる。

40

#### 【0241】

また、図21（A）においては、ゲートドライバ504aとソースドライバ504bによって駆動回路部504を形成している例を示しているが、この構成に限定されない。例えば、ゲートドライバ504aのみを形成し、別途用意されたソースドライバ回路が形成された基板（例えば、単結晶半導体膜、多結晶半導体膜で形成された駆動回路基板）を実装する構成としても良い。

#### 【0242】

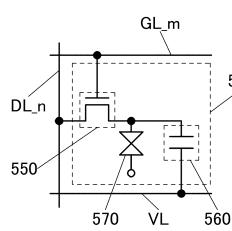

また、図21（A）に示す複数の画素回路501は、例えば、図21（B）に示す構成と

50

することができる。

【0243】

図21(B)に示す画素回路501は、液晶素子570と、トランジスタ550と、容量素子560と、を有する。トランジスタ550に先の実施の形態に示すトランジスタを適用することができる。

【0244】

液晶素子570の一対の電極の一方の電位は、画素回路501の仕様に応じて適宜設定される。液晶素子570は、書き込まれるデータにより配向状態が設定される。なお、複数の画素回路501のそれぞれが有する液晶素子570の一対の電極の一方に共通の電位(コモン電位)を与えてよい。また、各行の画素回路501の液晶素子570の一対の電極の一方に異なる電位を与えてよい。10

【0245】

例えば、液晶素子570を備える表示装置の駆動方法としては、TNモード、STNモード、VAモード、ASM(Axially Symmetric Aligned Micro-cell)モード、OCB(Optically Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、MVAモード、PVA(Patterned Vertical Alignment)モード、IPSモード、FFSモード、又はTBA(Transverse Bend Alignment)モードなどを用いてよい。また、表示装置の駆動方法としては、上述した駆動方法の他、ECB(Electrically Controlled Birefringence)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、PNLC(Polymer Network Liquid Crystal)モード、ゲストホストモードなどがある。ただし、これに限定されず、液晶素子及びその駆動方式として様々なものを用いることができる。20

【0246】

m行n列目の画素回路501において、トランジスタ550のソース電極またはドレイン電極の一方は、データ線DL\_nに電気的に接続され、他方は液晶素子570の一対の電極の他方に電気的に接続される。また、トランジスタ550のゲート電極は、走査線GL\_mに電気的に接続される。トランジスタ550は、オン状態またはオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。30

【0247】

容量素子560の一対の電極の一方は、電位が供給される配線(以下、電位供給線VL)に電気的に接続され、他方は、液晶素子570の一対の電極の他方に電気的に接続される。なお、電位供給線VLの電位の値は、画素回路501の仕様に応じて適宜設定される。容量素子560は、書き込まれたデータを保持する保持容量としての機能を有する。

【0248】

例えば、図21(B)の画素回路501を有する表示装置では、例えば、図21(A)に示すゲートドライバ504aにより各行の画素回路501を順次選択し、トランジスタ550をオン状態にしてデータ信号のデータを書き込む。40

【0249】

データが書き込まれた画素回路501は、トランジスタ550がオフ状態になることで保持状態になる。これを行毎に順次行うことにより、画像を表示できる。

【0250】

また、図21(A)に示す複数の画素回路501は、例えば、図21(C)に示す構成とすることができる。

【0251】

また、図21(C)に示す画素回路501は、トランジスタ552、トランジスタ554と、容量素子562と、発光素子572と、を有する。トランジスタ552及びトランジ50

スタ 5 5 4 のいずれか一方または双方に先の実施の形態に示すトランジスタを適用することができる。

**【 0 2 5 2 】**

トランジスタ 5 5 2 のソース電極及びドレイン電極の一方は、データ信号が与えられる配線（以下、信号線 D L \_ n という）に電気的に接続される。さらに、トランジスタ 5 5 2 のゲート電極は、ゲート信号が与えられる配線（以下、走査線 G L \_ m という）に電気的に接続される。

**【 0 2 5 3 】**

トランジスタ 5 5 2 は、オン状態またはオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

10

**【 0 2 5 4 】**

容量素子 5 6 2 の一対の電極の一方は、電位が与えられる配線（以下、電位供給線 V L \_ a という）に電気的に接続され、他方は、トランジスタ 5 5 2 のソース電極及びドレイン電極の他方に電気的に接続される。

**【 0 2 5 5 】**

容量素子 5 6 2 は、書き込まれたデータを保持する保持容量としての機能を有する。

**【 0 2 5 6 】**

トランジスタ 5 5 4 のソース電極及びドレイン電極の一方は、電位供給線 V L \_ a に電気的に接続される。さらに、トランジスタ 5 5 4 のゲート電極は、トランジスタ 5 5 2 のソース電極及びドレイン電極の他方に電気的に接続される。

20

**【 0 2 5 7 】**

発光素子 5 7 2 のアノード及びカソードの一方は、電位供給線 V L \_ b に電気的に接続され、他方は、トランジスタ 5 5 4 のソース電極及びドレイン電極の他方に電気的に接続される。

**【 0 2 5 8 】**

発光素子 5 7 2 としては、例えば有機エレクトロルミネセンス素子（有機 E L 素子ともいう）などを用いることができる。ただし、発光素子 5 7 2 としては、これに限定されず、無機材料からなる無機 E L 素子を用いても良い。

**【 0 2 5 9 】**

なお、電位供給線 V L \_ a 及び電位供給線 V L \_ b の一方には、高電源電位 V D D が与えられ、他方には、低電源電位 V S S が与えられる。

30

**【 0 2 6 0 】**

図 2 1 ( C ) の画素回路 5 0 1 を有する表示装置では、例えば、図 2 1 ( A ) に示すゲートドライバ 5 0 4 a により各行の画素回路 5 0 1 を順次選択し、トランジスタ 5 5 2 をオン状態にしてデータ信号のデータを書き込む。

**【 0 2 6 1 】**

データが書き込まれた画素回路 5 0 1 は、トランジスタ 5 5 2 がオフ状態になることで保持状態になる。さらに、書き込まれたデータ信号の電位に応じてトランジスタ 5 5 4 のソース電極とドレイン電極の間に流れる電流量が制御され、発光素子 5 7 2 は、流れる電流量に応じた輝度で発光する。これを行毎に順次行うことにより、画像を表示できる。

40

**【 0 2 6 2 】**

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

**【 0 2 6 3 】**

( 実施の形態 4 )

本実施の形態では、本発明の一態様の半導体装置を有する表示モジュール及び電子機器について、図 2 2 及び図 2 3 を用いて説明を行う。

**【 0 2 6 4 】**

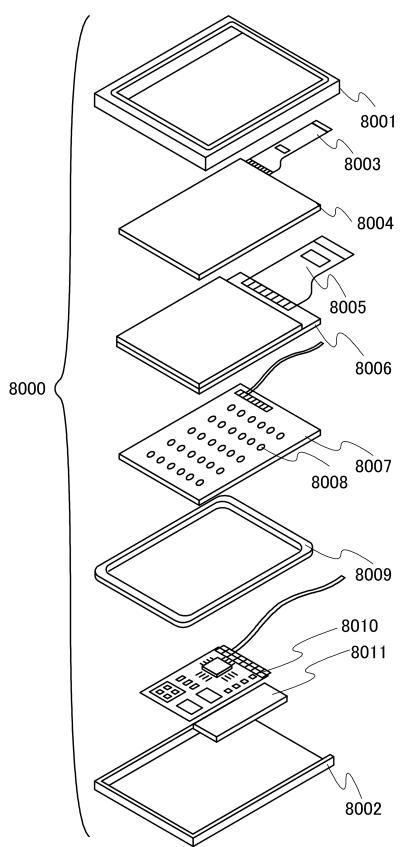

図 2 2 に示す表示モジュール 8 0 0 0 は、上部カバー 8 0 0 1 と下部カバー 8 0 0 2 との間に、F P C 8 0 0 3 に接続されたタッチパネル 8 0 0 4 、F P C 8 0 0 5 に接続された

50

表示パネル 8006、バックライトユニット 8007、フレーム 8009、プリント基板 8010、バッテリー 8011 を有する。

【0265】

本発明の一態様の半導体装置は、例えば、表示パネル 8006 に用いることができる。

【0266】

上部カバー 8001 及び下部カバー 8002 は、タッチパネル 8004 及び表示パネル 8006 のサイズに合わせて、形状や寸法を適宜変更することができる。

【0267】

タッチパネル 8004 は、抵抗膜方式または静電容量方式のタッチパネルを表示パネル 8006 に重畠して用いることができる。また、表示パネル 8006 の対向基板（封止基板）に、タッチパネル機能を持たせるようにすることも可能である。また、表示パネル 8006 の各画素内に光センサを設け、光学式のタッチパネルとすることも可能である。

10

【0268】

バックライトユニット 8007 は、光源 8008 を有する。なお、図 22 において、バックライトユニット 8007 上に光源 8008 を配置する構成について例示したが、これに限定さない。例えば、バックライトユニット 8007 の端部に光源 8008 を配置し、さらに光拡散板を用いる構成としてもよい。なお、有機 EL 素子等の自発光型の発光素子を用いる場合、または反射型パネル等の場合においては、バックライトユニット 8007 を設けない構成としてもよい。

【0269】

フレーム 8009 は、表示パネル 8006 の保護機能の他、プリント基板 8010 の動作により発生する電磁波を遮断するための電磁シールドとしての機能を有する。またフレーム 8009 は、放熱板としての機能を有していてもよい。

20

【0270】

プリント基板 8010 は、電源回路、ビデオ信号及びクロック信号を出力するための信号処理回路を有する。電源回路に電力を供給する電源としては、外部の商用電源であっても良いし、別途設けたバッテリー 8011 による電源であってもよい。バッテリー 8011 は、商用電源を用いる場合には、省略可能である。

【0271】

また、表示モジュール 8000 は、偏光板、位相差板、プリズムシートなどの部材を追加して設けてもよい。

30

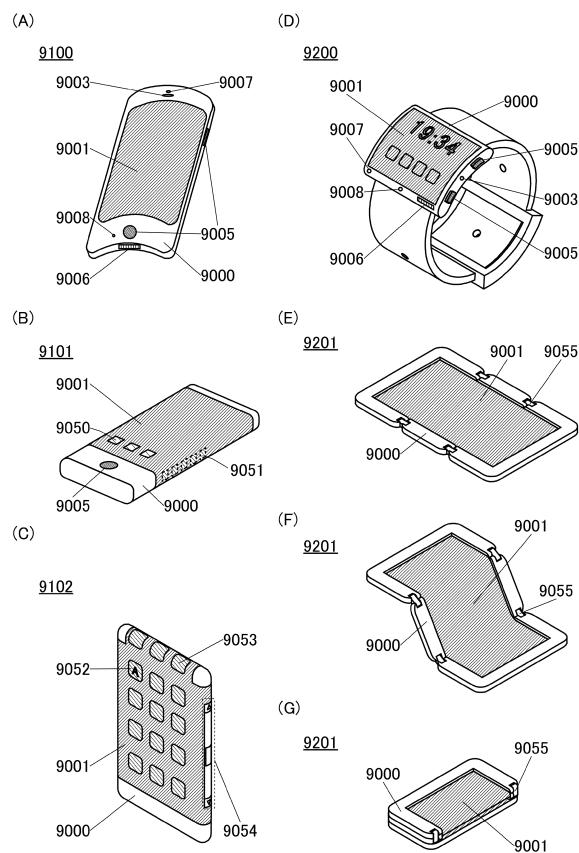

【0272】

図 23 (A) 乃至図 23 (G) は、電子機器を示す図である。これらの電子機器は、筐体 9000、表示部 9001、スピーカー 9003、操作キー 9005（電源スイッチ、又は操作スイッチを含む）、接続端子 9006、センサ 9007（力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい又は赤外線を測定する機能を含むもの）、マイクロフォン 9008、等を有することができる。

【0273】

図 23 (A) 乃至図 23 (G) に示す電子機器は、様々な機能を有することができる。例えば、様々な情報（静止画、動画、テキスト画像など）を表示部に表示する機能、タッチパネル機能、カレンダー、日付または時刻などを表示する機能、様々なソフトウェア（プログラム）によって処理を制御する機能、無線通信機能、無線通信機能を用いて様々なコンピュータネットワークに接続する機能、無線通信機能を用いて様々なデータの送信または受信を行う機能、記録媒体に記録されているプログラムまたはデータを読み出して表示部に表示する機能、等を有することができる。なお、図 23 (A) 乃至図 23 (G) に示す電子機器が有することのできる機能はこれらに限定されず、様々な機能を有することができる。また、図 23 (A) 乃至図 23 (G) には図示していないが、電子機器は、複数の表示部を有する構成としてもよい。また、該電子機器にカメラ等を設け、静止画を撮影する機能、動画を撮影する機能、撮影した画像を記録媒体（外部またはカメラに内蔵）に

40

50

保存する機能、撮影した画像を表示部に表示する機能、等を有していてもよい。

**【0274】**

図23(A)乃至図23(G)に示す電子機器の詳細について、以下説明を行う。

**【0275】**

図23(A)は、携帯情報端末9100を示す斜視図である。携帯情報端末9100が有する表示部9001は、可撓性を有する。そのため、湾曲した筐体9000の湾曲面に沿って表示部9001を組み込むことが可能である。また、表示部9001はタッチセンサを備え、指やスタイルスなどで画面に触れることで操作することができる。例えば、表示部9001に表示されたアイコンに触れることで、アプリケーションを起動することができる。

10

**【0276】**

図23(B)は、携帯情報端末9101を示す斜視図である。携帯情報端末9101は、例えば電話機、手帳又は情報閲覧装置等から選ばれた一つ又は複数の機能を有する。具体的には、スマートフォンとして用いることができる。なお、携帯情報端末9101は、スピーカー9003、接続端子9006、センサ9007等を省略して図示しているが、図23(A)に示す携帯情報端末9100と同様の位置に設けることができる。また、携帯情報端末9101は、文字や画像情報をその複数の面に表示することができる。例えば、3つの操作ボタン9050(操作アイコンまたは単にアイコンともいう)を表示部9001の一の面に表示することができる。また、破線の矩形で示す情報9051を表示部9001の他の面に表示することができる。なお、情報9051の一例としては、電子メールやSNS(ソーシャル・ネットワーキング・サービス)や電話などの着信を知らせる表示、電子メールやSNSなどの題名、電子メールやSNSなどの送信者名、日時、時刻、バッテリーの残量、アンテナ受信の強度などがある。または、情報9051が表示されている位置に、情報9051の代わりに、操作ボタン9050などを表示してもよい。

20

**【0277】**

図23(C)は、携帯情報端末9102を示す斜視図である。携帯情報端末9102は、表示部9001の3面以上に情報を表示する機能を有する。ここでは、情報9052、情報9053、情報9054がそれぞれ異なる面に表示されている例を示す。例えば、携帯情報端末9102の使用者は、洋服の胸ポケットに携帯情報端末9102を収納した状態で、その表示(ここでは情報9053)を確認することができる。具体的には、着信した電話の発信者の電話番号又は氏名等を、携帯情報端末9102の上方から観察できる位置に表示する。使用者は、携帯情報端末9102をポケットから取り出すことなく、表示を確認し、電話を受けるか否かを判断できる。

30

**【0278】**

図23(D)は、腕時計型の携帯情報端末9200を示す斜視図である。携帯情報端末9200は、移動電話、電子メール、文章閲覧及び作成、音楽再生、インターネット通信、コンピュータゲームなどの種々のアプリケーションを実行することができる。また、表示部9001はその表示面が湾曲して設けられ、湾曲した表示面に沿って表示を行ふことができる。また、携帯情報端末9200は、通信規格された近距離無線通信を実行することができる。例えば無線通信可能なヘッドセットと相互通信することによって、ハンズフリーで通話することもできる。また、携帯情報端末9200は、接続端子9006を有し、他の情報端末とコネクターを介して直接データのやりとりを行うことができる。また接続端子9006を介して充電を行うこともできる。なお、充電動作は接続端子9006を介さずに無線給電により行ってもよい。

40

**【0279】**

図23(E)(F)(G)は、折り畳み可能な携帯情報端末9201を示す斜視図である。また、図23(E)が携帯情報端末9201を展開した状態の斜視図であり、図23(F)が携帯情報端末9201を展開した状態または折り畳んだ状態の一方から他方に変化する途中の状態の斜視図であり、図23(G)が携帯情報端末9201を折り畳んだ状態の斜視図である。携帯情報端末9201は、折り畳んだ状態では可搬性に優れ、展開した

50

状態では、継ぎ目のない広い表示領域により表示の一覧性に優れる。携帯情報端末 920

1が有する表示部 9001は、ヒンジ 9055によって連結された3つの筐体 9000に

支持されている。ヒンジ 9055を介して2つの筐体 9000間を屈曲させることにより

、携帯情報端末 9201を展開した状態から折りたたんだ状態に可逆的に変形させること

ができる。例えば、携帯情報端末 9201は、曲率半径 1mm 以上 150mm 以下で曲げ

ることができる。

#### 【0280】

本実施の形態において述べた電子機器は、何らかの情報を表示するための表示部を有することを特徴とする。ただし、本発明の一態様の半導体装置は、表示部を有さない電子機器にも適用することができる。また、本実施の形態において述べた電子機器の表示部においては、可撓性を有し、湾曲した表示面に沿って表示を行うことができる構成、または折り畳み可能な表示部の構成について例示したが、これに限定されず、可撓性を有さず、平面部に表示を行う構成としてもよい。

#### 【0281】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

#### 【符号の説明】

##### 【0282】

|       |          |    |

|-------|----------|----|

| 100   | 基板       | 20 |

| 101   | 絶縁膜      |    |

| 102   | 絶縁膜      |    |

| 102 a | 絶縁膜      |    |

| 102 b | 絶縁膜      |    |

| 104   | 導電膜      |    |

| 106   | 半導体膜     |    |

| 106 a | 半導体膜     |    |

| 106 b | 半導体膜     |    |

| 106 c | 半導体膜     |    |

| 110 a | 絶縁膜      | 30 |

| 110 b | 絶縁膜      |    |

| 112   | 絶縁膜      |    |

| 114   | 導電膜      |    |

| 116 a | 導電膜      |    |

| 116 b | 導電膜      |    |

| 150   | トランジスタ   |    |

| 208   | 低抵抗領域    |    |

| 208 a | 低抵抗領域    |    |

| 208 b | 低抵抗領域    |    |

| 208 c | チャネル形成領域 |    |

| 210   | 絶縁膜      | 40 |

| 210 a | 絶縁膜      |    |

| 210 b | 絶縁膜      |    |

| 250   | トランジスタ   |    |

| 310 a | 絶縁膜      |    |

| 310 b | 絶縁膜      |    |

| 350   | トランジスタ   |    |

| 501   | 画素回路     |    |

| 502   | 画素部      |    |

| 504   | 駆動回路部    |    |

| 504 a | ゲートドライバ  | 50 |

|         |            |    |

|---------|------------|----|

| 5 0 4 b | ソースドライバ    |    |

| 5 0 6   | 保護回路       |    |

| 5 0 7   | 端子部        |    |

| 5 5 0   | トランジスタ     |    |

| 5 5 2   | トランジスタ     |    |

| 5 5 4   | トランジスタ     |    |

| 5 6 0   | 容量素子       |    |

| 5 6 2   | 容量素子       |    |

| 5 7 0   | 液晶素子       |    |

| 5 7 2   | 発光素子       | 10 |

| 7 0 0   | 表示装置       |    |

| 7 0 1   | 基板         |    |

| 7 0 2   | 画素部        |    |

| 7 0 4   | ソースドライバ回路部 |    |

| 7 0 5   | 基板         |    |

| 7 0 6   | ゲートドライバ回路部 |    |

| 7 0 8   | F P C 端子部  |    |

| 7 1 0   | 信号線        |    |

| 7 1 1   | 配線部        |    |

| 7 1 2   | シール材       | 20 |

| 7 1 6   | F P C      |    |

| 7 3 0   | 絶縁膜        |    |

| 7 3 2   | 封止膜        |    |

| 7 3 4   | 絶縁膜        |    |

| 7 3 6   | 着色膜        |    |

| 7 3 8   | 遮光膜        |    |

| 7 5 0   | トランジスタ     |    |

| 7 5 2   | トランジスタ     |    |

| 7 6 0   | 接続電極       |    |

| 7 6 4   | 絶縁膜        | 30 |

| 7 6 6   | 絶縁膜        |    |

| 7 7 0   | 平坦化絶縁膜     |    |

| 7 7 2   | 導電膜        |    |

| 7 7 4   | 導電膜        |    |

| 7 7 5   | 液晶素子       |    |

| 7 7 6   | 液晶層        |    |

| 7 7 8   | 構造体        |    |

| 7 8 0   | 異方性導電膜     |    |

| 7 8 2   | 発光素子       |    |

| 7 8 4   | 導電膜        | 40 |

| 7 8 6   | E L 層      |    |

| 7 8 8   | 導電膜        |    |

| 7 9 0   | 容量素子       |    |

| 5 1 0 0 | ペレット       |    |

| 5 1 2 0 | 基板         |    |

| 5 1 6 1 | 領域         |    |

| 8 0 0 0 | 表示モジュール    |    |

| 8 0 0 1 | 上部カバー      |    |

| 8 0 0 2 | 下部カバー      |    |

| 8 0 0 3 | F P C      | 50 |

|         |            |

|---------|------------|

| 8 0 0 4 | タッチパネル     |

| 8 0 0 5 | F P C      |

| 8 0 0 6 | 表示パネル      |

| 8 0 0 7 | バックライトユニット |

| 8 0 0 8 | 光源         |

| 8 0 0 9 | フレーム       |

| 8 0 1 0 | プリント基板     |

| 8 0 1 1 | バッテリー      |

| 9 0 0 0 | 筐体         |

| 9 0 0 1 | 表示部        |

| 9 0 0 3 | スピーカー      |

| 9 0 0 5 | 操作キー       |

| 9 0 0 6 | 接続端子       |

| 9 0 0 7 | センサ        |

| 9 0 0 8 | マイクロフォン    |

| 9 0 5 0 | 操作ボタン      |

| 9 0 5 1 | 情報         |

| 9 0 5 2 | 情報         |

| 9 0 5 3 | 情報         |

| 9 0 5 4 | 情報         |

| 9 0 5 5 | ヒンジ        |

| 9 1 0 0 | 携帯情報端末     |

| 9 1 0 1 | 携帯情報端末     |

| 9 1 0 2 | 携帯情報端末     |

| 9 2 0 0 | 携帯情報端末     |

| 9 2 0 1 | 携帯情報端末     |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

(B)

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

(B)

(C)

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

(B)

(C)

【図22】

【図23】

---

フロントページの続き

| (51)Int.Cl.             | F I                  |

|-------------------------|----------------------|

| H 01 L 51/50 (2006.01)  | H 01 L 29/78 6 1 7 T |

| H 05 B 33/14 (2006.01)  | H 01 L 29/78 6 1 7 V |

| H 01 L 21/265 (2006.01) | H 05 B 33/14 A       |

| H 01 L 21/477 (2006.01) | H 05 B 33/14 Z       |

|                         | H 01 L 21/265 Q      |

|                         | H 01 L 21/477        |

(72)発明者 中澤 安孝

栃木県栃木市都賀町升塚161-2 アドバンスト フィルム ディバイス インク株式会社内

(72)発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 脇水 佳弘

(56)参考文献 特開2013-251534(JP,A)

特開2011-151394(JP,A)

実開平03-101556(JP,U)

特開2011-135063(JP,A)

特開2014-029994(JP,A)

特開2014-075580(JP,A)

特開2011-243971(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 786

H 01 L 21 / 265

H 01 L 21 / 336

H 01 L 21 / 477

H 01 L 21 / 8234

H 01 L 27 / 06

H 01 L 27 / 088

H 01 L 51 / 50

H 05 B 33 / 14