(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5203352号

(P5203352)

(45) 発行日 平成25年6月5日(2013.6.5)

(24) 登録日 平成25年2月22日(2013.2.22)

|                         |                      |

|-------------------------|----------------------|

| (51) Int.Cl.            | F 1                  |

| HO 1 L 29/786 (2006.01) | HO 1 L 29/78 6 1 6 V |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 6 1 6 L |

| HO 1 L 21/02 (2006.01)  | HO 1 L 29/78 6 1 8 B |

| HO 1 L 27/12 (2006.01)  | HO 1 L 29/78 6 1 8 E |

|                         | HO 1 L 27/12 B       |

請求項の数 4 (全 8 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2009-503114 (P2009-503114)  |

| (86) (22) 出願日 | 平成19年2月22日 (2007.2.22)        |

| (65) 公表番号     | 特表2009-532875 (P2009-532875A) |

| (43) 公表日      | 平成21年9月10日 (2009.9.10)        |

| (86) 國際出願番号   | PCT/US2007/062559             |

| (87) 國際公開番号   | W02007/117775                 |

| (87) 國際公開日    | 平成19年10月18日 (2007.10.18)      |

| 審査請求日         | 平成22年1月20日 (2010.1.20)        |

| (31) 優先権主張番号  | 11/393,340                    |

| (32) 優先日      | 平成18年3月30日 (2006.3.30)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 テキサス州 78735<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100142907<br>弁理士 本田 淳                                                                                      |

| (72) 発明者  | チャン、ダー<br>アメリカ合衆国 78717 テキサス州<br>オースティン カッサンドラ ドライブ<br>10137                                               |

最終頁に続く

(54) 【発明の名称】エッチング停止層を用いてソース／ドレイン・ストレッサの形成を最適化する半導体の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体の製造方法であって、

埋め込み酸化物 (BOX) 層の上のエッチング停止層 (ESL) の上の活性半導体層を含む集積回路ウエハを形成することと、

前記活性半導体層のトランジスタチャネルの上にゲート誘電体の上のゲート電極を含むゲート構造を形成することと、

トランジスタチャネルの両側面に退けられたソース／ドレイン領域のエッチングを行い、前記 ESL を露出するソース／ドレイン空隙を形成することと、

ソース／ドレイン・ストレッサを用いて前記 ESL の上の前記ソース／ドレイン空隙を充填することと、前記ソース／ドレイン・ストレッサの格子定数は活性半導体層の格子定数と異なることと、

を含み、

前記集積回路ウエハを形成することは、

ドナーウエハの半導体基板上に前記エッチング停止層を形成することと、

前記エッチング停止層上に誘電体層を堆積させることと、

前記ドナーウエハへ水素を注入し、前記ドナーウエハの前記半導体基板に損傷領域を形成することと、

ハンドルウエハの半導体基板上に誘電体層を堆積させることと、

ドナーウエハの誘電体層をハンドルウエハの誘電体層に接合することと、

10

20

前記損傷領域に沿って前記ドナーウエハを分断することと、

を含む方法。

【請求項 2】

前記活性半導体層を形成することはシリコンを含み、前記 E S L は半導体化合物を含む請求項 1 に記載の方法。

【請求項 3】

前記半導体化合物は前記活性半導体層に擬似格子整合している請求項 2 に記載の方法。

【請求項 4】

前記半導体化合物はシリコンゲルマニウム化合物  $\text{Si}_{(1-x)}\text{Ge}_x$  を含み、同シリコンゲルマニウム化合物中のゲルマニウムの百分率 (X) は、5 ~ 15 % の範囲にある請求項 3 に記載の方法。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体製造の分野に関し、より詳細には、歪みトランジスタチャネルを用いる半導体の製造方法に関する。

【背景技術】

【0002】

歪みトランジスタを用いる半導体の製造方法はよく知られている。通常、トランジスタチャネルは、チャネルのキャリア移動度を改良することによってトランジスタ性能を向上させるため、1つ以上の軸に沿って引張または圧縮応力を加えられる。チャネルに応力を加えるための1つの技術には、ソース／ドレイン・ストレッサ (stressor) の使用が含まれる。ソース／ドレイン (S / D) ストレッサとは、トランジスタチャネル材料（通常はシリコン）の格子定数とは異なる格子定数を有するソース／ドレイン材料の使用を指す。S / D ストレッサは、通常、デバイス S / D 領域のエッチングに続き、そのエッチングの行われたキャビティにおける歪みフィルムのエピタキシャル成長によってもたらされる。この種類のソース／ドレイン・ストレッサを形成することは、ソース／ドレインのエッチング処理の制御が困難であるために、問題となることがある。S / D エッチングレートは、通常、ウエハを通じて異なり、デバイスフィーチャ密度の異なる領域に対しても変化する。その結果、エッチング処理には、望ましくない S / D リセス深さの変動が伴う。 20 30

【発明の開示】

【発明が解決しようとする課題】

【0003】

ソース／ドレイン・ストレッサを形成するための従来の技術に関連した処理変動性に対処する処理を実現することが望ましい。

【課題を解決するための手段】

【0004】

一態様では、半導体の製造方法には、シリコン・オン・インシュレータ (SOI) ウエハの活性層と BOX 層との間に、エッチング停止層 (E S L) が組み込まれる。この E S L によって、ソース／ドレイン・ストレッサの形成が容易となる。詳細には、E S L は、活性層と E S L との間で高い選択性を有するエッチング処理が利用可能な材料である。一実施形態では、活性層はシリコン活性層であり、E S L はシリコンゲルマニウムであり、ソース／ドレイン・ストレッサは、PMOSトランジスタ用のシリコンゲルマニウムまたはNMOSトランジスタ用のシリコン炭素など、シリコンの格子定数とは異なる格子定数を有する半導体化合物である。E S L および非常に選択性的なソース／ドレインエッチング処理を組み込むことによって、ソース／ドレイン・ストレッサを形成する従来の方法に関連した望ましくない変動性は、減少または除去される。本明細書に記載の半導体の製造方法の一態様は、活性半導体層と BOX 層との間に E S L を有する SOI ウエハの形成である。 40 50

**【発明を実施するための最良の形態】**

**【0005】**

ここで図1～6を参照する。図1～6には、一実施形態によるそのようなウエハの製造における選択された段階を示している。示したシーケンスには、第1のウエハ(ドナーウエハ)を処理して、誘電体層、ESLおよび活性半導体層を含むスタックを形成することが含まれる。この処理には、ドナーウエハの基板を分断し、活性半導体層を形成することが含まれ得る。誘電体層は、第2のウエハ(ハンドルウエハ)の半導体基板上に堆積される。次いで、ドナーウエハの誘電体層がハンドルウエハの誘電体層に対し接合される。接合された誘電体層はBOX層を形成する。

**【0006】**

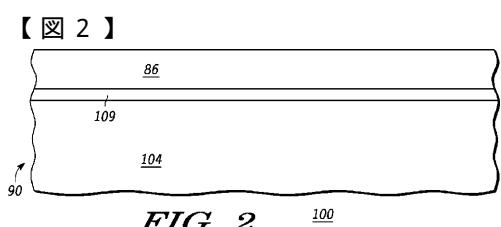

まず図1を参照する。図1には、製造方法の中間段階における集積回路100の部分的な断面図を示す。示した段階では、第1のウエハ(本明細書ではドナーウエハ90と呼ぶ)の半導体バルク104の上にESL109が形成されている。ESL109は、好適には約5～30nmの範囲の厚さ、さらに好適には約10nm以下の厚さを有する、比較的薄い膜である。ESL109の組成は、主として、そのエッティング特性により選択される。より詳細には、ESL109は、好適には、半導体バルク104の材料に関してエッティング選択的な材料である。本開示の目的では、エッティング処理が一方の材料に対し非常に選択的であることが見出される場合、ある材料は別の材料に関してエッティング選択的である。好適な実施形態では、ESL109と半導体バルク104との間の選択性は、好適には、10:1より大きい。ESL109についての第2の考慮事項は、トランジスタ性能に対しESL109が有し得る効果である。

10

**【0007】**

一部の実施形態では、半導体バルク104は結晶性シリコンであり、ESL層は、半導体バルク104に擬似格子整合した(*pseudomorphic*)半導体化合物である。それらの実施形態では、シリコンゲルマニウム化合物(Si<sub>(1-x)</sub>Ge<sub>x</sub>)はESL109に適した材料である。これは、シリコンゲルマニウムはシリコンに関して非常にエッティング選択的であるため、また、トランジスタチャネルの下のシリコンゲルマニウムの薄膜の存在は、トランジスタ特性に対し有益な効果を有し得るためである。これらの実施形態におけるESL109のゲルマニウム含有量(X)は、好適には、約5～15%の範囲にあり、一部の実施形態では、図9に関して以下に記載するように、続いて形成されるシリコンゲルマニウムのソース/ドレイン・ストレッサ中のゲルマニウム含有量の関数である。

20

**【0008】**

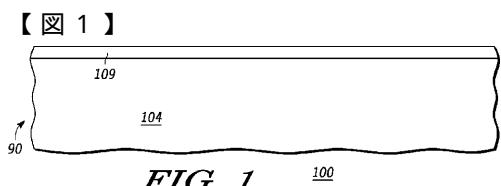

ここで図2を参照すると、ESL109の上に、堆積その他によって誘電体層86が形成されている。誘電体層86は、完成した集積回路において、BOX層のうちの少なくとも一部として機能する。誘電体層86の厚さは、好適には、約20～200nmの範囲にある。誘電体層86は、TEOS(テトラエチルオルトリケート)源を用いて従来のように形成されるケイ素酸化物層など、CVDケイ素酸化物層であってよい。

30

**【0009】**

ここで図3を参照すると、半導体バルク104内に注入損傷層84を形成するために、イオン注入82が実行されている。注入損傷層84によって、半導体バルク104は、ESL109に隣接した第1の領域105と、ESL109から離れた第2の領域107とに分けられる。一実施形態では、注入損傷層84は、5×10<sup>16</sup>cm<sup>-2</sup>以上の注入量を用いて半導体バルク104へ水素を注入することによって生成される。

40

**【0010】**

ここで図4を参照すると、集積回路ウエハ101を形成するために、参照符号92によって示されるように、ドナーウエハ90に対しハンドルウエハ94が接合されている。ハンドルウエハ94の示した実施形態では、バルク部分98の上に誘電体層96が備えられる。ハンドルウエハ94の誘電体層96は、好適には、ドナーウエハ90の誘電体層86と同じ誘電体または類似の誘電体である。ハンドルウエハ94のバルク部分98は、好適

50

には、結晶性シリコンなど半導体である。

#### 【0011】

注入損傷層84によって、図5に示す分断処理113が容易となる。図5では、注入損傷層84「の下の」半導体バルク104の第2の領域107は、ドナーウエハ90の残る部分から切り離され、破棄される。一実施形態では、イオン注入82には、損傷層84が約50nmだけESL109から移動した比較的狭い幅であるような、エネルギーおよび注入種が用いられる。適切な注入種には水素が含まれる。分断処理113と、デバイス処理用の第1の領域105の新たな面の調製との後、ドナーウエハ90の第1の領域105は、トランジスタや場合によっては他のデバイスが形成される集積回路100の活性層として機能する。したがって、本明細書では、第1の領域105を活性層105と呼ぶことがある。10

#### 【0012】

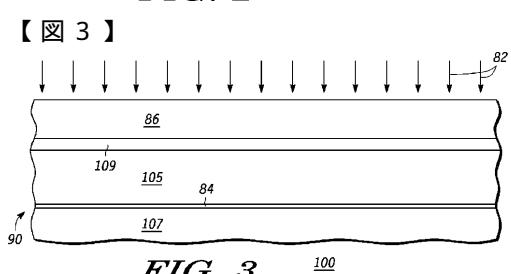

示した実施形態では、熱接合または別の既知の接合技術を用いて、集積回路ウエハ101にBOX層102を形成するために、ドナーウエハ90の誘電体層86がハンドルウエハ94の誘電体層96に対し接合される。この実施形態では、集積回路ウエハ101は、図6に示すように、半導体活性層105とBOX層102との間に位置するESL109を有するSOIウエハとして記載される。ESL109の存在によって、BOX層102に対しエッチングが行われることなく活性層105のロバストなエッティングを行うことが可能となり、これによってストレッサ形成処理（より詳細に以下に記載する）が容易となる。20

#### 【0013】

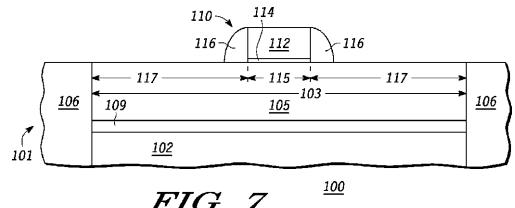

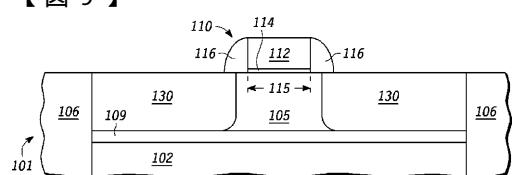

ここで図7を参照すると、分離構造106およびゲート構造110を形成するために、一実施形態による続く集積回路ウエハ101の処理が実行されている。分離構造106によって、活性層105の活性領域またはトランジスタ領域103の側方の境界が形成される。ゲート電極110は、ゲート誘電体114の上のゲート電極112と、ゲート電極112の側壁上のスペーサ構造（スペーサ）116とを備える。ゲート電極112の側方の境界によって、活性層105のトランジスタチャネル115の両側面に配置された、トランジスタチャネル115およびソース／ドレイン領域117の側方の境界がほぼ形成される。ゲート電極112は、ドーピングの行われたポリシリコンの導体構造、金属もしくは金属シリサイド材料、またはそれらの組み合わせである。ゲート誘電体114は、好適には、熱的に形成された二酸化シリコンか、またはハフニウム酸化物（HfO<sub>2</sub>）などの高K誘電体である。スペーサ116は、好適には、シリコン窒化物、シリコン酸化物またはそれらの組み合わせである。ソース／ドレイン拡張型の注入がスペーサ形成前に行われてもよい。30

#### 【0014】

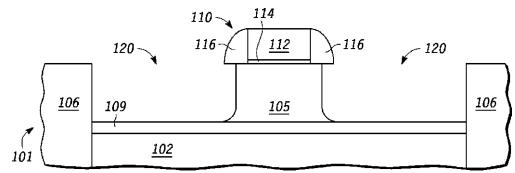

図8では、ESL109の上面を露出するソース／ドレイン空隙120を形成するために、活性層105のソース／ドレイン領域117がほぼ除去されている。一実施形態では、ソース／ドレイン領域117の除去には、ESL109に対し非常に選択的なエッティング処理が含まれる。本開示の目的では、非常に選択的なエッティングとは、主な対象である2つの材料（すなわち、エッティングされる層およびESL）間に10：1を超えるエッティングレート比を有するエッティング処理を指す。例えば、ソース／ドレイン領域117がシリコンであり、ESL109がシリコングルマニウムである一実施形態では、ソース／ドレイン領域117を除去するエッティング処理には、約75まで加熱されたNH<sub>4</sub>OH：H<sub>2</sub>O溶液を用いるウェットエッティング構成要素が含まれてもよい。例えば、フェン・ワング（Feng Wang）らによる、「Si対SiGeの高選択性化学エッティング（Highly Selective Chemical Etching of Si vs. SiGe）」、J. Electrochemical Society、1997年、第144巻、第3号、pp. L37～L39を参照されたい（80：1を超えるSi：SiGe選択性が報告されている）。40

#### 【0015】

ここで図9を参照すると、本明細書ではソース／ドレイン・ストレッサ130と呼ぶソース／ドレイン構造によって、図8のソース／ドレイン空隙120が充填されている。一実施形態では、ソース／ドレイン・ストレッサ130は、トランジスタチャネル115の大部分を占める元の活性層105の格子定数とは異なる格子定数を有する。ソース／ドレイン・ストレッサ130によって、トランジスタチャネル115に対する歪みがもたらされ、好適には、トランジスタチャネルにおいて関連するキャリアの移動度が改良される。

P MOSトランジスタでは、例えば、トランジスタチャネル115に圧縮応力を生じるソース／ドレイン・ストレッサ130によってホール移動度が改良されることによって、PMOSトランジスタの性能が改良される。NMOSトランジスタでは、ソース／ドレイン・ストレッサ130によって、好適には、トランジスタチャネル115に引張応力が生じて、電子移動性およびNMOSトランジスタ性能が改良される。PMOSトランジスタに適したソース／ドレイン・ストレッサ材料はシリコンゲルマニウムであり、NMOSトランジスタに適したソース／ドレイン・ストレッサ材料はシリコン炭素である。一実施形態では、ソース／ドレイン・ストレッサ130はシリコンゲルマニウム化合物( $\text{Si}_{(1-y)}\text{Ge}_y$ )であり、ESL109はシリコンゲルマニウム化合物( $\text{Si}_{(1-x)}\text{Ge}_x$ )である。ここで、XとYは異なる。好適には、この実施形態では、ソース／ドレイン・ストレッサ130の圧縮効果を強化するため、YはXより大きい。ストレッサフィルムには、適切な導電型のためにドーピングが行われてもよい。ドーピング処理は、適切な反応源を提供することによって、ストレッサフィルムのエピタキシャル成長中、系中で( $\text{in situ}$ )行われてもよく、注入によるストレッサフィルム成長の後に行われてもよい。アニュール処理はドーピング処理の後に行われてもよい。

#### 【0016】

上述においては、特定の実施形態に関連して本発明について記載した。しかしながら、当業者には、特許請求の範囲に述べる本発明の範囲から逸脱することなく、様々な修正および変更が可能であることが認められる。例えば、示した実施形態には、集積回路ウエハを形成するために、酸化物/Si STACKを有するハンドルウエハに対しSi/SiGe/酸化物STACKを有するドナーウエハを接合することが含まれているが、他の実施形態では、極薄体(UTB)SiGe・オン・インシュレータ(SGOI)ウエハから開始して、Si活性層をエピタキシャル成長させることによって、SiGeエッチング停止層が形成されてもよい。さらに他の処理では、分離BOXの上にSiGe層を有する従来のSGOIウエハから開始し、SiGe上層を薄化させてESLを形成し、Si活性層をエピタキシャル成長させてもよい。したがって、明細書および図面は限定的な意味ではなく例示として捉えられるものであり、そのような修正は全て、本発明の範囲の内に含まれることが意図される。

#### 【図面の簡単な説明】

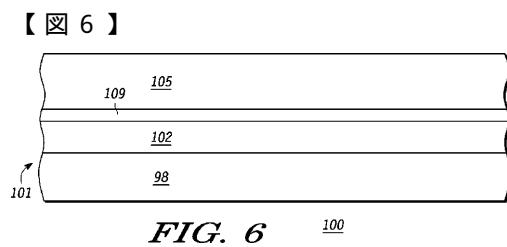

#### 【0017】

【図1】本発明の一実施形態による集積回路の製造の初期段階における半導体ウエハの部分的な断面図であり、ドナーウエハの半導体基板上のエッチング停止層の形成を強調して示す。

【図2】図1に続く、エッチング停止層上に誘電体層が形成される処理を示す図。

【図3】図2に続く、ドナーウエハ基板に損傷層が形成される処理を示す図。

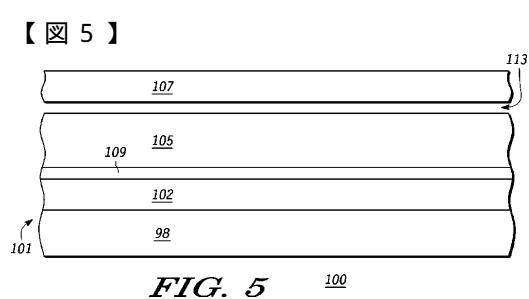

【図4】図3に続く、集積回路ウエハを形成するためにハンドルウエハ上の誘電体層にドナーウエハの誘電体層が接合される処理を示す図。

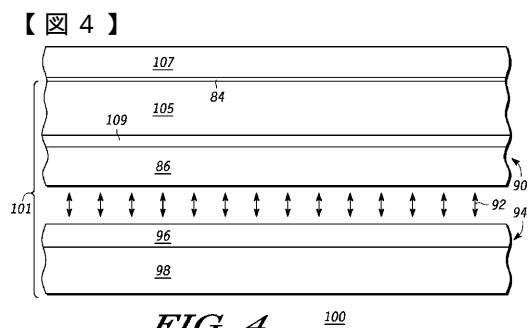

【図5】図4に続く、新たな上面を露出するために図3の損傷層にてドナーウエハが分断される処理を示す図。

【図6】図5に続く、デバイス処理のために図5の新たな上面が調製される処理を示す図。

【図7】図6に続く、活性半導体層のトランジスタチャネルの上において、活性半導体層上にゲート構造が形成される処理を示す図。

【図8】図7に続く、トランジスタチャネルの両側面に配置されたウエハのソース／ドレ

10

20

30

40

50

イン領域にソース / ドレイン空隙のエッチングが行われる処理を示す図。

【図9】図8に続く、ソース / ドレイン・ストレッサによってソース / ドレイン空隙が充填される処理を示す図。

【図7】

FIG. 7 100

【図8】

FIG. 8 100

【図9】

FIG. 9 100

---

フロントページの続き

(72)発明者 ホワイト、テッド

アメリカ合衆国 78731 テキサス州 オースティン ローレルウッド ドライブ 6508

(72)発明者 グエン、ビック イエン

アメリカ合衆国 78733 テキサス州 オースティン ローレルウッド ドライブ 110

審査官 井上 弘亘

(56)参考文献 米国特許出願公開第2006/0030093(US, A1)

特開2003-078116(JP, A)

国際公開第2006/011912(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/02

H01L 21/336

H01L 27/12