(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5041250号

(P5041250)

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月20日(2012.7.20)

(51) Int.CI.

H01L 21/027 (2006.01)

F 1

H01L 21/30 570

請求項の数 20 (全 20 頁)

(21) 出願番号 特願2008-529192 (P2008-529192)

(86) (22) 出願日 平成18年8月28日 (2006.8.28)

(65) 公表番号 特表2009-507375 (P2009-507375A)

(43) 公表日 平成21年2月19日 (2009.2.19)

(86) 國際出願番号 PCT/US2006/033703

(87) 國際公開番号 WO2007/027686

(87) 國際公開日 平成19年3月8日 (2007.3.8)

審査請求日 平成20年4月28日 (2008.4.28)

(31) 優先権主張番号 11/219,346

(32) 優先日 平成17年9月1日 (2005.9.1)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 595168543

マイクロン テクノロジー, インク.

アメリカ合衆国, アイダホ州 83716

-9632, ボイズ, サウス フェデ

ラル ウエイ 8000

(74) 復代理人 100105485

弁理士 平野 雅典

(74) 代理人 100106851

弁理士 野村 泰久

(74) 代理人 100074099

弁理士 大菅 義之

(72) 発明者 サンデュ, ガーテ, エス.

アメリカ合衆国, アイダホ州 83706

, ボイズ, イースト パークリバー ドラ

イブ 2964

最終頁に続く

(54) 【発明の名称】ピッチ増大用のスペーサを有するマスク・パターン、およびその形成方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板の上のある領域にわたって一時的な材料で形成され、空所によって分離された複数の一時的なプレースホルダを形成するステップと、

一時的なプレースホルダの各々の上表面の上にあるキャップ層を形成するステップと、前記一時的な材料の一部を、複数のマスク・フィーチャを形成する別の材料に変換して、複数のスペーサを形成するステップであって、前記キャップ層は前記上表面における反応を禁止し、前記別の材料に変換された前記材料の一部は、前記一時的なプレースホルダの上に固相反応物からなる共形の層をブランケット堆積することによって、前記一時的なプレースホルダの側壁を前記固相反応物と選択的に反応させるステップと、

未変換の一時的な材料を選択的に除去するステップと、

前記複数のスペーサによって画定されたマスク・パターンを介して前記基板を処理するステップとを含む、半導体処理方法。

## 【請求項2】

前記複数の一時的なプレースホルダの側壁を選択的に反応させるステップが、アニールを実施するステップを含み、反応条件を選択するステップが、前記アニールの温度および継続時間を前記マスク・フィーチャの所望の限界寸法に基づいて選択するステップを含む、請求項1に記載の方法。

## 【請求項3】

前記一時的な材料の一部を変換するステップが、前記固相反応物を含む層の一部分を前

10

20

記一時的な材料と反応させ、さらに前記層の反応しない残存物を選択的に除去するステップを含む、請求項 1 に記載の方法。

【請求項 4】

基板の上のある領域にわたって一時的な材料で形成され、空所によって分離された複数の一時的なプレースホルダを形成するステップと、

一時的なプレースホルダの各々の上表面の上にあるキャップ層を形成するステップと、前記一時的な材料の一部を、複数のマスク・フィーチャを形成する別の材料に変換して、複数のスペーサを形成するステップであって、前記キャップ層は前記上表面における反応を禁止し、前記別の材料に変換された前記材料の一部は、前記一時的なプレースホルダの上に固相反応物からなる共形の層をプランケット堆積することによって、前記側壁を前記固相反応物と反応させるべく前記複数の一時的なプレースホルダの側壁を化学種と選択的に反応させるステップを含み、且つ、前記固相反応物が金属を含み、前記別の材料が金属シリサイドを含むものであり、さらに

未変換の一時的な材料を選択的に除去するステップと、

前記複数のスペーサによって画定されたマスク・パターンを介して前記基板を処理するステップとを含む、半導体処理方法。

【請求項 5】

前記金属が、チタン、タンタル、ハフニウム、およびニッケルからなる群から選択される、請求項 4 に記載の方法。

【請求項 6】

前記複数の一時的なプレースホルダを形成するステップが、

基板の上の選択的に画定可能な層内にパターンを画定するステップと、

前記パターンを前記選択的に画定可能な層から、前記一時的な材料で形成された下にある層に転写するステップとを含む、請求項 1 に記載の方法。

【請求項 7】

前記パターンを画定するステップが、フォトリソグラフィを実施するステップを含む、請求項 6 に記載の方法。

【請求項 8】

前記一時的な材料がシリコンを含む、請求項 1 に記載の方法。

【請求項 9】

前記別の材料がポリマーを含む、請求項 1 に記載の方法。

【請求項 10】

集積回路のある領域内にマンドレルを設けるステップと、

前記マンドレルの上に固相反応物を共形で形成する材料の層をプランケット堆積させるステップと、

前記固相反応物は金属からなり、前記マンドレルと前記固相反応物の側面を反応させて、前記マンドレルの側面に金属シリサイドからなる他の材料を形成するステップと、

前記他の材料の層を等方的にエッチングして、前記マンドレルの側面に露出された、金属シリサイドからなるスペーサを残すステップと、

前記スペーサによって形成されたスペーサパターンを下にあるハードマスク層に転写するステップと、

前記スペーサパターンを前記ハードマスク層から基板に転写するステップと、を含む、集積回路を製作する方法。

【請求項 11】

前記金属はチタンであり、前記金属シリサイドはチタン・シリサイドである、請求項 1 に記載の方法。

【請求項 12】

前記マンドレルを前記スペーサに対して選択的に除去するステップをさらに含む、請求項 10 に記載の方法。

【請求項 13】

10

20

30

40

50

前記スペーサがサブリソグラフィ・フィーチャである、請求項 10 に記載の方法。

【請求項 14】

前記スペーサの側面に追加スペーサ材料の層を堆積させるステップと、

前記追加スペーサ材料の層を異方的にエッチングして、前記スペーサの側壁上に追加スペーサを形成するステップと、

前記追加スペーサの間の前記スペーサを選択的に除去して、自立追加スペーサのパターンを残すステップとをさらに含む、請求項 10 に記載の方法。

【請求項 15】

部分的に製作された集積回路の上にある中間マスク・パターンであって、

マンドレル材料で形成され、間隔をおいて配置された複数のマンドレルと、

10

前記複数のマンドレルそれぞれの上部表面に重なるキャップ層と、

各キャップ層の上にあるプリスペーサ材料からなるブランケット堆積層と、

前記複数のマンドレルそれぞれの側面上にスペーサを形成し、該スペーサが前記プリスペーサ材料と前記マンドレル材料の組合せから成り、前記プリスペーサ材料が、隣接するスペーサの間に延び、前記プリスペーサ材料が固相反応物を含み、また該固相反応物が金属を含み、前記スペーサが金属シリサイドを含む、中間マスク・パターン。

【請求項 16】

前記キャップ層が酸化シリコンまたは窒化シリコンを含む、請求項 15 に記載の中間マスク・パターン。

【請求項 17】

20

前記マンドレルがシリコンを含む、請求項 15 に記載の中間マスク・パターン。

【請求項 18】

前記スペーサがサブリソグラフィ・フィーチャである、請求項 15 に記載の中間マスク・パターン。

【請求項 19】

前記上部表面の幅が約 80 nm 未満である、請求項 15 に記載の中間マスク・パターン。

【請求項 20】

前記スペーサが約 50 nm 未満で分離される、請求項 19 に記載の中間マスク・パターン。

30

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本出願は次のものに関連する。2004年9月2日出願の A batch evらの「ピッチ増倍を用いる集積回路製作方法 (Method for Integrated Circuit Fabrication Using Pitch Multiplication)」という名称の米国特許出願第 10/934778 号、および 2005 年 3 月 15 日出願の Tran らの「フォトリソグラフィ・フィーチャに比べてピッチ縮小されたパターン (Pitch Reduced Patterns Relative To Photolithography Features)」という名称の米国仮特許出願第 60/662323 号。

40

【0002】

本発明は、一般には集積回路製作に関し、より詳細にはマスキング技術に関する。

【背景技術】

【0003】

携帯性、計算能力、メモリ容量およびエネルギー効率の向上に対する要求を含む、多くの要因の結果として、集積回路は継続的により高密度にされている。集積回路を形成する構成要素フィーチャのサイズ、たとえば電気デバイスや相互接続線のサイズは、この小形化を促進するために常に縮小されている。

50

## 【0004】

フィーチャ・サイズを縮小する傾向は、たとえば、ダイナミック・ランダム・アクセス・メモリ (D R A M ) 、フラッシュ・メモリ、スタティック・ランダム・アクセス・メモリ (S R A M ) 、強誘電体メモリなどのメモリ回路またはメモリ・デバイスにおいて明らかである。これらのメモリ・デバイスは一般に、メモリ・セルと呼ばれる数百万の同じ回路素子を含む。従来のD R A M などでの、キャパシタをベースとするメモリ・セルは一般に、2つの電気デバイス、すなわち蓄積キャパシタおよびアクセス電界効果トランジスタからなる。各メモリ・セルは、1ビット (2進数) のデータを記憶できるアドレス可能場所である。ビットは、トランジスタを介してセルに書き込むことができ、キャパシタ内の電荷を感知することによって読み出すことができる。一部のメモリ技術では、記憶デバイスとしてもスイッチとしても機能することができる素子 (たとえば、銀ドープされたカルコゲナイトガラスを使用するデンドリティック (d e n d r i t i c ) メモリ) を使用し、一部の不揮発性メモリでは、セルごとのスイッチを必要としない (たとえば磁気抵抗R A M ) 。一般的には、メモリを構成する電気デバイスのサイズと、メモリ・セルにアクセスする導電線のサイズとを縮小することによって、メモリ・デバイスをより小さくすることができる。加えて、より多くのメモリ・セルをメモリ・デバイス内の所与の領域上に収めることによって、記憶容量を増大させることができる。

10

## 【0005】

フィーチャ・サイズが継続的に縮小すると、フィーチャを形成するために用いられる技術に対する要望がますます大きくなる。たとえば、導電線などのフィーチャをパターニングするためにフォトリソグラフィが一般に使用される。そのパターンが、アレイの形に繰り返しフィーチャを含む場合には、これらのフィーチャのサイズを表すのにピッチの概念を用いることができる。ピッチは、2つの隣り合うフィーチャ内の同一の点間の距離として定義される。これらのフィーチャは、一般には各隣接フィーチャの間の空所によって画定され、この空所は絶縁物などの材料で充填される。その結果ピッチは、フィーチャの幅と、隣接したフィーチャからそのフィーチャを分離する、フィーチャの片側の空所の幅との合計と見ることができる。しかし、光学装置類や光または照射の波長などの要因により、フォトリソグラフィ技術にはそれぞれ最少ピッチがあり、それ未満には、特定のフォトリソグラフィ技術によりフィーチャを確実に形成することができない。したがって、フォトリソグラフィ技術の最少ピッチは、継続的なフィーチャ・サイズ縮小に対する障害になる。

20

## 【0006】

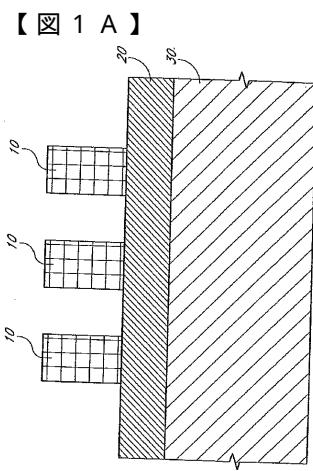

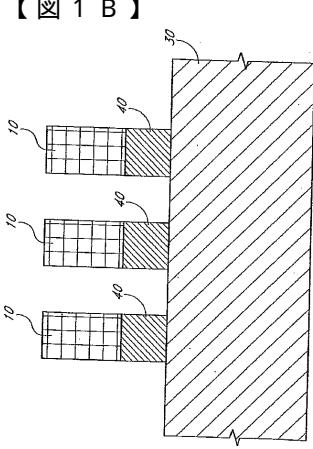

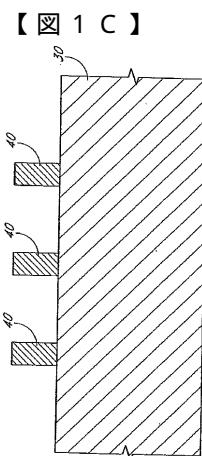

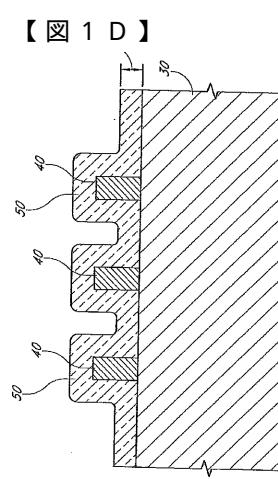

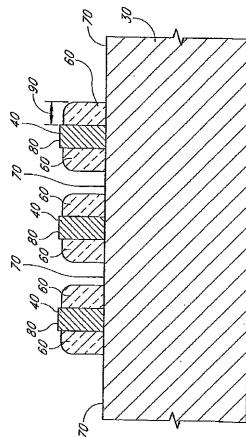

「ピッチ倍増 (p i t c h d o u b l i n g ) 」または「ピッチ増大 (p i t c h m u l t i p l i c a t i o n ) 」は、フォトリソグラフィ技術の可能性をその最小ピッチ以上に拡張する1つの方法である。1つのピッチ倍増法が図1 A ~ 1 F に示されており、またLowreyらの米国特許第5 3 2 8 8 1 0号に記載されている。同文献の開示全体を参照により本明細書に組み込む。図1 A を参照すると、線1 0 のパターンがフォトリソグラフィでフォトレジスト層として形成されており、これは消耗材料の層2 0 の上にあり、層2 0 は基板3 0 の上にある。次に、図1 B に示されたように、エッチング (好ましくは異方性エッチング) を用いてパターンを層2 0 に転写し、それによってプレースホルダ、すなわちマンドレル4 0 を形成する。フォトレジスト線1 0 を剥ぎ取り、マンドレル4 0 を等方的にエッチングして、図1 C に示されたように各隣接マンドレル4 0 の間の距離を増すことができる。図1 D に示されたように、スペーサ材料の層5 0 を引き続きマンドレル4 0 の上に堆積させる。次に、スペーサ6 0 、すなわち別の材料の側壁から延びる材料、または最初はそこから延びて形成された材料をマンドレル4 0 の側面に形成する。このスペーサ形成は、スペーサ・エッチングを実施することによって、すなわち、図1 E に示されるように、水平面7 0 からスペーサ材料を選択的、指向的にエッチングすることによって実現することができる。次に、残っているマンドレル4 0 を除去し、それによって後にスペーサ6 0 だけを基板の上に残す。図1 F に示されたように、各スペーサはともにパターニング用のマスクの働きをする。したがって、前には所与のピッチに1つのフィ

30

40

50

ーチャおよび1つの空所を画定するパターンが含まれていたところに、今では同じ幅に2つのフィーチャおよび2つの空所が含まれており、たとえばスペーサ60によって空所が画定されている。その結果、あるフォトリソグラフィ技術で可能な最少フィーチャ・サイズが効果的に縮小される。

#### 【0007】

上記の例では、ピッチが実際には半分になるが、このピッチの縮小は慣例的にピッチ「倍増」、またはより一般的にピッチ「増大」と呼ばれている。すなわち慣例的に、ある一定の率でのピッチの「増大」とは、実はその率でピッチを縮小することを意味する。本明細書では、慣例的な用語はそのままとする。

#### 【発明の開示】

10

#### 【発明が解決しようとする課題】

#### 【0008】

エッティング加工では、ある表面の異なる部分を異なる速度で除去することがあることを理解されたい。たとえば、材料40のトリム・エッティングは、エッティング速度の局部的差異を引き起こしうる温度の局部的差異のために、基板全体にわたって変化する速度でマンドレル40の側壁をエッティングすることがある。その場合、これらの不均一性が、側壁上に形成されるスペーサ60に移転されて最終的に、スペーサ60を使用して基板30内にパターニングされるフィーチャの不均一性につながる可能性がある。

#### 【0009】

さらに、マンドレル40を形成するために使用される材料には、一般に様々な処理ステップとの適合性がなければならない。たとえばこの材料は、一般には、適切な選択的等方性エッティングが（トリム・エッティングを実施するために）利用可能な材料であり、また様々なパターン形成ステップおよびパターン転写ステップにおいて（たとえば、上にあるレジストからパターンを転写するために）適切な選択的異方性エッティングが利用可能な材料である。次に、マンドレル40の材料は、後で堆積させる材料、たとえばスペーサ材料の選択を制限することがある。というのは、後で堆積させる材料の堆積条件が、一般にはマンドレル40に不利に影響を及ぼしてはならないからである。適合性のあるエッティング、および堆積させる材料に対する他の要件に加えて、等方性エッティングの要件は、ピッチ倍で使用される材料の選択を制限し、それによって処理許容度を限定することがある。

#### 【0010】

20

したがって、ピッチ増大の可能性を拡張する方法が必要とされている。

#### 【課題を解決するための手段】

#### 【0011】

本発明の一態様によれば、1つの半導体処理（または加工）方法が提供される。この方法は、基板の上に一時的なフィーチャを設けることを含む。一時的なフィーチャは、第1の材料を含む。第1の材料は化学種と反応して、反応の生成物を含むマスク・フィーチャを第1の材料と化学種の間に形成する。未反応の第1の材料は、その後選択的に除去される。

#### 【0012】

本発明の別の態様によれば、1つの半導体処理方法が提供される。この方法は、一時的な材料で形成された複数の一時的なプレースホルダ（p l a c e h o l d e r）を基板の上のある領域全体にわたって形成することを含む。一時的なプレースホルダは空所によって分離される。一時的な材料の一部は、別の材料に変換されて複数のスペーサを形成する。この別の材料は、複数のマスク・フィーチャを形成する。未変換の一時的な材料は選択的に除去される。基板は、複数のスペーサによって画定されたマスク・パターンを介して処理される。

#### 【0013】

本発明の別の態様によれば、繰り返しフィーチャのアレイを集積回路内に形成する方法が提供される。この方法は、複数のレジスト・フィーチャを基板の上のレジスト層内にリソグラフィで画定してパターンを形成することを含む。レジスト・フィーチャはそれぞれ

40

50

、幅がリソグラフィで画定されている。パターンは、レジスト層の下のマンドレル材料の層に転写されて、基板のあるレベルに複数のマンドレルが形成される。マンドレルはそれぞれ、幅がレジスト・フィーチャの幅とほぼ等しい。パターンを転写した後にマンドレルをエッティングしないで、複数のスペーサがマンドレルのレベルに形成される。スペーサの間の距離は、マンドレルの幅より小さくなる。スペーサによって画定されたパターンは基板に転写されて、繰り返しフィーチャのアレイが形成される。

【0014】

本発明のさらに別の態様によれば、集積回路を製作する方法が提供される。この方法は、マンドレルを集積回路のある領域内に設けることを含む。ある材料の層がマンドレルの上に堆積される。この材料の層は等方的にエッティングされて、露出スペーサがマンドレルの側面に残る。

10

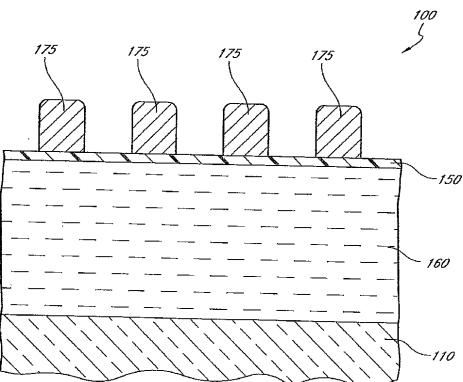

【0015】

本発明の別の態様によれば、部分的に製作された集積回路の上に重なる中間マスク・パターンが設けられる。マスク・パターンは、間隔を置いて配置された複数のマンドレルを含み、このマンドレルはそれぞれ、その上面に重なるキャップ層を有する。各キャップ層の上にプリスペーサ材料の層が重なる。部分的に製作された集積回路はさらに、それぞれのマンドレルの側面にスペーサを含む。スペーサは、プリスペーサ材料とマンドレル材料の組合せを含む。プリスペーサ材料はまた、隣接するスペーサの間に延びる。

【0016】

本発明は、発明を実施するための最良の形態、および添付の図面を参照すれば理解がより深まるであろう。これらは本発明を例示するものであり、限定するものではない。

20

【発明を実施するための最良の形態】

【0017】

本発明の好ましい実施形態では、マスキング工程において、スペーサなどのマスク・フィーチャが、マンドレルなどの一時的なフィーチャとの反応によって形成される。好ましくは、スペーサはマンドレルの側面に形成され、マンドレルのトリム・エッティングが不要である。マンドレルは、好ましくは少なくとも他の1つの材料または化学種と反応を起こして、反応の生成物であるスペーサ材料を含むスペーサを形成する。キャップ層が、好ましくはマンドレルの上部水平面を覆って形成されて、その面での反応を抑止する。したがって反応は、好ましくはマンドレルの側面で起こり、側壁マンドレル材料をスペーサ材料に変換する。次に、未反応マンドレル材料が好ましくは除去されて、自立スペーサのパターンが残る。好ましくはスペーサは、スペーサ・エッティングを用いないで、すなわちスペーサ材料を水平面から選択的に除去する指向性エッティングを実施しないで形成される。マンドレル材料を除去した後、自立スペーサのパターンは、下にある基板を続いて加工するためのマスク内で使用することができる。

30

【0018】

マンドレル材料のスペーサ材料への変換は、たとえば酸化、窒化、シリサイド化、および重合を含む様々な処理によって実施することができる。たとえば、ある材料の層をマンドレルの側面に(たとえばマンドレルの上に共形プランケット堆積を実施することによって)形成し、たとえばアニールを実施することによってマンドレルをその材料の層と反応させる。別の実施形態では、マンドレルを1つまたは複数のガス状反応物にさらしてスペーサ材料を作ることができ、あるいはマンドレルをエネルギー(たとえば光)または他の作用物(たとえば触媒)にさらして、さらされたマンドレル材料の側壁をたとえば重合する、または架橋することにより、さらされたマンドレル材料を別の材料に変換することができる。

40

【0019】

有利なことに、マンドレルの部分をスペーサ材料に変換することによってスペーサが形成されるので、マンドレルのトリミングが不要である。各スペーサは、マンドレル中に延びて形成され、したがってスペーサがマンドレルの側壁上に形成された場合よりも相互により近接して作製することができる。スペーサ形成反応の程度は、各スペーサの厚さにも

50

、それらの間の間隔にも影響を及ぼしうる。有利なことに、このスペーサ分離は、典型的なピッチ増倍工程でマンドレル・トリム・エッティングを実施した後に得られる分離と同様とすることができる。さらに、トリム・エッティングが不要であるので、マンドレルの材料の選択は、トリム・エッティングとの適合性がある材料に限定されない。加えて、有利なことにスペーサ・エッティングを回避することもできる。スペーサ・エッティングではスペーサの上部の縁部に丸みをつけることがあることを理解されたい。このような丸みをつけることは、それがたとえばスペーサのアスペクト比を実際上低減させ、かつ／またはスペーサの下にあるいずれかの層へのエッティング液または他の材料の塗布中に、エッティング液または他の材料の不均一な分布を助長するので、望ましくないことがある。有利なことに、好みしい実施形態により形成されたスペーサは、より一様な四角い形状を有することができる。さらに、スペーサ・エッティングはより侵攻的であり、下にある材料を、好みしい実施形態における未反応材料の除去を超える程度にまで浸食することもある。

#### 【0020】

ここで図を参照する。図では、同じ数字が全体を通して同じ部分を指す。図は必ずしも原寸に比例して示されていないことを理解されたい。

#### 【0021】

最初に、諸材料の一連の層が、基板の上でのスペーサの形成を可能にするように形成される。

#### 【0022】

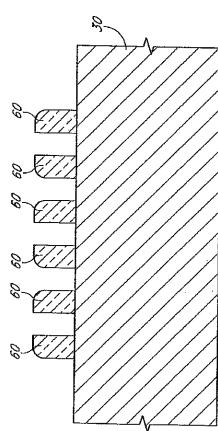

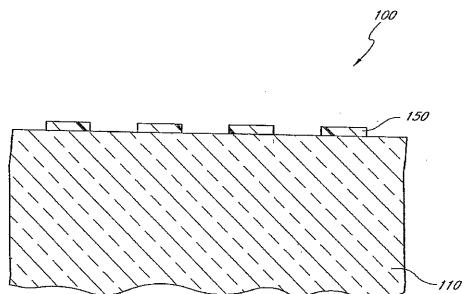

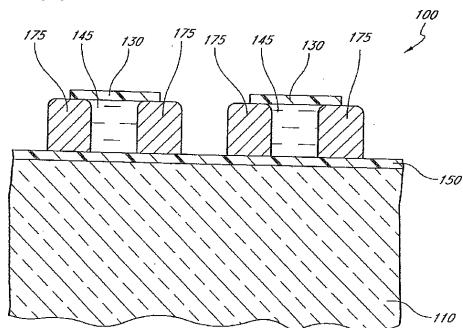

図2は、部分的に形成された集積回路100の断面側面図である。好みしい実施形態を用いてどんな集積回路も形成することができるが、好みしい実施形態は、特に有利には電気デバイスの繰り返しパターンすなわちアレイを有するデバイスの形成に適用され、このデバイスには、DRAM、相変化RAM、プログラム可能導体（PCRAM）、ROM、またはNANDフラッシュ・メモリを含むフラッシュ・メモリなど、揮発性および不揮発性メモリ・デバイス用のメモリ・セル・アレイが含まれ、あるいは論理アレイまたはゲート・アレイを有する集積回路が含まれる。たとえば論理アレイは、メモリ・アレイと類似のコア・アレイと、サポート論理回路を伴う周辺部とを有する利用者書き込み可能ゲート・アレイ（FPGA）でありうる。したがって集積回路100は、たとえばメモリ・チップまたはプロセッサとすることができる、これらは論理アレイも埋込みメモリも含むことができ、あるいは論理回路またはゲート・アレイを有する他の任意の集積回路を含むこともできる。

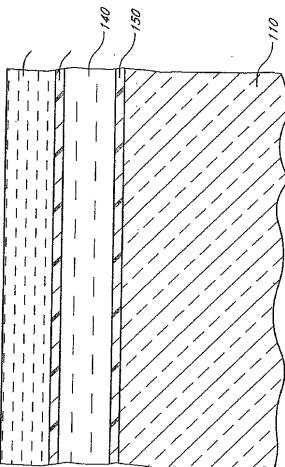

#### 【0023】

引き続いて図2を参照すると、様々なマスキング層120～150が、好みしくは基板110の上に設けられている。基板160はシリコン・ウェハ、あるいはウェハの上にある材料からなる任意の構造または層でよいことを理解されたい。たとえば基板100は、絶縁膜を含むことができる。

#### 【0024】

以下で論じるように、層120～150をエッティングして、基板110をパターニングするためのマスクを形成する。層120～150の材料は、好みしくは、本明細書で論じる様々なパターン形成ステップおよびパターン転写ステップに関する化学反応条件および処理条件についての考察に基づいて選択される。最上部の選択的に画定可能な層120と基板110の間の層が好みしくは、選択的に画定可能な層120から得られたパターンを基板110に転写するように機能するので、選択的に画定可能な層120と基板110の間の層130～150は、好みしくは、以下で説明するように、それらを様々な段階で他の露出材料に対して選択的にエッティングできるように選択される。材料は、それに対するエッティング速度が周囲の材料よりも少なくとも5倍大きく、好みしくは約10倍大きく、より好みしくは約20倍大きく、最も好みしくは約40倍大きい場合に、選択的、すなわち選別的に（preferentially）エッティングされるとみなされることを理解されたい。基板110の上にある層120～150の目的が、よりよく画定されたパターンをその基板110内に形成できるようにすることなので、他の適切な材料、化学反応、

10

20

30

40

50

および／または処理条件が用いられる場合には、1つまたは複数の層120～150を省略または置換することが可能であることを理解されたい。たとえば、層120と130の間に反射防止膜が、そのような層の分解能向上特性が望ましい一部の実施形態では形成されることがある。以下でさらに論じる別の実施形態では、付加的なマスキング層を層150と基板110の間に追加して、基板110と比べて改善されたエッチング選択性を有するマスクを形成することができる。任意選択で、適切なエッチング化学反応が利用可能である場合には、層150を省略し、スペーサ175(図10)をマスクとして使用して、たとえばどんな介在材料も用いずに基板をパターニングすることができる。本明細書で論じる様々な層の例示的な材料には、酸化シリコン、窒化シリコン、シリコン、アモルファス・カーボン、誘電体反射防止膜(DARC、シリコンが多い窒化酸化シリコン)、および有機の底部反射防止膜(BARC)が含まれ、応用例に応じて、これらの材料それぞれを他の少なくとも2つまたは3つの材料に対して選択的にエッチングすることができる。10

#### 【0025】

様々な層について適切な材料を選択することに加えて、層120～150の厚さは、好みしくは、本明細書で論じるエッチング化学反応および処理条件との適合性に応じて選択される。たとえば、上にある層を選択的にエッチングすることによって上の層から下の層へパターンを転写する場合、材料が両方の層からある程度除去される。上の層は、パターンを転写する間にそれが消耗しないように十分に厚いことが好みしい。

#### 【0026】

選択的に画定可能な層120は、好みしくはハード・マスク層130の上にあり、以下で論じるように、このハード・マスク層は、好みしくは反応性薬剤からマンドレル145(図5)を保護するためのキャップ層として機能することができる。層130はマンドレル層140の上にあり、層140は第2のハード・マスク層またはエッチ・ストップ層150の上にあり、層150は、マスクを介して処理(たとえばエッチング)されるべき基板110の上にある。選択的に画定可能な層120は、好みしくは光画定可能であり、たとえば当技術分野で周知の任意のフォトレジストを含むフォトレジストで形成される。たとえばこのフォトレジストは、157nm、193nm、248nm、または365nmの波長の装置、193nm波長の液浸装置、極紫外線の装置(13.7nm波長の装置を含む)、または電子ビーム・リソグラフィ装置と適合する任意のフォトレジストでよい。加えて、マスクレス・リソグラフィ、またはマスクレス・フォトリソグラフィを使用して、選択的に画定可能な層120を画定することもできる。好みしいフォトレジスト材料の例には、フッ化アルゴン(ArF)感受性フォトレジスト、すなわちArF光源とともに使用するのに適したフォトレジストと、フッ化クリプトン(KrF)感受性フォトレジスト、すなわちKrF光源とともに使用するのに適したフォトレジストとが含まれる。ArFフォトレジストは、好みしくは比較的短波長の、たとえば193nmの光を利用するフォトリソグラフィ装置とともに使用される。KrFフォトレジストは、好みしくは248nmの装置など、より長い波長のフォトリソグラフィ装置とともに使用される。別の実施形態では、層120およびそれに続くどのレジスト層も、ナノインプリント・リソグラフィによってパターニングできるレジスト、たとえばレジストをパターニングする型または機械的力を用いることによってパターニングできるレジストで形成することができる。30

#### 【0027】

ハード・マスク層130の材料は、好みしくは無機材料を含む。例示的な材料には、それだけには限らないが、酸化シリコンおよび窒化シリコンが含まれる。図示の実施形態では、ハード・マスク層130は窒化シリコンを含む。マンドレル層140は、好みしくは、スペーサ材料に変換できる材料で形成され、このスペーサ材料はまた、未反応マンドレル材料、ハード・マスク層130、およびスペーサ材料の下にある材料と比べて、良好なエッチング選択性を示す。図示の実施形態では、マンドレル材料はシリコンである。

#### 【0028】

第2のハード・マスク層150の材料は、好みしくはスペーサ175(図11)、および下にある基板110に使用される材料に基づいて選択される。層150が、基板11040

50

をエッティングするためのマスクとして使用される場合には、層150は、好ましくは、マスクを介して実施されるべき基板110の所望の処理（たとえばエッティング、ドーピング、酸化など）に対して耐性があり、スペーサ175（図11）に対して選択的にエッティングできる材料で形成される。たとえば、第2のハード・マスク層150は窒化物、たとえば窒化シリコンとし、あるいは酸化物、たとえば酸化シリコンとすることができる。図示の実施形態では、第2のハード・マスク層150は酸化シリコンを含む。

#### 【0029】

本明細書で論じる様々な層は、当技術分野で周知の様々な方法によって形成することができる。たとえば、スピノン・オン・コーティング処理を用いて光画定可能層、B A R C、およびスピノン・オン誘電体酸化物層を形成することができる。スパッタリング、化学気相成長（C V D）、および／または原子層成長（A L D）などの様々な気相成長法を用いて、様々なハード・マスク層、キャップ層、およびマンドレル層を形成することができる。加えて、一部の層、たとえば層140に反応を起こさせて別の層を形成することもできる。たとえば、シリコン前駆体と窒素前駆体を使用して窒化シリコン層を堆積させるのではなく、窒素前駆体を使用してシリコン層140の上部表面を窒化し、窒化シリコン層を形成することができ、この窒化シリコン層は、（以下の議論を考慮すればよりよく理解されるように）ハード・マスク層、または続いて製作されるマンドレルのキャップ層として機能することができる。

#### 【0030】

所望の層のスタックを形成したので、次にスペーサのパターンを形成する。

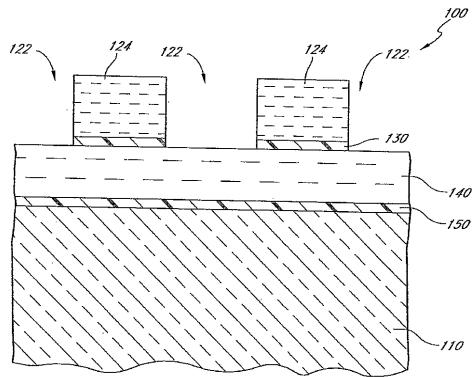

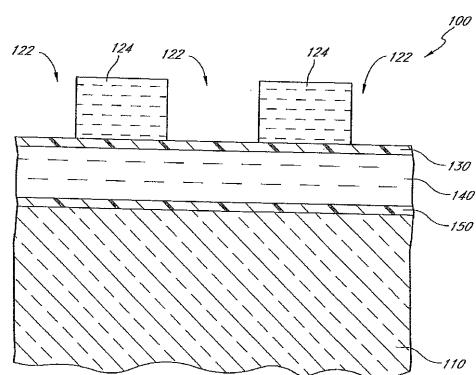

#### 【0031】

図3を参照すると、空所すなわちトレンチ122を含むパターンが光画定可能層120内に形成されており、トレンチ122は、光画定可能材料で形成されたフィーチャ124によって区切られている。トレンチ122は、たとえば、層120がレチクルを介して放射にさらされ現像される、248 nmまたは193 nmの光を用いたフォトリソグラフィによって形成することができる。残りの光画定された材料は、現像された後に、図示の線124（断面のみを示す）などのマスク・フィーチャを形成する。有利には、線124は、約120 nm以下または約80 nm以下の幅で形成されて、ピッチが約100 nm以下のスペーサを形成することができる。

#### 【0032】

図4を参照すると、フォトレジスト・フィーチャ124およびトレンチ122のパターンが、ハード・マスク層130に転写されている。この転写は、好ましくはC F<sub>4</sub>、C F<sub>4</sub> / H<sub>2</sub>、C F<sub>4</sub> / O<sub>2</sub>、S F<sub>6</sub>またはN F<sub>3</sub>を含むプラズマを使用するエッティングなど、異方性エッティングを用いて実施されるが、ハード・マスク層130が十分に薄くて、転写パターン内の空所の望ましくない拡大なしに貫通してエッティングされる場合には、湿式（等方性）エッティングもまた適していることがある。

#### 【0033】

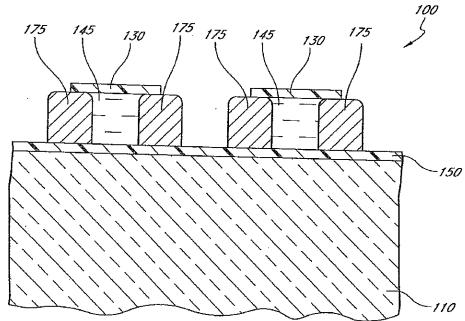

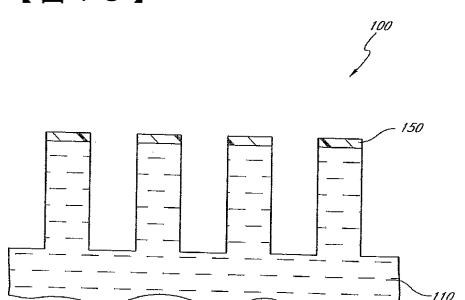

図5を参照すると、光画定可能層120内およびハード・マスク層130内のパターンがマンドレル層140に転写されて、マンドレル145、すなわち一時的なプレースホルダを形成している。この転写は、好ましくは、たとえばH B r / H C 1またはC H C 1<sub>3</sub> / C 1<sub>2</sub>を含むプラズマを使用する異方性エッティングを用いて実施される。マンドレル145の幅は、好ましくは線124の幅とほぼ同等である。たとえばマンドレル145は、好ましくは幅が約120 nm以下、または約80 nm以下である。

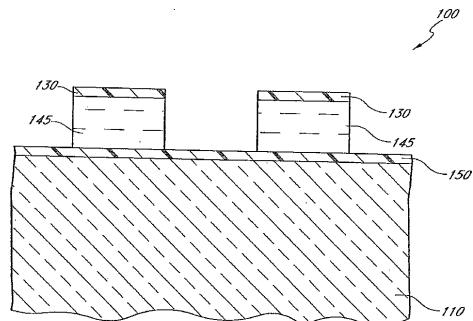

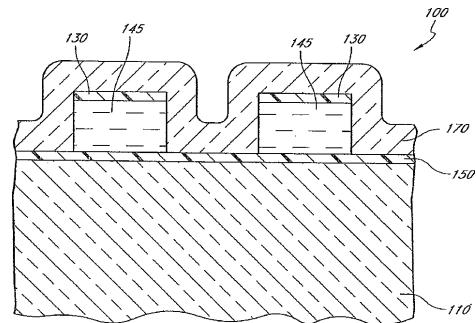

#### 【0034】

図6を参照すると、プリスペーサ材料、すなわち反応を起こしてスペーサを形成する材料が、マンドレル145の側壁上に堆積されている。好ましくはプリスペーサ材料は、層170としてマンドレル145上にブランケット堆積させる。図示の実施形態では、層170を形成するプリスペーサ材料はチタンである。この堆積は、当技術分野で周知の様々な方法、たとえばC V DおよびA L Dによって実施することができる。層170の厚さは、以下で論じるように、好ましくはマンドレル145とのプリスペーサ材料170の反応

10

20

30

40

50

の後に、所望の幅のスペーサ 175 (図 7) を形成するのに十分な材料を供給するように選択される。

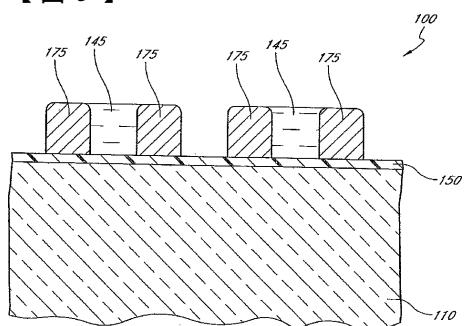

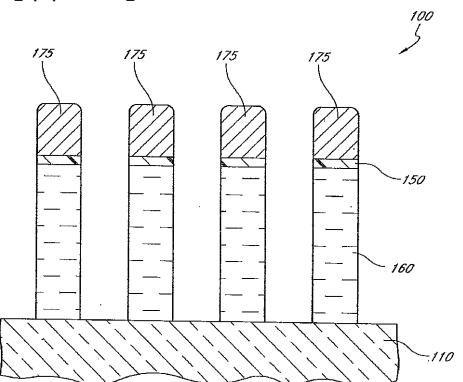

【0035】

図 7 を参照すると、次にチタン・プリスペーサ層 170 とマンドレル 145 が互いに反応して、図示の実施形態ではチタン・シリサイドからなるスペーサ 175 を形成する。マンドレル 145 が好ましくはキャップ層を備えて、マンドレル 145 の側壁に反応が集中することを理解されたい。図示の実施形態では、ハード・マスク層 130 が好ましくはキャップ層として機能して、チタン・プリスペーサ層 170 とマンドレル 145 の上部表面との接触を防止することによって、マンドレル 145 の上部が反応を起こさないようにする。別の実施形態では、キャップ層は、ハード・マスク層 130 が存在しようとしまいと、たとえばマンドレル 145 の上部での堆積または反応によって別個に形成することができる。

【0036】

好ましくは、層 170 およびマンドレル 145 は高温にさらし、たとえばアニールにかけて自己整合シリサイド化反応を起こさせる。たとえば、部分的に製作された集積回路 100 を約 550 ~ 800 、より好ましくは約 650 ~ 680 の温度で、約 5 ~ 90 秒間、より好ましくは約 20 ~ 60 秒間、急速熱処理 ( RTP ) にかけることができる。

【0037】

マンドレル 145 のシリコンと反応する層 170 の中の反応の程度、およびチタンの量は、温度およびアニール継続時間と関係することを理解されたい。したがって、有利なことに、温度およびアニール継続時間などの反応条件は、スペーサ 175 の幅、および / または所望の分離距離に応じて選択することができる。たとえば、マンドレル 145 と層 170 は、離隔距離が約 80 nm 以下、より好ましくは 50 nm 以下になるまで反応させることができる。

【0038】

別の実施形態では、チタン層 170 の、マンドレル 145 の側壁のところの部分は、好ましくは完全に反応させる。層 170 の厚さが、反応によって形成されるスペーサ 175 の最大幅の限界を与えるので、有利なことにこれらの部分を完全に反応させると、アニールのためのより大きな処理窓と、スペーサ 175 の幅の良好な制御とが可能になる。たとえば、層 170 を所与の幅まで堆積させることによって、アニールの継続時間および / または温度が、その幅のスペーサ 175 を形成するのに必要な継続時間および / または温度を超えることを可能にできる。というのは、層 170 の材料の量 ( たとえば幅 ) は一般に、スペーサ 175 の成長を、特に層 170 の方向に制限するからである。

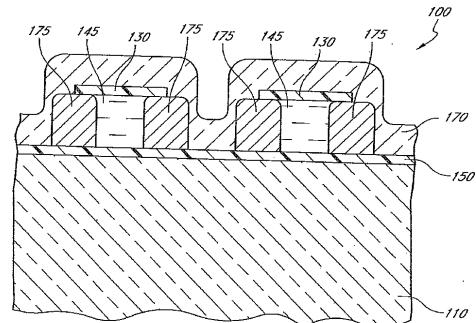

【0039】

図 8 を参照すると、層 170 内の未反応チタンが選択的に除去されて、マンドレル 145 の側面にスペーサ 175 が残っている。この除去は、湿式または乾式エッチングによって実施することができる。湿式エッチングには、コストが低く、スペーサ 175 の構造の損傷が少ないという利点がありうる。適切なエッチングの一例は、H<sub>2</sub>O、H<sub>2</sub>O<sub>2</sub> および NH<sub>4</sub>OH を含む湿式エッチングである。好ましくは、スペーサ 175 はサブリソグラフィであり、すなわちある限界寸法たとえば限界幅を有し、この寸法は、スペーサ・パターンを形成するために用いられるフォトリソグラフィ技術の分解能限界未満であり、この場合は、層 120 をパターニングするために用いられるフォトリソグラフィ技術の分解能限界未満である。

【0040】

図 9 を参照すると、窒化シリコン・キャップ層 130 が、スペーサ 175 に対して選択的に除去されている。この除去は、乾式エッチング、または、たとえば熱リン酸を使用する湿式エッチングを用いて実施することができる。

【0041】

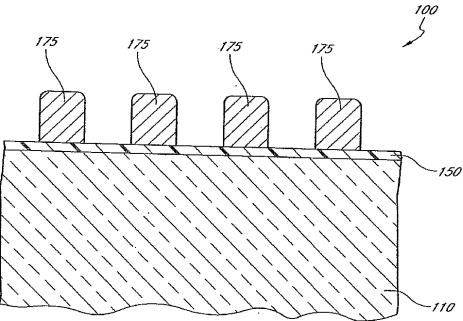

次に、図 10 に示されるように、未反応マンドレル材料を選択的に除去して、自立スペーサ 175 のパターンを形成する。この除去には乾式または湿式エッチングを用いること

10

20

30

40

50

ができる。例示的な湿式エッティングはHF、HNO<sub>3</sub>、およびH<sub>2</sub>Oを含む。ハード・マスク層150をスペーサ175の下に設けて基板110を保護し、基板110内の材料を意図せずに除去することなく未反応マンドレル材料を除去できるようにする。したがって、有利なことに、フォトリソグラフィによって最初に形成されたフォトレジスト線124および空所122(図3)のほぼ半分のピッチで、スペーサ175を形成することができる。フォトレジスト線124のピッチが約200nmであった場合には、ピッチが約100nm以下のスペーサ175を形成することができる。

#### 【0042】

スペーサ175がマンドレル145の側壁に形成されるので、スペーサ175は、一般にマンドレル145の輪郭に追従し、したがって通常では閉ループを形成することを理解されたい。ピッチ増倍パターンを使用して導電線などのフィーチャを形成した場合に、追加の処理ステップを用いて切り離し、または別な方法でこれらのループの端部でのパターンの転写を防止することができ、その結果各ループは、個別の2本の非接続線を形成するようになることを理解されたい。これはたとえば、ループの上に保護材料の層を堆積させ、その保護層をパターニングして、保持されるべき線の部分の周囲に保護マスクを形成し、次にループの非保護部分、たとえば端部をエッティング除去することによって実施することができる。ループの端部を切り離す適切な方法が、2004年8月31日出願のT ranらの米国特許出願第10/931771号に開示されている。同文献の開示全体を参照により本明細書に組み込む。

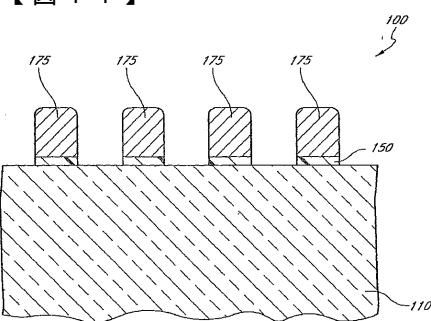

#### 【0043】

図11を参照すると、スペーサ除去中に基板110を保護することに加えて、ハード・マスク層150は、好ましくは、スペーサ175のパターンが基板110に転写されるべき場合に、基板110に対する改善されたエッティング選択性を可能にする。上記で論じたように、図示の実施形態では、ハード・マスク層150は酸化シリコンで形成される。スペーサ175のパターンは、好ましくは異方性エッティング、たとえばCHF<sub>3</sub>、CF<sub>4</sub>、またはC<sub>2</sub>F<sub>6</sub>プラズマを含むエッティングを用いて層150に転写される。ハード・マスク層150が十分に薄い場合には、湿式エッティングを用いてもパターン転写を最小のアンダーカッティングで実施できることを理解されたい。

#### 【0044】

次に、ハード・マスク層150を用いて、下にある基板110をパターニングすることができる。

#### 【0045】

スペーサ175は、基板110をエッティングする前後に除去できることを理解されたい。好ましくは、ハード・マスク層150の材料が基板110の材料に対して良好なエッティング選択性を示す場合、たとえばスペーサ175がハード・マスク層150を補助する必要がない場合には、パターンが基板110に転写される前にスペーサ175を除去することができる。このスペーサ除去は、たとえば希釈したHF湿式エッティング液を用いて実施することができる。有利なことに、スペーサ除去により、処理がそれを通して行われる空所、たとえばエッティング液が基板110に到達するためにそこを通って移動しなければならない空所のアスペクト比が低減するとともに、特にスペーサ175が非常に高く、かつ/または細い場合に、スペーサ175の崩壊または変形によってパターンの変化が生じる可能性が最小限になる。すなわち、図11に示されたように、スペーサ175を除去して基板のエッティングを容易にすることができます。

#### 【0046】

図13を参照すると、たとえば基板110の材料に対して選択性的なエッティング液、または複数のエッティング液の組合せを使用して、ハード・マスク層150内のパターンを基板110に転写することができる。マスクを介して基板をエッティングすることに加えて、別の実施形態では、層150内のマスクを介した他の種類の処理もまた可能である。他の処理の非限定的な例には、注入、拡散ドーピング、リフトオフ・パターン化堆積、酸化、窒化などが含まれる。

10

20

30

40

50

## 【0047】

別の実施形態の図14を参照すると、特に基板110が、エッチングするのが困難である場合、またはマスクを介した長期の処理が望ましい場合には、マスキング材料からなる1つまたは複数の追加介在層をスペーサ175と基板110の間に形成することができる。たとえば、同時係属の2005年3月15日出願のTransらの「フォトリソグラフィ・フィーチャに比べてピッチ縮小されたパターン」という名称の米国仮特許出願第60/662323号、弁理士整理番号MICRON.316PR(Micron参照番号2004-1130.00/US)で論じられているように、追加層160を設けることができる。同文献の開示全体を参照により本明細書に組み込む。

## 【0048】

図14を続けて参照すると、層150は、好ましくはスペーサ175、層160、およびマンドレル145(図9)に対して良好なエッチング選択性を有する材料を含む。層160は、好ましくはアモルファス・カーボンで形成され、これは有利なことに、基板110中のシリコン材料を除去するための多くのエッチング化学反応に対して耐性がある。

## 【0049】

図15を参照すると、スペーサ175によって画定されたパターンを層160に転写することができ、この層160は次に、基板110をパターニングするための1次マスク160として機能する。有利なことに、別の実施形態では、アモルファス・カーボンをエッチングする場合の極度の選択性の可用度により、スペーサ175の除去の後に、パターニングされたハード・マスク層150を用いてパターンを層150から層160に転写することができ、その結果、パターンを1次マスキング層160に転写するために使用されるマスクが、より小さくより均一なアスペクト比のフィーチャを有するようになる。別の実施形態では、他の適切な材料とともに、ハード・マスク層150はそれ自体、アモルファス・カーボンで形成することができる。

## 【0050】

さらに別の実施形態では、基板110とスペーサ175の間に介在層、たとえばハード・マスク層150がないことがある。このような場合、特に基板に対して良好なエッチング選択性をスペーサ材料が有する場合には、どんな介在ハード・マスク層もなしで、スペーサ175のパターンによって基板110を処理することができる。

## 【0051】

好ましい実施形態によるスペーサの形成には多数の利点があることを理解されたい。たとえば、マンドレル・トリム・エッチングが不要であり、そのようなトリム・エッチングによって生じる可能性のあるスペーサの不均一性をなくすことができる。その代わりに、プリスペーサ層170の堆積、およびスペーサ形成反応、たとえばアニールの程度が、スペーサ幅もスペーサ間隔も決定する。さらに、トリム・エッチングが実施されないので、トリム・エッチングとの適合性に関する要件が取り除かれるに伴い、マンドレルを形成するのに使用できる材料の範囲が拡大されることもある。したがって、処理の融通性を向上させることができる。加えて、指向性スペーサ・エッチングが不要であり、それによって効果が、対称形の肩を有するスペーサ175を形成し、下にある層の損傷を最少にすることに關してもたらされる。

## 【0052】

好ましい実施形態では、有利なことにスペーサ・エッチングが不要であるが、いくつかの構成では、スペーサ・エッチングをプリスペーサ材料の層170に実施して、プリスペーサ材料で形成されるスペーサ・フィーチャを、プリスペーサ材料とマンドレル材料を反応させる前にマンドレルの側面に形成することができる。これらのスペーサ・フィーチャは、次にマンドレル材料と反応させて、マンドレル材料、および下にある材料に対して選択的にエッチング可能なスペーサ175を形成することができる。

## 【0053】

図示の実施形態における特定の処理ステップおよび材料に関して論じたが、様々な改変形態が可能であることもまた理解されたい。たとえば、チタン・シリサイドに加え様々な

10

20

30

40

50

シリサイドを使用してスペーサを形成することができる。金属シリサイドを作る他の金属の例には、タンタル、ハフニウム、およびニッケルが含まれる。上記の例では、これらの金属をマンドレルの上に堆積させ、アニールして金属シリサイドを作る。他の構成では、材料の組合せを逆にすることができる。たとえば、マンドレル 145 を金属とすることができる、このマンドレルの上にシリコン層を堆積させて金属シリサイドを作る。加えて、マンドレル 145 はアモルファス・カーボンを含むことができ、層 170 は、アモルファス・カーボンと反応しやすい他の様々な材料を含むことができる。たとえば層 170 は、シリコンを含んで炭化ケイ素のスペーサ 175 を形成することができ、あるいは金属を含んで炭化金属を作ることもできる。

## 【0054】

10

図 16 を参照すると、堆積金属層がマンドレルと反応する固体反応としてのスペーサ 175 の形成が示されているが、スペーサ 175 は、固体反応物の間の反応以外に様々な過程で形成できることを理解されたい。いくつかの実施形態では、マンドレル 145 をガス状反応物と反応させて、シリサイドではないスペーサを含め、スペーサを形成することができ。たとえば、シリコン・マンドレル 145 のシリサイド化は、マンドレル 145 をガス状金属反応物（たとえば TiC<sub>14</sub>、WF<sub>6</sub> など）にさらすことによって実施することができ、あるいは金属マンドレル 145 の気相シリサイド化は、マンドレル 145 をガス状シリコン反応物（たとえば SiH<sub>4</sub>）にさらすことによって実施することができ。加えて、シリコン・マンドレルを酸化剤にさらすことによって酸化シリコン・スペーサを形成することができ、あるいは、キャップ層が窒化シリコン以外の適切な材料である場合には、反応しやすい窒素種にシリコン・マンドレルをさらすことによって窒化シリコンを作ることができ。別の実施形態では、マンドレル 145 は、アモルファス・カーボン、レジスト、または炭素をドープした材料などの炭素種と作ることができ（たとえば米国特許第 6515355 号に開示されているもの。同文献の開示全体を参照により本明細書に組み込む）、この炭素種はポリマーに変換され、または架橋されてスペーサ 175 を形成する。この変換は、エネルギー（たとえば光）または他の作用物（たとえば触媒）にさらすことによって引き起こすことができる。スペーサ 175 が形成された後、図 9～15 に関する以上で論じたように、部分的に製作された集積回路 100 を処理することができる。

## 【0055】

30

加えて、図および説明を簡単にするために以上では 2 つの材料を論じたが、2つよりも多い材料を反応させて所望のスペーサ材料、たとえば気相反応物との反応によって作られる SiO<sub>x</sub>N<sub>y</sub> 作ることができる。これらの追加材料は、たとえば、プリスペーサ材料の複数の堆積層を互いの上に形成し、次にアニールを実施することによって反応させることができ、かつ／またはプリスペーサ材料の単一の層を堆積させ、アニールを実施してその層をマンドレル材料と反応させ、次にプリスペーサ材料の 1 つまたは複数の追加層を堆積させ、次にアニールを実施することによって反応させることができる。別の実施形態では、追加材料は、プリスペーサ材料の堆積層の代替物として、またはそれに追加してガス状反応物として導入することができる。

## 【0056】

40

さらに、マンドレルの形成においてはトリム・エッチングを実施しないことが好ましいが、必要に応じてトリム・エッチングを実施することも可能である。たとえば、現像された後でフォトレジスト層をトリム・エッチングにかけることができ、かつ／またはマンドレルをトリム・エッチングにかけることもできる。このようなトリム・エッチングは、互いに非常に近接したスペーサを形成するのに有用なことがある。

## 【0057】

加えて、マンドレルを形成した後にキャップ層を形成することができる。たとえば、マンドレルの上部は、たとえばイオン注入と類似の処理で方向性をもって加えられた反応物と反応して、キャップ層を形成することができる。

## 【0058】

50

さらに、スペーサはマンドレルのキャップ層なしでも形成される。たとえば、金属層をマンドレルの上に共形に堆積させて、マンドレルの上部も側面も反応させることができる。次に、たとえば方向性乾式エッティングによって、あるいはマンドレル間の何も入っていない空所を充填材で充填し、化学的機械的研磨を実施して上部を除去し、次に充填材を除去することによって、反応を起こした上部を除去することができる。

#### 【0059】

スペーサと同様に、本明細書で論じた他の様々な層および部分にも他の材料を使用できることもまた理解されたい。好ましくは、使用されてよい他のどんな材料も、以上で論じたように、選択的エッティング・ステップ中にさらされる材料に対して適切なエッティング選択性を示す。さらに基板110は、異なる材料、たとえば異なる材料の層を含み、あるいは基板の横方向の異なる領域内に異なる材料を含むことができる。スペーサによって画定されたパターンをそのような基板に転写するために、単一の化学反応では異なる材料すべてをエッティングするのに不十分な場合には一連の異なる化学反応を用いて、好ましくは乾式エッティング化学反応を用いて、これらの異なる材料を貫通して連続的にエッティングすることができる。

#### 【0060】

用いられる1つまたは複数の化学反応にもよるが、上にあるスペーサおよびハード・マスク層をエッティングできることもまた理解されたい。場合によっては、優れたエッティング選択性を得るために追加マスキング層160(図14)を使用することが好ましい。1次マスク層160にアモルファス・カーボンを使用すると、有利なことに従来のエッティング化学反応に対して、特にシリコン含有材料をエッティングするために用いられるものに対して優れた耐性を示す。したがって1次マスク層160は、複数の基板層を貫通してエッティングするためのマスク、あるいは高アスペクト比のトレーニングを形成するためのマスクとして効果的に使用することができる。

#### 【0061】

また、本明細書で論じたマスクを使用して、それだけには限らないが、高密度の繰り返しパターンが望ましい、特にメモリ・アレイおよび論理アレイ用の導電相互接続線、ランディング・パッド、およびキャパシタやトランジスタなどの様々な電気デバイスの部品を含む様々な集積回路フィーチャ、あるいはフラット・パネル・ディスプレイを形成することができる。そのようなものとして、図を簡単にするために規則的な間隔および規則的な幅がある線として示されているが、マスクは間隔が可変のフィーチャを有することもできる。また、単一のレベルに形成されたスペーサが図示されているが、別の実施形態では、スペーサを上下の複数のレベルに形成してから単一のレベルに統合して、マスク・パターンを形成することができる。

#### 【0062】

加えて、フォトレジスト層120内に形成されたパターンのピッチを、倍増を超えるものにもできる。たとえば、追加スペーサをスペーサ175の周りに形成し、次にスペーサ175を除去し、次いで前にはスペーサ175の周りにあったスペーサの周りにスペーサを形成するなど、スペーサ175を従来のピッチ増大法のマンドレルとして使用することによって、パターンをさらにピッチ増大することができる。

#### 【0063】

好ましい実施形態をまた、集積回路製作工程の全体を通して複数回使用して、上下の複数のレベルにフィーチャを形成することもでき、これらのフィーチャは上下に隣接することもあり、隣接しないで上下に分離されることもある。このような場合には、パターンングされるべき個々のレベルそれが基板110を構成する。加えて、好ましい実施形態のいくつかは、別の好ましい実施形態と組み合わせて、または当技術分野で周知の他のマスキング法と組み合わせて、同じ基板110の異なる領域上に、または上下異なるレベルにフィーチャを形成することができる。

#### 【0064】

したがって、このような、また他の様々な省略、追加、および改変を本発明の範囲から

10

20

30

40

50

逸脱することなく上述の方法および構成に加えられてよいことが、当業者には理解されよう。このようなすべての改変および変更は、添付の特許請求の範囲に定義される本発明の範囲内に入るものである。

【図面の簡単な説明】

【0065】

【図1A】従来技術のピッチ倍増法による、導電線を形成するための一連のマスキング・パターンの概略断面側面図である。

【図1B】従来技術のピッチ倍増法による、導電線を形成するための一連のマスキング・パターンの概略断面側面図である。

【図1C】従来技術のピッチ倍増法による、導電線を形成するための一連のマスキング・パターンの概略断面側面図である。 10

【図1D】従来技術のピッチ倍増法による、導電線を形成するための一連のマスキング・パターンの概略断面側面図である。

【図1E】従来技術のピッチ倍増法による、導電線を形成するための一連のマスキング・パターンの概略断面側面図である。

【図1F】従来技術のピッチ倍増法による、導電線を形成するための一連のマスキング・パターンの概略断面側面図である。

【図2】本発明の好ましい実施形態による、部分的に形成された集積回路の概略断面側面図である。

【図3】本発明の好ましい実施形態による、図2の部分的に形成された集積回路の、フォトトレジスト層内にフィーチャを形成した後の概略断面側面図である。 20

【図4】本発明の好ましい実施形態による、図3の部分的に形成された集積回路の、ハード・マスク層を貫通してエッチングした後の概略断面側面図である。

【図5】本発明の好ましい実施形態による、図4の部分的に形成された集積回路の、ハード・マスク層からマンドレル材料の層にパターンを転写してマンドレルのパターンを一時的な層内に形成した後の概略断面側面図である。

【図6】本発明の好ましい実施形態による、図5の部分的に形成された集積回路の、プリスペーサ材料の層を堆積させた後の概略断面側面図である。

【図7】本発明の好ましい実施形態による、図6の部分的に形成された集積回路の、プリスペーサの層に反応を起こさせてスペーサをマンドレル側壁上に形成した後の概略断面側面図である。 30

【図8】本発明の好ましい実施形態による、図7の部分的に形成された集積回路の、未反応プリスペーサ材料を選択的に除去した後の概略断面側面図である。

【図9】本発明の好ましい実施形態による、図8の部分的に形成された集積回路の、ハード・マスク層を除去した後の概略断面側面図である。

【図10】本発明の好ましい実施形態による、図9の部分的に形成された集積回路の、未反応マンドレル材料を選択的に除去した後の概略断面側面図である。

【図11】本発明の好ましい実施形態による、図10の部分的に形成された集積回路の、スペーサによって形成されたパターンをスペーサの下にあるハード・マスク層に転写した後の概略断面側面図である。 40

【図12】本発明の好ましい実施形態による、図11の部分的に形成された集積回路の、スペーサを除去した後の概略断面側面図である。

【図13】本発明の好ましい実施形態による、図12の部分的に形成された集積回路の、マスキング層内のパターンを下にある基板に転写した後の概略断面側面図である。

【図14】本発明の好ましい実施形態による、スペーサと基板の間に配置されたハード・マスク層および追加のマスキング層を有する、部分的に形成された集積回路の概略断面側面図である。

【図15】本発明の好ましい実施形態による、図14の部分的に形成された集積回路の、スペーサ・パターンを追加のマスキング層中および下にある基板中に転写した後の概略断面側面図である。 50

【図1A】本発明の好ましい実施形態による、図5の部分的に形成された集積回路の、気相反応によってスペーサをマンドレルの側面に形成した後の概略断面側面図である。

FIG. 1A

(PRIOR ART)

FIG. 1B

(PRIOR ART)

FIG. 1C

(PRIOR ART)

FIG. 1D

(PRIOR ART)

&lt;div[](./img/1E.png)

FIG. 1E

(PRIOR ART)

【図1F】

FIG. 1F

(PRIOR ART)

【 四 4 】

FIG. 4

【 図 5 】

FIG. 5

【 义 2 】

FIG. 2

【図3】

FIG. 3

【図6】

FIG. 6

【図7】

FIG. 7

【図 8】

FIG. 8

【図 10】

FIG. 10

【図 9】

FIG. 9

【図 11】

FIG. 11

【図 12】

FIG. 12

【図 13】

FIG. 13

【図 14】

FIG. 14

【図 15】

FIG. 15

【図16】

FIG. 16

---

フロントページの続き

(72)発明者 プラル, キルク, ディ.

アメリカ合衆国, アイダホ州 83706, ボイズ, サウス ハーモニー ストリート 2548

審査官 秋田 将行

(56)参考文献 特開昭52-048983(JP, A)

特開昭57-048237(JP, A)

特開昭59-107518(JP, A)

特開昭62-232127(JP, A)

特開昭64-035916(JP, A)

特開平01-119028(JP, A)

特開平01-124219(JP, A)

特開平07-307333(JP, A)

特開平07-326562(JP, A)

特開平10-150027(JP, A)

特開2003-077922(JP, A)

特開2003-249437(JP, A)

米国特許第05328810(US, A)

米国特許第05795830(US, A)

米国特許第06383952(US, B1)

米国特許第06534243(US, B1)

米国特許第06638441(US, B1)

米国特許第06667237(US, B1)

米国特許第06875703(US, B1)

米国特許第06893972(US, B1)

米国特許出願公開第2002/0043690(US, A1)

米国特許出願公開第2003/0006410(US, A1)

米国特許出願公開第2003/0157436(US, A1)

Yang-Kyu Choi, Joon Sung Lee, Ji Zhu, Gabor A. Somorjai, Luke P. Lee, Jeffrey Bokor, S

ublithographic nanofabrication technology for nanocatalysts and DNA chips, Journal of

Vacuum Science and Technology B, 2003年12月 9日, Vol.21, No.6, pp.2951-2955

寺井護、豊島利之、熊田輝彦、長江偉, 半導体用ホールパターン縮小技術 - ArF 対応 R E L

A C S - , 電気材料技術雑誌, 2004年 9月 25日, Vol.13, No.1, pp.82-86

(58)調査した分野(Int.Cl., DB名)

H01L 21/027

H01L 21/3065

G03F 7/20 -7/24

G03F 9/00 -9/02