(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294629

(P2005-294629A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

**H01L 29/786**

**G02F 1/1345**

**G02F 1/1368**

**G02F 1/167**

**G09F 9/30**

F 1

H01L 29/78 623A

G02F 1/1345

G02F 1/1368

G02F 1/167

G09F 9/30 338

テーマコード(参考)

2H092

5C094

5F110

審査請求 未請求 請求項の数 8 O L (全 10 頁)

(21) 出願番号

特願2004-109095 (P2004-109095)

(22) 出願日

平成16年4月1日 (2004.4.1)

(71) 出願人

000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人

100123788

弁理士 宮崎 昭夫

(74) 代理人

100106297

弁理士 伊藤 克博

(74) 代理人

100106138

弁理士 石橋 政幸

(72) 発明者

吉永 秀樹

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者

森 秀雄

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】表示装置の製造方法

## (57) 【要約】

【課題】 表示装置の製造工程、特に表示装置用マトリクスアレイ基板の製造工程における静電破壊に対する耐性をより向上させることができる表示装置の製造方法を提供する。

【解決手段】 表示装置は、少なくとも一表面上に絶縁層101が形成された導電性の金属基板100と、金属基板100の絶縁層101が形成されている面側にマトリクス状に形成されたゲート配線106およびソース配線111と、金属基板100の上記面側にさらに形成された、ゲート配線106に接続されたゲートショート配線105およびソース配線111に接続されたソースショート配線104とを備えたマトリクスアレイ基板を有している。この表示装置の製造方法は、少なくともマトリクスアレイ基板の製造工程において、金属基板100とゲートショート配線105およびソースショート配線104とをコンタクトホール102, 103を介して電気的に接続する工程を有している。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

少なくとも一表面上に絶縁層が形成された導電性基板と、該導電性基板の前記絶縁層が形成されている面側にマトリクス状に形成された走査電極および情報電極と、前記導電性基板の前記面側にさらに形成された、前記走査電極に接続された第1の配線および前記情報電極に接続された第2の配線と、を備えた表示装置用マトリクスアレイ基板の製造方法において、

少なくとも前記マトリクスアレイ基板の製造工程において、前記導電性基板と少なくとも前記第1または第2の配線のいずれかとを電気的に接続する工程を有していることを特徴とする表示装置用マトリクスアレイ基板の製造方法。

**【請求項 2】**

前記第1の配線同士を接続する第1のショート配線と、前記第2の配線同士を接続する第2のショート配線との少なくとも一方を形成する工程を含んでいる、請求項1に記載の表示装置用マトリクスアレイ基板の製造方法。

**【請求項 3】**

前記絶縁層にコンタクトホールを形成し、該コンタクトホールを介して前記第1のおよび第2のショート配線の少なくとも一方と前記導電性基板とを電気的に接続する工程を含んでいる、請求項2に記載の表示装置用マトリクスアレイ基板の製造方法。

**【請求項 4】**

前記第1のショート配線と前記第2のショート配線との両方を形成する工程を含み、前記第1のショート配線と前記第2のショート配線とを、互いに交差するクロス部を形成するように互いに異なる導電層に形成し、前記クロス部において互いに電気的に接続する工程を含んでいる、請求項2または3に記載の表示装置用マトリクスアレイ基板の製造方法。

**【請求項 5】**

導電性基板上に複数のアクティブ素子が構成されてなるマトリクスアレイ基板を有する表示装置の製造方法であって、

前記導電性基板の一表面上に第1の絶縁層を形成する工程と、

該第1の絶縁層に第1のコンタクトホールを形成する工程と、

前記第1の絶縁層上および前記第1のコンタクトホール内に第1の導電層を形成し、該第1の導電層をパターンニングすることによって、第1の配線を形成する工程と、

該第1の配線の上に第2の絶縁層および半導体層を形成する工程と、

前記第2の絶縁層および前記半導体層に第2のコンタクトホールを形成する工程と、

少なくとも該第2のコンタクトホールを含む領域に第2の導電層を形成し、該第2の導電層をパターンニングすることによって第2の配線を形成し、前記導電性基板と前記第1の配線と前記第2の配線とを前記第1および第2のコンタクトホールを介して電気的に接続する工程と、

を含むことを特徴とする表示装置の製造方法。

**【請求項 6】**

前記第2の配線上にパッシベーション層を形成する工程と、

該パッシベーション層に第3のコンタクトホールを形成し、少なくとも該第3のコンタクトホールを含む領域に第3の導電層を形成し、該第3の導電層をパターンニングして画素電極を形成する工程と、

前記導電性基板上の構成の最上面に白色散乱層を形成する工程と、

該白色散乱層上に第3の絶縁層を形成する工程と、

該第3の絶縁層上に金属層、第1のフォトレジスト層、および第2のフォトレジスト層を順に形成した後に、該金属層、該第1のフォトレジスト層、および該第2のフォトレジスト層をパターンニングして隔壁を形成する工程と、

前記隔壁で仕切られた空間内に、絶縁性液体中に電気泳動粒子を分散させてなる分散液を充填する工程と、

第2の基板を前記隔壁に接触させた状態に固定する工程と、

前記導電性基板と前記第1の配線と前記第2の配線との電気的な接続を切断する工程と

、

をさらに含んでいる、請求項5に記載の表示装置の製造方法。

【請求項7】

前記導電性基板と前記第1の配線と前記第2の配線との電気的な接続を切断する工程は、前記マトリクスアレイ基板の少なくとも前記第1および第2のコンタクトホールを含む領域を前記マトリクスアレイ基板から除去する工程からなる、請求項6に記載の表示装置の製造方法。

【請求項8】

請求項5～7のいずれか1項に記載された表示装置の製造方法を用いて製造された表示装置を有する情報機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置の製造方法等に関し、さらに詳しくは、絶縁層又は絶縁体により絶縁された導電性基板上にマトリクス配線を有する表示装置の製造方法等に関する。

【背景技術】

【0002】

薄膜トランジスタ（以下、TFT（Thin Film Transistor）と記す。）は、液晶表示素子やエレクトロルミネッセント（EL）表示素子、または電気泳動表示装置用のアクティブマトリクス基板として用いられ、例えば電気泳動表示装置においては、各画素において泳動液内に封入されたトナーに電界をかけるために制御電極電位を制御するための素子として用いられる。

【0003】

各画素に設けたTFTに用いられる半導体膜には非晶質のシリコン薄膜（a-Si薄膜）や多結晶のシリコン薄膜（polycrystalline-Si薄膜）がある。

【0004】

従来、これらの技術では、例えば表示装置である液晶ディスプレイ用途ではガラスを基板として用いることが多い、それゆえ、使用用途にもよるが、表示装置は耐衝撃性や柔軟性が十分ではない。

【0005】

また、昨今では、上述したような電気泳動表示装置を用いた、従来では実現し得なかつた、薄く、丈夫で、かつ紙のようなしなやかさを備えたディスプレイの開発も盛んに行われている。それに伴い、表示素子を駆動するためのTFTバックプレーンを、従来のガラス基板ではなく、割れにくく丈夫な、可撓性のある薄い金属板やプラスチック板の上に形成することが考えられている。

【0006】

ところで、導電性材料の一つであるステンレス鋼（以下、SUS（Steel Use Stainless）と記す。）からなる導電性基板を用いた場合は、現在多く用いられているガラス基板や、現在検討が進められているプラスチック板やプラスチックフィルムを基板とした場合と大きく異なる点がある。すなわち、導電性基板を前述したような表示装置用の基板として用いる場合には、少なくとも導電性基板の機能面を絶縁加工する必要がある。導電性基板の機能面を絶縁加工する技術は、例えば特許文献1に開示されている。

【0007】

導電性基板を絶縁加工する方法としては、酸化膜を成膜するなどの幾つかの方法が考えられる。その他にも、例えば、窒化シリコン層を導電性基板上に成膜し、その上に走査電極または情報電極を形成する方法が考えられる。

【0008】

このような、アクティブマトリクス基板の製造工程において、例えば液晶ディスプレイ

10

20

30

40

50

(LCD) 用途であればラビング工程、その他のデバイスにおいても製造工程中に静電気が生じ、マトリクス配線間の絶縁破壊や、アクティブ素子を有する場合は電気的特性の変化が生じることがある。そのため、従来では、各配線、各素子、または各配線と各素子とを同電位にするために、それらをいわゆるショートリングに電気的に接続した状態で製造が行われている。

【特許文献1】特開平9-179106号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかしながら、導電性基板を用いた場合に、従来のように、各配線や各素子電極の電位を同電位とするためにそれらをショートリングに電気的に接続した状態で製造を行ったとしても、基板絶縁層をはさむ導電性基板と各電極または各素子電極等との間に依然として電位差が生じ、基板絶縁層が部分的に破壊されてしまう場合がある。その結果、基板配線間にショートが生じたり、アクティブ素子を有する場合においてはそのアクティブ素子の電気的特性が変化したりするなどの問題が依然として生じてしまうこととなる。

【0010】

そこで本発明は、表示装置の製造工程、特に表示装置用マトリクスアレイ基板の製造工程における静電破壊に対する耐性をより向上させることができる表示装置の製造方法等を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記目的を達成するため、本発明の表示装置用マトリクスアレイ基板の製造方法は、少なくとも一表面上に絶縁層が形成された導電性基板と、該導電性基板の前記絶縁層が形成されている面側にマトリクス状に形成された走査電極および情報電極と、前記導電性基板の前記面側にさらに形成された、前記走査電極に接続された第1の配線および前記情報電極に接続された第2の配線と、を備えた表示装置用マトリクスアレイ基板の製造方法において、少なくとも前記マトリクスアレイ基板の製造工程において、前記導電性基板と少なくとも前記第1または第2の配線のいずれかとを電気的に接続する工程を有していることを特徴とする。

【0012】

また、本発明に係る表示装置の製造方法は、導電性基板上に複数のアクティブ素子が構成されてなるマトリクスアレイ基板を有する表示装置の製造方法であって、前記導電性基板の一表面上に第1の絶縁層を形成する工程と、該第1の絶縁層に第1のコンタクトホールを形成する工程と、前記第1の絶縁層上および前記第1のコンタクトホール内に第1の導電層を形成し、該第1の導電層をパターニングすることによって、第1の配線を形成する工程と、該第1の配線の上に第2の絶縁層および半導体層を形成する工程と、前記第2の絶縁層および前記半導体層に第2のコンタクトホールを形成する工程と、少なくとも該第2のコンタクトホールを含む領域に第2の導電層を形成し、該第2の導電層をパターニングすることによって第2の配線を形成し、前記導電性基板と前記第1の配線と前記第2の配線とを前記第1および第2のコンタクトホールを介して電気的に接続する工程と、を含むことを特徴とする。

【0013】

上記のような本発明の製造方法によれば、マトリクスアレイ基板の製造工程中、導電性基板と第1の配線と第2の配線とが第1および第2のコンタクトホールを介して電気的に接続されるので、それらが略同電位に保たれる。そのため、例えば、製造工程中に生じる静電気によって静電破壊が生じて、導電性基板と第1または第2の配線との間でショートが生じるようなことがないので、製造工程における静電破壊に対する耐性をより向上させることが可能になる。

【0014】

また、本発明の情報機器は、上記本発明の表示装置の製造方法を用いて製造された表示

10

20

30

40

50

装置を有する。

【発明の効果】

【0015】

以上説明したように、本発明の製造方法によれば、表示装置の製造工程、特に表示装置用マトリクスアレイ基板の製造工程における静電破壊に対する耐性をより向上させることができる。

【発明を実施するための最良の形態】

【0016】

次に、本発明の実施形態について図面を参照して説明する。

【0017】

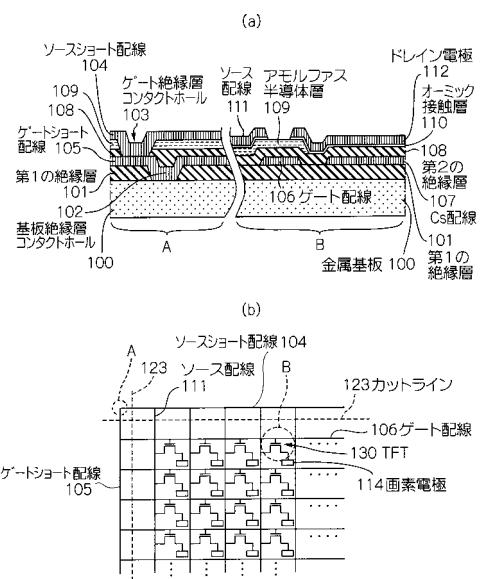

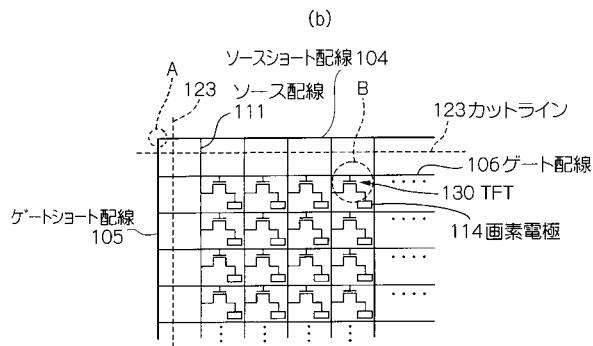

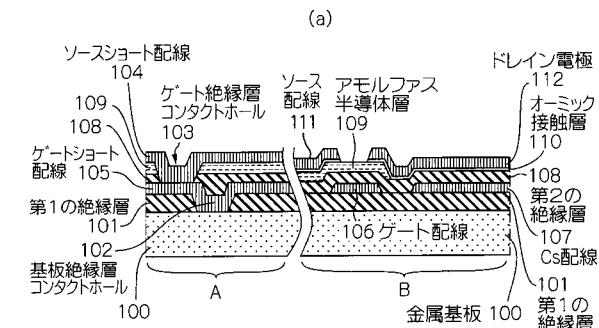

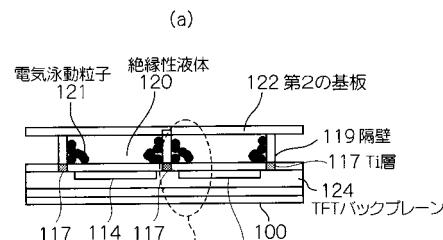

図1(a)は本発明の一実施形態に係る表示装置におけるマトリクスアレイ基板の一部の断面を模式的に示す図であり、図1(b)は本実施形態の表示装置における300行×250列のTFTアクティブマトリクスアレイ基板の一部分を示す模式図である。なお、図1(a)のA部分は図1(b)におけるA領域の断面を示し、図1(a)のB部分は図1(b)におけるB領域の断面を示している。

【0018】

図1(a)に示すように、本実施形態に係る表示装置は、導電性基板としての薄型の金属基板100上に、例えばプラズマCVD(Chemical Vapor Deposition)法により形成されたSiN等からなる第1の絶縁層101が設けられている。金属基板100のうち、いわゆるショートリングが形成され製造工程後に切り離される領域(図1(b)のカットライン123の外側の領域)に設けられている第1の絶縁層101には、第1のコンタクトホールである基板絶縁層コンタクトホール102が形成されている。この基板絶縁層コンタクトホール102は、例えばエッチングプロセスによって形成される。

【0019】

第1の絶縁層101の上には、表示装置が例えばボトムゲート構成のTFTを備えた構成の場合には、走査電極としてのゲート配線106、ゲート配線106が接続された第1のショート配線としてのゲートショート配線105、およびCs(補助容量)配線107が形成されている。

【0020】

ここで、これらの配線105、106、107の形成方法について簡単に説明すると、これらの配線の材料として例えば抵抗率が比較的低いAlを用いて配線層を形成し、その後のプロセスにAlの融点を超えるようなプロセスがある場合は、その配線層の上にCr、Ta、あるいはAl-Ndをスパッタリングによって蒸着させて導電膜を形成する。続いて、その導電膜の上にレジストを塗布してこれを選択的に露光および現像し、導電膜をエッチングによって所定の形状にパターニングする。以上により、配線105、106、107が形成される。

【0021】

それらの配線105、106、107の上には第2の絶縁層108が形成され、さらにその上にはアモルファス半導体層109が形成されている。金属基板100のうち、いわゆるショートリングが形成され製造工程後に切り離される領域における第2の絶縁層108およびアモルファス半導体層109には、第2のコンタクトホールであるゲート絶縁層コンタクトホール103が形成されている。このゲート絶縁層コンタクトホール103は、例えばエッチングプロセスによって形成される。

【0022】

第2の絶縁層108上には、例えばイオン注入法によって形成された後に選択除去されたオーミック接触層110が形成されている。さらに、それらの層の上には、情報電極としてのソース配線111(図1(b)参照)、ソース配線111が接続された第2のショート配線としてのソースショート配線104、およびドレイン電極112が形成されている。

【0023】

10

20

30

40

50

第1のショート配線であるゲートショート配線105と、前記第2のショート配線ソースショート配線104とは、互いに交差するクロス部を形成するように、互いに異なる導電層に形成されている。ゲート絶縁層コンタクトホール103はそのクロス部に形成されており、これらのショート配線104, 105はそのクロス部においてゲート絶縁層コンタクトホール103を介して互いに電気的に接続されている。

#### 【0024】

なお、ゲートショート配線105とソースショート配線104はカットライン123の外側に設けられており、これらのショート配線104, 105とコンタクトホール102, 103は製造工程終了後に金属基板100から切り離される。これらショート配線104, 105および導電性基板100は、例えば、実装端子の先で電気的に接続されている

10

。

#### 【0025】

このように、本実施形態の表示装置は、導電性の薄型の金属基板100上に基板絶縁層101を形成し、続いてその上にTFTマトリクスアレイを形成したマトリクスアレイ基板を備えており、少なくともそのマトリクスアレイ基板の製造工程中は、金属基板100と各ゲート配線106と各ソース配線111とが、ショート配線104, 105およびコンタクトホール102, 103を介して互いに電気的に接続されている。なお、TFTマトリクスアレイ基板の形態で出荷する場合などは、上記の電気的な接続を保った状態で出荷すれば、製品の輸送中に生じる静電気等に対しても耐性を有することになるので好ましい。また、上述の方法でショート配線、導電性基板を接続するのが好ましいが、導電性基板とゲートショート配線、ソースショート配線の少なくとも一方とがショート配線のクロス部以外でコンタクトホールを形成して接続していてもよい。

#### 【0026】

図1(b)に示すように、本実施形態の表示装置におけるTFTマトリクスアレイ基板には、複数のゲート配線106と複数のソース配線111とがマトリクス状に配置されている。ゲート配線106とソース配線111とに囲まれた各領域には、アクティブ素子であるTFT130が設けられている。各TFT130のドレイン電極側には画素電極114が接続されている。

#### 【0027】

本実施形態の表示装置についてさらに詳細に説明する。

30

#### 【0028】

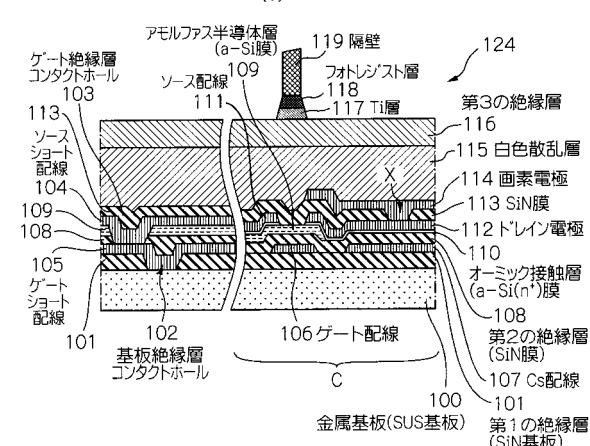

図2(a)は本発明の一実施形態に係る表示装置の一部の表示画素の断面を模式的に示す図であり、図2(b)は主に図2(a)におけるC部を拡大して示す断面図である。

#### 【0029】

図2(a)に示すように、本実施形態の表示装置は、金属基板100上に構成されたTFTバックプレーン124上の隔壁119に、第2の基板122が接合されている。隔壁119によって仕切られた各画素空間には、メモリー性を有する表示素子として、絶縁性液体120中に電気泳動粒子121を分散させてなる分散液(電気泳動表示素子)が設けられている。各画素の電気泳動表示素子は、TFTバックプレーン124上に画素ごとに設けられた画素電極114とTi層117とからなる一対の電極によって駆動される。より具体的に説明すると、本実施形態の表示装置は、画素電極114とTi層117とに正負の電圧を印加して、電気泳動粒子121を画素電極114の形成面と隔壁119の近傍との間を移動させることによって電気泳動表示素子を駆動し、表示を行う。なお、図2(a)は、電気泳動粒子121がTi層117に引き寄せられて隔壁119の近傍に移動した状態を示している。

#### 【0030】

以下に、図2を参照しながら、本実施形態の表示装置の製造工程について説明する。

(1) まず、厚さ0.2mmのSUSからなる導電性基板としての金属基板100上に、

CVD法によって、第1の絶縁層としてのSiN膜101を500nmの厚さに成膜する

40

。

50

(2) 金属基板100のうち、いわゆるショートリングが形成され製造工程後に切り離される領域(図1(b)のカットライン123の外側の領域)に設けられているSiN膜101に、ドライエッチングによって基板絶縁層コンタクトホール102を形成し、金属基板100の一部を露出させる。

(3) SiN膜101上に、Al-Ndをスパッタリングによって200nmの厚さに成膜して第1の導電層を形成し、フォトマスク(不図示)を用いてこの第1の導電層をウェットエッチングすることにより、ゲート配線106、各ゲート配線106を電気的に同電位とするためのゲートショート配線105、およびCs配線107を形成する。これと同時に、基板絶縁層コンタクトホール102を介して、ゲートショート配線105と金属基板100とを電気的に接続する。

### 【0031】

なお、本実施形態のような電気泳動表示装置はTFT130の保持駆動を行う際の補助容量を必要とするため、ゲート配線106と同じ導電層にCs(補助容量)配線107を形成している。

(4) それらの配線105, 106, 107の上に、層間絶縁膜としてSiN膜108を250nmの厚さにCVDによって成膜し、さらにその上に、アモルファス半導体層としてa-Si膜109を200nmの厚さにCVDによって成膜する。

(5) 金属基板100のうち、いわゆるショートリングが形成され、製造工程後に切り離される領域における絶縁層108およびアモルファス半導体層109に、ドライエッチングによってゲート絶縁層コンタクトホール103を形成する。

(6) 絶縁層108およびアモルファス半導体層109上の所定の領域に、オーミック接觸層として、a-Si( $n^+$ )膜110を20nmの厚さにCVDによって成膜する。

(7) オーミック接觸層110の上にAl-Ndを200nmの厚さにスパッタリングによって成膜して、第2の導電層を形成する。

(8) この第2の導電層をフォトマスク(不図示)を用いてウェットエッチングすることによって、TFT部分を含むソース配線111、ドレイン電極112、および各ソース配線111群を電気的に同電位とするために互いに電気的に接続するソースショート配線104を形成する。この段階で、ソースショート配線104とゲートショート配線105とがゲート絶縁層コンタクトホール103を介して接続され、これにより、ソースショート配線104とゲートショート配線105と金属基板100とがコンタクトホール102, 103を介して電気的に接続される。

### 【0032】

引き続いて、所定のレジストパターンを用いたドライエッチングによってTFTチャネル部のa-Si( $n^+$ )層110を除去して半導体層109の一部を露出させ、上記配線104, 111, 112および一部が露出した半導体層109の上にパッシベーション層としてのSiN膜113を300nmの厚さに成膜する。

(9) SiN膜113に、ドライエッチングによって図2(b)のX部に示すように第3のコンタクトホールを形成し、ドレイン電極112の一部を露出させる。

(10) 一部が露出したドレイン電極112およびSiN膜113の上にAl-Ndを200nmの厚さにスパッタリングによって成膜し、第3の導電層を形成する。

(11) フォトマスク(不図示)を用い、この第3の導電層をウェットエッチングによってパターニングして画素電極114を形成する。

(12) 金属基板100上の上記構成の最上面上に、TiO<sub>2</sub>を含有したアクリル樹脂を4μmの厚さに塗布し、白色散乱層115を形成する。

(13) 白色散乱層115の上にアクリル系の樹脂を1μmの厚さに成膜して、第3の絶縁層116を形成する。

(14) 第3の絶縁層116の上に、Tiを300nmの厚さに成膜して金属層としてのTi層117を形成し、さらにその上に、第1のフォトレジスト層としてカーボンを含有したフォトレジスト層118を300nmの厚さに成膜する。

(15) 次に、フォトレジスト層118の上に第2のフォトレジスト層として厚膜フォト

10

20

20

30

40

50

レジスト層を 15 μm の厚さに形成し、厚膜フォトレジスト層が画素間の隔壁 119 を構成するように、この厚膜フォトレジスト層を画素間の部分を残して現像除去する。

(16) 厚膜フォトレジスト層で形成された隔壁 119 を用いて、Ti 層 117 とフォトレジスト層 118 とをエッチングし、TFT バックプレーン 124 を形成する。

(17) 次に、パラフィン系炭化水素溶媒を主成分とする絶縁性液体 120 中に、カーボンブラックを含有したポリスチレン樹脂から成る黒色の電気泳動粒子 120 を分散させた分散液を、隔壁 119 で区画された空間内に充填し、透明な第 2 の基板 122 を隔壁 119 上に接着剤(不図示)によって固定する。

(18) 最後に、金属基板 100 をカットライン 123(図 1 (b)) で切断し、各ゲート配線 106 および各ソース配線 111 と金属基板 100 とを電気的に接続しているショートリング部を金属基板 100 から切り離す。

#### 【0033】

以上により、本実施形態の表示装置の製造工程が完了する。

#### 【0034】

上述したように、本実施形態によれば、少なくともマトリクスアレイ基板の製造工程において、ソースショート配線 104 とゲートショート配線 105 と金属基板 100 とがコンタクトホール 102, 103 を介して電気的に連通し、それらが略同電位に保たれている。そのため、製造工程中に生じる静電気によって基板絶縁層の静電破壊が生じて、例えば、金属基板 100 とゲート配線 106 との間でのショートや、金属基板 100 とソース配線 111 との間のショートが生じるようなことがないので、表示装置の製造工程における静電破壊に対する耐性をより向上させることができることになり、TFT バックプレーンを導電性基板上に構成した場合においても良好な画質の表示装置を製造することができる。

#### 【0035】

なお、本実施形態では電気泳動表示装置の TFT バックプレーンの場合について説明したが、本発明を適用できるのはこれに留まらず、例えば反射型の液晶表示装置に応用することも可能である。この場合、例えば第 2 の基板 122 に ITO (Indium Tin Oxide) 膜のような透明な導電膜を形成してコモン電極を構成し、ドレイン電極との間に液晶を挟持し、ドレイン電極 - コモン電極間に所望の電界をかけることで表示を行うことができる。

#### 【0036】

また、本実施形態ではアモルファスシリコンを用いた逆スタガー型のいわゆるボトムゲート型の構成を採用しているが、これに代えて、例えばトップゲート型の構成等を採用しても何ら問題はない。加えて、アモルファスシリコンを用いた TFT に限らず、例えば、レーザーアニールを用いたポリシリコン TFT や、単結晶 TFT の転写技術を用いても良い。

#### 【0037】

また、上記の製造方法によって製造した本実施形態の電気泳動表示装置は、薄く形成することができ、また、ある程度の折り曲げに対応できるようなフレキシブルな構成になっているため、各種の情報機器用の表示装置として好適に用いられる。例えば、紙媒体に置き換えられるような用途や、情報携帯端末 (PDA) のような情報端末の表示用ディスプレイとしても用いることができる。

#### 【産業上の利用可能性】

#### 【0038】

本発明は、薄型でフレキシブルな表示装置の製造方法、およびそのような製造方法を用いて製造された表示装置を有する情報機器に適用可能である。

#### 【図面の簡単な説明】

#### 【0039】

【図 1】図 (a) は本発明の一実施形態に係る表示装置におけるマトリクスアレイ基板の一部の断面を模式的に示す図であり、図 (b) は本実施形態の表示装置における 300 行 × 250 列の TFT アクティブマトリクスアレイ基板の一部分を示す模式図である。

10

20

30

40

50

【図2】図(a)は本発明の一実施形態に係る表示装置の一部の表示画素の断面を模式的に示す図であり、図(b)は主に図(a)におけるC部を拡大して示す断面図である。

【符号の説明】

【0040】

- |     |                      |    |

|-----|----------------------|----|

| 100 | 金属基板 (SUS基板)         | 10 |

| 101 | 第1の絶縁層 (SiN膜)        |    |

| 102 | 基板絶縁層コンタクトホール        |    |

| 103 | ゲート絶縁層コンタクトホール       |    |

| 104 | ソースショート配線            |    |

| 105 | ゲートショート配線            |    |

| 106 | ゲート配線                |    |

| 107 | Cs配線                 |    |

| 108 | 第2の絶縁層 (SiN膜)        | 20 |

| 109 | アモルファス半導体層 (a-Si膜)   |    |

| 110 | オーム接触層 (a-Si (n+) 膜) |    |

| 111 | 隔壁                   |    |

| 112 | 絶縁性液体                |    |

| 113 | 電気泳動粒子               |    |

| 114 | 第2の基板                |    |

| 115 | カットライン               |    |

| 116 | TFTパックプレーン           |    |

| 117 | TFT                  |    |

【図1】

【図2】

---

フロントページの続き

F ターム(参考) 2H092 GA64 HA06 HA12 HA18 JA24 JB21 JB79 NA14 PA01

5C094 AA42 BA03 BA43 EB10

5F110 AA22 BB01 CC07 DD01 DD14 EE03 EE04 EE06 EE14 EE44

FF03 FF29 GG02 GG13 GG15 GG24 GG44 HK06 HK09 HK16

HK21 HK33 HK34 HL06 HL23 NN01 NN02 NN24 NN27 NN72

NN73 PP03