(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-3256

(P2012-3256A)

(43) 公開日 平成24年1月5日(2012.1.5)

(51) Int.Cl.

G02F 1/1368 (2006.01)

F 1

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 未請求 請求項の数 17 O L (全 36 頁)

(21) 出願番号 特願2011-1111014 (P2011-1111014)

(22) 出願日 平成23年5月18日 (2011.5.18)

(31) 優先権主張番号 特願2010-115983 (P2010-115983)

(32) 優先日 平成22年5月20日 (2010.5.20)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 相原 大和

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

(72) 発明者 神長 正美

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

(72) 発明者 佐藤 来

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示装置および液晶表示装置の作製方法

## (57) 【要約】

【課題】反射型ゲストホスト液晶表示装置において、使用者の目に優しい紙面に近い表示が実現できることを課題の一とする。より視認性の良好で高画質な液晶表示装置を提供することを目的の一とする。

【解決手段】画素電極層(第1の電極層ともいう)である反射膜が設けられた第1の基板と、共通電極層(第2の電極層ともいう)が設けられた第2の基板とでゲストホスト液晶層を挟持する液晶表示装置において、画素電極層である反射膜が液晶層に突出し、ミクロンサイズの第1の凹凸、及び第1の凹凸上にナノサイズの第2の凹凸を形成して配置される。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

ゲストホスト液晶を挟持する一対の基板と、

前記一対の基板の一方に設けられた透光性の電極と、

前記一対の基板の他方に設けられた、第1の凹凸を有し該第1の凹凸の表面に第2の凹凸が設けられた絶縁層と、

前記絶縁層の第1の凹凸の表面に沿って形成され且つ該第2の凹凸によって表面が粗面化された画素電極層と、を有し、

前記画素電極層は、反射性を有することを特徴とする液晶表示装置。

## 【請求項 2】

請求項1において、

前記絶縁層は、感光性有機樹脂であることを特徴とする液晶表示装置。

## 【請求項 3】

請求項1において、

前記絶縁層に設けられた第1の凹凸は平面方向に1.5  $\mu\text{m}$ 以上20  $\mu\text{m}$ 以下の大きさであることを特徴とする液晶表示装置。

## 【請求項 4】

請求項1乃至3のいずれか一項において、

前記絶縁層に設けられた第1の凹凸は0.1  $\mu\text{m}$ 以上20  $\mu\text{m}$ 以下の高さであることを特徴とする液晶表示装置。

## 【請求項 5】

請求項1乃至4のいずれか一項において、

前記絶縁層に設けられた第2の凹凸は平面方向に0.1  $\mu\text{m}$ 以上1  $\mu\text{m}$ 以下の大きさであることを特徴とする液晶表示装置。

## 【請求項 6】

請求項1乃至5のいずれか一項において、

前記絶縁層に設けられた第2の凹凸は0.1  $\mu\text{m}$ 以上1  $\mu\text{m}$ 以下の高さであることを特徴とする液晶表示装置。

## 【請求項 7】

請求項1乃至6のいずれか一項において、前記絶縁層に形成される凹凸は、

第1の凹凸よりも第2の凹凸の方が小さく形成されることを特徴とする液晶表示装置。

## 【請求項 8】

請求項1乃至7のいずれか一項において、前記絶縁層にそって形成される画素電極層は、5 nm以上500 nm以下の厚さで反射性を有することを特徴とする液晶表示装置。

## 【請求項 9】

請求項1乃至8のいずれか一項において、前記ゲストホスト液晶は、二色性色素をゲスト分子として含むネマティック液晶であることを特徴とする液晶表示装置。

## 【請求項 10】

請求項1乃至9のいずれか一項において、前記第1の基板と、前記画素電極層との間にトランジスタが設けられ、

前記画素電極層は前記トランジスタと電気的に接続されていることを特徴とする液晶表示装置。

## 【請求項 11】

請求項10において、前記トランジスタは酸化物半導体層を含むことを特徴とする液晶表示装置。

## 【請求項 12】

感光性の有機樹脂を用いて、第1の凹凸を形成し、

前記第1の凹凸上にプラズマ処理にて第2の凹凸を形成し、

前記第1の凹凸、及び前記第2の凹凸上にそって反射性のある画素電極層を形成することを特徴とする液晶表示装置の作製方法。

10

20

30

40

50

**【請求項 1 3】**

請求項 1 2 において、

前記第 2 の凹凸を形成するプラズマ処理は、前記第 1 の凹凸を有する有機樹脂に酸素ガス雰囲気下にて形成することを特徴とする液晶表示装置の作製方法。

**【請求項 1 4】**

請求項 1 2 において、

前記第 1 の凹凸は、平面方向に  $1.5 \mu m$  以上  $20 \mu m$  以下の大きさで形成することを特徴とする液晶表示装置の作製方法。

**【請求項 1 5】**

請求項 1 2 または請求項 1 4 において、

前記第 1 の凹凸は、 $0.1 \mu m$  以上  $20 \mu m$  以下の高さで形成することを特徴とする液晶表示装置の作製方法。

**【請求項 1 6】**

請求項 1 2 において、

前記第 2 の凹凸は、平面方向に  $0.1 \mu m$  以上  $1 \mu m$  以下の大きさで形成することを特徴とする液晶表示装置の作製方法。

**【請求項 1 7】**

請求項 1 2 または請求項 1 6 において、

前記第 2 の凹凸は、 $0.1 \mu m$  以上  $1 \mu m$  以下の高さで形成することを特徴とする液晶表示装置の作製方法。

10

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

液晶表示装置および液晶表示装置の作製方法に関する。

**【背景技術】****【0 0 0 2】**

薄型、軽量化を図った表示装置（所謂フラットパネルディスプレイ）には液晶素子を有する液晶表示装置、自発光素子を有する発光装置、フィールドエミッഷンディスプレイ（FED）などが競合し、開発されている。

20

**【0 0 0 3】**

表示装置として、広く用いられている液晶表示装置は、偏光板やバックライトなど多くの光学部材を用いるため、材料コストの削減や、バックライトに使用される電力を低減する必要がある。

30

**【0 0 0 4】**

また、液晶表示装置は種々のモードがあり、ツイスト配向、又はスーパーツイスト配向されたネマティック液晶を用いたTNモードあるいはSTNモードが主流となっている。しかしながら、これらのモードは動作原理上一対の偏光板が必要であり、その光吸収があるため透過率が低く明るい表示画面が得られない。

**【0 0 0 5】**

また、これらのモードの他、二色性色素を利用したゲストホスト液晶も開発されている。ゲストホスト液晶を用いた表示装置は、液晶層のホスト分子に対して、二色性色素をゲスト分子として混合し、液晶に加える電圧によってホスト分子、及びゲスト分子の配列を変化させて、液晶層における光吸収率を変化させている。例えば、ゲスト分子として、棒状構造の二色性色素を用いると、二色性色素はホスト分子に対し、平行に配向する性質があるので、電界を印加してホスト分子の配向を変化させると、二色性色素の配向方向も変化する。

40

**【0 0 0 6】**

また、上記ゲストホスト液晶と反射膜、または反射板を組み合わせた反射型の液晶表示装置も開発されている。反射型の液晶表示装置は、背面光源（バックライト）を利用するこなく外光のみで表示を写し出すことができる為、低消費電力であり携帯情報端末のディ

50

スプレイなどに広く利用可能であり、実用化に向けて研究が行われている。

【0007】

この反射型のゲストホスト液晶を用いた液晶表示装置の主要な構成要素の一つとして、光を反射させるための反射膜、又は反射板が挙げられる。

【0008】

従来の反射膜では、入射光を鏡面反射するため、正面からパネルを観察した場合には、垂直入射光がそのまま垂直反射光となって、観察者側に戻るため良好な表示が得られる。しかし、斜め方向からパネルを観察すると、入射光がほとんど観察者側に戻ってこないため、表示の視認性が悪くなる。また、反射面が鏡面であると表示の背景に反射像が映って表示が見難くなるといった課題がある。

10

【0009】

上記課題の対策として、樹脂層表面に凹凸を形成し、該凹凸の形状に沿った反射膜を設けることが提案されている（例えば、特許文献1参照）。これを用いることにより、入射した外光を散乱させて、高い反射特性、及び明度の高い表示を可能にすることができます。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2002-296585号公報

【発明の概要】

【発明が解決しようとする課題】

20

【0011】

特許文献1では、樹脂層表面の凹凸の形成方法として、樹脂層に感光性の樹脂を利用し、露光条件の照射エネルギーを変化させることにより、該樹脂層表面に凹凸を形成する。その後熱処理を行うことで、樹脂層の熱的変形特性の分布を調整し、該樹脂層に凹凸を形成し、該凹凸に沿って反射性の高い膜を形成し反射膜を形成する技術が開示されている。しかしながら、特許文献1で開示された反射膜は、比較的大きな凹凸形状しか作製することができず、開示された反射膜を用いても、未だ十分に安定して高い反射特性を実現できていない。

【0012】

このような問題に鑑み、本発明においては、安定して高い反射特性を実現できる反射膜を有したゲストホスト液晶表示装置、及びその製造方法を提供することを課題の一つとする。

30

【課題を解決するための手段】

【0013】

反射型ゲストホスト液晶表示装置において、液晶層に接する反射性の画素電極層の表面に凹凸を設け、該凹凸はミクロンサイズの第1の凹凸に、さらにナノサイズの第2の凹凸が設けられて構成（形成）される。より詳細には次の通りである。

【0014】

本明細書で開示する発明の一形態は、ゲストホスト液晶を挟持する一対の基板と、一対の基板の一方に設けられた透光性の電極と、一対の基板の他方に設けられた第1の凹凸を有し、該第1の凹凸の表面に第2の凹凸が設けられた絶縁層と、絶縁層の第1の凹凸の表面に沿って形成され且つ該第2の凹凸によって表面が粗面化された画素電極層と、を有し、画素電極層は、反射性を有することを特徴とする液晶表示装置である。

40

【0015】

上記構成において、絶縁層は、感光性有機樹脂層を用いてもよい。また、絶縁層に設けられた第1の凹凸は、平面方向に1.5μm以上20μm以下の大きさとすることができます、0.1μm以上20μm以下の高さとすることができます。

【0016】

また、上記構成において、絶縁層に設けられた第2の凹凸は、平面方向に0.1μm以上1μm以下の大きさとすることができます、0.1μm以上1μm以下の高さとすることができます

50

きる。このように、第1の凹凸と比較し、第2の凹凸の方が小さく形成することができる。

【0017】

反射性の画素電極層は、第1の凹凸、及び第2の凹凸を有する絶縁層上に反射膜を形成することで作製することができる。反射性の画素電極層の下地膜として用いる絶縁層は、第1の凹凸を有する樹脂層を形成し、第1の凹凸を有する樹脂層にプラズマ処理を行うことによって、第1の凹凸上にさらに第2の凹凸を形成することができる。

【0018】

以上のように、第1の凹凸と第2の凹凸は、その大きさにより、それぞれミクロンサイズの凹凸、及びナノサイズの凹凸と、本明細書等において記載する場合がある。

10

【0019】

また、上記構成において、絶縁層にそって形成する画素電極層は、5nm以上500nm以下の厚さであってもよい。

【0020】

また、上記構成において、ゲストホスト液晶層は二色性色素をゲスト分子として混合したネマティック液晶を用いることができる。

【0021】

また、ゲストホスト液晶を用いた液晶表示装置は、二色性色素であるゲスト分子自体が光の吸収を行い黒表示となり、偏光板が不要となる。すなわち、偏光板による光の吸収が無く、白表示を行う際に優れた白表示を行うことが出来る。

20

【0022】

また、上記構成において、他方の基板と、画素電極層との間にトランジスタが設けられ、画素電極層はトランジスタと電気的に接続されてもよい。

【0023】

また、上記構成において、トランジスタは酸化物半導体層を用いてもよい。

【0024】

また、本明細書で開示する発明の他の一形態は、有機樹脂層上に第1の凹凸を形成し、第1の凹凸上にプラズマ処理にて第2の凹凸を形成し、第1の凹凸、及び前記第2の凹凸上に沿って反射性のある画素電極層を形成することを特徴とする液晶表示装置の作製方法である。

30

【0025】

上記構成において、第2の凹凸を形成するプラズマ処理は、酸素ガス雰囲気にて、第1の凹凸を有する有機樹脂層上に行ってもよい。

【0026】

第2の凹凸を形成するプラズマ処理は、例えば、ドライエッチング装置（もしくはアッシング装置とも呼ぶ）を用いて作製することができる。また、ドライエッチング装置のガス種、ガス流量、圧力、温度、高周波電力、処理時間の少なくとも一つを変えて、第2の凹凸の大きさ、及び高さを制御できる。

【発明の効果】

【0027】

安定して高い反射特性を実現できる反射膜を有したゲストホスト液晶表示装置、及びその製造方法を提供することができる。

40

【0028】

よって、高いコントラストが得られ、紙面に近い表示が実現でき、使用者の目に優しく、疲労感を低減させることができる。

【図面の簡単な説明】

【0029】

【図1】液晶表示装置の一形態を説明する図。

【図2】マルチチャンバー設備及びプラズマ装置の一形態を説明する図。

【図3】本発明の一態様である凹凸の断面SEM像。

50

【図4】液晶表示装置の一形態を説明する図。

【図5】液晶表示モジュールの一形態を説明する図。

【図6】液晶表示装置に適用できるトランジスタの一形態を説明する図。

【図7】液晶表示装置に適用できるトランジスタ及びトランジスタの作製方法の一形態を説明する図。

【図8】電子機器を説明する図

【図9】電子機器を説明する図。

【発明を実施するための形態】

【0030】

実施の形態について、図面を用いて詳細に説明する。但し、以下の説明に限定されず、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0031】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0032】

(実施の形態1)

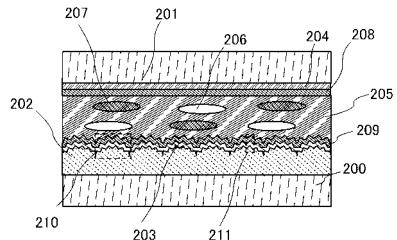

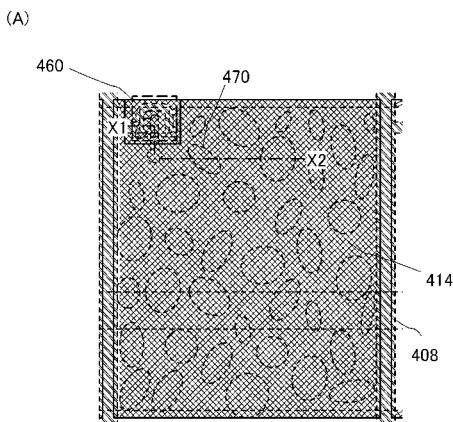

本明細書で開示する発明の構成の一形態である液晶表示装置を、図1を用いて説明する。図1は液晶表示装置の断面図である。

【0033】

図1は、配向膜209、画素電極層203、及び絶縁層202が設けられた第1の基板200と、共通電極層204と配向膜208が設けられた第2の基板201と、により挟持された液晶層205を有する液晶表示装置である。

【0034】

第1の基板200に形成された絶縁層202上には、ミクロンサイズの第1の凹凸210が形成されており、該第1の凹凸210の表面には、さらにナノサイズの第2の凹凸211が設けられている。また、絶縁層202上に形成された第1の凹凸210、及び第2の凹凸211の形状にそって反射性を有する画素電極層203が形成され、画素電極層203上には、液晶層205の配向を制御する配向膜209が形成されている。

【0035】

また、絶縁層202は、ミクロンサイズの第1の凹凸の形成位置や面積、及び凸部の高さを制御することで、画素電極層203表面の凹凸の大きさ、及び高さが制御することができるため、白表示の画質を調整できる。

【0036】

また、第2の基板201は、第2の基板上に共通電極層204を形成し、当該共通電極層204上に配向膜208を形成している。

【0037】

液晶層205としては、ホスト分子のネマティック液晶分子206と、ゲスト分子である二色性色素207と、により構成されたゲストホスト液晶である。

【0038】

なお、画素電極層203が反射性を有しており、液晶層205は、ゲストホスト液晶であるため、反射型ゲストホスト液晶と呼ぶことができる。

【0039】

液晶層205を形成する方法として、ディスペンサ法(滴下法)や、第1の基板200と第2の基板201とを貼り合わせてから毛細管現象を用いて液晶を注入する注入法を用いることができる。

【0040】

10

20

30

40

50

ここで、この反射型ゲストホスト液晶での動作について説明する。電圧無印加状態では、ネマティック液晶分子206は水平に配向しており、二色性色素207も同様に水平に配向する。第2の基板201側から入射した光が液晶層205に進むと、入射光のうち二色性色素207の分子の長軸方向に対して平行な振動面を持つ成分が二色性色素207によって吸収され、黒表示となる。一方、電圧印加時にはネマティック液晶分子206は電界方向に沿って垂直に配向し、二色性色素207も同様に垂直に配向する。第2の基板201側から入射した光は、二色性色素207によって吸収されないため液晶層205を通過し、画素電極層203で反射する。反射光は再び液晶層205を通過する。

## 【0041】

白表示を行う際、画素電極層203が反射性を有しているため、入射した光が画素電極層203によって液晶層205側に反射される。さらに画素電極層203は、絶縁層202に設けられた第1の凹凸210と第2の凹凸211にそって形成されており、画素電極層203に入射した光は液晶層205側に様々な方向に反射することができる。よって、優れた白表示を行うことができる。

10

## 【0042】

なお、液晶層205の厚さであるセルギャップは5μm以上30μm以下（好ましくは10μm以上20μm以下）とすればよい。なお、本明細書等においてセルギャップの厚さとは、液晶層の厚さ（膜厚）の最大値とする。

20

## 【0043】

画素電極層203下側に配置される絶縁層202は有機材料で形成することができる。代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いるのが好ましい。例えば、アクリル樹脂、エポキシ樹脂、アミン樹脂などを用いることができる。なお、絶縁層202は複数の薄膜の積層構造であってもよい。

20

## 【0044】

また、画素電極層203下側に配置される絶縁層202に形成するミクロンサイズの凹凸（第1の凹凸210）の形状は、錐形の先端が平面である断面が台形の形状、錐形の先端が丸いドーム状などを用いることができる。本明細書において画素電極層203は、第1の凹凸210の上面及び側面を覆うように形成されるため、第1の凹凸210は画素電極層203の被覆性が良好なように表面に曲面を有するような形状が好ましい。また、画素電極層203下側に配置される絶縁層202の高さは0.1μm以上20μm以下にすればよい。

30

## 【0045】

絶縁層202の形成方法は特に限定されず、材料に応じて、蒸着法、スパッタリング法、プラズマCVD法などの乾式法、又はスピンコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法）、ナノインプリント、各種印刷法（スクリーン印刷、オフセット印刷）等などの湿式法を用い、必要に応じてエッチング法（ドライエッチング又はウェットエッチング）により所望のパターンに加工すればよい。例えば感光性の有機樹脂にフォトリソグラフィ工程を行って絶縁層202を形成し第1の凹凸210を形成することができる。

40

## 【0046】

なお、絶縁層202に設ける第2の凹凸211は、第1の凹凸210形成後にプラズマ処理を行い形成することができる。また、第2の凹凸の高さは0.1μm以上1μm以下が好ましい。

## 【0047】

また、絶縁層202に設けられる第2の凹凸211の形成方法としては、ドライエッチング装置によるプラズマ処理を用いることができる。

## 【0048】

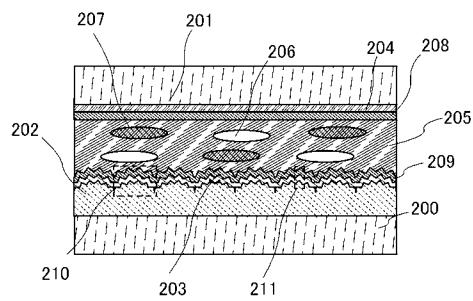

ここで、絶縁層202に設けられる第2の凹凸211の形成方法について、図2を用いて説明する。

## 【0049】

50

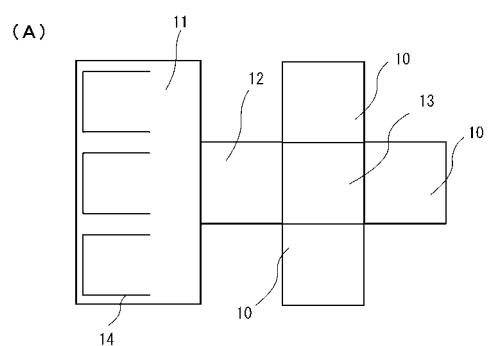

図2( A )は、枚葉式マルチチャンバー設備の上面図の一例を示し、図2( B )は、第2の凹凸の形成を行うプラズマ装置(ドライエッティング装置、もしくはアッシング装置とも呼ぶ)の断面図の一例である。

【0050】

図2( A )に示す枚葉式マルチチャンバー設備は、図2( B )に示すプラズマ装置10を3つ有し、被処理基板を収容するカセットポート14を3つ有する基板供給室11や、ロードロック室12や、搬送室13などを有している。基板供給室11に供給された基板は、ロードロック室12と搬送室13を介してプラズマ装置10内の真空チャンバー15に搬送されてプラズマ処理が行われる。プラズマ処理が終了した基板は、プラズマ装置10からロードロック室12と搬送室13を介して基板供給室11に搬送される。なお、基板供給室11及び搬送室13には、被処理基板を搬送するための搬送口ポートがそれぞれ配置されている。

10

【0051】

図2( B )を参照すると、プラズマ装置10は、真空チャンバー15を備える。真空チャンバー15の上部には、複数のガス吹き出し口(図示しない)と、プラズマ発生源であるICPコイル16(誘導結合プラズマコイル)が配置されている。

【0052】

ガス吹き出し口は、プラズマ装置10の上面から見て放射状に配置されている。それぞれのガス吹き出し口は、ガスを供給するためのガス供給源とガス流路17を介して接続されており、ガス供給源は、マスフローコントローラ等を備え、所望の流量(0より多く5000sccm以下)でガス流路17に対して酸素ガスを供給することができる。ガス供給源から供給される酸素ガスは、ガス流路17からガス吹き出し口を介して真空チャンバー15内に供給される。

20

【0053】

ICPコイル16は、複数本の帯状の導体を螺旋状に配置してなる。各導体の一端は、インピーダンス調整のためのマッチング回路を介して第1の高周波電源18(13.56MHz)に電気的に接続され、他端は接地されている。

【0054】

真空チャンバー15の下部には、下部電極として機能する基板ステージ19が配置されている。基板ステージ19に設けられた静電チャックなどにより、基板ステージ19上に被処理基板20が着脱可能に保持される。基板ステージ19には、加熱機構としてヒータを備えている。基板ステージ19は、基板バイアス電圧印加用の第2の高周波電源21(13.56MHz)に接続されている。

30

【0055】

また、真空チャンバー15には、排気口24が設けられ、圧力制御弁22(スロットルバルブとも呼ぶ。)が備えられる。圧力制御弁22はドライポンプ23に接続される。圧力制御弁22は真空チャンバー15内の圧力制御を行い、ドライポンプ23は、真空チャンバー15内を減圧する。

【0056】

次に、図2( B )に示す真空チャンバー15内にプラズマを発生させ、被処理基板20に設けられている有機樹脂にプラズマ処理を行う一例を示す。

40

【0057】

まず、ドライポンプ23を作動させて、真空チャンバー15内を所望の圧力に保持した後、被処理基板20を真空チャンバー15内の基板ステージ19に設置する。なお、基板ステージ19に保持する被処理基板20には少なくとも有機樹脂を備えるものとする。本実施の形態では、真空チャンバー15内の圧力を40Paに保持する。なお、酸素ガスをガス吹き出し口から真空チャンバー15内に供給する流量を1800sccmに設定する。

【0058】

次いで、第2の高周波電源21から高周波電力を印加し、プラズマを発生させる。そして、プラズマを発生させた状態を一定時間(30秒以上6000秒以下)維持する。なお、

50

第2の高周波電源21から印加する高周波電力は、100W以上5000W以下とする。本実施の形態では、850Wとする。この際、第1の高周波電源18からICPコイル16に高周波電力を印加してもよい。本実施の形態では0W、すなわち無印加とする。

【0059】

本実施の形態では、プラズマを発生させた状態を600秒維持した後、被処理基板20を真空チャンバー15から搬出する。こうして、被処理基板20に設けられている有機樹脂膜に第2の凹凸を形成することができる。

【0060】

なお、本明細書において、液晶表示装置は、外光の光を反射することによって表示を行う反射型の液晶表示装置である。よって、少なくとも視認側に設けられる第2の基板201、共通電極層204などは光を透過させる必要がある。よって光が透過する領域に存在する基板、絶縁層、電極層などは、すべて可視光の波長領域の光に対して透光性とする。一方、光を透過する視認側と反対側には反射性を有する画素電極層203を設ける。

【0061】

画素電極層203としては、反射性を有する導電性材料を用いる。また、反射性を有する導電性材料は、スパッタリング法等により形成することができる。例えば、タンゲステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。

【0062】

一方、共通電極層204としては、透光性を有する導電性材料を用いる。例えば、インジウム錫酸化物(ITO)、酸化インジウムに酸化亜鉛(ZnO)を混合したIZO(indium zinc oxide)、酸化インジウムに酸化珪素(SiO<sub>2</sub>)を混合した導電性材料、有機インジウム、有機スズ、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物を用いて形成することができる。

【0063】

また、第1の基板200、第2の基板201にはバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、石英基板、プラスチック基板などを用いることができる。

【0064】

以上のように、反射型ゲストホスト液晶表示装置において、第1の凹凸210、及び第2の凹凸211を有した絶縁層202にそって反射性の画素電極層203が設けられている。画素電極層203は、第1の凹凸210、及び第2の凹凸211により表面が粗面化されている。したがって、安定して高い反射特性を実現できる反射膜を有した表示装置を提供することができる。

【0065】

また、液晶層にゲストホスト液晶を用いることにより、液晶層にゲスト分子として混合した二色性色素により光の吸収を行うため、偏光板が不要となる。偏光板が不要となることで、偏光板による光の吸収がなく、より高輝度な明るい表示画面とすることができる。このように、光の利用効率がよいため消費電力を低減し、さらに偏光板にかかる工程はコストを削減することができる。

【0066】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0067】

(実施の形態2)

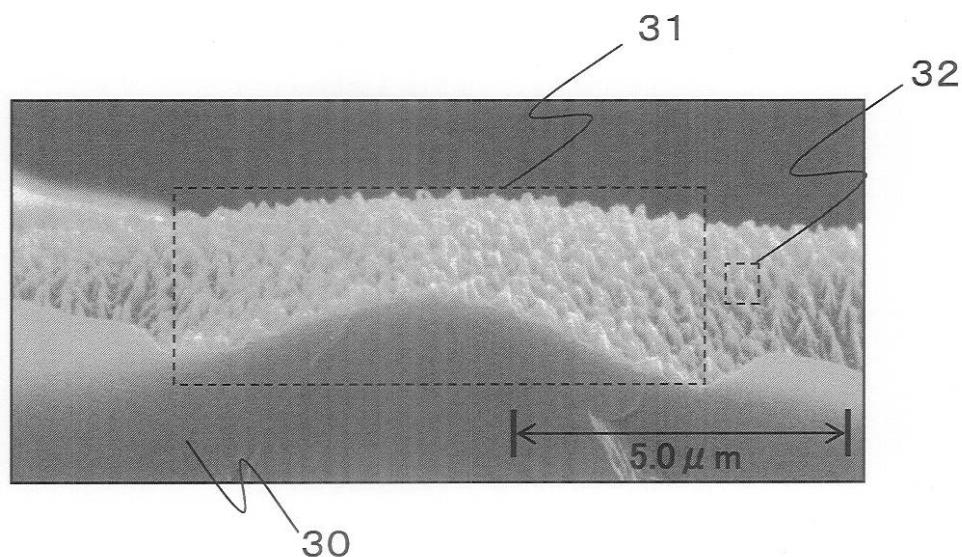

本明細書に開示する発明を適用したアクティブマトリクス型の液晶表示装置の例を、図4

10

20

30

40

50

を用いて説明する。

【0068】

図4(A)は液晶表示装置の平面図であり1画素分の画素を示している。図4(B)は図4(A)の線X1-X2における断面図である。

【0069】

図4において、複数のソース配線層(ソース電極層405aを含む)が互いに平行(図中上下方向に延伸)かつ互いに離間した状態で配置されている。複数のゲート配線層(ゲート電極層401を含む)は、ソース配線層に略直交する方向(図中左右方向)に延伸し、かつ互いに離間するように配置されている。容量配線層408は、複数のゲート配線層にそれぞれに隣接する位置に配置されており、ゲート配線層に概略平行な方向、つまり、ソース配線層に概略直交する方向(図中左右方向)に延伸している。ソース配線層と、ゲート配線層とによって、略長方形の空間が囲まれているが、この空間に液晶表示装置の画素電極層414が配置され、液晶層444を介して共通電極層448が配置されている。画素電極層414を駆動するトランジスタ460は、図4(A)中左上の角に配置されている。また、画素電極層414及びトランジスタ460は、マトリクス状に複数配置されている。

10

【0070】

なお、図4(A)の平面図は素子基板である第1の基板441側を示したもので、液晶層444、共通電極層448、配向膜450、第2の基板442は省略している。

20

【0071】

図4の液晶表示装置において、トランジスタ460に電気的に接続する画素電極層414が画素電極として機能し、対向して設けられた共通電極層448が共通電極として機能する。なお、画素電極層414と容量配線層408によって容量が形成されている。

30

【0072】

なお、画素電極層414には、トランジスタ460の半導体層403と電気的に接続するソース電極層405a及びドレイン電極層405bを介して、画像信号の電位が与えられる。一方、共通電極層448には、画素電極層414に供給される画像信号の電位に対して基準となる固定電位(一例としてはグラウンド電位(接地電位))が与えられる。共通電位はデータとして送られる画像信号の中間電位近傍でフリッカーの生じないレベルに設定すると好ましい。また、共通電極層448とはフローティング状態(電気的に孤立した状態)として動作させることも可能である。

30

【0073】

図4(B)は、トランジスタ460と、トランジスタ460上に第1の凹凸470及び第2の凹凸480を有した絶縁層417と、絶縁層417上に画素電極層414と、が設けられた第1の基板441と、共通電極層448が設けられた第2の基板442とが、液晶層444を間に挟持して対向するように配置された液晶表示装置である。なお、画素電極層414上には配向膜451が形成され、同様に共通電極層448上にも配向膜450が形成されている。また、絶縁層417はトランジスタ460の層間膜としても兼用している。

40

【0074】

トランジスタ460は、ゲート電極層401、ゲート絶縁層402、半導体層403、ソース電極層405a、及びドレイン電極層405bにより構成されている。

40

【0075】

また、トランジスタ460上には、絶縁層407、絶縁層409、絶縁層417、画素電極層414が形成されており、絶縁層417、絶縁層409、及び絶縁層407には、ソース電極層405a及びドレイン電極層405bに達するコンタクトホール449が設かれている。また、画素電極層414は、ソース電極層405a及びドレイン電極層405bを介して半導体層403と電気的に接続されている。

【0076】

なお、図4(B)において、コンタクトホール449内にはナノサイズの第2の凹凸48

50

0は図示していないが、コンタクトホール内にもナノサイズの第2の凹凸480を形成しても良い。

【0077】

第1の凹凸470、及び第2の凹凸480は、複数配置することによって凹凸を形成している。画素電極層414は、第1の凹凸470、及び第2の凹凸480上を覆うように形成することによって、表面に凹凸を有している。また、第1の凹凸470、及び第2の凹凸480は、液晶層444中に突出して設けられている。また、第1の凹凸470の形状は、図4(A)に示すように平面図において、橢円状に不規則に形成すればよい。なお、本明細書において、凹凸とは、少なくとも二つ以上の凸部を有する構造体と、凸部を有する構造体間により形成された凹部と、を有し、凹凸の高さとは、凸部の最も高い位置と、凹部の最も低い位置との距離であり、凹凸の大きさとは、凸部を有する構造体の頂点を含む断面において、異なる凸部を有する構造体の頂点間の距離とする。

10

【0078】

なお、第1の凹凸470の形状は、特に限定されず、橢円、正方形、長方形などの形状を用いてもよい。

【0079】

絶縁層417の形成法は、特に限定されず、その材料に応じて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ロールコート、カーテンコート、ナイフコート等を用いることができる。

20

【0080】

なお、第1の基板441と第2の基板442との固着工程は、液晶層444を間に挟持させてシール材(図示しない)によって行うことができる。

【0081】

シール材としては、代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いるのが好ましい。代表的には、アクリル樹脂、エポキシ樹脂、アミン樹脂などを用いることができる。また、光(代表的には紫外線)重合開始剤、熱硬化剤、フィラー、カップリング剤を含んでもよい。

【0082】

液晶層444としては、ホスト分子であるネマティック液晶分子と、ゲスト分子である二色性色素により構成されたゲストホスト液晶を用いる。液晶層444は、実施の形態1で示した液晶層205と同様の材料及び方法により形成すればよい。

30

【0083】

また、液晶層444において、画素電極層414と共に電極層448が電圧無印加状態(オフ状態ともいう)のとき、ゲストホスト液晶内に分散しているネマティック液晶分子、及び二色性色素は、水平に配列しているため、入射した光は液晶層444にて吸収される。よって視認側から確認できる表示は黒表示となる。

【0084】

一方、画素電極層414と共に電極層448に電圧を印加した場合(オン状態ともいう)、液晶層444に電界が形成され、ネマティック液晶分子、及び二色性色素は電界方向に配列し、入射した光はネマティック液晶分子、及び二色性色素で吸収されず、液晶層444を透過する。よって、液晶層444は透光性となり透明な状態となる。液晶層444が透光性な状態となった場合は、視認側から確認できる表示は、液晶層444の前後に設けられる材料に依存する。

40

【0085】

画素電極層414が反射性を有しているため、入射した光が液晶層444側に反射される。さらに画素電極層414は絶縁層417に形成した第1の凹凸470及び第2の凹凸480にそって形成されており、画素電極層414に入射した光は液晶層444に様々な方向に反射することができる。よって、優れた白表示を行うことができる。

【0086】

ここで、トランジスタ460の作製方法について、以下説明を行う。

50

## 【0087】

まず、第1の基板441上にゲート電極層401を形成する。

## 【0088】

下地膜となる絶縁膜を第1の基板441とゲート電極層401の間に設けてもよい。下地膜は、第1の基板441からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

## 【0089】

ゲート電極層401の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

10

## 【0090】

例えば、ゲート電極層401の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、または銅層上にモリブデン層を積層した二層構造、または銅層上に窒化チタン層若しくは窒化タンタルを積層した二層構造、窒化チタン層とモリブデン層とを積層した2層構造とすることが好ましい。3層の積層構造としては、タングステン層または窒化タングステンと、アルミニウムとシリコンの合金またはアルミニウムとチタンの合金と、窒化チタン層またはチタン層とを積層した構造とすることが好ましい。

。

## 【0091】

次に、ゲート電極層401上にゲート絶縁層402を形成する。

20

## 【0092】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。また、ゲート絶縁層402として、有機シランガスを用いたCVD法により酸化シリコン層を形成することも可能である。有機シランガスとしては、珪酸エチル (TEOS : 化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$  )、テトラメチルシラン (TMS : 化学式  $\text{Si}(\text{CH}_3)_4$  )、テトラメチルシクロテトラシロキサン (TMCTS)、オクタメチルシクロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン ( $\text{SiH}(\text{OC}_2\text{H}_5)_3$  )、トリスジメチルアミノシラン ( $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$  )等のシリコン含有化合物を用いることができる。

30

## 【0093】

なお、半導体層、電極層、配線層の形成、及び作製工程において、各層のパターニングには、多階調マスクにより形成した複数（代表的には二種類）の厚さの領域を有するレジストマスクを用いると、レジストマスクの数を減らすことができるため、工程簡略化、低コスト化が図れる。また、各層の薄膜を所望の形状に加工するためにエッティング工程を用いる。エッティング工程は、ドライエッティングやウェットエッティングを用いることができる。

40

## 【0094】

ドライエッティングに用いるエッティング装置としては、反応性イオンエッティング法 (RIE法) を用いたエッティング装置や、ECR (Electron Cyclotron Resonance) やICP (Inductively Coupled Plasma) などの高密度プラズマ源を用いたドライエッティング装置を用いることができる。

## 【0095】

また、ドライエッティングを行う場合、所望の加工形状にエッティングできるように、エッティング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

## 【0096】

また、ウェットエッティングを行う場合、所望の加工形状にエッティングできるように、材料

50

に合わせてエッティング条件（エッティング液、エッティング時間、温度等）を適宜調節する。

【0097】

次に、ゲート絶縁層402上に、半導体層403を形成する。半導体層403としては、酸化物半導体層を用いることができる。

【0098】

次に、半導体層403、及びゲート絶縁層402上に、ソース電極層405a、及びドレイン電極層405bを形成する。

【0099】

ソース電極層405a、ドレイン電極層405bの材料としては、Al、Cr、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、熱処理を行う場合には、この熱処理に耐える耐熱性を導電膜に持たせることが好ましい。例えば、Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。Alと組み合わせる耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物で形成する。

10

【0100】

なお、トランジスタ460の半導体層403は一部のみがエッティングされ、溝部(凹部)を有する半導体層の例である。

20

【0101】

次に、ゲート絶縁層402、半導体層403、ソース電極層405a、及びドレイン電極層405b上に絶縁層407、及び絶縁層409を形成する。

【0102】

絶縁層407、及び絶縁層409としては、乾式法や湿式法で形成される無機絶縁膜、有機絶縁膜を用いることができる。例えば、プラズマCVD法やスパッタリング法などを用いて得られる窒化シリコン膜、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化タンタル膜などを用いることができる。また、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low-k材料)、シロキサン系樹脂等を用いることができる。

30

【0103】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基(例えばアルキル基やアリール基)やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。シロキサン系樹脂は塗布法により成膜し、焼成することによって絶縁層407として用いることができる。

【0104】

なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層407、絶縁層409を形成してもよい。例えば、無機絶縁膜上に有機樹脂膜を積層する構造としてもよい。

40

【0105】

以上の工程により、第1の基板441上にトランジスタ460を形成することができる。

【0106】

次にトランジスタ460上に、絶縁層417を形成する。また、絶縁層417には、第1の凹凸470、及び第2の凹凸480が設けられる。絶縁層417、第1の凹凸、及び第2の凹凸は、それぞれ、実施の形態1で示した絶縁層202、第1の凹凸210、第2の凹凸211と同様の材料、及び手法により形成することができる。

【0107】

次に、第1の凹凸470、及び第2の凹凸480にそって画素電極層414を形成する。

50

画素電極層 414 は、反射性を有する導電性材料を用いることができ、実施の形態 1 に示した画素電極層 203 と同様の材料、及び手法により形成することができる。

【0108】

以上のように、トランジスタ 460 を有した第 1 の基板 441 上に、絶縁層 417 が形成され、該絶縁層 417 には、第 1 の凹凸 470、及び第 2 の凹凸 480 が形成されている。また、画素電極層 414 は、第 1 の凹凸 470、及び第 2 の凹凸 480 にそって形成されているため、画素電極層 414 に入射した光は、液晶層 444 側に様々な方向に反射することができる。

【0109】

また、本実施の形態に示した反射型ゲストホスト液晶は、入射した光に偏光を行わないため、偏光板を設けなくてもよい。

10

【0110】

従って、反射型ゲストホスト液晶を用いた液晶表示装置は、偏光板を設けないため、偏光板による光の吸収がなく、より高輝度な明るい表示画面とすることができる。よって、光の利用効率がよいため、低消費電力化にもなる。偏光板にかかる工程やコストを削減することができ、より高スループット、低コストを実現できる。よって、表示装置に反射型ゲストホスト液晶材料を用いることはより効果的である。

【0111】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

20

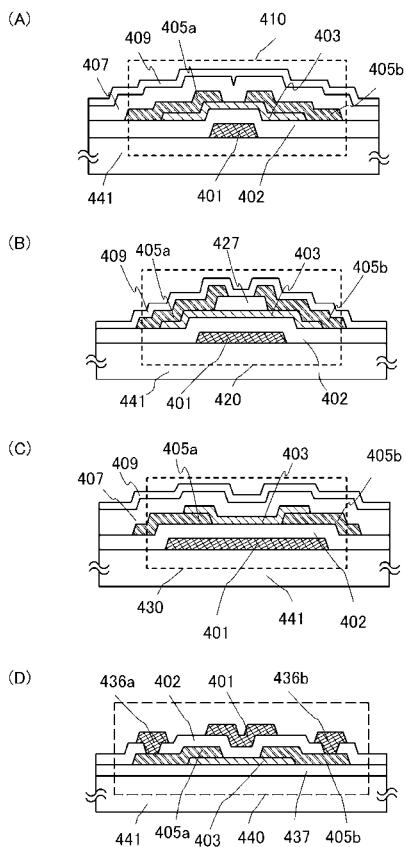

【0112】

(実施の形態 3)

本実施の形態では、本明細書に開示する液晶表示装置に適用できるトランジスタの例を示す。本明細書に開示する液晶表示装置に適用できるトランジスタの構造は特に限定されず、例えばトップゲート構造、又はボトムゲート構造のスタガ型及びブレーナ型などを用いることができる。また、トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、2つ形成されるダブルゲート構造もしくは3つ形成されるトリブルゲート構造であっても良い。また、チャネル領域の上下にゲート絶縁層を介して配置された2つのゲート電極層を有する、デュアルゲート型でもよい。なお、図 6 (A) 乃至 (D) にトランジスタの断面構造の一例を以下に示す。

30

【0113】

図 6 (A) に示すトランジスタ 410 は、ボトムゲート構造の薄膜トランジスタの一つであり、逆スタガ型薄膜トランジスタともいう。

【0114】

トランジスタ 410 は、絶縁表面を有する基板 441 上に、ゲート電極層 401、ゲート絶縁層 402、半導体層 403、ソース電極層 405a、及びドレイン電極層 405b を含む。また、トランジスタ 410 を覆い、半導体層 403 に積層する絶縁層 407 が設けられている。絶縁層 407 上にはさらに絶縁層 409 が形成されている。

【0115】

図 6 (B) に示すトランジスタ 420 は、チャネル保護型（チャネルトップ型ともいう）と呼ばれるボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

40

【0116】

トランジスタ 420 は、絶縁表面を有する基板 441 上に、ゲート電極層 401、ゲート絶縁層 402、半導体層 403、半導体層 403 のチャネル形成領域を覆うチャネル保護層として機能する絶縁層 427、ソース電極層 405a、及びドレイン電極層 405b を含む。また、トランジスタ 420 を覆い、絶縁層 409 が形成されている。

【0117】

図 6 (C) に示すトランジスタ 430 はボトムゲート型の薄膜トランジスタであり、絶縁表面を有する基板である基板 441 上に、ゲート電極層 401、ゲート絶縁層 402、ソース電極層 405a、ドレイン電極層 405b、及び半導体層 403 を含む。また、トランジスタ 430 を覆い、絶縁層 409 が形成されている。

50

ンジスタ430を覆い、半導体層403に接する絶縁層407が設けられている。絶縁層407上にはさらに絶縁層409が形成されている。

【0118】

トランジスタ430においては、ゲート絶縁層402は基板441及びゲート電極層401上に接して設けられ、ゲート絶縁層402上にソース電極層405a、ドレイン電極層405bが接して設けられている。そして、ゲート絶縁層402、及びソース電極層405a、ドレイン電極層405b上に半導体層403が設けられている。

【0119】

図6(D)に示すトランジスタ440は、トップゲート構造の薄膜トランジスタの一つである。トランジスタ440は、絶縁表面を有する基板441上に、絶縁層437、半導体層403、ソース電極層405a、及びドレイン電極層405b、ゲート絶縁層402、ゲート電極層401を含み、ソース電極層405a、ドレイン電極層405bにそれぞれ配線層436a、配線層436bが接して設けられ電気的に接続している。

10

【0120】

絶縁表面を有する基板441に使用することができる基板に大きな制限はないが、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板を用いる。

【0121】

ボトムゲート構造のトランジスタ410、420、430において、下地膜となる絶縁膜を基板441とゲート電極層401の間に設けてもよい。下地膜は、基板441からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

20

【0122】

ゲート電極層401の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。

【0123】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、酸化ガリウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。例えば、第1のゲート絶縁層としてプラズマCVD法により膜厚50nm以上200nm以下の窒化シリコン層(SiNy(y>0))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層(SiOx(x>0))を積層して、合計膜厚500nm以下のゲート絶縁層とする。

30

【0124】

ソース電極層405a、及びドレイン電極層405bに用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等を用いることができる。また、Al、Cuなどの金属層の下側又は上側の一方または双方にTi、Mo、Wなどの高融点金属層を積層させた構成としても良い。また、Al膜に生ずるヒロックやウィスカーの発生を防止する元素(Si、Nd、Scなど)が添加されているAl材料を用いることで耐熱性を向上させることができる。

40

【0125】

ソース電極層405a、及びドレイン電極層405bに接続する配線層436a、及び配線層436bのような導電膜も、ソース電極層405a、及びドレイン電極層405bと同様な材料を用いることができる。

【0126】

また、ソース電極層405a、ドレイン電極層405b(これと同じ層で形成される配線層を含む)となる導電膜としては導電性の金属酸化物で形成しても良い。導電性の金属酸

50

化物としては酸化インジウム ( $In_2O_3$ )、酸化スズ ( $SnO_2$ )、酸化亜鉛 ( $ZnO$ )、酸化インジウム酸化スズ合金 ( $In_2O_3 - SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金 ( $In_2O_3 - ZnO$ ) またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

## 【0127】

絶縁層407は、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などの無機絶縁膜を用いることができる。

## 【0128】

絶縁層409は、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜を用いることができる。

10

## 【0129】

また、絶縁層409上にトランジスタ起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。平坦化絶縁膜としては、ポリイミド、アクリル、ベンゾシクロブテン、等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料 (low-k材料) 等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁膜を形成してもよい。

## 【0130】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

20

## 【0131】

## (実施の形態4)

上記実施の形態2または3において、トランジスタの半導体層に用いることのできる例として酸化物半導体について説明する。

## 【0132】

実施の形態2で示したトランジスタ460、または実施の形態3で示した図6(A)乃至(D)のトランジスタ410、420、430、440において、半導体層403として酸化物半導体を用いることができる。

30

## 【0133】

半導体層403に用いる酸化物半導体としては、四元系金属酸化物である  $In - Sn - Ga - Zn - O$  系や、三元系金属酸化物である  $In - Ga - Zn - O$  系、 $In - Sn - Zn - O$  系、 $In - Al - Zn - O$  系、 $Sn - Ga - Zn - O$  系、 $Al - Ga - Zn - O$  系、 $Sn - Al - Zn - O$  系や、二元系金属酸化物である  $In - Ga - O$  系、 $In - Zn - O$  系、 $Sn - Zn - O$  系、 $Al - Zn - O$  系、 $Zn - Mg - O$  系、 $Sn - Mg - O$  系、 $In - Mg - O$  系や、 $In - O$  系、 $Sn - O$  系、 $Zn - O$  系などを用いることができる。また、上記酸化物半導体に  $SiO_2$  を含んでもよい。ここで、例えば、 $In - Ga - Zn - O$  系酸化物半導体とは、少なくとも  $In$  と  $Ga$  と  $Zn$  を含む酸化物であり、その組成比に特に制限はない。また、 $In$  と  $Ga$  と  $Zn$  以外の元素を含んでもよい。

30

## 【0134】

また、酸化物半導体層は、化学式  $InM_3O_3$  ( $ZnO$ ) $_m$  ( $m > 0$ ) で表記される薄膜を用いることができる。ここで、Mは、 $Ga$ 、 $Al$ 、 $Mn$  および  $Co$  から選ばれた一または複数の金属元素を示す。例えばMとして、 $Ga$ 、 $Ga$  および  $Al$ 、 $Ga$  および  $Mn$ 、または  $Ga$  および  $Co$  などがある。

40

## 【0135】

また、酸化物半導体として  $In - Zn - O$  系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、 $In : Zn = 50 : 1 \sim 1 : 2$  (モル数比に換算すると  $In_2O_3 : ZnO = 25 : 1 \sim 1 : 4$ )、好みしくは  $In : Zn = 20 : 1 \sim 1 : 1$  (モル数比に換算すると  $In_2O_3 : ZnO = 10 : 1 \sim 1 : 2$ )、さらに好みしくは  $In : Zn = 15 : 1 \sim 1 : 5 : 1$  (モル数比に換算すると  $In_2O_3 : ZnO = 15 : 2 \sim 3 : 4$ ) とする。例えば、 $In - Zn - O$  系酸化物半導体の形成に用いるターゲットは、原子数比が  $In : Zn : O = X : Y : Z$  のとき、 $Z > 1 : 5X + Y$  とする。

50

## 【0136】

酸化物半導体層を用いたトランジスタ410、420、430、440、460は、オフ状態における電流値（オフ電流値）を低くすることができる。

## 【0137】

また、半導体層403として酸化物半導体層を用いたトランジスタ410、420、430、440、460は、比較的高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に該トランジスタを用いることで、高画質な画像を提供することができる。また、該トランジスタを用いて、同一基板上に駆動回路部または画素部を作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

10

## 【0138】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【0139】

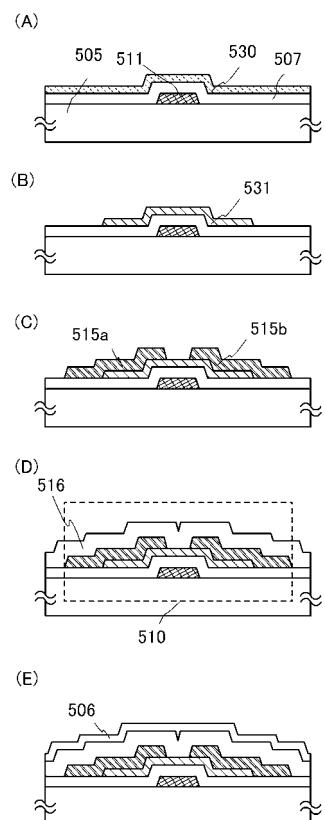

## (実施の形態5)

本実施の形態は、酸化物半導体層を含むトランジスタ、及び作製方法の他の一例を図7を用いて詳細に説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

20

## 【0140】

図7(A)乃至(E)にトランジスタの断面構造の一例を示す。図7(A)乃至(E)に示すトランジスタ510は、図6(A)に示すトランジスタ410と同様なボトムゲート構造の逆スタガ型薄膜トランジスタである。

## 【0141】

本実施の形態の半導体層に用いる酸化物半導体は、n型不純物である水素を酸化物半導体から除去した後酸素を供給し、酸化物半導体の構成元素以外の不純物が極力含まれないように高純度化することによりI型（真性）の酸化物半導体、又はI型（真性）に限りなく近い酸化物半導体としたものである。すなわち、水素や水等の不純物を極力除去し、酸素を供給したことにより、高純度化されたI型（真性半導体）又はそれに近づけることを特徴としている。そうすることにより、フェルミ準位（Ef）を真性フェルミ準位（Ei）と同じレベルにまですることができる。従って、トランジスタ510が有する酸化物半導体層は、高純度化及び電気的にI型（真性）化された酸化物半導体層である。

30

## 【0142】

また、高純度化された酸化物半導体中にはキャリアが極めて少なく（ゼロに近い）、キャリア濃度は $1 \times 10^{14} / \text{cm}^3$ 未満、好ましくは $1 \times 10^{12} / \text{cm}^3$ 未満、さらに好ましくは $1 \times 10^{11} / \text{cm}^3$ 未満である。

## 【0143】

酸化物半導体中にキャリアが極めて少ないため、トランジスタの電気特性の一つである、オフ電流を少なくすることができる。オフ電流は少なければ少ないと好ましい。

40

## 【0144】

具体的には、上述の酸化物半導体層を具備するトランジスタ510は、オフ状態における電流値（オフ電流値）を、チャネル幅 $1 \mu\text{m}$ 当たり $10 \text{ zA} / \mu\text{m}$ 未満、85にて $10 \text{ zA} / \mu\text{m}$ 未満レベルにまで低くすることができる。

## 【0145】

また、上述の酸化物半導体層を具備するトランジスタ510はオン電流の温度依存性がほとんど見られず、オフ電流も非常に小さいままである。また、光劣化によるトランジスタ特性の変動も少ない。

## 【0146】

以下、図7(A)乃至(E)を用い、基板505上にトランジスタ510を作製する工程を説明する。

50

## 【0147】

まず、絶縁表面を有する基板505上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層511を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0148】

絶縁表面を有する基板505は、実施の形態3に示した基板441と同様な基板を用いることができる。本実施の形態では基板505としてガラス基板を用いる。

## 【0149】

下地膜となる絶縁膜を基板505とゲート電極層511との間に設けてもよい。下地膜は、基板505からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

## 【0150】

また、ゲート電極層511の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

## 【0151】

次いで、ゲート電極層511上にゲート絶縁層507を形成する。ゲート絶縁層507は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化ガリウム層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。また、本実施の形態の酸化物半導体は、不純物を除去され、酸素が供給されることによりI型化又は実質的にI型化された酸化物半導体を用いる。このような高純度化された酸化物半導体は界面準位、界面電荷に対して極めて敏感であるため、酸化物半導体層とゲート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層は、高品質化が要求される。

## 【0152】

例えば、μ波(例えば周波数2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

## 【0153】

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

## 【0154】

また、ゲート絶縁層507、酸化物半導体層530に水素、水酸基及び水分がなるべく含まれないようにするために、酸化物半導体層530の成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層511が形成された基板505、又はゲート絶縁層507までが形成された基板505を予備加熱し、基板505に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、絶縁層516の成膜前に、ソース電極層515a及びドレイン電極層515bまで形成した基板505にも同様に行ってもよい。

## 【0155】

次いで、ゲート絶縁層507上に、膜厚2nm以上200nm以下、好ましくは5nm以上30nm以下の酸化物半導体層530を形成する(図7(A)参照。)。

10

20

30

40

50

## 【0156】

なお、酸化物半導体層530をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行い、ゲート絶縁層507の表面に付着している粉状物質（パーティクル、ごみともいう）を除去することが好ましい。逆スパッタリングとは、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加することによって、基板表面をプラズマに曝して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

## 【0157】

酸化物半導体層530に用いる酸化物半導体は、実施の形態3に示した四元系金属酸化物や、三元系金属酸化物や、二元系金属酸化物や、In-O系、Sn-O系、Zn-O系などの酸化物半導体を用いることができる。また、上記酸化物半導体にSiO<sub>2</sub>を含んでもよい。本実施の形態では、酸化物半導体層530としてIn-Ga-Zn-O系酸化物ターゲットを用いてスパッタリング法により成膜する。この段階での断面図が図7(A)に相当する。また、酸化物半導体層530は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下においてスパッタリング法により形成することができる。

10

## 【0158】

酸化物半導体層530をスパッタリング法で作製するためのターゲットとしては、例えば、組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol比]（すなわち、In : Ga : Zn = 1 : 1 : 0.5 [atom比]）を用いることができる。また、他にも、In : Ga : Zn = 1 : 1 : 1 [atom比]、又はIn : Ga : Zn = 1 : 1 : 2 [atom比]の組成比を有するターゲットを用いてもよい。酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体層は緻密な膜となる。

20

## 【0159】

酸化物半導体層530を、成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

## 【0160】

減圧状態に保持された成膜室内に基板を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板を加熱しながら成膜することにより、成膜した酸化物半導体層に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタリングガスを導入し、上記ターゲットを用いて基板505上に酸化物半導体層530を成膜する。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体層に含まれる不純物の濃度を低減できる。

30

## 【0161】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源5kW、Ar = 50sccm、酸素 = 50sccm（酸素流量比率50%）雰囲気下の条件が適用される。なお、パルス直流電源を用いると、成膜時に発生する粉状物質（パーティクル、ごみともいう）が軽減でき、膜厚分布も均一となるために好ましい。

40

## 【0162】

次いで、酸化物半導体層530を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインク

50

ジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0163】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体層530の加工時に同時にを行うことができる。

【0164】

なお、ここで酸化物半導体層530のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。例えば、酸化物半導体層530のウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液、アンモニア過水(31重量%過酸化水素水: 28重量%アンモニア水: 水 = 5:2:2)などを用いることができる。また、ITO07N(関東化学社製)を用いてもよい。

10

【0165】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、または400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層531を得る(図7(B)参照。)。

【0166】

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

20

【0167】

例えば、第1の加熱処理として、650~700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。

30

【0168】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

40

【0169】

また、第1の加熱処理で酸化物半導体層を加熱した後、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア(露点が-40以下、好ましくは-60以下)を導入してもよい。酸素ガスまたはN<sub>2</sub>Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN<sub>2</sub>Oガスの純度を、6N以上好ましくは7N以上(即ち、酸素ガスまたはN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。酸素ガス又はN<sub>2</sub>Oガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型(真性)化する。

【0170】

50

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体層530に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

【0171】

なお、第1の加熱処理は、上記以外にも、酸化物半導体層成膜後であれば、酸化物半導体層上にソース電極層及びドレイン電極層を積層させた後、あるいは、ソース電極層及びドレイン電極層上に絶縁層を形成した後、のいずれで行っても良い。

【0172】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体層530に第1の加熱処理を行う前でも行った後に行ってもよい。

10

【0173】

また、酸化物半導体層を2回に分けて成膜し、2回に分けて加熱処理を行うことで、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜厚の厚い結晶領域（単結晶領域）、即ち、膜表面に垂直にc軸配向した結晶領域を有する酸化物半導体層を形成してもよい。例えば、3nm以上15nm以下の第1の酸化物半導体層を成膜し、窒素、酸素、希ガス、または乾燥空気の雰囲気下で450以上850以下、好ましくは550以上750以下の第1の加熱処理を行い、表面を含む領域に結晶領域（板状結晶を含む）を有する第1の酸化物半導体層を形成する。そして、第1の酸化物半導体層よりも厚い第2の酸化物半導体層を形成し、450以上850以下、好ましくは600以上700以下の第2の加熱処理を行い、第1の酸化物半導体層を結晶成長の種として、上方に結晶成長させ、第2の酸化物半導体層の全体を結晶化させ、結果として膜厚の厚い結晶領域を有する酸化物半導体層を形成してもよい。

20

【0174】

次いで、ゲート絶縁層507、及び酸化物半導体層531上に、ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる導電膜を形成する。ソース電極層、及びドレイン電極層に用いる導電膜としては、実施の形態3に示したソース電極層405a、ドレイン電極層405bに用いる材料を用いることができる。

30

【0175】

第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層515a、ドレイン電極層515bを形成した後、レジストマスクを除去する（図7（C）参照。）。

【0176】

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いるとよい。酸化物半導体層531上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm～数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet）を用いて第3のフォトリソグラフィ工程でのレジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化できる。

40

【0177】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

50

## 【0178】

なお、導電膜のエッティングの際に、酸化物半導体層531がエッティングされ、分断することのないようエッティング条件を最適化することが望まれる。しかしながら、導電膜のみをエッティングし、酸化物半導体層531を全くエッティングしないという条件を得ることは難しく、導電膜のエッティングの際に酸化物半導体層531は一部のみがエッティングされ、溝部(凹部)を有する酸化物半導体層となることもある。

## 【0179】

本実施の形態では、導電膜としてTi膜を用い、酸化物半導体層531にはIn-Ga-Zn-O系酸化物半導体を用いたので、エッティング液としてアンモニア過水(アンモニア、水、過酸化水素水の混合液)を用いる。

10

## 【0180】

次いで、N<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理を行い、露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる絶縁層516を形成する。

## 【0181】

絶縁層516は、少なくとも1nm以上の膜厚とし、スパッタリング法など、絶縁層516に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。絶縁層516に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体層中の酸素の引き抜き、が生じ酸化物半導体層のバックチャネルが低抵抗化(N型化)してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁層516はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

20

## 【0182】

本実施の形態では、絶縁層516として膜厚300nmの酸化シリコン膜をスパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化シリコン膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガスと酸素の混合雰囲気下において行うことができる。また、ターゲットとして酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素を含む雰囲気下でスパッタリング法により酸化シリコンを形成することができる。酸化物半導体層に接して形成する絶縁層516は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。

30

## 【0183】

酸化物半導体層530の成膜時と同様に、絶縁層516の成膜室内の残留水分を除去するためには、吸着型の真空ポンプ(クライオポンプなど)を用いることが好ましい。クライオポンプを用いて排気した成膜室で成膜した絶縁層516に含まれる不純物の濃度を低減できる。また、絶縁層516の成膜室内の残留水分を除去するための排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。

40

## 【0184】

絶縁層516を、成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

## 【0185】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル形成領域)が絶縁層516と接した状態で加熱される。

## 【0186】

以上の工程を経ることによって、酸化物半導体層に対して第1の加熱処理を行って水素、

50

水分、水酸基又は水素化物（水素化合物ともいう）などの不純物を酸化物半導体層より意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する材料の一つである酸素を供給することができる。よって、酸化物半導体層は高純度化及び電気的にI型（真性）化する。

## 【0187】

以上の工程でトランジスタ510が形成される（図7（D）参照。）。

## 【0188】

また、絶縁層516に欠陥を多く含む酸化シリコン層を用いると、酸化シリコン層形成後の加熱処理によって酸化物半導体層中に含まれる水素、水分、水酸基又は水素化物などの不純物を酸化物絶縁層に拡散させ、酸化物半導体層中に含まれる該不純物をより低減させる効果を奏する。

10

## 【0189】

絶縁層516上にさらに保護絶縁層506を形成してもよい。例えば、RFスパッタリング法を用いて窒化シリコン膜を形成する。保護絶縁層は、水分などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化シリコン膜、窒化アルミニウム膜などを用いる。本実施の形態では、保護絶縁層506を、窒化シリコン膜を用いて形成する（図7（E）参照。）。

## 【0190】

本実施の形態では、保護絶縁層506として、絶縁層516まで形成された基板505を100～400の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタリングガスを導入しシリコン半導体のターゲットを用いて窒化シリコン膜を成膜する。この場合においても、絶縁層516と同様に、処理室内の残留水分を除去しつつ保護絶縁層506を成膜することが好ましい。

20

## 【0191】

保護絶縁層の形成後、さらに大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。

## 【0192】

このように、本実施の形態を用いて作製した、高純度化された酸化物半導体層を含むトランジスタを用いることにより、オフ状態における電流値（オフ電流値）をより低くすることができる。

30

## 【0193】

液晶表示装置に設けられる保持容量の大きさは、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間の間電荷を保持できるように設定される。保持容量の大きさは、トランジスタのオフ電流等を考慮して設定すればよい。本実施の形態で示した高純度の酸化物半導体層を有するトランジスタを用いるのであれば、各画素における液晶容量に対して1/3以下、好ましくは1/5以下の容量の大きさを有する保持容量を設ければ充分である。

40

## 【0194】

また、高純度化された酸化物半導体層を含むトランジスタは、高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に該トランジスタを用いることで、高画質な画像を提供することができる。また、該トランジスタによって、同一基板上に駆動回路部または画素部を作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

## 【0195】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【0196】

（実施の形態6）

50

上記実施の形態2乃至5において、トランジスタの半導体層に用いることのできる他の材料の例を説明する。

【0197】

半導体素子が有する半導体層を形成する材料は、シリコンやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法で作製される非晶質（アモルファス）半導体、該非晶質半導体を光エネルギーや熱エネルギーを利用して結晶化させた多結晶半導体、或いは微結晶半導体などを用いることができる。半導体層はスパッタリング法、LPCVD法、またはプラズマCVD法等により成膜することができる。

【0198】

微結晶半導体膜は、周波数が数十MHz～数百MHzの高周波プラズマCVD法、または周波数が1GHz以上のマイクロ波プラズマCVD法により形成することができる。代表的には、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などの珪素化合物を水素で希釈して形成することができる。また、これらの珪素化合物を、水素、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの珪素化合物に對して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。

10

【0199】

アモルファス半導体としては、代表的には水素化アモルファスシリコン、結晶性半導体としては代表的にはポリシリコンなどがあげられる。ポリシリコン（多結晶シリコン）には、800以上 のプロセス温度を経て形成されるポリシリコンを主材料として用いた所謂高温ポリシリコンや、600以下のプロセス温度で形成されるポリシリコンを主材料として用いた所謂低温ポリシリコン、また結晶化を促進する元素などを用いて、非晶質シリコンを結晶化させたポリシリコンなどを含んでいる。もちろん、前述したように、微結晶半導体又は半導体層の一部に結晶相を含む半導体を用いることもできる。

20

【0200】

半導体層に、結晶性半導体膜を用いる場合、その結晶性半導体膜の作製方法は、種々の方法（レーザ結晶化法、熱結晶化法、またはニッケルなどの結晶化を助長する元素を用いた熱結晶化法等）を用いれば良い。また、SAS（Semi Amorphous Semiconductor）である微結晶半導体をレーザ照射して結晶化し、結晶性を高めることもできる。結晶化を助長する元素を導入しない場合は、非晶質珪素膜にレーザ光を照射する前に、窒素雰囲気下500で1時間加熱することによって非晶質珪素膜の含有水素濃度を $1 \times 10^{-2}$ atoms/cm<sup>3</sup>以下にまで放出させる。これは水素を多く含んだ非晶質珪素膜にレーザ光を照射すると非晶質珪素膜が破壊されてしまうからである。

30

【0201】

非晶質半導体膜への金属元素の導入の仕方としては、当該金属元素を非晶質半導体膜の表面又はその内部に存在させ得る手法であれば特に限定はなく、例えばスパッタリング法、CVD法、プラズマ処理法（プラズマCVD法も含む）、吸着法、金属塩の溶液を塗布する方法を使用することができる。このうち溶液を用いる方法は簡便であり、金属元素の濃度調整が容易であるという点で有用である。また、このとき非晶質半導体膜の表面の濡れ性を改善し、非晶質半導体膜の表面全体に水溶液を行き渡らせるため、酸素雰囲気中のUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を成膜することが望ましい。

40

【0202】

また、非晶質半導体膜を結晶化し、結晶性半導体膜を形成する結晶化工程で、非晶質半導体膜に結晶化を促進する元素（触媒元素、金属元素とも示す）を添加し、熱処理（550～750で3分～24時間）により結晶化を行ってもよい。結晶化を助長（促進）する元素としては、鉄（Fe）、ニッケル（Ni）、コバルト（Co）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスミウム（Os）、イリジウム（Ir）、白金（Pt）、銅（Cu）及び金（Au）から選ばれた一種又は複数種類を用いること

50

ができる。

【0203】

結晶化を助長する元素を結晶性半導体膜から除去、又は軽減するため、結晶性半導体膜に接して、不純物元素を含む半導体膜を形成し、ゲッタリングシンクとして機能させる。不純物元素としては、n型を付与する不純物元素、p型を付与する不純物元素や希ガス元素などを用いることができ、例えばリン(P)、窒素(N)、ヒ素(As)、アンチモン(Sb)、ビスマス(Bi)、ボロン(B)、ヘリウム(He)、ネオン(Ne)、アルゴン(Argon)、クリプトン(Kr)、キセノン(Xe)から選ばれた一種または複数種を用いることができる。結晶化を促進する元素を含む結晶性半導体膜に、希ガス元素を含む半導体膜を形成し、熱処理(550～750で3分～24時間)を行う。結晶性半導体膜中に含まれる結晶化を促進する元素は、希ガス元素を含む半導体膜中に移動し、結晶性半導体膜中の結晶化を促進する元素は除去、又は軽減される。その後、ゲッタリングシンクとなった希ガス元素を含む半導体膜を除去する。

10

【0204】

非晶質半導体膜の結晶化は、熱処理とレーザ光照射による結晶化を組み合わせてもよく、熱処理やレーザ光照射を単独で、複数回行っても良い。

【0205】

また、結晶性半導体膜を、直接基板にプラズマ法により形成しても良い。また、プラズマ法を用いて、結晶性半導体膜を選択的に基板に形成してもよい。

20

【0206】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0207】

(実施の形態7)

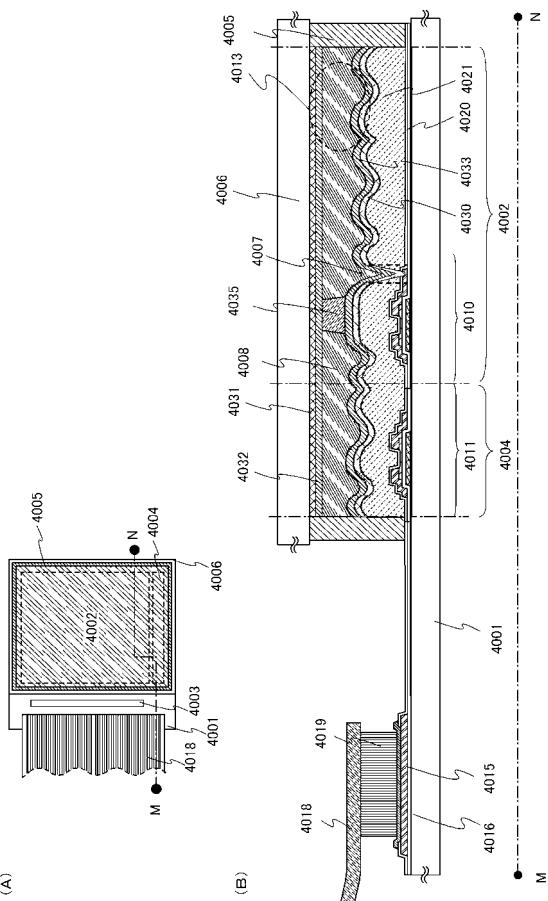

本実施の形態においては、液晶表示装置の一形態に相当する液晶表示装置の外観及び断面について、図5(A)、及び図5(B)を用いて説明する。図5(A)、及び図5(B)は、第1の基板4001上に形成されたトランジスタ4010、トランジスタ4011、及び液晶層4008を含む液晶素子4013を、第2の基板4006との間にシール材4005によって封止した、液晶表示装置の上面図及び断面図に相当する。

30

【0208】

トランジスタ4010、及びトランジスタ4011としては、実施の形態2乃至6のいずれかで示したトランジスタを用いることができる。トランジスタは画素部、さらには駆動回路に用いることができる。トランジスタを駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

【0209】

図5(A)において、第1の基板4001上に設けられた画素部4002及び走査線駆動回路4004を囲むようにして、シール材4005が設けられ、第2の基板4006によって封止されている。図5(A)においては、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体又は多結晶半導体で形成された信号線駆動回路4003が実装されている。また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、FPC(Flexible printed circuit)4018から供給されている。

40

【0210】

また図5(A)においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

【0211】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG(Chip-on-glass)

50

ip On Glass) 方法、ワイヤボンディング方法、或いは TAB ( Tape Automated Bonding ) 方法などを用いることができる。図 5 ( A ) は、COG 方法により信号線駆動回路 4003 、走査線駆動回路 4004 を実装する例である。

【 0212 】

また、液晶表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含む IC 等を実装した状態にあるモジュールとを含む。

【 0213 】

なお、本実施の形態において表示装置とは、画像表示デバイス、表示デバイス、もしくは光源（照明装置含む）を指す。また、コネクター、例えば FPC もしくは TAB テープもしくは TCF が取り付けられたモジュール、TAB テープや TCF の先にプリント配線板が設けられたモジュール、または表示素子に COG 方式により IC ( 集積回路 ) が直接実装されたモジュールも全て表示装置に含むものとする。

10

【 0214 】

また、第 1 の基板 4001 上に設けられた画素部 4002 と、走査線駆動回路 4004 は、トランジスタを複数有しており、実施の形態 2 乃至 6 のいずれかで示したトランジスタを用いることができる。図 5 ( B ) では、画素部 4002 に含まれるトランジスタ 4010 、及び走査線駆動回路 4004 に含まれるトランジスタ 4011 を例示している。

【 0215 】

また、図示しないが、絶縁層上において駆動回路用のトランジスタの半導体層のチャネル形成領域と重なる位置に導電層を設けてもよい。導電層を酸化物半導体層のチャネル形成領域と重なる位置に設けることによって、トランジスタのしきい値電圧の変動量を低減することができる。また、導電層は、電位がトランジスタのゲート電極層と同じでもよいし、異なっていても良く、第 2 のゲート電極層として機能させることもできる。また、導電層の電位が GND 、 0V 、或いはフローティング状態であってもよい。

20

【 0216 】

また、該導電層は外部の電場を遮蔽する、すなわち外部の電場が内部（トランジスタを含む回路部）に作用しないようにする機能（特に静電気に対する静電遮蔽機能）も有する。導電層の遮蔽機能により、静電気などの外部の電場の影響によりトランジスタの電気的な特性が変動することを防止することができる。

30

【 0217 】

図 5 では、接続端子電極 4015 が、画素電極層 4030 と同じ導電膜から形成され、端子電極 4016 は、トランジスタ 4010 のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

【 0218 】

接続端子電極 4015 は、FPC 4018 が有する端子と、異方性導電膜 4019 を介して電気的に接続されている。

【 0219 】

本実施の形態において、液晶表示装置は外光の光を反射することによって表示を行う反射型の液晶表示装置である。よって、少なくとも画素領域において視認側に設けられる基板、電極層や絶縁層は光を透過させる必要がある。よって光が透過する画素領域に存在する基板、絶縁層、電極層などの薄膜はすべて可視光の波長領域の光に対して透光性とする。一方、光を透過する視認側と反対側には反射性を有する電極層や膜などを設ける。

40

【 0220 】

なお、図 5 の液晶表示装置は第 2 の基板 4006 側が視認側である。

【 0221 】

本実施の形態では、共通電極層 4031 は、透光性の導電材料を用いて形成する。例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITO と示す。）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

50

## 【0222】

また、共通電極層4031として、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。

## 【0223】

また、画素電極層4030は、反射性の導電性材料を用いればよく、タンゲステン（W）、モリブデン（Mo）、ジルコニウム（Zr）、ハフニウム（Hf）、バナジウム（V）、ニオブ（Nb）、タンタル（Ta）、クロム（Cr）、コバルト（Co）、ニッケル（Ni）、チタン（Ti）、白金（Pt）、アルミニウム（Al）、銅（Cu）、銀（Ag）等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。

10

## 【0224】

液晶素子4013の液晶層4008として、ゲストホスト液晶を用いる。液晶層4008は実施の形態1で示した液晶層205と同様の材料及び方法により形成すればよい。

## 【0225】

液晶層4008において、画素電極層4030と共に電圧を印加しない場合は、ゲストホスト液晶内に分散している二色性色素であるゲスト分子によって、入射した光は吸収され黒表示となる。一方、画素電極層4030と共に電圧を印加した場合、液晶層4008に電界が形成され、液晶層内のホスト分子、及び二色性色素であるゲスト分子は電界方向に配列し、入射した光は、液晶層4008を透過する。よって、液晶層4008は透明な状態となり、画素電極層4030が反射性を有するので、表示画面では白表示となる。

20

## 【0226】

また、画素電極層4030は、絶縁層4021上に設けられる。また、絶縁層4021は、第1の凹凸、及び第2の凹凸を有しており、画素電極層4030は、絶縁層4021の形状に沿った凹凸を有する。なお、第1の凹凸、及び第2の凹凸が設けられた絶縁層4021は、実施の形態1に示した絶縁層202と同様の材料、及び手法により形成することができる。

30

## 【0227】

なお、図5（B）に示す絶縁層4021、及び画素電極層4030はナノサイズの第2の凹凸を図示してあるが、図面上では認識が難しい。ただし、実施の形態1で示した絶縁層417及び、画素電極層414と同様の材料及び方法により形成すればよい。

## 【0228】

また、画素電極層4030上には配向膜4033が形成され、同様に共通電極層4031上にも配向膜4032が形成されている。

## 【0229】

絶縁層4021はトランジスタの層間膜としても、兼用しているためコンタクトホール4007を形成している。図5（B）において、コンタクトホール4007内にはナノサイズの第2の凹凸は図示していないが、コンタクトホール内にもナノサイズの第2の凹凸を形成しても良い。

40

## 【0230】

本実施の形態に示した液晶表示装置において、第1の凹凸、及び第2の凹凸を有した絶縁層4021上に画素電極層4030が形成されている。したがって、画素電極層4030に入射した光は、液晶層4008側に様々な方向で反射することができる。よって、液晶層4008で効率よく光が散乱され、優れた白表示を行うことができる。

## 【0231】

また、液晶層4008は、ゲストホスト液晶を用いている。ゲストホスト液晶は、入射した光に偏光を行わなくてもよいため、偏光板を設けなくてもよい。

## 【0232】

従って、ゲストホスト液晶を用いた液晶表示装置は、偏光板による光の吸収がなく、より高輝度な明るい表示画面とすることができます。よって、光の利用効率がよいため、低消費

50

電力化にもなる。また、偏光板にかかる工程やコストを削減することができ、より高スループット、低成本を実現できる。よって、トランジスタを有する液晶表示装置にゲストホスト液晶材料を用いることはより効果的である。

【0233】

なお、第1の基板4001、第2の基板4006としては、透光性を有するガラス、プラスチックなどを用いることができる。プラスチックとしては、FRP (Fiberglass-Reinforced Plastics) 板、PVF (ポリビニルフルオライド) フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。

【0234】

また、4035は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、液晶層4008の膜厚(セルギャップ)を制御するために設けられている。なお球状のスペーサを用いていても良い。液晶層4008を用いる液晶表示装置において液晶層の厚さであるセルギャップは5μm以上30μm以下(好ましくは10μm以上20μm以下)とすればよい。

10

【0235】

また、本実施の形態においては、トランジスタの保護膜として機能する絶縁層4020で覆う構成としている。ただし、特に限定はなく、保護膜を形成しない構成としてもよい。

【0236】

なお、保護膜は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。保護膜は、スパッタリング法を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化ガリウム膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、又は窒化酸化アルミニウム膜の単層、又は積層で形成すればよい。

20

【0237】

また、絶縁層4020上に形成する絶縁層4021としては、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(LOW-k材料)、シロキサン系樹脂等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層を形成してもよい。

30

【0238】

積層する絶縁層の形成法は、特に限定されず、その材料に応じて、スパッタリング法、スピニコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ロールコート、カーテンコート、ナイフコート等を用いることができる。

【0239】

また、液晶表示装置において、光学部材(光学基板)などは適宜設けてよい。

【0240】

また、トランジスタは静電気などにより破壊されやすいため、ゲート線またはソース線に對して、駆動回路保護用の保護回路を同一基板上に設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

40

【0241】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0242】

(実施の形態8)

本明細書に開示する液晶表示装置は、さまざまな電子機器に適用することができる。特に本明細書に開示する液晶表示装置は、液晶層にゲストホスト液晶を使用し、ゲスト分子である二色性色素により光を吸収し黒表示を行い、反射性の画素電極層による光散乱によって、白表示を行うために、紙面のような良質な画質を有するので、使用者の目に優しく、電子ペーパーとして好適に適用することができる。電子ペーパーは、情報を表示するもの

50

であればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍（電子ブック）、ポスター、電車などの乗り物の車内広告における表示等に適用することができる。

【0243】

また、他の電子機器としては、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）などに用いてもよい。上記実施の形態で説明した液晶表示装置を具備する電子機器の例について説明する。

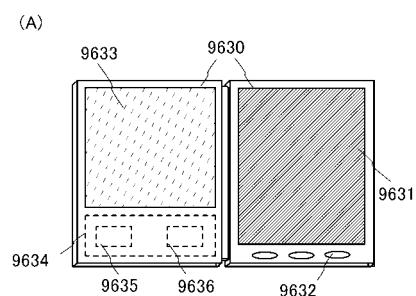

【0244】

図8（A）は電子書籍（E-bookともいう）であり、筐体9630、表示部9631、操作キー9632、太陽電池9633、充放電制御回路9634を有することができる。図8（A）に示した電子書籍は、様々な情報（静止画、動画、テキスト画像など）を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。なお、図8（A）では充放電制御回路9634の一例としてバッテリー9635、DCDCコンバータ（以下、コンバータと略記）9636を有する構成について示している。実施の形態1乃至7のいずれかで示した液晶表示装置を表示部9631に適用することにより、より視認性の良好で高画質な電子書籍とすることができます。よって使用者の目に優しく、疲労感を低減させることができる。

10

【0245】

図8（A）に示す構成とすることにより、表示部9631として反射型の液晶表示装置を用いる場合、比較的明るい状況下での使用も予想され、太陽電池9633による発電、及びバッテリー9635での充電を効率よく行うことができ、好適である。なお太陽電池9633は、筐体9630の空きスペース（表面や裏面）に適宜設けることができるため、効率的なバッテリー9635の充電を行う構成とでき、好適である。なおバッテリー9635としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

20

【0246】

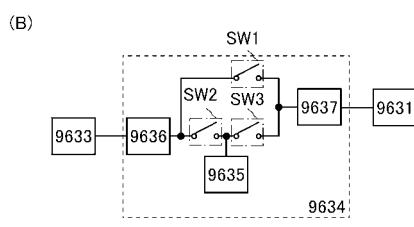

また図8（A）に示す充放電制御回路9634の構成、及び動作について図8（B）にブロック図を示し説明する。図8（B）には、太陽電池9633、バッテリー9635、コンバータ9636、コンバータ9637、スイッチSW1乃至SW3、表示部9631について示しており、バッテリー9635、コンバータ9636、コンバータ9637、スイッチSW1乃至SW3が充放電制御回路9634に対応する箇所となる。

30

【0247】

まず外光により太陽電池9633により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー9635を充電するための電圧となるようコンバータ9636で昇圧または降圧がなされる。そして、表示部9631の動作に太陽電池9633からの電力が用いられる際にはスイッチSW1をオンにし、コンバータ9637で表示部9631に必要な電圧に昇圧または降圧をすることとなる。また、表示部9631での表示を行わない際には、SW1をオフにし、SW2をオンにしてバッテリー9635の充電を行う構成とすればよい。

40

【0248】

次いで外光により太陽電池9633により発電がされない場合の動作の例について説明する。バッテリー9635に蓄電された電力は、スイッチSW3をオンにすることでコンバータ9637により昇圧または降圧がなされる。そして、表示部9631の動作にバッテリー9635からの電力が用いられることとなる。

【0249】

なお太陽電池9633については、充電手段の一例として示したが、他の手段によるバッテリー9635の充電を行う構成であってもよい。また他の充電手段を組み合わせて行う構成としてもよい。

【0250】

図9（A）（B）は、上記実施の形態を適用して形成される液晶表示装置を可携性を有す

50

る電子書籍に適用した例である。図9(A)は、電子書籍を開いた状態であり、図9(B)は電子書籍を閉じた状態である。第1の表示パネル4311、第2の表示パネル4312、第3の表示パネル4313に上記実施の形態を適用して形成される液晶表示装置を用いることができる。本発明の液晶表示装置を適用することにより、より視認性の良好で高画質な電子書籍とすることができます。よって使用者の目に優しく、疲労感を低減させることができる。

#### 【0251】

第1の筐体4305は第1の表示部4301を有する第1の表示パネル4311を有し、第2の筐体4306は操作部4304及び第2の表示部4307を有する第2の表示パネル4312を有し、両面表示型パネルである第3の表示パネル4313は、第3の表示部4302及び第4の表示部4310を有し、第3の表示パネル4313は、第1の表示パネル4311と第2の表示パネル4312の間に挿入されている。第1の筐体4305、第1の表示パネル4311、第3の表示パネル4313、第2の表示パネル4312、及び第2の筐体4306は駆動回路が内部に設けられた綴じ部4308によって接続されている。図9の電子ブックは第1の表示部4301、第2の表示部4307、第3の表示部4302、及び第4の表示部4310の4つの表示画面を有している。

#### 【0252】

第1の筐体4305、第1の表示パネル4311、第3の表示パネル4313、第2の表示パネル4312、及び第2の筐体4306は可撓性を有しており、フレキシビリティが高い。また、第1の筐体4305、第2の筐体4306にプラスチック基板を用い、第3の表示パネル4313に薄いフィルムを用いると、薄型な電子書籍とすることができます。

#### 【0253】

第3の表示パネル4313は第3の表示部4302及び第4の表示部4310を有する両面表示型パネルである。第3の表示パネル4313は、片面射出型の表示パネルを貼り合わせて用いればよい。また、第3の表示パネル4313を省略し、見開きの電子書籍としてもよい。

#### 【0254】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【実施例1】

#### 【0255】

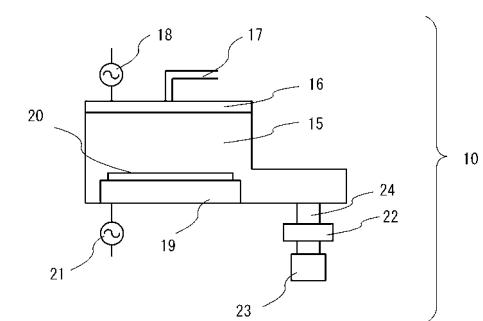

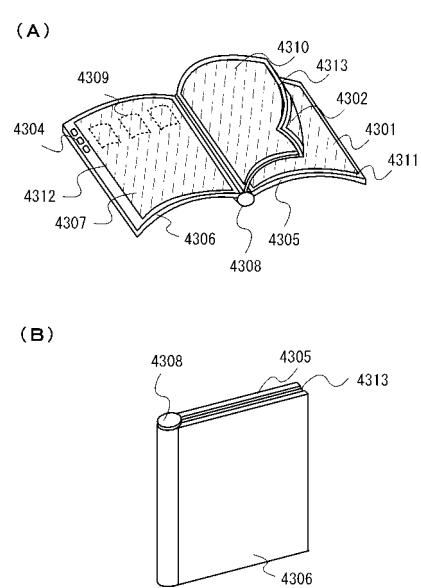

本実施例では、実施の形態1の図2に示したプラズマ装置を用いて、第2の凹凸の形成を行った。以下、図3を用いて詳細な説明を行う。

#### 【0256】

図3は、本実施例で形成した第2の凹凸のSEM(走査型電子顕微鏡、Scanning Electron Microscope)の断面写真である。

#### 【0257】

なお、図3に示す断面写真については、絶縁層30、第1の凹凸31、及び第2の凹凸32が形成されており、実施の形態1に示した絶縁層202、第1の凹凸210、及び第2の凹凸211にそれぞれ対応する。

#### 【0258】

図3を参照すると、絶縁層30に第1の凹凸31、及び第2の凹凸32が形成されていることがわかる。なお、本実例では、第1の凹凸31は感光性の有機樹脂を用いてフォトリソグラフィを用いて形成した。また、第2の凹凸32は、実施の形態1の図2に示したプラズマ装置を用いて酸素ガス雰囲気下にてプラズマ処理を行うことで形成した。

#### 【0259】

以上のように、第1の凹凸31を有する絶縁層30に、酸素ガス雰囲気下にてプラズマ処理を行うことで、第2の凹凸32が形成することが確認された。

#### 【0260】

本実施例は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能であ

10

20

30

40

50

る。

【符号の説明】

【0 2 6 1】

|         |            |    |

|---------|------------|----|

| 1 0     | プラズマ装置     |    |

| 1 1     | 基板供給室      |    |

| 1 2     | ロードロック室    |    |

| 1 3     | 搬送室        |    |

| 1 4     | カセットポート    |    |

| 1 5     | 真空チャンバー    |    |

| 1 6     | I C Pコイル   | 10 |

| 1 7     | ガス流路       |    |

| 1 8     | 高周波電源      |    |

| 1 9     | 基板ステージ     |    |

| 2 0     | 被処理基板      |    |

| 2 1     | 高周波電源      |    |

| 2 2     | 圧力制御弁      |    |

| 2 3     | ドライポンプ     |    |

| 2 4     | 排気口        |    |

| 3 0     | 絶縁層        |    |

| 3 1     | 凹凸         | 20 |

| 3 2     | 凹凸         |    |

| 2 0 0   | 基板         |    |

| 2 0 1   | 基板         |    |

| 2 0 2   | 絶縁層        |    |

| 2 0 3   | 画素電極層      |    |

| 2 0 4   | 共通電極層      |    |

| 2 0 5   | 液晶層        |    |

| 2 0 6   | ネマティック液晶分子 |    |

| 2 0 7   | 二色性色素      |    |

| 2 0 8   | 配向膜        | 30 |

| 2 0 9   | 配向膜        |    |

| 2 1 0   | 凹凸         |    |

| 2 1 1   | 凹凸         |    |

| 4 0 1   | ゲート電極層     |    |

| 4 0 2   | ゲート絶縁層     |    |

| 4 0 3   | 半導体層       |    |

| 4 0 5 a | ソース電極層     |    |

| 4 0 5 b | ドレイン電極層    |    |

| 4 0 7   | 絶縁層        |    |

| 4 0 8   | 容量配線層      | 40 |

| 4 0 9   | 絶縁層        |    |

| 4 1 0   | トランジスタ     |    |

| 4 1 4   | 画素電極層      |    |

| 4 1 7   | 絶縁層        |    |

| 4 2 0   | トランジスタ     |    |

| 4 2 7   | 絶縁層        |    |

| 4 3 0   | トランジスタ     |    |

| 4 3 6 a | 配線層        |    |

| 4 3 6 b | 配線層        |    |

| 4 3 7   | 絶縁層        | 50 |

|         |          |    |

|---------|----------|----|

| 4 4 0   | トランジスタ   |    |

| 4 4 1   | 基板       |    |

| 4 4 2   | 基板       |    |

| 4 4 4   | 液晶層      |    |

| 4 4 8   | 共通電極層    |    |

| 4 4 9   | コンタクトホール |    |

| 4 5 0   | 配向膜      |    |

| 4 5 1   | 配向膜      |    |

| 4 6 0   | トランジスタ   |    |

| 4 7 0   | 凹凸       | 10 |

| 4 8 0   | 凹凸       |    |

| 5 0 5   | 基板       |    |

| 5 0 6   | 保護絶縁層    |    |

| 5 0 7   | ゲート絶縁層   |    |

| 5 1 0   | トランジスタ   |    |

| 5 1 1   | ゲート電極層   |    |

| 5 1 5 a | ソース電極層   |    |

| 5 1 5 b | ドレイン電極層  |    |

| 5 1 6   | 絶縁層      |    |

| 5 3 0   | 酸化物半導体層  | 20 |

| 5 3 1   | 酸化物半導体層  |    |

| 4 0 0 1 | 基板       |    |

| 4 0 0 2 | 画素部      |    |

| 4 0 0 3 | 信号線駆動回路  |    |

| 4 0 0 4 | 走査線駆動回路  |    |

| 4 0 0 5 | シール材     |    |

| 4 0 0 6 | 基板       |    |

| 4 0 0 7 | コンタクトホール |    |

| 4 0 0 8 | 液晶層      |    |

| 4 0 1 0 | トランジスタ   | 30 |

| 4 0 1 1 | トランジスタ   |    |

| 4 0 1 3 | 液晶素子     |    |

| 4 0 1 5 | 接続端子電極   |    |

| 4 0 1 6 | 端子電極     |    |

| 4 0 1 8 | FPC      |    |

| 4 0 1 9 | 異方性導電膜   |    |

| 4 0 2 0 | 絶縁層      |    |

| 4 0 2 1 | 絶縁層      |    |

| 4 0 3 0 | 画素電極層    |    |

| 4 0 3 1 | 共通電極層    | 40 |

| 4 0 3 2 | 配向膜      |    |

| 4 0 3 3 | 配向膜      |    |

| 4 3 0 1 | 表示部      |    |

| 4 3 0 2 | 表示部      |    |

| 4 3 0 4 | 操作部      |    |

| 4 3 0 5 | 筐体       |    |

| 4 3 0 6 | 筐体       |    |

| 4 3 0 7 | 表示部      |    |

| 4 3 0 8 | 綴じ部      |    |

| 4 3 1 0 | 表示部      | 50 |

|         |         |

|---------|---------|

| 4 3 1 1 | 表示パネル   |

| 4 3 1 2 | 表示パネル   |

| 4 3 1 3 | 表示パネル   |

| 9 6 3 0 | 筐体      |

| 9 6 3 1 | 表示部     |

| 9 6 3 2 | 操作キー    |

| 9 6 3 3 | 太陽電池    |

| 9 6 3 4 | 充放電制御回路 |

| 9 6 3 5 | バッテリー   |

| 9 6 3 6 | コンバータ   |

| 9 6 3 7 | コンバータ   |

10

【図1】

【図2】

【 四 4 】

This cross-sectional diagram illustrates a semiconductor device structure. The top layer features a series of recessed contact holes, each labeled with a reference number: 442, 460, 448, 444, 449, 470, 480, and 417. Below these holes, a layer of material is shown with a wavy or undulating pattern, labeled 450. The structure then transitions into a region with a dotted pattern, labeled 451. A vertical line labeled 414 extends downwards from this region. The bottom-most layer is a thick, textured structure labeled 405a. Above this, a thinner layer is labeled 401, and a layer immediately above 401 is labeled 403. A vertical line labeled 405b is positioned between 401 and 403. The bottom-most contact hole, labeled 441, is situated between the layers 401 and 403. The entire structure is bounded by horizontal lines labeled X1 and X2 at the far left and far right respectively.

【 図 5 】

【 図 6 】

【図7】

【図8】

【図9】

【図3】

---

フロントページの続き

(72)発明者 荒川 徹

栃木県栃木市都賀町升塚161-2 アドバンスト フィルム ディバイス インク株式会社内

Fターム(参考) 2H092 GA43 GA48 GA51 GA55 GA59 GA60 JA26 JA33 JA35 JA36

JA40 JB07 JB57 JB58 KA08 KA12 KA19 KB05 KB14 KB22

KB24 KB25 MA04 MA05 MA07 MA13 NA01 QA08