# (10) **DE 602 23 051 T2** 2008.07.24

# Übersetzung der europäischen Patentschrift

(97) EP 1 421 463 B1

(21) Deutsches Aktenzeichen: 602 23 051.9

(86) PCT-Aktenzeichen: PCT/US02/27669

(96) Europäisches Aktenzeichen: 02 773 259.3

(87) PCT-Veröffentlichungs-Nr.: WO 2003/021407

(86) PCT-Anmeldetag: 29.08.2002

(87) Veröffentlichungstag

der PCT-Anmeldung: 13.03.2003

(97) Erstveröffentlichung durch das EPA: 26.05.2004

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **17.10.2007** (47) Veröffentlichungstag im Patentblatt: **24.07.2008**

(30) Unionspriorität:

315655 P 29.08.2001 US

(73) Patentinhaber:

Analog Devices Inc., Norwood, Mass., US

(74) Vertreter:

Kuhnen & Wacker Patent- und Rechtsanwaltsbüro, 85354 Freising

(51) Int Cl.8: **G06F 1/08** (2006.01)

**H03L** 7/08 (2006.01) **H03L** 7/095 (2006.01)

(84) Benannte Vertragsstaaten:

DE, FR, GB

(72) Erfinder:

BIRK, Palle, DK-9260 Gistrup, DK; SOERRNSEN, Joern, DK-9600 Aars, DK

(54) Bezeichnung: ANORDNUNG UND VERFAHREN ZUM SCHNELLEN EINSCHALTEN EINER PHASE-LOCKED LOOP

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelegt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## **Beschreibung**

#### Gebiet der Erfindung

**[0001]** Diese Erfindung betrifft das Gebiet von Phasenregelkreis-(PLL)-Frequenzmultiplizierern und insbesondere Verfahren und eine Vorrichtung zum Reduzieren des Overhead-Phänomens bzw. einer zusätzlichen Zeitanforderung, die mit dem Aktivieren eines Phasenregelkreises durch Bereitstellen eines funktionsfähigen Taktsignals während des Einrastzeitintervalls des PLL in Verbindung steht.

#### Hintergrund der Erfindung

[0002] In vielen Rechensystemen, digitalen Bauelementen etc. werden die verschiedenen Taktsignale, die durch einen Prozessor benötigt werden, häufig mit einem einzelnen Referenztaktsignal synchronisiert und dann auf die entsprechenden logischen Schaltungen, Teilsysteme und Komponenten des Prozessors verteilt. Unter dem Begriff Prozessor versteht man im Allgemeinen eine beliebige Vorrichtung, die logische Operationen, Rechenaufgaben und/oder Steuerfunktionen ausführt. Ein Prozessor kann ein oder mehrere Teilsysteme, Komponenten und/oder andere Prozessoren beinhalten. Ein Prozessor beintypischerweise verschiedene haltet logische und/oder digitale Komponenten, die unter Verwendung eines Taktsignals arbeiten, um Daten zwischenzuspeichern, logische Zustände voranzutreiben und/oder zu sequenzieren, Berechnungen und logische Operationen zu synchronisieren und/oder andere Zeitsteuerungsfunktionen zu ermöglichen.

[0003] Ein Mobiltelefon kann beispielsweise einen Prozessor mit mehreren Teilsystemen oder Komponenten, wie einen digitalen Signalprozessor (DSP), der mit einer hohen Taktfreguenz arbeitet, um rechnerisch intensive und häufig zeitkritische Aufgaben in Echtzeit auszuführen, und einen Mikrocontroller (MCU) beinhalten, der mit einer niedrigeren Taktfrequenz arbeitet, um beispielsweise verschiedene Steuerungsfunktionen auszuführen, Ereignisse zu koordinieren, eine Systemsoftware auszuführen etc. Außerdem können der DSP und der MCU jeweils arbeiten oder unterstützende Komponenten aufweisen, die mit mehreren Taktfrequenzen arbeiten. Die Taktfrequenzanforderung zu einem beliebigen gegebenen Zeitpunkt kann von der rechnerischen Ansprüchen des Prozessors abhängen.

**[0004]** Ein durch einen analogen oder digitalen Phasenregelkreis (PLL) oder Verzögerungsregelkreis (DLL) implementierter Frequenzmultiplizierer wird häufig verwendet, um ein Hochfrequenz-Taktsignal zu erzeugen und dieses mit einem Referenztakt in Phase zu bringen. Das Hochfrequenz-Taktsignal kann dann zugeführt werden, um eine logische Schaltung oder Komponente anzusteuern, einem

Taktverteilungsbaum eines digitalen Bauelements bereitgestellt werden und/oder anderweitig an einen Prozessor verteilt werden, um die Taktungsanforderungen des Systems zu erfüllen. Somit können die Taktfrequenzanforderungen der verschiedenen Komponenten eines Prozessors von einem einzelnen Referenztaktsignal unterstützt und synchronisiert werden.

[0005] Der Begriff "bereitgestellt" beschreibt im Kontext des Bereitstellens eines Taktsignals ein Signal, das nicht deaktiviert, umgangen, ausgesperrt oder anderweitig daran gehindert wird, an die bestimmungsgemäßen logischen Gatter, digitalen Komponenten und/oder einen Schaltungsaufbau etc. angelegt, durch diese empfangen oder für einen Betrieb verwendet zu werden. Im Allgemeinen wird hierin der Begriff getaktete Komponente verwendet, um eine beliebige der vorstehend erwähnten Komponenten zu beschreiben. Ein Taktsignal kann beispielsweise einer Umgehungsauswähleinrichtung, einer Deaktivierungslogik, einem Taktverteilungsbaum etc. bereitgestellt werden, wird jedoch letztlich einer oder mehreren Tiefpegelkomponenten wie logischen Verknüpfungsgliedern, Flipflops etc. bereitgestellt, die einen Takt als Logikpegel, Zeitsteuerungssignal, Signalspeicher etc. benötigen. Diese Tiefpegelkomponenten oder Kollektionen von Tiefpegelkomponenten werden im Allgemeinen als getaktete Komponenten bezeichnet.

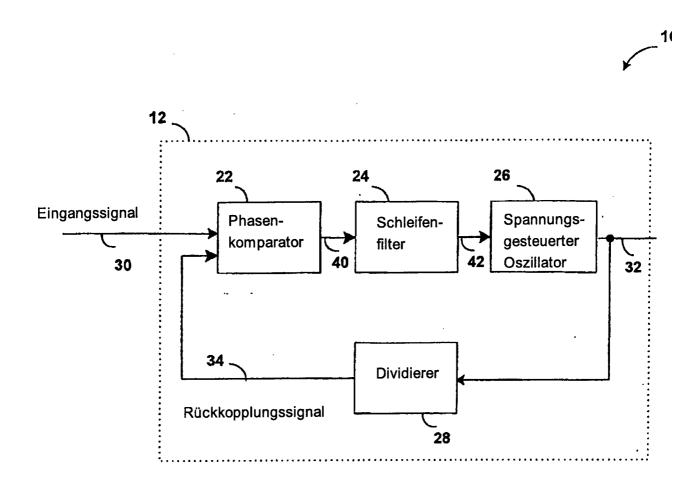

[0006] Fig. 1 stellt ein Blockdiagramm eines herkömmlichen Frequenzmultiplizierers 10 dar, der ein Ausgangstaktsignal aus einem Eingangstaktsignal erzeugt. Der Frequenzmultiplizierer 10 beinhaltet einen PLL 12, der ein Hochfrequenz-Ausgangstaktsignal 32 erzeugt und das Signal mit einem Eingangstaktsignal 30 in Phase bringt.

[0007] Unter dem Begriff Taktsignal oder einfach Takt versteht man im Allgemeinen ein beliebiges analoges oder digitales periodisches Signal und insbesondere ein periodisches Signal, das für ein oder zum Erzeugen von zumindest einem Zeitsteuerungssignal oder einem Logikpegel für eine logische Komponente, digitale Schaltung oder anderweitig (d. h. eine getaktete Komponente) verwendet wird. Ein Taktsignal kann eine beliebige von verschiedenen Wellenformen sein, die Sinuskurven, viereckige Wellen, Pulsfolgen etc. beinhaltet, aber nicht auf diese beschränkt ist. Ein Taktsignal kann beispielsweise ein Signal sein, das letztlich verwendet wird, um den Zustand eines Prozessors voranzutreiben, Daten zwischenzuspeichern, logische Operationen auszuführen etc. Signale wie Schwing-Sinuskurven und Signale von beispielsweise Kristalloszillatoren, aus denen ein oder mehrere Taktsignale entstehen und/oder hergeleitetet werden, gelten ebenfalls als Taktsignale.

[0008] Die PLL 12 beinhaltet einen Phasenkomparator 22, ein Schleifenfilter 24, einen spannungsgesteuerten Oszillator und einen Dividierer 28. Der Phasenkomparator 22 empfängt ein Eingangstaktsignal 30 und ein Rückkopplungstaktsignal 34 und vergleicht die Phase der beiden Signale. Das Eingangstaktsignal 30 kann beispielsweise ein Systemtakt sein, der einen Prozessor mit einem Referenztakt versieht, mit dem die Taktsignale mit höherer Frequenz, die an den Prozessor verteilt sind, synchronisiert werden sollen. Das Rückkopplungssignal 34 ist auf das Ausgangstaktsignal 32 bezogen, wobei es im Wesentlichen die gleiche Phase wie das Ausgangstaktsignal 32 und im Wesentlichen die gleiche Frequenz wie das Eingangstaktsignal 30 aufweist. Der Phasenkomparator 22 stellt ein Phasenfehlersignal 40 proportional zur Phasendifferenz zwischen dem Eingangstaktsignal 30 und dem Rückkopplungstaktsignal 34 bereit.

[0009] Das Schleifenfilter 24 ermöglicht dem Phasenfehlersignal 40 einen Rauschentfernungs- und Glättungsvorgang. Das Schleifenfilter 24 kann beispielsweise ein Tiefpassfilter beinhalten. Zusätzlich verwandelt ein Schleifenfilter 24 das Phasenfehlersignal 40 in ein Signal, das eine Veränderung der Spannung anzeigt, die benötigt wird, um das Ausmaß des Phasenfehlersignals 40 zu reduzieren. Ein Spannungskorrektursignal 42, das durch das Schleifenfilter 24 erzeugt wird, wird dem VCO bereitgestellt, um die Phasendifferenz zwischen dem Eingangstaktsignal 30 und dem Rückkopplungssignal 34 zu korrigieren.

[0010] Ein spannungsgesteuerter Oszillator (VCO) stellt typischerweise einem Oszillator eine Spannung bereit, der ein Signal mit einer Frequenz proportional zu der bereitgestellten Spannung erzeugt. Somit empfängt der VCO 26 ein Spannungskorrektursignal 42 vom Schleifenfilter 24 und passt dementsprechend eine dem Oszillator bereitgestellte Spannung an. Die Frequenz des Ausgangstaktsignals 32 wird dadurch angepasst, um den Phasenfehler zu korrigieren, der durch den Phasenkomparator 22 erfasst wird (d. h. das Ausgangstaktsignal 32 wird mit dem Eingangstaktsignal 30 in Phase gebracht).

[0011] Das Ausgangstaktsignal 32 wird dem Phasenkomparator durch einen Dividierer 28 zurückgeführt. Der Dividierer 28 kann beispielsweise ein Durch-n-dividieren-Zähler sein, der die Frequenz des Ausgangstaktsignals dividiert, um ein Rückkopplungstaktsignal 34 zum Vergleich mit dem Eingangstaktsignal 30 bereitzustellen. Somit wird das Dividiererverhältnis n typischerweise gewählt, dass es mit dem Multipliziererverhältnis übereinstimmt, das durch den VCO erreicht wird, wodurch das Rückkopplungstaktsignal mit einer im Wesentlichen identischen Frequenz wie dem Eingangstaktsignal und mit der im Wesentlichen identischen Phase wie das Aus-

gangstaktsignal bereitgestellt wird.

[0012] Typischerweise liegen verschiedene Verzögerungen vor, die einem Erzeugen eines Ausgangstaktsignals zugeschrieben werden, das mit einem Eingangstaktsignal phasensynchronisiert wird. Insbesondere gibt es ein Zeitintervall, das zum Konvergieren des Phasenregelkreises erforderlich ist (d. h. um das Ausgangstaktsignal mit dem Eingangstaktsignal in Phase zu bringen). Die während des Erreichens einer Phasenrastung eintretende Verzögerung wird häufig als Synchronisations- bzw. Einrastzeit bezeichnet.

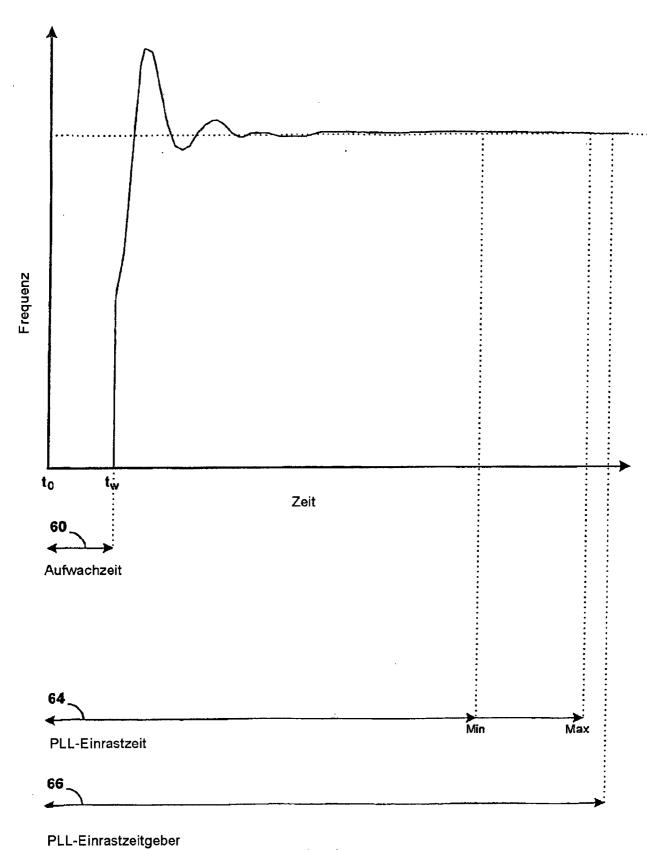

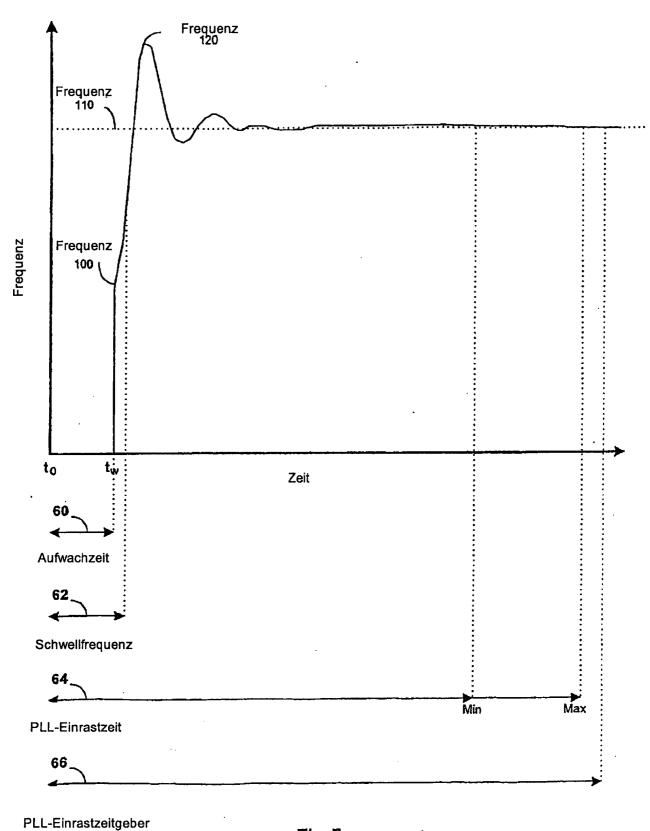

[0013] Fig. 2 stellt ein Zeitsteuerungsdiagramm dar, das Verzögerungen darstellt, die häufig einem Erzeugen eines Ausgangstaktsignals zugeschrieben werden, das mit einem Eingangstaktsignal mittels eines Frequenzmultiplizierers, wie dem, der in Fig. 1 dargestellt ist, phasensynchronisiert wird. Eine Auftragung 5 stellt die Frequenz eines Ausgangstaktsignals (z. B. Ausgangstaktsignal 32) abhängig von der Zeit dar. In Fig. 2 wird davon ausgegangen, dass der PLL zum Zeitpunkt to nicht aktiv ist. Dem PLL wird beispielsweise kein Eingangstaktsignal bereitgestellt, der VCO wird nicht aktiviert und es wird kein Ausgangstaktsignal erzeugt. In anderen Worten bezeichnet der Zeitpunkt to den Moment, wenn erstmals gewünscht wird, dass ein Eingangstakt dem Frequenzmultiplizierer zugeführt wird und der VCO hochgefahren werden soll, d. h., wenn gewünscht wird, dass der PLL aktiviert werden soll.

[0014] Ein endlicher Zeitbetrag kann erforderlich sein, bis dem Phasenkomparator des PLL ein stabiler Eingangstakt bereitgestellt wird. Diese Zeit ist Teil eines Intervalls, das als Aufwachzeit bezeichnet wird und als Intervall 60 bezeichnet wird. Unterschiedliche PLL- oder DLL-Implementierungen können andere Verzögerungen aufweisen, die der Aufwachzeit zugeschrieben sind. Im PLL von Fig. 1 kann beispielsweise eine Verzögerung vorliegen, die einer Aktivierung des VCO zugeschrieben ist, um mit der Bereitstellung einer Spannung zum Oszillator beginnen zu können. Im Allgemeinen bezieht sich die Aufwachzeit auf das Intervall der Zeit, das der Aktivierung der verschiedenen Signale und/oder Komponenten des PLL zugeschrieben ist. Insbesondere bezieht sich die Aufwachzeit auf das Intervall der Zeit zwischen dem Moment, wenn gewünscht wird, ein Ausgangstaktsignal zu erzeugen, und der Zeit, wenn der Signalgenerator das erste Mal ein Signal ausgibt.

[0015] Zusätzlich können Verzögerungen vorliegen, die der Zeit zugeschrieben werden, die der PLL benötigt, um eine Phasenrastung zwischen einem Eingangs- und einem Ausgangstaktsignal zu erreichen. Diese Verzögerungen sind als Zeitintervalle 64 und 66 angezeigt, die jeweils als PLL-Einrastzeit und als PLL-Einrastzeitgeber bezeichnet werden. Ein Zeitin-

tervall **64** zeigt die tatsächliche Zeit an, die erforderlich ist, um eine Phasenrastung zwischen einem Eingangstaktsignal und dem Ausgangstaktsignal zu erreichen. Die präzise Erfassung, wann der PLL effektiv eingerastet ist, gestaltet sich jedoch häufig schwierig. Um die Sache noch zu verkomplizieren, kann die tatsächliche Einrastzeit als eine Funktion des gewünschten Frequenzanstiegs des Multiplizierers, des Betrags des Rauschens des Eingangstaktsignals etc. variieren. Somit kann ein gewisses Maß an Ungewissheit bei der Prognose der Einrastzeit einer PLL vorliegen.

[0016] Um diese zum Erfassen und/oder Prognostizieren der tatsächlichen Einrastzeit gehörige Ungewissheit zu bekämpfen, kann ein Einrastzeitgeber verwendet werden, um ein Intervall der Zeit, das größer oder gleich der im ungünstigsten Fall vorliegenden Einrastzeit des PLLs ist, aufzuzeichnen. Der Einrastzeitgeber beginnt rückwärts zu zählen, wenn der PLL zunächst aktiviert wird. Typischerweise gilt der PLL erst dann als eingerastet und stabil, wenn der Einrastzeitgeber abgelaufen ist. Dementsprechend wird die Latenz eines Frequenzmultiplizierers häufig durch die im Einrastzeitgeber aufgezeichnete Verzögerung (z. B. Intervall 60) eingeschränkt. Unter dem Begriff Latenz versteht man im Allgemeinen ein Intervall der Zeit, das verstreicht, bevor ein operatives Taktsignal von einem Frequenzmultiplizierer ausgegeben wird.

[0017] Ein operatives Taktsignal bezieht sich auf ein Taktsignal, das einer getakteten Komponente bereitgestellt werden kann, um dessen bestimmungsgemäße Funktion auszuführen. Im Allgemeinen liefert ein operatives Taktsignal ein brauchbares Zeitsteuerungsreferenz- und/oder Logiksignal so dass eine brauchbare Berechnung und/oder Verarbeitung ohne Datenverlust oder andere nachträgliche Effekte ausgeführt werden kann. Ein operatives Taktsignal kann beispielsweise ein Taktsignal sein, dass ausreicht, um einen Prozessor voranzutreiben, Daten zwischenzuspeichern, logische Ereignisse zu synchronisieren und/oder andere logische Operationen auszuführen, die ein Taktsignal benötigen, ohne dabei außerhalb der Toleranzen der getakteten Komponenten zu arbeiten und ohne zu bewirken, dass die getakteten Komponenten fehlerhaft arbeiten.

**[0018]** Es sind verschiedene Verfahren vorgeschlagen worden, um die Latenz eines Frequenzmultiplizierers zu verringern. Diese Verfahren konzentrieren sich jedoch häufig auf das Reduzieren der Einrastzeit des Phasenregelkreises und folglich auf ein Reduzieren der Verzögerung, die der Einrastzeitgeber benötigt, um im ungünstigsten Fall vorliegende die Einrastzeit zu berücksichtigen.

[0019] In der EP 895358 ist ein Taktgenerator offenbart, bei dem der PLL zwei Operationsmodi aufweist,

nämlich 1) einen breiten Bandbreiten-(hohen Verstärkungs-)Modus, so dass der PLL sich der Zielfrequenz rasch annähern kann, und 2) einen Schmalbandmodus, so dass der PLL auf die Zielfrequenz einrasten kann. Der Betrieb im Breitbandmodus kann zu Frequenzüberschwingungen führen. Um dies zu verhindern, verwendet das System in EP 895358 einen Dividierer, um einen Takt zu erzeugen. Während des Hochfahrens wird ein Taktsignal zu einer steuernden CPU gehemmt, bis eine Steuerungsschaltung innerhalb des PLL bestimmt, dass der PLL bereit ist, vom breiten Bandbreiten- zum schmalen Bandbreitenmodus zu schalten. Erst dann ist die CPU aktiviert. Gleichzeitig wird ein Zähler/Zeitgeber initiiert, um zu behindern, dass der Dividierer auf "Teile durch 1" geschaltet wird, bis die Zeitspanne, die durch den Zähler/Zeitgeber definiert ist, verstrichen ist.

## Kurzfassung der Erfindung

[0020] Die Anmelderin hat festgestellt, dass die durch Verfahren zum Reduzieren der Frequenzmultiplizierer-Einrastzeit erhaltene Latenz möglicherweise immer noch den Nachteil eines erheblichen Verlustes der Verarbeitungszeit und des Leistungsverbrauchs aufweist, während das System darauf wartet, dass der Frequenzmultiplizierer eine Phasenrastung erreicht. Zusätzlich können gewisse Verarbeitungssituationen einen Frequenzmultiplizierer voraussetzen, der eine Latenz aufweist, die geringer ist als die, die durch Verfahren zum Reduzieren der Einrastzeit erhalten wird.

**[0021]** Gemäß einem ersten Aspekt der vorliegenden Erfindung wird ein Verfahren gemäß Anspruch 1 geschaffen.

**[0022]** Gemäß einem zweiten Aspekt der vorliegenden Erfindung wird ein Frequenzmultiplizierer gemäß Anspruch 4 geschaffen.

## Kurzbeschreibung der Zeichnung

**[0023]** Fig. 1 stellt ein Blockdiagramm eines Phasenregelkreis-(PLL)-Frequenzmultiplizierers dar;

**[0024]** Fig. 2 stellt ein Zeitsteuerungsdiagramm von Verzögerungen dar, die einem Aktivieren und Erhalten einer Phasenrastung im PLL-Frequenzmultiplizierer von Fig. 1 zugeschrieben sind;

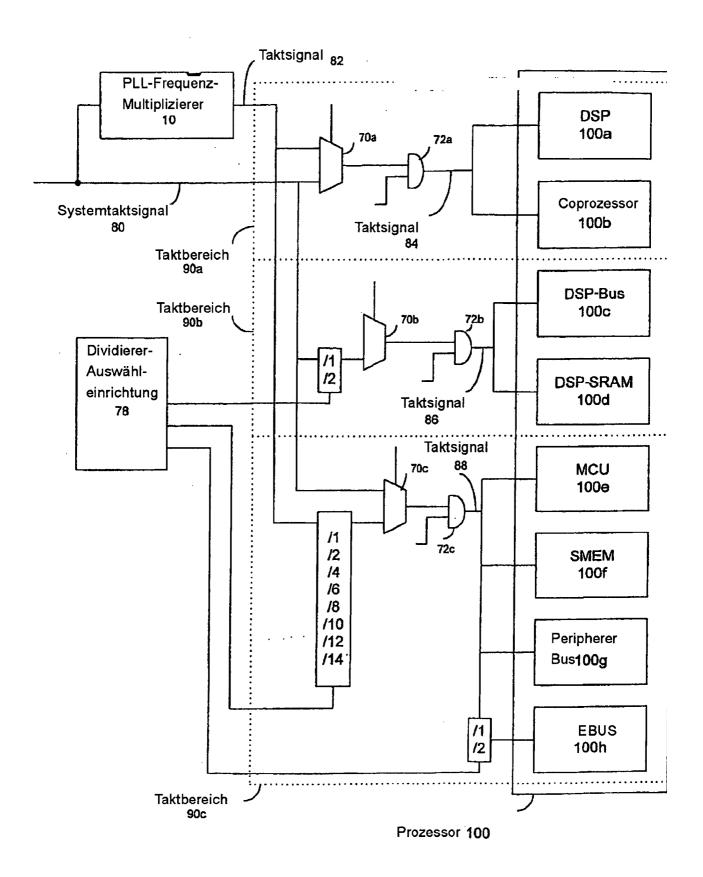

[0025] Fig. 3 stellt ein Taktungsschema und eine Steuerung für einen Prozessor dar, der einen PLL-Frequenzmultiplizierer beinhaltet;

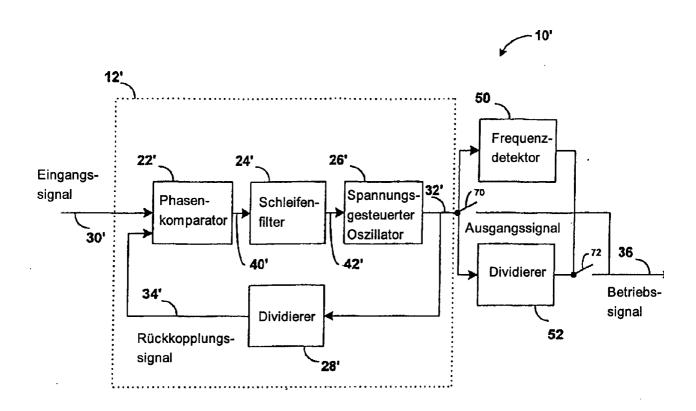

**[0026]** Fig. 4 stellt einen PLL-Frequenzmultiplizierer mit einer reduzierten Latenz gemäß einer Ausführungsform der vorliegenden Erfindung dar;

[0027] Fig. 5 stellt ein Zeitsteuerungsdiagramm von

Verzögerungen dar, die einem Aktivieren und Erreichen einer Phasenrastung zugeschrieben sind, und der reduzierten Latenz des PLL-Frequenzmultiplizierers, der in Fig. 4 gezeigt ist; und

**[0028]** Fig. 6 stellt einen PLL-Frequenzmultiplizierer mit einer reduzierten Latenz gemäß einer anderen Ausführungsform der vorliegenden Erfindung dar.

#### Ausführliche Beschreibung

**[0029]** In vielen Geräten, insbesondere batteriebetriebenen Geräten wie Mobiltelefonen, Laptop-Computern, persönlichen digitalen Assistenten (PDAs) und anderen tragbaren Geräten kann sich der Leistungsverbrauch negativ auf die Zeit auswirken, während diese Geräte betrieben werden können, bevor sie eine erneute Aufladung oder eine Wechselstromquelle benötigen.

**[0030]** Die Anmelderin hat erkannt, dass der Leistungsverbrauch eines Geräts auf das Quadrat der Spannung bezogen ist, die dem Prozessor des Geräts zugeführt wird, und proportional zur Frequenz ist, mit der der Prozessor arbeitet. Der Leistungsverbrauch eines Geräts kann wie folgt ausgedrückt werden:

$$P_D = cV^2F$$

(Gleichung 1)

wenn

- V = die dem Prozessor zugeführte Spannung (d. h. die Differenz zwischen Vdd und Gnd)

- F = die Frequenz (z. B. die Taktfrequenz eines Prozessors)

- eine Konstante, die durch die bei V und F arbeitenden Schaltungen bestimmt wird.

[0031] Zusätzlich hat die Anmelderin festgestellt, dass die zum Betreiben des Prozessors notwendige Spannung eine Funktion der Taktfrequenz sein kann, die einem Prozessor bereitgestellt wird. Dementsprechend besteht eine Möglichkeit zum Reduzieren des Leistungsverbrauchs darin, die dem Prozessor zugeführte Frequenz dynamisch an die minimale Frequenz anzupassen, die erforderlich ist, um die rechnerischen und/oder auf die Verarbeitung bezogenen Anforderungen des Prozessors zu erfüllen.

[0032] Das Systemtaktungsschema, das in Fig. 3 dargestellt ist, wird herangezogen, um verschieden Verarbeitungssituationen zu veranschaulichen, die in einem beispielhaften Prozessor entstehen können. Ein Prozessor kann ein Systemtaktungsschema ähnlich dem Schema aufweisen, das in Fig. 3 dargestellt ist. Ein PLL-Multiplizierer 10 empfängt als Eingabe ein Systemtaktsignal 80 und gibt ein Hochfrequenztaktsignal 82 aus. Das Hochfrequenztaktsignal kann verschiedenen Prozessorkomponenten bereitgestellt

werden, die innerhalb von drei dargestellten Taktbereichen arbeiten: Taktbereich **90a**, Taktbereich **90b** und Taktbereich **90c**.

[0033] Der Taktbereich 90 kann beispielsweise einem digitalen Signalprozessor (DSP) 100a und einem dedizierten DSP-Coprozessor 100b ein Taktsignal 84 bereitstellen. Die Frequenz eines Taktsignals 84 (d. h. die Frequenz des Takts, der den Komponenten im Taktbereich 90a bereitgestellt wird) wird durch einen Multiplexer 70a und ein UND-Glied 72a bestimmt. Der Multiplexer 70a wählt entweder das Hochfrequenz-Taktsignal 82 oder das Systemtaktsignal 80 zur Verteilung an die verschiedenen getakteten Komponenten, die innerhalb des Taktbereichs 90a arbeiten, aus. Das UND-Glied 72a stellt entweder das Taktsignal bereit, das durch den Multiplexer 70a ausgewählt worden ist, oder unterdrückt das Taktsignal, wodurch die Taktbäume (nicht gezeigt) deaktiviert werden, die ein Taktsignal 84 an die getakteten Komponenten des DSP und des Coprozessors verteilen.

[0034] Desgleichen stellt der Taktbereich 90b beispielsweise für den dedizierten Bus (DSP-Bus 100c), der durch das DSP-Teilsystem verwendet wird, um Daten auszutauschen, Steuersignale zu übertragen etc., und für einen dedizierten Speicher (DSP-SRAM 100d) wie einem Cache-Speicher oder Notizspeicher ein Taktsignal 86 bereit. Der Multiplexer 70b wählt entweder das Hochfrequenz-Taktsignal oder den Systemtakt aus, und das UND-Glied aktiviert oder deaktiviert das Taktsignal, das durch den Multiplexer bereitgestellt wird. Zusätzlich ermöglichen die Dividierer 74b dem Hochfrequenz-Taktsignal 82, in seiner Frequenz reduziert zu werden (z. B. durch einen Faktor 2), wenn das Hochfrequenzsignal ausgewählt wird.

[0035] Der Taktbereich 90c stellt für verschiedene andere beispielhafte Teilsysteme und Komponenten des Prozessors 100 ein Taktsignal 88 bereit. Im Besonderen arbeiten im Taktbereich 90c ein Microcontroller (MCU) 100e, ein Systemspeicher 100f, ein Peripheriebus 100g und ein externer Bus 100h. Dividierer 74c ermöglichen dem Hochfrequenz-Taktsignal 82, in seiner Frequenz um einen Faktor von 2, 4, 6, 8, 10, 12 oder 14 reduziert zu werden, bevor es einem Multiplexer 74c zur Auswahl oder Umgehung in der vorstehend in Verbindung mit den Taktbereichen 90a und 90b beschriebenen Weise bereitgestellt wird.

[0036] Der Prozessor 100 kann eine Anzahl von Betriebsmodi aufweisen, wobei eine oder mehrere der Komponenten sich in einem inaktiven Zustand befinden und/oder ein oder mehrere Taktbereiche für den Betrieb nicht benötigt werden. Man nehme beispielsweise ein Mobiltelefon, das einen Prozessor 100 beinhaltet. Wenn das Mobiltelefon eingeschaltet ist, jedoch nicht betrieben wird (z. B. im Bereitschaftsmo-

# DE 602 23 051 T2 2008.07.24

dus), behält das Mobiltelefon den Kontakt mit einer Basisstation in einer Zelle bei, in der es sich derzeit befindet. Die Basisstation sendet in periodischen Abständen (z. B. alle zwei Sekunden) an alle Mobiltelefone in dieser Zellen Informationen, ob ein Anruf empfangen worden ist und ob das Telefon in eine Rufbetriebsmodus übergehen soll. Den als Sendefunkrufkanal bekannten Funkrufkanal muss das Mobiltelefon überwachen, um herauszufinden, ob es einen Anruf empfangen hat oder nicht.

[0037] Es ist jedoch eine sehr geringe Verarbeitungsleistung notwendig, um die Informationen vom Funkrufkanal zu erhalten. Somit setzt der Prozessor möglicherweise nur voraus, dass der Systemtakt während der Erreichens des Funkrufkanals in Betrieb ist. Im Gegensatz dazu kann der DSP benötigt werden, um diese Informationen zu verarbeiten, sobald sie in das Mobiltelefon verbracht worden sind (z. B. in einem Pufferspeicher gespeichert worden sind), um zu bestimmen, ob ein Anruf getätigt worden ist oder nicht. Für den Großteil dieses Betriebsmodus ist der DSP jedoch nicht erforderlich.

[0038] Somit kann es wünschenswert sein, den PLL zu deaktivieren, wenn die rechnerischen Anforderungen des Prozessors diesen nicht benötigen, beispielsweise wenn der DSP sich in einem inaktiven Zustand befindet. Indem der DSP in einen inaktiven Zustand versetzt wird, kann das Hochfrequenztaktsignal deaktiviert werden (d. h. der Frequenzmultiplizierer kann in den Schlafmodus versetzt oder deaktiviert werden). Wenn jedoch die Verarbeitungsleistung des DSP erneut benötigt wird, z. B., um die vom Funkrufkanal erhaltenen Informationen zu verarbeiten, muss der PLL aktiviert werden, um die notwendigen Taktfrequenzen bereitzustellen, die durch die erhöhten Anforderungen an dem Prozessor notwendig geworden sind.

**[0039]** Dem Aktivieren des Frequenzmultiplizierers wird jedoch ein Overhead-Phänomen zugeschrieben, das auf die Latenz des PLL bezogen ist. Insbesondere während des Einrastzeitintervalls eines PLL wird zwar Leistung verbraucht, jedoch keine rechnerische Arbeit erledigt. Der Verlust der effektiven Verarbeitungszeit, der dem Aktivieren des Frequenzmultiplizierers zugeschrieben wird, kann dazu führen, dass es bevorzugt wird und, unter gewissen Umständen, auch erforderlich wird, dass der Frequenzmultiplizierer, trotz des zusätzlichen Verbrauchs der Leistung, aktiv bleibt.

[0040] Der Begriff "Aktivieren eines Frequenzmultiplizierers" wird verwendet, um die Vorgänge zu beschreiben, die in den Anstieg der Frequenz eines Ausgangstaktsignals des Frequenzmultiplizierers involviert sind. Sowohl der Vorgang des Aktivierens eines Frequenzmultiplizierers aus einem Schlaf- oder deaktivierten Zustand als auch des Erhöhens des

Multipliziererverhältnisses des PLL werden als Aktivieren des Frequenzmultiplizierers betrachtet. Das dem Aktivieren eines PLL zugeschriebene Overhead-Phänomen kann sowohl als eine Zeitkomponente als auch eine Leistungskomponenten aufweisend betrachtet werden.

[0041] Die Anmelderin hat erkannt, dass es möglicherweise nicht notwendig ist, eine Phasenrastung zwischen einem Eingangstaktsignal und einem Ausgangstaktsignal zu erreichen, bevor das Ausgangstaktsignal als operativ gelten kann. Insbesondere hat die Anmelderin festgestellt, dass es für das Ausgangstaktsignal ausreichend sein kann, eine vorbestimmte minimale Frequenz zu erhalten, und dass das Ausgangstaktsignal eine vorbestimmte maximale Frequenz nicht erreichen soll, damit der Ausgangstakt als operativ erachtet wird. Die minimalen und maximalen Frequenzen können durch Kennlinien der getakteten Komponenten bestimmt werden, denen das Ausgangstaktsignal bereitgestellt wird.

**[0042]** Wenn z. B. das Ausgangstaktsignal ein Takt ist, der einen Prozessor ansteuert, muss das Taktsignal möglicherweise eine gewisse minimale Frequenz erreichen, die in der Lage ist, den Prozessor voranzutreiben, ohne dass es zu Überschneidungen mit der Zeitsteuerung kommt. Zusätzlich ist es für das Ausgangstaktsignal möglicherweise notwendig, dass es unter der durch den Prozessor unterstützten maximalen Frequenz bleibt, um einen korrekten Betrieb sicherzustellen.

[0043] In einer Ausführungsform gemäß der vorliegenden Erfindung wird das Overhead-Phänomen des Aktivierens eines Frequenzmultiplizierers reduziert, indem ein operatives Taktsignal während des Einrastzeitintervalls des Frequenzmultiplizierers bereitgestellt wird. Insbesondere wird die Latenz des Frequenzmultiplizierers auf einen Wert, der im Wesentlichen gleich der Aufwachzeit des Frequenzmultiplizierers ist, reduziert. Somit kann eine rechnerische Arbeit während einer Einrastzeit erreicht werden, und die effektive Verarbeitungszeit während einer Aktivierung des Frequenzmultiplizierers wird verlängert.

[0044] Nachstehend erfolgt eine ausführliche Beschreibung der verschiedenen Konzepte, die auf die Verfahren und die Vorrichtung gemäß der vorliegenden Erfindung bezogen sind, sowie der Ausführungsformen derselben. Es wird darauf hingewiesen, dass verschiedene Aspekte der Erfindung, die vorstehend erörtert wurden und weiter unter kurz dargestellt werden, mittels einer beliebigen von zahlreichen Möglichkeiten implementiert werden können, da die Erfindung nicht auf eine spezielle Art der Implementierung beschränkt ist. Beispiele einer spezifischen Implementierung sind nur zu Darstellungszwecken angeführt.

[0045] Der nachstehend beschriebene PLL-Frequenzmultiplizierer wird beispielsweise zur Darstellung von verschiedenen Aspekten der vorliegenden Erfindung verwendet. Das Gebiet der Frequenzmultiplizierer beinhaltet jedoch zahlreiche und weitrechende Variationen und Implementierungen. Es wird darauf hingewiesen, dass die vorliegende Erfindung nicht durch irgendeine spezielle Implementierung eines Frequenzmultiplizierers begrenzt ist und dass somit ein beliebiger Frequenzmultiplizierer mit einem endlichen Zeitintervall, das zum Synchronisieren eines Ausgangstaktsignals mit einem Eingangstaktsignal erforderlich ist, als im Schutzumfang der Erfindung befindlich betrachtet werden kann.

[0046] Der Begriff Frequenzmultiplizierer wird auf eine beliebige Komponente angewendet, die ein Ausgangstaktsignal bereitstellt, das mit einem Eingangstaktsignal synchronisiert wird, wobei das Ausgangstaktsignal eine Frequenz aufweist, die größer ist als das Eingangstaktsignal. Im Allgemeinen beinhaltet ein Frequenzmultiplizierer einen Signalgenerator, um ein Signal mit einer gewünschten Frequenz zu erzeugen, ein Verfahren zum Vergleichen des erzeugten Signals mit einem Eingangstaktsignal und ein Verfahren zum Synchronisieren des erzeugten Signals mit dem Eingangstaktsignal basierend auf dem Vergleich. Wenn der Vergleich auf einer Phase basiert, wird der Begriff Phasenregelkreis (PLL) zur Beschreibung eines solchen Frequenzmultiplizierers herangezogen.

[0047] Ein Phasenvergleich kann durch eine beliebige Anzahl von Möglichkeiten wie Edge-Tracking bzw. Flankenüberwachung (z. B. Vergleichen der Anstiegs- und/oder Abfallflanken der Taktsignale), Signalnulldurchgänge, Nullen in der Signalableitung etc. realisiert werden Zusätzlich kann eine Phasenrastung durch ein beliebiges von verschiedenen Verfahren wie dem Variieren der Frequenz des Ausgangstaktsignals gemäß dem Phasenvergleich, Verzögern des Ausgangstaktsignals gemäß dem Phasenfehler etc. erreicht werden.

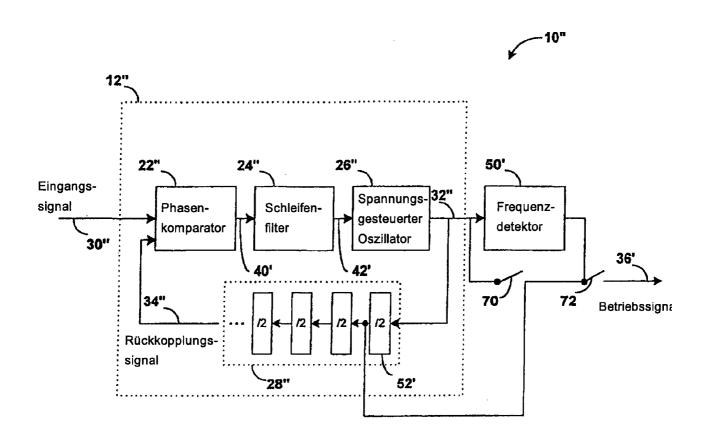

[0048] Fig. 4 stellt eine Ausführungsform eines Frequenzmultiplizierers gemäß der vorliegenden Erfindung dar. Ein Frequenzmultiplizierer 10' beinhaltet einen Phasenregelkreis 12'. Der Phasenregelkreis arbeitet in einer Weise ähnlich dem PLL 12, der in Verbindung mit Fig. 1 beschrieben ist. Insbesondere beinhaltet der PLL 12' einen Phasenkomparator 22', der ein Phasenfehlersignal 40' bereitstellt, das die Phasendifferenz zwischen einem Eingangstaktsignal 30' und dem Rückkopplungstaktsignal 34' anzeigt. Ein Schleifenfilter 24' empfängt das Phasenfehlersignal 40' und liefert ein Spannungskorrektursignal 42'. Der VCO 26' empfängt ein Korrektursignal 42' und passt die Spannung, die dem Oszillator bereitgestellt wird, an, um ein Ausgangstaktsignal bereitzustellen, das dazu tendiert, das Ausmaß des Phasenfehlersignals **40'** zu reduzieren. Der Dividierer **28'** dividiert das Ausgangstaktsignal, um das Rückkopplungstaktsignal **34'** bereitzustellen, das eine Frequenz aufweist, die im Wesentlichen mit der des Eingangstaktsignals **30'** identisch ist, und eine Phase aufweist, die im Wesentlichen mit der des Ausgangstaktsignals **32'** identisch ist.

[0049] Darüber hinaus beinhaltet ein Frequenzmultiplizierer 12 einen Frequenzdetektor 50 und einen Dividierer 52. Das Ausgangstaktsignal 32', das durch den VCO 26' erzeugt wird, wird sowohl einem Detektor 50 als auch einem Dividierer 52 bereitgestellt. Der Detektor 50 und der Dividierer 52 stellen sicher, dass ein Taktsignal, das dem Prozessor bereitgestellt wird, keine Frequenzen enthält, die bewirken können, dass der Prozessor fehlerhaft arbeitet, oder einen Datenverlust verursachen, d. h., der Detektor 50 und der Dividierer 52 stellen ein operatives Taktsignal 36 bereit.

[0050] Nach dem Aufwachintervall (z. B. Intervall 60 in Fig. 2) und bevor das Ausgangstaktsignal mit dem Eingangstaktsignal in Phase eingerastet wird, kann das Ausgangstaktsignal für Frequenzen anfällig sein, die über jene hinausgehen, die von den getakteten Komponenten, die das Taktsignal empfangen, erwartet werden. Das Ausgangssignal kann beispielsweise über einer Zielfrequenz liegende Frequenzen erleben. Die Zielfrequenz bezieht sich auf die bestimmungsgemäße Frequenz, die durch den Frequenzmultiplizierer erhalten wird. Insbesondere handelt es sich bei der Zielfrequenz um die Frequenz des Signals, das durch den VCO erzeugt wird, nachdem der PLL eingerastet ist.

**[0051]** Darüber hinaus kann das Ausgangstaktsignal, kurz nachdem der VCO aktiviert worden ist (d. h. am Ende des Aufwachintervalls), Frequenzen erleben, die unter jenen einer Schwellfrequenz liegen, die von den getakteten Komponenten benötigt wird, die das Taktsignal empfangen. Somit sollten die Frequenzen, die außerhalb eines Frequenzbereichs liegen, der durch die Schwellfrequenz und die Zielfrequenz definiert ist, unterdrückt werden, um ein operatives Taktsignal bereitzustellen.

**[0052]** Fig. 5 stellt eine Frequenz-/Zeitdiagramm-kennlinie des Aktivierungsintervalls von PLLs dar, die nicht kritisch gedämpft werden. Wenn die Latenz eines PLL von Bedeutung ist, wird der PLL häufig nicht kritisch gedämpft, d. h. der PLL wird nicht gedämpft, um ein Überschwingen der Zielfrequenz zu verhindern. Typischerweise weist ein gedämpfter PLL eine verlängerte Einrastzeit auf und ist möglicherweise für viele Anwendungen, bei denen das PLL-Aktivierungs-Overhead von Bedeutung ist, nicht geeignet.

[0053] Die Zielfrequenz (d. h. die Frequenz, die durch den Frequenzmultiplizierer erreicht werden

soll) des Ausgangstaktsignals des PLL ist durch die gestrichelte Linie auf der Frequenzachse als Frequenz **110** gekennzeichnet. Die Zielfrequenz kann beispielsweise der hohe Frequenztakt sein, der einem DSP bereitgestellt wird, wie in <u>Fig. 3</u> dargestellt ist.

[0054] Nachdem der VCO aktiviert worden ist (d. h. zum Zeitpunkt t), erreicht das Ausgangstaktsignal nahezu unmittelbar eine Frequenz 100, die durch die vertikale Linie zum Zeitpunkt  $t_{\rm w}$  schematisch dargestellt ist. Wie dargestellt ist, nimmt die Frequenz des Ausgangstaktsignals zu, und der PLL tendiert während des Einrastzeitintervalls zum Überschwingen der Zielfrequenz. Somit kann das Ausgangstaktsignal Frequenzen bis zu einer Frequenz 120 erfahren. Das Taktsignal oszilliert dann in einer Frequenz um die Zielfrequenz herum, bis es gegen die Zielfrequenz konvergiert, während der PLL einrastet.

[0055] Frequenzen, die die Zielfrequenz 110 überschreiten, falls diese z. B. einem Prozessor bereitgestellt werden, können bewirken, dass der Prozessor fehlerhaft arbeitet. Dies kann zu korrumpierten Daten oder Datenverlust, einer fehlerhaften Zeitsteuerung oder Synchronisation führen oder anderweitige schadhafte Effekte auf den Betrieb des Prozessors ausüben. Wenn somit das Taktsignal, das dem Prozessor während des Einrastzeitintervalls bereitgestellt wird, als operativ betrachtet wird, müssen Frequenzen, die die Zielfrequenz überschreiten, möglicherweise unterdrückt werden.

[0056] Um zu verhindern, dass über der Zielfrequenz liegende Frequenzen an die getakteten Komponenten des Prozessors angelegt werden, wird das Ausgangstaktsignal 32' in der in Fig. 3 dargestellten Ausführungsform dem Dividierer 52 bereitgestellt. Der Dividierer 52 dividiert die Frequenz des Ausgangstaktsignals durch N, um sicherzustellen, dass die getakteten Komponenten des Prozessor für einen Datenverlust oder einen fehlerhaften Betrieb aufgrund von Taktsignalfrequenzen, die den maximalen Wert überschreiten, mit dem die getakteten Komponenten arbeiten sollten, nicht anfällig sind.

[0057] Der Dividierer 52 kann beispielsweise ein Durch-2-dividieren-Zähler sein. Die Erfindung ist jedoch nicht auf die Wahl eines speziellen Dividiererverhältnisses beschränkt. Entwurfsüberlegungen und Eigenschaften des PLL können die Wahl von N für eine spezielle Implementierung beeinflussen. Durch die Wahl von N sollte jedoch verhindert werden, dass das Taktsignal, das dem Prozessor bereitgestellt wird, Frequenzen erlebt, die bewirken können, dass der Prozessor fehlerhaft arbeitet, d. h., es sollte ein operatives Taktsignal bereitgestellt werden.

[0058] Darüber hinaus kann eine getaktete Komponente, die ein Taktsignal empfängt, eine minimale

Frequenz aufweisen, mit der sie arbeiten kann. Die Zeitsteuerung eines Prozessors kann beispielsweise von einer Bereitstellung eines Taktsignals über einer minimalen Frequenz abhängig sein. Um sicherzustellen, dass das Taktsignal operativ ist, wenn das Taktsignal zuerst der getakteten Komponente oder Komponenten bereitgestellt wird, wird ein Frequenzdetektor 50 vorgesehen, um das Ausgangstaktsignal zu überwachen. Erst wenn das Ausgangstaktsignal eine Schwellfrequenz überschreitet, darf die Ausgabe aus dem Dividierer 52 als operatives Taktsignal 36 bereitgestellt werden. Die Schwellfrequenz kann vom Typ und den Anforderungen der getakteten Komponenten abhängen, die das Taktsignal empfangen.

[0059] Fig. 4 zeigt einen Schalter 72, der durch den Frequenzdetektor gesteuert wird, während er ein operatives Taktsignal 36 während des Einrastzeitintervalls bereitstellt, wenn die Schwellfrequenz überschritten worden ist. Es kann jedoch ein beliebiges von verschiedenen Verfahren verwendet werden, um das Taktsignal einer getakteten Komponente oder Komponenten bereitzustellen, wenn bestimmt worden ist, dass das Signal operativ ist. Nachdem der PLL eingerastet worden ist, wird der Dividierer 52 typischerweise umgangen (z. B. durch Schließen des Schalters 72 und Öffnen eines Schalters 70 oder durch einen entsprechenden Mechanismus), und das Ausgangstaktsignal 32' wird den verschiedenen getakteten Komponenten des Prozessors als das operative Taktsignal bereitgestellt.

[0060] Somit stellt der Frequenzmultiplizierer 10' dem Prozessor während des Einrastzeitintervalls des PLL ein operatives Taktsignal bereit. Die rechnerische Arbeit, logischen Operationen, die Zeitsteuerung und andere verschiedene Verarbeitungsaufgaben können dann während der Einrastzeit des PLL ausgeführt werden. Die Latenz des Frequenzmultiplizierers ist im Wesentlichen gleich der Aufwachzeit, und somit wird das Overhead-Phänomen des Aktivierens des PLL reduziert. Darüber hinaus kann das Zeit-Overhead-Phänomen, das dem Aktivieren des PLL zugeschrieben ist, in Verarbeitungssituationen berücksichtigt werden, wo von der Einrastzeit abhängige Latenzen verhindert haben können, dass der Frequenzmultiplizierer deaktiviert wird. Somit können die Taktfrequenzen, die einem Prozessor bereitgestellt werden, dynamisch angepasst werden, um den rechnerischen Anforderungen des Prozessors gerecht zu werden, ohne dass er in hochenergetischen Zuständen verbleiben muss, wenn dieses Berechnungsniveau nicht notwendig ist.

**[0061]** Es wird darauf hingewiesen, dass die Anordnung, Anzahl und die Art der Komponenten, die in den vorstehenden Ausführungsformen dargestellt sind, lediglich exemplarischen Charakter haben. Fachleute sind sich vieler Entwurfsabwandlungen bewusst. Diese Abwandlungen sollten aber nicht als

Abweichung vom Schutzbereich der Erfindung aufgefasst werden.

**[0062]** Der Dividierer, der bereitgestellt ist, um Frequenzen über der Zielfrequenz zu unterdrücken (z. B. Dividierer **52**), muss z. B. kein zusätzlicher und/oder separater Dividierer sein. Der gesamte oder ein Teil des Dividierers innerhalb der Regelkreises (z. B. Dividierer **28'**) kann beispielsweise genutzt werden, um eine Unterdrückung von Überschwingfrequenzen zu erreichen.

[0063] In Fig. 6 wird der Dividierer 28" als eine in Reihe geschaltete Reihe von Durch-2-dividieren-Zählern dargestellt. Ein Taktsignal wird nach dem ersten Durch-2-dividieren-Zähler abgegriffen und als operatives Taktsignal 36' bereitgestellt, d. h. der Dividierer 52' ist die erste Dividiererstufe des Dividierers 28'. Somit stellt der Dividierer 52' einen Frequenzreduktionsfaktor von 2 bereit, um Frequenzen über einer Zielfrequenz des Frequenzmultiplizierers zu unterdrücken. Abhängig von der gewünschten Frequenzreduktion kann jedoch das Signal von einer beliebigen Stufe eines Dividierers 28" genommen werden. Darüber hinaus muss der Dividierer 28" keine Durch-2-dividieren-Zähler aufweisen, sondern kann eine beliebige Frequenzdividiererkomponete mit einem passenden Dividiererverhältnis sein.

[0064] Zusätzlich kann der Frequenzdetektor zum Bestimmen, wann eine Schwellfrequenz überschritten worden ist, (z. B. ein Frequenzdetektor 50) die Frequenz eines Taktsignals mit Ausnahme des Signals erfassen, das direkt vom VCO bereitgestellt wird, wie in Fig. 7 dargestellt ist. Der Frequenzdetektor kann beispielsweise die Frequenz des Signals überwachen, nachdem es einem Dividierer, der Frequenzen über einer Zielfrequenz unterdrückt (z. B. Dividierer 52, 52' etc.), bereitgestellt worden ist oder von diesem abgegriffen worden ist.

[0065] Darüber hinaus kann ein Frequenzdetektor programmiert werden, um zu erfassen, wann ein Taktsignal eine variable Schwellfrequenz überschritten hat. Unter Bezugnahme auf den Prozessor 100, der in Fig. 3 dargestellt ist, kann der größte Dividiererfaktor, der in einem beliebigen der Taktbereiche zu einer gegebenen Zeit ausgewählt wird, den Wert der Schwellfrequenz bestimmen, um sicherzustellen, dass eine jeweilige Komponente, die ein Taktsignal empfängt, mit einem Taktsignal mit einer Frequenz versehen wird, die die minimale Frequenzanforderung der getakteten Komponenten erfüllt oder überschreitet. Beispielsweise muss die Schwellfrequenz möglicherweise erhöht werden, wenn der Taktbereich 90c die Teilung durch den Faktor 14 ausgewählt hat, und kann möglicherweise reduziert werden, wenn ein geringerer Reduktionsfaktor oder gar kein Reduktionsfaktor ausgewählt worden ist.

[0066] In einigen Ausführungsformen kann ein Frequenzdetektor zum Erfassen, wann eine Schwellfrequenz überschritten worden ist, überflüssig sein. Die Eigenschaften des Signalgenerators (z. B. ein VCO) und die Anforderungen der getakteten Komponenten, die das Taktsignal empfangen, das durch den Frequenzmultiplizierer ausgegeben wird, können dergestalt sein, dass das anfängliche Ausgangstaktsignal, das durch den Signalgenerator bereitgestellt wird, wenn dieser aktiviert wird, bereits über der Schwellfrequenz liegen kann. In solchen Fällen kann der Frequenzdetektor (z. B. Frequenzdetektor 50) durch eine Logik ersetzt werden, die ungeachtet der Frequenz einfach erfasst, wann der Signalgenerator das erste Mal mit der Ausgabe eines Signal beginnt. Da der Signalgenerator eine Frequenz, die die Schwellfrequenz überschreitet, bekanntermaßen unmittelbar erreicht, ist das Ausgangstaktsignal operativ, sobald der Signalgenerator aktiviert ist.

[0067] Für Fachleute sind viele andere Modifizierungen, Abwandlungen und Alternativen in Bezug auf die Anzahl, den Typ und die Konfiguration der Komponenten zum Bereitstellen eines Ausgangstaktsignals mit Frequenzen, die ausschließlich in einem spezifizierten Bereich liegen, selbstverständlich. Diese Abwandlungen sind als im Schutzbereich der Erfindung liegend zu betrachten.

[0068] Nach einer ausführlichen Beschreibung mehrerer Ausführungsformen der Erfindung werden Fachleuten verschiedene Ausführungen und Verbesserungen ohne Weiteres verständlich. Dementsprechend ist die vorstehende Beschreibung lediglich beispielhaft und nicht einschränkend aufzufassen. Beschränkt ist die Erfindung nur durch die nachstehenden Ansprüche und deren Entsprechungen.

#### **Patentansprüche**

1. In einem Frequenzmultiplizierer, der ein erstes Ausgangstastsignal (32') bereitstellt, das mit einem Eingangstaktsignal (30') synchronisiert werden soll, gibt es ein Verfahren zum Reduzieren eines Overhead-Phänomens zum Aktivieren des Frequenzmultiplizierers (12'), wobei das Verfahren folgende Schritte aufweist:

Bereistellen eines Eingangstaktsignals (30') mit einer ersten Frequenz;

Erzeugen des ersten Ausgangstaktsignals (32') mit einer zweiten Frequenz, die im Wesentlichen gegen eine Zielfrequenz konvergiert, wobei die Zielfrequenz größer ist als die erste Frequenz; gekennzeichnet durch

Erfassen einer Zeit, wenn die zweite Frequenz eine Schwellfrequenz überschritten hat und bevor die zweite Frequenz die Zielfrequenz erreicht hat, wobei die Zeit den Beginn eines ersten Intervalls bestimmt; Erzeugen eines zweiten Ausgangstaktsignals von dem ersten Ausgangstaktsignal, wobei das zweite

Ausgangstaktsignal eine dritte Frequenz aufweist, die geringer ist als die zweite Frequenz und die Zielfrequenz nicht überschreitet, wobei die dritte Frequenz im Wesentlichen gegen einen Faktor der Zielfrequenz konvergiert;

Bestimmen, wann das erste Ausgangstaktsignal mit dem Eingangstaktsignal synchronisiert wird, wobei die Bestimmung der Synchronisierung das erste Intervall beendet; und

Hemmen eine Ausgabe eines Taktsignals auf die zumindest eine getaktete Komponente vor Beginn des ersten Intervalls, wobei der zweite Ausgangstakt während des ersten Intervalls ausgegeben wird, und am Ende des ersten Intervalls das erste Ausgangstaktsignal bereitgestellt wird, um die zumindest eine getaktete Komponente zu betreiben.

- 2. Verfahren nach Anspruch 1, wobei der Vorgang des Erzeugens des zweiten Ausgangstaktsignals einen Vorgang des Dividierens der zweiten Frequenz durch N beinhaltet, wobei N den Faktor der Zielfrequenz bestimmt.

- 3. Verfahren nach Anspruch 3, wobei der Vorgang des Dividierens der zweiten Frequenz durch N ein Dividieren der zweiten Frequenz durch zumindest 2 beinhaltet.

- 4. Frequenzmultiplizierer, der folgende Merkmale aufweist:

einen Komparator (22') zum Empfangen eines Eingangstaktsignals (30') mit einer ersten Frequenz und einem Rückkopplungssignal (34'), wobei der Komparator ein Fehlersignal (40') bereitstellt, das eine Phasendifferenz zwischen dem Eingangstaktsignal und dem Rückkopplungssignal anzeigt;

einen Signalgenerator (26'), der mit dem Komparator (22') verbunden ist, um ein erstes Ausgangstaktsignal (32') mit einer zweiten Frequenz bereitzustellen, wobei der Signalgenerator (26') eine Phase oder Frequenz des ersten Ausgangstaktsignals basierend auf dem Fehlersignal anpasst, um die Phasendifferenz zwischen dem Eingangstaktsignal und dem Rückkopplungssignal zu reduzieren;

eine Rückkopplungsschleife mit einem Dividierer (28'), um ein Rückkopplungssignal, basierend auf dem ersten Ausgangstaktsignal, an den Komparator bereitzustellen, wobei der Rückkopplungsschleife ein erstes Zeitintervall zugeordnet ist, um die Differenz in einer ersten Eigenschaft zu reduzieren, so dass die erste Eigenschaft des Eingangstaktsignals und die erste Eigenschaft des Rückkopplungssignals im Wesentlichen identisch sind;

gekennzeichnet durch eine Einrichtung zum Erfassen einer Zeit, wenn die zweite Frequenz eine Schwell-Frequenz überschritten hat und bevor die zweite Frequenz die Zielfrequenz erreicht hat, wobei die Zeit den Beginn eines ersten Intervalls bestimmt; einen Dividierer zum Erzeugen eines zweiten Ausgangstaktsignals von dem ersten Ausgangstaktsig-

nal, wobei das zweite Ausgangstaktsignal eine dritte Frequenz aufweist, die geringer ist als die zweite Frequenz und die Zielfrequenz nicht überschreitet, wobei die dritte Frequenz im Wesentlichen gegen einen Faktor der Zielfrequenz konvergiert;

eine Einrichtung zum Bestimmen, wann das erste Ausgangstaktsignal mit dem Eingangstaktsignal synchronisiert wird, wobei die Bestimmung der Synchronisierung das erste Intervall beendet; und

eine Einrichtung zum Hemmen einer Ausgabe eines Taktsignals an zumindest eine getaktete Komponente vor Beginn des ersten Intervalls, zum Ausgeben des zweiten Ausgangstaktsignals von Beginn des ersten Intervalls bis zum Ende des ersten Intervalls und zum anschließenden Ausgeben des ersten Ausgangstakts.

- 5. Frequenzmultiplizierer nach Anspruch 4, der einen Detektor (50) aufweist, um zu bestimmen, wann die zweite Frequenz die Schwell-Frequenz überschritten hat.

- 6. Frequenzmultiplizierer nach Anspruch 4 oder 5, wobei die erste Eigenschaft eine Phase ist.

- 7. Frequenzmultiplizierer nach Anspruch 4, 5 oder 6, wobei der Komparator die Differenz zwischen zumindest entweder einer Anstiegsflanke oder einer Abfallflanke des Eingangstaktsignals und des Rückkopplungssignals bestimmt.

- 8. Frequenzmultiplizierer nach Anspruch 4, 5, 6 oder 7, wobei der Komparator (22') die Differenz zwischen Nulldurchgängen des Eingangstaktsignals und des Rückkopplungssignals bestimmt.

- 9. Frequenzmultiplizierer nach einem der Ansprüche 4 bis 8, in Kombination mit zumindest einem Prozessor (100c).

- 10. Kombination nach Anspruch 9, wobei das Eingangstaktsignal ein Prozessorsystem-Taktsignal ist.

- 11. Kombination nach Anspruch 9, wobei das erste und das zweite Ausgangstaktsignal auf getaktete Komponenten von dem zumindest einen Prozessor verteilt wird.

- 12. Kombination nach Anspruch 9, wobei der zumindest eine Prozessor eine Mehrzahl von Teilsystemen aufweist, wobei die Mehrzahl der Teilsysteme in der Lage ist, eine Mehrzahl von Frequenzen zu betreiben.

- 13. Kombination nach Anspruch 12, wobei der Frequenzmultiplizierer Taktsignale an die Mehrzahl von Teilsystemen des zumindest einen Prozessors bereitstellt.

Es folgen 6 Blatt Zeichnungen

# Anhängende Zeichnungen

Fig. 1

Fig.2

Fig. 3

Fig. 4

Fig.5

Fig. 6