(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6239525号

(P6239525)

(45) 発行日 平成29年11月29日(2017.11.29)

(24) 登録日 平成29年11月10日(2017.11.10)

(51) Int.Cl.

HO2M 7/48 (2007.01)

HO2M 1/00 (2007.01)

F 1

HO2M 7/48 Z H V M

HO2M 1/00 F

HO2M 7/48 Z

請求項の数 15 (全 12 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-545054 (P2014-545054)  |

| (86) (22) 出願日 | 平成24年12月5日 (2012.12.5)        |

| (65) 公表番号     | 特表2015-503319 (P2015-503319A) |

| (43) 公表日      | 平成27年1月29日 (2015.1.29)        |

| (86) 國際出願番号   | PCT/CA2012/001125             |

| (87) 國際公開番号   | W02013/082705                 |

| (87) 國際公開日    | 平成25年6月13日 (2013.6.13)        |

| 審査請求日         | 平成27年11月18日 (2015.11.18)      |

| (31) 優先権主張番号  | 61/567,800                    |

| (32) 優先日      | 平成23年12月7日 (2011.12.7)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 505020293<br>ティーエム4・インコーポレーテッド<br>カナダ・ケベック・J 4 B・8 P 1・ボウ<br>シェヴィル・ジェイアマンド・ボンバー<br>デール・135・ビューロー・25 |

| (74) 代理人  | 100106909<br>弁理士 棚井 澄雄                                                                              |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                                                               |

| (72) 発明者  | ジャン-マルク・カー<br>カナダ・ケベック・J 5 R・O L 6・キャ<br>ンディアック・リュ・シェルブル・33<br>1                                    |

最終頁に続く

(54) 【発明の名称】 IGBTのターンオフ過電圧の制限

## (57) 【特許請求の範囲】

## 【請求項1】

ゲート、コレクタおよびエミッタを各々有する第1および第2のIGBTと、前記第2のIGBTのコレクタの寄生インダクタンスに接続される1次巻線、および2次巻線を有するトランジスタとを含むDC - AC電力コンバータであって、前記各IGBTの前記ゲートは、リファレンスを含むゲートドライバに接続され、前記第1のIGBTのゲートドライバリファレンスは、前記電力コンバータの接地バスに接続され、前記第2のIGBTのゲートドライバリファレンスは、前記トランジスタの2次巻線を介して前記第1のIGBTの前記コレクタに接続され、前記第2のIGBTの前記エミッタの寄生インダクタンスは、前記トランジスタの2次巻線によって、前記第2のIGBTのターンオフにおける過電圧を制限する制御を可能にするように増加するDC - AC電力コンバータ。

## 【請求項2】

各IGBTについて、前記ゲートドライバは、直列に接続され、前記対応するIGBTの前記エミッタの寄生インダクタンスに接続される第1および第2の抵抗器を含み、前記ゲートドライバリファレンスは、前記第1の抵抗器と前記第2の抵抗器との間の接続ポイントに接続される、請求項1に記載のDC - AC電力コンバータ。

## 【請求項3】

前記トランジスタの2次巻線は、前記第2のIGBTの前記エミッタの前記寄生インダクタンスならびに第1および第2の抵抗器に直列に接続されている、請求項1に記載のDC - AC電力コンバータ。

10

20

**【請求項 4】**

前記第2のIGBTの前記エミッタと前記第1のIGBTの前記コレクタとの間にコネクタを設けることによって、前記第2のIGBTの前記エミッタの前記寄生インダクタンスが増加し、前記コレクタは、増加された等価な寄生インダクタンスを与えるように構成される、請求項1に記載のDC - AC電力コンバータ。

**【請求項 5】**

前記第2のIGBTの前記エミッタはエミッタパッドに接続され、前記第1のIGBTの前記コレクタはコレクタパッドに接続され、前記コネクタは、前記エミッタパッドと前記コレクタパッドとの間に設けられる、請求項4に記載のDC - AC電力コンバータ。

**【請求項 6】**

前記エミッタパッドは複数のエミッタパッドを含み、前記コレクタパッドは複数のコレクタパッドを含む、請求項5に記載のDC - AC電力コンバータ。

**【請求項 7】**

前記コネクタはU字形の断面を有する、請求項5に記載のDC - AC電力コンバータ。

**【請求項 8】**

前記U字形のコネクタは、前記パッドと相互接続するように構成される脚部を含む、請求項7に記載のDC - AC電力コンバータ。

**【請求項 9】**

コレクタ、エミッタ、ゲートおよびリファレンスを含むゲートドライバを有する第1のIGBTと、コレクタ、エミッタ、ゲートおよびリファレンスを含むゲートドライバを有する第2のIGBTと、を含むDC - AC電力コンバータであって、前記電力コンバータは、

直列に接続され、前記第1のIGBTの前記エミッタの寄生インダクタンスに接続される第1および第2の抵抗器であり、前記第1のIGBTのゲートドライバリファレンスが前記第1の抵抗器と前記第2の抵抗器との間の接続ポイントに接続される第1および第2の抵抗器と、

前記第2のIGBTの前記コレクタの前記寄生インダクタンスに接続される1次巻線と前記第2のIGBTの前記エミッタの前記寄生インダクタンスに接続される2次巻線とを有するトランスと、を含み、前記第2のIGBTの前記ゲートドライバの前記リファレンスは、前記トランスの前記2次巻線に接続されるDC - AC電力コンバータ。

**【請求項 10】**

前記ゲートドライバリファレンスは、第3の抵抗を介して前記トランスの前記2次巻線に接続される、請求項9に記載のDC - AC電力コンバータ。

**【請求項 11】**

コレクタ、エミッタ、ゲートおよびリファレンスを含むゲートドライバを有する第1のIGBTと、コレクタ、エミッタ、ゲートおよびリファレンスを含むゲートドライバを有する第2のIGBTと、を含むDC - AC電力コンバータであって、前記電力コンバータは、

直列に接続され、前記第1のIGBTの前記エミッタの寄生インダクタンスに接続される第1および第2の抵抗器であり、前記第1のIGBTのゲートドライバリファレンスが前記第1の抵抗器と前記第2の抵抗器との間の接続ポイントに接続される第1および第2の抵抗器と、

前記第2のIGBTの前記コレクタの前記寄生インダクタンスに接続される1次巻線、および前記第2のIGBTの前記エミッタの前記寄生インダクタンスに直列に接続される2次巻線を有するトランスと、を含み、前記第2のIGBTのゲートドライバリファレンスは、前記トランスの前記2次巻線に接続されるDC - AC電力コンバータ。

**【請求項 12】**

前記トランスの前記2次巻線は、前記第2のIGBTの前記エミッタの前記寄生インダクタンスならびに第3および第4の抵抗器の両方と直列に接続され、前記第2のIGBTの前記ゲートドライバリファレンスは、前記第3の抵抗器と前記第4の抵抗器との間の接続ポイントに接続される、請求項11に記載のDC - AC電力コンバータ。

**【請求項 13】**

前記トランスの前記2次巻線は、前記第2のIGBTの前記エミッタの前記寄生インダクタンス、前記第1のIGBTの前記コレクタの前記寄生インダクタンス、ならびに前記第3および前

10

20

30

40

50

記第4の抵抗器に直列に接続される、請求項12に記載のDC - AC電力コンバータ。

**【請求項 14】**

高周波ループを含むDC - AC電力コンバータであって、前記高周波ループは、

ゲート、コレクタおよびエミッタを各々有する下部IGBTおよび上部IGBTであり、前記各IGBTの前記ゲートがリファレンスを含むゲートドライバに接続され、前記下部IGBTのゲートドライバリファレンスは、前記電力コンバータの接地バスに接続され、前記上部IGBTのゲートドライバリファレンスは、前記下部IGBTの前記コレクタに接続される、下部IGBTおよび上部IGBTと、

前記高周波ループの様々な素子の相互接続によって定義される寄生インダクタンスと、を有し、前記上部IGBTの前記エミッタの、および前記下部IGBTの前記コレクタの前記寄生インダクタンスは、前記高周波ループの前記寄生インダクタンスの一部であり、10

前記高周波ループの前記寄生インダクタンスで誘起された電圧の一部は、トランスによって、前記上部IGBTの前記エミッタの、および前記下部IGBTの前記コレクタの寄生インダクタンスで誘起された電圧に付加されて、前記上部IGBTのゲート - エミッタ電圧 ( $V_{ge}$ ) の勾配を緩やかにし、前記トランスは、前記高周波ループの寄生インダクタンスに接続される1次巻線、および前記上部IGBTの前記エミッタの前記寄生インダクタンスと直列に前記上部IGBTの前記ゲートドライバに接続される2次巻線を有している、

DC - AC電力コンバータ。

**【請求項 15】**

各IGBTについて、前記ゲートドライバは、直列に接続され、前記対応するIGBTの前記エミッタの寄生インダクタンスに接続される第1および第2の抵抗器を含み、前記ゲートドライバリファレンスは、前記第1の抵抗器と前記第2の抵抗器との間の接続ポイントに接続される、請求項14に記載のDC - AC電力コンバータ。20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本開示は、一般的には絶縁ゲートバイポーラトランジスタ(IGBT)に関する。より具体的には、本開示は、IGBT上のターンオフ過電圧を制限し、それによってIGBTの全体効率を改善するための構成および方法に関する。30

**【背景技術】**

**【0002】**

電気および/または電気ハイブリッド自動車応用の電力インバータ回路で許容されるスペースは限られ、また半導体のコストは高いために、電力エレクトロニクスの集積化に対する要求が増大する。

**【0003】**

車両用インバータの半導体が占めるスペースを減らす周知の方法は、冷却面のサイズを小さくできるように半導体の効率を上昇させることである。

**【0004】**

従来のインバータの設計に存在するIGBTモジュールの損失は、主に2つの原因によって生じる。すなわち、伝導損失およびスイッチング損失である。IGBTモジュールのスイッチング損失を改善する1つの方法は、一般的に、IGBTのターンオンおよびターンオフを加速することによるものである。しかし、より速いIGBTターンオフを用いると、高周波ループの浮遊インダクタンスによる過電圧が非常に高くなるので、デバイスを保護するためにターンオフの減速がしばしば必要となり、それによってインバータの効率に重大な影響を与える。40

**【発明の概要】**

**【課題を解決するための手段】**

**【0005】**

1つの例示的態様によれば、ゲート、コレクタおよびエミッタを各々有する第1および第2のIGBTを含むDC-AC電力コンバータが提供される。各IGBTのゲートは、リファレンスを含50

むゲートドライバに接続される。第1のIGBTのゲートドライバリファレンスは、電力コンバータの接地バスに接続され、第2のIGBTのゲートドライバリファレンスは、第1のIGBTのコレクタに接続される。第2のIGBTのエミッタの寄生インダクタンスは、第2のIGBTのターンオフにおける過電圧を制限する制御を可能にするように増加する。

#### 【0006】

別の例示的態様によれば、コレクタ、エミッタ、ゲートおよびリファレンスを含むゲートドライバを有する第1のIGBTと、コレクタ、エミッタ、ゲートおよびリファレンスを含むゲートドライバを有する第2のIGBTと、を含むDC-AC電力コンバータが提供される。電力コンバータは、

直列に接続され、第1のIGBTのエミッタの寄生インダクタンスに接続される第1および第2の抵抗器であり、第1のIGBTのゲートドライバリファレンスが第1の抵抗器と第2の抵抗器との間の接続ポイントに接続される第1および第2の抵抗器と、

第2のIGBTのコレクタの寄生インダクタンスに接続される1次巻線と第2のIGBTのエミッタの寄生インダクタンスに接続される2次巻線とを有するトランスと、を含み、第2のIGBTのゲートドライバのリファレンスは、トランスの2次巻線に接続される。

#### 【0007】

さらに別の例示的態様によれば、コレクタ、エミッタ、ゲートおよびリファレンスを含むゲートドライバを有する第1のIGBTと、コレクタ、エミッタ、ゲートおよびリファレンスを含むゲートドライバを有する第2のIGBTと、を含むDC-AC電力コンバータが提供される。電力コンバータは、

直列に接続され、第1のIGBTのエミッタの寄生インダクタンスに接続される第1および第2の抵抗器であり、第1のIGBTのゲートドライバリファレンスが第1の抵抗器と第2の抵抗器との間の接続ポイントに接続される第1および第2の抵抗器と、

第2のIGBTのコレクタの寄生インダクタンスに接続される1次巻線、および第2のIGBTのエミッタの寄生インダクタンスに直列に接続される2次巻線を有するトランスと、を含み、第2のIGBTのゲートドライバリファレンスは、トランスの2次巻線に接続される。

#### 【図面の簡単な説明】

#### 【0008】

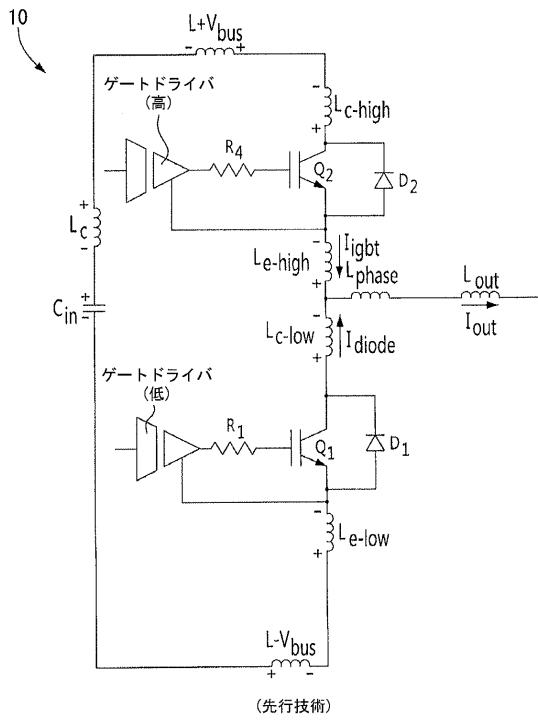

【図1】浮遊インダクタンスおよびゲートドライバがそれらのリファレンスを取得する論理接続を示す、高周波ループを有する典型的なゲートドライブIGBT構成の回路図である。

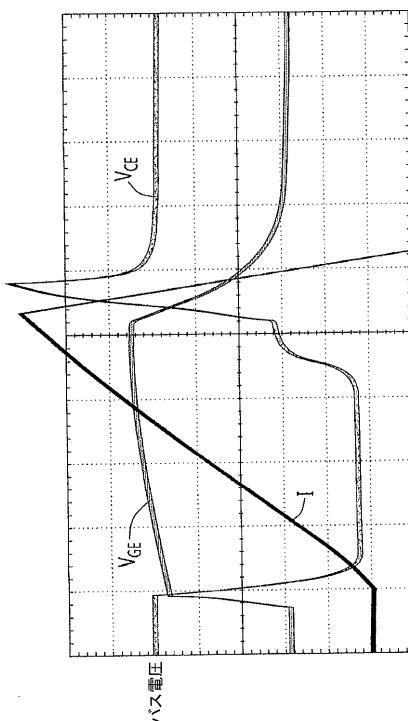

【図2】短絡条件下で過電圧を示す電流および電圧波形を示す線図である。

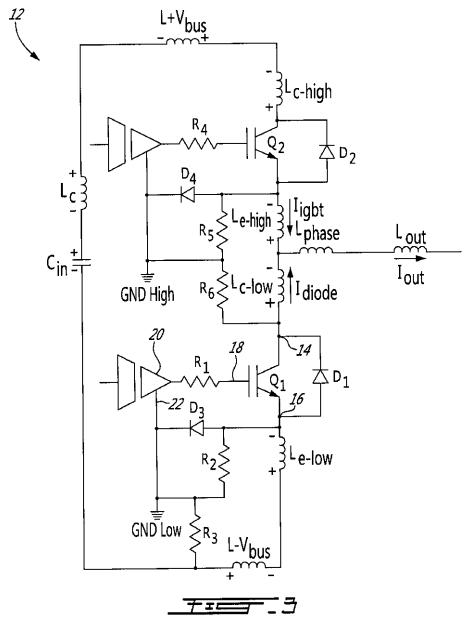

【図3】例示的実施形態による、エミッタ浮遊インダクタンスに接続される抵抗分割器を用いて過電圧を低減させるゲートドライブIGBTの回路図である。

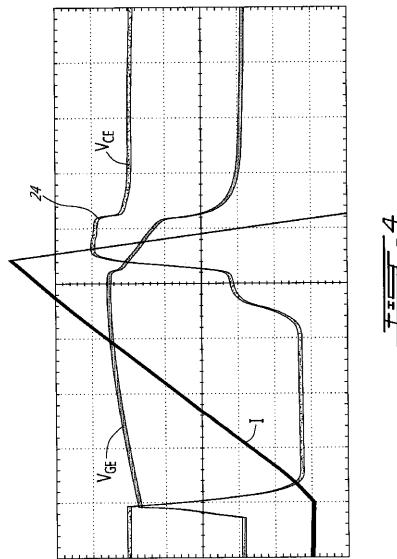

【図4】500Vのバス電圧を伴う短絡条件において、抵抗分割器を用いたIGBTのターンオフ波形を示す線図である。

【図5】短絡条件下で、300Vの最大バス電圧に対して調整された抵抗分割器を用いたIGBTのターンオフ波形を示す線図である。

【図6】別の例示的実施形態による、上部IGBTのためのトランスを用いて過電圧を低減させるドライブIGBTの回路図である。

【図7】別の例示的実施形態による、トランスおよび抵抗分割器を用いて過電圧を低減させるドライブIGBTの回路図である。

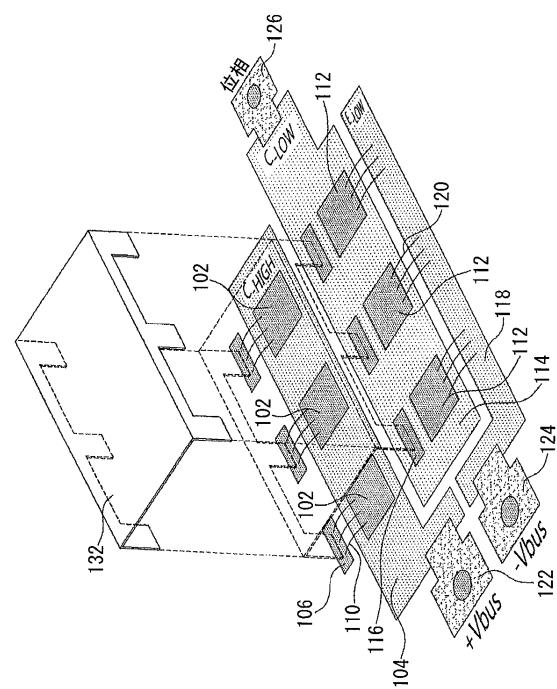

【図8】上部IGBTのエミッタインダクタンスを調整することができるIGBTモジュールの模式的なレイアウト図である。

【図9】図8のIGBTモジュールに類似のIGBTモジュールの別の模式的なレイアウト図である。

#### 【発明を実施するための形態】

#### 【0009】

特許請求の範囲および/または明細書において用語「含む(comprising)」と共に用いられる単語「1つの(aまたはan)」の使用は、「1つの」を意味することができるが、それは「1つまたは複数」、「少なくとも1つ」、および「1つまたは2つ以上」の意味とも矛盾し

10

20

30

40

50

ない。同様に、「別の(another)」という語は、少なくとも第2のまたはそれ以上を意味することができる。

#### 【0010】

この明細書および特許請求の範囲において用いられるように、「含む(comprise)」、「有する(have)」、「含む(include)」、または「含む(contain)」という語は、包括的で拡張可能であり、付加的な列挙されていない要素またはプロセス工程を除外するものではない。

#### 【0011】

本明細書および添付した特許請求の範囲においては、本来、方向的、幾何学的および/または空間的な様々な用語、例えば「縦の」、「水平の」、「前方の」、「後方の」、「上方に」「下方に」などが用いられる。このような用語は、説明の容易さのため、そして相対的な意味においてのみ用いられるのであって、いかなる形であれ、本開示の範囲を限定するものとみなすべきでないことを理解すべきである。10

#### 【0012】

他の対象、利点および特徴は、例えば添付の図面に関して与えられるその例示的実施形態についての以下の非限定的な記載を読むことで、より明確になろう。

#### 【0013】

IGBTのターンオフで $dI/dt$ は、高周波ループの浮遊インダクタンスにかかる電圧を生成し、その電圧はIGBTに対してバス電圧より上に印加される。所定の値を超える過電圧期間にだけ過電圧を減少させるようにゲート電圧の勾配を緩やかにするために、ゲートドライブのIGBTにかかる過電圧のサンプルの注入に基づく解決策が本明細書で提案される。20

#### 【0014】

図1は、先行技術とラベルされており、例えば、バッテリ(図示せず)から三相電気モーター(図示せず)の駆動に用いられる三相電力コンバータ10の1/3を開示する。

#### 【0015】

この種のコンバータはよく知られていると考えられるので、それは本明細書では詳細に記載しない。しかし、本質的にワイヤ、接続、デカップリングキャパシタおよび回路基板トレースにおいて提供されるインダクタンスが、図1に表現されていることに留意すべきである。

#### 【0016】

図1から分かるように、各ゲートドライバのリファレンスは、対応するIGBTの論理的ピンとして典型的に知られているエミッタに接続している。簡潔にするために、IGBT Q<sub>1</sub>を含む下部の部分を説明する。30

#### 【0017】

IGBT Q<sub>1</sub>がオフするとき、すなわちQ1からD2へ電流が流れる過電圧の期間には、IGBTは、回路に存在する様々な寄生インダクタンス(L<sub>c</sub>、L<sub>+bus</sub>、L<sub>c-high</sub>、L<sub>e-high</sub>、L<sub>c-low</sub>およびL<sub>e-low</sub>)における $dI/dt$ によって生成される過電圧を支持することが可能でなければならない。実際、インダクタンスがその電流変化に抵抗するので、図1に示す寄生インダクタンスの極性から分かるように、付加的な電圧が回路に生じる。電源電圧に追加されるこれらの電圧は、しばしば結果として、IGBTのコレクタとエミッタとの間に安全に存在し得る通常の最大電圧(V<sub>ce</sub>)よりしばしば大きい電圧になる。40

#### 【0018】

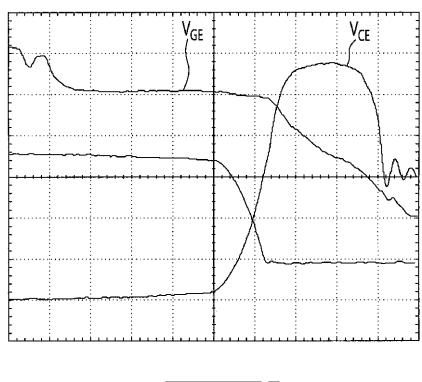

図2は、ターンオフにおけるV<sub>ce</sub>、V<sub>ge</sub>および電流Iを示す。V<sub>ce</sub>の主要な過電圧は、ターンオフ時にバス電圧より高くなることが分かるであろう。

#### 【0019】

一般に述べられるように、ゲートドライバのリファレンスを図1の論理的ピンから接地バスへ(下部IGBT Q<sub>1</sub>について)、また論理的ピンから下部IGBTのコレクタへ(上部IGBT Q<sub>2</sub>について)変更することにより、ターンオフ期間におけるV<sub>ce</sub>のこの過電圧を減少させることができる。

#### 【0020】

50

言い換えれば、ゲートドライバのリファレンスを、論理的ピンの代わりにIGBTのパワータブに接続するための技術が開発された。後述するように、 $V_{ge}$ の負の勾配を緩やかにするために、IGBTのエミッタにおける負電圧を生成するようにエミッタインダクタンスにかかる電圧をゲートドライバに注入する。この結果は、いかなる遅延も $dI/dt$ 制限も伴わない、ゲート電圧の直接作用である。

#### 【0021】

市販されているIGBTモジュールでは、論理接続と電力接続との間の最適なエミッタインダクタンスが存在しないので、抵抗分割器を用いて、ゲートドライブ回路において注入される過電圧のサンプルを最適化するための技術が開発された。

#### 【0022】

図3は抵抗分割器技術を用いた過電圧の最適化を示し、図4は500Vdcのバス電圧について関連する波形を示す。

#### 【0023】

また、図3の三相電力コンバータ12の下部部分について述べると、IGBT Q<sub>1</sub>は寄生インダクタンスL<sub>e-1ow</sub>を有するコレクタ14、寄生インダクタンスL<sub>e-1ow</sub>を有するエミッタ16、および抵抗器R<sub>1</sub>を介してゲートドライバ20に接続されるゲート18を含む。ゲートドライバ20のリファレンス22は、2つの抵抗器R<sub>2</sub>およびR<sub>3</sub>ならびにターンオンに影響を与えないようすることを可能にするダイオードD<sub>3</sub>を含む抵抗分割回路に接続される。

#### 【0024】

抵抗器R<sub>2</sub>およびR<sub>3</sub>の値は、Q<sub>1</sub>に許容される過電圧レベルに従って選択される。図4は500Vdcのバス電圧での動作について、また図5は500Vdcのバス電圧での動作について最適化された抵抗分割器の結果を示す。R<sub>3</sub>に対するR<sub>2</sub>の比は、過電圧を低減するために増加する。並列な2つの抵抗器の値は、R<sub>1</sub>と直列に、ゲートドライバ抵抗器として設定される。ゲート抵抗器のこの値は、適切な整流挙動に従って調整される。

#### 【0025】

抵抗器の値を適正に設定することによって、効率を改善することを可能にする最大の過電圧を得るように、エミッタインダクタンスの効果を低減させることができる。

#### 【0026】

言い換えれば、上部のIGBTがオフするときに下部のIGBTのゲートドライブを負電圧から保護するダイオードの電流を制限するためにゲートの接地接続に抵抗器を用いる通常の方法は、抵抗器を2つに分割し、修正する $dI/dt$ に及ぼすエミッタインダクタンスの影響を制限するようにそれらの比を適応することによって修正された。全抵抗は同じままであるが、分圧器は望ましいレベルに過電圧を制限するためにエミッタインダクタンスの所望の重みを与える。

#### 【0027】

最大IGBT定格に達するためには、過電圧は、明らかに可能な限り最適化されなければならない。パワータブR<sub>2</sub>に接続された抵抗器と比較して論理的エミッタR<sub>3</sub>に接続された抵抗器を低減させることによって、これが実行される。エミッタインダクタンスにかかる電圧は2つに分割され、論理的抵抗器にかかる電圧だけがゲート電圧降下を制限するためにゲートドライブ回路に印加される。

#### 【0028】

抵抗器R<sub>2</sub>およびR<sub>3</sub>は、寄生インダクタンスL<sub>e-1ow</sub>およびL<sub>vbus</sub>に接続されて示しているが、それらは寄生インダクタンスL<sub>e-1ow</sub>にだけ接続することができ、この寄生インダクタンスが十分でなければならない点に留意すべきである。

#### 【0029】

図4は、図3の回路のターンオフ期間における電流Iおよび電圧V<sub>ge</sub>およびV<sub>ce</sub>を示す。当業者は、ターンオフ期間におけるV<sub>ce</sub>の過電圧が非常に減少することに気づくであろう(平坦部分24を参照のこと)。電圧V<sub>ge</sub>の降下率が寄生インダクタンスからの電圧の挿入によって低下すると共に、この平坦部分24が発生する。

#### 【0030】

10

20

30

40

50

平坦部分の継続時間は、ターンオフ期間における損失に大きく影響を与える。すなわち、平坦部分が長いほど、損失が大きくなる。過電圧およびその長さを同時に制限したいという要求のため、過電圧の平坦部分の矩形波形状が好適である。過電圧の固有の挙動(自然なフィードバック)が、この形状を与える。

#### 【0031】

図4および図5は、異なるバス電圧で抵抗分割器を用いる場合の過電圧の矩形形状を示す。

#### 【0032】

エミッタインダクタンスが十分大きいので、この技術は下部IGBTについては非常に有効であるが、しかし上部IGBTについては、デバイスを保護するためにゲート抵抗器を増加させずに電圧を最適にクランプするには、エミッタインダクタンスはしばしば小さすぎる。実際のところ、上部IGBTにかかる過電圧を望ましいレベルに制限するためには、上部IGBTのエミッタインダクタンスは非常にしばしば低すぎる。

10

#### 【0033】

実際、IGBTモジュールの実装上の制約のために、上方の半導体および下方の半導体は互いに近接して実装され、したがって上方のIGBTのインダクタンス $L_{e-high}$ は非常に小さく、 $2,3nH$ のオーダーである。一方、下方のIGBTの論理的エミッタ以外の唯一の接続ポイントは-Vbusのパワータブであるから、下方のIGBTのインダクタンス $L_{e-low}$ は上方のエミッタインダクタンス $L_{e-high}$ の5倍である。-Vbusタブの接続は、その長さおよび曲線のために非常にインダクティブである。

20

#### 【0034】

言い換えれば、全てのIGBTモジュールは、高周波ループの一部である2つの電力接続+Vbusおよび-Vbusを有し、それらは最もインダクティブである。-Vbusが下部IGBTのエミッタのバスにあるので、それは下部IGBTのゲートドライバのIGBTにかかる過電圧のサンプルを注入するために用いることができる。残念なことに、+Vbus接続が上部IGBTのコレクタに接続されているので、このインダクタンスはゲートドライバのフィードバックとして直接用いることができない。

#### 【0035】

したがって、ゲートドライバのフィードバックとして $L_{e-high}$ を用いるために、それは、高周波ループの全体のインダクタンスを過度に増加させずに、そのインダクタンスを何とかして増加させることが必要である。 $L_{e-high}$ インダクタンスを増加させる2つの可能な技術について、以下に述べる。

30

#### 【0036】

上部IGBTのターンオフを最適化するために、コレクタをエミッタから分離するためのトランスを用いて、上部IGBTにかかる過電圧のサンプルを注入するコレクタ寄生インダクタンスを用いる第1の技術が設計された。

#### 【0037】

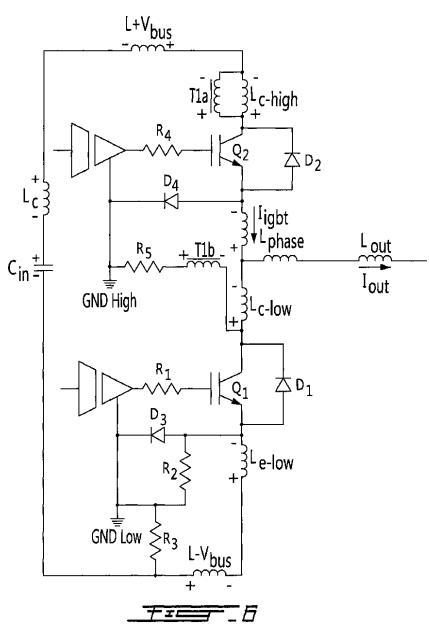

図6は、トランスの接続を示す。より具体的には、トランスT1aの1次巻線は $L_{c-high}$ 寄生インダクタンスに接続され、トランスT1bの2次巻線は抵抗器 $R_5$ と直列に接続される。

40

#### 【0038】

したがって、ゲート電圧の勾配を緩やかにするためにエミッタに負電圧を印加する上部IGBTの電流が減少すると、負電圧がトランスに発生する。その場合、過電圧の最適化は、トランスの巻数比によっても成される。

#### 【0039】

図6の回路の動作原理が図3の回路の動作原理に非常に類似することが理解されよう。しかし、上部IGBT Q<sub>2</sub>のエミッタの寄生インダクタンス( $L_{e-high}$ )は、ターンオフ時の $V_{ce}$ の負の勾配を適切に減速するのに十分でないので、上部IGBT Q<sub>2</sub>のコレクタの寄生インダクタンス( $L_{c-high}$ )のサンプルは、トランスによる $L_{e-high}$ と直列に配置される。

#### 【0040】

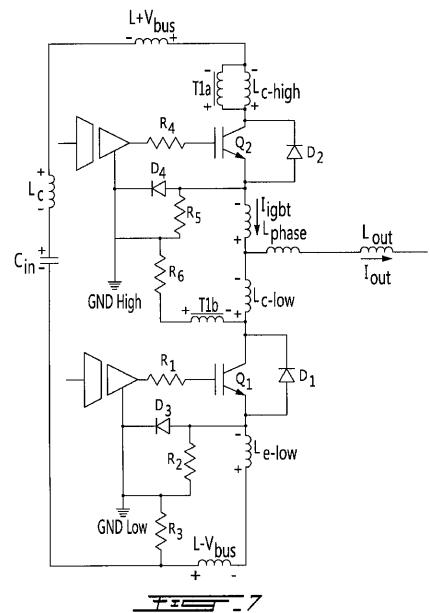

添付の図面の図7は、別の実施形態による、トランスおよび抵抗分割器の組合せを用い

50

て過電圧を低減するIGBTドライブの回路図である。図7は、図6の回路と類似の回路を示す。これらの回路の主要な違いは、 $V_{ge}$ の負の勾配の形状の微細な調整を可能にする抵抗器 $R_5$ および $R_6$ を含む抵抗分割器に関する。

#### 【0041】

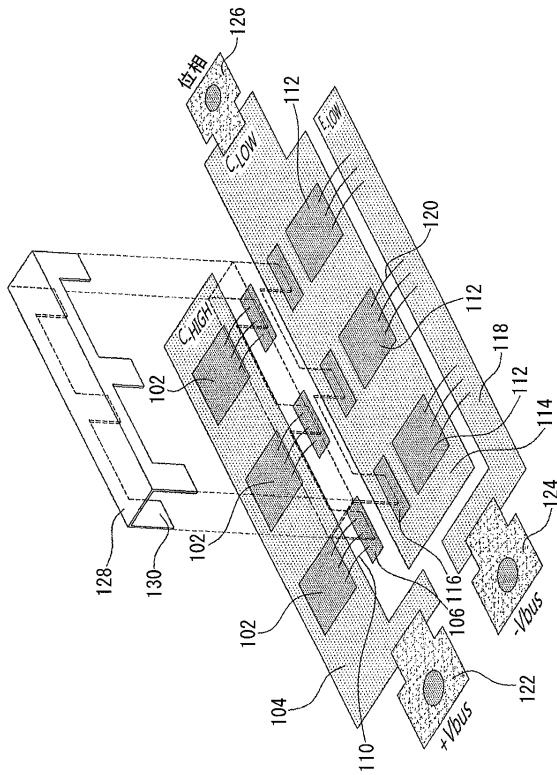

上部IGBT Q2のエミッタインダクタンスを増加させる第2の技術について、図8および図9を参照して説明する。それらは共にIGBTモジュールの配置の変形例を示す。これらのIGBTモジュールレイアウトは図3に示す回路を製造するために用いられ、後述するように、寄生インダクタンス $L_{e-high}$ が適切に調整される。

#### 【0042】

当業者が理解するように、上部IGBTの寄生インダクタンスを増加させることは高周波ループ全体のインダクタンスに影響を及ぼすおそれがあるが、それが過電圧の制御に与える影響の方がより重要である。

#### 【0043】

図8から分かるように、IGBT Q<sub>2</sub>を形成するIGBT 102は、トレース104に載置されるコレクタを有し、したがって、トレース104はC-Highと呼ばれ、それらのエミッタは、ワイヤボンド110を介してエミッタパッド106に接続される。同様に、IGBT Q1を形成するIGBT 112は、C-Lowと呼ばれるトレース114に載置されるコレクタを有し、それらのエミッタはワイヤボンド120を介してトレース118に接続され、したがってトレース118はE-Lowと呼ばれる。

#### 【0044】

トレース114も、それに接続されるコレクタパッド116を有する。

#### 【0045】

+Vbusタブはトレース104に接続され、-Vbusタブはトレース118に接続される。位相タブ126は、トレース114に接続される。

#### 【0046】

明瞭にするために、またこの図は模式的なものであるから、IGBT 102および112のゲートは図8に示していないことに留意すべきである。

#### 【0047】

パッド106および116は、6つの脚部130を有するU字形のコネクタ128によって相互接続され、コネクタ128はパッド106および116に接続するように構成され、サイズが設定され、配置される。当業者が理解するように、U字形のコネクタ128がQ2のエミッタとQ1のコレクタとを相互接続するので、U字形のコネクタ128は寄生インダクタンス $L_{e-high}$ を定義する。U字形のコネクタ128は比較的大きく、直角を含むので、上述したように、 $L_{e-high}$ インダクタンスは比較的高く、IGBT Q2の過電圧を制限するために用いることができる。また、必要とされる所望の寄生インダクタンスに従って、コネクタ128のサイズおよび形状を決定することができることも、理解されよう。

#### 【0048】

次に簡単に図9を参照すると、IGBTモジュールの類似のレイアウトが記載されている。

#### 【0049】

一般的に述べると、図8のレイアウトと図9のレイアウトとの主な違いはタブ106の位置であり、パッド116からより遠くに配置されている。これによって、より大きなコネクタ132、したがってより大きい寄生インダクタンス $L_{e-high}$ を用いることが可能になる。

#### 【0050】

IGBTのターンオフ過電圧の制限は、その応用において、添付の図面に示して上述した構成および部品の詳細に限定されるものでないことを理解すべきである。IGBTのターンオフ過電圧の制限は、他の実施形態で可能であり、また様々な方法で実施することが可能である。本明細書において用いられる語法または用語は、説明することが目的であって、限定することが目的ではないことも、また理解すべきである。それゆえ、上記の説明がその例示的実施形態によって成されたにもかかわらず、主題発明の趣旨、範囲および本質から逸脱することなく、それを変更することができる。

10

20

30

40

50

## 【符号の説明】

## 【0051】

|     |           |    |

|-----|-----------|----|

| 10  | 三相電力コンバータ |    |

| 12  | 三相電力コンバータ |    |

| 14  | コレクタ      |    |

| 16  | エミッタ      |    |

| 18  | ゲート       |    |

| 20  | ゲートドライバ   |    |

| 22  | リファレンス    |    |

| 24  | 平坦部分      | 10 |

| 102 | IGBT      |    |

| 104 | トレース      |    |

| 106 | エミッタパッド   |    |

| 110 | ワイヤボンド    |    |

| 112 | IGBT      |    |

| 114 | トレース      |    |

| 116 | コレクタパッド   |    |

| 118 | トレース      |    |

| 120 | ワイヤボンド    |    |

| 126 | 位相タブ      | 20 |

| 128 | U字形のコネクタ  |    |

| 130 | 脚部        |    |

| 132 | より大きなコネクタ |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

【図9】

---

フロントページの続き

(72)発明者 マーライニン・エル・ヤコウビ

カナダ・ケベック・H 3 H・2 J 7・モントリオール・サン・マチウ・2 2 8 5・アパルトマン・

1 9 0 2

(72)発明者 モハメッド・アマール

カナダ・ケベック・H 2 T・1 W 2・モントリオール・アヴニュ・コロニアル・4 6 5 6

(72)発明者 パスカル・フルリー

カナダ・ケベック・J 0 H・1 S 0・サント・マデレーヌ・プラモンドン・8 0

審査官 神田 太郎

(56)参考文献 特開2 0 0 3 - 3 3 8 7 4 2 (JP, A)

特開平0 7 - 2 0 3 6 8 8 (JP, A)

特開2 0 0 4 - 2 0 1 4 6 2 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 2 M 7 / 4 8

H 0 2 M 1 / 0 0