## (12) 发明专利

(10) 授权公告号 CN 111900156 B

(45) 授权公告日 2025.02.14

(21) 申请号 202010857239.6

(74) 专利代理机构 北京康信知识产权代理有限公司

(22) 申请日 2015.05.14

11240

(65) 同一申请的已公布的文献号

专利代理人 刘彬

申请公布号 CN 111900156 A

(51) Int.CI.

(43) 申请公布日 2020.11.06

H10D 80/20 (2025.01)

(30) 优先权数据

H10D 48/34 (2025.01)

14/277,820 2014.05.15 US

H01L 23/49 (2006.01)

(62) 分案原申请数据

H10D 62/83 (2025.01)

201580037680.7 2015.05.14

H10D 30/66 (2025.01)

(73) 专利权人 沃孚半导体公司

(56) 对比文件

地址 美国北卡罗来纳州

CN 102184914 A, 2011.09.14

(72) 发明人 姆里纳尔·K·达斯 亨利·林

US 2013248883 A1, 2013.09.26

马塞洛·舒普巴赫

CN 101263547 A, 2008.09.10

约翰·威廉斯·帕尔穆尔

CN 202917466 U, 2013.05.01

审查员 曹毓涵

权利要求书2页 说明书8页 附图9页

## (54) 发明名称

高电流、低切换损耗SiC功率模块

## (57) 摘要

本发明公开了高电流、低切换损耗SiC功率模块。一种功率模块包括具有内部腔室的壳体和安装在壳体的内部腔室内的多个切换模块。切换模块互相连接并被配置为促进切换到负载的功率。切换模块中的每个包括至少一个晶体管和至少一个二极管。至少一个晶体管和至少一个二极管可以由宽带隙材料系统(诸如碳化硅(SiC))形成，从而当相比于常规功率模块时，允许该功率模块在高频率以及更低切换损耗下工作。

1.一种功率模块,包括:

壳体,具有内部腔室;

第一端子和第二端子,其中,彼此相对的一部分所述第一端子和一部分所述第二端子布置在彼此的1.5mm内,以减少跨所述功率模块的所述第一端子和所述第二端子两端提供的至少一部分漏电感;

爬电分隔器,在所述第一端子与所述第二端子之间;以及

多个切换模块,在所述第一端子与所述第二端子之间安装在所述内部腔室内,并且所述多个切换模块互相连接以促进切换到负载的功率,其中,所述多个切换模块中的每一者包括至少一个晶体管和至少一个二极管。

2.根据权利要求1所述的功率模块,其中,所述功率模块能够阻断至少1200伏特、并且传导至少120安培,所述功率模块具有小于25毫焦耳的切换损耗。

3.根据权利要求1所述的功率模块,其中,所述至少一个晶体管和所述至少一个二极管是碳化硅器件。

4.根据权利要求3所述的功率模块,其中,所述至少一个晶体管是金属氧化物半导体场效应晶体管,所述至少一个二极管是肖特基二极管。

5.根据权利要求3所述的功率模块,其中,所述至少一个晶体管与所述至少一个二极管反向并联耦接。

6.根据权利要求1所述的功率模块,其中,所述第一端子和所述第二端子包括至少150mm<sup>2</sup>的面积。

7.根据权利要求1所述的功率模块,其中,至少一个二极管是所述至少一个晶体管的内部体二极管。

8.根据权利要求1所述的功率模块,其中,至少一个二极管在所述至少一个晶体管的外部。

9.根据权利要求1所述的功率模块,其中,

所述功率模块进一步包括功率基板;

所述多个切换模块中的每一者进一步包括至少一个栅极电阻器;并且

所述多个切换模块中的每一者的所述至少一个栅极电阻器、所述至少一个晶体管和所述至少一个二极管安装在所述功率基板上,使得所述功率基板的表面提供所述多个切换模块中的每一者的所述至少一个栅极电阻器、所述至少一个晶体管和所述至少一个二极管之间的电气连接。

10.根据权利要求9所述的功率模块,其中,所述功率基板包括氮化铝。

11.根据权利要求10所述的功率模块,进一步包括:底板,使得所述功率基板在所述底板上,并且所述底板包括氮化硅铝。

12.根据权利要求1所述的功率模块,其中,所述爬电分隔器是所述壳体的一部分。

13.根据权利要求1所述的功率模块,其中,所述爬电分隔器提供所述第一端子与所述第二端子之间的电气隔离。

14.一种功率模块,包括:

壳体,具有内部腔室;

第一功率基板和第二功率基板,在所述内部腔室内;

多个晶体管，所述多个晶体管包括第一多个晶体管，其中，所述第一多个晶体管在所述第一功率基板的表面上，所述第一多个晶体管形成一部分切换模块，并且所述多个晶体管进一步包括第二多个晶体管；

所述第二多个晶体管在所述第二功率基板的表面上；以及

栅极连接器，所述栅极连接器经由栅极连接总线耦接至所述第一多个晶体管中的每一者的栅极接触，所述栅极连接总线包括所述第一功率基板的表面上的在所述第一多个晶体管与所述第二多个晶体管之间延伸的栅极总线导电迹线。

15. 根据权利要求14所述的功率模块，其中，所述栅极总线导电迹线在所述第一功率基板和所述第二功率基板的相对侧之间行进。

16. 根据权利要求14所述的功率模块，

其中，所述多个晶体管是碳化硅器件。

17. 根据权利要求16所述的功率模块，其中，所述栅极连接器经由所述栅极连接总线和一条或多条同轴电缆耦接至所述多个晶体管中的每一者的所述栅极接触。

18. 根据权利要求16所述的功率模块，进一步包括：

第一端子和第二端子，所述第一端子和所述第二端子包括至少 $150\text{mm}^2$ 的面积；以及

爬电分隔器，在所述第一端子与所述第二端子之间。

19. 根据权利要求16所述的功率模块，其中，所述功率模块能够阻断至少1200伏特、并且传导至少120安培，所述功率模块具有小于25毫焦耳的切换损耗。

20. 一种功率模块，包括：

壳体，具有内部腔室；

第一端子和第二端子；

爬电分隔器，在所述第一端子与所述第二端子之间；以及

多个切换模块，安装在所述内部腔室内并互相连接以促进切换到负载的功率，其中，所述多个切换模块中的每一者包括至少一个晶体管，所述至少一个晶体管被配置为经由所述至少一个晶体管中的沟道沿第一方向引导电流、并且经由所述至少一个晶体管中的内部体二极管沿与所述第一方向相对的第二方向引导电流，

其中，彼此相对的一部分所述第一端子和一部分所述第二端子布置在彼此的1.5mm内，以减少跨端子提供的至少一部分漏电感。

21. 根据权利要求20所述的功率模块，其中，所述功率模块能够阻断1200伏特、并且传导至少120安培，所述功率模块具有小于25毫焦耳的切换损耗。

22. 根据权利要求20所述的功率模块，其中，所述至少一个晶体管是碳化硅(SiC)器件。

23. 根据权利要求20所述的功率模块，其中，所述第一端子和所述第二端子包括至少 $150\text{mm}^2$ 的面积，以减少所述第一端子和所述第二端子之间的漏电感，并且其中，所述功率模块被配置为以至少50kHz的切换频率工作。

## 高电流、低切换损耗SiC功率模块

[0001] 本申请是分案申请,其母案申请的申请号为2015800376807,申请日为2015年5月14日,发明名称为“高电流、低切换损耗SiC功率模块”。

[0002] 相关申请

[0003] 本申请是2013年5月14日提交的美国专利申请序列号13/893,998的部分继续申请,而后者是2012年8月17日提交的美国专利申请序列号13/588,329的部分继续申请,其要求在2011年9月11日提交的美国临时专利申请号61/533,254的权益,将所述专利的全部公开内容通过引用方式并入本文中。

### 技术领域

[0004] 本公开涉及用于控制到负载的功率传送的功率模块。

### 背景技术

[0005] 随着功率成本持续增长和环境影响问题的增长,对具有提高性能和效率的功率器件的需求持续增长。提供功率器件的性能和效率的一种方法是通过使用碳化硅(SiC)制造器件。相比于常规的硅功率器件,预期由碳化硅(SiC)制成的功率器件在切换速度、功率处理能力和温度处理能力方面上展现出巨大的优势。特别地,当相比于常规的硅器件时,SiC器件的高临界场和宽带隙允许性能和效率两者的增加。

[0006] 由于硅中固有的性能限制,当阻断高电压(例如,大于5kV的电压)时,常规的功率器件会需要双极结构,诸如绝缘栅双极晶体管(IGBT)。虽然利用双极结构大体上降低由于其电导率调制引起的漂移层的电阻,但是双极结构也遭受相对较慢的切换时间。如将由本领域技术人员所清楚的那样,双极结构的反向恢复时间(归因于少数载流子的相对较慢扩散)限制其最大切换时间,从而使得硅器件大体上不适于高电压和高频率应用。

[0007] 由于关于SiC功率器件的上述性能增强,单极SiC功率器件可以用于阻断高达10kV或更大的电压。此类单极SiC功率器件的多数载流子本性有效地消除器件的反向恢复时间,从而允许非常高的切换速度(例如,对于具有10kV阻断能力和约 $100\text{m}\Omega \cdot \text{cm}^2$ 的比导通电阻的双扩散金属氧化物半导体场效应晶体管(DMOSFET)小于100ns)。

[0008] 功率器件经常互相连接且集成为功率模块,所述功率模块工作以通过各种部件诸如电机、转换器、发生器等动态地切换大量功率。如上所讨论,由于功率成本和环境影响问题的持续增长,仍持续需要更小、制造成本更廉价以及更有效,同时提供比它们的常规对应物类似或更好地性能的功率模块。

### 发明内容

[0009] 本公开涉及用于控制到负载的功率传送的功率模块。根据一个实施例,功率模块包括:壳体,具有内部腔室;和多个切换模块,安装在壳体的内部腔室内。切换模块互相连接且被配置为促进切换功率(power)到负载。切换模块中的每个切换模块包括至少一个晶体管和至少一个二极管。同时,切换模块能够阻断1200伏特,传导300安培并具有小于20毫焦

耳的切换损耗。通过将切换模块包括在功率模块中,以使得对于1200V/300A额定值,功率模块具有小于20毫焦耳的切换损耗,当相比于常规的功率模块时,该功率模块的性能显著提高。

[0010] 根据一个实施例,功率模块包括具有内部腔室的壳体、在内部腔室内的至少一个功率基板(power substrate)以及栅极连接器。功率基板包括在功率基板的第一表面上的用于促进切换功率到负载的切换模块。切换模块包括至少一个晶体管和至少一个二极管。栅极连接器经由信号路径耦接到至少一个晶体管的栅极接触,该信号路径包括在功率基板的第一表面上的第一导电迹线。使用在功率基板的第一表面上的导电迹线将栅极连接器连接到至少一个晶体管的栅极,减小功率模块中的干扰,并增加栅极连接器和至少一个晶体管的栅极接触之间的连接可靠性。

[0011] 根据一个实施例,功率模块包括具有内部腔室的壳体、一对输出接触(contact)以及多个切换模块。多个切换模块安装在壳体的内部腔室内,并且互相连接以促进将来自耦接在输出接触之间的功率源的功率切换到负载。该对输出接触被布置为使得输出接触的每个输出接触的至少 $150\text{mm}^2$ 的面积位于距离另一输出接触小于 $1.5\text{mm}$ 。提供距离另一输出接触小于 $1.5\text{mm}$ 的至少 $150\text{mm}^2$ 的每个输出接触的面积减少输出接触之间的漏电感,从而增加功率模块的性能。

[0012] 在阅读以下与附图相关联的优选实施例的详细描述后,本领域的技术人员将清楚本公开的范围并实现本公开的另外方面。

## 附图说明

[0013] 结合在本说明书中且形成本说明书一部分的附图与用于解释本公开原则的描述一起示出本公开的各种方面。

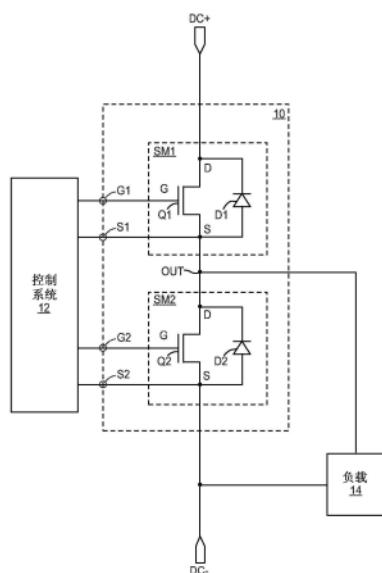

[0014] 图1是示出根据本公开一个实施例的功率模块的细节的示意图。

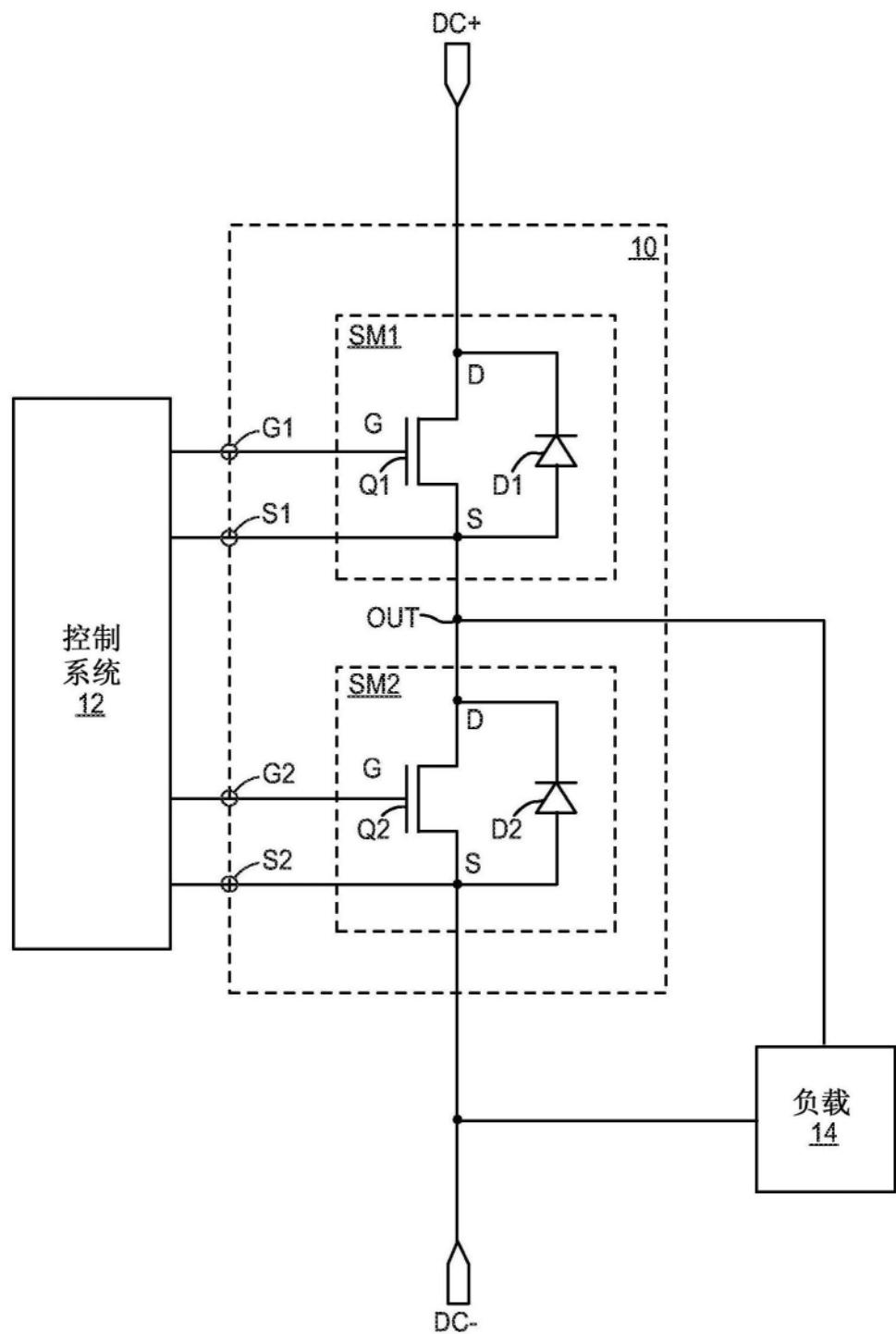

[0015] 图2是示出由图1所示的功率模块产生的各种信号的图形。

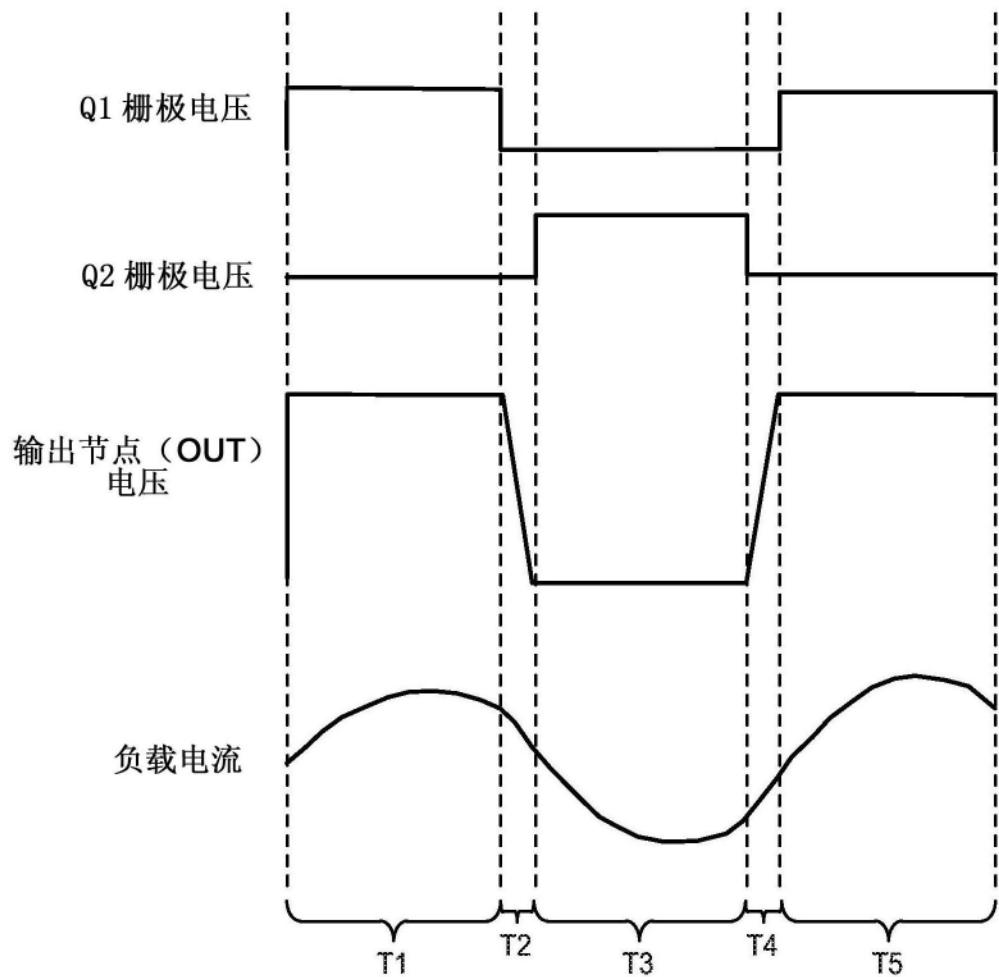

[0016] 图3是示出在图1所示的功率模块中的切换模块的细节的示意图。

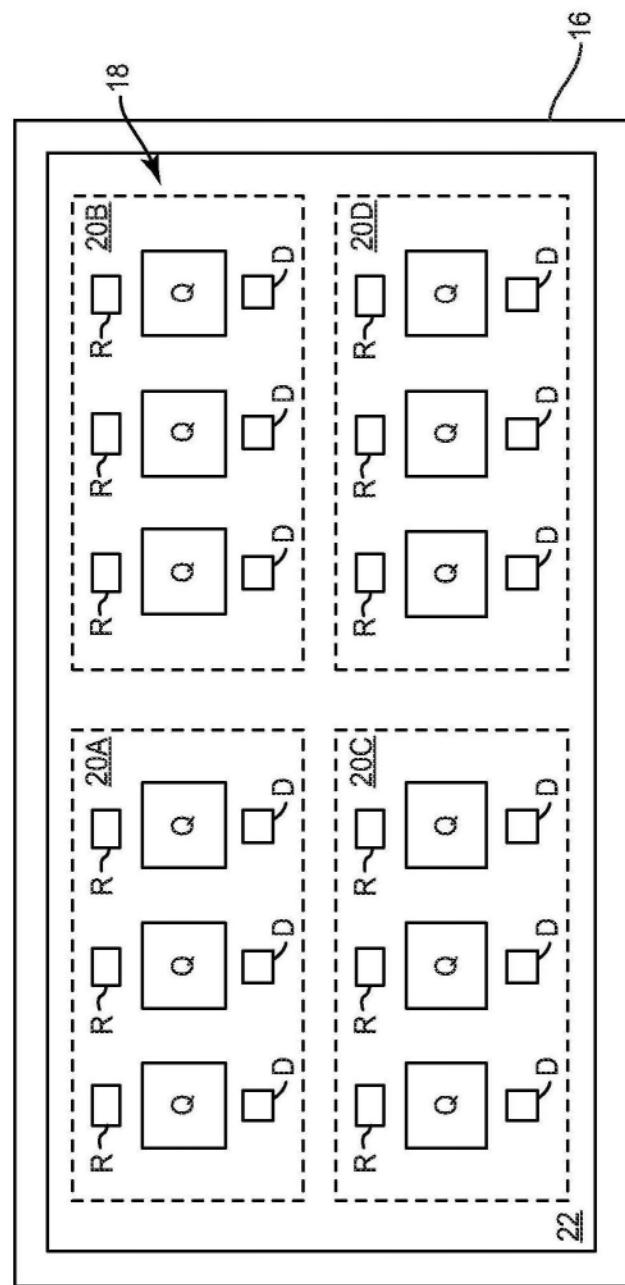

[0017] 图4是示出根据本公开一个实施例的图1所示的功率模块的细节的方框图。

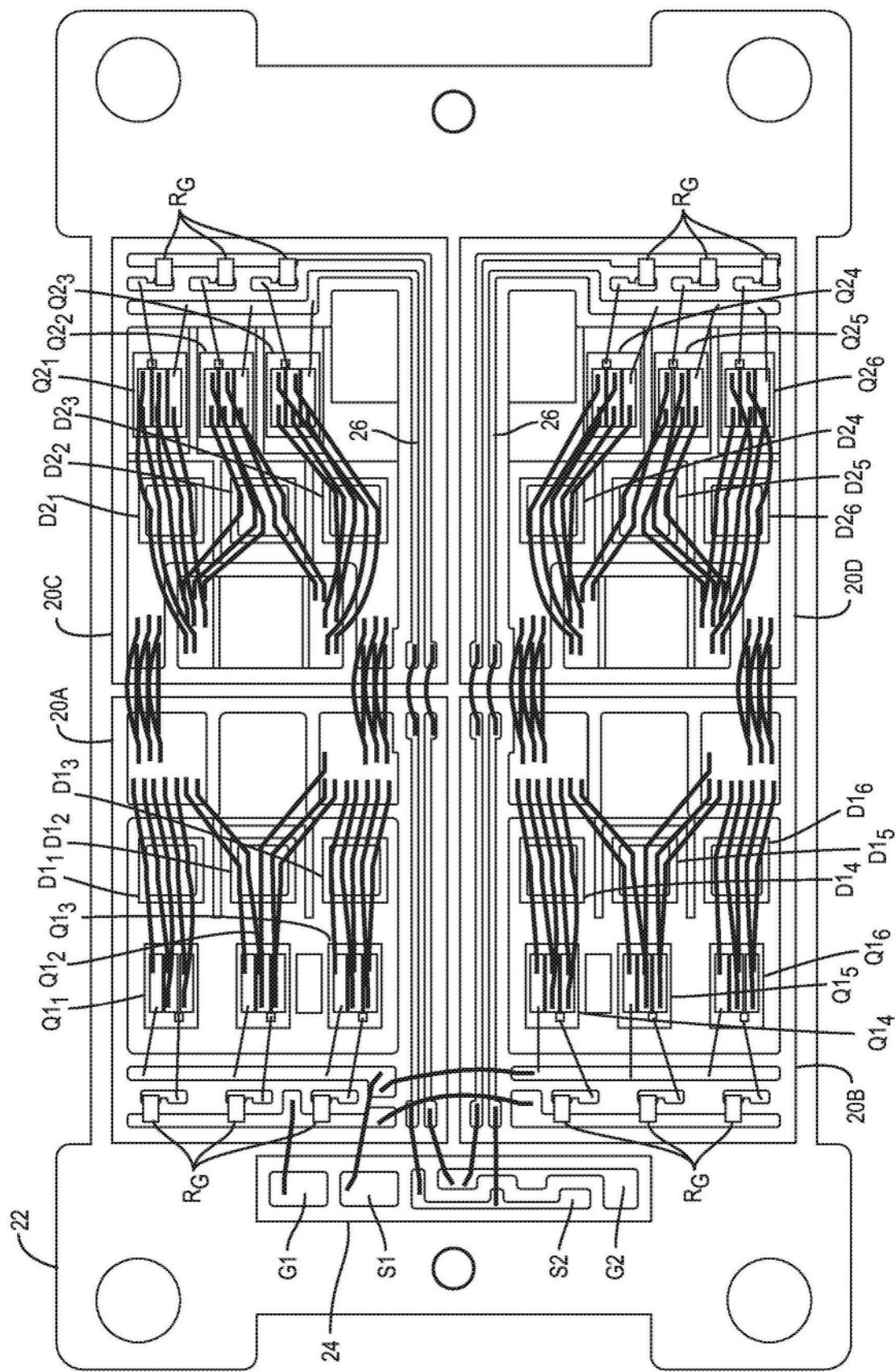

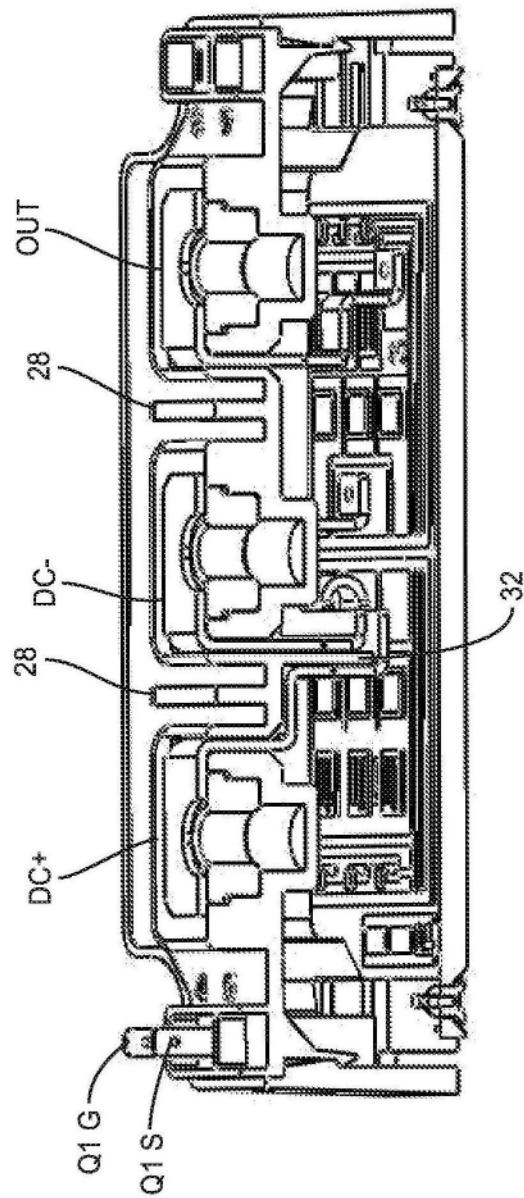

[0018] 图5是示出根据本公开一个实施例的图1所示的功率模块的细节的平面图。

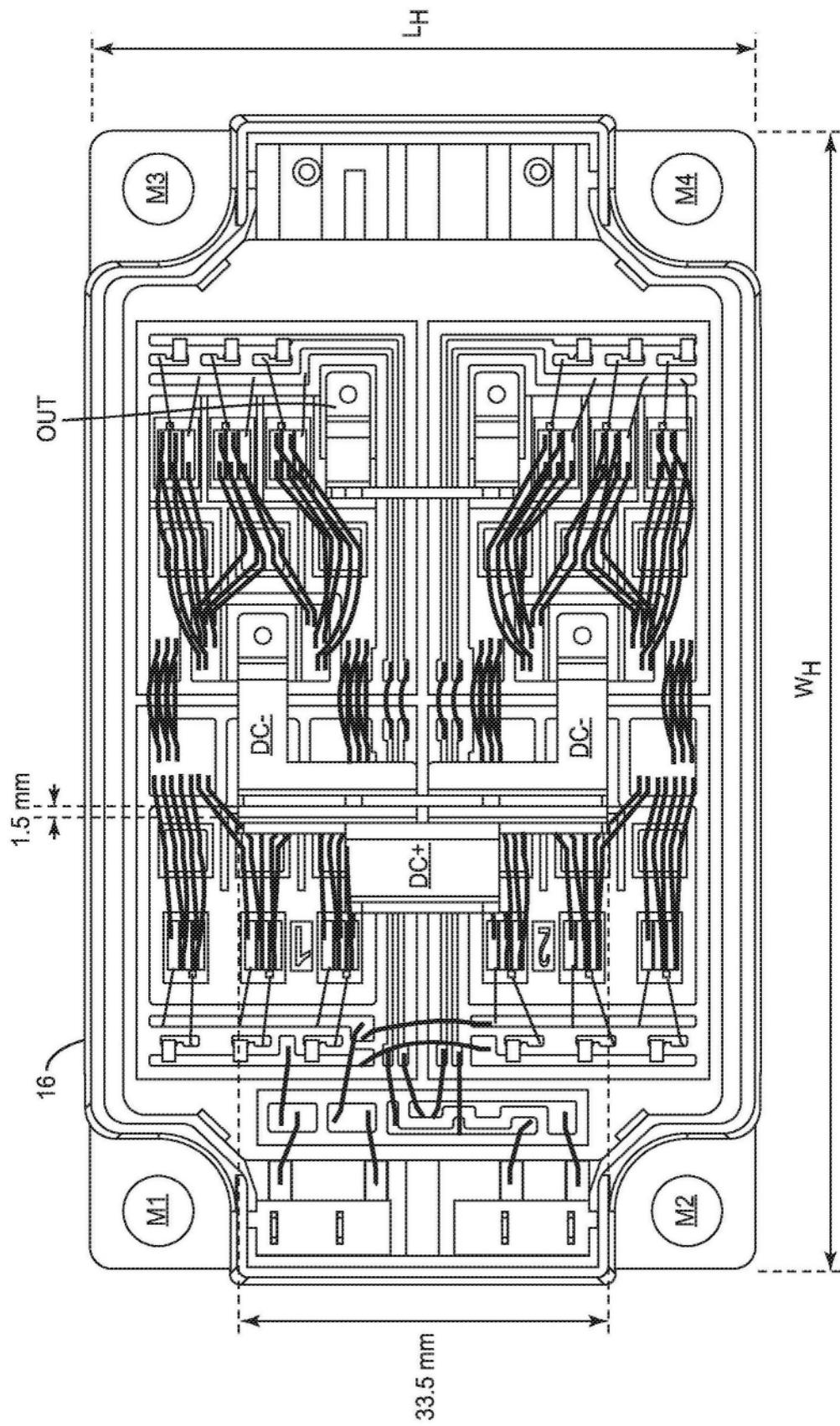

[0019] 图6是示出根据本公开一个实施例的图1所示的功率模块的另外细节的平面图。

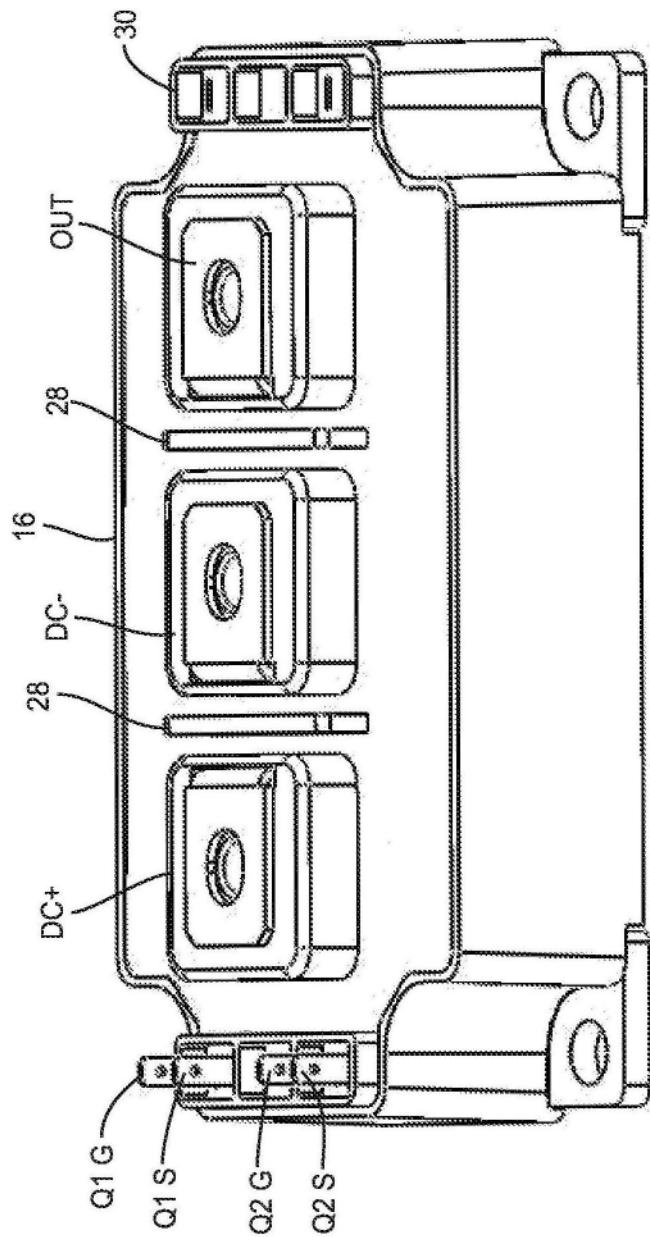

[0020] 图7是示出根据本公开一个实施例的图1所示的功率模块的外壳体的平面图。

[0021] 图8是示出根据本公开一个实施例的图1所示的功率模块的外壳体细节的平面图。

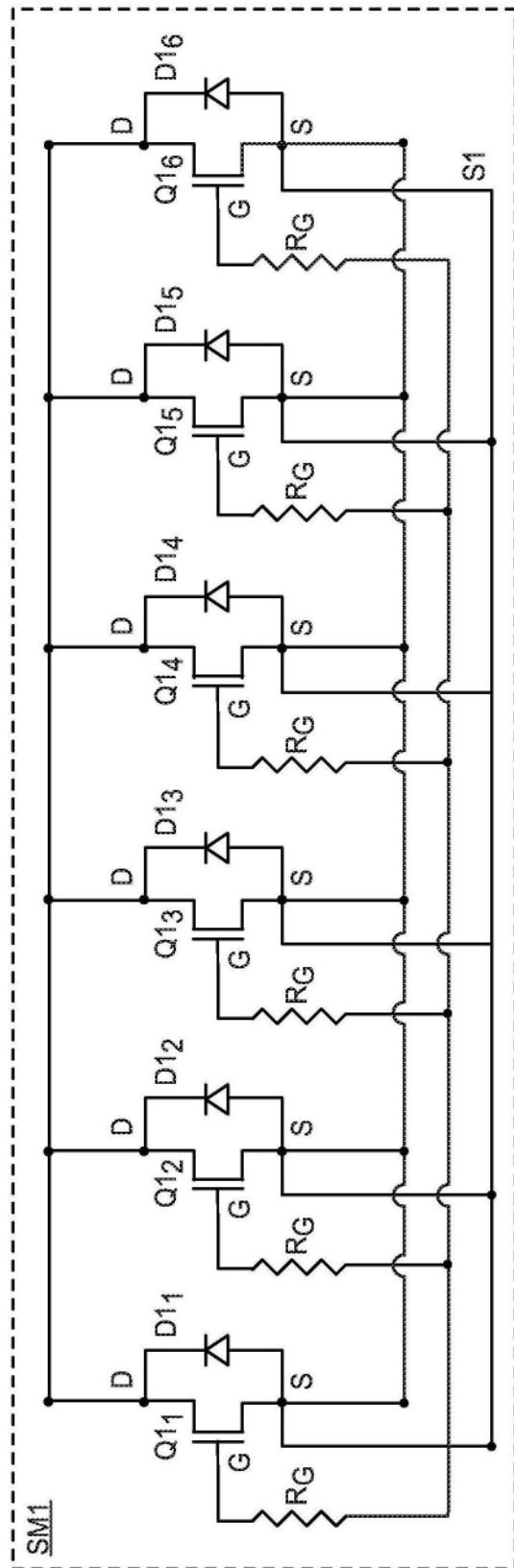

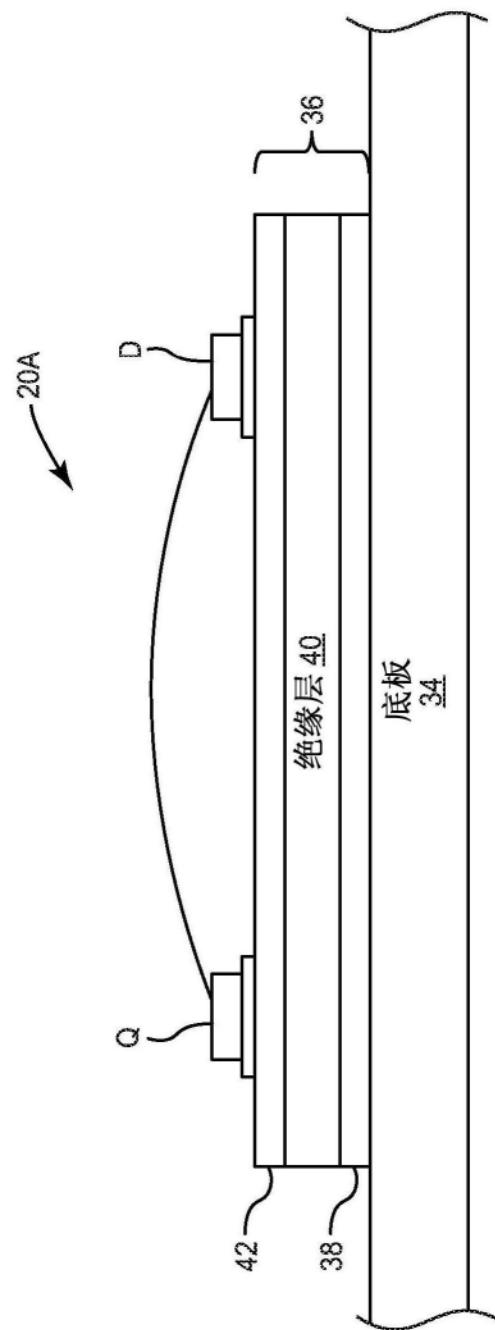

[0022] 图9是示出根据本公开一个实施例的图4所示的功率模块中的功率基板的细节的方框图。

## 具体实施方式

[0023] 以下阐述的实施例表示使得本领域技术人员能够实践实施例必要的信息并且示出实践实施例的最佳模式。在根据附图阅读以下描述后,本领域技术人员将理解本公开的概念并将意识到在此并未具体提及这些概念的应用。应理解,这些概念和应用落在本公开的范围和所附权利要求内。

[0024] 将理解,尽管在本文中术语第一、第二等可以用于描述各种元件,但是这些元件不

应受限于这些术语。这些术语仅用于区分元件。例如,在不背离本公开的范围情况下,第一元件可以被称为第二元件,并且类似地,第二元件可以被称为第一元件。如本文所使用,术语“和/或”包括相关联所列项目中的一个或多个的任意组合和所有组合。

[0025] 应理解,当元件诸如层、区域或基板被称为“在”另一元件“上”或延伸“到”另一元件“上”时,其可以直接在另一个元件或直接延伸到另一个元件上或者也可以存在介入元件。相反,当元件被称为“直接在”另一元件“上”或“直接”延伸“到”另一元件上时,不存在介入元件。同样,将理解,当元件诸如层、区域或基板被称为“在”另一元件“之上”或延伸“在”另一元件“之上”时,其可以直接在另一个元件之上或直接延伸在另一个元件之上,或者也可以存在介入元件。相反,当元件被称为“直接在”另一元件“之上”或“直接”延伸“在”另一元件“之上”时,不存在介入元件。还将理解,当元件被称为“连接”或“耦接”到另一元件时,其可以直接连接或耦接到另一个元件,或者可以存在介入元件。相反,当元件被称为“直接连接”或“直接耦接”到另一元件时,不存在介入元件。

[0026] 相对术语诸如“在…下方”或“在…上方”或“上部”或“下部”或“水平”或“垂直”在文中可以用于描述一个元件、层或区域对如图中所示出的另一元件、层或区域的关系。应理解,这些术语和上述讨论的术语旨在涵盖除了图中所描绘的方位之外的器件的不同方位。

[0027] 本文中所使用的术语仅用于描述具体实施例的目的,并不旨在成为本公开的限制。如本文所使用,除非上下文另外清楚地指示,否则单数形式“一”、“一个”和“该”也旨在包括复数形式。另外应理解,当术语“包含”、“包含的”、“包括”和/或“包括的”用于本文时,其指定所述特征、整数、步骤、工作、元件和/或部件的存在,但不排除一个或多个其它特征、整数、步骤、工作、元件、部件和/或其组的存在或添加。

[0028] 除非另有定义,否则本文所使用的所有术语(包括技术术语和科学术语)均具有与本公开所属领域中技术人员通常理解的含义相同。将另外理解,本文所使用的术语应当被解释为与它们本说明书和相关领域的上下文中的含义相一致,并且不以理想化或过度形式化的意义来解释,除非本文明确地这么定义。

[0029] 图1示出根据本公开一个实施例的示例性功率模块10。功率模块10包括两个切换模块SM1和SM2,所述两个切换模块通过控制系统12控制以受控方式将来自电源(DC+/DC-)的电力传送到负载14。如本领域技术人员将理解,切换模块SM1和SM2形成半桥,所述切换模块的细节在以下讨论。切换模块SM1和SM2中的每个切换模块包括与第一二极管反向并联的至少第一晶体管。特定地,第一切换模块SM1包括与第一二极管D1反向并联的第一晶体管Q1,并且第二切换模块SM2包括与第二二极管D2反向并联的第二晶体管Q2。在一个实施例中,第一晶体管Q1和第二晶体管Q2是金属氧化物半导体场效应晶体管(MOSFET)。然而,本领域的技术人员将清楚,在不背离本公开的原则情况下,任何合适的切换器件,例如,绝缘栅双极晶体管(IGBT)、场效应晶体管(FET)、结型场效应晶体管(JFET)、高电子迁移率晶体管(HEMT)等,均可以用于切换模块SM1和SM2中。第一二极管D1和第二二极管D2可以是肖特基二极管,并且具体是结型势垒肖特基二极管。再次,本领域技术人员将清楚,在不背离本公开的原则情况下,任何合适的二极管器件,例如,P-N二极管和PiN二极管可以用于切换模块SM1和SM2。在一个实施例中,省略了第二二极管D1和第二二极管D2,并且它们的功能分别由第一晶体管Q1和第二晶体管Q2的内部体二极管(internal body diode)替代。使用替代第一二极管D1和第二二极管D2的第一晶体管Q1和第二晶体管Q2的内部体二极管可在功率

模块10中节约空间和成本。

[0030] 第一晶体管Q1的栅极接触G和第一晶体管Q1的源极接触S耦接到控制系统12。类似地,第二晶体管Q2的栅极接触G和源极接触S也耦接到控制系统12。显著地,从第一晶体管Q1和第二晶体管Q2的栅极接触G到控制系统12的连接可以分别经由相对较低功率栅极连接器G1和G2实现。类似地,从第一晶体管Q1和第二晶体管Q2的源极接触S到控制系统12的连接,可以分别经由用于测量第一晶体管Q1和第二晶体管Q2的一个或多个工作参数的低电源返回连接(low-power source return connection)S1和S2实现。第一晶体管Q1的漏极接触D耦接到正电源端子DC+。第二晶体管Q2的漏极接触D耦接到输出端子OUT。第一晶体管Q1的源极接触S也耦接到输出端子OUT。第二晶体管Q2的源极接触S耦接到负电源端子DC-。最后,负载14耦接在输出端子OUT和负DC电源端子DC-之间。

[0031] 第一晶体管Q1、第一二极管D1、第二晶体管Q2以及第二二极管D2可各自为多数载流子器件。多数载流子器件大体上包括FET,诸如MOSFET、HEMT、JFET等,但不包括晶闸管、双极晶体管以及绝缘栅极双极晶体管(IGBT)。因此,当相比于采用双极器件的常规功率模块时,功率模块10可以能够在高切换速度下工作并且遭受较低的切换损耗。在一个实施例中,第一晶体管Q1、第一二极管D1、第二晶体管Q2以及第二二极管D2是宽带隙器件(wide band-gap device)。出于本公开的目的,宽带隙器件时具有大于或等于3.0电子伏特(eV)的带隙的半导体器件。例如,第一晶体管Q1、第一二极管D1、第二晶体管Q2以及第二二极管D2可以是碳化硅(SiC)器件或氮化镓(GaN)器件。出于参考目的,Si具有约1.1eV的带隙,而SiC具有约3.3eV的带隙。如上所讨论,当相比于常规硅(Si)IGBT基功率模块时,使用SiC用于第一晶体管Q1、第一二极管D1、第二晶体管Q2以及第二二极管D2显著地减少每个器件的切换时间,并另外遭受更低的切换损耗。例如,如果功率模块10的额定值是1200V和300A,那么功率模块10在-40°C和150°C之间工作时,在各种实施例中可维持小于25毫焦耳(mJ)、小于20mJ以及甚至小于15mJ的切换损耗,同时也提供低导通状态电压降。如本领域技术人员将理解,功率模块10的切换损耗将不会将到低于1mJ。在另外实施例中,第一晶体管Q1、第一二极管D1、第二晶体管Q2以及第二二极管D2是多数载流子器件和带宽隙器件。

[0032] 在工作中,控制系统12以互补方式操作第一切换模块SM1和第二切换模块SM2,以使得当第一切换模块SM1导通时,阻断第二切换模块SM2,并且反之亦然。示出在功率模块10的切换周期过程中的第一晶体管Q1的栅极接触G处的电压、第二晶体管Q2的栅极接触G处的电压、输出端子OUT处的电压以及通过负载14的电流的图形示出在图2中。在第一时段T1期间,第一切换模块SM1导通,同时阻断第二切换模块SM2。因此,输出端子OUT连接到正电源端子DC+,从而将正电源电压提供到负载14并使得电流从正电源端子DC+流经第一晶体管Q1并流入负载14中。一般,负载14是感应负载,从而使得在第一切换模块SM1导通时通过负载14的电流缓慢提高。

[0033] 在第二时段T2期间,第一切换模块SM1切换到阻断模式。另外,第二切换模块SM2保持阻断模式。在这时段内,由于与第一切换模块SM1和第二切换模块SM2中每个切换模块相關联的内部电容,电流持续从输出端子OUT流到负载14。特定地,通过负载14的约一半电流由切换模块SM1和SM2中的每个切换模块的内部电容提供。因此,在输出端子OUT处的电压以给定速率转换到接地,并且通过负载14的电流逐渐降低。

[0034] 当在第三时段T3中第二切换模块SM2切换到导通模式时,输出端子OUT耦接到负电

源端子DC-,所述负电源端子DC-在一些实施例中可以接地。因此,电流流经第二晶体管Q2并通过输出端子OUT流入负载14中,使得电流变得越来越负。

[0035] 在第四时段T4期间,第二切换模块SM2切换到阻断模式。另外,第一切换模块SM1处于阻断模式中。在这时段中,由于与第一切换模块SM1和第二切换模块SM2中每个切换模块相关联的内部电容,负电流持续从输出端子OUT流向负载。特定地,通过负载14的约一半电流由切换模块SM1和SM2中的每个切换模块的内部电容提供。因此,在输出端子OUT处的电压从接地转换到在正电源端子DC+处提供的正电源电压,并且通过负载14的电流越来越正。最后,在第五时段T5期间,切换周期重新开始,以使得第一切换模块SM1处于导通模式,而第二切换模块SM2处于阻断模式。

[0036] 图3示出根据本公开一个实施例的第一切换模块SM1的细节。第二切换模块SM2可以经配置类似于第一切换模块SM2,但是为简便起见未示出。如图3所示,第一切换模块SM1的第一晶体管Q1和第一二极管D1可包括并联耦接的多个晶体管Q1<sub>1-6</sub>和多个反向并联二极管D1<sub>1-6</sub>。特定地,多个晶体管Q1<sub>1-6</sub>中每个晶体管的漏极接触D可以耦接在一起,晶体管Q1<sub>1-6</sub>中每个晶体管的源极接触S可以耦接在一起,并且晶体管Q1<sub>1-6</sub>中每个晶体管的栅极接触G可通过栅极电阻器R<sub>G</sub>各自耦接在一起。晶体管Q1<sub>1-6</sub>中每个晶体管包括耦接在源极接触S和其漏极接触D之间的反向并联二极管Q1<sub>1-6</sub>。尽管六个晶体管Q1<sub>1-6</sub>示出与六个反向并联二极管D1<sub>1-6</sub>并联耦接,但是在不背离本公开的原则情况下,可以使用任何数目的晶体管和反向并联的二极管。

[0037] 包括多个并联耦接的晶体管Q1<sub>1-6</sub>和多个反向并联二极管D1<sub>1-6</sub>允许第一切换模块SM1处理比其它方式可能的更大量的功率。例如,在一个实施例中,晶体管Q1<sub>1-6</sub>中每个晶体管被额定为阻断1.2kV并传导50A,从而使得第一切换模块SM1能够传导300A。在其它实施例中,晶体管Q1<sub>1-6</sub>中每个晶体管可以被额定为阻断1.2kV并传到40A,从而使得第一切换模块SM1能够传导240A。在又一实施例中,晶体管Q1<sub>1-6</sub>中每个晶体管可以被额定为阻断1.2kV并传到20A,从而使得第一切换模块SM1能够传导120A。

[0038] 可以提供栅极电阻器R<sub>G</sub>以在第一切换模块SM1中抑制当第一切换模块SM1以相对高的转变速度(例如,大于20V/ns)驱动时可能发生的任何不期望的振荡。栅极电阻器R<sub>G</sub>的电阻可根据晶体管Q1<sub>1-6</sub>中每个晶体管的额定电流以及因此第一切换模块SM1的所有额定电流而改变。在其中第一切换模块SM1具有120A的额定电流的实施例中,栅极电阻器R<sub>G</sub>中每个电阻器具有约1Ω和15Ω之间的电阻。在其中第一切换模块SM1具有240A的额定电流的另外实施例中,栅极电阻器R<sub>G</sub>中每个电阻器具有约1Ω和15Ω之间的电阻。在其中第一切换模块SM1具有300A的额定电流的又一实施例中,栅极电阻器中每个电阻器具有约15Ω和20Ω之间的电阻。

[0039] 图4示出根据本公开一个实施例的功率模块10的细节。如图4所示,功率模块10包括设置有保持一个或多个功率基板20的内部腔室18的壳体16。特定地,壳体16的内部腔室18保持第一功率基板(power substrate)20A、第二功率基板20B、第三功率基板20C以及第四功率基板20D。本领域技术人员将清楚,在不背离本公开的原则的情况下,壳体16的内部腔室18可容纳任何数目的功率基板20。示出功率基板20中的每个功率基板包括表示第一切换模块SM1和第二切换模块SM2的主要部件的多个晶体管Q、多个二极管D以及多个电阻器R。在一个实施例中,第一切换模块SM1由第一功率基板20A和第二功率基板20B提供,而第二切

换模块SM2分别由第三功率基板20C和第四功率基板20D提供。在功率基板20的每个功率基板上的部件之间的必要互相连接可以由在功率基板20的表面上的金属迹线(未示出)提供。另外,可以提供焊线(未示出)以互相连接不同的功率基板20以及将功率基板20连接到一个或多个外部连接器(未示出)。功率基板20可以安装到附着于壳体16的安装结构22上。在一个实施例中,安装结构22是平面散热器,所述平面散热器还起到散发由第一切换模块SM1和第二切换模块SM2产生的热量的作用。

[0040] 如以上所讨论,多个晶体管Q和二极管D可以是多数载流子器件,从而降低与晶体管Q和二极管D中每个相关联的切换时间和损耗。因此,功率模块10比常规功率模块,可在更高频率下工作并遭受更小的切换损耗。另外,晶体管Q和二极管D可以是宽带隙器件(wide band-gap device),诸如SiC器件。如以上所讨论,使用SiC用于晶体管Q和二极管D显著地减少晶体管Q和二极管D的切换时间和切换损耗,从而增加功率模块10的性能。

[0041] 图5示出根据本公开一个实施例的示例性安装结构22和功率基板20的细节。如图5所示,第一功率基板20A、第二功率基板20B、第三功率基板20C以及第四功率基板20D设置在安装结构22上。第一功率基板20A包括第一切换模块SM1的六个晶体管中三个晶体管Q<sub>1-3</sub>、三个栅极电阻器R<sub>G</sub>以及六个反向并联二极管中三个反向并联二极管D<sub>1-3</sub>。第二功率模块包括第一切换模块SM1的剩余晶体管Q<sub>1-6</sub>、栅极电阻器R<sub>G</sub>以及反向并联二极管D<sub>1-6</sub>。类似地,第三功率模块20C包括第二切换模块SM2的六个晶体管中三个晶体管Q<sub>2-3</sub>、三个栅极电阻器R<sub>G</sub>以及六个反向并联二极管中三个反向并联二极管D<sub>2-3</sub>。第四功率基板20D包括第二切换模块SM2的剩余晶体管Q<sub>2-6</sub>、栅极电阻器R<sub>G</sub>以及反向并联二极管D<sub>2-6</sub>。较厚的黑线表示功率模块10中各种部件之间和功率模块10的各种部件和一个或多个输出端24之间的焊线。功率模块10的输出端24包括如上所讨论的第一栅极连接器G1、第二栅极连接器G2、第一源极返回连接器S1以及第二源极返回连接器S2。在功率基板20上的部件之间的其它连接有金属迹线提供。显著地,栅极总线26设置在功率基板20上,并在第二切换模块SM2中的晶体管Q<sub>2-6</sub>的栅极接触G和功率模块的输出端24之间行进。特定地,栅极总线26在第二切换模块SM2中的晶体管Q<sub>2-6</sub>的栅极接触G和第二栅极连接器G2之间行进,并且可另外提供从第二切换模块SM2中的晶体管Q<sub>2-6</sub>的源极接触S到第二源极返回连接器S2的低的功率路径。栅极总线26是在功率基板20的每个功率基板上的金属迹线,所述金属迹线减少功率模块10的干扰,并且增加第二切换模块SM2中的晶体管Q<sub>2-6</sub>的栅极接触和功率模块10的输出端24之间的连接可靠性,尤其是当相比于在常规功率模块中使用的“跨”栅极连接时。如所示,安装结构22可形成散热器的所有部分或一部分,所述散热器起到散发由第一切换模块SM1和第二切换模块SM2产生的热量的作用。

[0042] 在一个实施例中,栅极总线26可以由一个或多个同轴电缆替换以连接第二切换模块中的晶体管Q<sub>2-6</sub>的栅极接触G和功率模块10的输出端24。当相比于其他解决方案时,使用同轴电缆以将输出端连接到晶体管Q<sub>2-6</sub>的栅极接触G可提供改进的隔离,从而改进功率模块10的性能。另外,尽管针对切换模块SM1和第二切换模块SM2两者的栅极接触G的输出端均设置在壳功率模块10的壳体16的相同侧上,但是在其它实施例中,它们可以设置在壳体16的相对侧上。将第一切换模块SM1和第二切换模块SM2的栅极接触G的输出端24设置在壳体16的相对侧上,可将较短的连接路线提供给第二切换模块SM2的栅极接触G中每个栅极接触,从而减少干扰并改进功率模块10的耐用性。另外,将第一切换模块SM1和第二切换模块

SM2的栅极接触G的输出端24设置在壳体16的相对侧上,可减少在第二切换模块SM2中晶体管Q2<sub>1-6</sub>中每个晶体管的栅极电阻器R<sub>G</sub>的所需电阻,因为栅极接触G和输出端24之间的较短连接路径减少由晶体管Q2<sub>1-6</sub>看到的振荡量。

[0043] 图6示出根据本公开一个实施例的壳体16、输出端子OUT、正电源端子DC+以及负电源端子DC-的另外细节。如图6所示,壳体16基本上是矩形的,包括用于将功率模块10安装到平台的安装孔M1-M4的切口。另外,示出正电源端子DC+、负电源端子DC-以及输出端子OUT。如本领域技术人员将清楚,在正电源端子DC+和负电源端子DC-两端的杂散电感尤其是在功率模块10的高频率工作下可导致功率模块10的性能降低。因此,正电源端子DC+和负电源端子DC-彼此靠近地设置,大体上间隔开小于1.5mm,以便减轻端子两端的漏电感。另外,端子可以被制成宽的,大体上约33.5mm宽,以便最大化相对端子附近的面积。一般,正电源端子DC+和负电源端子DC-在彼此1.5mm间隔内将具有约150mm<sup>2</sup>和200mm<sup>2</sup>之间的面积。在一个实施例中,正电源端子DC+和负电源端子DC-在彼此1.5mm间隔内将具有约187.31mm<sup>2</sup>的面积。如本领域技术人员将清楚,通过将正电源端子DC+的相对较大面积置于紧密地靠近负电源端子DC-的较大面积产生的电容效应减少端子之间的漏电感,从而改进功率模块10的性能。

[0044] 图7示出根据本公开一个实施例的壳体16的另外细节。如图7所示,壳体16包括功率基板20,并且提供用于正电源端子DC+、负电源端子DC-、输出端子OUT以及相应路径的输出端子,以将第一切换模块SM1和第二切换模块SM2连接到控制系统12。显著地,壳体16和各种输出端子是工业标准的,从而允许功率模块10用作原有平台的置入式解决方案。此外,爬电分隔器(creepage divider)28设置在正电源端子DC+、负电源端子DC-以及输出端子OUT的每个之间,其增加了相应端子之间的爬电距离约50%。因此,功率模块10可以用于较高电压应用中,而不会由短路或其它损害的风险。

[0045] 如图7所示,一个或更多未用端子位置30可存在于壳体16中。未使用的端子位置30可以用于为功率模块10的一个或多个部件提供开尔文(Kelvin)连接,或者可以用于向在各种实施例中包括在功率模块10中的NTC温度传感器模块提供连接。

[0046] 图8示出根据本公开一个实施例的功率模块10的切口(cutaway)视图。显著地,另外的爬电分隔器32设置在正电源端子DC+和负电源端子DC-之间,其将相应的节点彼此分离,并因此保护免于在高压下短路,而同时允许功率模块10利用以上所讨论的节点之间的漏电感的减少。

[0047] 图9示出根据本公开一个实施例的第一功率基板20A的细节。第二功率基板20B、第三功率基板20C以及第四功率基板20D可以被配置为类似于第一功率基板20A,但是为了简便起见未示出。如图9所示,第一功率基板20A形成在底板(baseplate)34(其可以是铜)上。本领域技术人员将理解,存在用于底板34的许多不同的材料,所有这些材料均涵盖在本文中。在一个实施例中,底板34为碳化铝硅(A1SiC),其可以是比铜重量更轻并提供与一个或多个所附部件更好的热匹配。底板34可以共享在功率基板20中每个功率基板之间,以使得第一功率基板20A、第二功率基板20B、第三功率基板20C以及第四功率基板20D均形成在底板34上。直接粘合铜(DBC)基板36可以设置在底板34之上。DBC基板36可包括在底板34表面上的第一金属层38、在第一金属层38之上的绝缘层40以及在绝缘层40之上与第一金属层38相对的第二金属层42。第一金属层38和第二金属层42可以是例如铜。本领域技术人员将清楚,存在用于第一金属层38和第二金属层42的许多不同的合适材料,所有这些材料均涵盖

在本文中。绝缘层40可以是例如氮化铝(A1N)。本领域技术人员将清楚,存在用于绝缘层40的许多不同合适的材料,例如氧化铝( $\text{Al}_2\text{O}_3$ )或氮化硅( $\text{Si}_3\text{N}_4$ ),所有这些材料均涵盖在本文中。

[0048] 当相比于常规氧化铝或氮化硅(SiN)层时,使用A1N用于绝缘层40可提供高得多的热导率。鉴于与SiC器件相关联的相对低的电阻和A1N的低热电阻,因此功率模块10可比常规功率模块处理更高的电流。可以基于目标隔离电压选择绝缘层40的厚度。由于通过使用SiC部件和A1N绝缘层40提供的优点,功率模块10能够比相同尺寸的常规器件处理更大的功率,并且/或者可以比其常规对应物减小到更小的尺寸。

[0049] 本领域技术人员将认识到对本公开优选实施例的改进和修改。所有此类改进和修改均被认为在本文所公开的概念的范围内和以下权利要求书内。

图1

图2

图3

图4

图5

图6

图7

图8

图9