(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5085939号

(P5085939)

(45) 発行日 平成24年11月28日(2012.11.28)

(24) 登録日 平成24年9月14日(2012.9.14)

(51) Int.Cl.

G06F 12/16 (2006.01)

F 1

G06F 12/16 340P

請求項の数 14 (全 18 頁)

(21) 出願番号 特願2006-547166 (P2006-547166)

(86) (22) 出願日 平成16年12月16日 (2004.12.16)

(65) 公表番号 特表2007-520801 (P2007-520801A)

(43) 公表日 平成19年7月26日 (2007.7.26)

(86) 國際出願番号 PCT/US2004/042462

(87) 國際公開番号 WO2005/066973

(87) 國際公開日 平成17年7月21日 (2005.7.21)

審査請求日 平成19年12月7日 (2007.12.7)

(31) 優先権主張番号 10/751,096

(32) 優先日 平成15年12月31日 (2003.12.31)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 511226960

サンディスク テクノロジース インコ

ーポレイテッド

アメリカ合衆国、75024、テキサス州

、プレーノ、ノース・ダラス・パークウ

エイ 6900、ツワー・レガシー・タウ

ン・センター

(74) 代理人 100075144

弁理士 井ノ口 毅

(72) 発明者 リン、ジェイソン

アメリカ合衆国、95051、カリフォル

ニア州、サンタ クララ、インバーソン

コート 2670

最終頁に続く

(54) 【発明の名称】書き込み／消去失敗検出機構を有するフラッシュ記憶システム

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のデータ記憶領域を備える不揮発性メモリであって、

各データ記憶領域が、

ユーザデータ部と、

オーバーヘッドラーダ部と、を備え、

各データ記憶領域のオーバーヘッドラーダ部が第1のフラグを含み、

前記不揮発性メモリは、第1のデータ記憶領域にユーザデータの第1の論理ページを書き込み、第2のデータ記憶領域にユーザデータの第2の論理ページを書き込み、また第2のデータ記憶領域の第1のフラグを利用することによって、第1のデータ記憶領域が適正に書き込まれたことを示すように構成され、た不揮発性メモリにおいて、

各データ記憶領域の第1のフラグをデータ記憶領域のユーザデータ部と同時に書き込み

、各データ記憶領域のオーバーヘッドラーダ部は、そのデータ記憶領域自体が適正に書き込まれたことを示す第2のフラグをさらに含む不揮発性メモリ。

## 【請求項 2】

請求項1記載の不揮発性メモリにおいて、

前記データ記憶領域は、それぞれデータセクタに対応する不揮発性メモリ。

## 【請求項 3】

請求項1または2記載の不揮発性メモリにおいて、

10

20

前記データ記憶領域を複数の消去ユニットに編成し、各消去ユニット内の所定のデータ記憶領域のオーバーヘッドデータ部は、所定のデータ記憶領域が属する消去ユニットが消去動作を完了したことを示す第3のフラグをさらに含む不揮発性メモリ。

**【請求項4】**

請求項3記載の不揮発性メモリにおいて、前記第3のフラグは、複数ビットからなる不揮発性メモリ。

**【請求項5】**

請求項1記載の不揮発性メモリにおいて、前記データ記憶領域を複数の消去ユニットに編成し、

前記消去ユニットは、それぞれそのオーバーヘッドデータ部が前記第2のフラグを有するが、前記第1のフラグを有していない追加のデータ記憶領域をさらに含む不揮発性メモリ。

**【請求項6】**

請求項5記載の不揮発性メモリにおいて、

前記第1のフラグを有していないデータ記憶領域のそれぞれのオーバーヘッドデータ部は、前記第1のフラグを有していないデータ記憶領域が属する消去ユニットが消去動作を完了したことを示す第3のフラグを含む不揮発性メモリ。

**【請求項7】**

請求項6記載の不揮発性メモリにおいて、

前記データ記憶領域は、所定のシーケンスに従って書き込まれ、前記データ記憶領域とは別のデータ記憶領域は、シーケンスにおいて先行するデータ記憶領域であり、

前記第1のフラグを有していないデータ記憶領域は、それらが属するそれぞれのプロック内の前記シーケンスにおける第1のデータ記憶領域である不揮発性メモリ。

**【請求項8】**

請求項1記載の不揮発性メモリにおいて、

前記第1のフラグは、それぞれ複数ビットからなる不揮発性メモリ。

**【請求項9】**

請求項1～6のいずれか記載の不揮発性メモリにおいて、

前記データ記憶領域は、所定のシーケンスに従って書き込まれ、前記データ記憶領域とは別のデータ記憶領域は、シーケンスにおいて先行するデータ記憶領域である不揮発性メモリ。

**【請求項10】**

請求項1記載の不揮発性メモリにおいて、

前記第1のフラグとユーザデータ部のコンテンツは、誤り訂正符号によって保護される不揮発性メモリ。

**【請求項11】**

請求項1記載の不揮発性メモリにおいて、

データをメモリに読み込みかつ書き込むためのコントローラをさらに備え、2つまたはそれ以上の前記データ記憶領域へのデータの順次書き込み処理中に、第1のデータ記憶領域に続く各データ記憶領域ごとに、先行するデータ記憶領域の書き込みを示す表示がその書き込み処理の一部として現行のデータ記憶領域に書き込まれる不揮発性メモリ。

**【請求項12】**

請求項11記載の不揮発性メモリにおいて、

前記コントローラは、順次書き込み処理の最後のデータ記憶領域について、順次書き込み処理中に、最後のデータ記憶領域の書き込みを示す表示が最後のデータ記憶領域に書き込まれるようにさらに構成される不揮発性メモリ。

**【請求項13】**

不揮発性メモリの動作方法であって、

10

20

30

40

50

第 1 のデータ記憶領域にユーザデータの第 1 の論理ページをプログラムするステップと

第 1 の論理ページが前記第 1 のデータ記憶領域に適正にプログラムされたかを検証するステップと、

引き続いて、第 2 のデータ記憶領域にユーザデータの第 2 の論理ページをプログラムするステップと、

前記第 2 の論理ページをプログラムするステップと同時に、第 1 のデータ記憶領域が適正にプログラムされたことを示す表示を前記第 2 のデータ記憶領域に書き込むステップと、を含む方法において、

前記データ記憶領域は、所定の順序で書き込まれ、

10

前記データ記憶領域を消去ユニットにグループ化し、

前記第 2 の論理ページをプログラムするステップに引き続いて、前記第 2 の論理ページが前記第 2 のデータ記憶領域に適正にプログラムされたかを検証するステップと、

前記第 2 のデータ記憶領域が、前記第 2 のデータ記憶領域が属する消去ユニットに所定の順序で書き込まれた最後のデータ記憶領域である場合は、引き続いて前記第 2 のデータ記憶領域が適正にプログラムされたことを示す表示を前記第 2 のデータ記憶領域に書き込むステップと、をさらに含む方法。

**【請求項 1 4】**

請求項 1 3 記載の方法において、

前記第 2 の論理ページと、前記第 1 のデータ記憶領域が適正にプログラムされたことを示す表示は、誤り訂正符号によって保護される方法。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、一般に不揮発性メモリとその動作に関し、特に失敗した書き込みおよび消去動作の判定に関する。

**【背景技術】**

**【0002】**

フラッシュ EEPROM デバイスの一般的な用途は、電子デバイス用の大容量データ記憶サブシステムとしてである。このようなサブシステムは一般に、複数のホストシステムに挿入可能な出し入れ自在のメモリカードとして、或いはホストシステム内に取り外し不能に内蔵された記憶装置として実装される。双方の実装例とも、サブシステムは 1 つまたは複数のフラッシュデバイス、また多くの場合サブシステムコントローラを含む。

30

**【0003】**

フラッシュ EEPROM デバイスは 1 つまたは複数のトランジスタセルアレイから構成され、各セルは 1 ビットまたは複数のビットのデータの不揮発性記憶が可能である。このように、フラッシュメモリはプログラムされたデータを保持するために電力を必要としない。しかし、一旦プログラムされると、セルは新規のデータ値を再プログラミングしうる前に消去されなければならない。これらのセルアレイは読み出し機能、プログラミング機能、および消去機能を効率よく実施するためにグループに区分される。大容量記憶用の代表的なフラッシュメモリ構成は大きなセル群を消去可能なブロックへと配列し、ブロックは一度で消去可能な最小数のセル（消去ユニット）を含む。

40

**【0004】**

商用の一形態では、各ブロックは、ユーザデータの 1 つのセクタに加えてユーザデータおよび / またはそれが記憶されているブロックに関連する何らかのオーバーヘッドデータを記憶するのに充分なセルを含む。セクタ内に含まれるユーザデータ量は、1 つのクラスのこのようなメモリシステムでは標準的な 512 バイトであるが、別のサイズであってもよい。個々に消去可能にするために必要な個々のセルブロックの相互の絶縁は集積回路チップにスペースを取るので、別のクラスのフラッシュメモリはブロックを大幅に大きくするため、このような絶縁に必要なスペースは少なくなる。しかし、大幅に小さいセクタ内

50

のユーザデータを処理することも望まれるので、各々の大きなブロックは、ユーザデータを読み出し、かつプログラムするための基本ユニットである個々にアドレス指定可能なページへとさらに区分されることが多い。各ページは通常、1つのユーザデータセクタを記憶するが、ページは部分セクタまたは複数のセクタを記憶することもある。本願明細書において、“セクタ”とは、ホストへおよびホストからユニットとして伝送されるユーザデータ量を意味する。

#### 【0005】

大ブロックシステム内のサブシステムコントローラは、メモリサブシステムによってホストから受信される論理アドレスと、メモリセルアレイ内の物理的アドレスとの間の変換を含む幾つかの機能を実行する。この変換機能は、論理ブロック番号（LBN）および論理ページ用に中間項の使用を含むことが多い。コントローラは、インターフェイスバスを介してフラッシュメモリデバイスに発する一連のコマンドによって、低レベルのフラッシュ回路動作をも管理する。コントローラが実行する別の機能は、例えば誤り訂正符号（ECC）の利用などの様々な手段でサブシステムに記憶されたデータの完全性を保持することである。

10

#### 【0006】

このようなメモリ回路の動作中に停電した場合、例えばメモリカードがホストから取り出されるか、或いは集積メモリを有するデバイスから電源が遮断された場合に、メモリが書き込み動作または消去動作の途中となりうるため、その結果、動作が不完全になることがある。例えば、書き込み中のグループ内の全部ではないがほとんどのセルがその目標状態に達しているプログラミング処理中にメモリシステムから電源が遮断されると、書き込みグループは多数のエラーを含むことがある。この分野ではよく知られているように、データエラーを判定し、修正するためにメモリシステムに誤り訂正符号（ECC）を組み込むことは一般的である。プログラミング動作の完了前の停電によって、書き込みグループは、中断された書き込みグループを読み出す際に以下の3つの状態になることがある。すなわち、（1）ECCによる修正が可能である状態、（2）ECCによる修正が不能である状態、および（3）ECCの検出ミスが発生する可能性である。第1の場合では、エラーの範囲は誤り訂正符号が充分にデータを回収することができるほど小さい。第2の場合では、データは正しくないが、システムがその状態を判定する。第3の場合では、これもデータは正しくないが、ECCの検出ミスによりシステムはその状態を認識しない。

20

#### 【0007】

この最後の場合、すなわちECCの検出ミスは、例えば、ECCが、例えば最大4ビットエラーまで修正する容量を有しているが、書き込みグループに7ビットのデータが不適正に書き込まれた場合に発生することがある。その場合、システムは不適正に書き込まれたデータを認識せず、書き込みグループ内のエラーをいずれも修正したかのように動作するが、データは依然として不正である。消去処理中に電源が遮断された場合も同様の状態が発生することがある。これらのシナリオによってECCの書き込みおよび消去失敗検出は完全なものとは程遠くなり、データが適正に入力されたか否かを知ることが重要なミッションクリティカル状況では特に問題である。したがって、メモリシステムのこの態様には改良の余地がある。

30

【特許文献1】米国特許第6,522,580号

【特許文献2】米国特許出願第10/086,495号

【特許文献3】米国特許第6,282,130号

【特許文献4】米国特許第5,546,341号

【特許文献5】米国特許出願第09/956,201号

【特許文献6】米国特許第5,418,752号

【特許文献7】国際公開特許第W003/027828号

【特許文献8】米国公開特許出願第2003/0065899号

【特許文献9】2002年10月25日に出願されたエリヤホウ・ハラリ、ジョージ・スマチサ、ジャック・エイチ・ユアンおよびダニエル・シー・グッターマンによる「誘電記

40

50

憶素子を使用する不揮発性集積回路メモリシステム」という米国特許出願

【特許文献 10】米国特許第 5,768,192 号

【特許文献 11】米国特許第 4,630,086 号

【特許文献 12】米国特許第 5,991,193 号

【特許文献 13】米国特許第 5,892,706 号

【発明の開示】

【0008】

本発明は、第 1 の態様によると、不揮発性メモリのプログラミングおよび消去中に電源が遮断された場合に、システム性能への最小限の犠牲で書き込みおよび消去失敗検出のための信頼することができる機構を保証する不揮発性メモリおよびその動作方法を提供する。1 つの例示的な実施形態では、性能に対する影響を最小限にして書き込み失敗エラーの確実な検出を保証するために、新規の書き込み失敗検出機構が導入される。このアルゴリズムはセクタのオーバーヘッド情報に先行するセクタ状態フラグ (PSS) と、最後のセクタ状態フラグ (LSS) とを含み、この場合、先行するセクタ状態フラグ (PSS) は ECC によって保護されてもよい。

【0009】

データをセクタ 0 にプログラムした後、ブロック内のセクタ 0 から x に書き込む複数セクタ書き込み処理において、アルゴリズムはセクタ 1 にデータと共にセクタ 1 の PSS を書き込んで、セクタ 0 がプログラミングを完了し、書き込みの失敗が生じなかったことを示す。セクタ 1 がプログラムされた後、アルゴリズムはセクタ 2 にデータと共にセクタ 2 の PSS を書き込んで、セクタ 1 がプログラミングを完了し、書き込みの失敗が生じなかったことを示す。最後のセクタがプログラムされるまで以下同様である。最後のセクタが書き込みの失敗なくプログラミングを完了したことを示すために、最後のセクタの LSS が書き込まれる。したがって、書き込み失敗検出を確実にするために、ホストプログラミングコマンド内の最後のセクタだけが 2 回のプログラミング動作を必要とする。

【0010】

本発明の別の態様では、この機構は、セクタがブロック内の最後にプログラムされたセクタ、またはブロックの最後の物理セクタである場合は、次の物理セクタの PSS および現行のセクタの LSS を探索することによって書き込み失敗エラーの検出を確実なものにする。

【0011】

本発明のさらに別の態様では、正常な消去動作の後、ブロックの第 1 のセクタ内の消去失敗フラグ (EAF) がマークされてもよい。これらのフラグを用いて、システムは次の電源を投入した際の次の初期化中に書き込みの失敗または消去の失敗を正常に検出することができる。書き込み失敗検出方式は多状態メモリ用に特に有効である。(1) 多状態システムを処理するハードウェアを設計するのは、長いプログラミング時間を要するのでより困難でコストがかかる。また、(2) 多状態システムでは全ての単一セクタで 2 回プログラムしないことで得られる性能は、これも長いプログラミング時間を要するので大幅に高まる。

【0012】

本発明の追加の態様、特徴および利点は、添付図面を参照しながら読むことが望ましい例示的な実施形態の以下の説明に含まれる。

【発明を実施するための最良の形態】

【0013】

### 不揮発性メモリシステムの実施例

特定の実施例を提示するために図 1 ~ 7 を参照して、本発明の様々な態様が実施される特定の不揮発性メモリシステムを説明する。消去処理における外乱の量を減らすために、本発明は選択されない記憶素子のコントロールゲートを基底のウエル構造と同じ電圧レベルに保つ。例示的な実施形態では、記憶素子はウエル構造の上に形成されている。消去処理中、ウエル上方の選択された記憶素子と選択されない記憶素子の双方とも、ウエル内に

10

20

30

40

50

その電圧レベルを確立すると同時に消去電圧まで上昇される。次に、この電圧はウエルと選択されない記憶素子で保持されることによって、消去に関連するいかなる外乱の機会を減らす一方、選択された記憶素子は放電可能にされて必要な消去条件を作り出す。さらに、これは回路のピッチ領域を増やしたり、或いはメモリアレイ内に新たなワイヤを補足したりせずに達成することができ、その結果、回路に追加される付加的な周辺領域は最小限となる。

#### 【0014】

一般化についてはさらに後述するが、特定の例として本発明をNAND形のEEPROMフラッシュメモリについて説明する。特に、本願明細書の説明は、米国特許第6,522,580号（特許文献1）に記載されている種類のシステム、および前に参照により援用されているNANDシステムに関連する他の応用を用いている。以下で特定の電圧が必要な場合、設計に応じて他の値を用いることもできるが、消去電圧 $V_{erase}$ を15～20ボルトの範囲とし、低い論理レベル $V_{dd}$ を1.5～3ボルトの範囲とする。10

#### 【0015】

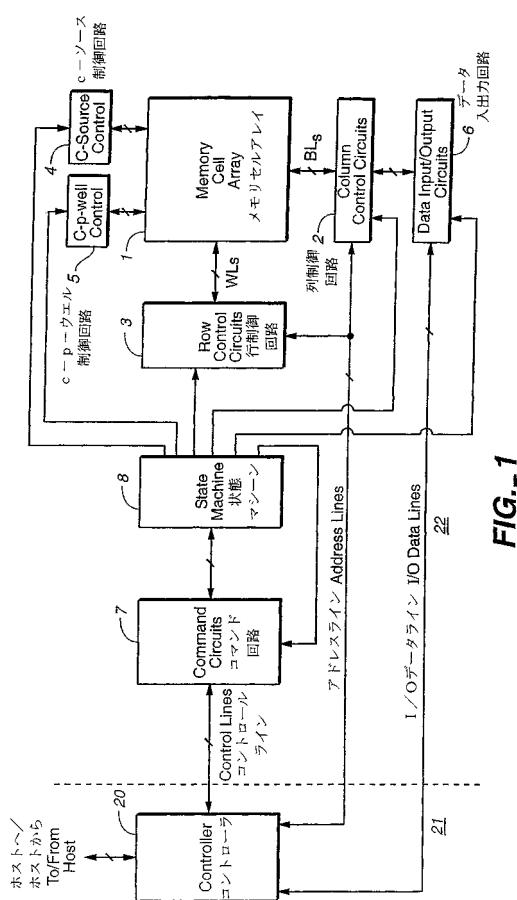

図1は、フラッシュメモリシステムのブロック図である。マトリクスに配置された複数の記憶ユニットMを含むメモリセルアレイ1は、列制御回路2、行制御回路3、c-pソース制御回路4、およびc-pウエル制御回路5によって制御される。メモリセル（M）に記憶されたデータを読み出し、プログラミング動作中のメモリセル（M）の状態を判定し、プログラミングを促進し、或いはプログラミングを抑制するようにビットライン（BL）の電位レベルを制御するために、列制御回路2はメモリセルアレイ1のビットライン（BL）に接続されている。ワードライン（WL）の1つを選択し、読み出し電圧を印加し、列制御回路2によって制御されるビットラインの電位レベルと組み合わせてプログラミング電圧を印加し、かつメモリセル（M）が形成されているP形領域（図3に“c-p-ウエル”11と表記されている）の電圧と結合して消去電圧を印加するように、行制御回路3はワードライン（WL）に接続されている。c-pソース制御回路4はメモリセル（M）に接続された共通ソースライン（図2に“c-ソース”と表記されている）を制御する。c-pウエル制御回路5はc-pウエルの電圧を制御する。20

#### 【0016】

メモリセル（M）に記憶されたデータは列制御回路2によって読み出され、I/Oラインおよびデータ入出力バッファ6を経て外部I/Oラインに出力される。メモリセルに記憶されるべきプログラミングデータは、外部I/Oラインを経てデータ入出力バッファ6に入力され、列制御回路2に伝送される。外部I/Oラインはコントローラ20に接続されている。フラッシュメモリデバイスを制御するためのコマンドデータは、コントローラ20に接続された外部コントロールラインに接続されているコマンドインターフェイスに入力される。コマンドデータはフラッシュメモリにどの動作が要求されているかを通知する。入力コマンドは、列制御回路2、行制御回路3、c-pソース制御回路4、c-pウエル制御回路5、およびデータ入出力バッファ6を制御する状態マシーン8に伝送される。状態マシーン8はREADY/BUSY（レディー/ビジー）またはPASS/FAIL（パス/フェイル）などのフラッシュメモリの状態データを出力することができる。30

#### 【0017】

コントローラ20は、パーソナルコンピュータ、デジタルカメラまたは携帯情報端末などのホストシステムに接続されるか、或いは接続可能である。ホストは、メモリアレイ1にデータを記憶したり、或いはメモリアレイ1から読み出すなどのコマンドを起動し、このようなデータをそれぞれ供給または受信する。コントローラはこのようなコマンドをコマンド回路7による解釈および実行可能なコマンド信号へと変換する。さらに、コントローラは典型的に、メモリアレイに書き込まれるか、或いはメモリアレイから読み出されるユーザデータ用のバッファメモリも含む。典型的なメモリシステムは、コントローラ20を含む集積回路チップ21と、メモリアレイおよび関連する制御回路、入出力回路および状態マシーン回路を各々含む1つまたは複数の集積回路チップとを備えている。もちろん40

システムのメモリアレイとコントローラ回路とを共に1つまたは複数の集積回路チップに組み込むことが趨勢である。メモリシステムはホストシステムの一部として組み込まれてもよく、或いはホストシステムの差込ソケットに着脱自在に挿入可能なメモリカードに含まれていてもよい。このようなカードはメモリシステム全体を含んでいてもよく、或いは別個のカードにコントローラおよびメモリアレイを関連する周辺回路と共に備えてよい。

#### 【0018】

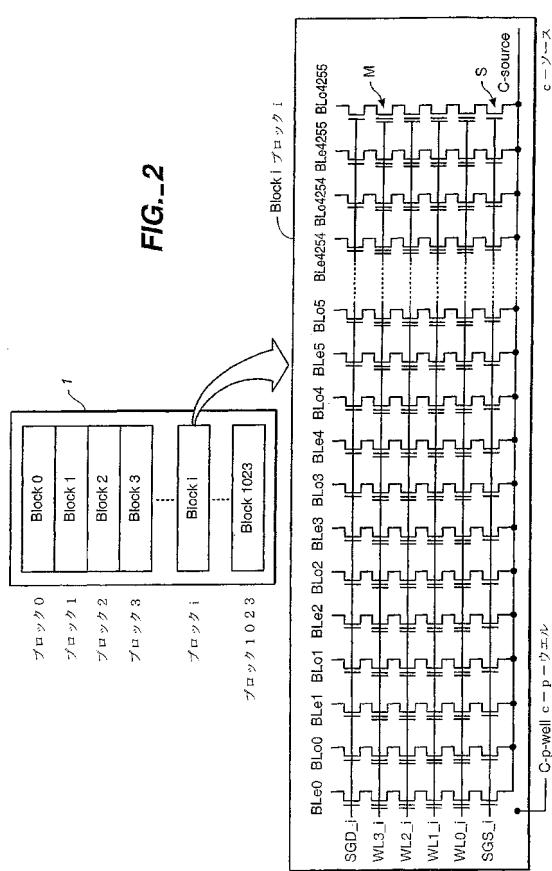

図2を参照してメモリセルアレイ1の例示的な構造を説明する。一例として、NAND形のフラッシュ EEPROMを説明する。メモリセル(M)は、特定の例において、1,024個もの多数のブロックに区分されている。各ブロックに記憶されるデータは同時に消去される。このように、ブロックは同時に消去可能な多数のセルの最小ユニットである。各ブロック内には、この例ではN=8,512列であるN列があり、これらは米国特許第6,522,580号(特許文献1)にさらに詳細に記載されているように、左列と右列とに分割されている。ビットラインも左ビットライン(BLL)と右ビットライン(BLR)とに分割されている。各ゲート電極でワードライン(WL0~WL3)に接続された4つのメモリセルが直列接続されてNANDセルユニットを形成する。NANDセルユニットの一端子は、ゲート電極が第1の(ドレイン)選択ゲートライン(SGD)に結合された第1の選択トランジスタ(S)を介して対応するビットライン(BL)に接続され、他端子は、ゲート電極が第2の選択ゲートライン(SGS)に結合された第2の(ソース)選択トランジスタ(S)を介してc-ソースに接続されている。簡略化するために、各セルユニットには4つのフローティングゲートトランジスタが含まれるように示されているが、8、16または32もの別の数のトランジスタも使用される。図2は、ウエル電圧を供給するための接続部c-p-ウエルも含む。

#### 【0019】

各ブロック内には、この例では8,512の列が偶数番号の列と奇数番号の列とに分割されている。ビットラインも偶数番号のビットライン(BLe)と奇数番号のビットライン(BLo)とに分割されている。各ゲート電極でワードライン(WL0~WL3)に接続された4つのメモリセルは直列に接続されてNANDセルユニットを形成する。NANDセルユニットの一端子は、ゲート電極が第1の選択ゲートライン(SGD)に結合された第1の選択トランジスタ(S)を介して対応するビットライン(BL)に接続され、他端子は、ゲート電極が第2の選択ゲートライン(SGS)に結合された第2の選択トランジスタ(S)を介してc-ソースに接続されている。簡略化するために、各セルユニットには4つのフローティングゲートトランジスタが含まれるように示されているが、8、16または32もの別の数のトランジスタも使用される。

#### 【0020】

本願明細書において参照により援用されている2002年2月27日に出願された米国特許出願第10/086,495号(特許文献2)に記載されているような別の一連の実施形態では、アレイを奇数偶数配列ではなく左右の部分に分割可能である。左側と右側は付加的に独立したウエル構造を有していてもよく、アレイの右側と左側は各々このような別個のウエル構造の上に形成されることで、図1のc-p-ウエル制御回路5によって電圧レベルを別個に設定することができる。さらに別の変形例では、それによって、ブロックの全ての区分よりも少ないサブブロックの消去も可能になり得る。本発明と適合するさらに別の変形例も、米国特許出願第10/086,495号(特許文献2)に記載されている。

#### 【0021】

例示的な実施形態では、ページのサイズは512バイトであり、これは同じワードライン上のセル数よりも少ない。このページサイズはユーザの嗜好と協定に基づくものである。ワードラインのサイズを1ページ分以上のセルに対応させることができれば、異なるページ分のデータがデコーダを共用することができるので、Xデコーダ(行制御回路3)のスペースを節減することができる。ユーザデータの読み出しおよびプログラミング動作中

10

20

30

40

50

、この実施例では  $N = 4, 256$  個のセル (M) が同時に選択される。選択されたセル (M) は同じワードライン (WL)、例えば WL2 と、同じ種類のビットライン (BL) とを有する。したがって、532 バイトのデータを同時に読み出したり、或いはプログラムすることが可能である。同時に読み出されるか、或いはプログラムされたこの 532 バイトのデータが論理的に “ページ” を形成する。したがって、1つのブロックが少なくとも 8 ページを記憶することができる。各メモリセル (M) が 2 ビットのデータ、すなわちマルチレベルのセルを記憶する際に、1 ブロックは、セル記憶当たり 2 ビットの場合、16 ページを記憶する。この実施形態では、各メモリセルの記憶素子、この場合、各メモリセルのフローティングゲートは、2 ビットのユーザデータを記憶する。

## 【0022】

10

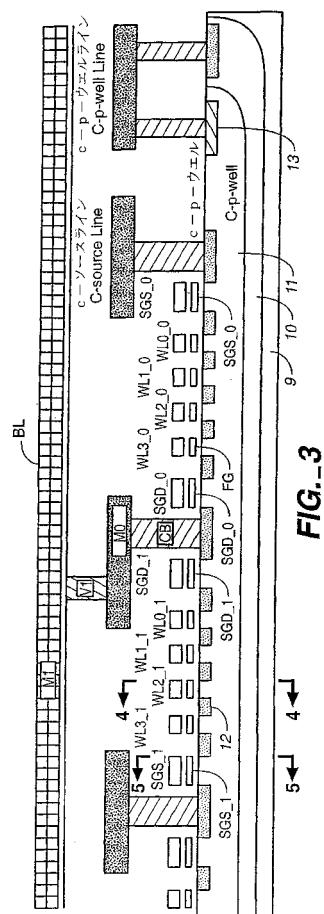

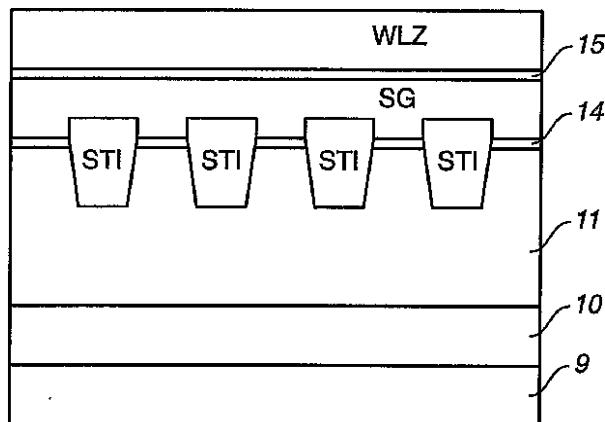

図 3 は、図 2 に概略的に示されている種類の NAND セルユニットのビットライン (BL) 方向での断面図を示す。P 形半導体基板 9 の表面に p 形領域の c - p - ウエル 11 が形成され、左右の各 c - p - ウエルは n 形領域 10 によって囲われて c - p - ウエルが p 形基板から電気的に絶縁されている。n 形領域 10 は、第 1 の接点孔 (CB) および n 形拡散層 12 を経て第 1 の金属 M0 からなる c - p - ウエルラインに接続されている。p 形領域の c - p ウエル 11 も第 1 の接点孔 (CB) および p 形拡散層 13 を経て c - p - ウエルラインに接続されている。c - p ウエルライン 11 は c - p - ウエル制御回路 5 (図 1) に接続されている。

## 【0023】

20

例示的な実施形態は、各メモリセルがセルに記憶されるデータに対応する電荷量を蓄積するフローティングゲート (FG)、ゲート電極を形成するワードライン (WL)、および p 形拡散層 12 からなるドレイン電極およびソース電極を有するフラッシュ EEPROM 記憶ユニットを使用している。フローティングゲート (FG) はトンネル酸化膜 (14) を介して c - p - ウエルの表面上に形成されている。ワードライン (WL) は絶縁膜 (15) を介してフローティングゲート (FG) 上に積層されている。ソース電極は第 2 の選択トランジスタ (S) および第 1 の接点孔 (CB) を経て第 1 の金属 (M0) からなる共通ソースライン (c - ソース) に接続されている。共通ソースラインは c - ソース制御回路 (4) に接続されている。ドレイン電極は第 1 の選択トランジスタ (S)、第 1 の接点孔 (CB)、第 1 の金属 (M0) の中間配線、および第 2 の接点孔 (V1) を経て、第 2 の金属 (M1) からなるビットライン (BL) に接続されている。ビットラインは列制御回路 (2) に接続されている。

## 【0024】

30

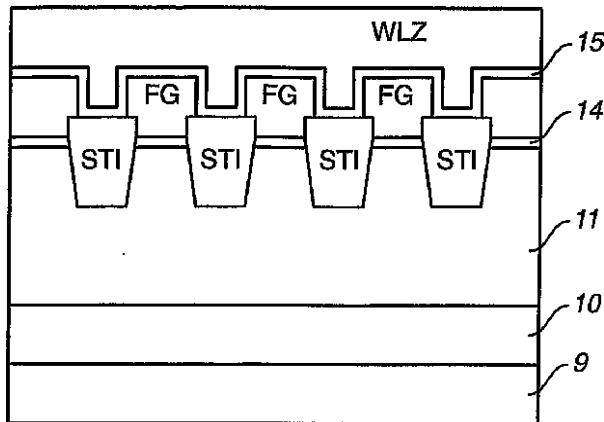

図 4 および 5 は、メモリセル (図 3 の 4 - 4 断面)、および選択トランジスタ (図 3 の 5 - 5 断面) のワードライン (WL2) 方向での断面図をそれぞれ示している。各列は、基板内に形成され絶縁材料を充填した、シャロー・トレーナー・アイソレーション (STI) として知られているトレーナーによって隣接する列から分離されている。フローティングゲート (FG) は STI および絶縁膜 (15) およびワードライン (WL) によって互いに絶縁されている。選択トランジスタ (S) のゲート電極 (SG) はフローティングゲート (FG) およびワードライン (WL) と同じ形成処理の段階で形成されるので、積層ゲート構造を呈する。これらの 2 つの選択ゲートライン (SG) はラインの端部で分路されている。

40

## 【0025】

前に参照により援用されている米国特許第 6,522,580 号 (特許文献 1) には、メモリセルアレイ 1 を動作するために印加される様々な電圧が記載され、特定の例では、各メモリセルのフローティングゲートは状態 “11”、“10”、“01”、“00” のうちの 1 つを有する 2 ビットを記憶する。消去、読み出し、またはプログラミング用にワードライン “WL2” およびビットライン “BLe” が選択される場合についてここで簡単に検討する。c - p - ウエルの電圧を消去電圧  $V_{erase} = 15 \sim 20 \text{ V}$  まで上昇させ、選択されたブロックのワードライン (WL) を接地することによって、選択されたブロックのデータが消去される。選択されないブロックのワードライン (WL)、ビットライン

50

(B L)、選択ライン (S G)、およびc - ソースは全て浮動状態になるので、これらも c - p - ウエルとの容量結合によりほぼ  $V_{erase}$  まで上昇される。したがって、選択されたメモリセル (M) のトンネル酸化膜 1 4 (図 4 および図 5) だけに強い電界が印加され、トンネル電流がトンネル酸化膜 1 4 を流れると選択されたメモリセルのデータが消去される。消去されたセルは、この例では、可能性がある 4 つのプログラミング状態のうちの 1 つ、すなわち “1 1” である。

#### 【0026】

消去およびプログラミング値で用いられる高い電圧値は(図 1 には示されていない)電荷ポンプを使用してそれよりも低い供給電圧値から発生されうる。より高いこれらの電圧はメモリチップ 2 2 自体で生成されることも、メモリシステム内の別のチップから供給されることもできる。高圧源の使用および位置は、本願明細書において参照により援用されている米国特許第 6,282,130 号(特許文献 3)に記載され、付加的な参考文献としてここで引用されている。10

#### 【0027】

図 6 は、このような先行技術の構成を概略的に示す。代表的な 3 本のワードライン  $WL_A$ 、 $WL_B$ 、および  $WL_C$  が、トランジスタ 101、103、および 105 のそれぞれを介して様々な電圧レベルを供給するライン 107 に接続されている。トランジスタ 101、103、および 105 はライン 107 と共に図 1 の行制御回路 3 の一部でありうる。図 1 の c - p - ウエル制御回路 5 はウエル構造 c - p - ウエル 11 用の電圧を供給する。次に、ワードラインはウエル構造 11 を越えて図 2 に示されているメモリ 1 の異なるブロックの様々なワードラインのいずれかにつながる。消去処理では、ワードライン  $WL_C$  は選択されたワードラインに該当し、 $WL_A$  と  $WL_B$  は共に選択されずに、c - p - ウエル内の電圧は消去電圧、例えば 17 ボルトに上昇され、ライン 107 は接地される。トランジスタ 105 のゲートはワードライン  $WL_C$  を接地に取って高レベルの  $V_{dd}$  に設定される一方、トランジスタ 101 および 103 の双方はゲートを接地することによってオフに転換され、 $WL_A$  および  $WL_B$  は浮動状態に留まる。その結果、選択されない消去ゲートが(例えば、前に援用されている米国特許第 5,546,341 号(特許文献 4)に記載されているように)ウエルからの容量結合によって荷電され、選択された消去ゲートが強制接地される消去条件になる。消去処理の別の態様は、本願明細書において参照により援用されている 2001 年 9 月 17 日に出願された米国特許出願第 09/956,201 号(特許文献 5)に記載されている。具体的には、米国特許出願第 09/956,201 号(特許文献 5)には、選択されないワードラインを浮動させることができる処理が記載され、これは本発明の様々な態様の代替の実施形態に組み込むこともできる処理である。20

#### 【0028】

プログラミング動作中にフローティングゲート (F G) に電子を蓄積するために、選択されたワードライン  $WL_2$  はプログラミングパルス  $V_{pgm}$  に接続され、選択されたビットライン  $BL_e$  は接地される。一方、プログラムされないメモリセル (M) でのプログラミングを抑制するために、該当するビットライン  $BL_e$  は、例えば 3 V である電源の  $V_{dd}$ 、および選択されないビットライン  $BL_o$  に接続される。選択されないワードライン  $WL_0$ 、 $WL_1$  および  $WL_3$  は 10 V に接続され、第 1 の選択ゲート (SGD) は  $V_{dd}$  に接続され、第 2 の選択ゲート (SGS) は接地される。その結果、プログラムされているメモリセル (M) のチャネル電位は 0 V に設定される。プログラミング抑制におけるチャネル電位は、チャネル電位がワードライン (WL) との容量結合によってブルアップされる結果、約 6 V まで上昇する。前に説明したように、プログラミング中はメモリセル (M) のトンネル酸化膜 1 4 だけに強い電界が印加され、トンネル電流はトンネル酸化膜が消去と比較して逆方向に流れ、論理状態は “1 1” から他の状態 “1 0”、“0 1”、または “0 0” のうちの 1 つに変化する。40

#### 【0029】

読み出しおよび検証動作では、選択ゲート (SGD および SGS) と、選択されないワードライン ( $WL_0$ 、 $WL_1$  および  $WL_3$ ) とは、4.5 V の読み出しバス電圧に上昇さ50

れて、これらがパスゲートにされる。このメモリセルのしきい値電圧がこのレベルに達したか否かを判定するために、選択されたワードライン（W L 2）は各々の読み出しおよび検証動作ごとに指定された電圧レベルに接続される。例えば、R E A D（読み出し）10動作では、選択されたワードラインW L 2は接地されるので、しきい値電圧が0V以上であるか否かが判定される。この読み出しの場合は、読み出しレベルが0Vであると言うことができる。V E R I F Y（検証）01動作では、選択されるワードラインW L 2は2.4Vに接続されるので、しきい値電圧が2.4Vに達したか否かが検証される。この検証の場合は、検証レベルが2.4Vであると言うことができる。繰り返すと、説明した全ての処理で、説明されている電圧レベルは例示的な値であるにすぎない。

## 【0030】

10

選択されたビットライン（B L e）は高レベル、例えば0.7Vにプリチャージされる。しきい値電圧が読み出しされた場合は検証レベル以上である場合、メモリセル（M）が非導電性であるので、このビットライン（B L e）の電位レベルは高レベルに保たれる。これに対して、しきい値電圧が読み出しされた場合は検証レベル未満である場合、メモリセル（M）が導電性であるので、このビットライン（B L e）の電位レベルは低レベル、例えば0.5V以下まで低下する。読み出しおよび検証動作のさらなる詳細を以下に説明する。

## 【0031】

書き込み／消去失敗検出機構の実施例

本発明の基本的な態様は、メモリのプログラミングおよび消去中に電源が遮断された場合に、システム性能への最小限の犠牲で書き込みおよび消去失敗検出のための信頼性がある機構を確保する技術である。構想は以下にさらに説明するようにさらに一般化して適用されるが、参照のための特定の実施形態を用いる場合、本発明は、主としてこれまでに説明してきたようにN A N D構成を有するフラッシュ形のメモリに関して記載されている。

20

## 【0032】

書き込みの失敗を防止するための公知の1つの方法は、本願明細書において参照により援用されている米国特許第5,418,752号（特許文献6）に記載されているように、メモリの動作が完了するまで、メモリのV<sub>dd</sub>を保持するために追加のハードウェアを加えることである。変形例では、電源遮断状況で失われてしまうデータを記憶するために、書き込み時間がより迅速な不揮発性メモリの代替形態を使用してもよい。コストが比較的高く、常に簡単に実装することができるわけではないのでこのアプローチには欠点がある。書き込み失敗検出の別の方針は、予約済み領域を再更新してプログラミング動作の完了を確認するために、実際のプログラミング動作前と実際のプログラミングが行われた後の双方で、予約済み領域内の意図されるプログラミングセクタのアドレスを指定することである。この方法には、データの実際のプログラミングを含めて単一のセクタの書き込みごとにユーザによる3回のプログラミング動作が必要である。別の方法は、セクタがプログラムされた後、事前定義された書き込み失敗ヘッダを書き込むことである。この方法には書き込まれるセクタごとに2回のプログラミング動作が必要である。消去に関しては、消去の前に予約済み領域に消去されるブロックまたはセクタのアドレスを書き込み、かつ消去動作の完了後に予約済み領域にアドレスを再度書き込むことができる。本発明の主要な態様はこれらの技術を改良するものである。

30

## 【0033】

40

より具体的には、性能に対する影響を最小限にして書き込み失敗エラーの確実な検出を保証するために、新規の書き込み失敗検出機構が導入される。この例示的な実施形態では、アルゴリズムはセクタのオーバーヘッド情報に先行するセクタ状態フラグ（P S S）および最後のセクタ状態フラグ（L S S）を導入する。システムがブロック内のセクタ0から×に書き込むことを想定すると、アルゴリズムはセクタ1にデータと共にセクタ1のP S Sを書き込んで、セクタ0がプログラミングを完了し、書き込みの失敗が生じなかったことを示す。それによって、E C C、すなわちオーバーヘッドを含むセクタ全体向けのE C C、或いはこのエラーを有する実施形態のオーバーヘッドE C CによってP S Sフラグを保護することができる。同様に、セクタ2が書き込まれる際に、セクタ1が書き込みの

50

失敗なしでプログラミングを完了したことを示すためにセクタ2のPSSが書き込まれ、書き込みコマンドの最後のセクタに達するまで以下同様である。最後のセクタであるセクタxに達すると、このセクタはセクタxデータが入力されるのと同時に入力されたセクタ(x-1)に対応するPSSフラグを同様に有するが、それは、書き込みの最後のセクタであるため、セクタxに対応するPSSフラグを設定すべき次のセクタはない。これを説明するために、LSSフラグが使用される。セクタのLSSフラグはセクタ自体に対応し、それを含むセクタが書き込みの失敗なくプログラミングを完了したことを示す。

#### 【0034】

セクタxがプログラムされた後、アルゴリズムはセクタxのLSSをプログラムすることができる。これは書き込み失敗検出を確実にするために、ホストプログラミングコマンドの最後のセクタだけが2回のプログラム動作をすればよいことを意味している。PSS方式は、コントローラによってキャッシュされるホストのアトミックな書き込みコマンドまたはコマンド群内の全てのセクタに適用される。LSS方式はシーケンス外のページのプログラミングが許容されない場合に、ホストのアトミックな書き込みコマンドおよびブロックの最後の物理的ページに適用される。メモリシステムはホストコマンドからプログラムされるセクタ番号を判定することができ、またPSSおよびLSSを用いた書き込み動作を管理するためにホストキャッシュを利用するによって、システム性能に対する影響を最小限にすることができる。例えば、コントローラはホストの複数のアトミックな書き込みを1つのメモリ動作シーケンスにグループ分けすることができ、それによって大きなセクタのチャンク(chunk of sector)にわたって書き込みLSSのオーバーヘッドを減衰(amortize)するので、性能に対する影響を低減することができる。これらの機構によって、セクタがブロック内の最後にプログラムされたセクタ、或いはブロックの最後の物理セクタである場合は、次の物理セクタのPSSおよび現行のセクタのLSSを探索することによって書き込み失敗エラーの検出を確実なものにする。

#### 【0035】

消去の場合、正常な消去動作の後に消去失敗フラグ(EAF)をマークしてもよい。EAFフラグはブロックの第1のセクタなどの事前指定された位置に設定することができる。PSSフラグおよびEAFフラグの双方について(ブロックが單一セクタ以上を含んでいる場合)、1つのセクタでの正常な動作の表示は別のセクタでも保持されることに留意されたい。これらのフラグを用いて、システムは次の電源が投入される際の次の初期化中に書き込みの失敗または消去の失敗を正常に検出することができる。これらの失敗検出方式は多状態(MLC)メモリ用に特に有効である。というのは、MLCを処理するハードウェアを設計するのは、長いプログラミング時間と消去時間とを要するのでより困難でコストがかかり、またMLCでは全ての单一セクタで2回プログラムしないことで得られる性能は、これも一般的には長いプログラミング時間を要するので大幅に高まるからである。

#### 【0036】

例示的な実施形態はセクタレベルに基づいてPSSおよびLSSフラグを使用する。セクタは、ホストが処理する最小のデータユニットであるので、便利である場合が多い。より一般的には、PSSおよびLSSフラグは、典型的には何らかの物理的データユニットまたは構造に基づいて大量のデータのそれぞれの正常な書き込みごとに設定可能である。例えば、データ書き込みユニットが複数セクタのデータページである場合は、データページの正常なプログラミングを次のページと同時にプログラムされたPSSフラグに記録することができ、次に最後のページの正常な書き込み用にLSSフラグが設定される。例示的な実施形態のこの説明はセクタに関してなされ、またフラグ名は“セクタ”を含んでいるが、これらの実施形態は全てより一般的な状況にも適用可能である。同様に、例示的な実施形態でのEAFフラグは、これが消去ユニットなのでブロックレベルで使用されるが、より一般的にはメタブロック用の单一の消去フラグなどの異なるスケールでも使用可能である。

#### 【0037】

10

20

30

40

50

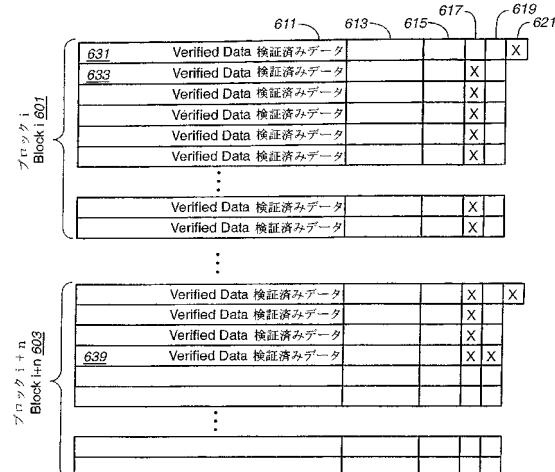

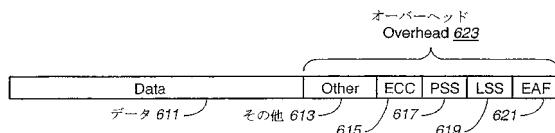

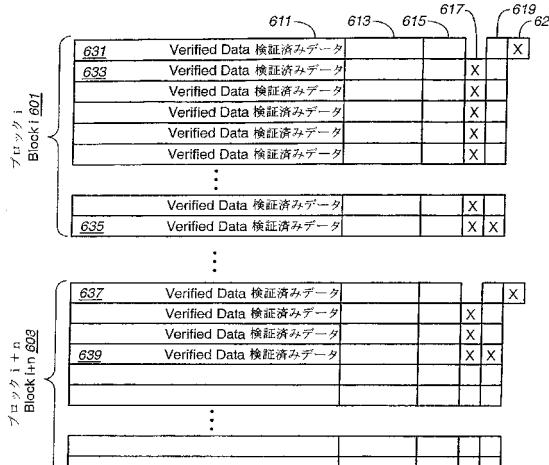

一対の例示的な実施形態が図 6 A ~ 6 C に概略的に示され、図 6 A および 6 C はセクタの構造を示し、また図 6 B は様々なフィールドを説明している。図 6 A はメモリセルアレイ 1 からの n 個のブロックを表し、これらはブロック  $i \_6\ 0\ 1$  からブロック  $i + n \_6\ 0\ 3$  まで並んでいる。各ブロック内には 6 3 1 や 6 3 3 などのセクタ番号が示され、各々が図の行で表されている。様々なフィールドが図 6 B に示されている。

#### 【 0 0 3 8 】

包括的なセクタの様々な部分が図 6 B に記載されている。これらは、ユーザデータが記憶されるデータ部 6 1 1 と、対応する誤り訂正符号 (ECC) 6 1 5 および当該技術分野で知られているその他の種類のオーバーヘッド (その他 6 1 3 ) などのセクタに関する様々なデータを含むヘッダまたはオーバーヘッド部 6 2 3 とから構成されている。ECC はデータとオーバーヘッドの双方のための兼用でもよく、それそのための別個の ECC であってもよい。これらの図では説明の目的のために様々なフィールドが分離して示されているが、実際にはこれらは実際の記憶素子内に混在している。加えて、物理セクタがデータだけを格納し、他の物理的記憶位置はオーバーヘッド専用であるような、オーバーヘッドが別個に記憶される実施形態もある。新たな特徴は、オーバーヘッドにフラグ PSS 6 1 7 、 LSS 6 1 9 、および EAF 6 2 1 が含まれることである。

#### 【 0 0 3 9 】

図 6 A に戻ると、各セクタは、先行するセクタが正常に書き込まれたことを表示するように設定可能な PSS フラグ 6 1 7 と、セクタ自体が適正に書き込まれたことを表示するように設定可能な LSS フラグ 6 1 9 の双方を有している。以下に説明するように、これらの各フラグは複数ビットからなることができる。PSS フラグの状態はセクタの書き込み前に判明しているので、これはデータおよびオーバーヘッドコンテンツと同時に書き込まれ、ECC によって保護されることができる。残りのセクタが正常に書き込まれたことに応じて引き続き LSS フラグが書き込まれるので、これは以前に書き込まれている ECC によって保護されない。

#### 【 0 0 4 0 】

ブロックのコンテンツは全て消去されるので、例示的な実施形態は各ブロックについて単一の消去失敗フラグ、 EAF 6 2 1 だけを使用することができる。本発明は、これも複数ビットからなることができる EAF フラグがブロック  $i \_6\ 0\ 1$  内のセクタ 6 3 1 などのブロックの第 1 のセクタ内に設定される仕様を採用している。消去処理が正常に完了した後、 EAF が設定される。したがって、この例示的な実施形態では、 EAF フラグは常時設定される必要がある。それが設定されないのは、消去動作後に EAF フラグを設定する動作が行われない、消去の失敗が生じた時だけである。 EAF フラグはデータがブロックに書き込まれる前に既に設定されるので、 ECC による保護はなされない。( EAF フラグが ECC によって保護されることが望ましい場合は、それを消去してからデータと共に再書き込みされる必要があり、付加的なプログラミングオーバーヘッドをこうむる。) 好ましい実施形態は消去失敗検出用の EAF フラグと書き込み失敗検出用の PSS / LSS フラグの双方を含んでいるが、これらは本発明とは別個の態様であり、メモリデバイスに別個に組み込むことができることに留意されたい。

#### 【 0 0 4 1 】

図 6 A はブロック  $i \_6\ 0\ 1$  のセクタ 0 ~ 6 3 1 で始まり、ブロック  $i + n \_6\ 0\ 3$  のセクタ 6 3 9 に至る書き込み処理の正常な終了時のセクタフラグ PSS 6 1 7 および LSS 6 1 9 の配列を示している。これらの各セクタのデータ部 6 1 1 は全て正常に書き込まれたので検証済みデータを含む。オーバーヘッド部には、フラグ PSS 6 1 7 、 LSS 6 1 9 、および EAF 6 2 1 の状態だけが示され、 X は設定されたフラグを、また空白の四角はフラグが未設定であることを示している。オーバーヘッドの他の部分 ( 6 1 3 および 6 1 5 ) のコンテンツは図に示されていない。データ部 6 1 1 はホストから供給されたユーザデータまたはシステムデータを記憶することができ、その例が、本願明細書において参照により援用されている国際公開特許第 WO 0 3 / 0 2 7 8 2 8 号 ( 特許文献 7 ) に記載されている。

10

20

30

40

50

## 【0042】

ブロックは消去の失敗を生じないで既に正常に消去されたので、EAFフラグ621がブロックに設定される。最初に書き込まれるセクタ631にはそのPSSフラグ617もそのLSSフラグ619も設定されない。次のセクタ633にはそのPSSフラグ617が設定され、先行するセクタ631が正常に書き込まれたことが示される。同様に、最後の書き込みセクタ639を含むこのセクタまでの後続するセクタの各々にはそのPSSフラグが設定される。最後に書き込まれるセクタには付加的にそのLSSフラグ619が設定され、それは自動書き込み処理でこのフラグが設定される唯一のセクタとなる。（LSSフラグが設定され、PSSフラグが設定されないセクタの状況は、単一のセクタだけが書き込まれる場合にだけ生じうる。）

10

## 【0043】

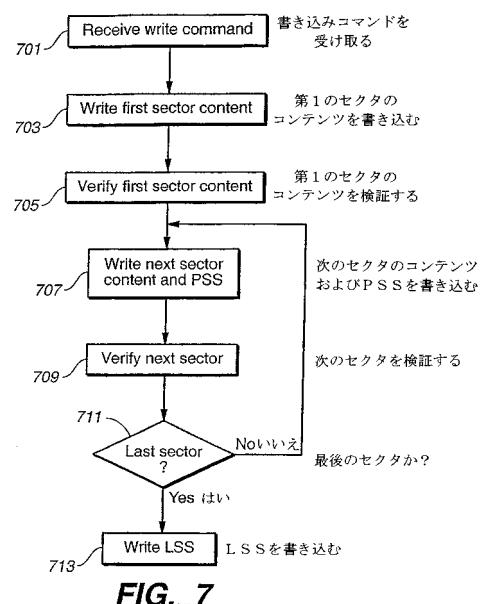

図7は例示的な書き込み処理のフローチャートである。これは、複数の論理データセクタを書き込むための書き込みコマンドを有するステップ701で開始される。次に、第1の論理セクタが対応する物理セクタ（703）に書き込まれる。データが適正に入力されたことが検証された後（705）、処理は次のセクタに進む。データコンテンツが次のセクタに書き込まれると（707）、先行するセクタが適正にプログラムされたことを示すPSSフラグもそのオーバーヘッド領域に設定される。書き込みはステップ709で検証される。それが最後のセクタではない場合は（711、“NO（いいえ）”）、書き込み処理は次のセクタに進み、ステップ707および709を繰り返して、先行するループ内でステップ709に応答してステップ707でPSSフラグを再び設定する。最後のセクタの書き込みがなされ、確認されると（711、“YES（はい）”）、PSSフラグが設定されるべき次のセクタがないので、LSSフラグが最後のセクタに設定される。セクタがブロック内に書き込まれる順序、およびブロックがアトミックな書き込み処理で書き込まれる順序は、例えば本願明細書において参照により援用されている米国公開特許出願第2003/0065899号（特許文献8）におけるようなポインタ構造に基づいて固定順でも可変順でもよい。（順序が固定されていない場合は、どのセクタがPSSフラグに対応する先行するセクタであるかを判定するために、順序は保持される必要がある。NAND構成を有するメモリはセクタの逐次書き込みを使用するので、結果として図7の方式で使用されるセクタの逐次書き込みになる。）

20

## 【0044】

30

図6Aおよび6Bに戻ると、書き込み処理が正常に行われたか否かを判定するにはPSS617とLSS619のフラグだけをチェックすればよい。これらのフラグはセクタが正常に書き込まれたことの保証として使用される。セクタのLSSフラグが設定されると、そのセクタおよび書き込み処理の全ての先行するセクタが正常にプログラムされたことになる。例えば、書き込み処理中に電源の遮断があった場合は、フラグを走査することができる。LSSフラグが設定されれば、プログラミングは完了している。LSSフラグ619が設定されなければ、PSSフラグ617へと逆向きに戻ることによって、最初に設定されたPSSフラグは、電源遮断前に書き込み処理の全てのセクタが正常に書き込まれたことを示す。同様に、EAFフラグ621をチェックすることによって、ブロック全体のデータコンテンツをチェックする必要なく消去処理が正常に完了したことを見ることができる。それによって、システムは、偶然全てゼロになった全ての有効データを含むブロックと（これはPSSおよびLSSフラグによっても判定できうる）、実際に消去されるブロックとを識別することも可能になる。

40

## 【0045】

図6Cは、多くの用途に好ましい図6Bの実施形態の変形例である。この実施形態では、全てのブロックが書き込まれると、書き込みが他のブロック内のそれ以上のセクタで継続される場合でも、ブロックに書き込まれた最後のセクタ用にLSSフラグが設定される。したがって、図6Cではセクタ635のLSSフラグが設定される。セクタ635自体のセクタ635の正常な書き込みが記録されるので、別のブロックの第1のセクタである次に書き込まれるセクタにPSSフラグを設定する必要はない。このように、先行するセ

50

クタが正常に書き込まれた場合でもセクタ 637 にはその PSS フラグは設定されず、そのことは先行するブロック内の最後のセクタの LSS フラグによって示される。したがって、各ブロック内の第 1 のセクタにはその PSS フラグが設定される必要がないので、図 6C のセクタ 631 および 637 について示されているように、これらのセクタについてはこのフラグは削除可能である。セクタ 0 内のビットと同様に、これらのビットを EAF フラグ用に使用してもよい。したがって、EAF フラグ 621 は図 6C では別個のものとして示されているが、他のセクタ内の PSS フラグ用に使用されるはずの領域をセクタ 0 内の EAF 用に利用することができる。

#### 【0046】

図 6C の構成は、ブロック内の最後のセクタの LSS フラグを探索するだけでブロック内の全てのセクタの状態をチェックすることができるという利点を有する。さらに、セクタ 0 は EAF および PSS フラグの双方を有する必要がないので、ブロック内の全てのセクタが同数のデータビットを有するという利点がある。10

#### 【0047】

図 6C の構成では、現行のセクタがブロックの第 1 のセクタである場合、ステップ 707 で PSS フラグが設定されないという点で、図 7 のフローチャートはやや変更される。ブロックの最後のセクタ用にステップ 709 と 711 との間で LSS を設定する必要がある。

#### 【0048】

フラグの構造を検討すると、これらは単一ビットのフラグでも複数ビットのフラグでもよい。それは設計上の選択であり、フラグの信頼性と使用されるスペース量との兼ね合いである。フラグ内のビット数が増加すると不良ビットまたはフラグ自体の書き込みエラーの確率も高まり、フラグの目的はデータ書き込みが正常であったか否かを判定することなので、フラグ自体がエラーのリスクの増大に直面すると逆効果になることも考慮される。例示的な実施形態は、使用される ECC とほぼマッチする各々数ビットのフラグを使用している。加えて、信頼性を付加するため、多状態メモリの場合でもフラグをバイナリモードで記憶してもよい。実際のデータと同じ MLC プログラミング動作中に PSS フラグが設定されるので、バイナリフラグを使用するとプログラミングアルゴリズムが幾分複雑なものになり、複数ビットのフラグを使用可能であるほとんどの用途では必要ない。上ページと下ページがある前述したような例示的な実施形態では、動作の複雑さを軽減するために上ページフラグと下ページフラグとに対応するマルチレベルのフラグ方式でフラグを記憶することも好ましい。2030

#### 【0049】

前述したように、本発明は例示的な実施形態の NAND 形フラッシュメモリに適用することができるだけではなく、その他の構成およびメモリ技術にも適用することもできる。例えば、ウエル消去を伴う NOR 形フラッシュメモリなどの他の EEPROM または電荷蓄積セルを利用してもよい。同様に、記憶素子がフローティングゲートトランジスタではない場合、例えば、本願明細書において参照により援用されている 2002 年 10 月 25 日に出願されたエリヤホウ・ハラリ、ジョージ・サマチサ、ジャック・エイチ・ユアン、およびダニエル・シー・グッターマンによる「誘電体格納エレメントを用いる多状態不揮発性 IC メモリシステム」という米国特許出願（特許文献 9）に記載されている種類の誘電体記憶素子にも本発明を適用することが可能である。また、これまでの説明はメモリデバイス用のフローティングゲート EEPROM またはフラッシュセルなどの電荷蓄積デバイスを使用した実施形態に集中してきたが、例えば、エイタンの米国特許第 5,768,192 号（特許文献 10）、およびサトウらの米国特許第 4,630,086 号（特許文献 11）にそれぞれ記載されているような NROM および MNOS セル、或いはギャラガーラの米国特許第 5,991,193 号（特許文献 12）、およびシミズらの米国特許第 5,892,706 号（特許文献 13）にそれぞれ記載されているような磁気 RAM および FRAM セルのような他の実施形態にも適用することができる。これらの特許は、本願明細書において参照により援用されている。4050

## 【0050】

本発明の様々な態様を特定の実施形態と関連して説明してきたが、本発明は添付の特許請求の範囲の全範囲にわたってその権利が保護されるべきことが理解されよう。

## 【図面の簡単な説明】

## 【0051】

【図1】本発明の様々な態様が実装されるものと説明されている不揮発性メモリシステムのブロック図である。

【図2】NAND形の場合の図1のメモリアレイの既存の回路および構成を示す。

【図3】半導体基板上に形成されたNAND形メモリアレイの、列に沿った横断面図である。

10

【図4】図3のメモリアレイの4-4断面の横断面図である。

【図5】図3のメモリアレイの5-5断面の横断面図である。

【図6A】例示的な実施形態によるブロック構造の概略図である。

【図6B】例示的な実施形態によるブロック構造の概略図である。

【図6C】例示的な実施形態によるブロック構造の概略図である。

【図7】書き込み処理の例のフローチャートである

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

【図4】

FIG. 4

【図5】

FIG. 5

【図6A】

FIG. 6A

【図6B】

FIG. 6B

【図 6C】

【図 7】

---

フロントページの続き

(72)発明者 コンレー , ケビン エム .

アメリカ合衆国、95120、カリフォルニア州、サンホセ、マンクーソ ストリート 615

2

(72)発明者 チャング , ロバート シー .

アメリカ合衆国、94506、カリフォルニア州、ダンヴィル、スタントン コート 10

審査官 野田 佳邦

(56)参考文献 特開2003-331586 (JP, A)

特開2003-036209 (JP, A)

特開2003-015929 (JP, A)

特開2001-250388 (JP, A)

特開2002-169729 (JP, A)

特開平06-035776 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/16