(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7596243号

(P7596243)

(45)発行日 令和6年12月9日(2024.12.9)

(24)登録日 令和6年11月29日(2024.11.29)

(51)国際特許分類

|        |                  |        |       |         |

|--------|------------------|--------|-------|---------|

| H 01 L | 29/78 (2006.01)  | H 01 L | 29/78 | 6 5 7 D |

| H 01 L | 21/336 (2006.01) | H 01 L | 29/78 | 3 0 1 D |

| H 01 L | 29/739 (2006.01) | H 01 L | 29/78 | 6 5 2 D |

| H 01 L | 29/861 (2006.01) | H 01 L | 29/78 | 6 5 3 C |

| H 01 L | 29/868 (2006.01) | H 01 L | 29/78 | 6 5 8 F |

請求項の数 16 (全22頁) 最終頁に続く

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2021-154468(P2021-154468) |

| (22)出願日  | 令和3年9月22日(2021.9.22)        |

| (65)公開番号 | 特開2023-45862(P2023-45862A)  |

| (43)公開日  | 令和5年4月3日(2023.4.3)          |

| 審査請求日    | 令和5年9月7日(2023.9.7)          |

|          |                                                 |

|----------|-------------------------------------------------|

| (73)特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号           |

| (73)特許権者 | 317011920<br>東芝デバイス＆ストレージ株式会社<br>東京都港区芝浦一丁目1番1号 |

| (74)代理人  | 100119035<br>弁理士 池上 徹真                          |

| (74)代理人  | 100141036<br>弁理士 須藤 章                           |

| (74)代理人  | 100178984<br>弁理士 高下 雅弘                          |

| (72)発明者  | 布施 香織<br>東京都港区芝浦一丁目1番1号 東芝デ<br>バイス＆ストレージ株式会社内   |

最終頁に続く

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

第1電極と、

前記第1電極の上に設けられた、第1導電型の第1半導体層と、

前記第1半導体層の上に設けられた、第2導電型の第2半導体層と、

前記第2半導体層の上に設けられた第2電極と、

前記第2半導体層から前記第1半導体層に到達する第1トレンチと、

前記第2半導体層内において、前記第1トレンチに接して設けられ、前記第2半導体層より第2導電型不純物濃度の高い第1半導体領域と、

前記第2半導体層内において、前記第1半導体領域に接して設けられた第1絶縁膜と、

を備え、

前記第1半導体層から前記第2半導体層に向かう方向を第1方向、前記第1方向に交差する方向を第2方向としたときに、前記第2方向において、前記第1トレンチ、前記第1半導体領域、前記第1絶縁膜、前記第2半導体層の順に位置する、

半導体装置。

## 【請求項2】

前記第1方向における前記第1絶縁膜の長さは、前記第1方向における前記第1半導体領域の長さの0.6倍以上1.5倍以下である、

請求項1記載の半導体装置。

## 【請求項3】

前記第1方向における前記第2半導体層の長さは、前記第1方向における前記第1絶縁膜の長さより長い、

請求項1又は請求項2記載の半導体装置。

【請求項4】

前記第1方向における前記第2半導体層の長さは、前記第1方向における前記第1半導体領域の長さより長い、

請求項1乃至請求項3いずれか一項記載の半導体装置。

【請求項5】

前記第1絶縁膜は酸化シリコンを含む、

請求項1乃至請求項4いずれか一項記載の半導体装置。

10

【請求項6】

前記第2半導体層内において、互いに離間して設けられた複数の前記第1半導体領域をさらに備える請求項1乃至請求項5いずれか一項記載の半導体装置。

【請求項7】

前記第2半導体層内において、互いに離間して設けられた複数の前記第1半導体領域と、

前記第2半導体層内において、互いに離間して設けられた複数の前記第1絶縁膜と、

をさらに備える請求項1乃至請求項5いずれか一項記載の半導体装置。

【請求項8】

前記第2方向において前記第2半導体層と接する第2トレンチと、

前記第2半導体層内において、前記第2トレンチに接して設けられ、前記第2半導体層より第2導電型不純物濃度の高い第2半導体領域と、

20

前記第2半導体層内において、前記第2半導体領域に接して設けられた第2絶縁膜と、を備える請求項1乃至請求項7いずれか一項記載の半導体装置。

【請求項9】

前記第1トレンチ及び前記第2トレンチは、前記第1方向及び前記第2方向に交差する第3方向に延伸し、

前記第3方向における前記第2半導体領域の長さは、前記第3方向における前記第1半導体領域の長さより短い、

請求項8記載の半導体装置。

【請求項10】

30

前記第3方向における前記第2半導体領域の長さは、前記第2方向における前記第2絶縁膜の長さより短い、

請求項9記載の半導体装置。

【請求項11】

前記第2方向において前記第2半導体層と接する第2トレンチをさらに備え、

前記第2トレンチの少なくとも一部は、前記第2半導体層内において前記第2半導体層より第2導電型不純物濃度の高い第2半導体領域と接しない部分を有する、

請求項1乃至請求項7いずれか一項記載の半導体装置。

【請求項12】

前記第2トレンチは、前記第2半導体領域と接する部分を有する、

請求項11記載の半導体装置。

40

【請求項13】

前記第2半導体層内において、互いに離間して設けられた複数の前記第2半導体領域をさらに備える請求項8乃至請求項10いずれか一項記載の半導体装置。

【請求項14】

前記第2半導体層内において、互いに離間して設けられた複数の前記第2半導体領域と、

前記第2半導体層内において、互いに離間して設けられた複数の前記第2絶縁膜と、

をさらに備える請求項8乃至請求項10いずれか一項記載の半導体装置。

【請求項15】

前記第2トレンチは、前記第1半導体層に到達する、

50

請求項 8 乃至請求項 1 4 いずれか一項記載の半導体装置。

【請求項 1 6】

前記第 2 トレンチの底部は、前記第 2 半導体層内に設けられている、

請求項 8 乃至請求項 1 4 いずれか一項記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0 0 0 2】

ダイオードの逆方向回復特性（リカバリ特性）を改善するための開発が行われている。近年、インバータなどの電力変換装置に用いられる半導体装置として I G B T ( I n s u l a t e d G a t e B i p o l a r T r a n s i s t o r ) 、ダイオード等が用いられている。ダイオードは、一般に I G B T と逆並列に接続され、還流用ダイオードとして用いられる。このため、ダイオードは、 F W D ( F r e e W h e e l i n g D i o d e ) と呼ばれることがある。

10

【0 0 0 3】

インバータなどの電力変換装置の特性改善には、 I G B T の特性改善と並行して F W D の特性改善が重要になっている。 F W D の重要な特性としては、オン電圧（すなわち、導通状態での電圧降下）、リカバリ時間（すなわち、リバースリカバリ時のリカバリ電流の消滅時間）およびリカバリ時の安全動作領域（すなわち、リカバリ電流が流れている状態で電圧が印加されても破壊しない領域）等がある。また、リカバリ時の電流・電圧振動は少ないほうがより望ましい。なかでも、リカバリ時間の短縮しつつ、リカバリ時の安全動作領域を広くすることは重要である。

20

【先行技術文献】

【特許文献】

【0 0 0 4】

【文献】再公表 2 0 1 8 - 0 5 2 0 9 9 号公報

【発明の概要】

【発明が解決しようとする課題】

30

【0 0 0 5】

本発明が解決しようとする課題は、リカバリ損失の低減が達成され、安全動作領域が拡大された半導体装置を提供することにある。

【課題を解決するための手段】

【0 0 0 6】

実施形態の半導体装置は、第 1 電極と、第 1 電極の上に設けられた、第 1 導電型の第 1 半導体層と、第 1 半導体層の上に設けられた、第 2 導電型の第 2 半導体層と、第 2 半導体層の上に設けられた第 2 電極と、第 2 半導体層から第 1 半導体層に到達する第 1 トレンチと、第 2 半導体層内において、第 1 トレンチに接して設けられ、第 2 半導体層より第 2 導電型不純物濃度の高い第 1 半導体領域と、第 2 半導体層内において、第 1 半導体領域に接して設けられた第 1 絶縁膜と、を備え、第 1 半導体層から第 2 半導体層に向かう方向を第 1 方向、第 1 方向に交差する方向を第 2 方向としたときに、第 2 方向において、第 1 トレンチ、第 1 半導体領域、第 1 絶縁膜、第 2 半導体層の順に位置する。

40

【図面の簡単な説明】

【0 0 0 7】

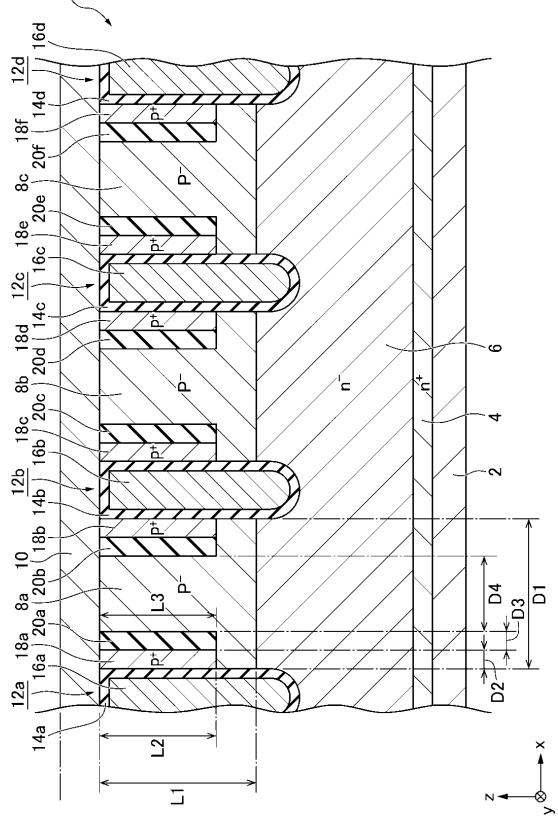

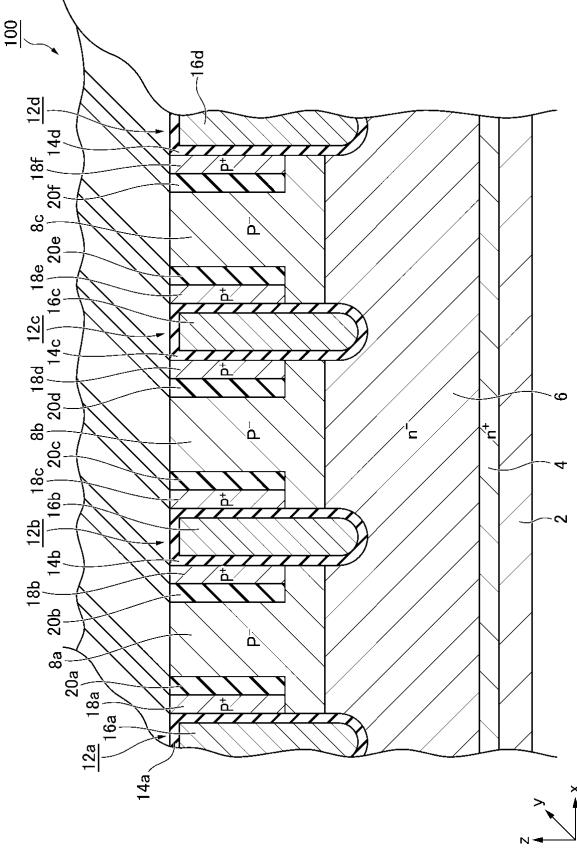

【図 1】第 1 実施形態の半導体装置の模式断面図である。

【図 2】第 1 実施形態の半導体装置の模式斜視図である。

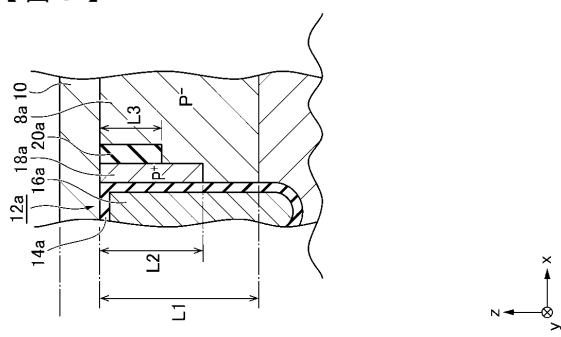

【図 3】第 1 実施形態の半導体装置の要部の模式断面図の一例である。

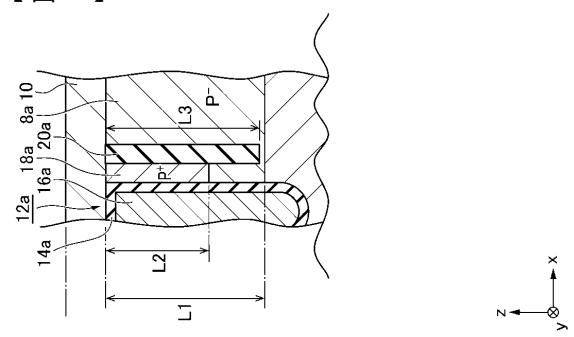

【図 4】第 1 実施形態の半導体装置の要部の模式断面図の他の一例である。

【図 5】第 1 実施形態の半導体装置の製造工程の一部を示す模式断面図である。

50

【図 6】第 1 実施形態の半導体装置の製造工程の一部を示す模式断面図である。

【図 7】第 1 実施形態の半導体装置の製造工程の一部を示す模式断面図である。

【図 8】第 1 実施形態の比較形態となる半導体装置の要部の模式断面図である。

【図 9】第 1 実施形態の半導体装置の作用効果を説明するための模式図である。

【図 10】第 2 実施形態の半導体装置の模式斜視図である。

【図 11】第 3 実施形態の半導体装置の模式斜視図である。

【図 12】第 4 実施形態の半導体装置の模式斜視図である。

【図 13】第 5 実施形態の半導体装置の模式斜視図である。

【図 14】第 6 実施形態の半導体装置の模式斜視図である。

【図 15】第 7 実施形態の半導体装置の模式斜視図である。

10

【発明を実施するための形態】

【0008】

以下、図面を参照しつつ本発明の実施形態を説明する。なお、以下の説明では、同一の部材等には同一の符号を付し、一度説明した部材等については適宜その説明を省略する。

【0009】

以下の説明において、 $n^+$ 、 $n$ 、 $n^-$  および、 $p^+$ 、 $p$ 、 $p^-$  の表記は、各導電型における不純物濃度の相対的な高低を表す。すなわち  $n^+$  は  $n$  よりも  $n$  型の不純物濃度が相対的に高く、 $n^-$  は  $n$  よりも  $n$  型の不純物濃度が相対的に低いことを示す。また、 $p^+$  は  $p$  よりも  $p$  型の不純物濃度が相対的に高く、 $p^-$  は  $p$  よりも  $p$  型の不純物濃度が相対的に低いことを示す。なお、 $n^+$  型、 $n^-$  型を単に  $n$  型、 $p^+$  型、 $p^-$  型を単に  $p$  型と記載する場合もある。

20

【0010】

本明細書中、部品等の位置関係を示すために、カソード電極 2 からドリフト層 6 に向かう方向を「上」と言い、その反対方向を「下」と言う。本明細書中、「上」、「下」の概念は、必ずしも重力の向きとの関係を示す用語ではない。

【0011】

以下、第 1 導電型が  $n$  型、第 2 導電型が  $p$  型である場合を例に説明する。

【0012】

(第 1 実施形態)

本実施形態の半導体装置は、第 1 電極と、第 1 電極の上に設けられた、第 1 導電型の第 1 半導体層と、第 1 半導体層の上に設けられた、第 2 導電型の第 2 半導体層と、第 2 半導体層の上に設けられた第 2 電極と、第 2 半導体層から第 1 半導体層に到達する第 1 トレンチと、第 2 半導体層内において、第 1 トレンチに接して設けられ、第 2 半導体層より第 2 導電型不純物濃度の高い第 1 半導体領域と、第 2 半導体層内において、第 1 半導体領域に接して設けられた第 1 絶縁膜と、を備える。

30

【0013】

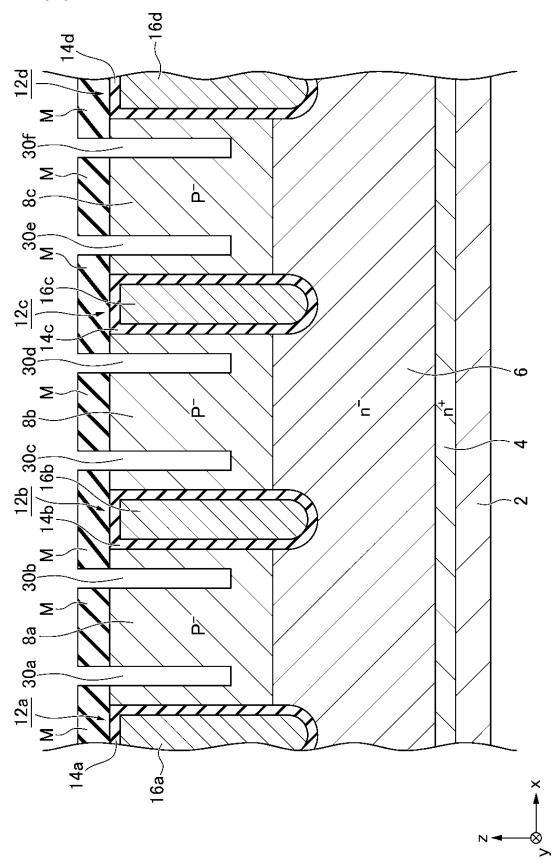

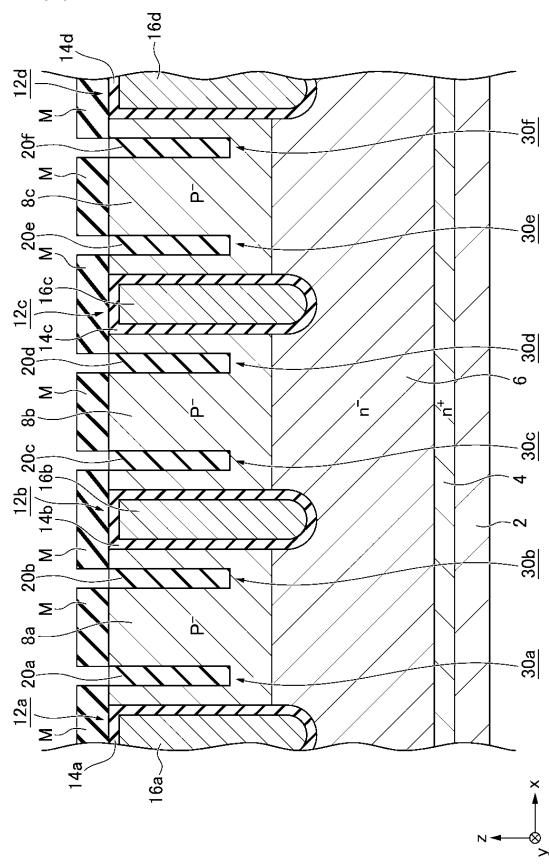

図 1 は、本実施形態の半導体装置 100 の模式断面図である。図 2 は、本実施形態の半導体装置 100 の要部の模式斜視図である。図 2 は、図 1 に示した半導体装置 100 について、説明の便宜のため、アノード電極 10 を取り除いて図示したものである。

【0014】

半導体装置 100 は、トレンチ 12 を有する PIN ダイオードである。例えば、1 チップ内に IGBT と PIN ダイオードを有する RC-IGBT (Reverse Conduction IGBT) において、IGBT の動作のために設けられたトレンチ 12 と同様のトレンチ 12 が、半導体装置 100 内に設けられている。なお、本実施形態の半導体装置 100 は、上記のような PIN ダイオードに限定されるものではない。

40

【0015】

図 1 及び図 2 を用いて、本実施形態の半導体装置 100 の説明をする。

【0016】

カソード電極（第 1 電極の一例）2 は、PIN ダイオードのカソード電極として機能する電極である。カソード電極 2 は、例えば、Al（アルミニウム）又は Cu（銅）等の導

50

電材料を含む。

〔 0 0 1 7 〕

$n^+$ 型のカソード層4は、カソード電極2の上に設けられている。カソード層4は、PINダイオードのカソード層として機能する層である。例えば、カソード層4は、 $3 \times 10^{17} \text{ atoms/cm}^3$ 以上のn型不純物を含むことが好ましい。

〔 0 0 1 8 〕

$n^-$ 型のドリフト層（第1半導体層の一例）6は、カソード層4の上に設けられている。ドリフト層6は、PINダイオードのドリフト層として機能する層である。例えば、ドリフト層6は、 $1 \times 10^{12} \text{ atoms/cm}^3$ 以上 $1 \times 10^{15} \text{ atoms/cm}^3$ 以下の $n^-$ 型不純物を含むことが好ましい。ドリフト層6の膜厚は、例えば $40 \mu\text{m}$ 以上 $700 \mu\text{m}$ 以下である。

【 0 0 1 9 】

ここで、X方向（第2方向の一例）と、X方向に対して垂直に交差するY方向（第3方向の一例）と、X方向及びY方向に垂直に交差するZ方向（第1方向の一例）を定義する。カソード電極2、カソード層4及びドリフト層6は、X方向及びY方向に平行なXY平面に平行に設けられた層状の形状をしている。Z方向は、カソード電極2からドリフト層6に向かう方向である。

( 0 0 2 0 )

p-型のアノード層（第2半導体層の一例）8は、ドリフト層6の上に設けられている。アノード層8は、PINダイオードのアノード層として機能する層である。例えば、アノード層8は、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上 $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下のp型不純物を含むことが好ましい。アノード層8の膜厚は、例えば2μm以上8μm以下である。図1には、アノード層8a、8b及び8cが示されている。

[ 0 0 2 1 ]

アノード電極（第2電極の一例）10は、アノード層8の上に設けられている。アノード電極10は、PINダイオードのアノード電極として機能する電極である。アノード電極10は、例えば、Al（アルミニウム）又はCu（銅）等の導電材料を含む。アノード電極10は、例えば、アノード層8とショットキー接觸する。

〔 0 0 2 2 〕

トレンチ（第1トレンチの一例）12は、アノード層8からカソード電極2に、Z方向に平行に延伸し、ドリフト層6に到達するように設けられている。図1には、トレンチ12の一例として、トレンチ12a、トレンチ12b、トレンチ12c及びトレンチ12dが設けられている。トレンチ12a、12b、12c及び12dは、図2に示すように、Y方向に延伸している。本実施形態において、トレンチ12a、トレンチ12b、トレンチ12c及びトレンチ12dは第1トレンチである。

[ 0 0 2 3 ]

電極 16 は、トレンチ 12 内に設けられている。電極 16 は、例えば、不純物を含むシリコンを含む。絶縁膜 14 は、トレンチ 12 内において、電極 16 の周囲に、電極 16 を取り囲むように設けられている。絶縁膜 14 は、例えば酸化シリコン等の絶縁物を含む。なお、トレンチ 12 内には、電極 16 が設けられていなくてもよい。

〔 0 0 2 4 〕

p<sup>+</sup>型の半導体領域（第1半導体領域の例）18は、アノード層8内において、トレンチ12の側壁にX方向で接して設けられている。半導体領域18もPINダイオードのアノード層として働く。半導体装置100においては、アノード層8a内において、トレンチ12aの側壁にX方向で接して、半導体領域18aが設けられている。アノード層8a内において、トレンチ12bの側壁にX方向で接して、半導体領域18bが設けられている。アノード層8b内において、トレンチ12bの側壁にX方向で接して、半導体領域18cが設けられている。アノード層8b内において、トレンチ12cの側壁にX方向で接して、半導体領域18dが設けられている。アノード層8c内において、トレンチ12cの側壁にX方向で接して、半導体領域18eが設けられている。アノード層8c内において、トレンチ12dの側壁にX方向で接して、半導体領域18fが設けられている。

て、トレンチ 12 d の側壁に X 方向で接して、半導体領域 18 f が設けられている。トレンチ 12 b は、X 方向において、半導体領域 18 b と半導体領域 18 c の間に設けられている。トレンチ 12 c は、X 方向において、半導体領域 18 d と半導体領域 18 e の間に設けられている。半導体領域 18 a、18 b、18 c、18 d、18 e 及び 18 f は、例えば、図 2 に示すように、Y 方向に、トレンチ 12 の側壁に沿って、Y 方向に延伸している。Z 方向におけるアノード層 8 の長さは、Z 方向における半導体領域 18 の長さより長い。例えば、半導体領域 18 は、 $1 \times 10^{17} \text{ atoms/cm}^3$  以上  $1 \times 10^{21} \text{ atoms/cm}^3$  以下の p 型不純物を含むことが好ましい。

#### 【0025】

ここで半導体装置 100 の動作について説明する。

10

#### 【0026】

最初に、カソード側からアノード側に流れる電子電流について説明する。

#### 【0027】

オン状態（導通状態）においては、カソード・アノード間に順方向電圧が印加されている。すなわち、カソード電極 2 の電位よりも、アノード電極 10 の電位の方が高くなるようにカソード・アノード間に電圧が印加されている。

#### 【0028】

ここで、n<sup>+</sup>型カソード層 4 はカソード電極 2 にオーミック接合をしている。従って、電子は、n<sup>+</sup>型カソード層 4 から n<sup>-</sup>型のドリフト層 6 を経由して p<sup>-</sup>型のアノード層 8 に到達する。

20

#### 【0029】

p<sup>-</sup>型アノード層 8 は、アノード電極 10 に抵抗性接触あるいはショットキー接合をしている。すなわち、p 形半導体と金属による抵抗性接触あるいはショットキー接合である。このため、p<sup>-</sup>型アノード層 8 とアノード電極 10 との間は、ホールにとってはエネルギー障壁となるが、電子にとってはエネルギー障壁とはならない。

#### 【0030】

従って、電子は、n<sup>+</sup>型カソード層 4 から n<sup>-</sup>型ドリフト層 6、p<sup>-</sup>型アノード層 8 を経由してアノード電極 10 に流れ込む。

#### 【0031】

次に、アノード側からカソード側に流れるホール電流について説明する。

30

#### 【0032】

上述したように、p<sup>-</sup>型アノード層 8 とアノード電極 10 との間は、電子にとってはエネルギー障壁とはならない。しかし、p<sup>+</sup>型の半導体領域 18 と p<sup>-</sup>型アノード層 8 との間は、電子にとってはエネルギー障壁となる。従って、p<sup>-</sup>型アノード層 8 にまで流れた電子は、p<sup>+</sup>型の半導体領域 18 には流れ込み難くなる。

#### 【0033】

これにより、電子は、カソード側からアノード側の方向に流れた後、p<sup>+</sup>型の半導体領域 18 付近にまで到達すると、その後は p<sup>+</sup>型の半導体領域 18 の下方において横方向 (X 方向) に移動する。

#### 【0034】

この p<sup>-</sup>型アノード層 8 付近における電子の移動により、p<sup>+</sup>型の半導体領域 18 の下方部分が、アノード電極 10 に接触した p<sup>+</sup>型の半導体領域 18、すなわち、アノード電極 10 に対して、負極になるようにバイアスされる。

40

#### 【0035】

p<sup>+</sup>型の半導体領域 18 の下方部分とアノード電極 10 との間に形成されたバイアスによって、p<sup>+</sup>型の半導体領域 18 の下方においては、p<sup>-</sup>型アノード層 8 と p<sup>+</sup>型の半導体領域 18 との間のホールに対するエネルギー障壁が低くなる。これにより、p<sup>+</sup>型の半導体領域 18 から p<sup>-</sup>型アノード層 8 にホールが注入される。

#### 【0036】

ホール電流は、p<sup>+</sup>型の半導体領域 18 の X 方向における幅、もしくは p<sup>+</sup>型の半導体

50

領域 1 8 とアノード電極との接触面積が大きくなるほど増大する。換言すれば、その幅もしくはその接触面積によって、アノード側からのホールの注入量が調整される。

#### 【 0 0 3 7 】

このように、オン状態では、アノード側からカソード側にホールが流れ、カソード側からアノード側に電子が流れる。ここで、アノード側では、 $p^+$ 型の半導体領域 1 8 からホールが注入するのに対して、 $p^-$ 型アノード層 8 はほぼ電子の排出に寄与する。そのため、 $p^-$ 型アノード層 8 を設けない半導体装置に比べてホールの注入量が抑制される。これにより、リカバリ時に排出するホールが低減し、リカバリ動作が高速化することが出来、リカバリ損失が低減する。

#### 【 0 0 3 8 】

10

次にターンオフ状態の動作（リカバリ動作）を説明する。

#### 【 0 0 3 9 】

カソード・アノード間に順方向電圧を印加した状態から、カソード・アノード間に逆方向電圧を印加する。 $n^-$ 型ドリフト層 6 に存在するホールは、アノード電極 1 0 の側に移動し、 $p^+$ 型の半導体領域 1 8 を経由してアノード電極 1 0 に流れ込み、電子はカソード電極 2 の側に移動し、 $n^+$ 型カソード層 4 を経由してカソード電極 2 に流れ込む。

#### 【 0 0 4 0 】

リカバリ時に、電子がカソード電極 2 に流れ、ホールがアノード電極 1 0 に流れている状態では、 $p^-$ 型アノード層 8 と $n^-$ 型ドリフト層 6 との接合部を起点にして、空乏層が $n^-$ 型ドリフト層 6 および $p^-$ 型アノード層 8 に拡がる。これにより、カソード・アノード間の導通はしだいに遮断される。

20

#### 【 0 0 4 1 】

但し、PINダイオードにおいては、一般的にリカバリ時に $p$  $n$ 接合部のいずれかの箇所で電界集中が起こり、アバランシェ降伏が引き起こされる場合がある。本実施形態のようにトレンチ 1 2 がある構造では、トレンチ 1 2 底部の電界が強くなり、トレンチ 1 2 底部でアバランシェ降伏を生じるようになる。アバランシェ降伏が起因となる電流集中よって、熱破壊等を生じ、素子が破壊することがある。

#### 【 0 0 4 2 】

ここで、トレンチ 1 2 底部でアバランシェ降伏によって発生したホールも、 $p^+$ 型の半導体領域 1 8 を経由してアノード電極 1 0 に流れ込む。よって $p^+$ 型の半導体領域 1 8 がトレンチ 1 2 底部に近い、つまり、Z 方向の長さ  $L_2$  が長くし、ホールの排出を強化することで素子の破壊を抑制することが可能となる。

30

#### 【 0 0 4 3 】

絶縁膜（第 1 絶縁膜の一例）2 0 は、アノード層 8 内において、半導体領域 1 8 の X 方向に接して設けられている。前述のように、 $p^+$ 型の半導体領域 1 8 の X 方向における幅、もしくは $p^+$ 型の半導体領域 1 8 とアノード電極 1 0 との接触面積によって、アノード側からのホールの注入量が調整される。しかし、本実施形態のように $p^+$ 型の半導体領域 1 8 の Z 方向の長さ  $L_2$  が大きくなると、 $p^+$ 型の半導体領域 1 8 の側面においても $p^+$ 型の半導体領域 1 8 の下方部分と同様の効果によりホール注入を生じ、ホール注入量を抑制するのが困難になる。絶縁膜 2 0 は、半導体領域 1 8 内における X 方向のホールの注入を抑制するために設けられている。

40

#### 【 0 0 4 4 】

半導体装置 1 0 0 においては、アノード層 8 a 内において、半導体領域 1 8 a に X 方向で接して絶縁膜 2 0 a が設けられている。アノード層 8 a 内において、半導体領域 1 8 b に X 方向で接して絶縁膜 2 0 b が設けられている。アノード層 8 b 内において、半導体領域 1 8 c に X 方向で接して絶縁膜 2 0 c が設けられている。アノード層 8 b 内において、半導体領域 1 8 d に X 方向で接して絶縁膜 2 0 d が設けられている。アノード層 8 c 内において、半導体領域 1 8 e に X 方向で接して絶縁膜 2 0 e が設けられている。アノード層 8 c 内において、半導体領域 1 8 f に X 方向で接して絶縁膜 2 0 f が設けられている。トレンチ 1 2 b は、絶縁膜 2 0 b と絶縁膜 2 0 c の間に設けられている。トレンチ 1 2 d は

50

、絶縁膜 20d と絶縁膜 20e の間に設けられている。絶縁膜 20a、20b、20c、20d、20e 及び 20f は、図 2 に示すように、Y 方向に、それぞれ半導体領域 18 に沿って延伸している。絶縁膜 20 は、例えば、酸化シリコン、窒化シリコン、又はカーボン等の絶縁材料を含む。

#### 【0045】

Z 方向における絶縁膜 20 の長さ  $L_3$  は、Z 方向における半導体領域 18 の長さ  $L_2$  の 0.6 倍以上 1.5 倍以下であることが好ましい。なお、図 1 においては、 $L_2 = L_3$  として図示を行っている。図 3 は、本実施形態の半導体装置の要部の模式断面図の一例である。 $L_3 = L_2 \times 0.6$  として図示を行っている。図 4 は、本実施形態の半導体装置の要部の模式断面図の他の一例である。 $L_3 = L_2 \times 1.5$  として図示を行っている。

10

#### 【0046】

Z 方向におけるアノード層 8 の長さ  $L_1$  は、Z 方向における絶縁膜 20 の長さ  $L_3$  より長いことが好ましい。同様に、Z 方向におけるアノード層 8 の長さ  $L_1$  は、Z 方向における半導体領域 18 の長さ  $L_2$  より長いことが好ましい。

#### 【0047】

図 1 に図示したように、X 方向におけるトレンチ 12a とトレンチ 12b の距離を  $D_1$  とする。X 方向における半導体領域 18 の長さを  $D_2$  とする。X 方向における絶縁膜 20 の長さを  $D_3$  とする。X 方向における絶縁膜 20a と絶縁膜 20b の距離を  $D_4$  とする。このとき、p<sup>+</sup>型の半導体領域 18 の下方部分からのホールの注入を抑制するために、 $D_2 < D_4$  であることが好ましい。

20

#### 【0048】

カソード層 4、ドリフト層 6、アノード層 8 及び半導体領域 18 に用いられる半導体材料は、例えばシリコン (Si) である。しかし、カソード層 4、ドリフト層 6、アノード層 8 及び半導体領域 18 に用いられる半導体材料は、例えば炭化シリコン (SiC)、窒化ガリウム (GaN) 又はヒ化ガリウム (GaAs) 等の他の半導体材料であってもかまわない。

#### 【0049】

半導体材料としてシリコンが用いられる場合、n 型不純物としては例えばヒ素 (As)、リン (P) 又はアンチモン (Sb) を、また p 型不純物としては例えば B (ホウ素) を、それぞれ用いることができる。

30

#### 【0050】

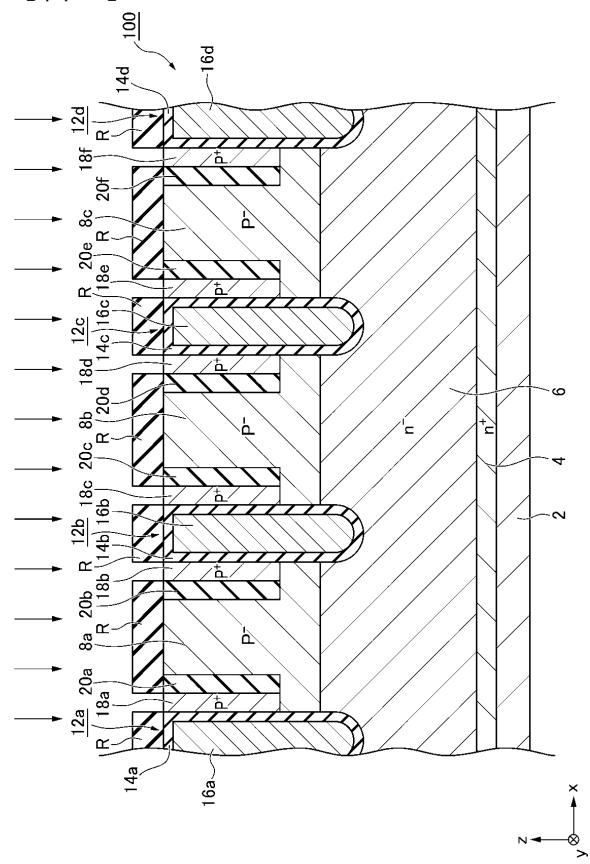

図 5 乃至図 7 は、本実施形態の半導体装置の製造工程の一部を示す模式断面図である。

#### 【0051】

まず、例えば、ドリフト層 6 を半導体基板とする。次に、ドリフト層 6 の表面に、例えばイオン注入により、アノード層 8 を形成する。次に、例えばフォトリソグラフィー及び RIE (Reactive Ion Etching) を用いて、アノード層 8 にトレンチ 12 を形成する。次に、トレンチ 12 の内部に、例えば CVD (Chemical Vapour Deposition) により、絶縁膜 14 及び電極 16 を形成する。次に、例えばエッチバックにより絶縁膜 14 の一部及び電極 16 の一部を除去し、アノード層 8 の上、絶縁膜 14 の上及び電極 16 の上を露出させる。次に、アノード層 8 の上、絶縁膜 14 の上及び電極 16 の上に、例えば酸化シリコンを含むフォトマスク M を形成する。

40

#### 【0052】

次に、例えば RIE により、アノード層 8 内に溝 30 を形成する (図 5)。図 5 においては、アノード層 8a に溝 30a 及び溝 30b が形成されている。また、アノード層 8b に溝 30c 及び溝 30d が形成されている。また、アノード層 8c に溝 30e 及び溝 30f が形成されている。

#### 【0053】

なお、図 5、以下に示す図 6、及び以下に示す図 7 では、電極 16 の上に設けられている絶縁膜 14 の一部とフォトマスク M は、別の構成物として図示をしている。しかし、例えば、電極 16 の上に設けられている絶縁膜 14 の一部は、フォトマスク M と同一の製造

50

工程で形成されていてもかまわない。また、電極 16 の上に設けられている絶縁膜 14 の一部は、上述のフォトマスク M と別の製造工程で形成されていてもかまわない。

【0054】

X 方向における溝 30a と溝 30b の距離、溝 30c と溝 30d の距離、及び溝 30e と溝 30f の距離は、例えば  $2 \mu m$  程度である。X 方向における溝 30 の開口幅は、例えば  $0.4 \mu m$  程度である。Z 方向における溝 30 の深さは、例えば  $1 \mu m$  である。ただし、X 方向における溝 30 間の距離、X 方向における溝 30 の開口幅、及び Z 方向における溝 30 の深さは、上記の記載に限定されるものではない。

【0055】

次に、例えば CVD により、溝 30 内に、絶縁膜 20 を形成する（図 6）。図 6 においては、溝 30a に絶縁膜 20a が形成されている。溝 30b に絶縁膜 20b が形成されている。溝 30c に絶縁膜 20c が形成されている。溝 30d に絶縁膜 20d が形成されている。溝 30e に絶縁膜 20e が形成されている。溝 30f に絶縁膜 20f が形成されている。

10

【0056】

次に、フォトマスク M を除去する。次に、アノード層 8 の上、絶縁膜 14 の上及び電極 16 の上に、フォトレジスト R を形成する。次に、例えばイオン注入により、トレンチ 12 と絶縁膜 20 の間に、 $p^+$  型の半導体領域 18 を形成する（図 7）。図 7 においては、トレンチ 12a と絶縁膜 20a の間に半導体領域 18a が形成されている。トレンチ 12b と絶縁膜 20b の間に半導体領域 18b が形成されている。トレンチ 12c と絶縁膜 20d の間に半導体領域 18d が形成されている。トレンチ 12c と絶縁膜 20e の間に半導体領域 18e が形成されている。トレンチ 12d と絶縁膜 20f の間に半導体領域 18f が形成されている。

20

【0057】

次に、フォトレジスト R を除去する。次に、不純物活性化のために、熱処理を行う。次に、カソード層 4 の下にカソード電極 2 を、またアノード層 8 の上、絶縁膜 14 の上及び電極 16 の上にアノード電極 10 を形成し、本実施形態の半導体装置 100 を得る。

【0058】

次に、本実施形態の半導体装置の作用効果を記載する。

30

【0059】

本実施形態の半導体装置のように、トレンチ 12 を有するダイオードを用いた半導体装置において、トレンチ 12 の底部にてアバランシェ降伏が発生した際に、トレンチ 12 の底部で発生したホールのアノード電極 10 への排出を促進させるため、トレンチ 12 の側壁に所定の深さを持つ  $p^+$  型の半導体領域 18 を設けることが考えられる。 $p^+$  型の半導体領域 18 においてはホールに対する抵抗が低くなる。従って、逆方向電圧が加わった際に、トレンチ 12 の底部で発生したホールを、 $n^-$  ドリフト層 6 からトレンチ 12 の側壁の  $p^+$  型の半導体領域 18 を経由して除去することが容易になる。

【0060】

しかし、かかる  $p^+$  型の半導体領域 18 を設けることにより、順方向電圧が印加された際、より多くのホールがアノードから注入されることとなる。逆方向電圧が加わった際には、この多くのホールが  $n^-$  ドリフト層 6 から除去される必要があり、その分のリカバリ損失が増加してしまうという問題があった。

40

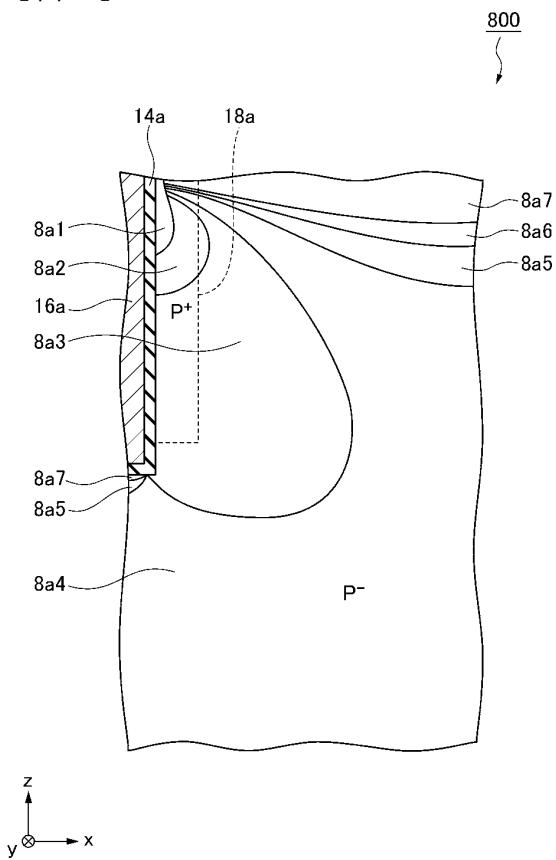

【0061】

図 8 は、本実施形態の比較形態となる半導体装置 800 の要部において、順方向電圧が印加された場合のホール電流を表す模式断面図である。半導体装置 800 においては、絶縁膜 20 が設けられていない。順方向電流が半導体装置 800 に流れている際に、アノード層 8a 内の、領域 8a1 において最も大きなホール電流が流れる。そして、領域 8a1、領域 8a2、領域 8a3、8a4、の順に、ホール電流が小さくなる。また、X 方向にも、 $p^+$  型の半導体領域 18 から  $p^-$  型アノード層 8 へホールが注入されている。かか

50

るX方向におけるホールの注入を抑制することにより、リカバリ損失の増加を抑制できると考えられる。

【0062】

そこで、本実施形態の半導体装置100は、アノード層8内において、半導体領域18に接して設けられた絶縁膜20を備える。

【0063】

ホールが、 $p^+$ 型の半導体領域18から $p^-$ 型アノード層8へ、絶縁膜20を通過して注入されることは出来ない。よって、アノード側のホール注入を抑制した半導体装置の提供が可能となる。

【0064】

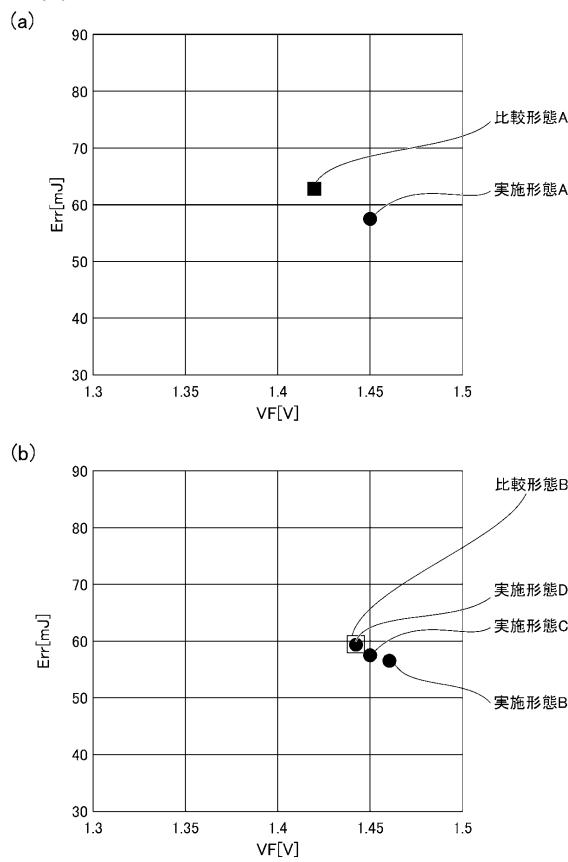

図9は、本実施形態の半導体装置100の作用効果を説明するための模式図である。図9(a)及び図9(b)は、リカバリ損失 $E_{rr}$ と順方向電圧 $V_F$ の関係を示したグラフである。

【0065】

図9(a)の比較形態Aに係る半導体装置は、トレンチの側壁に半導体領域18を備えている。比較形態Aに係る半導体装置は、絶縁膜20を備えていない。これに対して、図9(a)の実施形態Aに係る半導体装置は、半導体領域18及び絶縁膜20を備えている。

【0066】

実施形態Aに係る半導体装置の場合は、よりホール注入が抑制されるため、順方向電圧 $V_F$ が高くなり、リカバリ損失 $E_{rr}$ が低くなっている。そのため、本実施形態の半導体装置100は、比較形態Aに係る半導体装置に比べ、アノードの注入が抑制され、リカバリ損失 $E_{rr}$ を低減することができる。

【0067】

Z方向における絶縁膜20の長さ $L_3$ は、Z方向における半導体領域18の長さ $L_2$ の0.6倍以上1.5倍以下であることが好ましい。Z方向における絶縁膜20の長さ $L_3$ が、Z方向における半導体領域18の長さ $L_2$ の0.6倍未満である場合、絶縁膜20の長さが短すぎて、十分にX方向のホール電流を抑制することが出来なくなる。

【0068】

図9(b)の実施形態Bに係る半導体装置は、Z方向における絶縁膜20の長さ $L_3$ が、Z方向における半導体領域18の長さ $L_2$ の0.6倍となっている。図9(b)の実施形態Cに係る半導体装置は、Z方向における絶縁膜20の長さ $L_3$ が、Z方向における半導体領域18の長さ $L_2$ の1.0倍となっている。図9(b)の実施形態Dに係る半導体装置は、Z方向における絶縁膜20の長さ $L_3$ が、Z方向における半導体領域18の長さ $L_2$ の1.5倍となっている。なお、図9(b)には、比較形態Bに係る半導体装置についてもあわせて示している。比較形態Bに係る半導体装置は、絶縁膜20が設けられていない。このように、Z方向における絶縁膜20の長さ $L_3$ は、Z方向における半導体領域18の長さ $L_2$ の0.6倍以上1.5倍以下である場合に、よりホール注入が抑制されるため、順方向電圧 $V_F$ が高くなり、リカバリ損失 $E_{rr}$ が低くなっている。

【0069】

Z方向におけるアノード層8の長さ $L_1$ は、Z方向における絶縁膜20の長さ $L_3$ より長いことが好ましい。これは、Z方向における絶縁膜20の長さ $L_3$ がアノード層8の長さ $L_1$ 以上である場合には、絶縁膜20がドリフト層6に食い込んでしまい、絶縁膜20の下方の先端部に電界集中が発生してしまうためである。同様に、Z方向におけるアノード層8の長さ $L_1$ は、Z方向における半導体領域18の長さ $L_2$ より長いことが好ましい。

【0070】

絶縁膜20は、酸化シリコンを含むことが好ましい。容易に作成が可能であるためである。

【0071】

X方向における半導体領域18の長さを $D_2$ 、X方向における絶縁膜20aと絶縁膜20bの距離を $D_4$ としたときに、 $D_2 < D_4$ であることが好ましい。これは、 $D_2 = D_4$ で

10

20

30

40

50

ある場合には、より多くのホールが p + 型の半導体領域 18 から注入されることとなるため、逆方向電圧が加わった際にリカバリ損失が増加してしまうためである。

【 0 0 7 2 】

本実施形態の半導体装置によれば、リカバリ損失の低減が達成され、安全動作領域が拡大された半導体装置を提供することが可能となる。

【 0 0 7 3 】

( 第 2 実施形態 )

本実施形態の半導体装置は、第 2 半導体層内において、第 1 トレンチにそれぞれ接して、互いに離間して設けられ、第 2 半導体層よりそれぞれ第 2 導電型不純物濃度の高い複数の第 1 半導体領域と、第 2 半導体層内において、複数の第 1 半導体領域にそれぞれ接して、互いに離間して設けられた複数の第 1 絶縁膜と、をさらに備える点で、第 1 実施形態の半導体装置とは異なっている。ここで、第 1 実施形態の半導体装置と重複する内容の記載は省略する。

10

【 0 0 7 4 】

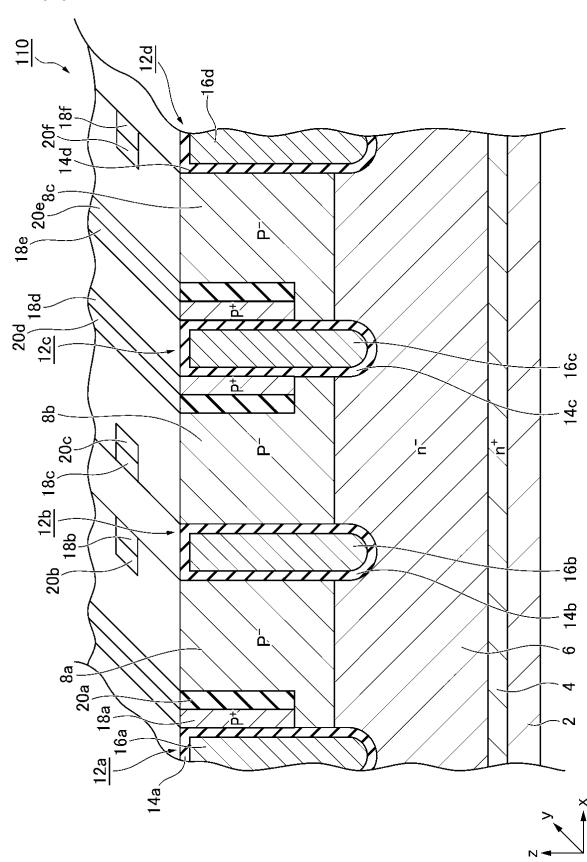

図 10 は、本実施形態の半導体装置 110 の模式斜視図である。

【 0 0 7 5 】

Y 方向における半導体領域 18b の長さは、Y 方向における半導体領域 18a の長さ及び Y 方向における絶縁膜 20a の長さより短い。また、Y 方向における絶縁膜 20b の長さは、Y 方向における半導体領域 18a の長さ及び Y 方向における絶縁膜 20a の長さより短い。

20

【 0 0 7 6 】

同様に、Y 方向における半導体領域 18c の長さは、Y 方向における半導体領域 18a の長さ及び Y 方向における絶縁膜 20a の長さより短い。また、Y 方向における絶縁膜 20c の長さは、Y 方向における半導体領域 18a の長さ及び Y 方向における絶縁膜 20a の長さより短い。

【 0 0 7 7 】

同様に、Y 方向における半導体領域 18f の長さは、Y 方向における半導体領域 18a の長さ及び Y 方向における絶縁膜 20a の長さより短い。また、Y 方向における絶縁膜 20f の長さは、Y 方向における半導体領域 18a の長さ及び Y 方向における絶縁膜 20a の長さより短い。

30

【 0 0 7 8 】

なお、図 10 において、Y 方向における絶縁膜 20b の長さは、Y 方向における半導体領域 18b の長さと同じとして図示されている。しかし、Y 方向における絶縁膜 20b の長さは、Y 方向における半導体領域 18b の長さと異なっていてもかまわない。例えば、Y 方向における絶縁膜 20b の長さは、Y 方向における半導体領域 18b の長さより長くてもかまわない。また、Y 方向における絶縁膜 20b の長さは、Y 方向における半導体領域 18b の長さより短くてもかまわない。しかし、アノードの低注入化の観点から、Y 方向における絶縁膜 20b の長さは、Y 方向における半導体領域 18b の長さ以上であることが好ましい。半導体領域 18c、絶縁膜 20c、半導体領域 18f 及び絶縁膜 20f についても同様である。

40

【 0 0 7 9 】

なお、例えば、Y 方向に沿って、トレンチ 12b の側壁にそれぞれ接して、互いに離間した複数の半導体領域 18b が設けられていてもかまわない。例えば、Y 方向に沿って、複数の半導体領域 18b にそれぞれ接して、互いに離間した複数の絶縁膜 20b が設けられていてもかまわない。例えば、Y 方向に沿って、トレンチ 12b の側壁に、互いに離間した複数の半導体領域 18c が設けられていてもかまわない。例えば、Y 方向に沿って、複数の半導体領域 18c にそれぞれ接して、互いに離間した複数の絶縁膜 20c が設けられていてもかまわない。例えば、Y 方向に沿って、トレンチ 12d の側壁に、互いに離間した複数の半導体領域 18f が設けられていてもかまわない。例えば、Y 方向に沿って、複数の半導体領域 18f にそれぞれ接して、互いに離間した複数の絶縁膜 20f が設けら

50

れてもかまわない。かかる場合、トレンチ 12 b は、第 1 トレンチの一例である。複数の半導体領域 18 b 及び複数の絶縁膜 20 b は、それぞれ、複数の第 1 半導体領域及び複数の第 1 絶縁膜の一例である。

#### 【 0 0 8 0 】

また、図 10においては、半導体領域 18 a、絶縁膜 20 a、半導体領域 18 d、絶縁膜 20 d、半導体領域 18 e 及び絶縁膜 20 e のように、Y 方向に延伸する半導体領域 18 及び絶縁膜 20 と、半導体領域 18 b、絶縁膜 20 b、半導体領域 18 c、絶縁膜 20 c、半導体領域 18 f 及び絶縁膜 20 f のように、Y 方向の長さがより短い半導体領域 18 及び絶縁膜 20 と、が図示されている。これらが X 方向において配置される順番は、特に図 10 に図示された様に限定されるものではない。さらに、図 10 においては Y 方向の長さがより短い半導体領域 18 及び絶縁膜 20 が複数設けられているように示したが、Y 方向の長さがより短い半導体領域 18 及び絶縁膜 20 の個数は 1 つでも実施可能である。

#### 【 0 0 8 1 】

言い換えると、トレンチ 12 b の少なくとも一部は、アノード層 8 内において、半導体領域 18 b 及び半導体領域 18 c と X 方向で接しない部分を有している。また、トレンチ 12 b は、半導体領域 18 b 及び半導体領域 18 c と X 方向で接する部分を有している。かかる場合、トレンチ 12 b は、第 2 トレンチの一例である。

#### 【 0 0 8 2 】

言い換えると、トレンチ 12 d の少なくとも一部は、アノード層 8 内において、半導体領域 18 f と X 方向で接しない部分を有している。また、トレンチ 12 d は、半導体領域 18 f と X 方向で接する部分を有している。

#### 【 0 0 8 3 】

半導体装置内に注入されるホールの量を少なくして、アノードを低注入化するためには、半導体領域 18 の体積をできるだけ小さくすることが好ましい。そこで、半導体装置 110 においては、Y 方向における半導体領域 18 b の長さをより短くする。これにより、アノード層 8 a における半導体領域 18 の体積をより小さくしている。また、アノード層 8 b 内においては、Y 方向における半導体領域 18 c の長さをより短くしている。これにより、アノード層 8 b 内における半導体領域 18 の体積をより小さくしている。また、アノード層 8 c 内においては、Y 方向における半導体領域 18 f の長さをより短くしている。これにより、アノード層 8 c 内における半導体領域 18 の体積をより小さくしている。これにより、リカバリ損失も低減しつつ、安全動作領域の維持も可能となる半導体装置を提供することが可能となる。

#### 【 0 0 8 4 】

Y 方向における絶縁膜 20 b の長さについては、X 方向における p<sup>+</sup> 半導体領域 18 b からのホール注入を抑制出来る程度に十分な長さが設けられていれば良い。そのため、Y 方向における絶縁膜 20 b の長さは、Y 方向における半導体領域 18 a の長さ及び絶縁膜 20 a の長さより短い。なお、Y 方向における絶縁膜 20 c の長さ及び Y 方向における絶縁膜 20 f の長さも、同様である。また、複数の半導体領域 18 b、複数の絶縁膜 20 b、複数の半導体領域 18 c、複数の絶縁膜 20 c、複数の半導体領域 18 f 及び複数の絶縁膜 20 f を設けることにより、p<sup>+</sup> の半導体領域 18 f からのホール注入及びホール拡散をより良く制御出来る。

#### 【 0 0 8 5 】

本実施形態の半導体装置においても、リカバリ損失の低減が達成され、安全動作領域が拡大された半導体装置を提供することが可能となる。

#### 【 0 0 8 6 】

##### ( 第 3 実施形態 )

本実施形態の半導体装置は、第 2 半導体層内において、第 2 トレンチに接して設けられ、第 2 半導体層より第 2 導電型不純物濃度の高い第 2 半導体領域は設けられておらず、第 2 半導体層内において、第 2 半導体領域に接する第 2 絶縁膜は設けられていない点で、第 1 実施形態及び第 2 実施形態の半導体装置と異なっている。ここで、第 1 実施形態及び第

2 実施形態と重複する内容の記載は省略する。

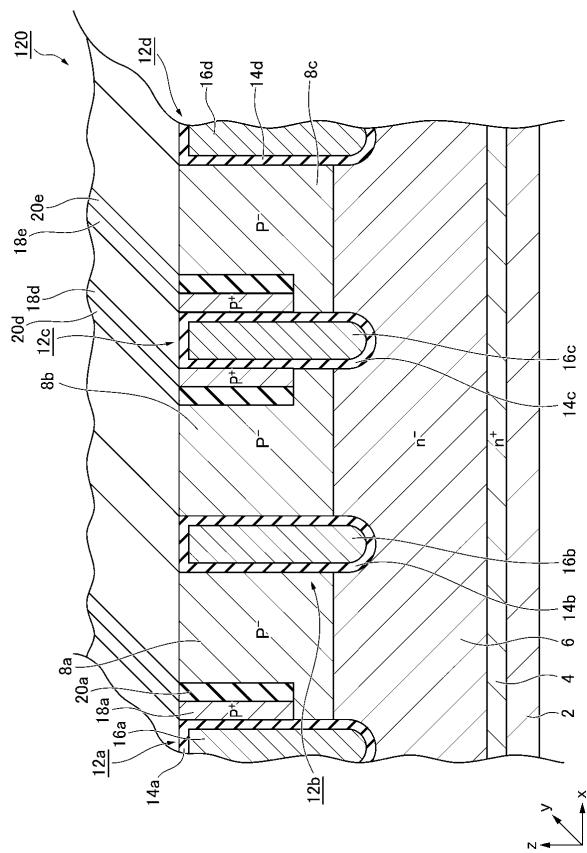

【0087】

図11は、本実施形態の半導体装置120の模式斜視図である。本実施形態においては、トレンチ12a及びトレンチ12cを第1トレンチの一例、トレンチ12bとトレンチ12dを第2トレンチの一例として説明する。半導体装置100及び半導体装置110と異なり、半導体装置120においては、トレンチ12bの側壁に接する半導体領域18b（第2半導体領域の一例）、半導体領域18c（第2半導体領域の一例）及びトレンチ12dの側壁に接する半導体領域18fは設けられていない。また、半導体領域18bに接する絶縁膜20b（第2絶縁膜の一例）、半導体領域18cに接する絶縁膜20c（第2絶縁膜の一例）及び半導体領域18fに接する絶縁膜20fも、設けられていない。

10

【0088】

言い換えると、トレンチ12bの少なくとも一部は、アノード層8内において、半導体領域18b及び半導体領域18cとX方向で接しない部分を有している。また、トレンチ12bは、半導体領域18b及び半導体領域18cとX方向で接する部分を有していない。

【0089】

言い換えると、トレンチ12dの少なくとも一部は、アノード層8内において、半導体領域18fとX方向で接しない部分を有している。また、トレンチ12dは、半導体領域18fとX方向で接する部分を有していない。

【0090】

なお、X方向において、第1トレンチ（トレンチ12a及びトレンチ12c）と、第2トレンチ（トレンチ12bとトレンチ12d）の配列は、図11に図示したものに限定されるものではない。

20

【0091】

上述の通り、半導体装置内に注入されるホールの量を少なくて、アノードを低注入化するためには、半導体領域18の体積をできるだけ小さくすることが好ましい。そこで、半導体装置120は、半導体領域18が設けられないトレンチ12bを備えている。半導体領域18が設けられていない場合、これに接する絶縁膜20を設けることは不要である。

【0092】

本実施形態の半導体装置においても、リカバリ損失の低減が達成され、安全動作領域が拡大された半導体装置を提供することが可能となる。

30

【0093】

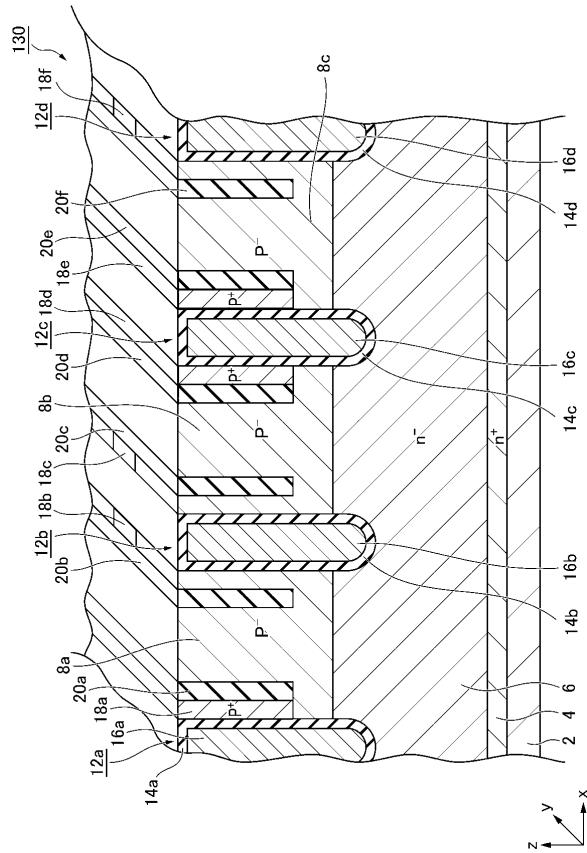

（第4実施形態）

本実施形態の半導体装置は、半導体領域18bに接する絶縁膜20bがY方向に延伸している点で、第2実施形態の半導体装置と異なっている。ここで、第1乃至第3実施形態と重複する内容の記載は省略する。

【0094】

図12は、本実施形態の半導体装置130の模式斜視図である。

【0095】

絶縁膜20a、絶縁膜20b、絶縁膜20c、絶縁膜20d、絶縁膜20e及び絶縁膜20fは、Y方向に延伸している。Y方向における半導体領域18b、半導体領域18c及び半導体領域18fの長さは、Y方向における半導体領域18a、半導体領域18e及び半導体領域18fの長さより短い。

40

【0096】

言い換えると、半導体装置130は、図10に示した半導体装置110と異なり、半導体領域18bに接する絶縁膜20b、半導体領域18cに接する絶縁膜20c及び半導体領域18fに接する絶縁膜20fが、Y方向に延伸している。このため、半導体領域18内におけるX方向のホールの拡散がより抑制される。

【0097】

本実施形態の半導体装置においても、リカバリ損失の低減が達成され、安全動作領域が拡大された半導体装置を提供することが可能となる。

50

## 【0098】

(第5実施形態)

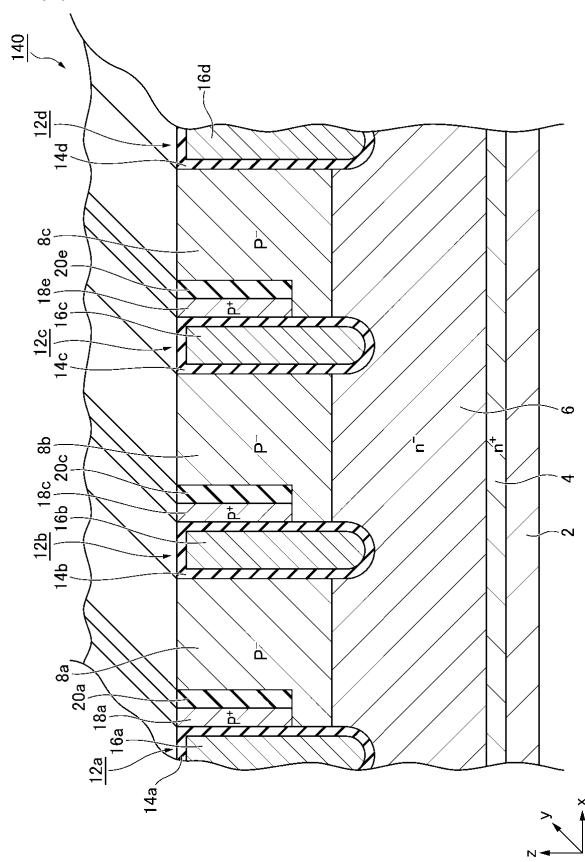

図13は、本実施形態の半導体装置140の模式斜視図である。

## 【0099】

半導体装置140においては、半導体領域18a、半導体領域18c及び半導体領域18eが設けられている。また、半導体装置140においては、絶縁膜20a、絶縁膜20c及び絶縁膜20eが設けられている。一方、半導体装置140においては、半導体領域18b、半導体領域18d及び半導体領域18fが設けられていない。また、半導体装置140においては、絶縁膜20b、絶縁膜20d及び絶縁膜20fが設けられていない。

## 【0100】

本実施形態の半導体装置の態様は以下の通りである。すなわち、図13の紙面で、それぞれのトレンチ12の右側に設けられた側壁に、半導体領域18及び絶縁膜20が設けられている。一方、それぞれのトレンチ12の左側に設けられた側壁には、半導体領域18及び絶縁膜20が設けられていない。

10

## 【0101】

言い換えると、図13の紙面で、トレンチ12bの左側に設けられた側壁において、トレンチ12bの少なくとも一部は、アノード層8a内において、半導体領域18bとX方向で接しない部分を有している。また、図13の紙面で、トレンチ12bの左側に設けられた側壁において、トレンチ12bは、半導体領域18bとX方向で接する部分を有していない。

20

## 【0102】

言い換えると、図13の紙面で、トレンチ12cの左側に設けられた側壁において、トレンチ12cの少なくとも一部は、アノード層8b内において、半導体領域18cとX方向で接しない部分を有している。また、図13の紙面で、トレンチ12cの左側に設けられた側壁において、トレンチ12cは、半導体領域18cとX方向で接する部分を有していない。

## 【0103】

言い換えると、図13の紙面で、トレンチ12dの左側に設けられた側壁において、トレンチ12dの少なくとも一部は、アノード層8c内において、半導体領域18dとX方向で接しない部分を有している。また、図13の紙面で、トレンチ12dの左側に設けられた側壁において、トレンチ12dは、半導体領域18dとX方向で接する部分を有していない。

30

## 【0104】

本実施形態の半導体装置140においては、第1の実施形態に係る半導体装置100と比較して半導体領域18の体積が小さいため、半導体装置内に注入されるホールの量を少なくし、アノードを低注入化することができる。

## 【0105】

本実施形態の半導体装置においても、リカバリ損失の低減が達成され、安全動作領域が拡大された半導体装置を提供することが可能となる。

40

## 【0106】

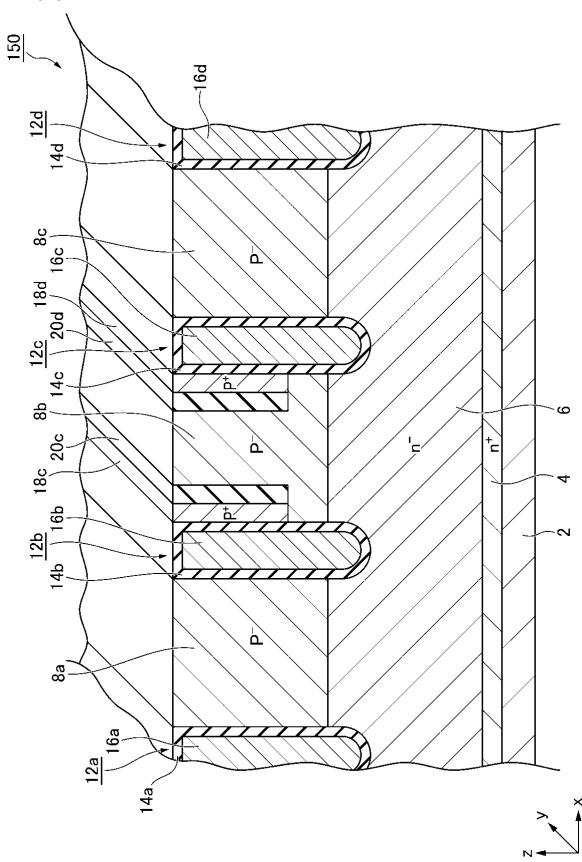

(第6実施形態)

図14は、本実施形態の半導体装置150の模式斜視図である。

## 【0107】

半導体装置140においては、半導体領域18c及び半導体領域18dが設けられている。また、半導体装置140においては、絶縁膜20c及び絶縁膜20dが設けられている。一方、半導体装置140においては、半導体領域18a、半導体領域18b、半導体領域18e及び半導体領域18fが設けられていない。また、半導体装置140においては、絶縁膜20a、絶縁膜20b、絶縁膜20e及び絶縁膜20fが設けられていない。

## 【0108】

本実施形態の半導体装置150においては、X方向においてアノード層8bを挟んで対

50

向するように絶縁膜 20c 及び絶縁膜 20d が設けられている。また、X 方向においてアノード層 8b を挟んで対向するように半導体領域 18c 及び半導体領域 18d が設けられている。一方、アノード層 8a 及びアノード層 8c には、半導体領域 18 及び絶縁膜 20 が設けられていない。

【0109】

言い換えると、図 14 の紙面で、トレンチ 12a の右側に設けられた側壁において、トレンチ 12a の少なくとも一部は、アノード層 8a 内において、半導体領域 18a と X 方向で接しない部分を有している。また、図 14 の紙面で、トレンチ 12a の右側に設けられた側壁において、トレンチ 12a は、半導体領域 18a と X 方向で接する部分を有していない。

10

【0110】

言い換えると、図 14 の紙面で、トレンチ 12b の左側に設けられた側壁において、トレンチ 12b の少なくとも一部は、アノード層 8a 内において、半導体領域 18b と X 方向で接しない部分を有している。また、図 14 の紙面で、トレンチ 12b の左側に設けられた側壁において、トレンチ 12a は、半導体領域 18b と X 方向で接する部分を有していない。

【0111】

言い換えると、図 14 の紙面で、トレンチ 12c の右側に設けられた側壁において、トレンチ 12c の少なくとも一部は、アノード層 8c 内において、半導体領域 18e と X 方向で接しない部分を有している。また、図 14 の紙面で、トレンチ 12c の右側に設けられた側壁において、トレンチ 12c は、半導体領域 18e と X 方向で接する部分を有していない。

20

【0112】

言い換えると、図 14 の紙面で、トレンチ 12d の左側に設けられた側壁において、トレンチ 12d の少なくとも一部は、アノード層 8c 内において、半導体領域 18f と X 方向で接しない部分を有している。また、図 14 の紙面で、トレンチ 12d の左側に設けられた側壁において、トレンチ 12d は、半導体領域 18f と X 方向で接する部分を有していない。

【0113】

本実施形態の半導体装置 150 においても、第 1 の実施形態に係る半導体装置 100 と比較して半導体領域 18 の体積が小さいため、半導体装置内に注入されるホールの量を少なくし、アノードを低注入化することができる。

30

【0114】

本実施形態の半導体装置においても、リカバリ損失の低減が達成され、安全動作領域が拡大された半導体装置を提供することが可能となる。

【0115】

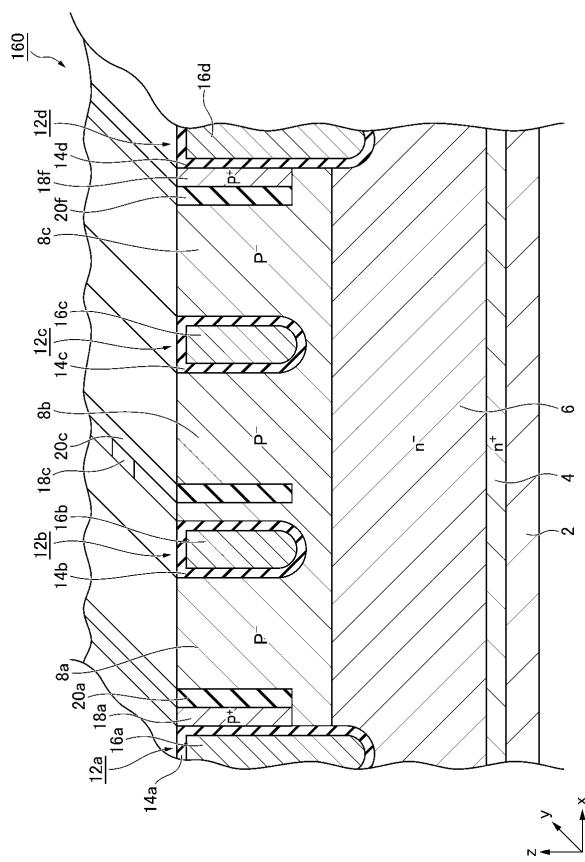

(第 7 実施形態)

本実施形態の半導体装置は、第 2 半導体層から第 1 半導体層に向かい、第 1 半導体層に到達しない、第 1 絶縁膜と離間して設けられた第 2 トレンチと、第 2 半導体層内において、第 2 トレンチに接して設けられ、第 2 半導体層より第 2 導電型不純物濃度の高い第 2 半導体領域と、第 2 半導体層内において、第 2 半導体領域に接して設けられた第 2 絶縁膜と、を備える点で、第 1 実施形態乃至第 6 実施形態の半導体装置と異なっている。ここで、第 1 乃至第 6 実施形態と重複する内容の記載は省略する。

40

【0116】

図 15 は、本実施形態の半導体装置 160 の模式斜視図である。トレンチ 12b (第 2 トレンチの一例) 及びトレンチ 12c は、ドリフト層 6 に到達していない。言い換えると、トレンチ 12b の底部及びトレンチ 12c の底部は、アノード層 8 内に設けられている。一方、トレンチ 12a 及びトレンチ 12d は、ドリフト層 6 に到達している。

【0117】

また、トレンチ 12a の側壁に接する半導体領域 18a 及びトレンチ 12d の側壁に接

50

する半導体領域 18 f が設けられている。一方、トレンチ 12 b の側壁に接して設けられている半導体領域 18 c (第 3 半導体領域の一例) の Y 方向における長さは、Y 方向における半導体領域 18 a の長さより短い。また、半導体装置 160 においては、半導体領域 18 b、半導体領域 18 d 及び半導体領域 18 e は、設けられていない。なお、半導体領域 18 c は、Y 方向に、トレンチ 12 b の側壁に沿って延伸していてもかまわない。言い換えると、Y 方向における半導体領域 18 c の長さは、Y 方向における半導体領域 18 a の長さと等しくてもかまわない。また、Y 方向における絶縁膜 20 c (第 2 絶縁膜の一例) の長さは、例えば、Y 方向における半導体領域 18 c の長さと等しくてもかまわない。さらに、例えば、Y 方向に沿って、トレンチ 12 b の側壁にそれぞれ接して、互いに離間した複数の半導体領域 18 c が設けられていてもかまわない。例えば、Y 方向に沿って、複数の半導体領域 18 c にそれぞれ接して、互いに離間した複数の絶縁膜 20 c が設けられていてもかまわない。

#### 【0118】

言い換えると、図 15 の紙面で、トレンチ 12 b の左側に設けられた側壁において、トレンチ 12 b の少なくとも一部は、アノード層 8 a 内において、半導体領域 18 b と X 方向で接しない部分を有している。また、図 14 の紙面で、トレンチ 12 b の左側に設けられた側壁において、トレンチ 12 a は、半導体領域 18 b と X 方向で接する部分を有していない。

#### 【0119】

言い換えると、図 15 の紙面で、トレンチ 12 c の左側に設けられた側壁において、トレンチ 12 c の少なくとも一部は、アノード層 8 b 内において、半導体領域 18 d と X 方向で接しない部分を有している。また、図 14 の紙面で、トレンチ 12 b の左側に設けられた側壁において、トレンチ 12 a は、半導体領域 18 b と X 方向で接する部分を有していない。

#### 【0120】

言い換えると、図 15 の紙面で、トレンチ 12 c の右側に設けられた側壁において、トレンチ 12 c の少なくとも一部は、アノード層 8 c 内において、半導体領域 18 e と X 方向で接しない部分を有している。また、図 15 の紙面で、トレンチ 12 c の右側に設けられた側壁において、トレンチ 12 c は、半導体領域 18 e と X 方向で接する部分を有していない。

#### 【0121】

アバランシェ降伏によって発生したホールの排出を強化するためには、トレンチ 12 b 及びトレンチ 12 c よりも Z 方向に長い、トレンチ 12 a の底部及びトレンチ 12 d の底部にてアバランシェ降伏を生じさせ、良好にホールを除去することが好ましい。Y 方向における長さが短い半導体領域 18 c が設けられていると、p<sup>+</sup> の半導体領域 18 が占める割合が小さくなり、アノード低注入化が実現できる。一方、リカバリ時は、半導体領域 18 c が設けられたトレンチ 12 b 近傍でのホール排出は弱くなる。つまりリカバリ時のホール排出はトレンチ 12 a およびトレンチ 12 d 近傍で行う必要がある。本実施形態では、トレンチ 12 b 及びトレンチ 12 c よりも Z 方向に長い、トレンチ 12 a の底部及びトレンチ 12 d の底部でアバランシェ降伏が起きやすい。よって、アバランシェ降伏によって生じたホールを効果的に排出させることができる。全体が同じ長さのトレンチ構造よりも安定的に狙ったトレンチ底部からホールを排出しやすくするためである。一方、Z 方向に短いトレンチ 12 b、トレンチ 12 c では、トレンチ底部におけるアバランシェ降伏が起きにくいくことから、ホール排出経路が少なくてもよい。

#### 【0122】

本実施形態の半導体装置においても、リカバリ損失の低減が達成され、安全動作領域が拡大された半導体装置を提供することが可能となる。

#### 【0123】

本発明のいくつかの実施形態及び実施例を説明したが、これらの実施形態及び実施例は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新

規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことが出来る。これら実施形態やその変形は、発明の範囲や要旨に含まれると共に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0124】

|     |                         |    |

|-----|-------------------------|----|

| 2   | ：カソード電極（第1電極）           | 10 |

| 6   | ：ドリフト層（第1半導体層）          |    |

| 8   | ：アノード層（第2半導体層）          |    |

| 10  | ：アノード電極（第2電極）           |    |

| 12  | ：トレンチ（第1トレンチ、第2トレンチ）    |    |

| 18  | ：半導体領域（第1半導体領域、第2半導体領域） |    |

| 20  | ：絶縁膜（第1絶縁膜、第2絶縁膜）       |    |

| 100 | ：半導体装置                  |    |

| 110 | ：半導体装置                  |    |

| 120 | ：半導体装置                  |    |

| 130 | ：半導体装置                  |    |

| 140 | ：半導体装置                  |    |

| 150 | ：半導体装置                  |    |

| 160 | ：半導体装置                  | 20 |

30

30

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【 义 5 】

【 図 6 】

【 四 7 】

【 図 8 】

10

20

30

40

50

【図 9】

【図 10】

【図 11】

【図 12】

10

20

30

40

50

### 【図13】

【図14】

【図15】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

H 01 L 21/329 (2006.01)

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 2 F |

| H 01 L | 29/78 | 6 5 2 S |

| H 01 L | 29/78 | 6 5 5 G |

| H 01 L | 29/78 | 6 5 5 B |

| H 01 L | 29/78 | 6 5 5 A |

| H 01 L | 29/91 | C       |

| H 01 L | 29/91 | A       |

(72)発明者 河村 圭子

東京都港区芝浦一丁目1番1号 東芝デバイス&amp;ストレージ株式会社内

(72)発明者 もたい 貴子

東京都港区芝浦一丁目1番1号 東芝デバイス&amp;ストレージ株式会社内

(72)発明者 末代 知子

東京都港区芝浦一丁目1番1号 東芝デバイス&amp;ストレージ株式会社内

(72)発明者 岩鍛治 陽子

東京都港区芝浦一丁目1番1号 東芝デバイス&amp;ストレージ株式会社内

審査官 志津木 康

(56)参考文献

|                       |

|-----------------------|

| 特開2020-072137 (JP, A) |

| 特開2018-190860 (JP, A) |

| 特開2018-073911 (JP, A) |

| 特開2015-177058 (JP, A) |

| 特開2015-195366 (JP, A) |

(58)調査した分野 (Int.Cl., DB名)

|                          |

|--------------------------|

| H 01 L 29 / 78           |

| H 01 L 21 / 336          |

| H 01 L 29 / 739          |

| H 01 L 29 / 86 - 29 / 96 |

| H 01 L 21 / 329          |