(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 693 05 203 T3 2006.08.24

## (12) Übersetzung der geänderten europäischen Patentschrift

(97) EP 0 560 226 B2

(21) Deutsches Aktenzeichen: 693 05 203.1

(96) Europäisches Aktenzeichen: 93 103 563.8

(96) Europäischer Anmeldetag: 05.03.1993

(97) Erstveröffentlichung durch das EPA: 15.09.1993

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 09.10.1996

(97) Veröffentlichungstag

des geänderten Patents beim EPA: 11.01.2006

(47) Veröffentlichungstag im Patentblatt: 24.08.2006

(51) Int Cl.<sup>8</sup>: G05B 19/414 (2006.01)

G05B 19/418 (2006.01)

(30) Unionspriorität:

847542 06.03.1992 US

(84) Benannte Vertragsstaaten:

DE, FR, GB, IT

(73) Patentinhaber:

Pitney Bowes, Inc., Stamford, Conn., US

(72) Erfinder:

Di Giulio, Peter C., Fairfield, Connect. 06430, US;

Lee, David K., Monroe, Connecticut 06468, US;

Riley, David W., Easton, Connecticut 06612, US;

Ryan, Frederick W., Jr., New Haven, Connecticut

06515, US

(74) Vertreter:

HOFFMANN & EITLE, 81925 München

(54) Bezeichnung: **Flexibile Kommunikationsarchitektur für ein Bewegungssteuerungssystem**

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Diese Erfindung betrifft Bewegungssteuersysteme mit Serienkommunikation, einschließlich derjenigen, die auf Robotersysteme anwendbar sind, sowie Autosysteme oder Partikelbearbeitungssysteme, insbesondere Papierhandhabungssysteme. In Papierhandhabungssystemen werden Papierbögen in allgemein aufeinanderfolgender Weise über eine Reihe von motorgetriebenen Komponenten geführt, beispielsweise Bänder und Walzen. Oft bewegen sich die Bögen mit hoher Geschwindigkeit, und während der Überleitung von einem Band oder einer Walze zu der nächsten erfahren sie besonders hohe Beschleunigungen. Der Betrieb der Bewegungssteuerkomponenten ist besonders sorgfältig in Echtzeit zu koordinieren, damit gewährleistet ist, daß die Komponenten-zu-Komponenten-Übergänge reibungslos und ohne Stau verlaufen. Es ist oft auch günstig, die Positionen der Bögen sowie die Positionen der Motorwellen und deren Geschwindigkeiten mit Sensoren zu überwachen. Üblicherweise erfolgt die Steuerung für die Motorsteuerung, die Sensorsteuerung und der allgemeinen Systemfunktionen mit zumindest einem Prozessor. Steuersignale müssen zu mechanischen Antriebsmaschinen abgegeben werden (Motor, Solenoide, Wandler, usw.), und Sensordaten werden durch die Sensoren erfaßt. Ist zudem mehr als ein Sensor in dem System vorgesehen, so ist die Prozessor-zu-Prozessorkommunikation zu unterstützen. Zusätzlich ist es in modularen Papierhandhabungssystemen erforderlich, eine Vorrichtung für die Rekonfiguration des Systems und zum Hinzufügen neuer Module vorzusehen.

**[0002]** In US-A-4 835 699 ist ein Kommunikationssystem mit Merkmalen gemäß denjenigen des Oberbegriffs des Patentanspruchs 1 beschrieben. In Elektronik Bd. 40, 29. Oktober 1991, Seiten 59-62, 65, 65, 68, 69 ist eine Netzwerkommunikation zwischen Knoten beschrieben, unter Einsatz von "Leitwegelementen", "Brücken", und "Gateway"-Elementen.

**[0003]** Relevanter Stand der Technik ist auch in dem technischen Artikel "Time Critical Communication Networks: Field Buses", IEEE Network, 2 (1988), Nr. 3, New York, NY, US, Seiten 55-63., von P. Pleineaux et. al. offenbart.

**[0004]** In EP-A-0 200 365 ist ein Steuersystem mit verteilten programmierbaren Kontrollern beschrieben. Ein "aktiver Monitor" ruft zum Bereitstellen einer Liste weitere Knoten in dem Netzwerk ab und ordnet jedem Knoten zum Senden für dessen Daten einen Zeitschlitz zu.

**[0005]** Demnach wäre es wünschenswert, eine Kommunikationsarchitektur für ein Bewegungssteuersystem zu schaffen, das eine Konfiguration des Systems derart ermöglicht, daß (a) ein zentralisierter Steuerknoten und periphere Randknoten vorgesehen sind, sowie (b) ein zentralisierter Steuerknoten und verteilte Steuerknoten oder (c) ein zentralisierter Steuerknoten, Randsteuerknoten und verteilte Steuerknoten.

**[0006]** Es wäre auch wünschenswert, eine Kommunikationsarchitektur zu ermöglichen, die das einfache Mit-einbeziehen zusätzlicher Module in das System ermöglicht.

**[0007]** Es wäre auch wünschenswert, den Umfang der Verdrahtung zum Verbinden der zahlreichen Elemente in den Bewegungssteuersystemen zu reduzieren.

**[0008]** Es wäre auch wünschenswert, eine Kommunikationsarchitektur für ein Bewegungssteuersystem zu ermöglichen, die eine sorgfältige Isolation der Verdrahtung gegenüber einer elektromagnetischen und einer Hochfrequenz-Interferenz ermöglicht.

**[0009]** Es wäre auch wünschenswert, eine Kommunikationsarchitektur für ein Bewegungssteuersystem zu ermöglichen, das eine Zunahme der Zahl der benützten gemeinsamen Teile ermöglicht, sowohl innerhalb einer Produktlinie als auch von Produktlinie zu Produktlinie, um hierdurch die Systemkosten zu reduzieren.

**[0010]** Es wäre auch wünschenswert, eine Kommunikationsarchitektur und ein Bewegungssteuersystem zu schaffen, das eine einfache Rekonfiguration für das System ermöglicht, für eine schnellere Produktentwicklung.

**[0011]** Es wäre auch wünschenswert, eine Kommunikationsarchitektur für ein Bewegungssteuersystem zu schaffen, bei dem Servicedienste auf Anwendungsebene während des Arbeitsbetriebs angeboten werden, einschließlich Herstellungs- und Servicediagnosefunktionen, und bei dem nach einer Systemrekonfiguration ein Netzwerk automatisch konfiguriert wird.

**[0012]** Es wäre auch wünschenswert, eine Architektur zu schaffen, die Bewegungssteuerungs-Systemknoten

ermöglicht, bei denen eine Boundary-Scan-Technik einsetzbar ist und bei der Boundary-Scan-Information von oder zu einem einzigen Netzwerkverbindungspunkt übertragbar ist, damit ein Herstellungstest und eine Servicediagnose möglich ist.

[0013] Es wäre auch wünschenswert, eine Kommunikationsarchitektur für ein Bewegungssteuersystem zu schaffen, bei dem die Angleichung der Kommunikations-Baudrate zum Erzielen einer optimalen Abwägung zwischen Kosten/Leisten ermöglicht wird.

[0014] Eine Aufgabe der vorliegenden Erfindung besteht in der Schaffung einer Kommunikationsarchitektur für ein Bewegungssteuersystem, das die Konfiguration des Systems mit (a) einem zentralisierten Knoten und peripheren Steuerknoten, (b) einen zentralisierten Steuerknoten und verteilten Steuerknoten oder (c) einem zentralisierten Steuerknoten und peripheren Steuerknoten und verteilten Steuerknoten ermöglicht.

[0015] Gemäß der Erfindung wird ein Steuersystem mit serieller Kommunikation gemäß dem Patentanspruch 1 geschaffen.

[0016] Die obigen und weitere Aufgaben und Vorteile dieser Erfindung ergeben sich bei Betrachtung der folgenden detaillierten Beschreibung im Zusammenhang mit der beiliegenden Zeichnung, in der gleiche Bezugszeichen gleiche Teile kennzeichnen; es zeigen:

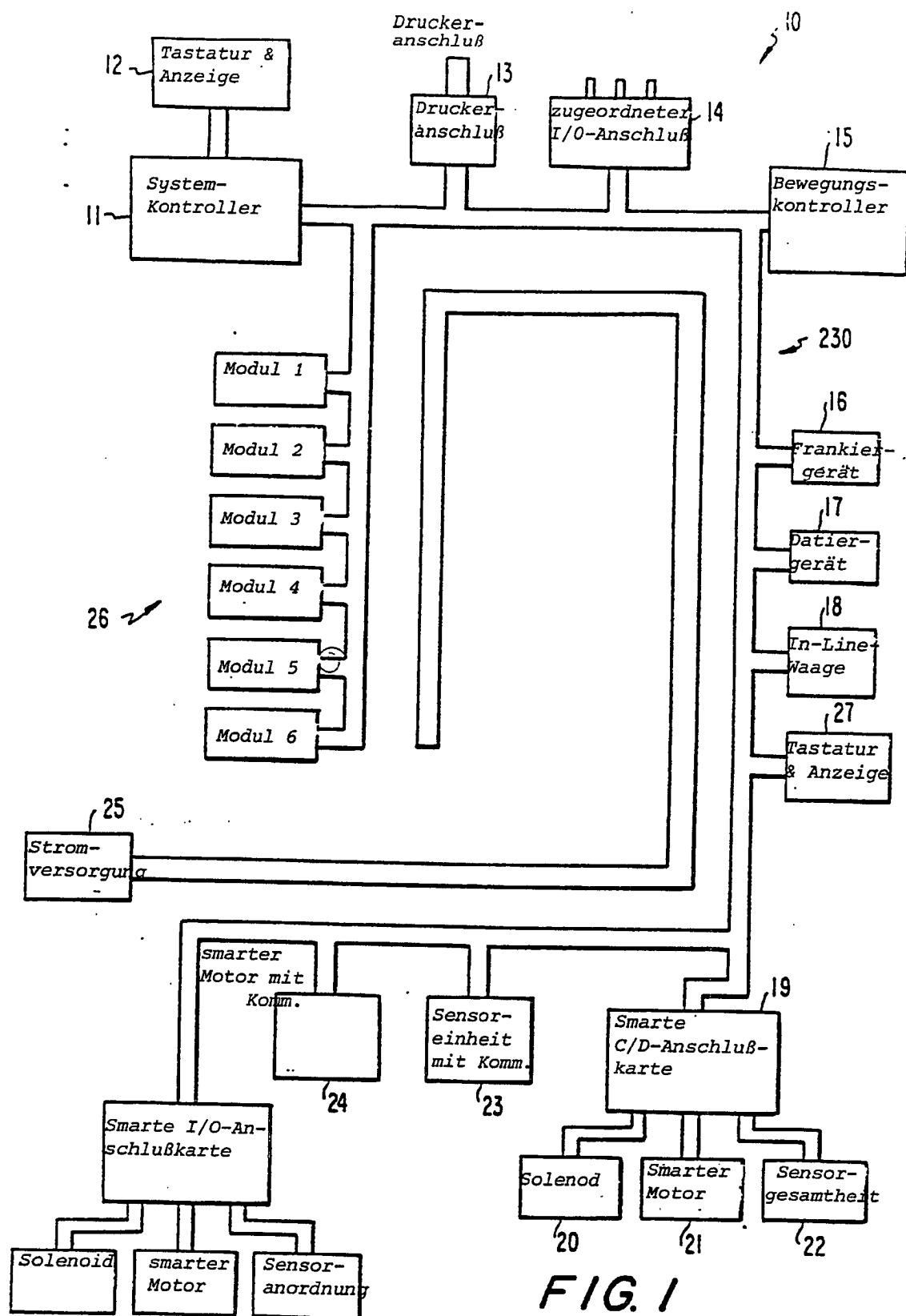

[0017] [Fig. 1](#) ein Blockschaltbild der Elemente eines Systems, die gemäß einer bevorzugten Ausführungsform der Architektur der vorliegenden Erfindung verbunden sind;

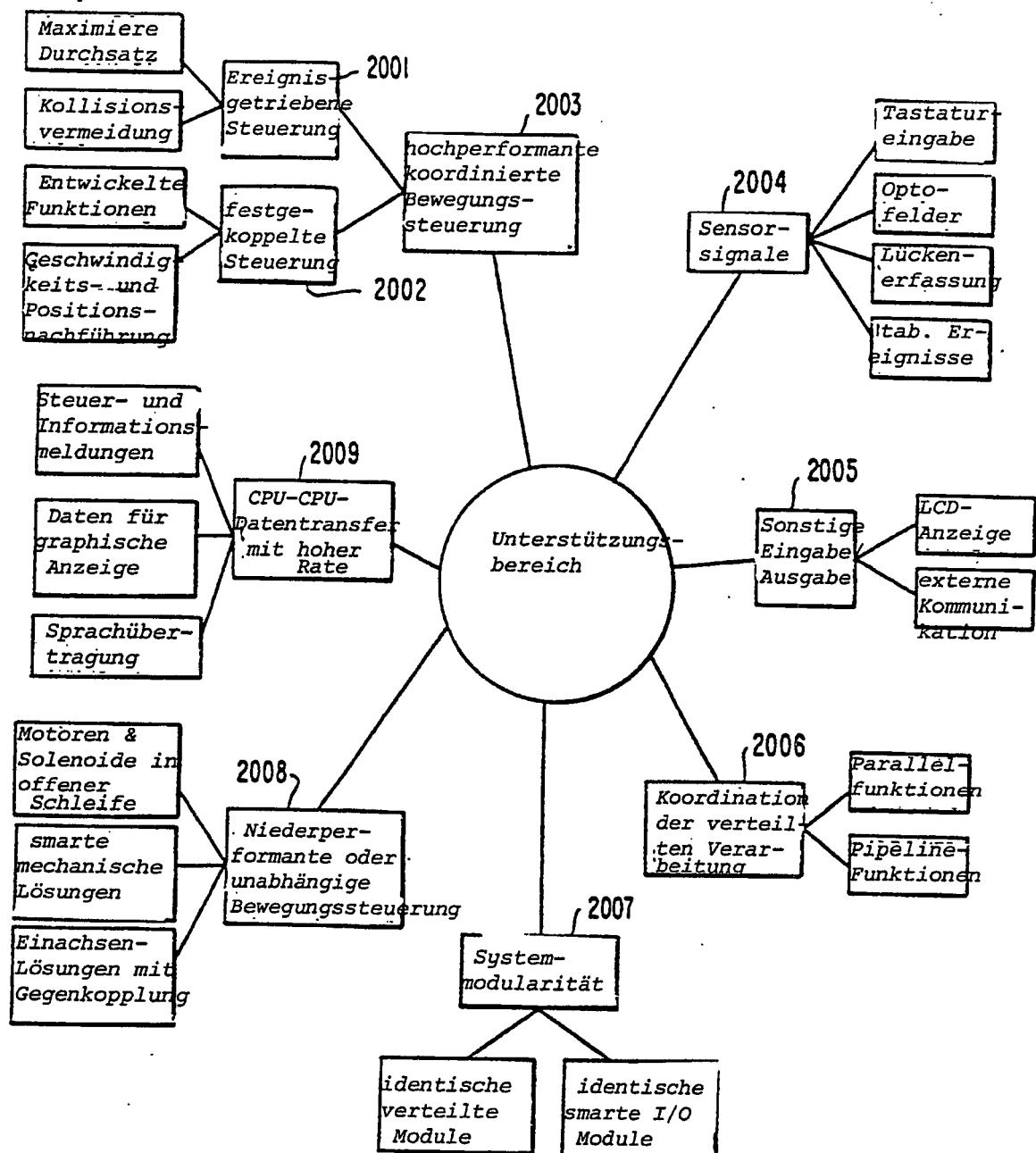

[0018] [Fig. 2](#) ein schematisches Diagramm zum Darstellen der Unterstützungsgebiete der Architektur gemäß der Erfindung;

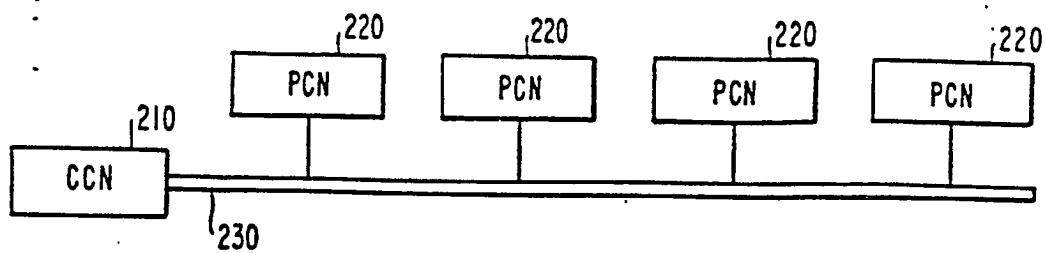

[0019] [Fig. 3](#) ein Blockschaltbild einer zentral gesteuerten Konfiguration gemäß der Erfindung;

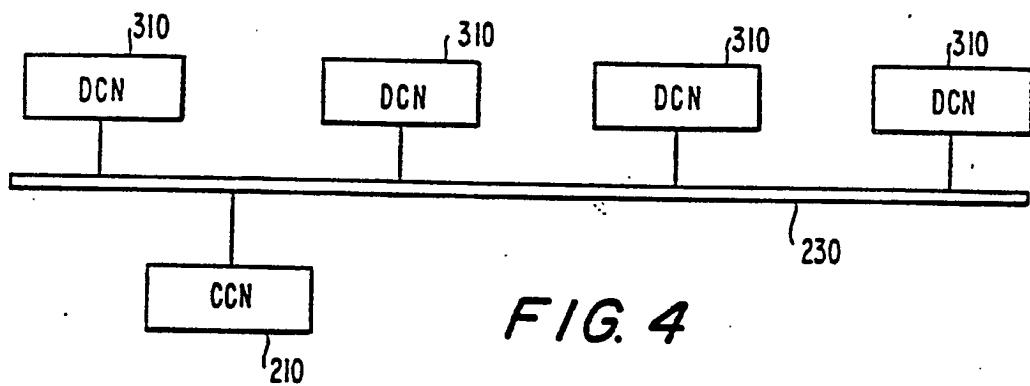

[0020] [Fig. 4](#) ein Blockschaltbild der verteilten Steuerkonfigurationen gemäß der Erfindung;

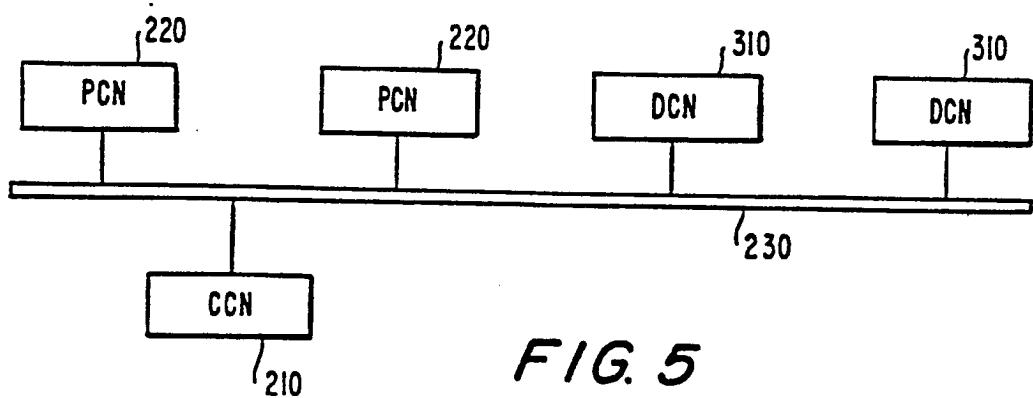

[0021] [Fig. 5](#) ein Blockschaltbild der kombinierten Steuerkonfiguration gemäß der Erfindung;

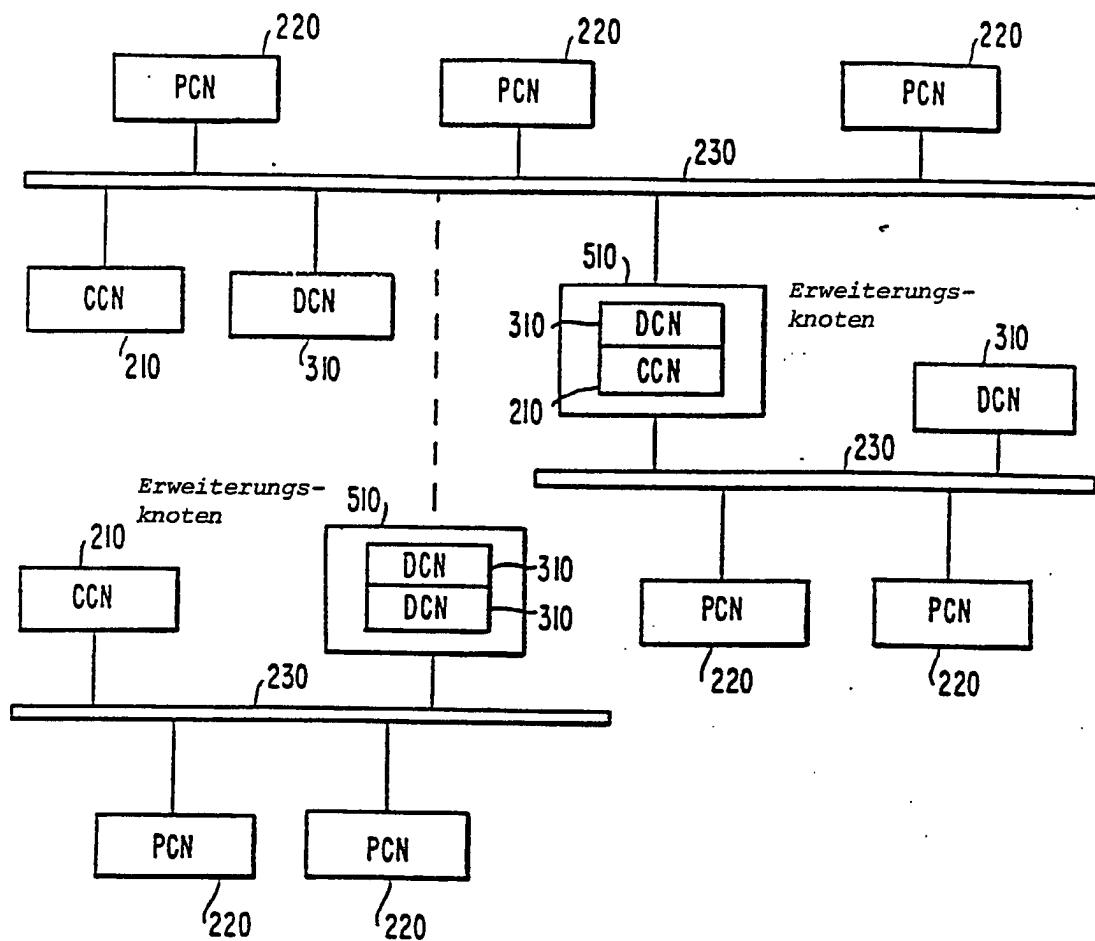

[0022] [Fig. 6](#) ein Blockschaltbild einer erweiterten Konfiguration gemäß der Erfindung;

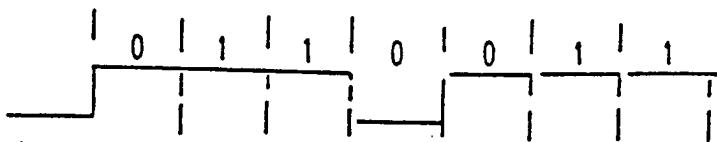

[0023] [Fig. 7](#) ein Diagramm eines Beispiels einer bevorzugten Ausführungsform für ein bei der vorliegenden Erfindung benütztes Codierschema;

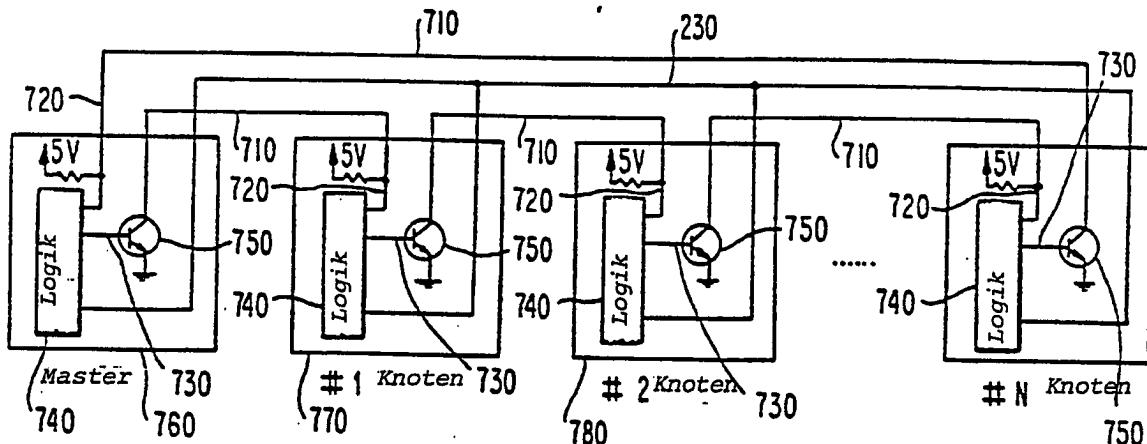

[0024] [Fig. 8](#) ein schematisches Blockschaltbild zum Darstellen dritter Leitungsverbindungen gemäß der Erfindung;

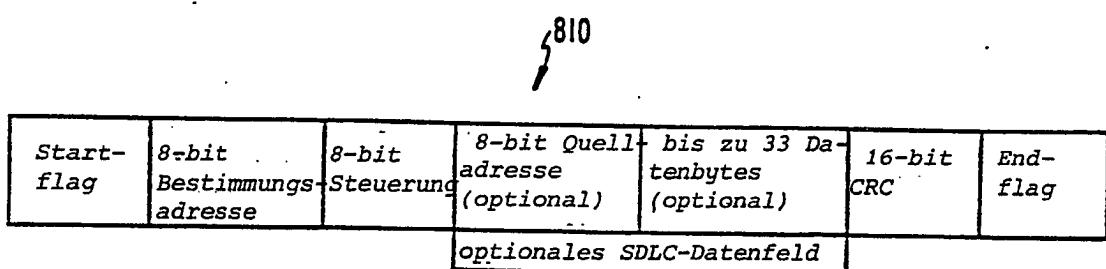

[0025] [Fig. 9](#) ein Diagramm eines gewählten Synchron-Datenübertragungssteuerungs-(SDLC, Synchronous Data Link Control)-Rahmens gemäß der Erfindung;

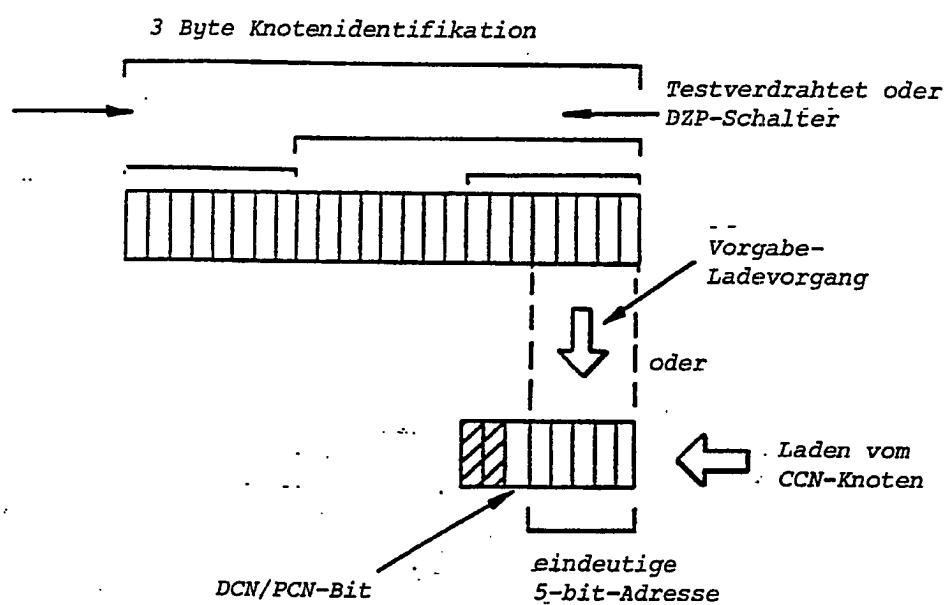

[0026] [Fig. 10](#) ein Diagramm gemäß einer Knotenidentifikation (ID, Node Identification) und einer Knotenadresse gemäß der Erfindung;

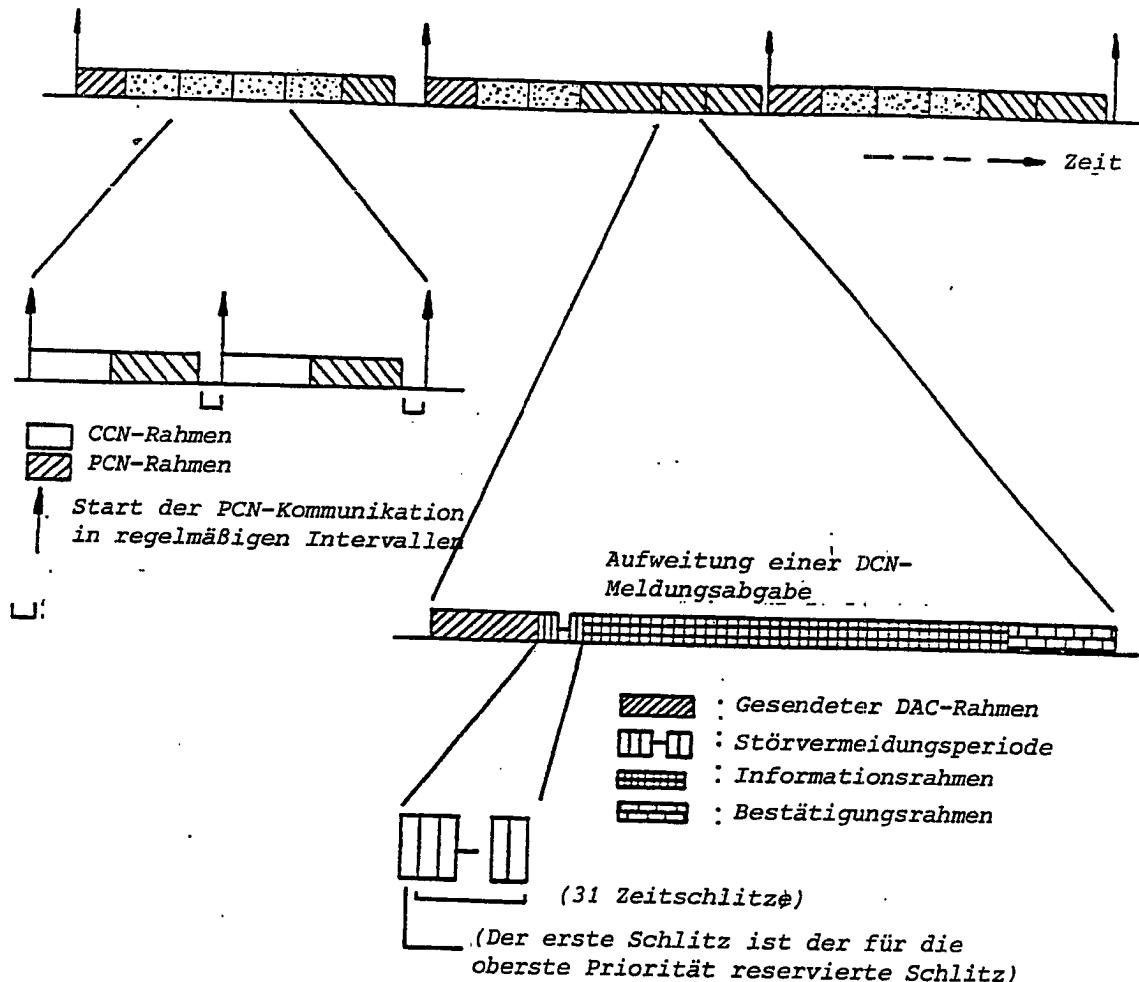

[0027] [Fig. 11](#) zum Darstellen der Zugriffsteuerungen gemäß der Erfindung;

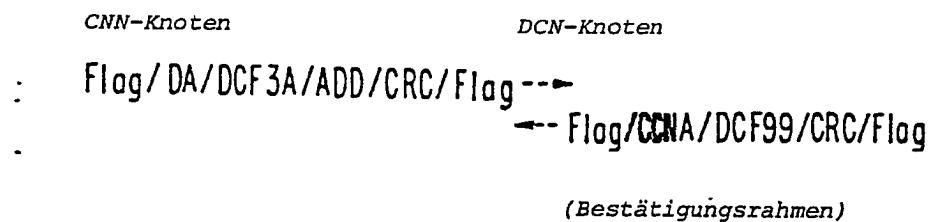

[0028] [Fig. 12](#) ein Diagramm zum Darstellen der Zugriffsteuerung für einen verteilten Steuerknoten (DCN, distributed control node) bei Betrieb gemäß der Erfindung;

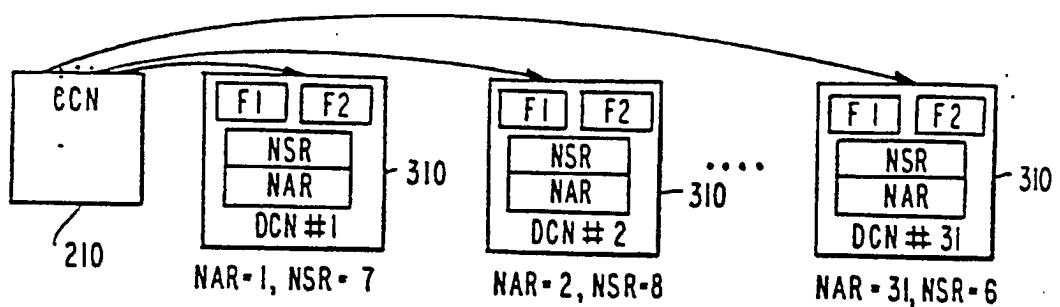

[0029] [Fig. 13](#) ein Diagramm zum Darstellen der DCN-Zugriffsssteuerung während des Normalbetriebs gemäß der Erfindung;

[0030] [Fig. 14](#) ein Diagramm zum Darstellen, wie gemäß der Erfindung ein DCN-Knoten einen Schnittzeitpunkt berechnet, um eine Störung zu vermeiden;

[0031] [Fig. 15](#) ein Diagramm zum weiteren Darstellen, wie gemäß der Erfindung ein DCN-Knoten einen Konkurrenzbetrieb vermeidet;

[0032] [Fig. 16](#) ein Diagramm zum Darstellen einer zyklischen Blockprüfung (cyclical redundancy check; CRC) gemäß der Erfindung für 16 Bit;

[0033] [Fig. 17](#) ein Diagramm zum Darstellen eines Steuerrahmens eines zentralisierten Steuerknotens (centralized control note) CCN gemäß der Erfindung;

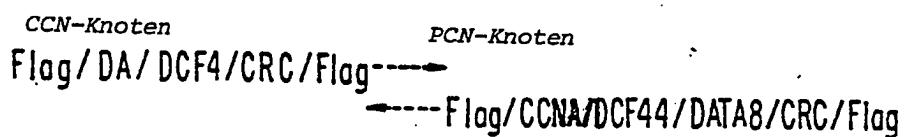

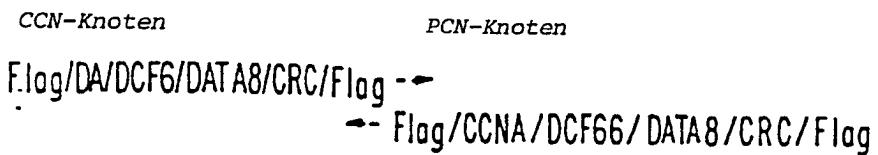

[0034] [Fig. 18](#) ein Diagramm eines Datenrahmens für die Übertragung zwischen dem CCN-Knoten zu einem PCN-Knoten (peripheral control node) oder umgekehrt gemäß der Erfindung;

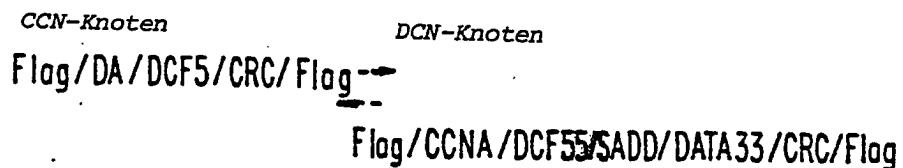

[0035] [Fig. 19](#) ein Diagramm eines Datenrahmens für die Übertragung von einem DCN-(CCN)-Knoten zu einem DCN-Knoten gemäß der Erfindung;

[0036] [Fig. 20](#) ein Diagramm eines Netzwerkaustauschrahmens zum Festlegen der Baudate gemäß der Erfindung;

[0037] [Fig. 21A](#) und [Fig. 21B](#) Diagramme der CNN-Austauschrahmen gemäß der Erfindung;

[0038] [Fig. 22](#) ein Diagramm eines Netzwerkkonfigurations-Austauschrahmens gemäß der Erfindung;

[0039] [Fig. 23A](#) und [Fig. 23B](#) Diagramme für eine Statusabfrage durch den CNN-Knoten gemäß der Erfindung;

[0040] [Fig. 24A](#) und [Fig. 24B](#) Diagramme für Schreibvorgänge zu einem Steuer/Konfigurationsregister gemäß der Erfindung;

[0041] [Fig. 25](#) ein Diagramm eines Austauschrahmens für die Zugriffsprioritätszuordnung/Lösung in einem DCN-Knoten gemäß der Erfindung;

[0042] [Fig. 26](#) einen Synchronisationssenderahmen (SYNC) gemäß der Erfindung;

[0043] [Fig. 27](#) ein Diagramm eines Boundary-Scan-Austauschrahmens gemäß der Erfindung;

[0044] [Fig. 28](#) ein Diagramm eines Eintaktrahmens zum Verbreiten von Boundary-Scan-Daten gemäß der Erfindung;

[0045] [Fig. 29A](#) und [Fig. 29B](#) Diagramme zum Abfragen von DCN-Knoten im Hinblick auf ein Boundary-Logikergebnis gemäß der Erfindung;

[0046] [Fig. 30](#) ein Diagramm für einen Datenaustauschrahmen zwischen dem DCN-Knoten und einem PCN-Knoten gemäß der Erfindung;

[0047] [Fig. 31](#) ein Diagramm mit einem Datenaustauschrahmen für die Übertragung von dem DCN-Knoten zu einem DCN-Knoten gemäß der Erfindung;

[0048] [Fig. 32](#) ein Diagramm eines Datenrahmens für die Übertragung von einem DCN-Knoten zu einem anderen DCN-Knoten gemäß der Erfindung;

[0049] [Fig. 33](#) ein Diagramm zum Darstellen von Netzwerk-Zustandsübergängen gemäß der Erfindung;

[0050] [Fig. 34](#) ein Diagramm der DCN-zu-DCN-Übergangs-Zustandsmaschine gemäß der Erfindung;

[0051] [Fig. 35](#) ein Diagramm eines Funktionsstatusbytes gemäß der Erfindung;

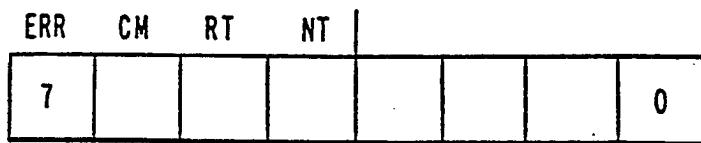

[0052] [Fig. 36](#) ein Diagramm eines Datenstatusbytes gemäß der Erfindung;

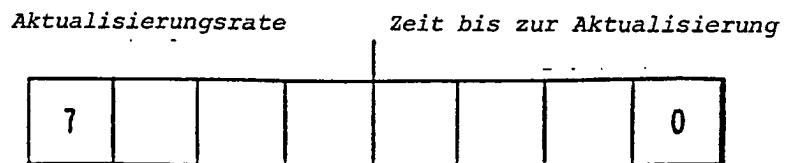

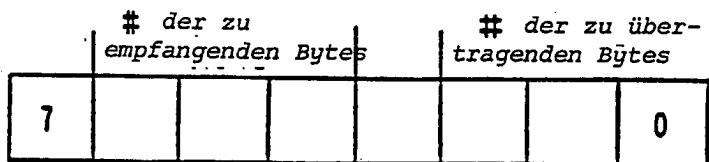

[0053] [Fig. 37](#) ein Diagramm gemäß einer Mitteilungslänge gemäß der Erfindung; und

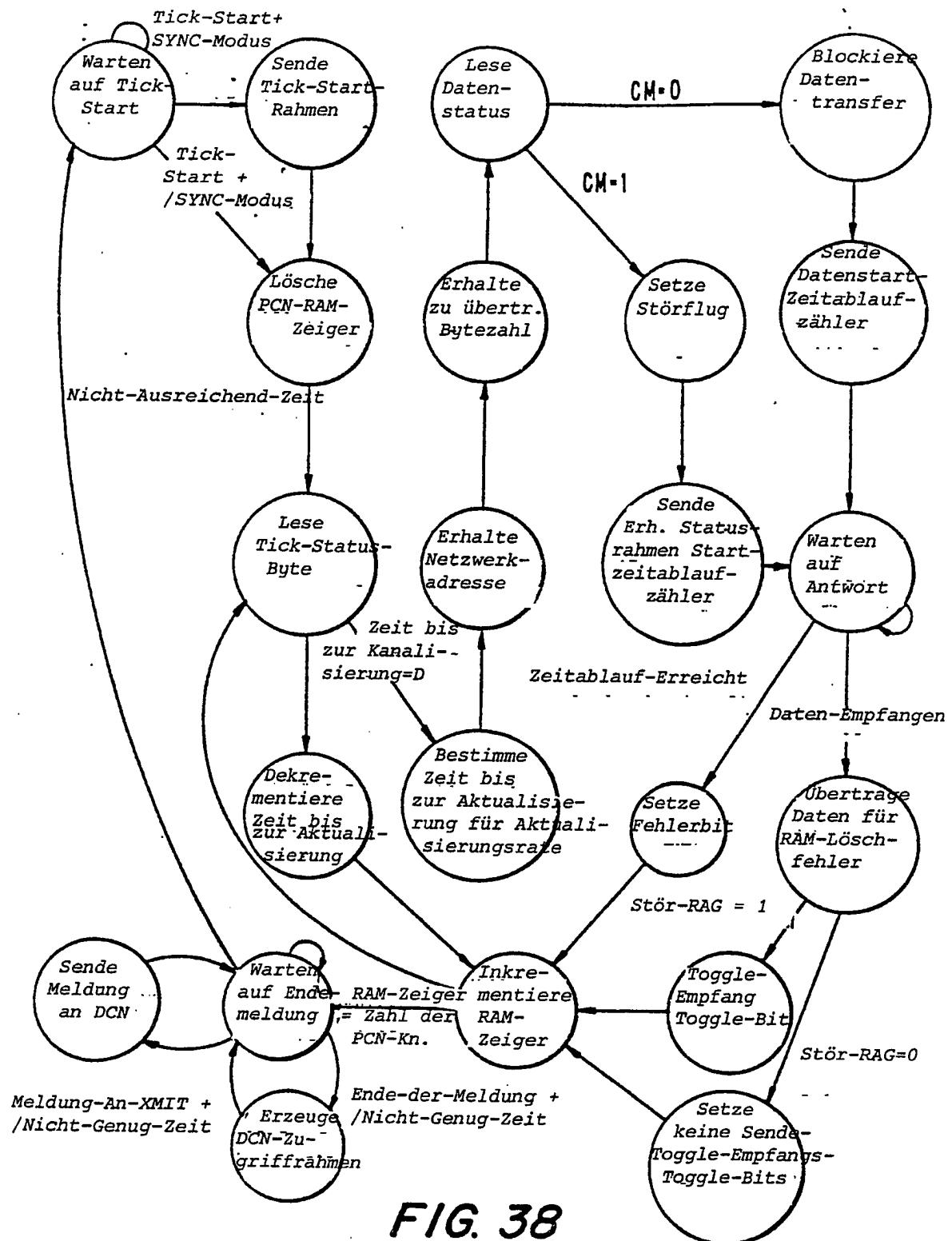

[0054] [Fig. 38](#) ein Diagramm einer Zugriffszustandsmaschine gemäß der Erfindung.

## Detaillierte Beschreibung der Erfindung

**[0055]** In dem Bewegungssteuerungsumfeld ist es nicht nur wichtig, eine Echtzeit-Bewegungssteuerung zu unterstützen, sondern auch eine Kommunikation zwischen anderen Elementen des Systems zu unterstützen. Diese Elemente können Eigenschaften aufweisen, die zu einem unterschiedlichen Satz von Kommunikationsanforderungen führen, die sich von denjenigen der im Zusammenhang mit der Bewegung vorgesehenen Elementen unterscheidet. Beispielsweise können Systemkonfigurationsparameter periodisch durch einen Betreiber eingegeben werden. Diese Information wird den Komponenten des Systems asynchron zugeführt. Ferner kann für die intelligenten Systemkomponenten auch zusätzlich die Durchführung asynchroner Kommunikationsvorgänge von einem gleichrangigen Element zu einem anderen gleichrangigen Element erforderlich sein. Im Gegensatz zu diesem ereignisgetriebenen Modus der Kommunikation sind hochleistungsfähige festgekoppelte Bewegungssteuerelemente üblicherweise in Echtzeit über einen Kanal mit hoher Bandbreite zu treiben.

**[0056]** Die vorliegende Erfindung schafft eine Kommunikationsarchitektur, die hinreichend flexibel ist, um sowohl eine synchrone als auch eine asynchrone Kommunikation in Bewegungssteuerungssystemen zu ermöglichen. Die Architektur setzt weiterhin einen seriellen Bus ein, der eine Reduzierung des Verdrahtungsaufwands für die Verbindung des Systems ermöglicht, insbesondere wenn das physikalische Layout eine lineare Anordnung der Komponenten aufweist. Der Aufbau im seriellen Bus ist auch leichter abzuschirmen als andere Aufbauten und ermöglicht eine Zunahme der Zahl der gemeinsamen Teile in dem System, was zu einer Reduktion der Kosten pro Einheit und demnach der gesamten Systemkosten führt. Durch die Architektur der vorliegenden Erfindung wird eine Vielzahl von Motorsteuersystem-Aufbauten unterstützt, was bei den diese Architektur einsetzenden Systemen eine einfache Modifikation und Erweiterung und eine einfache Entwicklung neuer Systeme ermöglicht.

**[0057]** In [Fig. 1](#) ist ein schematisches Schaltbild einer Systemimplementierung der Motorsteuer-Kommunikationsarchitektur **10** der vorliegenden Erfindung gezeigt. Das speziell gezeigte System ist ein Postversandsystem, das einen System-Controller **11** und eine Tastatur und eine Anzeige **12** für die Schnittstelle zu dem Betreiber aufweist. Das System enthält auch einen Bewegungs-Controller **15** zum Treiben von Solenoiden **20**, zum Treiben von smarten Motoren **21** und zum Empfangen von Daten von der Sensorgesamtheit **22**, jeweils über den seriellen Bus **230** und die smarte I/O-Anschlußkarte **19**. Gelegentlich ist es im Hinblick auf Plazierungsaspekte wirtschaftlich, anstelle des Aufbaus mit der Anschlußkarte **19** eine Sensorgesamtheit **23** mit eingebauter Kommunikationsschaltung und einem smarten Motor **24** mit eingebauter Kommunikationsschaltung einzusetzen. Der System-Controller **11** und der Bewegungs-Controller **15** kommunizieren asynchron über den Bus **230**. Weitere Module wie ein Meßgerät **16**, ein Datiergerät **17**, eine In-line-Waage **18**, ein Druckeranschluß **13** und ein zugeordnetes I/O-Element **14** kommunizieren über den Bus **230**. In dem System können auch Optionalmodule **26** vorgesehen sein, damit beispielsweise ein Modem für die externe Kommunikation bereitgestellt wird, oder ein Floppy-Laufwerk. Die Komponenten des Versandsystems werden durch die Stromversorgung **25** versorgt, die wie gezeigt, mit allen Knoten verbunden ist.

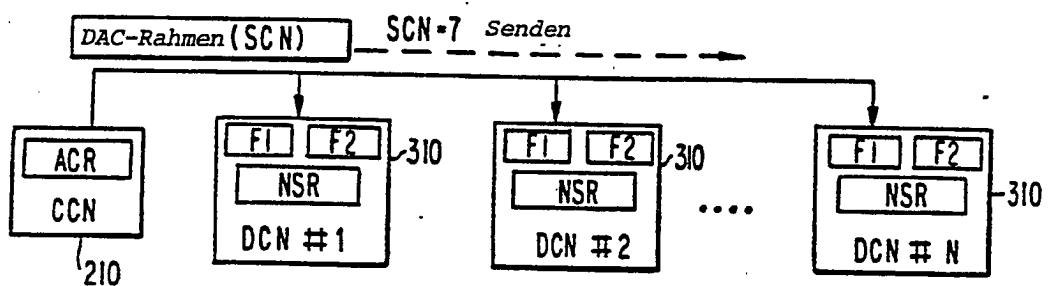

**[0058]** Die Bewegungssteuerungsarchitektur **10** unterstützt drei Arten von Komponenten oder Knoten. Wie in den [Fig. 1 – Fig. 6](#) gezeigt ist, bestehen die unterstützten Knotentypen aus einem zentralisierten Steuerknoten (CNN-Knoten) **210**, einem verteilten Steuerknoten **310** und peripheren Steuerknoten **220**, die wie gezeigt, konfiguriert werden können.

**[0059]** Die unterschiedlichen Knotentypen sind sowohl durch den Umfang ihrer elektronischen Leistungsfähigkeit als auch durch ihre Rolle in der gesamten Systemarchitektur gekennzeichnet. Ein zentralisierter Steuerknoten **210** weist ein signifikantes lokales Verarbeitungsvermögen auf, und zwar in der Form einer Zentralverarbeitungseinheit (CPU). Dieser Knoten vermittelt Kommunikationsvorgänge zwischen den weniger leistungsstarken verteilten Steuerknoten **310**, die typischerweise ebenfalls CPU-basiert sind. Der zentralisierte Steuerknoten **210** ist auch der Knoten, der direkt periphere Steuerknoten **220** treiben kann, die die am wenigsten leistungsfähigen Arten von Steuerknoten darstellen.

**[0060]** Die verteilten Steuerknoten **310** sind Knoten, die typischerweise einen lokalen Prozessor enthalten. Jedoch können die verteilten Steuerknoten **310** nicht Knoten-zu-Knoten-Kommunikationsvorgänge wie der zentralisierte Steuerknoten **210** vermitteln.

**[0061]** Der am wenigsten entwickelte Steuerknoten ist der periphere Steuerknoten **220**. Periphere Steuerknoten **220** enthalten elektronische Schaltungen vom mittleren Niveau zum Bilden einer Schnittstelle mit Hardware-Komponenten, beispielsweise Motoren, jedoch sind sie nicht CPU-basiert. Periphere Steuerknoten können durch den zentralisierten Steuerknoten **210** getrieben werden, können jedoch nicht das Netzwerk steuern

oder Kommunikationsvorgänge initiieren

**[0062]** Die zahlreichen in [Fig. 1](#) gezeigten Systemkomponenten können durch ihre Art des Knotentyps gekennzeichnet werden. Der Bewegungs-Controller **15** nimmt typischerweise die Rolle eines zentralisierten Steuerknotens **200** ein, während der Aufbau der Anschlußkarte **19** mit dem Solenoid **20**, dem smarten Motor **21** und der Sensorgesamtheit **22** einen der peripheren Steuerknoten **220** bildet. Die Sensorgesamtheit **23** mit eingebauter Kommunikationsschaltung und der smarte Motor **24** mit eingebauter Kommunikationsschaltung stellten ebenfalls periphere Randknoten **220** dar, genauso wie die Tastatur und die Anzeige **27**. Die verbleibenden in [Fig. 1](#) gezeigten Module, beispielsweise das Frankiergerät **16** und das Datiergerät **17**, sind typischerweise verteilte Steuerknoten **310**, obgleich alternative Anordnungen möglich sind. Beispielsweise könnte der System-Controller **11** der CCN-Knoten **210** sein, aber der Druckeranschluß **13** könnte als einer der PCN-Knoten **220** anstelle des DCN-Knotens **310** konfiguriert sein. Es ist möglich, einen zugeordneten I/O-Anschluß **14** einzusetzen, der einer der PCN-Knoten **220** ist, und zwar als kostengünstige Vorrichtung zum Bereitstellen einer Schnittstelle zwischen dem zentralisierten Steuerknoten **210** und einer Zentralverarbeitungseinheit (CPU) über den seriellen Bus **230**.

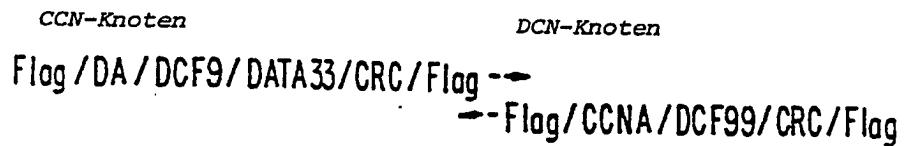

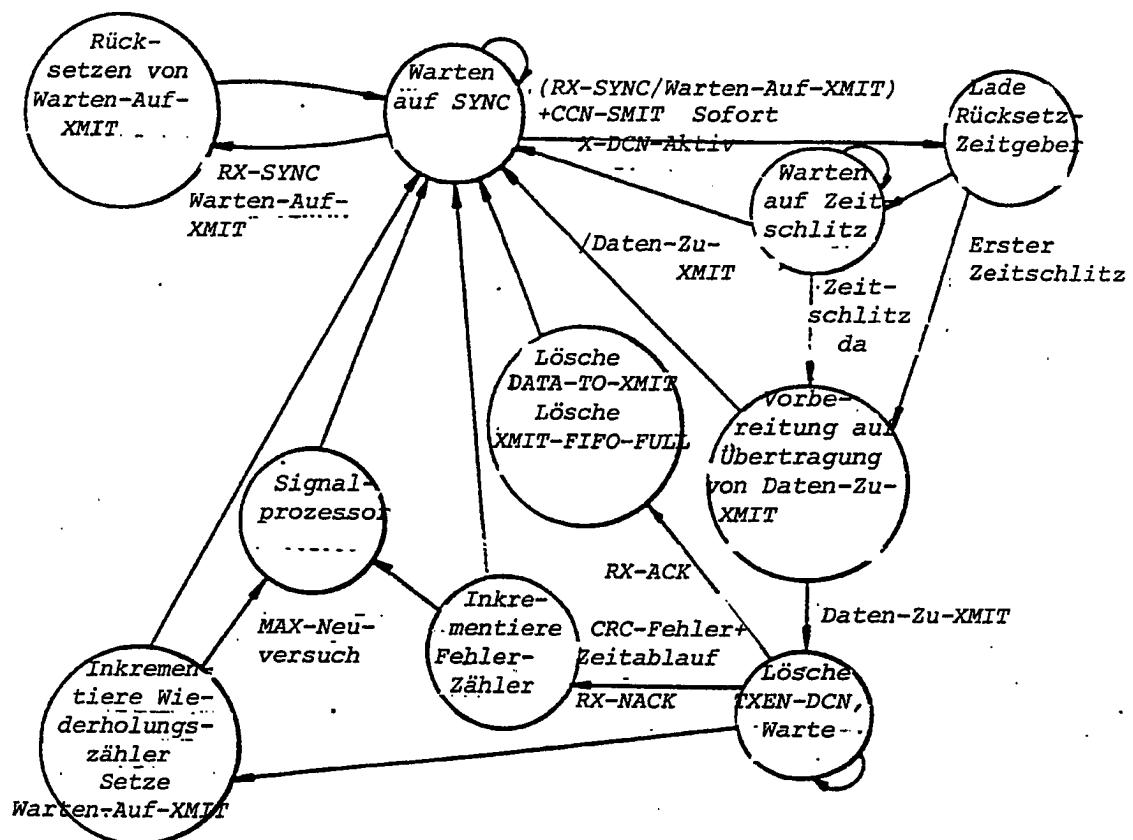

**[0063]** Wie in [Fig. 2](#) gezeigt ist, die den Unterstützungsbereich der Architektur **10** auf einem allgemeineren Niveau als in [Fig. 1](#) gezeigt darstellt, kann die Funktion der ereignisgetriebenen Steuerung **2001** durch Einsatz entweder eines PCN-Knotens **220** oder eines DCN-Knotens **310** erreicht werden, während die Funktion der festgekoppelten Steuerung **2002** typischerweise durch Einsatz eines der PCN-Knoten **220** erzielt wird. Die Funktion der Sensoreingabe **2004** wird üblicherweise durch Einsatz von PCN-Knoten **220** erreicht, obgleich bei einigen Funktionen DCN-Knoten **310** eingesetzt werden können. Sonstige Eingabe/Ausgabefunktionen **2005** werden allgemein durch Einsatz von DCN-Knoten **310** oder von PCN-Knoten **220** erzielt. Die Systemmodularität **2007** lässt sich durch Einsatz sowohl von PCN-Knoten **220** als auch von DCN-Knoten **310** erzielen. Die allgemeine Funktion der hochperformanten koordinierten Bewegungssteuerung **2003** wird typischerweise durch Einsatz eines der PCN-Knoten **220** erreicht. Die durch die geringere Performanz gekennzeichneten Funktionen oder die unabhängige Bewegungssteuerung **2004** kann durch die PCN-Knoten **220** oder die DCN-Knoten **310** erzielt werden, während CPU-zu-CPU-Datenübertragungen mit hoher Rate **2009** vorzugsweise durch Einsatz von DCN-Knoten **310** erzielt werden.

**[0064]** In allen Betriebsmoden führt der CCN-Knoten **210** die Netzwerksteuerfunktion durch. In einem Betriebsmodus, der zentralisierten Steuerung, steuert ein CPU-basierter Netzwerkmaster-DCN-Knoten **210** mehrere PCN-Knoten **220**, die nicht CPU-basiert sind, sondern im Gegensatz eine smarte Eingabe/Ausgabe-(I/O)-Logik-Verarbeitungshardware und eine serielle Kommunikationslogik enthalten. Typische I/O-Verarbeitungsfunktionen sind Pulsbreitenmodulation, Quadraturdekodierung, Sensorabtastung, usw.. Die PCN-Knoten **220** bilden eine Schnittstelle auf mittlerem Niveau zu den Bewegungssteuerelementen, beispielsweise den Motoren, den Solenoiden und den Sensoren in dem System.

**[0065]** Bei der verteilten Steuerung können die CPU-basierten DCN-Knoten **310** Zuordnungsaufgaben unabhängig von dem CCN-Knoten **210** durchführen, während der CCN-Knoten **210** eine Kommunikation zwischen DCN-Knoten **310** ermöglicht.

**[0066]** Ein hybrides System mit sowohl DCN-Knoten **310** und PCN-Knoten **220** wird ebenfalls unterstützt, beispielsweise in einer Anordnung, die eine Systemerweiterung über eine Verzweigung ermöglicht.

**[0067]** Wie schematisch in [Fig. 3](#) gezeigt ist, wird ein hochwertiges Bewegungssteuerungs-Umfeld mit vielen PCN-Knoten **220** (smarter I/O-Servomotor und smarte Sensorknoten) unter zentralisierter Steuerung unterstützt. Der DCN-Knoten **210** sendet Bewegungssteuerdaten an Servomotoren und Solenoide und empfängt jeweils einen Sensorstatus und Motorcodier-Wellenpositionsdaten von den Motoren und den Sensoren. Die Kommunikation dieser Daten enthält eine Fehlerdetektorlogik. Da die Steuer/Statusdaten zu/von diesen Knoten mit hohen Raten regeneriert werden, ist eine erneute Datenübertragung bei Erfassung von Fehlern nicht erforderlich. Bis zu 31 der PCN-Knoten **220** können an dem seriellen Mehrfachabzweig-Kommunikationsbus **230** angeschlossen sein. Jeder der PCN-Knoten **220** ist vollständig mit Hardwarelogik ohne eine CPU implementiert. Die PCN-Knoten **220** empfangen Meldungen lediglich von dem CCN-Knoten **210**. Der PCN-Knoten **220** dekodiert die Meldung, führt die Zuordnungsfunktionen der Meldung durch, gewinnt eine Rückmeldung und überträgt sie zu dem CCN-Knoten **210**. Allgemein dienen die Befehle des CCN-Knotens **210** der Steuerung der Ausgangsleitungen der PCN-Knoten **220**, wohingehend die Antworten der PCN-Knoten **220** zum Anzeigen des Status der Eingabeleitungen der PCN-Knoten **220** dienen. Die Anwendungshardwarelogik der PCN-Knoten **220** ermöglicht eine intelligente Verarbeitung der Ausgabebefehle des DCN-Knotens **210** und der ungefähren Eingabedaten der PCN-Knoten **220**, damit der CCN-Knoten **210** nicht die I/O-Verarbeitung auf

niedrigem Niveau durchführen muß. Zum Vereinfachen der Kommunikation mit den PCN-Knoten **220** ist es erforderlich, daß unmittelbar nach dem Senden einer Meldung durch den CCN-Knoten **210** an die PCN-Knoten **220** dieser eine unmittelbare Antwortmeldung anfordert. Diese Antwortmeldung wird durch den CCN-Knoten **210** auch als implizite Bestätigung kleiner Meldung benutzt. Eine Kommunikation von einem PCN-Knoten **220** zu einem PCN-Knoten **220** wird nicht zugelassen.

**[0068]** Der Modus mit verteilter Steuerung unterstützt die Kommunikation zwischen intelligenten Knoten in dem System. In diesem Modus erfolgt die Steuerung und die Übertragung von Daten zum Unterstützen der folgenden Vorgänge: Prozessor-zu-Prozessor-Kommunikation, Motorbefehle, Motor/Sensor-Status, initialisierte Befehle, Diagnosemitteilungen und Fehlerstatus. Diese steuerungsorientierte Datenübertragung basiert vollständig auf einer Fehlerdetektion, einer erneuten Übertragung und einem duplizierten Meldungsschutz sowohl auf dem Niveau der Datenpakete als auch der Meldungen mit mehreren Paketen.

**[0069]** Der Aufbau des Netzwerks unter Einsatz lediglich der DCN-Knoten **310** ist in [Fig. 4](#) gezeigt. Bis zu 31 DCN-Knoten **310** können an dem Bus angeschlossen sein. Jeder DCN-Knoten **310** kann mit jedem anderen der DCN-Knoten **310** kommunizieren, einschließlich dem DCN-Knoten **210**, auf einem Niveau einer Kommunikation zwischen gleichrangigen Elementen. Demnach kann ein DCN-Knoten **310** eine logische Datenverbindung zu einem anderen DCN-Knoten **310** herstellen. Die Rolle des Netzwerkmaster-DCN-Knoten **210** in diesem Aufbau besteht in der Bereitstellung von Netzwerkdiensten, beispielsweise dem Sammeln und Verteilen von Information für die Zugriffssteuerung zu dem Bus **320** bei Stromversorgung, Überwachung des Netzwerks und Durchführen der Netzwerkdagnostik. Der DCN-Knoten **210** kann auch die Funktion eines der DCN-Knoten **310** durchführen.

**[0070]** Es ist auch möglich, sowohl PCN-Knoten **220** als auch DCN-Knoten **310** in einem einzigen Netzwerk zu kombinieren, wie in [Fig. 5](#) gezeigt ist. Bis zu 31 gemischte Knoten lassen sich an dem Bus **330** anschließen. Der DCN-Knoten **210** steuert das Zugriffsrecht eines Knoten auf den Bus **230** in fester Weise. Der DCN-Knoten **210** ordnet einem der PCN-Knoten **220** Priorität gegenüber den DCN-Knoten **310** zu, da die PCN-Knoten **220** allgemein eine synchronisierte Kommunikation mit hohen Regenerierdaten erfordern, wohingehend der kritische Punkt für die Kommunikation des DCN-Knotens **310** in der Meldungswartezeit und dem publizierten Meldungsschutz besteht. Nachdem alle Kommunikationsanforderungen für die PCN-Knoten **220** erfüllt sind, berechnet der DCN-Knoten **210** den Umfang der für einen DCN-Knoten **310** zu einem anderen DCN-Knoten **310** zur Verfügung stehenden Zeit, und er kann den Befehl abgeben, der es einem der DCN-Knoten **310** ermöglicht, die Übertragung zu initiieren. Es wird davon ausgegangen, daß die Bandbreite des Kommunikationskanals groß genug ist, um PCN-Knoten **220** und DCN-Knoten **310** handzuhaben. Bei diesem Aufbau wird nicht zugelassen, daß DCN-Knoten **310** direkt PCN-Knoten **220** ansprechen, und auch eine Kommunikation von einem PCN-Knoten **220** zu einem anderen PCN-Knoten **220** wird nicht zugelassen. Ist das Ansprechen von PCN-Knoten **220** durch einen der DCN-Knoten **310** erforderlich, so überträgt der DCN-Knoten **210** die Meldungen.

**[0071]** Zusätzlich kann das System, wie in [Fig. 6](#) gezeigt ist, erweitert werden. Ein Erweiterungsknoten **510** ist so aufgebaut, daß er sowohl die Funktionen des DCN-Knotens **310** als auch des DCN-Knotens **210** durchführt. Der Erweiterungsknoten **510** kann an einem Netzwerk in derselben Weise angeschlossen sein, wie es für einen der DCN-Knoten **310** der Fall wäre, der PCN-Knoten **220** in einem Unternetzwerk steuert, genauso wie jetzt für den CCN-Knoten **210** der Fall wäre.

**[0072]** Bevorzugte Spezifikationen für Systeme, die die Bewegungssteuerungs-Kommunikationsarchitektur **10** einsetzen, sind in der Tabelle 1 zusammengestellt.

## TABELLE 1

|                                                 |                                                                                                                               |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PHYSIKALISCHE SCHICHT:                          | verdrilltes Drahtpaar RS485 (kann ein Abschirmen erfordern)                                                                   |

| DISTANZ:                                        | maximal 75 Fuß                                                                                                                |

| MAXIMALZAHL DER KNOTEN:                         | 32 (1 CCN-Knoten mit irgendeiner Kommunikation der DCN-Knoten und der PCN-Knoten)                                             |

| DATENRATE:                                      | bei der Netzwerkinitialisierung wählbar (10 Mbps, 5 Mbps, 2,5 Mbps, 1,25 Mbps, 675 Kbps)                                      |

| RAHMENTECHNIK:                                  | SDLC (International Business Machines, Inc., Synchronous Data Link Control, Allgemeine Information, IBM Formblatt, GA27-3093) |

| UNTERSTÜTZTE KOMMUNIKATION                      |                                                                                                                               |

| VERTEILT:                                       | CPU-zu-CPU                                                                                                                    |

| ZENTRALISIERT:                                  | Master/Slave von Zentrale CPU zu smarten I/O-Knoten                                                                           |

| ZUGRIFFSSTEUERUNG:                              |                                                                                                                               |

| VERTEILT:                                       | Zeitschlitzzugriff zwischen CPU-Knoten                                                                                        |

| ZENTRALISIERT:                                  | zeitsynchron auf Grundlage eines Ansprechens                                                                                  |

| FEHLERERFASSUNG:                                | SCLC-16-bit-CRC mit unmittelbaren Bestätigen                                                                                  |

| FEHLERBEHEBUNG:                                 |                                                                                                                               |

| VERTEILT:                                       | Bestätigung mit erneutem Versuch und Duplizierungsschutz                                                                      |

| ZENTRALISIERT:                                  | hohe Regenerierrate für smarte I/O-Knoten                                                                                     |

| DATENLÄNGE                                      |                                                                                                                               |

| VERTEILT:                                       | bis zu 33 Bytes Daten, die einem Anwender zugeordnet sind                                                                     |

| ZENTRALISIERT:                                  | bis zu 8 Bytes Daten                                                                                                          |

| LEISTUNG BEI 10 Mbps:                           |                                                                                                                               |

| VERTEILT:                                       | maximale Wartezeit für Meldung < 5 ms unter der Annahme, daß zumindest 30% der Bandbreite den DCN-Knoten zugeordnet ist       |

| ZENTRALISIERT:                                  | Wiederholungen mit durchschnittlich 1 ms bei bis zu 31 PCN-Knoten                                                             |

| UNTERSTÜZUNGSANFORDERUNGEN AUF ANWENDUNGSNIVEAU |                                                                                                                               |

| AUTOMATISCHE SYSTEMKONFIGURATION                |                                                                                                                               |

| MODULARITÄT:                                    | Option zum Hinzufügen identischer Module mit geringer/keinen Anpassungen                                                      |

| HERSTELLUNGS/SERVICEDIAGNOSE                    |                                                                                                                               |

| PROGRAMMLADEFÄHIGKEIT                           |                                                                                                                               |

**[0073]** Bewegungssteuersysteme, die die Kommunikationsarchitektur **10** einsetzen, können viele Module enthalten, die als Hauptuntereinheiten identifiziert werden. Im Hinblick auf die Kommunikation kann ein Modul

jedoch als Kommunikationsknoten betrachtet werden. Sind Module durch Kabel verbunden, so kann es erforderlich sein, daß der Netzwerk-Controller (CCN-Knoten **210**) die physikalische Reihenfolge der Modulverbindungen bestimmt. Identische Module können in einem System in Serie verbunden sein. Demnach kann – wie im folgenden gezeigt – ein zusätzlicher Draht in dem Kommunikationskabel zum Erfüllen dieser Anforderung enthalten sein, zusätzlich zu den Kommunikationssignalleitungen.

**[0074]** In allen Systemkonfigurationen teilen die Knoten vorzugsweise einen bidirektionalen RS485-Mehr-fachanschlußbus **230**, obgleich andere Hardwareimplementierungen auch einsetzbar sind, beispielsweise optische Glasfaserkabel, IEEE-802.3 10-Basis-T-Busse oder Busse mit offenem Kollektor. Der Bus **230** kann bis zu 35 Fuß von einem Ende bis zum anderen Ende lang sein und mit bis zu 10 Mbps betrieben werden. Größere Längen können bei entweder geringeren Geschwindigkeiten (< 10 Mbps) oder bei einer Ringtopologie mit anderen Kommunikationsmedien erzielt werden. Bis zu 32 Knoten - ein zwingend erforderlicher CCN-Knoten **210** und eine Kombination von bis zu 31 PCN-Knoten **220** und DCN-Knoten **210** – können mit einem Bus **230** verbunden sein.

**[0075]** Bei einer Kommunikation lediglich zwischen PCN-Knoten **220** ist die Bandbreitenkapazität des Systems groß genug, um die Abtastrate von 1000 Abtastungen pro Sekunde pro PCN-Knoten **220** für bis zu 31 PCN-Knoten **220** handzuhaben, um hochleistungsfähige Motoren zu unterstützen. Eine Abtastung entspricht einem Rahmen von dem CCN-Knoten **210** zu dem PCN-Knoten **220** und dem Antwortrahmen von dem PCN-Knoten **220** zu dem CCN-Knoten **210**. Jeder Rahmen weist 8 Byte Informationsdaten auf. In diesem Kontext enthält ein Rahmen sämtliche Rahmen-Overheads zum Bereitstellen von Informationsdaten. Das System ermöglicht einem Anwender die Abtastkapazität zwischen den PCN-Knoten **220** zuzuordnen, da einige PCN-Knoten **220** mehr als 1000 Abtastungen pro Sekunde erfordern können und andere PCN-Knoten **220** mit einer erheblich geringeren Abtastung betrieben werden können. Innerhalb einer festgelegten Kapazität sind zahlreiche Zuordnungen möglich, beispielsweise 2000 Abtastungen/sek für alle 16 Knoten oder 2000 Abtastungen/sek für 10 Knoten und 500 Abtastungen/sek für weitere 20 Knoten.

**[0076]** Es ist möglich, die Abtastrate für die zahlreichen PCN-Knoten **220** dynamisch anzulegen, um den Hochleistungsanforderungen einiger PCN-Knoten **220** während gewisser Abschnitte der Maschinenzyklen gerecht zu werden, und anderen PCN-Knoten das Erzielen einer höheren Performanz während anderer Perioden des Maschinenzyklus zu ermöglichen, ohne daß die gesamte Kommunikationsbandbreite der PCN-Knoten **220**, die durch das Netzwerk ermöglicht wird, überschritten wird.

**[0077]** Für eine Kommunikation mit lediglich den DCN-Knoten **310** sollte das System in der Lage sein, einen Datendurchsatz von 30000 Meldungen (mit einer Durchschnittslänge von 16 Byte) pro Sekunde zu unterstützen, damit die Aktualisierungsanforderungen für Graphikdaten unterstützt werden. Eine Meldung ohne Rahmen-Overheads kann zwischen 1 und 33 Bytes lang sein und sie kann von einem DCN-Knoten **310** zu irgendeinem anderen der DCN-Knoten **310** mit einer positiven Bestätigung abgegeben werden. Die Wartezeit eines Rahmens übersteigt nicht 5 ms. Meldungen, die länger als 33 Byte sind, werden durch einen stabilen Software-Kommunikationstreiber gehandhabt. (Bei der genauen Definition der synchronen Datenverbindungssteuerung (SDLC) ist das Quellenadressenfeld bei der Kommunikationsarchitektur **10** ein Teil des SDLC-Datenfelds. Ein Anwender kann eine Meldung von bis zu 33 Bytes ausschließlich der Quelladresse senden, die automatisch durch die Kommunikationshardwarearchitektur **10** gehandhabt wird).

**[0078]** Für das kombinierte Netzwerk ist in dem System eine Vorrichtung vorgesehen, mit der ein Anwender die Kapazität zwischen den PCN-Knoten **220** und den DCN-Knoten **310** zuordnen kann. Die Zuordnungsriorität wird vorzugsweise den PCN-Knoten **220** eingeräumt. Ein Anwender ordnet vorzugsweise den Kommunikationsverkehr in optimierter Weise, um die Wartezeitanforderungen der DCN-Knoten innerhalb der Grenzen der Kanalbandbreite zu erfüllen.

**[0079]** Parameter der physikalischen Schicht der Bewegungssteuerungs-Kommunikationsarchitektur **10** sind wechselseitig abhängig und beeinflussen auch den Kommunikations-Hardwareentwurf und das Protokoll. Die gewählte Kanaltopologie besteht aus einem Mehrfachanschluß-, Bidirektional-, Halbduplexdifferential-Signalbus mit einer vorgegebenen Betriebsgeschwindigkeit von bis zu 10 Mbps (Megabit pro Sekunde). Demnach müssen die die Kommunikation regelnden Logikschaltungen ebenfalls an diese Geschwindigkeit angepaßt sein. Beim Anschalten wird das System mit der niedrigsten Vorgabegeschwindigkeit, 675 Kbps (Kilobit pro Sekunde) betrieben. Ein Anwender kann das Netzwerk auf eine höhere Geschwindigkeit einstellen: 1,25 Mbps, 3,5 Mbps, 5 Mbps oder bis zu 10 Mbps. Da die Geschwindigkeit wählbar ist, wird der Begriff "Bitzeit" benutzt, da er geschwindigkeitsunabhängig ist.

**[0080]** Der Kanal erzeugt kein übermäßiges elektromagnetisches Rauschen, und gleichzeitig widersteht er dem Rauschen in dem Umfeld. In einem System kann Rauschen auf dem Kanal aufgrund der Hochgeschwindigkeitslogik, der Treiberschaltungen, der Motoren und Erddifferentialen einwirken. Es wird ein Differentialtreiber eingesetzt, der den RS422A und den RS485-Standard erfüllt. Ein derartiger Transceiver steht über den Betreiber zur Verfügung und kann mit bis zu 35 Mbps betrieben werden.

**[0081]** Im Zusammenhang mit der Kanallänge basieren aufgrund der Tatsache, daß die Gesamtlänge zwischen den beiden Enden des Netzwerks vorzugsweise niedriger als 35 Fuß ist, die Berechnungen der Übertragungsverzögerung auf der Maximallänge von 35 Fuß. Die Verzögerungszeit wird auch durch die Modulationsgeschwindigkeit und den Kabeltyp beeinflußt. Die vom Ausgang des Transceivers gemessene Verbindungsstrecke zu dem Kanalkabel wird vorzugsweise minimal gehalten. Der Kommunikationskanal ist vorzugsweise auch auf die Impedanz des ausgewählten Kabels abgestimmt. Die Zahl der Leiter für das Serienkommunikationssignal wird vorzugsweise zu 2 gewählt, was sowohl für das Kabel als auch den Verbinder gilt. Ein optionaler Leitungsdraht zum Bestimmen der physikalischen Reihenfolge der Knotenverbindungen kann erforderlich sein. In einem rauen Umfeld muß das Kabel zum Schützen des Signals gegenüber einem Rauschen abgeschirmt sein, wohingehend bei niedriger Geschwindigkeit und/oder einem günstigen Umfeld das Abschirmen nicht erforderlich sein muß.

**[0082]** Bis zu 32 Knoten können an dem Bus **230** angeschlossen sein. Beispielsweise können bei einem Netzwerk mit ausschließlich PCN-Knoten **220** bis zu 31 der PCN-Knoten **220** und ein CCN-Knoten **210** vorliegen. Für ein Netzwerk mit lediglich DCN-Knoten **310** können bis zu 31 DCN-Knoten **310** und ein CCN-Knoten **210** an dem Kanal angeschlossen sein.

**[0083]** Ein sich langsam veränderndes Signal eignet sich nicht für eine Übertragung über eine lange Distanz. Andererseits kann ein besonders schnelles Schalten zur Emission von elektrischem Rauschen führen, und elektronische Komponenten können teuer werden. Bei dieser Implementierung wird das NRZI-(das invertierte NRZ-Schreibverfahren)-Codierschema bei der SDLC-Steuerung benutzt. Bei der NRZI-Codierung werden Daten dadurch übertragen, daß der Zustand des Ausgangs immer dann geändert wird, wenn eine logische 0 übertragen wird. Immer dann, wenn eine logische 1 übertragen wird, bleibt der Ausgang wie bei dem vorhergehenden Bit unverändert und über die gesamte Bitzeit gültig. Ein Beispiel ist in [Fig. 7](#) gezeigt. Bei der SDLC-Steuerung wird ein Bit-Einfügen zusammen mit der NRZI-Codierung eingesetzt. Treten fünf aufeinanderfolgende logische Einsen in dem Datenstrom auf, so wird das 0-Bit eingefügt.

**[0084]** Bei der Architektur **10** wird vorzugsweise ein Mehrfachanschlußbus **230** eingesetzt, der in und von sich selbst aus keine Vorrichtung zum Bestimmen der physikalischen Reihenfolge der Verbindung ist. Zum Erzielen der Modularität wird eine optionale Verbindung zusätzlich zu dem Mehrfachanschlußbus **230** eingesetzt. (Unter "Modularität" wird hier die Fähigkeit verstanden, identische Module zum Durchführen derselben Funktion an unterschiedlichen physikalischen Stellen in einem Bewegungssteuersystem anzuschließen.) Der CCN-Knoten **210** bestimmt dann die Identität und die physikalischen Stelle sämtlicher Knoten und lädt – soweit erforderlich – neue Adressen zum Unterscheiden identischer Module, wie vollständiger nachfolgend beschrieben wird. Da das RS485-Differenzsignal zwei Drähte benutzt, wird diese optionale Verbindung oft als "dritter Draht" bezeichnet. Wie in [Fig. 8](#) gezeigt ist, wird der dritte Draht zum Bilden eines kostengünstigen Rings eingesetzt. Das im Zusammenhang mit der Kommunikation übertragene Steuersignal kann die physikalische Reihenfolge festlegen. Für den kostengünstigen Ring ist jeder Knoten mit einer Eingangsmeßleitung **720** versehen, sowie einer Logik **740** und einer Ausgangsleitung **730**, die mit dem Treiber **750** verbunden ist, der die Eingangsmeßleitung **720** des benachbarten Knotens treibt.

**[0085]** Bei der Architektur **10** erfolgt vorzugsweise die Bestimmung der physikalischen Reihenfolge der Verbindung wie folgt. Zum Rücksetzen des Netzwerks zieht ein Master **760** (typischerweise der CCN-Knoten **210**) seinen offenen Kollektorausgang (Leitung **730**) auf L-Pegel. Jeder Knoten in dem Netzwerk spricht auf ein niedrigewertiges Eingangssignal bei der Leitung **720** an, indem ein Rücksetzen erfolgt, sowie ein Ziehen an dessen offenem Kollektorausgang auf den L-Pegel; hierdurch breitet sich das Rücksetzsignal durch das Netzwerk aus. (Hier wird die gesamte Systemelektronik in einem Rücksetzzustand gehalten, mit Ausnahme des CCN-Knotens **210**). Zum erneuten Starten des Kommunikationsnetzwerks zieht der Master **760** seinen offenen Kollektorausgang auf den H-Pegel und sendet eine Mitteilung, die eine Antwort von einem Knoten verlangt, der gerade einen Rücksetzzustand verlassen hat. Wie in [Fig. 10](#) gezeigt ist, antwortet der benachbarte Knoten **770** mit seiner Knotenidentifikation einschließlich der Vorgabeadresse. Dann fordert der Master **760** den Knoten **770** auf, seinen offenen Kollektorausgang anzuheben. Hierdurch wird dieselbe Situation bei dem zweiten Knoten **780** erzeugt, wie sie zuerst bei dem ersten Knoten **770** vorlag. Der Master **760** wiederholt die Sendemeldung, und der Prozeß wird wiederholt, bis der Master **760** auf seiner Eingabeleitung einen H-Pegel erfaßt.

Durch diesen Prozeß bestimmt der Master **760** die physikalische Reihenfolge der Knotenverbindungen, die Zahl der Knoten und den Typ eines Knotens (PCN-Knoten **220** oder DCN-Knoten **310**).

**[0086]** Der Master **760** setzt dann das Netzwerk erneut zurück, indem er seinen offenen Kollektorausgang auf L-Pegel zieht. Erfäßt der Master **760** einen L-Pegel an seinem Eingang **720**, so hebt er seinen offenen Kollektorausgang erneut an und sendet dann, falls erforderlich, eine neue Adresse, und anschließend sendet er einen Befehl zum Anheben des offenen Kollektorausgangs. Jeder Knoten spricht auf die neue gesendete Adresse lediglich dann an, wenn sein Eingang **720** auf H-Pegel liegt und wenn er noch nicht einem Befehl zum Anheben seines offenen Kollektorausgangs empfangen hat. Dieser Prozeß wird für jeden Knoten wiederholt, so daß das Netzwerk mit einer einzigen Adresse für jeden Knoten konfiguriert wird.

**[0087]** Dieser kostengünstige Ring läßt sich unter Einsatz eines offenen Kollektorausgangs mit einem Hochziehwiderstand am Eingang des benachbarten Knotens implementieren. In diesem Fall kann bei dem Empfänger ein einfaches digitales Filter zum Kompensieren des elektrischen Rauschens zwischen zwei benachbarten Knoten erforderlich sein, oder der Einsatz eines teureren RS485-Treibers kann erforderlich sein. Die Auswahl dieser Schnittstelle wird durch die Systemerdungstopologie bestimmt.

**[0088]** Die Architektur **10** basiert auf einem einfachen Protokoll auf der Datenverbindungsebene, da dies die Dokumentation, die Implementierung, das Debugging/Testen fördert und die Zuverlässigkeit erhöht.

**[0089]** Die hier angegebenen Spezifikationen gelten für die Datenverbindungs-Steuerungsschicht (DLC), sowie unterhalb in der schichtweisen Kommunikationsarchitektur **10**. In diesem Zusammenhang besteht ein Kommunikationsknoten aus vielen Schichten. Eine oberhalb der Datenverbindungsschicht liegende Schicht, möglicherweise die Netzwerkschicht oder die Anwendungsschicht, generiert eine Meldung und fordert die Datenverbindungsschicht auf, diese zu senden. Ein Rahmen oder ein Paket wird durch Hinzufügen der erforderlichen Bits zu einer Meldung aufgebaut. Auf dem DLC-Niveau werden sämtliche Meldungen über den Rahmen **810** übertragen. Der gewählte SDLC-Rahmen **810** ist in [Fig. 9](#) gezeigt. Der Rahmen **810** besteht aus dem Startflag, einer Adresse(en), einem Befehlsbyte, einem optionalen Datenfeld, Bits für die zyklische Blockprüfung (CRC), die den Bereich zwischen dem Adressenfeld und dem optionalen Datenfeld abdecken, und das Endflag. Eine Meldung ist in dem Datenfeld aufgenommen, und deren Länge beträgt 8 Byte für die Kommunikation für die PCN-Knoten **220** und 33 Byte bei DCN-Knoten **310** ausschließlich der Quelladresse. Bei der Kommunikation mit DCN-Knoten **310** kann es nötig sein, daß das optimale Datenfeld vorliegt, da die Architektur **10** das erste Byte des optionalen Datenfelds als Quelladresse benutzt.

**[0090]** Durch die beiden Flags werden das Stimmungsadressenfeld, das Steuerfeld und das CRC-Feld identifiziert. Demnach kann die Länge einer Meldung in einem Rahmen ohne eine Bytezählung bestimmt werden. Die empfangenen Daten sind für einen Anwender über eine FIFO-Schnittstelle verfügbar. Entsprechend wird für übertragene Daten eine FIFO-Schnittstelle eingesetzt, um Anwenderdaten der Kommunikationshardware zur Verfügung zu stellen.

**[0091]** Die Architektur **10** ist vorzugsweise lediglich an dem SCLC-Rahmen **710** angepaßt, und sie entspricht nicht der SDLC-Steuerung im Hinblick auf die logische Datenverbindungssteuerung. Die Architektur **10** weist ihre eigene Definition für das Steuerfeld auf, und sie benutzt sowohl Quell- als auch Bestimmungsadressen für die Kommunikation mit DCN-Knoten **310**.

**[0092]** Ein Knoten muß vorzugsweise in der Lage sein, das Startflag zu detektieren, um den Empfangsprozeß auszulösen, sowie das Endflag, um den Empfang eines Rahmens **710** abzuschließen. Das Bitmuster der Flags muß eindeutig sein, und darf sich innerhalb des Rahmens **710** nicht wiederholen. Detektiert ein Knoten das Endflag mit oder ohne einem Rahmenfehler (d.h., ein Rahmen ist zu kurz oder zu lang), so sollte er in den Neustartzustand sobald wie möglich zurückkehren. Gemäß der SDLC ist 01111110 als Start/Endflag spezifiziert. Da bei der NRZI-Codierung die 0 als Übergang am Beginn einer Bitzeit definiert ist, muß der ruhige oder freie Zustand des Kanalsignals das Gegenteil des Signalpegels nach dem ersten O-Übergang des Rahmens **710** sein. Da dieser allererste Übergang von dem ruhigen Zustand im Vergleich zu anderen Bitübergängen bei hoher Geschwindigkeit und einer langen Übertragungsleitung sein kann, geht ein Zweibitmuster (0 gefolgt durch 1) dem 01111110-Startflag voraus. Dieses Muster, das als eine Art von Präambel betrachtet werden kann, wird durch den Empfänger zur Rahmensynchronisierung benutzt. Zum Übertragen mehrerer Rahmen **710** wird vorzugsweise ein festgelegter Umfang einer Totzeit zwischen dem Endflag und dem Start eines neuen Rahmens **710** vorgesehen.

**[0093]** Wie in [Fig. 10](#) gezeigt ist, weist jeder Knoten einschließlich des CNN-Knotens **210** vorzugsweise eine

Knotenidentifikation (ID) von drei Byte auf. Ein Teil der Knoten-ID wird als Knotenvorgabeadresse benutzt. Jeder Knoten weist vorzugsweise ein Knotenadressenregister auf, das von der Adressenerkennungshardware benutzt wird. Das Knotenadressenregister wird vorgabegemäß mit den niedrigerwertigeren Bits der Knotenidentifikation geladen. Es lässt sich durch den CNN-Knoten **210** dann modifizieren, wenn das Netzwerk mit der Modularitätsoption konfiguriert ist. Die [Fig. 10](#) zeigt das Laden eines Knotenadressenregisters. In dem Bewegungssteuersystem sind funktionelle Module Komponenten, die mit anderen Modulen kommunizieren. Die Identifikation eines Moduls in einem System oder in einer Reihe von zusammenhängenden Systemen ist zum Steuern der Systemvarianten und zum Konfigurieren des Systems wichtig. Die Architektur **10** ermöglicht die elektrische Identifikation und es erfolgt die Identifikation der Revisionsstufe der zugeordneten anwendungsspezifischen integrierten Schaltung (ASIC) für die Kommunikation. Für die elektrische Identifikation eines Moduls kann ein Mehrfachpositionsschalter benutzt werden, und ein Teil hiervon diesem kann als physikalische Adresse eingesetzt werden (beispielsweise 5 Bit). Der CNN-Knoten **210** benutzt vorzugsweise einen reservierten Befehl, um die Identifikationsinformation eines Knotens abzufragen. Empfängt einer der PCN-Knoten **220** oder der DCN-Knoten **310** diesen Befehl, so gibt er vorzugsweise den Registerwert mit 3 Byte an den CNN-Knoten **210** ab.

**[0094]** Der Wert eines Knotenadressenregisters erscheint vorzugsweise in dem Bestimmungsadressenfeld des SDLC-Rahmens. Die Architektur **10** nutzt vorzugsweise auch eine Quelladresse, die ebenfalls von einem Knotenadressenregister kommen muß. Um bis zu 32 PCN-Knoten **210** und 32 DCN-Knoten **310** eindeutig zu identifizieren, sind 6 bit erforderlich. Ein Positionsschalter mit 5 Bit kann zusammen mit einem knotenabhängigen vorprogrammierten Bit in dem ASIC benutzt werden. Lediglich der CNN-Knoten **210** kann die Sendeadresse erzeugen, während alle PCN-Knoten **220** und DCN-Knoten **310** in der Lage sind, die gesendeten Rahmen zu empfangen. Die Modularitätsoption der Architektur **10** ermöglicht das Laden der Adressen. Werden Adressen nicht geladen, so müssen die fest verdrahteten physikalischen Adressen eindeutig in dem in [Fig. 2](#) gezeigten Bereich liegen.

Tabelle 2

| Knotenadressenwert      |                      |           |           |

|-------------------------|----------------------|-----------|-----------|

| CCN:                    | x0000000             |           |           |

| DCN:                    | x0000001             | -x0011111 | (01 – 1F) |

| PCN                     | x0100000             | -x0111111 | (20 – 3F) |

| Senden an alle x1xxxxxx |                      |           |           |

| x:                      | Bit nicht festgelegt |           |           |

**[0095]** Selbst bei der Modularitätsoption kann sich ein Betreiber so entscheiden, daß er die Adresse nicht lädt. Sind Adressen zu laden, so ordnet der CNN-Knoten **210** eine eindeutige Adresse jedem Knoten gemäß der physikalischen Reihenfolge der Verbindung zu. Der Ladeprozess basiert vorzugsweise nicht auf einer Bestimmungsadresse, sondern benutzt die Sendeadresse im Zusammenhang mit dem dritten Draht.

**[0096]** Bei einer Kommunikation von einem zu einem anderen gleichwertigen Element, beispielsweise von einem DCN-Knoten **310** zu einem DCN-Knoten **310**, können die empfangenen Knoten feststellen, welcher Knoten einen Rahmen gesendet hat, da das erste Byte in dem optionalen Datenfeld des Rahmens **710** mit einer Quelladresse für die Kommunikation der DCN-Knoten **310** gewählt ist: Kommunikationsvorgänge zwischen PCN-Knoten **220** erfordern nicht den Einsatz von Quelladressen, da der CCN-Knoten **210** sämtliche PCN-Knoten **220** direkt steuern.

**[0097]** Der CCN-Knoten **210** steuert genau den Zugriff auf den Bus **230** für alle Knoten. Für die Kommunikation mit den PCN-Knoten **220** sendet der CCN-Knoten **210** einen Rahmen **710** zu dem PCN-Knoten **220**. Hierin besteht die einzige Möglichkeit für den adressierten PCN-Knoten **220** zum Übertragen. Für die Kommunikation mit DCN-Knoten **310** gibt der CCN-Knoten **210** einen Befehl für eine Kommunikation von einem DCN-Knoten **310** zu einem anderen DCN-Knoten **310** (oder den CCN-Knoten **210**) ab. Wenn der CCN-Knoten **210** einen Rahmen zu dem DCN-Knoten **310** sendet, so kann dies ohne die Abgabe eines speziellen Zugriffssteuerbefehls erfolgen. Während die DCN-Knoten **310** Hardwarelogik für die Zugriffsteuerung enthalten, ist für die PCN-Knoten **220** keine spezielle Logik erforderlich. Die Adressenerkennungsfähigkeit der PCN-Knoten **220** ist ausreichend, um auf einen Befehl des CCN-Knotens **210** zu antworten.

**[0098]** Wie in [Fig. 11](#) gezeigt ist, tastet der CCN-Knoten **210** zum Unterstützen der I/O-Funktionalitäten der PCN-Knoten **220** periodisch die PCN-Knoten **220** ab. Die Architektur **10** offeriert den Anwendern die Möglichkeit, die einzelne Abtastrate für jeden PCN-Knoten **220** zu steuern. Aus diesem Grund sendet der CCN-Knoten **210** einen speziellen Rahmen an alle Knoten, der als der Synchronisationsrahmen (SYNC-Rahmen) bezeich-

net-wird. Das Intervall für SYNC-Rahmen ist vorzugsweise anwenderkonfigurierbar, typischerweise zwischen 500 µs und einer Millisekunde. In dem Betriebsnormalmodus der Architektur **10** treten SYNC-Rahmen auf dem Bus **230** wie Taktimpulse auf. Das Zeitintervall zwischen zwei aufeinanderfolgenden SYNC-Rahmen wird als die (SYNC)-Tickperiode bezeichnet.

**[0099]** Der SYNC-Rahmen ist vor allem für die PCN-Knoten **220** vorgesehen. Das Fehlen der SYNC-Rahmen auf dem Bus **230** könnte auf einer Fehlerbedingung hinweisen. Ein SYNC-Rahmen-Überwachungsdatenzegeber kann zum Abschalten der I/O-Leitungen der PCN-Knoten **220** vorgesehen sein. Der PCN-Knoten **220** kann auch den SYNC-Rahmen benützen, um einen zeitlichen Versatz aufgrund des Einfügens eines Bits oder aus anderen Gründen benützen. Während einer Tickperiode lassen sich viele Rahmen zu unterschiedlichen PCN-Knoten **220** übertragen. Für einen perfekten Zeitallauf kann der PCN-Knoten **220** einen Betrieb im "synchronisierten" Modus durchführen und einen empfangenen Rahmen erhalten und dessen Inhalt synchron zu dem Ende eines SYNC-Rahmens ausführen. In dem synchronisierten Modus können die PCN-Knoten **220** so konfiguriert sein, daß sie auch die Eingabeleitungen unter simultanem Einsatz der SYNC-Rahmen abtasten. Hierdurch läßt sich eine besonders synchrone Aufnahme sämtlicher Sensoren in dem System erreichen.

**[0100]** Zum Eliminieren der zeitlichen Synchronisationsversatzes aufgrund des Einfügens von Bits bei dem SDLC-Protokoll startet der CCN-Knoten **210** die Übertragung am Beginn eines regulären Zeitintervalls. Dieses Intervall wird bestimmt, indem von einer Worst-Case-Biteinfügung für ein vorgegebenes System bei Einsatz der Architektur **10** ausgegangen wird. Für 8 Byte Daten mit ausschließlich logischen Einsen müssen 12 Bit logischer Nullen eingefügt werden. Die maximale Puffergröße für einen Übertragungspuffer und einen Empfangspuffer eines PCN-Knotens **220** werden durch den CCN-Knoten **210** nach dem Untersuchen der Tabelle der Knotenidentifikation bestimmt. Innerhalb eines Systems mit der Architektur **10** können PCN-Knoten **220** unterschiedliche Kommunikationspuffergrößen aufweisen. Die synchronisierte Übertragung der Meldungen der PCN-Knoten **220** basiert auf der Maximalgröße der Puffer der PCN-Knoten **220**. Demnach sollten Anwendungsprogramme vorzugsweise dieses Intervall für die Kommunikation mit PCN-Knoten **220** spezifizieren.

**[0101]** Die DCN-Knoten **310** erkennen auch den SYNC-Rahmen, da beispielsweise mit PCN-Knoten **220** einige Aktivitäten der DCN-Knoten **310** mit den Aktivitäten der PCN-Knoten **220** zu synchronisieren sind.

**[0102]** Die Kommunikation zwischen dem CCN-Knoten **210** und den PCN-Knoten **220** kann auch in einem "unmittelbaren" Modus durchgeführt werden, bei dem PCN-Knoten **220** auf Meldungen unmittelbar antworten, um empfangene Daten an ihre Ausgangsleitungen weiterzuleiten und/oder ihren Status unmittelbar rückzugeben. Vorzugsweise wird zum Aufrechterhalten der Synchronisation der CCN-Knoten **210** immer mit einem bestimmten PCN-Knoten **220** während desselben Zeitintervalls, bezogen auf den SYNC-Rahmen einer Tickperiode kommunizieren.

**[0103]** Als ein Beispiel sei angenommen, daß ein Netzwerk drei PCN-Knoten **220** enthält, A, B und C. Weiterhin sei angenommen, daß der Knoten A eine Aktualisierung bei jeder Tickperiode erfordert, während die Knoten B und C lediglich eine Aktualisierung bei jeder weiteren Tickperiode erfordern. Die Kommunikationsvorgänge können dann in einen Ablauf A, B; A, C; A, B; usw., eingeordnet werden. Die mit dem Stand der Technik Vertrauten erkennen, daß durch das Einordnen von Kommunikationsvorgängen innerhalb einer Periode, deren Länge ein ganzzahliges Vielfaches der Tickperioden ist, sich die Servofunktionen für die Bewegungssteuerung und dergleichen erheblich vereinfachen lassen. Jedoch werden die mit dem Stand der Technik Vertrauten auch erkennen, daß bei Anwendungen, die einen gewissen Umfang von Synchronisationsstörungen bei den Zeitabläufen von Kommunikationsvorgängen tolerieren, die Kommunikationsvorgänge in dem unmittelbaren Modus nicht periodisch verlaufen müssen.

**[0104]** Bei einer bevorzugten Ausführungsform der vorliegenden Erfindung kann jeder der PCN-Knoten **220** und das Netzwerk wahlweise entweder in einem synchronisierten oder in einem unmittelbaren Modus betrieben werden, und das Netzwerk als ganzes kann in einem synchronisierten, einem unmittelbaren oder einem gemischten Modus betrieben werden.

**[0105]** Die Zugriffsteuerung für DCN-Knoten **310** ist so entworfen, daß eine Wartezeit des DCN-Knoten **310** garantiert ist, d.h. die maximale Wartezeit für die Übertragung. Da ein Anwender die gesamte Bandbreite für die PCN-Knoten **220** benützen kann, muß ein Anwender eine bestimmte Bandbreite den DCN-Knoten **310** zuordnen. Bei der Architektur **10** ist die Vorrichtung vorgesehen, mit der ein Anwender die maximale Wartezeit der DCN-Knoten **310** steuern kann. Ein Anwender kann dynamisch eine kurze Wartezeit für einen wichtigen DCN-Knoten **310** auswählen.

**[0106]** Nachdem der CCN-Knoten **210** seine geplante Kommunikation mit den PCN-Knoten **220** innerhalb einer Tickperiode beendet hat, berechnet er die vor dem nächsten SYNC-Rahmen verbleibende Zeit. Ist die Zeit für eine Kommunikation mit einem DCN-Knoten **310** ausreichend, so initiiert der CCN-Knoten **210** eine Kommunikation von einem DCN-Knoten **310** zu einem anderen DCN-Knoten **310**, wie in [Fig. 11](#) gezeigt ist. Bis zu einer Meldung kann dann zwischen den beiden DCN-Knoten **310** ausgetauscht werden. Anschließend berechnet der CCN-Knoten **210** erneut die verbleibende Zeit vor dem nachfolgenden SYNC-Rahmen und der Prozeß kann wiederholt werden.

**[0107]** Die Kommunikationsvorgänge von einem DCN-Knoten **310** zu einem anderen DCN-Knoten **310** oder von einem DCN-Knoten **310** zu einem CCN-Knoten **210** bestehen aus den durch den CCN-Knoten **210** gesendeten DAC-(DCN-Zugriffssteuerungs)-Rahmen, der Störvermeidungsperiode, einem durch den DCN-Knoten **310** übertragenen Informationsrahmen und den durch den anderen DCN-Knoten **310** initiierten Bestätigungsrahmen. Die DCN-Knoten **310** wirken zusammen, um eine Störung während der Störvermeidungsperiode zu vermeiden. Aus diesem Grund nützen die DCN-Knoten **310** die Daten in dem DAC-Rahmen sowie die Daten in ihrem internen Speicher, die durch den CCN-Knoten **210** im Zeitpunkt der Netzwerkkonfiguration geladen wurden.

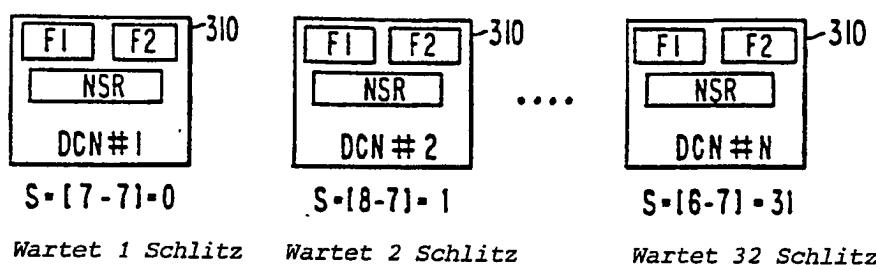

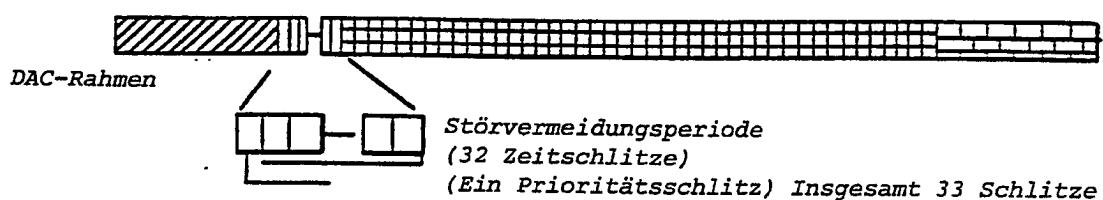

**[0108]** Die Störvermeidungsperiode besteht aus einem Prioritäts- und 32 Zeitschlitz, insgesamt also aus 33 Schlitzten. Ein Zeitschlitz ist als eine Zeitperiode definiert, indem die DCN-Knoten **310** den Start einer Rahmenübertragung durch andere DCN-Knoten **310** detektieren können. Die Periode eines Zeitschlitz ist unter Beachtung der Zeitkonstanten der Transceiverschaltung der DCN-Knoten **310** zu bestimmen, sowie der Verzögerung aufgrund der logischen Entscheidungsfindung, der Kanallänge und der Ausbreitungsverzögerung. Ein Zeitschlitz bei einem Mehrfachanschlußbus kann mehrere Bitzeiten oder den Bruchteil einer Bitzeit einnehmen. Alternativ kann bei der Architektur **10** eine Ringkombination eingesetzt werden, obgleich die Zeitschlitzperiode länger wäre.

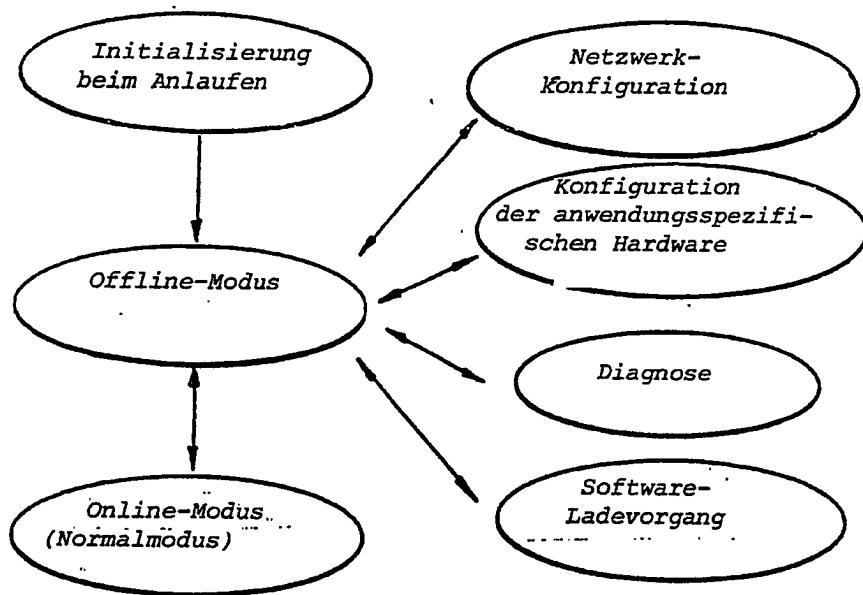

**[0109]** Die Architektur **10** ermöglicht den Prioritätsschlitz für ein Bewegungssteuer-Untersystem, bei dem der CCN-Knoten **210** auf das Auftreten eines Ereignis in einem bestimmten DCN-Knoten **310** warten kann. Derartige Ereignisse können in zahlreichen DCN-Knoten **310** auftreten. Wird ein wichtiges Ereignis vorweggenommen, so sollte den DCN-Knoten **310** eine hohe Priorität eingeräumt werden. Zum Erfüllen dieses Erfordernisses weist der CCN-Knoten **210** vorzugsweise die Fähigkeit auf, die Zuordnung eines DCN-Knotens **310** zum unmittelbaren Übertragen nach einem DAC-Rahmen unter Einsatz des Prioritätsschlitzes durchzuführen. Der CCN-Knoten **210** kann die Zuordnung des Prioritätsmodus löschen und diese zu einem anderen DCN-Knoten übergeben. Die DCN-Knoten **310** weisen Flags auf, die anzeigen, ob sie im Prioritätsmodus oder in dem Schlitzmodus betrieben werden sollten. Details der Zugriffsteuerung für die DCN-Knoten **310** sind in den [Fig. 11](#) bis [Fig. 14](#) gezeigt.

**[0110]** Wie in [Fig. 12](#) gezeigt ist, lädt zum Koordinieren der DCN-Knoten **310** während der Störvermeidungsperiode der CCN-Knoten **210** eine eindeutige Zahl in jeden -der DCN-Knoten **310** im Zeitpunkt der Netzwerkkonfiguration. Der DCN-Knoten **310** speichert die Zahl in seinem Knotenschlitzregister (note slot register, NSR). Wie in [Fig. 12](#) gezeigt ist; kennzeichnet F1 das Prioritätsmodusbit (der CCN-Knoten **210** schreibt in F1 über den Rahmen), und F2 ist ein durch den DCN-Knoten **310** gesetztes/rückgesetztes Bit zum Vermeiden aufeinanderfolgender Übertragungen, und der DCN-Knoten **310** enthält auch ein Knotenadreßregister (node address register, NAR). Für die in [Fig. 13](#) gezeigte Kommunikation des DCN-Knotens **310** im Normalbetrieb sendet der CCN-Knoten **210** vorzugsweise auch eine Schlitzsteuernummer (slot control number, SCN) in dem DAC-Rahmen. Die SCN bestimmt den Knoten zum Übertragen unter Einsatz des ersten Zeitschlitzes unmittelbar nach dem Prioritätsschlitz. Empfängt beispielsweise ein Knoten die SCN in einem DAC-Rahmen, die mit dem NSR-Wert übereinstimmt, d.h. ist die Differenz 0, so kann dieser unmittelbar nach dem Prioritätsschlitz übertragen. Wie in [Fig. 14](#) gezeigt ist, berechnen die DCN-Knoten **310** die Differenz zwischen der SCN und dem NSR in Modulo-32-Arithmetik, was anzeigt, wieviele Schlitz einer der DCN-Knoten **310** abwarten muß, bevor er eine Übertragung initiiert. Die Differenz ist bei den DCN-Knoten **310** eindeutig, da das NSR der DCN-Knoten **310** bei sämtlichen DCN-Knoten **310** eindeutig ist. Zum Vermeiden einer Störung werden keine zwei NSR-Werte dupliziert. Der CCN-Knoten **210** verändert den SCN-Wert derart, daß alle DCN-Knoten **310** eine gleiche Chance auf den Zugriff zu dem Bus **230** haben.

**[0111]** Wie in [Fig. 15](#) gezeigt ist, initiiert ein DCN-Knoten **310** dann, wenn er eine Meldung zu übertragen hat und wenn er einen DAC-Rahmen empfängt, eine Übertragung im Prioritätsschlitz, wenn der DCN-Knoten **310** sich in dem Prioritätsmodus befindet. Andernfalls wartet der DCN-Knoten **310** auf die Periode, die zu der Differenz zwischen dem NSR und der empfangenen SCN-Zahl identisch ist. Wird während dieser Periode keine Kommunikation erfaßt, so initiiert der DCN-Knoten **310** eine Übertragung. Andernfalls muß der DCN-Knoten

**310** auf den nächsten DAC-Rahmen des Prozesses warten. Wird ein Rahmen durch einen DCN-Knoten **310** übertragen, so sendet der empfangene DCN-Knoten **310** unmittelbar einen Bestätigungsrahmen. Nachdem ein DCN-Knoten **310** einen Rahmen erfolgreich überträgt, wird er in der nächsten Störvermeidungsperiode keine Übertragung initiieren, so daß anderen DCN-Knoten **310** einen möglichen Zugriff haben.

**[0112]** Für das System mit 31 DCN-Knoten **310**, d.h. die Maximalkonfiguration, muß der NSR-Wert die Knotenadresse bei jedem DCN-Knoten **310** sein. Der NSR-Vorgabewert ist die Knotenadresse beim Rücksetzen. Der CCN-Knoten **210** kann die Werte zu den NSR-Registern zum Verändern der Vorgabewerte laden. Der NSR-Wert muß eindeutig sein, wie eine Adresse der DCN-Knoten **310**. Die Ladefähigkeit ermöglicht einem Anwender DCN-Knoten **310** frei zu (re-)konfigurieren, um Anforderungen im Hinblick auf Zugriffsteuervorgänge zu erfüllen.

**[0113]** Zum Verbessern des Wirkungsgrades bei Netzwerken mit im wesentlichen weniger als 31 DCN-Knoten **310** erzeugt die Hardware des CCN-Knotens **210** vorzugsweise die DAC-Rahmen in einer optimierten Weise. Die SCN-Zahlen in einem DAC-Rahmen wird von dem Zugriffsteuerregister (ACR) des CCN-Knotens **210** kopiert. Das ACR wird automatisch bei jedem DAC-Rahmen inkrementiert. Erreicht das ACR einen bestimmten Maximalwert (anwenderspezifizierbar), so wird für eine Wiederholung das Register rückgesetzt. Der Maximalwert kann die Zahl der DCN-Knoten **310** in dem Netzwerk sein. Unter Einsatz dieses Merkmals wird ein Kommunikationstreiber unter Optimierung der Zugriffsteuervorgänge aufgebaut.

**[0114]** Der CCN-Knoten **210** kann die DAC-Rahmen innerhalb einer Tickperiode solange wiederholen, solange die verbleibende Zeit vor dem nächsten SYNC-Rahmens für eine DCN-Kommunikation ausreicht. Liegen keine Aktivitäten vor, die DCN-Knoten **310** einschließen, so ist es möglich, viele DAC-Rahmen hintereinander ohne andere Rahmen zu beobachten.

**[0115]** In einer bevorzugten kostengünstigen Ausführungsform wartet der CCN-Knoten **210** während einer festgelegten Zeit, die der Summe der Störvermeidungsperiode und der schlechtmöglichsten Zeit für eine Kommunikation eines PCN-Knotens **310** ist, und inkrementiert dann das ARC-Register und überträgt eine DAC-Rahmen, wenn ausreichend Zeit verbleibt.

**[0116]** Soll die Bandbreite des Netzwerks vollständiger ausgenutzt werden, so kann der CCN-Knoten **210** das Netzwerk überwachen und einen DAC-Rahmen unmittelbar nach der Störvermeidungsperiode übertragen, wenn kein DCN-Knoten **310** mit einer Übertragung begonnen hat, oder am Ende einer Meldung, wenn ausreichend Zeit verbleibt.

**[0117]** Wie in Tabelle 2 gezeigt ist, ist dem CCN-Knoten **210** vorzugsweise die Adresse 00(hex), die die Adresse eines DCN-Knoten **310** ist. Das heißt, das DCN/PCN-Bit ist 0. Demnach arbeitet bei einer Echtzeitkommunikation zwischen dem CCN-Knoten **210** und einem DCN-Knoten **310** (im Gegensatz zur Systemkonfiguration oder zur Kommunikationssteuerung) der CCN-Knoten **210** im wesentlichen in der gleichen Weise, und er enthält im wesentlichen die gleiche Schaltung, wie sie oben für den CCN-Knoten **210** beschrieben ist.

**[0118]** Die Architektur **10** ermöglicht die Detektion dreier Arten von Fehlern: Rahmenfehler, Zeitablauf und CRC-Fehler. Die Detektion einer Fehlerbedingung wird vollständig in Hardware implementiert. Obgleich ein Knoten zahlreiche Arten von Fehlern detektieren kann, zeigt er in seinem Statusregister vorzugsweise lediglich an, ob ein Fehler aufgetreten ist oder nicht. Ein Datenstrom, der nicht in einen festgelegten Rahmen paßt, wird als Rahmenfehler betrachtet. Beispiele enthalten: ein nicht definiertes Flagmuster, wenn ein bestimmtes erwartet wird, ein vorzeitiges Endflag, ein nicht erwartetes Startflag, eine nicht definierte Adresse, ein nicht definierter Steuercode, ein Überschreiten der festgelegten Länge eines Datenfelds oder ein Vorliegen eines Datenfelds, wenn kein Datenfeld erwartet wird.

**[0119]** Ein Zeitablauffehler wird festgestellt, wenn ein erwartetes Ereignis nicht auftritt. Überträgt der CCN-Knoten **210** einen Befehl zu einem PCN-Knoten **220**, so erwartet er unmittelbar eine Antwortmeldung oder eine explizite Bestätigung des adressierten PCN-Knotens **220**, da diese Funktion in Hardware implementiert ist. Wird keine Antwort innerhalb einiger Bitzeiten erhalten, so stellt der CCN-Knoten **210** den Zeitablauffehler für den PCN-Knoten **220** fest. Empfängt der PCN-Knoten **220** den SYNC-Rahmen nicht regulär, so erfaßt er den Zeitablauffehler. Überträgt ein DCN-Knoten **310** einen Daten-(Informations)-Rahmen an einen anderen DCN-Knoten **310**, so erwartet er eine positive oder negative Bestätigung von dem empfangenen Knoten innerhalb einiger Bitzeiten. In diesem Fall erfaßt der übertragende DCN-Knoten **310** den Zeitablauffehler.

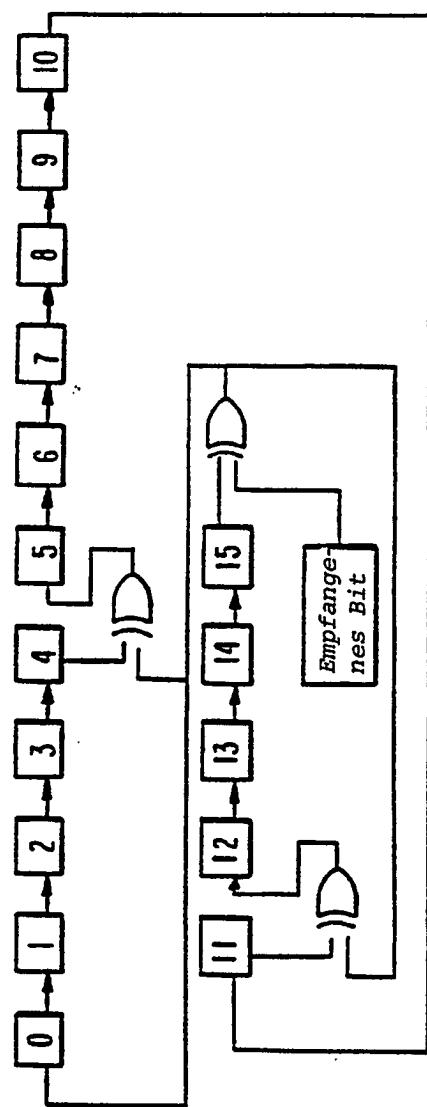

**[0120]** Die Durchführung und Überprüfung mit Hilfe der zyklischen Blockprüfung (CRC) stellt die wichtigste

Maßnahme zum Detektieren von Fehlern dar. Vorzugsweise wird der DRC-16 als Rahmenüberprüfungssequenz eingesetzt, und dieser wird durch die algebraische Gleichung  $X^{16} + X^{15} \dots + X^2 + 1$  dargestellt. Die CRC-Generierung ist in [Fig. 16](#) gezeigt. Während des Betriebs wird ein Bit empfangen und wird mit dem Bit 15 des momentanen CRC gemäß EXOR verknüpft und in einem Zwischenspeicher abgelegt. Das Ergebnis der EXOR-Verknüpfung des Bits 15 mit dem empfangenen Bit wird dann mit dem Bit 4 EXOR-verknüpft, und das Bit 11 des CRC wird um eine Position nach rechts verschoben. Das Bit in dem Zwischenspeicher wird in die Position 0 verschoben.

**[0121]** Bei der Architektur **10** kommen vorzugsweise zwei Arten von Rahmen zum Einsatz: Informationsrahmen und Steuerrahmen. Der Rahmentyp lässt sich in dem Steuerfeld spezifizieren. Einer der Steuerrahmen ist der Bestätigungs-(ACK)-Rahmen. Bei der Architektur **10** kann die Bestätigung explizit mit dem ACK-Rahmen erfolgen, oder implizit, wenn ein Antwortrahmen empfangen wird.

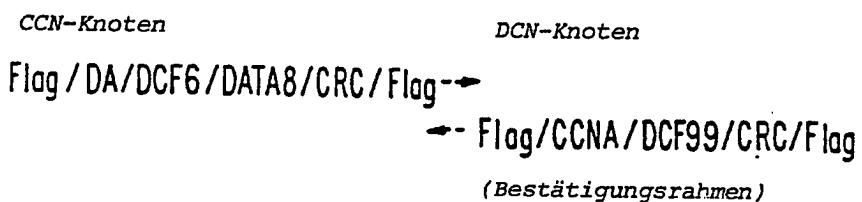

**[0122]** Für die Kommunikation mit den PCN-Knoten **220** sendet der CCN-Knoten **210** einen Rahmen, und anschließend sendet innerhalb mehrerer Bitzeiten der adressierte PCN-Knoten **220** einen Rahmen zurück, was zu einer Bestätigung führt. Aufgrund der hohen Abtastrate der PCN-Knoten **220** erfolgt keine Bestätigung für den PCN-Knoten **220** durch den CCN-Knoten **210**.

**[0123]** Für die Kommunikation mit den DCN-Knoten **310** werden sämtliche Rahmen vorzugsweise über den ACK-Rahmen innerhalb mehrerer Bitzeiten bestätigt. Jedoch muß der ACK-Rahmen selbst nicht bestätigt werden, und vorzugsweise wird er es auch nicht. Die Informationsrahmen der DCN-Knoten **310** benutzen sowohl Quell- als auch Bestimmungssadressen. Da ein ACK-Rahmen unmittelbar auf einen Informationsrahmen folgt, benutzt der ACK-Rahmen nicht die Quelladresse. Diese unmittelbare Bestätigung ist zum Vermeiden von einer Zwischenspeicherung von Meldungen ausgebildet. Der DCN-Knoten **310** sendet eine negative Antwort unter Einsatz des Bestätigungs-Rahmenformats lediglich dann, wenn er aufgrund einer Nichtverfügbarkeit eines Empfangspuffers einen Rahmen nicht empfangen kann.

**[0124]** Ein Empfang der Knoten kann entweder einen Rahmenfehler oder einen CRC-Fehler feststellen. Er kann die Art sowie das Auftreten der Fehler insgesamt bestimmen, den fehlerhaften Rahmen übergehen, jedoch keine Fehlerkorrektur durchführen. Ein übertragener Knoten ist immer für die Fehlerkorrektur bei Erfassung eines Zeitablauffehlers oder eines Rahmenfehlers während einer Bestätigung zuständig. Diese Strategie vermeidet mögliche Störungen beim Zugriff auf den Bus während einer Fehlerbeseitigung.

**[0125]** Bei der Kommunikation mit PCN-Knoten **220** soll keine Fehlerkorrektur durchgeführt werden. Stattdessen werden Fehler ignoriert. Erfaßt jedoch der CCN-Knoten **210** eine übermäßige Zahl von Kommunikationsfehlern während einer festgelegten Periode, so kann er bestimmen, daß das Netzwerk stillgelegt wird.

**[0126]** Bei der Kommunikation mit DCN-Knoten **310** basiert die Fehlerkorrektur auf einem erneuten Versuch. Im Zusammenhang mit der Zeitablauffehler-Bedingung oder einem Fehler bei dem erwarteten ACK-Rahmen wird der übertragende Knoten viele Versuche durchführen, bevor er anzeigt, daß eine Kommunikationsverbindung zu einem adressierten Knoten unterbrochen ist. Das Zeitintervall für die erneute Übertragung muß lange genug sein, so daß eine Umfeldbedingung, die den Fehler auslöst, nicht länger vorliegt. Demnach führt der DCN-Knoten **310** den erneuten Versuch nicht unmittelbar durch, sondern wartet auf seine nächste Gelegenheit, die durch einen Verzögerungszeitgeber für eine erneute Übertragung bestimmt ist. Zeigt ein DCN-Knoten **310** über das ACK-Rahmenformat an, daß er eine Meldung aufgrund eines nicht verfügbaren Puffers nicht empfangen kann, so sollte das Zeitintervall für die erneute Übertragung lange genug sein, so daß die CPU des DCN-Knoten **310** dessen Empfangspuffer löscht. Bei der Architektur **10** ist das Löschen des Empfangspuffers innerhalb einer vorgegebenen Maximalzeit durch den DCN-Knoten **310** erforderlich.

**[0127]** Die PCN-Knoten **220** und die DCN-Knoten **310** weisen einen Übertragungspuffer und einen Empfangspuffer unter Steuerung der Kommunikationshardware auf. Andererseits weist der CCN-Knoten **210** 31 Pufferpaare für die Kommunikation mit den PCN-Knoten **220** auf, sowie lediglich ein Pufferpaar für die Kommunikation mit den DCN-Knoten **310**. Jeder PCN-Knoten **220** ist so entworfen, daß er nach einer positiven CRC-Überprüfung seinen Empfangspuffer überschreibt. Der CCN-Knoten **210** gibt seinen Empfangspuffer frei, wenn er eine Übertragung zu einem PCN-Knoten **220** durchführt. Ein DCN-Knoten **310** ist für die Übertragung einer Meldung zu einem anderen DCN-Knoten **310** freigegeben, wenn davon ausgegangen wird, daß der adressierte Knoten einen verfügbaren Empfangspuffer aufweist. Wird eine negative Antwort empfangen, so führt der initiiierende DCN-Knoten **310** eine erneute Übertragung durch.

**[0128]** Eine Meldungsreihung (lediglich für die Kommunikation für DCN-Knoten **210**) wird eingefügt, um dup-

lizierte Meldungen zu erfassen (d.h., eine identische Meldung wird mehr als einmal übertragen, und zwar aufgrund einer erneuten Übertragung bei Erfassung eines Fehlers in dem ACK-Rahmen, oder wenn kein ACK-Rahmen vorliegt). Eine duplizierte Meldung wird erkannt und nicht berücksichtigt. Da eine Warteschlangenbildung für eine Meldung nicht benutzt wird und jede Meldung bestätigt wird, reicht 1 Bit pro Einfachkommunikation von Knoten zu Knoten. Liegen bis zu 31 DCN-Knoten **310** und der DCN-Knoten **310** vor, so sind 34 Bit Speicherplatz pro DCN-Knoten erforderlich, damit 32 Paare von Meldungsreihenfolgezahlen gespeichert werden. Dies unterscheidet sich von dem SDLC-Schema, bei dem ein Knoten bis zu sieben Meldungen ohne Bestätigung senden kann, da es bis zu sieben Empfangspuffer spezifiziert und 3 Bit für die Meldungsreihenfolgezahl benutzt. Diese Reihenfolgezahl wird zum Detektieren duplizierter Meldungen benutzt. Da bei der Hardware der Architektur **10** lediglich ein Empfangspuffer möglich ist, reicht ein Bitpaar zum Detektieren einer duplizierten Meldung.

**[0129]** Bei der Einreihung einer Meldung sind vorzugsweise lediglich zwei Knoten, beispielsweise als Knoten A und B, mit einbezogen. Es liegt vorzugsweise ein Paar von Laufnummern pro Einwegübertragung vor (d.h., die Übertragungslaufnummer des Knotens A steht lediglich im Zusammenhang mit der Empfangslaufnummer des Knotens B). Ein Knoten unterhält ein Paar von Empfangs/Übertragungs-Laufennummern, da er sowohl überträgt als auch empfängt. Laufnummern sind vorzugsweise synchronisiert (Rücksetzen zu 0), wenn das Netzwerk beim Anfahren der Stromversorgung initialisiert wird. Überträgt der Knoten A eine Meldung, so sendet er vorzugsweise seine in dem Steuerfeld gespeicherte Übertragungslaufnummer. Empfängt der Knoten B die Meldung ohne einen Fehler, so kippt er die Empfangslaufnummer und führt eine Rückantwort mit dem ACK-Rahmen durch. Empfängt der Knoten A den ACK-Rahmen korrekt, so kippt er die Übertragungslaufnummer, wodurch ein Zyklus beendet wird. Am Ende jedes erfolgreichen Zyklus sollten die Übertragungslaufnummer des Knotens A und die Empfangslaufnummer des Knotens B übereinstimmen. Eine Laufnummer ist in einem Meldungsrahmen enthalten, sie ist jedoch nicht in dem ACK-Rahmen enthalten.

**[0130]** Es sei angenommen, daß der Knoten A einen Rahmen gesendet hat und bei dem Knoten B ein Fehler aufgetreten ist. Der Knoten B führt keine Bestätigung durch. Keine Ablaufbits werden beeinflußt, und der Knoten A sollte erneut übertragen. In einem anderen Fall sei angenommen, daß der Knoten A einen Rahmen gesendet hat, und der Knoten B diesen korrekt empfangen hat. Der Knoten B hat eine Bestätigung gesendet, jedoch ist in dem Knoten A ein Fehler aufgetreten. Demnach wird der Knoten A den Rahmen erneut übertragen, obgleich der Knoten B den Rahmen bereits korrekt empfangen hat. Das Ablaufbit verhindert, daß der Knoten B einen duplizierten Rahmen empfängt.

**[0131]** Ein Empfangsknoten kann demnach eine duplizierte Meldung erkennen, daß seine gespeicherte Laufnummer nicht mit der empfangenen Laufnummer abgestimmt ist. Der Knoten läßt die duplizierte Meldung unberücksichtigt, sendet jedoch den ACK-Rahmen erneut zurück. Wird dieser ACK-Rahmen korrekt übertragen, so ist das Paar der Laufnummern der Einwegübertragung erneut synchronisiert. Es kann erforderlich sein, daß die Datenverbindungsschicht die Herstellung der Verbindung an eine höhere Schicht berichtet. Werden Laufnummern initialisiert, so sollten die Empfangs- und Übertragungspuffer gelöscht sein.

**[0132]** Die im Zusammenhang mit der Rahmenerzeugung, dem Empfang, der Deutung und zugeordneten Aktionen erforderlichen Logikfunktionen sind in Hardware realisiert. Bei der Architektur **10** ist die Zahl der definierten Rahmen, wenn möglich, minimiert. Obgleich bei der Architektur **10** der SDLC-Rahmen eingesetzt wird, erfolgt bei der Architektur **10** die Definition des Steuerfelds eines SDLC-Rahmens in eigener Weise, um die Datenverbindungssteuervorgänge in Hardware zu implementieren. Bei der Architektur **10** sind ferner zusätzliche Merkmale vorgesehen, die für die Systementwicklung wesentlich sind, beispielsweise ein Hardware-Rücksetzsignal oder eine Knotenidentifikation.