(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3772622号

(P3772622)

(45) 発行日 平成18年5月10日(2006.5.10)

(24) 登録日 平成18年2月24日(2006.2.24)

(51) Int.C1.

F 1

|               |              |                  |        |       |         |

|---------------|--------------|------------------|--------|-------|---------|

| <b>HO 1 G</b> | <b>4/252</b> | <b>(2006.01)</b> | HO 1 G | 1/14  | V       |

| <b>HO 1 G</b> | <b>4/30</b>  | <b>(2006.01)</b> | HO 1 G | 4/30  | 3 O 1 F |

| <b>HO 1 L</b> | <b>21/60</b> | <b>(2006.01)</b> | HO 1 G | 4/30  | 3 O 1 B |

| <b>HO 1 G</b> | <b>4/33</b>  | <b>(2006.01)</b> | HO 1 L | 21/60 | 3 1 1 S |

HO 1 G 4/06 1 O 2

請求項の数 5 (全 11 頁)

(21) 出願番号

特願2000-26527 (P2000-26527)

(22) 出願日

平成12年2月3日(2000.2.3)

(65) 公開番号

特開2001-217142 (P2001-217142A)

(43) 公開日

平成13年8月10日(2001.8.10)

審査請求日

平成14年1月16日(2002.1.16)

(73) 特許権者 000006231

株式会社村田製作所

京都府長岡京市東神足1丁目10番1号

(74) 代理人 100079577

弁理士 岡田 全啓

(72) 発明者 竹島 裕

京都府長岡京市天神二丁目26番10号

株式会社村田製作所内

(72) 発明者 坂部 行雄

京都府長岡京市天神二丁目26番10号

株式会社村田製作所内

審査官 大澤 孝次

最終頁に続く

(54) 【発明の名称】薄膜積層コンデンサおよびその実装方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板、および前記基板に形成された複数の誘電体層と電極層との積層体を含む薄膜積層コンデンサにおいて、

前記電極層は前記誘電体層によって電気的に分割される第1の電極層と第2の電極層とを含み、前記電極層の面上において部分的に形成された前記誘電体層を介して前記第1の電極層と前記第2の電極層とが交互に積層され、

前記電極層の面上であって前記誘電体層が形成されていない部分には導体膜が形成され、

前記誘電体層の形成されていない部分において複数の前記第1の電極層が互いに電気的に接続されるとともに、前記誘電体層の形成されていない部分において複数の前記第2の電極層が互いに電気的に接続され、

前記積層体の前記基板と反対側の面上に、前記電極層と電気的に接続する3つ以上の外部接続用の半田バンプが形成されたことを特徴とする、薄膜積層コンデンサ。

## 【請求項 2】

前記誘電体層の形成されていない部分において複数の前記第1の電極層が前記導体膜を介して互いに電気的に接続されるとともに、前記誘電体層の形成されていない部分において複数の前記第2の電極層が前記導体膜を介して互いに電気的に接続された、請求項1に記載の薄膜積層コンデンサ。

## 【請求項 3】

10

前記積層体の面上に開口部を有する保護膜が形成され、前記開口部において前記電極層に接続される半田によって前記半田バンプが形成された、請求項1または請求項2に記載の薄膜積層コンデンサ。

#### 【請求項4】

基板、および前記基板に形成された複数の誘電体層と電極層との積層体を含む薄膜積層コンデンサにおいて、

前記誘電体層は、少なくともBaまたはSrを含む酸化物薄膜であり、トリエチレンテトラミンあるいはテトラエチレンペニタミンを付加したジピバロイルメタネト錯体を原料としてMOCVD法を用いて成膜されたものであり、

前記積層体の前記基板と反対側の面に3つ以上の外部接続用の半田バンプが形成されたことを特徴とする、薄膜積層コンデンサ。

10

#### 【請求項5】

請求項1ないし請求項4のいずれかに記載の薄膜積層コンデンサを配線基板上に実装する薄膜積層コンデンサの実装方法であって、

前記半田バンプが前記配線基板上の配線に接続されることを特徴とする、薄膜積層コンデンサの実装方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は薄膜積層コンデンサおよびその実装方法に関し、特にたとえば、小型で比較的大容量の薄膜積層コンデンサおよびその実装方法に関する。

20

##### 【0002】

##### 【従来の技術】

近年、電子部品の分野においては、回路の高密度化に伴い、コンデンサなどの一層の小型化および高性能化が望まれている。小型のコンデンサとして積層セラミックコンデンサなどがあるが、このような積層セラミックコンデンサを作製するには、所定の大きさにカットされた誘電体セラミックグリーンシートが準備される。このセラミックグリーンシート上に電極ペーストを印刷し、乾燥後にセラミックグリーンシートの積層、圧着を行い、さらに所定の大きさにカットして焼成することにより、チップが得られる。このチップに外部電極ペーストを塗布し、焼き付けることにより、積層セラミックコンデンサが得られる。

30

##### 【0003】

しかしながら、このような方法で積層セラミックコンデンサを作製する場合、セラミック原料粉末粒径よりも誘電体層を薄くすることは不可能であり、その他誘電体層の欠陥によるショートや電極切れの問題から、現状では誘電体層の厚み3μm以下のものを作製することは困難であり、積層セラミックコンデンサの小型、大容量化には限界があった。

##### 【0004】

このような問題を解決するために、たとえば特開昭56-144523号公報には、基板上にスパッタリング法で誘電体部分を作製する積層セラミックコンデンサが提案されている。ここでは、Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, TiO<sub>2</sub>, BaTiO<sub>3</sub>の薄膜および電極をスパッタリング法で作製する方法が開示されている。

40

##### 【0005】

##### 【発明が解決しようとする課題】

しかしながら、Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, TiO<sub>2</sub>などは、材料そのものの誘電率が低いので、コンデンサとしての容量を上げようすると、膜厚を非常に薄くする必要があり、リーク電流、絶縁耐圧など、電子デバイスとしての信頼性に問題がでてくる。そこで、BaTiO<sub>3</sub>のほか、SrTiO<sub>3</sub>, (Ba, Sr)TiO<sub>3</sub>, PbTiO<sub>3</sub>, Pb(Zr, Ti)O<sub>3</sub>, Pb(Mg, Nb)O<sub>3</sub>などのような、材料としての誘電率の高いものを用いることが考えられる。しかしながら、これらの誘電率の高い材料を用いて薄膜状態で高誘電率を得ようとすると、MOCVD法などの成膜方法を用い、高温成膜で薄膜の結晶性

50

を向上させる必要があるが、これらの高誘電率を有する材料は固体の昇華を利用したものが多く、積層する際に高誘電率材料を再現性よく得ることが難しい。

#### 【0006】

また、これらの薄膜は機械的強度が低いため、セラミックグリーンシートを積層した従来の積層セラミックコンデンサのようにチップ部品として使用する場合、基板側を配線基板に取り付けようとすると、薄膜側を保持して移動させる必要があり、薄膜積層コンデンサが破損しやすいという問題がある。このような問題を解決するために、基板と反対側の薄膜面に半田バンプを形成し、基板側を保持して配線基板上に薄膜積層コンデンサを移動し、半田バンプで配線基板上に取り付けることが考えられる。

#### 【0007】

しかしながら、薄膜積層コンデンサの小型化、低背化を進めるためには、基板を可能な限り薄くし、半田バンプの厚みもなるべく小さくする必要がある。そのため、実装する際に薄膜積層コンデンサが配線基板に接触すると、外部応力によって基板そのものが破損する可能性がある。さらに、低背化の観点から、半田バンプで支持された薄膜積層コンデンサは、配線基板とほぼ平行の位置関係を保っていることが望ましい。

#### 【0008】

それゆえに、この発明の主たる目的は、小型かつ薄型であって、大容量を得ることができ、配線基板上に実装する際にも破損しにくい薄膜積層コンデンサを提供することである。また、この発明の目的は、このような薄膜積層コンデンサを配線基板上に実装するための薄膜積層コンデンサの実装方法を提供することである。

#### 【0009】

##### 【課題を解決するための手段】

この発明は、基板、および基板に形成された複数の誘電体層と電極層との積層体を含む薄膜積層コンデンサにおいて、電極層は誘電体層によって電気的に分割される第1の電極層と第2の電極層とを含み、電極層の面上において部分的に形成された誘電体層を介して第1の電極層と第2の電極層とが交互に積層され、電極層の面上であって誘電体層が形成されていない部分には導体膜が形成され、誘電体層の形成されていない部分において複数の第1の電極層が互いに電気的に接続されるとともに、誘電体層の形成されていない部分において複数の第2の電極層が互いに電気的に接続され、積層体の基板と反対側の面に、電極層と電気的に接続する3つ以上の外部接続用の半田バンプが形成されたことを特徴とする、薄膜積層コンデンサである。

このような薄膜積層コンデンサにおいて、誘電体層の形成されていない部分において複数の第1の電極層が導体膜を介して互いに電気的に接続されるとともに、誘電体層の形成されていない部分において複数の第2の電極層が導体膜を介して互いに電気的に接続された構造とができる。

また、積層体の面上に開口部を有する保護膜が形成され、開口部において電極層に接続される半田によって半田バンプを形成することができる。

また、この発明は、基板、および基板に形成された複数の誘電体層と電極層との積層体を含む薄膜積層コンデンサにおいて、誘電体層は、少なくともBaまたはSrを含む酸化物薄膜であり、トリエチレンテトラミンあるいはテトラエチレンペニタミンを付加したジピバロイルメタネット錯体を原料としてMOCVD法を用いて成膜されたものであり、積層体の基板と反対側の面に3つ以上の外部接続用の半田バンプが形成されたことを特徴とする、薄膜積層コンデンサである。

また、この発明は、上述のいずれかに記載の薄膜積層コンデンサを配線基板上に実装する薄膜積層コンデンサの実装方法であって、半田バンプが配線基板上の配線に接続されることを特徴とする、薄膜積層コンデンサの実装方法である。

#### 【0010】

基板上に形成された誘電体層と電極層との積層体上に3つ以上の半田バンプを形成することにより、基板と反対側の積層体面を配線基板上に取り付けることができる。そのため、基板側を保持して薄膜積層コンデンサを配線基板上に移動させることができる。また、3

10

20

30

40

50

つ以上の半田バンプを配線基板上の配線に接続することにより、配線基板に平行な状態で薄膜積層コンデンサを実装することができ、実装時の低背化を図ることができる。また、半田バンプにより配線基板に平行な状態で薄膜積層コンデンサを実装することができるため、薄膜積層コンデンサと配線基板との接触を防止することができ、外部応力による薄膜積層コンデンサの破損を防止することができる。

また、誘電体層を介して第1の電極層と第2の電極層とを積層することにより、第1の電極層と第2の電極層との対向面積が大きくなり、大容量のコンデンサとすることができる。

さらに、保護膜を形成することにより、積層体を保護することができる。そして、保護膜に開口部を形成することにより、積層体上に半田をのせることができ、半田バンプとして使用することができる。このとき、開口部および半田バンプは円形に形成することが望ましく、また半田バンプに使用される半田量は厳密に制御されていることが望ましい。

また、誘電体層は、少なくともBaまたはSrを含む材料で形成され、トリエチレンテトラミンあるいはテトラエチレンペニタミンを付加したジピバロイルメタネット錯体[M(DPM)<sub>2</sub>(terane)<sub>2</sub>, M(DPM)<sub>2</sub>(triene)<sub>2</sub>; M = Ba, Sr]を原料としてMOCVD法を用いて成膜する場合、材料の融点以上の温度で使用することができ、通常のバーリング法を用いて気化搬送することが可能となる。それにより、誘電体の成膜時に再現性が向上し、高誘電率薄膜を積層することが可能となる。

さらに、このような薄膜積層コンデンサを用いて、半田バンプで配線基板上に取り付けることにより、基板側を保持して移動させることができるために、薄膜積層コンデンサの破損を防ぐことができる。

#### 【0011】

この発明の上述の目的、その他の目的、特徴および利点は、図面を参照して行う以下の発明の実施の形態の詳細な説明から一層明らかとなろう。

#### 【0012】

##### 【発明の実施の形態】

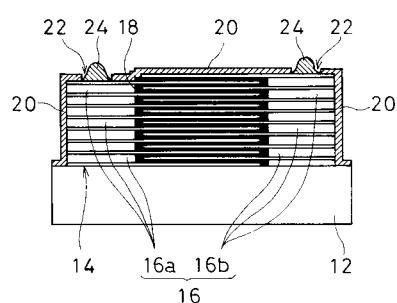

図1は、この発明の薄膜積層コンデンサの一例を示す断面図解図である。薄膜積層コンデンサ10は、基板12を含む。基板12としては、たとえばサファイアR面基板などが用いられる。基板12上には、積層体14が形成される。積層体14は、電極層16と誘電体層18とを積層することによって形成される。電極層16としては、たとえばPtなどが用いられ、スパッタリング法などによって形成される。また、誘電体層18としては、少なくともBaまたはSrを含む酸化物薄膜が用いられ、たとえば(Ba, Sr)TiO<sub>3</sub>などが用いられる。この誘電体層18は、MOCVD法などによって形成される。電極層16は、誘電体層18によって分割された複数の第1の電極層16aと複数の第2の電極層16bとで形成されている。

#### 【0013】

第1の電極層16aは基板12の長さ方向の一方側に形成され、第2の電極層16bは基板12の長さ方向の他方側に形成される。そして、基板12の中央部において、誘電体層18を介して第1の電極層16aと第2の電極層16bとが交互に積層される。これらの第1の電極層16aおよび第2の電極層16bは、スパッタリング法などによって複数層形成される。したがって、誘電体層18が形成されていない部分において、複数の第1の電極層16aが互いに電気的に接続され、複数の第2の電極層16bが互いに電気的に接続される。

#### 【0014】

積層体14の外周面には、保護膜20が形成される。保護膜20としては、たとえばシリコン酸化膜などが用いられ、プラズマCVD法などによって形成される。積層体14の基板12と反対側の面上において、保護膜20には、たとえば4つの円形の開口部22が形成される。これらの開口部22によって、第1の電極層16aと第2の電極層16bとが露出し、この部分に半田をのせることにより、半田バンプ24が形成される。このとき、保護膜20の開口部22にのせられる半田の量は、厳しく制御されることが望ましい。

10

20

30

40

50

## 【0015】

このような薄膜積層コンデンサ10では、MOCVD法やスパッタリング法などによって電極層16や誘電体層18を形成することにより、非常に薄い積層体14を得ることができる。このような薄い積層体14を形成する場合には、基板14も薄くすることができ、全体として小型で薄型の薄膜積層コンデンサ10を得ることができる。このように、小型で薄型の薄膜積層コンデンサであっても、誘電体層18を挟んで第1の電極層16aと第2の電極層16bとが交互に積層されることにより、これらの電極層の対向面積が大きくなり、大容量のコンデンサとすることができます。

## 【0016】

また、誘電体層18を作製する際に、少なくともBaまたはSrを含む材料が用いられ、トリエチレンテトラミンあるいはテトラエチレンペニタミンを付加したジピバロイルメタネト錯体を原料とすることにより、融点以上の温度で使用することができ、通常のバブリング法を用いて気化搬送することが可能となる。そのため、誘電体成膜時の再現性が向上し、高誘電率薄膜を積層することが可能となる。

10

## 【0017】

さらに、積層体14上に半田バンプ24が形成されているため、この半田バンプ24を配線基板上に形成された配線に接続して、薄膜積層コンデンサ10を配線基板に実装することができる。したがって、実装時において、基板12側を保持して薄膜積層コンデンサ10を移動させることができ、移動時における積層体14の破損を防ぐことができる。このような基板12側を保持した移動が可能であるため、マウントの自動化も容易である。

20

## 【0018】

また、半田バンプ24が4つ形成されることにより、薄膜積層コンデンサ10と配線基板とを平行な位置関係となるように、薄膜積層コンデンサ10を実装することができる。そのため、薄膜積層コンデンサ10を実装したときに、低背化を図ることができる。さらに、薄膜積層コンデンサ10と配線基板とを平行にすることができるため、薄膜積層コンデンサ10が配線基板に接触することを防止することができ、外部応力による薄膜積層コンデンサ10の破損を防ぐことができる。

## 【0019】

## 【実施例】

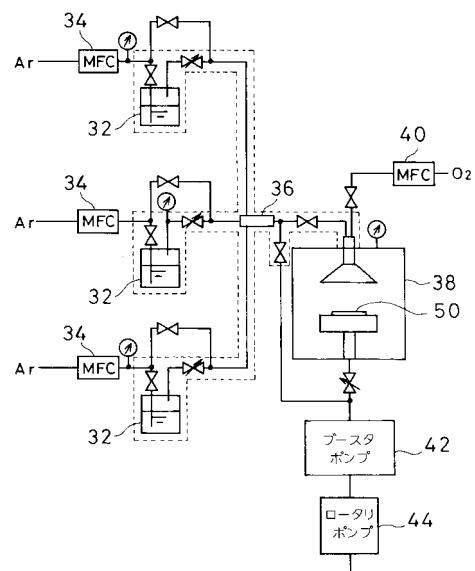

(Ba, Sr)TiO<sub>3</sub>薄膜(以後、BST薄膜という。)を作製するため、図2に示すようなMOCVD装置30を準備した。MOCVD装置30は、3つの原料タンク32を含み、ここに原料融液が充填される。これらの原料タンク32には、マスフローコントローラ34を介して、搬送ガスとしてのArガスが送り込まれる。搬送ガスによって原料融液は気化し、混合器36に搬送されて混合される。混合された原料は、成膜チャンバ38内に送り込まれる。このとき、マスフローコントローラ40を介して、O<sub>2</sub>ガスも送り込まれる。成膜チャンバ38内は、ブースタポンプ42およびロータリポンプ44によって低圧状態にされる。この状態で、基板50に混合材料ガスが当てられることにより、基板50上にBST薄膜が形成される。なお、原料タンク32から成膜チャンバ38までの点線で囲まれた部分は高温に保たれ、原料が気化した状態のまま成膜チャンバ38まで搬送される。

30

## 【0020】

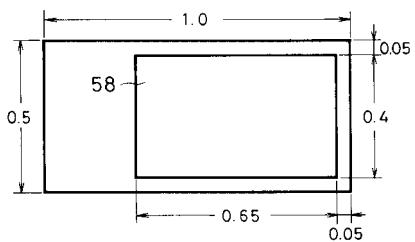

このMOCVD装置30を用いて、BST薄膜を形成するため、厚さ0.1mm、2インチ角のサファイアR面基板を準備した。そして、表1に示す条件で、メタルマスクを用いて、図3に示すようなパターンのBST薄膜52を形成した。成膜時間は75分で、膜厚は120nmである。なお、図3において、点線は切断部を示し、切りしろは0.1mmである。また、図3～図7中に記載されている寸法の単位はmmである。

40

## 【0021】

## 【表1】

|                     |                                                      |

|---------------------|------------------------------------------------------|

| Ba原料                | Ba (DPM) <sub>2</sub> (tetraene) <sub>2</sub>        |

| Ba気化器温度             | 120°C                                                |

| Ba気化器キャリアガス (Ar) 流量 | 100CCM                                               |

| Sr原料                | Sr (DPM) <sub>2</sub> (triene) <sub>2</sub>          |

| Sr気化器温度             | 110°C                                                |

| Sr気化器キャリアガス (Ar) 流量 | 50CCM                                                |

| Ti原料                | Ti (O-i-C <sub>3</sub> H <sub>7</sub> ) <sub>4</sub> |

| Ti気化器温度             | 40°C                                                 |

| Ti気化器キャリアガス (Ar) 流量 | 25CCM                                                |

| O <sub>2</sub> ガス流量 | 700CCM                                               |

| 気化器温度               | 150°C                                                |

| 成膜温度                | 650°C                                                |

| 成膜チャンバ圧力            | 1.3 kPa                                              |

| 成膜時間                | 75分                                                  |

## 【0022】

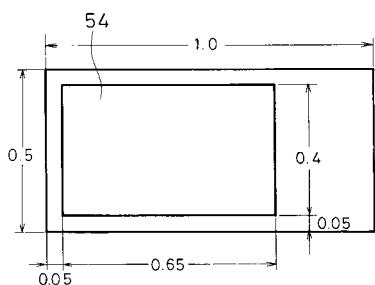

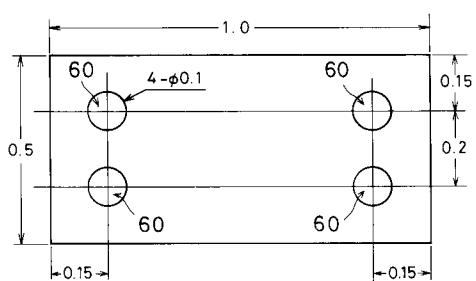

なお、BST薄膜52を成膜する前に、図4に示すパターンで、スパッタリング法によってPt膜54を形成した。なお、図4～図7については、図3の点線で示された切断部で切断した後の寸法を示してある。Pt成膜に使用したのはRFスパッタ装置であり、成膜時間は100秒で、膜厚は約150nmである。

## 【0023】

## 【表2】

|       |                           |

|-------|---------------------------|

| 成膜前圧力 | 6.7 × 10 <sup>-4</sup> Pa |

| 成膜時圧力 | 0.67 Pa                   |

| Ar流量  | 10CCM                     |

| RFパワー | 250W                      |

| 成膜温度  | 70°C                      |

## 【0024】

基板50上に図4に示すようなパターンのPt膜54を形成し、その上に図3に示すよう

10

20

30

40

50

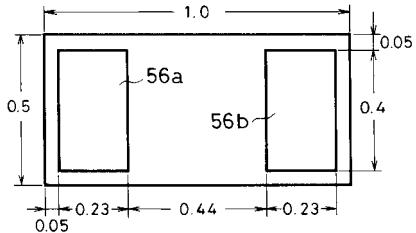

なパターンのB S T 薄膜5 2を形成することにより、切断後の基板5 0の長さ方向の一方側のみにおいて、P t 膜5 4がB S T 薄膜5 2から露出した状態となる。この状態で、図5に示すようなパターンで、表2の条件でP t 膜5 6 a , 5 6 bを形成した。成膜時間は8 0秒で、膜厚はB S T 薄膜5 2と同様に1 2 0 nmになるようにした。したがって、基板5 0の長さ方向の一端側において、P t 膜5 4とP t 膜5 6 aとが電気的に接続される。

#### 【0 0 2 5】

次に、表2に示す条件で、図6に示すようなパターンのP t 膜5 8を形成した。成膜時間は9 0秒である。したがって、切断後の基板5 0の長さ方向の他方側において、P t 膜5 6 bとP t 膜5 8とが電気的に接続される。そして、その上に、図3に示すパターンとなるように、B S T 薄膜5 2を形成した。したがって、基板5 0の長さ方向の一方側でP t 膜5 6 aがB S T 膜5 2から露出し、他方側でP t 膜5 8がB S T 薄膜5 2から露出した状態となる。また、基板5 0の長さ方向の一方側において、P t 膜5 8の端部で下層のB S T 薄膜5 2と上層のB S T 薄膜5 2とが連結される。

#### 【0 0 2 6】

このように、基板5 0上に、P t 膜5 4・B S T 薄膜5 2・P t 膜5 6 a , 5 6 b・P t 膜5 8・B S T 薄膜5 2・・・B S T 薄膜5 2・P t 膜5 6 a , 5 6 bを順次形成し、最後にP t 膜5 4またはP t 膜5 8を形成した。このようにして、1 5層のB S T 薄膜5 2を有する薄膜積層体を作製した。得られた薄膜積層体を酸素雰囲気中において6 5 0で3時間熱処理した。次に、表3に示す条件で、誘電体層および電極層の全面を覆うように、プラズマC V D法を用いて、保護膜としてシリコン酸化膜を成膜した。

#### 【0 0 2 7】

#### 【表3】

|                     |                                                            |

|---------------------|------------------------------------------------------------|

| S i 原料              | TEOS (S i (OC <sub>2</sub> H <sub>5</sub> ) <sub>4</sub> ) |

| TEOS流量              | 1 0 0 C C M                                                |

| O <sub>2</sub> ガス流量 | 5 0 0 0 C C M                                              |

| 基板温度                | 3 5 0 °C                                                   |

| チャンバ圧力              | 6 6 7 P a                                                  |

| 膜厚                  | 2 0 0 nm                                                   |

10

20

30

#### 【0 0 2 8】

さらに、図7に示す4つの開口部6 0を有するレジストを形成し、イオントリミングにより、開口部のシリコン酸化膜を取り除き、図3の点線部分でカットした。そののち、シリコン酸化膜を取り除いた部分に半田をのせ、半田バンプを形成した。その結果、図1に示すような構造の薄膜積層コンデンサを3 7 3 5個得ることができた。

40

#### 【0 0 2 9】

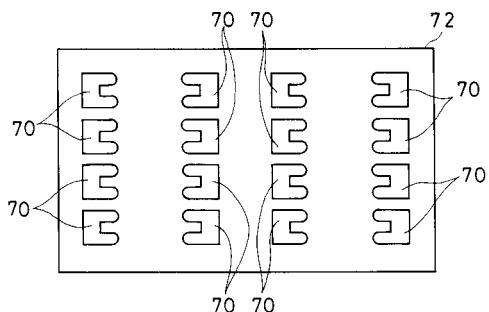

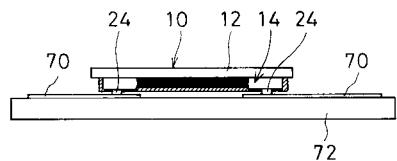

次に、図8に示すように配線層7 0をメタライズした配線基板7 2を準備した。この配線基板7 2では、薄膜積層コンデンサの半田バンプに対応する間隔で配線層7 0が形成されている。そして、図9に示すように、リフロー半田を用いて、薄膜積層コンデンサを配線層7 0に接合した。このようにして、1 0 0個の薄膜積層コンデンサを配線基板7 2に接合し、1 k H zにおける静電容量およびt a n<sup>-1</sup>を測定した。その結果を表4に示す。

#### 【0 0 3 0】

#### 【表4】

50

|               |     |               |

|---------------|-----|---------------|

| 静電容量          | 平均値 | 0. 11 $\mu$ F |

|               | CV値 | 2. 5%         |

| $\tan \delta$ | 平均値 | 1. 5%         |

|               | CV値 | 2. 2%         |

| ショート率         |     | 3%            |

10

## 【0031】

表4からわかるように、B S T薄膜が15層の薄膜積層コンデンサで、0.1  $\mu$ F以上の静電容量が得られている。また、この特性値からB S T薄膜の比誘電率を算出すると、600以上となり、高誘電率のB S T膜が再現性よく得られていることがわかる。

## 【0032】

また、この薄膜積層コンデンサを配線基板に接合した場合の高さは約0.12mmであり、非常に低背なコンデンサが得られている。この薄膜積層コンデンサのB S T薄膜層を1層増やしても、全体としての厚みは270nm増えるにすぎず、さらに積層数を増やすことにより、大容量の薄膜積層コンデンサを得ることが可能になる。

20

## 【0033】

## 【発明の効果】

この発明によれば、小型かつ薄型で、大容量の薄膜積層コンデンサを得ることができる。また、この薄膜積層コンデンサを配線基板上に実装する際に、基板側を保持して配線基板上に移動させることができ、移動時の薄膜積層コンデンサの破損を防止することができる。さらに、薄膜積層コンデンサと配線基板とが接触することなく、平行な位置関係で実装することができ、外部応力による薄膜積層コンデンサの破損を防止することができる。

## 【図面の簡単な説明】

【図1】この発明の薄膜積層コンデンサの一例を示す断面図解図である。

30

【図2】この発明の薄膜積層コンデンサを作製するためのM O C V D装置を示す図解図である。

【図3】実施例において作製するB S T薄膜のパターンを示す図である。

【図4】実施例において作製するP t膜のパターンの1つを示す図である。

【図5】実施例において作製するP t膜のパターンの他の1つを示す図である。

【図6】実施例において作製するP t膜のさらに他の1つを示す図である。

【図7】実施例において作製する保護膜の成膜パターンを示す図である。

【図8】実施例で作製した薄膜積層コンデンサを実装する配線基板上の配線層パターンを示す平面図である。

【図9】図8に示す配線基板に薄膜積層コンデンサを実装したときの正面図解図である。

40

## 【符号の説明】

10 薄膜積層コンデンサ

12 基板

14 積層体

16 電極層

16 a 第1の電極層

16 b 第2の電極層

18 誘電体層

20 保護膜

22 開口部

50

## 24 半田バンプ

【図1】

10

【図2】

30

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開平05-129149(JP,A)

特開平11-097289(JP,A)

特開平11-067829(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01G 4/252

H01G 4/30

H01G 4/33

H01L 21/60