(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5917618号

(P5917618)

(45) 発行日 平成28年5月18日(2016.5.18)

(24) 登録日 平成28年4月15日(2016.4.15)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 23/52  | (2006.01) |

| HO 1 L 27/12  | (2006.01) |

| HO 1 L 21/02  | (2006.01) |

| HO 1 L 21/336 | (2006.01) |

| HO 1 L 29/786 | (2006.01) |

| HO 1 L        | 27/12     |

| HO 1 L        | 27/12     |

| HO 1 L        | 29/78     |

| HO 1 L        | 27/08     |

| HO 1 L        | 27/08     |

請求項の数 2 (全 12 頁) 最終頁に続く

|              |                                   |                 |           |

|--------------|-----------------------------------|-----------------|-----------|

| (21) 出願番号    | 特願2014-142057 (P2014-142057)      | (73) 特許権者       | 000153878 |

| (22) 出願日     | 平成26年7月10日 (2014.7.10)            | 株式会社半導体エネルギー研究所 |           |

| (62) 分割の表示   | 特願2010-99455 (P2010-99455)<br>の分割 | 神奈川県厚木市長谷398番地  |           |

| 原出願日         | 平成22年4月23日 (2010.4.23)            | (72) 発明者        | 三上 真弓     |

| (65) 公開番号    | 特開2014-222766 (P2014-222766A)     | 神奈川県厚木市長谷398番地  | 株式会社      |

| (43) 公開日     | 平成26年11月27日 (2014.11.27)          | 半導体エネルギー研究所内    |           |

| 審査請求日        | 平成26年7月11日 (2014.7.11)            | (72) 発明者        | 泉 小波      |

| (31) 優先権主張番号 | 特願2009-108129 (P2009-108129)      | 神奈川県厚木市長谷398番地  | 株式会社      |

| (32) 優先日     | 平成21年4月27日 (2009.4.27)            | 半導体エネルギー研究所内    |           |

| (33) 優先権主張国  | 日本国 (JP)                          | 審査官             | 右田 勝則     |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、タングステンまたはモリブデンを有する第1の層を形成し、

前記第1の層上に、酸化珪素を有する第2の層を形成し、

前記第2の層上に、半導体素子を形成し、

前記半導体素子上に、絶縁層を形成し、

前記絶縁層を貫通し、前記第1の層に達する開口部を形成し、

前記開口部内部において露出した前記第1の層を酸化し、

前記絶縁層上及び前記開口部内部に、前記半導体素子と電気的に接続される配線を形成した後、

前記基板から前記半導体素子と前記絶縁層と前記配線とを分離し、前記開口部の底部において前記配線の一部の領域を露出させ、

前記領域と接するように、異方性導電接着材を設けることを特徴とする半導体装置の作製方法。

## 【請求項 2】

基板上に、タングステンまたはモリブデンを有する第1の層を形成し、

前記第1の層上に、酸化珪素を有する第2の層を形成し、

前記第2の層上に、半導体素子を形成し、

前記半導体素子上に、絶縁層を形成し、

前記絶縁層を貫通し、前記第1の層に達する開口部を形成し、

10

20

前記開口部内部において露出した前記第1の層を酸化し、

前記絶縁層上及び前記開口部内部に、前記半導体素子と電気的に接続される配線を形成

した後、

前記基板から前記半導体素子と前記絶縁層と前記配線とを分離し、前記開口部の底部に

おいて前記配線の一部の領域を露出させることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書に開示される発明は、半導体装置の作製方法に関する。

【背景技術】

【0002】

近年、絶縁基板上に設けられた半導体素子を転置する技術開発が進められている。このような技術として、例えば半導体素子と絶縁基板の間に分離層を設けて、当該分離層を除去することにより、半導体素子を絶縁基板から分離する技術がある（特許文献1及び特許文献2参照）。

【0003】

また分離した薄膜集積回路を積層して、3次元化された半導体装置を作製する技術がある（特許文献3参照）。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006-121062号公報

【特許文献2】特開2007-280368号公報

【特許文献3】特開平8-254686号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上述のような分離工程を用いて分離した半導体素子を、別の素子に積層及び電気的に接続させるには、分離工程で外部への接続配線を露出させなければならない。接続配線を露出させるには、分離層と接続配線との界面で分離させる必要がある。

【0006】

しかしながら、特に分離層と接続配線に金属膜を用いた場合、分離層と接続配線が密着性が強く、分離層と接続配線が分離しない恐れがある。また分離したとしても、分離した表面に接続配線が露出しない恐れがある。

【0007】

また分離層と接続配線が密着性が強いと、半導体素子全体が基板から分離しない恐れがある。また分離したとしても、分離した表面に接続配線が露出しないので、別の素子を積層しても、電気的に接続できない恐れがある。そのため、立体的に作製された半導体装置を作製できない恐れがある。

【課題を解決するための手段】

【0008】

接続配線を形成するために、絶縁層にまずスルーホールを形成する。そしてスルーホールの底面に分離層を露出させる。次いでスルーホール底部に露出した分離層に酸化工程を行う。これにより、露出した分離層表面と、接続配線との密着性を弱めることができる。

【0009】

またスルーホール底部に露出した分離層への酸化工程によって、分離層表面と接続配線との密着性を弱めると、半導体素子全体を基板から完全に分離させることができる。このような接続配線を有する半導体素子層を積層させることによって、3次元化された半導体装置を作製することが可能である。

【0010】

10

20

30

40

50

第1の基板上に、互いに密着性の弱い第1の層と第2の層を形成する。前記第2の層上に、第1の半導体素子層及び第1の絶縁層を形成する。前記第1の絶縁層中に、前記第1の層に達するスルーホールを形成する。前記スルーホール底部に露出した第1の層を酸化させる。前記第1の絶縁層上及び前記スルーホール内部に、前記第1の半導体素子層と電気的に接続される配線を形成する。前記第1の層と第2の層を分離する。これにより、前記第1の基板から、前記第2の層、前記第1の半導体素子層、前記第1の絶縁層、前記配線を分離して配線を露出させる。以上のようにして作製されることを特徴とする半導体装置の作製方法に関する。

#### 【0011】

第1の基板上に、互いに密着性の弱い第1の層と第2の層を形成する。前記第2の層上に、第1の半導体素子層及び第1の絶縁層を形成する。前記第1の絶縁層中に、前記第1の層に達するスルーホールを形成する。前記スルーホール底部に露出した第1の層を酸化させる。前記第1の絶縁層上及び前記スルーホール内部に、前記第1の半導体素子層と電気的に接続される配線を形成する。前記第1の層と第2の層を分離することにより、前記第1の基板から、前記第2の層、前記第1の半導体素子層、前記第1の絶縁層、前記配線を分離して配線を露出させる。さらに、第2の基板上に、互いに密着性の弱い第3の層と第4の層を形成する。前記第4の層上に、第2の半導体素子層を形成する。前記第3の層と第4の層を分離することにより、前記第2の基板から、前記第4の層、前記第2の半導体素子層を分離する。前記第2の半導体素子層と前記配線との間に、異方性導電接着剤を設ける。前記第1の半導体素子層と前記第2の半導体素子層は、前記異方性導電接着剤及び前記配線によって電気的に接続されている。以上のようにして作製されることを特徴とする半導体装置の作製方法に関する。

10

#### 【0012】

前記第1の層及び前記第3の層のそれぞれは、タンゲステン膜であり、前記第2の層及び前記第4の層それぞれは、酸化珪素膜である。

#### 【0013】

前記酸化工程は、過酸化水素水に浸す工程、あるいは、酸素プラズマを照射する工程である。

#### 【発明の効果】

#### 【0014】

分離工程において、不完全な分離を抑制することができ、半導体装置の信頼性が低下することを抑制することができる。

30

#### 【図面の簡単な説明】

#### 【0015】

【図1】半導体装置の作製工程を示す断面図。

【図2】半導体装置の作製工程を示す断面図。

【図3】半導体装置の作製工程を示す断面図。

【図4】半導体装置の作製工程を示す断面図。

【図5】半導体装置の作製工程を示す断面図。

【図6】分離工程の状態を示す図。

40

【図7】分離工程の状態を示す図。

【図8】半導体装置の作製工程を示す断面図。

【図9】半導体装置の作製工程を示す断面図。

#### 【発明を実施するための形態】

#### 【0016】

以下、本明細書に開示された発明の実施の態様について、図面を参照して説明する。但し、本明細書に開示された発明は多くの異なる態様で実施することができる、本明細書に開示された発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な

50

機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0017】

なお本明細書に開示された発明において、半導体装置とは、半導体を利用することで機能する素子及び装置全般を指し、電子回路、表示装置、発光装置等を含む電気装置およびその電気装置を搭載した電子機器をその範疇とする。

【0018】

[実施の形態1]

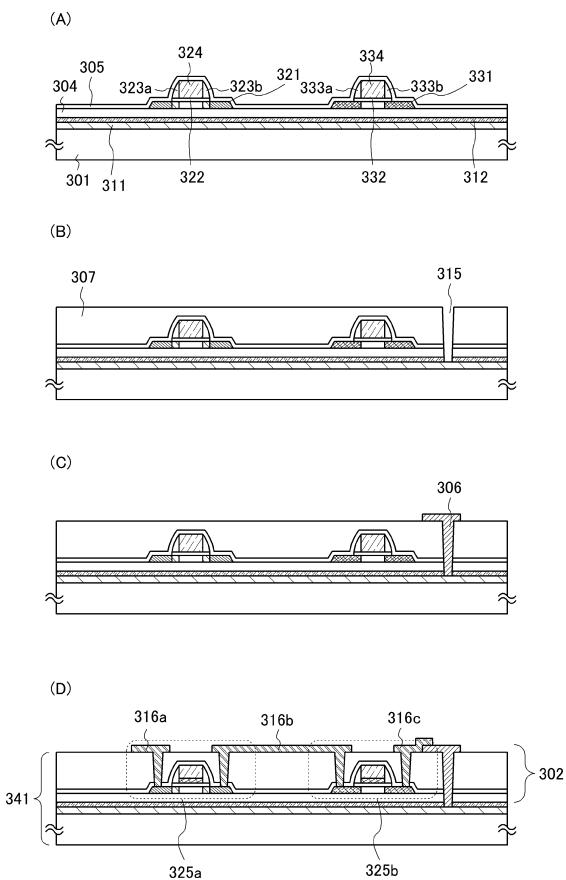

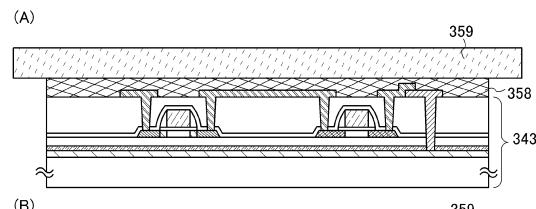

本実施の形態を、図1(A)～図1(D)、図2(A)～図2(C)を用いて説明する。

【0019】

まず、基板301上に、互いに密着性の弱い第1の層311及び第2の層312を積層する。後述する基板301と半導体素子層302の分離工程は、第1の層311と第2の層312を界面から分離することにより行われる。

【0020】

第1の層311及び第2の層312は、例えば、金属膜と酸化珪素膜などが挙げられる。具体的には、第1の層311としてタンゲステン膜やモリブデン膜、第2の層312として酸化珪素膜を、スパッタリング法により成膜してもよい。また、成膜時は密着性が低くなくても、成膜後に処理を加えることにより、密着性が低下する膜の組み合わせでもよい。例えば、第1の層311として非晶質珪素膜及び第2の層312として酸化珪素膜を積層し、成膜後に加熱または基板301の裏面からレーザビームを照射すると、非晶質珪素膜が結晶化され、結晶化された珪素膜と酸化珪素膜の密着性が低下する。

【0021】

次に、第1の層311及び第2の層312上に、下地層304、島状半導体膜321、ゲート絶縁膜322、ゲート電極324、サイドウォール323a、サイドウォール323b、島状半導体膜331、ゲート絶縁膜332、ゲート電極334、サイドウォール333a、サイドウォール333bを形成する。島状半導体膜321及び島状半導体膜331には、それぞれ一導電型を付与する不純物元素が含まれており、必要に応じてチャネル形成領域、高濃度不純物領域、低濃度不純物領域が形成される。

【0022】

島状半導体膜321、ゲート絶縁膜322、ゲート電極324、サイドウォール323a、サイドウォール323b、島状半導体膜331、ゲート絶縁膜332、ゲート電極334、サイドウォール333a、サイドウォール333bを覆って、保護層305が形成される(図1(A)参照)。

【0023】

保護層305上に、絶縁膜307が形成される。また、第2の層312、下地層304、保護層305、絶縁膜307の積層中に、スルーホール315を形成する。

【0024】

ここで、スルーホール315が第1の層311まで貫通してしまうと、後に分離工程が行えなくなる恐れがある。そのため、第1の層311を除去しないようにスルーホール315を形成する。

【0025】

次に、スルーホール315の底面に露出している第1の層311の表面を酸化させる。第1の層311の表面を酸化させるためには、過酸化水素水等の酸化力を有する溶液に浸す、あるいは、酸素プラズマを照射する(「O<sub>2</sub>アッシング」ともいう)等の方法を用いればよい。特にスルーホール315の底面の径が小さい場合は、過酸化水素水等の酸化力を有する溶液がスルーホール315の内部に進入しない恐れがあるため、酸素プラズマを照射することが望ましい(図1(B)参照)。

【0026】

次いで、スルーホール315を介して第1の層311に接する配線306を形成する(図1(C)参照)。配線306はアルミニウム、チタンとアルミニウムの積層、銅のいずれ

10

20

30

40

50

かを含んでよい

【0027】

次に、保護層305及び絶縁膜307中に、島状半導体膜321及び島状半導体膜331に達するコンタクトホールを形成する。コンタクトホールを介して、島状半導体膜321に接する配線316a及び配線316b、並びに、島状半導体膜331に接する配線316b及び配線316cが形成される。なお、配線316cは、配線306と電気的に接続されている。

【0028】

以上により、島状半導体膜321、ゲート絶縁膜322、ゲート電極324、サイドウォール323a、サイドウォール323b、配線316a、配線316bを有する薄膜トランジスタ(Thin Film Transistor(TFT))325a、並びに、島状半導体膜331、ゲート絶縁膜332、ゲート電極334、サイドウォール333a、サイドウォール333b、配線316b、配線316cを有するTFT325bが形成される。本実施の形態では、下地層304、TFT325a、TFT325b、保護層305、絶縁膜307の積層を半導体素子層302と呼ぶ。また、基板301及び半導体素子層302を総じて、積層構造体341と呼ぶこととする(図1(D)参照)。

【0029】

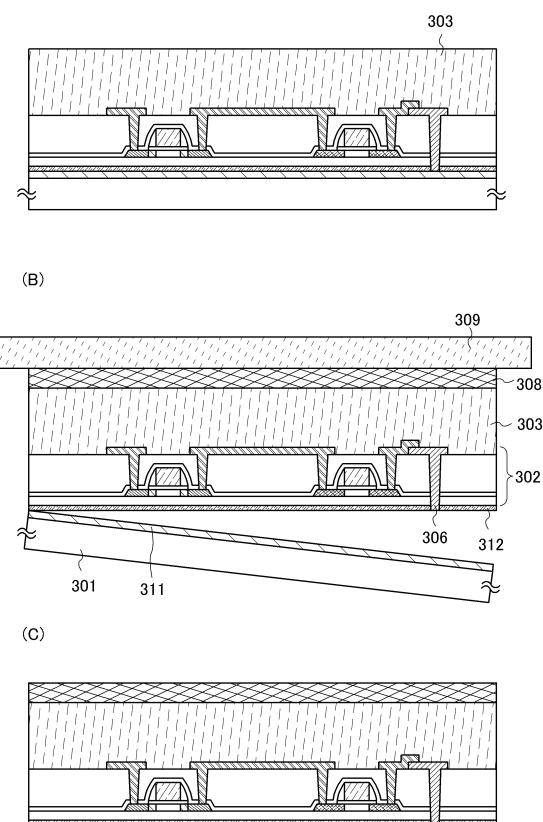

次に、半導体素子層302上に平坦化膜303を形成する(図2(A)参照)。平坦化膜303は、例えばエポキシ樹脂のような有機樹脂を用いればよい。

【0030】

次いで平坦化膜303の表面上に、後の工程で除去可能な支持基板309を、接着剤308を用いて貼り合わせる。

【0031】

支持基板309として、柔軟性のあるフレキシブル基板を用いると、基板301から半導体素子層302等を分離する際に、半導体素子層302等を傷つけることなく効率よく工程を進めることができる。また、接着剤308は、熱可塑性樹脂や光可塑性樹脂を用いることができる。

【0032】

次いで、半導体素子層302及び配線306を基板301から分離させる工程を行う(図2(B)参照)。この分離工程は、第1の層311と第2の層312を、第1の層311と第2の層312の界面から分離することから行われる。第1の層311は基板301に残留し、第2の層312は剥離された半導体素子層302側に付着する。このようにして半導体素子層302及び配線306を基板301から分離すると、基板301と接していた面には、配線306が露出していることになる。

【0033】

次いで支持基板309を除去する(図2(C))。可能であれば接着剤308も除去してもよい。

【0034】

以上の作製工程により、配線306を露出させた半導体装置を作製することができる。

【0035】

[実施の形態2]

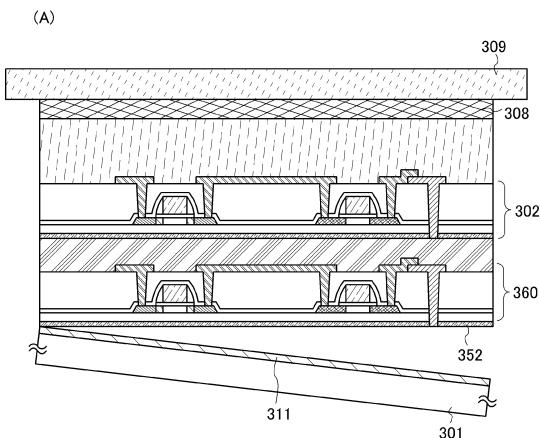

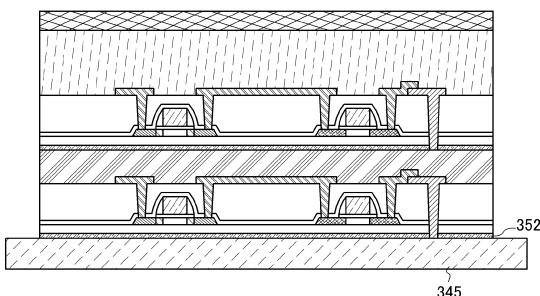

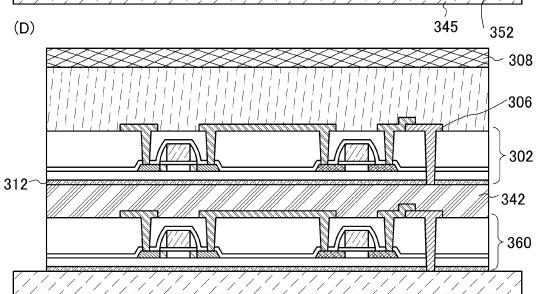

本実施の形態を、図3(A)～図3(B)、図8(A)～図8(B)、図9(A)～図9(D)を用いて説明する。

【0036】

まず実施の形態1の図1(A)～図1(D)、図2(A)～図2(B)に述べる作製工程に基づいて、半導体素子層302及び配線306を基板301から分離させる工程を行う。なお図3(A)と図2(B)は同じ図面である。

【0037】

次いで、分離した第2の層312、半導体素子層302、配線306を、新たに積層構造体343とアニソルム等の異方性導電接着剤342を用いて貼り合わせる(図3(B))

10

20

30

40

50

参照)。積層構造体343は図1(D)や図3(B)に示す積層構造体341と同一でも異なるっていても良い。以上の工程により、半導体素子層302と、新しく貼り合わせた積層構造体343中の半導体素子層360は、異方性導電接着剤342により電気的に接続される。ただし、新たな積層構造体343が最下層に配置される場合は、スルーホール355、配線356は形成しなくてもよい。

【0038】

次いで、新しく貼り合わせた積層構造体343中の第1の層351及び第2の層352を、それらの界面から分離することにより、新しく貼り合わせた積層構造体343中の基板350及び第1の層351と、第2の層352、半導体素子層302、360の積層体、接着剤308、支持基板309を分離する(図8(A)参照)。

10

【0039】

露出した第2の層352をフレキシブル基板345と貼り合わせ、支持基板309を分離する(図8(B)参照)。

【0040】

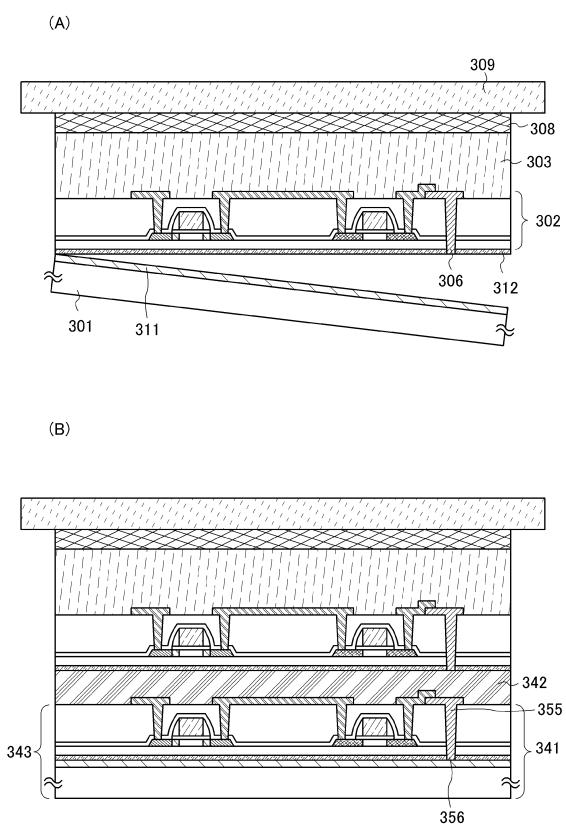

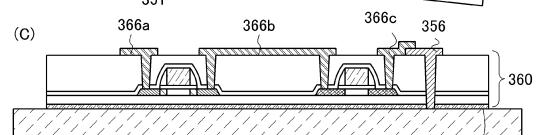

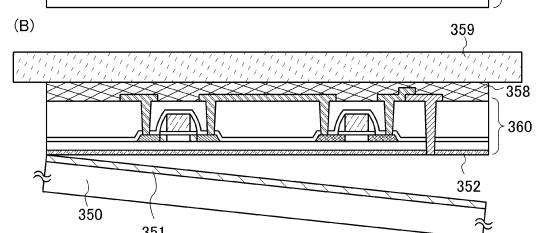

あるいは、別の作製方法で図8(B)に示す構造と同様の構造を得る方法を以下に述べる。まず、新たに積層構造体343を作製し、積層構造体343上に、接着剤358及び支持基板359を設ける(図9(A)参照)。

【0041】

次いで、積層構造体343中の基板350及び第1の層351と、第2の層352、半導体素子層360、接着剤358、支持基板359を分離する(図9(B)参照)。

20

【0042】

分離した第2の層352、半導体素子層360、接着剤358、支持基板359から、接着剤358及び支持基板359を除去し、配線366a、配線366b、配線366c、配線356を露出させる。次いで、第2の層352をフレキシブル基板345に貼り合わせる。

【0043】

次いで、図2(A)の工程で基板301及び第1の層311を分離した、第2の層312、半導体素子層302、配線306、接着剤308と、新たに作製したフレキシブル基板345、第2の層352、半導体素子層360、配線356を、異方性導電接着剤342で貼り合わせることにより、図9(D)に示す半導体装置を作製してもよい。なお図9(D)と図8(B)は同じ図面である。

30

【0044】

以上により配線306により互いに電気的に接続された半導体素子を有する3次元化された半導体装置を作製することができる。

【実施例1】

【0045】

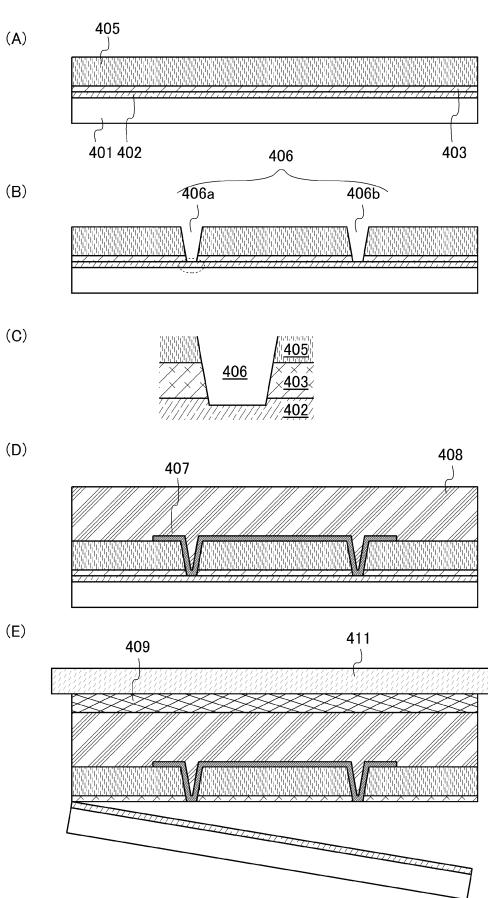

本実施例を、図4(A)～図4(E)、図5(A)～図5(B)、図6(A)～図6(B)、図7(A)～図7(B)を用いて説明する。

【0046】

まず基板401上に第1の層402、第2の層403、絶縁層405を形成する(図4(A)参照)。本実施例では、第1の層402として、タングステン膜をスパッタ法にて形成する。また、第2の層403として酸化珪素膜を形成する。さらに絶縁層405として、酸素を含む窒化珪素膜及び酸化珪素膜を積層した積層膜を用いる。

40

【0047】

絶縁層405及び第2の層403にスルーホール406a及びスルーホール406bを、ドライエッチング法にて形成する。本実施例では、スルーホール406a及びスルーホール406bを総じて、スルーホール406と呼ぶこととする。

【0048】

スルーホール406底面に露出している第1の層402に、酸化工程としてO<sub>2</sub>アッシングを行う。これにより、スルーホール406底面に露出している第1の層402の一部

50

が除去される（図4（C）参照）。

【0049】

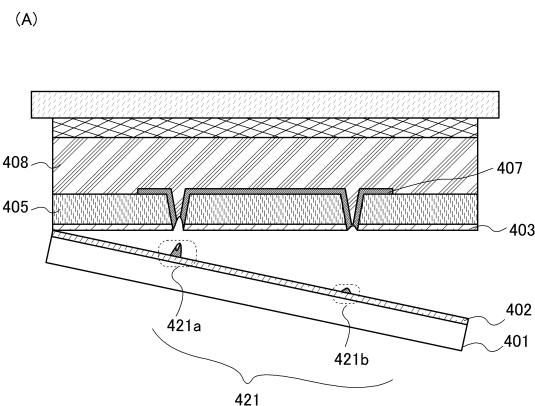

絶縁層405上及びスルーホール406内部に、配線407を形成する。次いで絶縁層405及び配線407上に、絶縁層408を形成する（図4（D）参照）。

【0050】

絶縁層408上に平坦化膜409を形成し、平坦化膜409上に後に除去できる支持基板411を貼り合わせる。次いで、絶縁層405、配線407、絶縁層408、平坦化膜409、支持基板411を、基板401から分離する（図4（E）参照）。この分離工程は、第1の層402と第2の層403の界面を分離することにより行われる。

【0051】

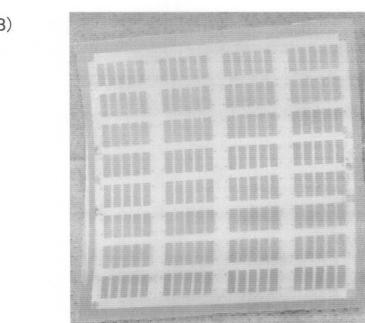

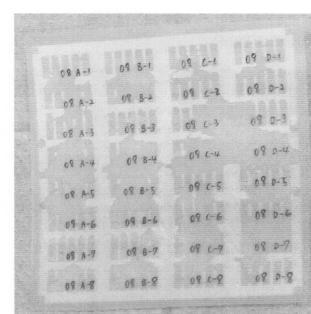

ここで、O<sub>2</sub>アッシングを行ってから分離工程を行ったものと、O<sub>2</sub>アッシングを行わないで分離工程を行ったものを比較したものを、図6（A）～図6（B）に示す。

【0052】

図6（A）に示す基板にはO<sub>2</sub>アッシングを行わないで分離工程を行い、図6（B）に示す基板にはO<sub>2</sub>アッシングを行った後分離工程を行っている。図6（A）に示す基板には、分離がうまくいかず、基板上に分離すべき材料が残ってしまった領域が存在することが分かる。

【0053】

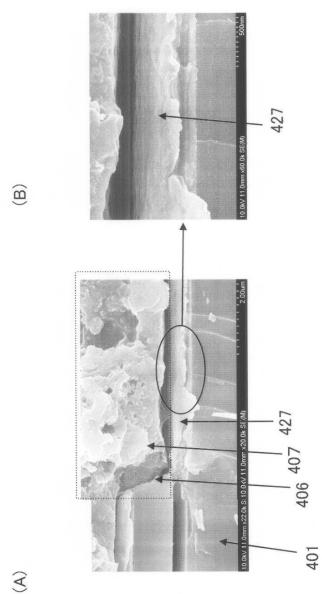

分離工程において、第1の層402と配線407の分離が行われないと、配線407の一部と共に、配線407の周りに存在する絶縁層408の一部が、第1の層402に貼り付いたまま基板401側に残ってしまう（図5（A）参照）。

【0054】

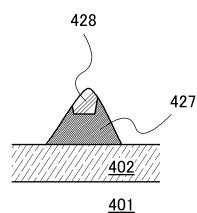

図5（A）では、第1の層402に貼り付いた配線407の一部を領域421b、第1の層402に貼り付いた配線407の一部及び絶縁層408の一部を領域421aとし、領域421a及び領域421bを総じて領域421とする。領域421aの拡大図を図5（B）に示す。領域421aには、配線407の一部である配線427、絶縁層408の一部である絶縁層428が含まれている。このように、本来分離されるべき配線427及び絶縁層428が基板401上に残ってしまうため、素子として機能しない恐れがある。

【0055】

図7（A）及び図7（B）に、O<sub>2</sub>アッシングを行なわず、分離工程で分離できずに基板401上に残った領域のSEM写真を示す。

【0056】

図7（A）において、配線407の一部である配線427が基板401上に残存している。図7（B）は図7（A）の拡大写真であるが、配線427が基板401上に残っていることが鮮明に示されている。

【符号の説明】

【0057】

|      |        |    |

|------|--------|----|

| 301  | 基板     |    |

| 302  | 半導体素子層 |    |

| 303  | 平坦化膜   | 40 |

| 304  | 下地層    |    |

| 305  | 保護層    |    |

| 306  | 配線     |    |

| 307  | 絶縁膜    |    |

| 308  | 接着剤    |    |

| 309  | 支持基板   |    |

| 311  | 第1の層   |    |

| 312  | 第2の層   |    |

| 315  | スルーホール |    |

| 316a | 配線     | 50 |

|         |          |    |

|---------|----------|----|

| 3 1 6 b | 配線       |    |

| 3 1 6 c | 配線       |    |

| 3 2 1   | 島状半導体膜   |    |

| 3 2 2   | ゲート絶縁膜   |    |

| 3 2 3 a | サイドウォール  |    |

| 3 2 3 b | サイドウォール  |    |

| 3 2 4   | ゲート電極    |    |

| 3 2 5 a | T F T    |    |

| 3 2 5 b | T F T    |    |

| 3 3 1   | 島状半導体膜   | 10 |

| 3 3 2   | ゲート絶縁膜   |    |

| 3 3 3 a | サイドウォール  |    |

| 3 3 3 b | サイドウォール  |    |

| 3 3 4   | ゲート電極    |    |

| 3 4 1   | 積層構造体    |    |

| 3 4 2   | 異方性導電接着剤 |    |

| 3 4 3   | 積層構造体    |    |

| 3 4 5   | フレキシブル基板 |    |

| 3 5 0   | 基板       |    |

| 3 5 1   | 第1の層     | 20 |

| 3 5 2   | 第2の層     |    |

| 3 5 5   | スルーホール   |    |

| 3 5 6   | 配線       |    |

| 3 5 8   | 接着剤      |    |

| 3 5 9   | 支持基板     |    |

| 3 6 0   | 半導体素子層   |    |

| 3 6 6 a | 配線       |    |

| 3 6 6 b | 配線       |    |

| 3 6 6 c | 配線       |    |

| 4 0 1   | 基板       | 30 |

| 4 0 2   | 第1の層     |    |

| 4 0 3   | 第2の層     |    |

| 4 0 5   | 絶縁層      |    |

| 4 0 6   | スルーホール   |    |

| 4 0 6 a | スルーホール   |    |

| 4 0 6 b | スルーホール   |    |

| 4 0 7   | 配線       |    |

| 4 0 8   | 絶縁層      |    |

| 4 0 9   | 平坦化膜     |    |

| 4 1 1   | 支持基板     | 40 |

| 4 2 1   | 領域       |    |

| 4 2 1 a | 領域       |    |

| 4 2 1 b | 領域       |    |

| 4 2 7   | 配線       |    |

| 4 2 8   | 絶縁層      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

(B)

【図8】

(B)

【図9】

【図6】

【図7】

---

フロントページの続き

| (51)Int.Cl.              | F I                |

|--------------------------|--------------------|

| H 01 L 21/8234 (2006.01) | H 01 L 27/08 102 E |

| H 01 L 27/088 (2006.01)  | H 01 L 27/00 301 B |

| H 01 L 27/08 (2006.01)   | H 01 L 29/78 613 Z |

| H 01 L 27/00 (2006.01)   |                    |

(56)参考文献 特開2007-318106 (JP, A)

特開2006-121062 (JP, A)

特開2007-059890 (JP, A)

特開2006-245544 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 23 / 52

H 01 L 21 / 02

H 01 L 21 / 336

H 01 L 21 / 8234

H 01 L 27 / 00

H 01 L 27 / 08

H 01 L 27 / 088

H 01 L 27 / 12

H 01 L 29 / 786