등록특허 10-2471151

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년11월28일

(11) 등록번호 10-2471151

(24) 등록일자 2022년11월22일

- (51) 국제특허분류(Int. Cl.)

*G06F 3/06* (2006.01) *G06F 13/16* (2006.01)

- (52) CPC특허분류

*G06F 3/0629* (2013.01)

*G06F 13/1668* (2013.01)

- (21) 출원번호 10-2016-0169763

- (22) 출원일자 2016년12월13일

심사청구일자 2021년12월13일

- (65) 공개번호 10-2017-0104112

- (43) 공개일자 2017년09월14일

- (30) 우선권주장

62/303,343 2016년03월03일 미국(US)

15/169,609 2016년05월31일 미국(US)

(56) 선행기술조사문헌

US20010003198 A1

(뒷면에 계속)

전체 청구항 수 : 총 19 항

심사관 : 김종기

## (54) 발명의 명칭 메모리 시스템 및 그것을 제어하는 방법

**(57) 요 약**

본 발명에 따른 메모리 시스템은, 복수의 메모리 장치들을 포함하고, 상기 복수의 메모리 장치들의 각각은 대응하는 쓰기 커밋(write commit) 정책들을 갖는 하나 이상의 메모리 모듈들, 및 상기 하나 이상의 메모리 모듈들에 연결되는 하나 이상의 메모리 제어기들을 포함하고, 상기 하나 이상의 메모리 제어기들은 상기 대응하는 쓰기 커밋 정책들에 따라 상기 복수의 메모리 장치들을 동작하기 위한 구성 가능한 쓰기 동작 프로토콜(configurable write operation protocol)을 가질 수 있다.

**대 표 도 - 도1**

(52) CPC특허분류

*G06F 3/0658* (2013.01)

*G06F 3/0685* (2013.01)

*G06F 3/0688* (2013.01)

(72) 발명자

정, 홍종

미국 캘리포니아주 95032 로스 가토스 칼튼 애비뉴

120 6호

헨손, 크레이그

미국 미네소타주 55316 챔플린 헤너핀 랜딩 740

임선영

경기도 화성시 반월동 산 16번지

김인동

경기도 화성시 반월동 산 16번지

(56) 선행기술조사문헌

US20040243753 A1

US9032162 B1

JP2012146360 A

CN1311509 A

## 명세서

### 청구범위

#### 청구항 1

복수의 메모리 장치들을 각각 포함하고, 상기 복수의 메모리 장치들은 대응하는 쓰기 커밋(write commit) 정책들을 갖는 하나 이상의 메모리 모듈들; 및

상기 하나 이상의 메모리 모듈들에 연결되는 하나 이상의 메모리 제어기들을 포함하고,

상기 하나 이상의 메모리 제어기들은 상기 대응하는 쓰기 커밋 정책들에 따라 상기 복수의 메모리 장치들을 동작하기 위한 구성 가능한 쓰기 동작 프로토콜(configurable write operation protocol)을 가지되,

상기 복수의 메모리 장치들 중 제 1 메모리 장치는 제 1 동작 이후 제 1 쓰기가 확인될 때 정의되는 제 1 쓰기 커밋 정책을 갖고, 그리고

상기 복수의 메모리 장치들 중 제 2 메모리 장치는 상기 제 1 동작 이후 제 2 쓰기가 확인될 때 정의되는 제 2 쓰기 커밋 정책을 갖고, 상기 제 2 쓰기 커밋 정책은 상기 제 1 쓰기 커밋 정책과는 다르고,

상기 제 1 쓰기 커밋 정책은 쓰기 확인 없는 쓰기 동작을 포함하고, 상기 제 1 쓰기 커밋 정책은 상기 제 1 메모리 장치의 SPD 정보의 영역에 저장되는 제 1 쓰기 커밋 데이터에 기초하여 식별되고, 및

상기 제 2 쓰기 커밋 정책은 쓰기 확인을 갖는 다른 쓰기 동작을 포함하고, 상기 제 2 쓰기 커밋 정책은 상기 제 2 메모리 장치의 SPD 정보의 영역에 저장되는 제 2 쓰기 커밋 데이터에 기초하여 식별되는 메모리 시스템.

#### 청구항 2

제 1 항에 있어서,

상기 복수의 메모리 장치들 중에서 상기 제 1 메모리 장치는 상기 제 1 메모리 장치의 메모리 셀들로 직접적으로 쓴 후에 상기 제 1 쓰기가 확인되는 상기 제 1 쓰기 커밋 정책을 갖는 메모리 시스템.

#### 청구항 3

제 2 항에 있어서,

상기 복수의 메모리 장치들 중에서 상기 제 2 메모리 장치는, 휘발성 데이터 버퍼에 쓴 후에, 상기 제 2 쓰기가 확인되는 상기 제 2 쓰기 커밋 정책을 갖는 메모리 시스템.

#### 청구항 4

제 3 항에 있어서,

상기 복수의 메모리 장치들 중에서 제 3 메모리 장치는, 페이지 오픈(page open) 후에 쓰기 확인(write confirmation)을 이용하지 않는 메모리 시스템.

#### 청구항 5

제 1 항에 있어서,

상기 하나 이상의 메모리 제어기들은, 상기 메모리 시스템의 파워-업에서 상기 복수의 메모리 장치들을 위한 SPD(serial presense detect) 정보를 수신하도록 구현되는 메모리 시스템.

#### 청구항 6

제 1 항에 있어서,

상기 하나 이상의 메모리 제어기들은 DDR4(double data rate generation 4) 커맨드를 재사용하도록 구현되고,

상기 DDR4 커맨드는 쓰기 동작 커맨드로써 비휘발성 메모리 장치들을 위해 이용되지 않는 메모리 시스템.

**청구항 7**

제 1 항에 있어서,

상기 하나 이상의 메모리 제어기들은 쓰기 동작 커맨드로써 RFU(reserved for future) 커맨드들 중에서 어느 하나를 이용하도록 구현되는 메모리 시스템.

**청구항 8**

제 1 항에 있어서,

상기 메모리 시스템은 복수의 메모리 모듈들을 포함하고,

동일한 메모리 모듈 내의 상기 복수의 메모리 장치들의 각각은 동일한 쓰기 커밋 정책을 가지고,

상기 동일한 쓰기 커밋 정책은 다른 메모리 모듈 내부의 상기 복수의 메모리 장치들의 쓰기 커밋 정책과 다른 메모리 시스템.

**청구항 9**

제 1 항에 있어서,

상기 하나 이상의 메모리 제어기들은 오픈 페이지(open page) 및 클로즈 페이지(close page) 정책들 모두를 지원하도록 구현되는 메모리 시스템.

**청구항 10**

대응하는 쓰기 커밋 정책들을 갖는 복수의 메모리 장치들을 각각 포함하는 하나 이상의 메모리 모듈들을 구성하는 메모리 시스템을 제어하는 방법에 있어서:

상기 복수의 메모리 장치들 각각의 SPD 정보의 영역에 저장되는 쓰기 커밋 데이터의 리드아웃을 근거로 하여 상기 복수의 메모리 장치들의 각각에 의해 이용되는 쓰기 커밋 정책을 식별하는 단계;

프로세서로부터 쓰기 커맨드를 수신하는 단계;

상기 쓰기 커맨드에 대응하는 상기 복수의 메모리 장치들 중에서 제 1 메모리 장치를 식별하는 단계; 및

상기 제 1 메모리 장치의 쓰기 커밋 정책에 따라 상기 쓰기 커맨드를 실행하는 단계를 포함하되,

상기 복수의 메모리 장치들 중 제 1 메모리 장치는 제 1 동작 이후 제 1 쓰기가 확인될 때 정의되는 쓰기 확인 없는 쓰기 동작을 포함하는 제 1 쓰기 커밋 정책을 갖고, 그리고 상기 복수의 메모리 장치들 중 제 2 메모리 장치는 상기 제 1 동작 이후 제 2 쓰기가 확인될 때 정의되는 쓰기 확인을 갖는 다른 쓰기 동작을 포함하는 제 2 쓰기 커밋 정책을 갖고, 상기 제 2 쓰기 커밋 정책은 상기 제 1 쓰기 커밋 정책과는 다른 방법.

**청구항 11**

제 10 항에 있어서,

상기 복수의 메모리 장치들 중에서 상기 제 1 메모리 장치는, 상기 제 1 메모리 장치의 메모리 셀들에 직접적으로 쓴 후에 상기 제 1 쓰기가 확인되는 상기 제 1 쓰기 커밋 정책을 갖는 방법.

**청구항 12**

제 11 항에 있어서,

상기 복수의 메모리 장치들 중에서 상기 제 2 메모리 장치는, 휘발성 데이터 버퍼에 쓴 후에, 상기 제 2 쓰기가 확인되는 상기 제 2 쓰기 커밋 정책을 갖는 방법.

**청구항 13**

제 12 항에 있어서,

상기 복수의 메모리 장치들 중에서 제 3 메모리 장치는, 페이지 오픈(page open) 후에 쓰기 확인(write

confirmation)을 이용하지 않는 방법.

#### 청구항 14

제 10 항에 있어서,

상기 메모리 시스템은 상기 복수의 메모리 장치들에 연결된 메모리 제어기를 더 포함하고, 그리고

상기 메모리 제어기는 각각의 쓰기 커밋 정책들에 따라 상기 복수의 메모리 장치들을 동작하기 위한 구성 가능한 쓰기 동작 프로토콜을 갖는 방법.

#### 청구항 15

제 14 항에 있어서,

상기 메모리 시스템은 복수의 메모리 모듈들을 포함하고,

동일한 메모리 모듈 내의 상기 복수의 메모리 장치들의 각각은 동일한 쓰기 커밋 정책을 가지고,

상기 동일한 쓰기 커밋 정책은 다른 메모리 모듈 내부의 상기 복수의 메모리 장치들의 쓰기 커밋 정책과 다른 방법.

#### 청구항 16

대응하는 쓰기 커밋 정책들을 갖는 복수의 메모리 장치들을 각각 포함하는 하나 이상의 메모리 모듈들; 및

상기 하나 이상의 메모리 모듈들에 연결되는 하나 이상의 메모리 제어기들을 포함하고,

상기 하나 이상의 메모리 제어기들은,

상기 복수의 메모리 장치들 각각의 SPD 정보의 영역에 저장되는 쓰기 커밋 데이터의 리드아웃을 근거로 하여 상기 복수의 메모리 장치들의 각각에 의해 이용되는 쓰기 커밋 정책을 식별하되,

상기 복수의 메모리 장치들 중에서 제 1 메모리 장치는 제 1 동작 이후 제 1 쓰기가 확인될 때 정의되는 쓰기 확인 없는 쓰기 동작을 포함하는 제 1 쓰기 커밋 정책을 갖고, 그리고 상기 복수의 메모리 장치들 중에서 제 2 메모리 장치는 상기 제 1 동작 이후 제 2 쓰기가 확인될 때 정의되는 쓰기 확인을 갖는 다른 쓰기 동작을 포함하는 상기 제 1 쓰기 커밋 정책과는 다른 제 2 쓰기 커밋 정책을 갖고,

프로세서로부터 쓰기 커맨드를 수신하고,

상기 쓰기 커맨드에 대응하는 상기 복수의 메모리 장치들 중에서 상기 제 1 메모리 장치를 식별하고, 및

상기 제 1 메모리 장치의 상기 제 1 쓰기 커밋 정책에 따라 상기 쓰기 커맨드를 실행하는 메모리 시스템.

#### 청구항 17

제 16 항에 있어서,

상기 복수의 메모리 장치들 중에서 상기 제 1 메모리 장치는 상기 제 1 메모리 장치의 메모리 셀들에 직접적으로 쓴 후에 상기 제 1 쓰기가 확인되는 상기 제 1 쓰기 커밋 정책을 갖는 메모리 시스템.

#### 청구항 18

제 17 항에 있어서,

상기 복수의 메모리 장치들 중에서 상기 제 2 메모리 장치는 휘발성 데이터 버퍼에 쓴 후에 상기 제 2 쓰기가 확인되는 상기 제 2 쓰기 커밋 정책을 갖는 메모리 시스템.

#### 청구항 19

제 18 항에 있어서,

상기 복수의 메모리 장치들 중에서 제 3 메모리 장치는 페이지 오픈 후에 쓰기 확인을 이용하지 않는 메모리 시스템.

## 청구항 20

삭제

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 메모리 시스템 및 그것을 제어하는 방법에 관한 것이다.

#### 배경 기술

[0002] 최근에, 차세대 메인 메모리 인터페이스들은 가변하는 읽기 및 쓰기 타이밍을 갖는 트랜잭션(transaction)에 기반하는 추세이고, 휘발성 혹은 비휘발성 메모리(NVM) 기술들을 이용할 수 있다. 하지만, 이러한 트랜잭션 메모리 채널들에 이용되는 다양한 비휘발성 메모리들은, DIMM(dual-in-line module)로부터 서로 다른 피드백 정보 요구 사항을 가질 수 있고, 서로 다른 쓰기 커밋(write commit) 매커니즘(혹은 프로토콜, 혹은 정책들)을 가질 수 있다. 이러한 쓰기 커밋 매커니즘은, 메모리 셀들에 직접 쓴 후에 쓰기 동작을 확인하는 것, 데이터가 버퍼에 쓰여질 때(다른 하드웨어가 데이터를 메모리 셀들로 쓰기 전에) 쓰기 동작을 확인하는 것, 및 어떤 경우에는 페이지가 오픈 된 후에 쓰기 확인을 제공하지 않는 것을 포함한다. NVM 기술들의 서로 다른 종류에 따라 서로 다른 쓰기 커밋 매커니즘들을 제어하는 방법 없이는, 동일한 메모리 모듈 내에 통합된 서로 다른 NVM 기술들을 갖는 메모리 모듈은 동작하지 않을 수 있다.

#### 발명의 내용

##### 해결하려는 과제

[0003] 본 발명의 목적은 서로 다른 쓰기 커밋 정책들을 갖는 비휘발성 메모리 장치들을 갖는 메모리 모듈이 정상적으로 동작하도록 하는 컴퓨팅 시스템 및 그것의 제어 방법을 제공하는데 있다.

##### 과제의 해결 수단

[0004] 본 발명의 실시 예에 따른 메모리 시스템은, 복수의 메모리 장치들을 포함하고, 상기 복수의 메모리 장치들의 각각은 대응하는 쓰기 커밋(write commit) 정책들을 갖는 하나 이상의 메모리 모듈들, 및 상기 하나 이상의 메모리 모듈들에 연결되는 하나 이상의 메모리 제어기들을 포함하고, 상기 하나 이상의 메모리 제어기들은 상기 대응하는 쓰기 커밋 정책들에 따라 상기 복수의 메모리 장치들을 동작하기 위한 구성 가능한 쓰기 동작 프로토콜(configurable write operation protocol)을 가질 수 있다.

[0005] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 제 1 메모리 장치는 상기 제 1 메모리 장치의 메모리 셀들로 직접적으로 쓴 후에 쓰기가 확인되는 쓰기 커밋 정책을 갖는다.

[0006] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 제 2 메모리 장치는, 휘발성 데이터 버퍼에 쓴 후에, 쓰기가 확인되는 쓰기 커밋 정책을 갖는다.

[0007] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 제 3 메모리 장치는, 페이지 오픈(page open) 후에 쓰기 확인(write confirmation)을 이용하지 않는다.

[0008] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 제 3 메모리 장치는, 상기 메모리 시스템의 파워-업에서 상기 복수의 메모리 장치들을 위한 SPD(serial presence detect) 정보를 수신하도록 구현될 수 있다.

[0009] 실시 예에 있어서, 상기 하나 이상의 메모리 제어기들은 DDR4(double data rate generation 4) 커맨드를 재사용하도록 구현되고, 상기 DDR4 커맨드는 쓰기 동작 커맨드로써 비휘발성 메모리 장치들을 위해 이용되지 않는다.

[0010] 실시 예에 있어서, 상기 하나 이상의 메모리 제어기들은 쓰기 동작 커맨드로써 RFU(reserved for future) 커맨드들 중에서 어느 하나를 이용하도록 구현될 수 있다.

[0011] 실시 예에 있어서, 상기 메모리 시스템은 복수의 메모리 모듈들을 포함하고, 동일한 메모리 모듈 내의 상기 복

수의 메모리 장치들의 각각은 동일한 쓰기 커밋 정책을 가지고, 상기 동일한 쓰기 커밋 정책은 다른 메모리 모듈 내부의 상기 복수의 메모리 장치들의 쓰기 커밋 정책과 다를 수 있다.

[0012] 실시 예에 있어서, 상기 하나 이상의 메모리 제어기들은 오픈 페이지(open page) 및 클로즈 페이지(close page) 정책들 모두를 지원하도록 구현될 수 있다.

[0013] 본 발명의 실시 예에 따른 쓰기 커밋 정책들을 갖는 복수의 메모리 장치들을 포함하는 하나 이상의 메모리 모듈로 구성하는 메모리 시스템을 제어하는 방법은, 상기 복수의 메모리 장치들의 각각에 의해 이용되는 쓰기 커밋 정책을 식별하는 단계, 프로세서로부터 쓰기 커맨드를 수신하는 단계, 상기 쓰기 커맨드에 대응하는 상기 복수의 메모리 장치들 중에서 제 1 메모리 장치를 식별하는 단계, 및 상기 제 1 메모리 장치의 쓰기 커밋 정책에 따라 상기 쓰기 커맨드를 실행하는 단계를 포함할 수 있다.

[0014] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 상기 제 1 메모리 장치는, 제 1 메모리 장치의 메모리 셀들에 직접적으로 쓴 후에 쓰기가 확인되는 쓰기 커밋 정책을 가질 수 있다.

[0015] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 제 2 메모리 장치는, 휘발성 데이터 버퍼에 쓴 후에, 쓰기가 확인되는 쓰기 커밋 정책을 가질 수 있다.

[0016] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 제 3 메모리 장치는, 페이지 오픈(page open) 후에 쓰기 확인(write confirmation)을 이용하지 않는다.

[0017] 실시 예에 있어서, 상기 복수의 메모리 장치들의 각각의 SPD(serial presence detect) 영역으로부터 SPD 정보의 리드아웃(readout)에 근거로 하여 상기 복수의 메모리 장치들의 각각에 이용되는 쓰기 커밋 정책을 식별하는 단계를 더 포함할 수 있다.

[0018] 실시 예에 있어서, 상기 메모리 시스템은 상기 복수의 메모리 장치들에 연결된 메모리 제어기를 더 포함하고, 상기 메모리 제어기는 각각의 쓰기 커밋 정책들에 따라 상기 복수의 메모리 장치들을 구동하는 구성 가능한 쓰기 동작 프로토콜을 가질 수 있다.

[0019] 실시 예에 있어서, 상기 메모리 시스템은 복수의 메모리 모듈들을 포함하고,

[0020] 동일한 메모리 모듈 내의 상기 복수의 메모리 장치들의 각각은 동일한 쓰기 커밋 정책을 가지고, 상기 동일한 쓰기 커밋 정책은 다른 메모리 모듈 내부의 상기 복수의 메모리 장치들의 쓰기 커밋 정책과 다를 수 있다.

[0021] 본 발명의 실시 예에 따른 메모리 시스템은, 대응하는 쓰기 커밋 정책들을 갖는 복수의 메모리 장치들을 포함하는 하나 이상의 메모리 모듈들, 및 상기 하나 이상의 메모리 모듈들에 연결되는 하나 이상의 메모리 제어기들을 포함하고, 상기 하나 이상의 메모리 제어기들은, 상기 복수의 메모리 장치들의 각각에 의해 이용되는 쓰기 커밋 정책을 식별하고, 프로세서로부터 쓰기 커맨드를 수신하고, 상기 쓰기 커맨드에 대응하는 상기 복수의 메모리 장치들 중에서 제 1 메모리 장치를 식별하고, 및 상기 제 1 메모리 장치의 상기 쓰기 커밋 정책에 따라 상기 쓰기 커맨드를 실행할 수 있다.

[0022] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 상기 제 1 메모리 장치는 상기 제 1 메모리 장치의 메모리 셀들에 직접적으로 쓴 후에 쓰기가 확인되는 상기 쓰기 커밋 정책을 가질 수 있다.

[0023] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 제 1 메모리 장치는 휘발성 데이터 버퍼에 쓴 후에 쓰기가 확인되는 쓰기 커밋 정책을 가질 수 있다.

[0024] 실시 예에 있어서, 상기 복수의 메모리 장치들 중에서 제 3 메모리 장치는 페이지 오픈 후에 쓰기 확인을 이용하지 않을 수 있다.

[0025] 이 요약은 몇몇 특징들 및 상기의 상세한 설명에서 설명되는 본 발명의 예시적인 실시 형태의 개념의 선택을 소개하는데 제공된다. 이 요약은 청구된 주제의 핵심 또는 필수적인 특징을 식별하거나, 본 발명의 범위를 제한하는데 사용되는 것으로 의도되지도 않을 것이다. 하나 이상의 예시적인 실시 예에 따른 전술한 기능이 하나 이상의 작동 가능한 장치를 제공하기 위해 하나 이상의 실시 예들에 따른 하나 또는 그 이상의 다른 기술 된 특성과 결합 될 수 있다.

### 발명의 효과

[0026] 본 발명의 실시 예에 따른 컴퓨팅 시스템 및 그것의 제어 방법은, 서로 다른 쓰기 정책들을 갖는 복수의 메모리 장치들(예, NVM 장치들)을 포함하며, 각 메모리 장치(예, NVM 장치)의 쓰기 커밋 정책들에 따라 읽기 혹은 쓰기

동작을 수행할 수 있다.

### 도면의 간단한 설명

[0027]

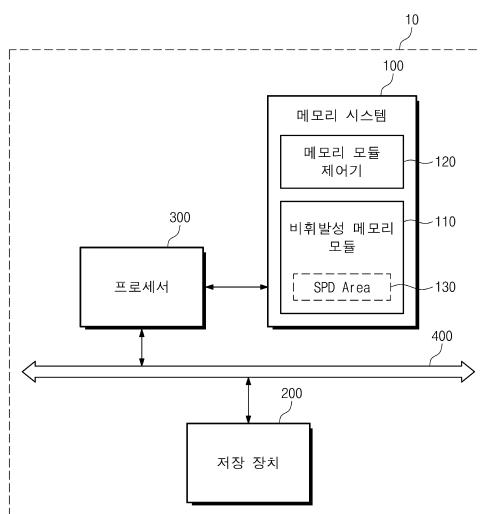

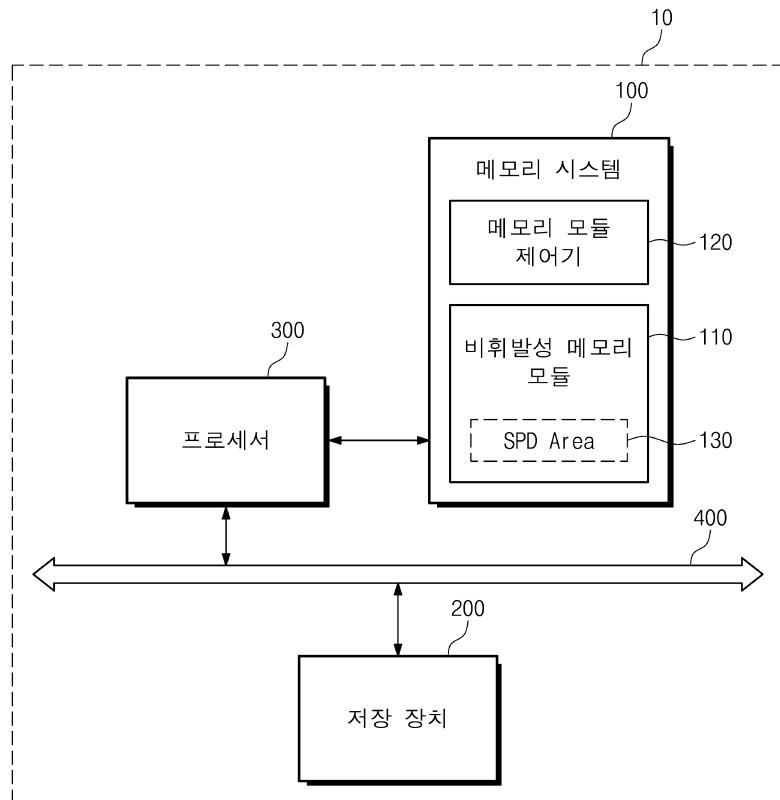

도 1은 본 발명의 실시 예에 따른 컴퓨팅 시스템의 블록 다이어그램을 예시적으로 보여주는 도면이다.

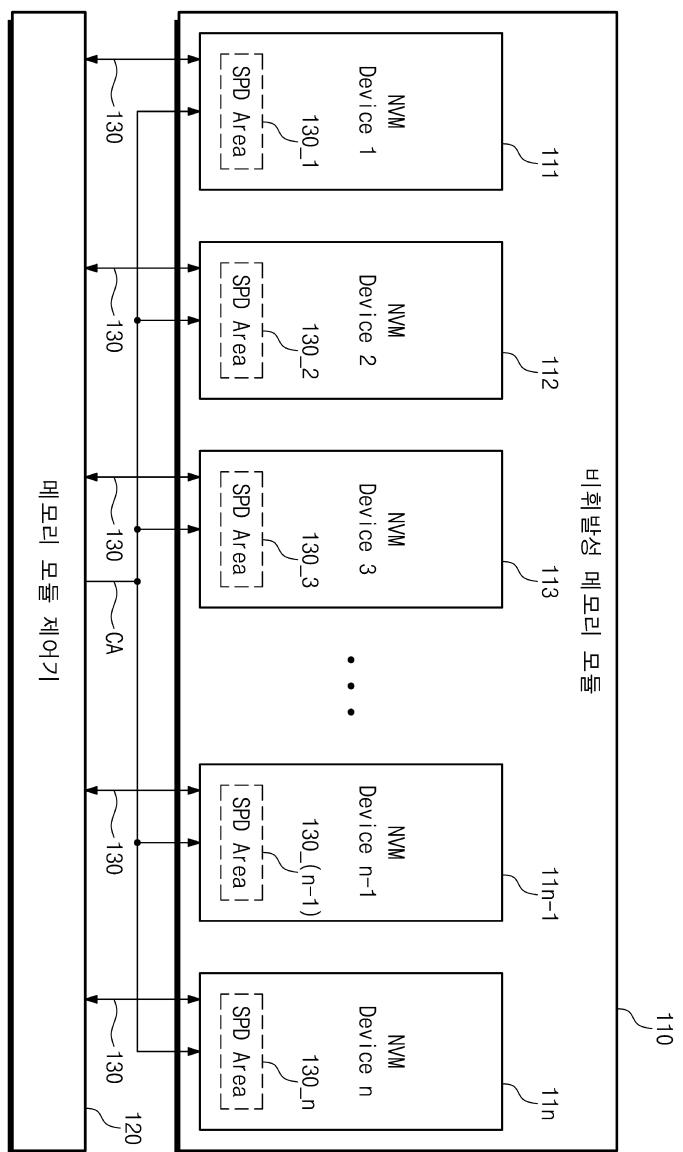

도 2a 및 도 2b는 본 발명의 실시 예에 따른 메모리 시스템의 블록 다이어그램들을 예시적으로 보여주는 도면들이다.

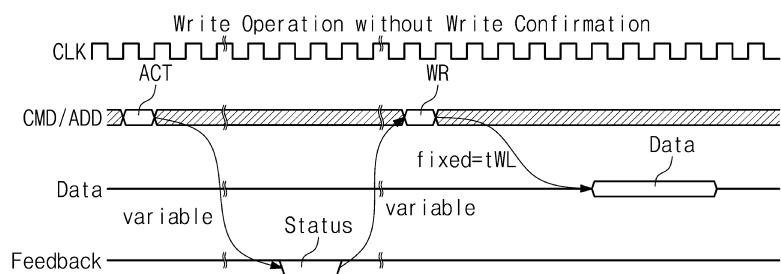

도 3은 본 발명의 실시 예에 따른 쓰기 확인 없이 쓰기 동작을 나타내는 타이밍 다이어그램이다.

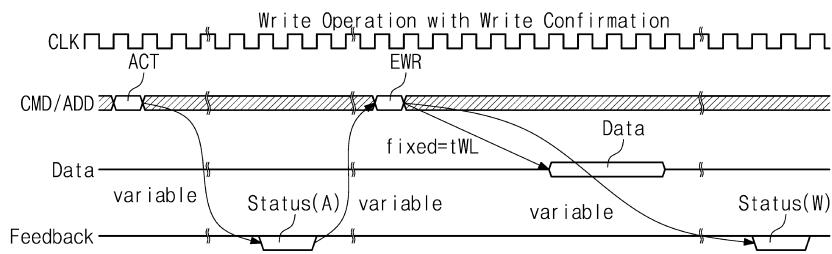

도 4는 본 발명의 실시 예에 따른 쓰기 확인을 갖는 쓰기 동작을 나타내는 타이밍 다이어그램이다.

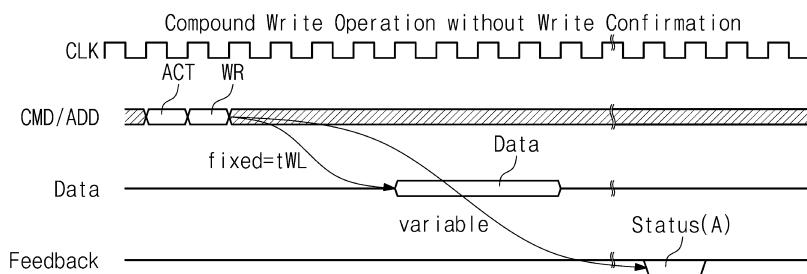

도 5는 본 발명의 실시 예에 따른 쓰기 확인없이 컴파운드(compound) 쓰기 동작을 나타내는 타이밍 다이어그램이다.

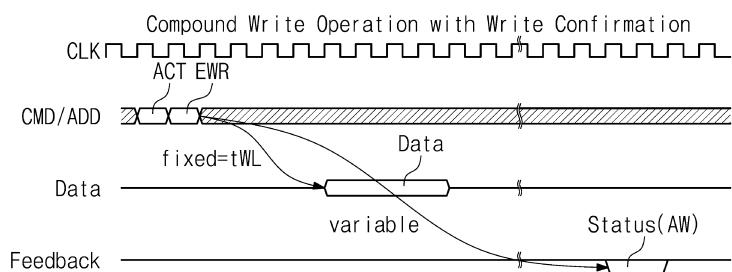

도 6은 본 발명의 실시 예에 따른 쓰기 확인을 갖는 컴파운드 쓰기 동작을 나타내는 타이밍 다이어그램이다.

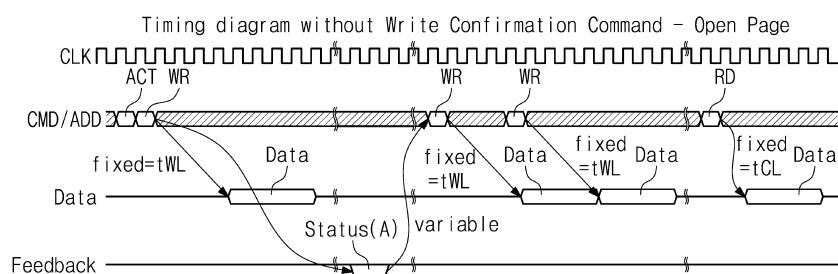

도 7은 본 발명의 실시 예에 따른 오픈 페이지 정책을 갖는 쓰기 확인 커맨드 없이 쓰기 동작을 나타내는 타이밍 다이어그램이다.

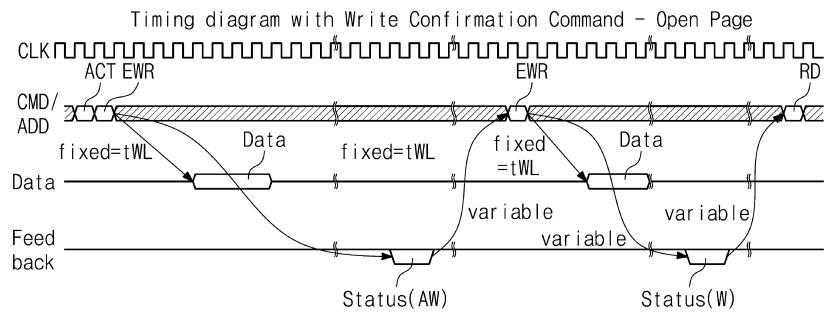

도 8은 본 발명의 실시 예에 따른 오픈 페이지 정책을 갖는 즉각적인(immediate) 쓰기 확인 커맨드를 갖는 쓰기 동작을 나타내는 타이밍 다이어그램이다.

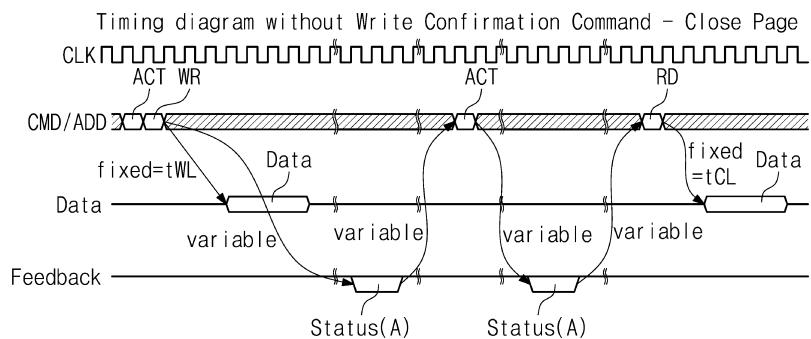

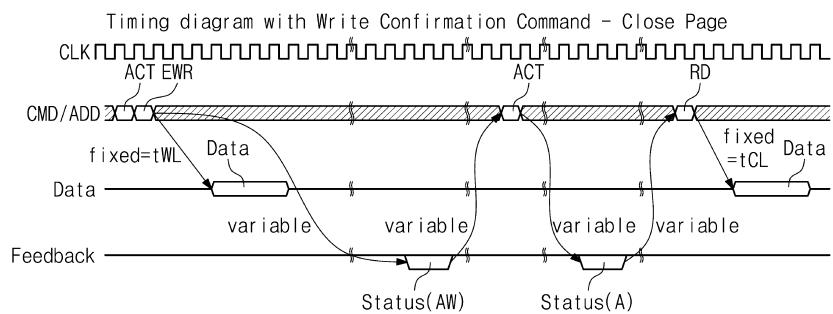

도 9는 본 발명의 실시 예에 따른 클로즈 페이지 정책을 갖는 쓰기 확인 커맨드 없이 쓰기 동작을 나타내는 타이밍 다이어그램이다.

도 10은 본 발명의 실시 예에 따른 클로즈 페이지 정책을 갖는 즉각적인 쓰기 확인 커맨드를 갖는 쓰기 동작을 나타내는 타이밍 다이어그램이다.

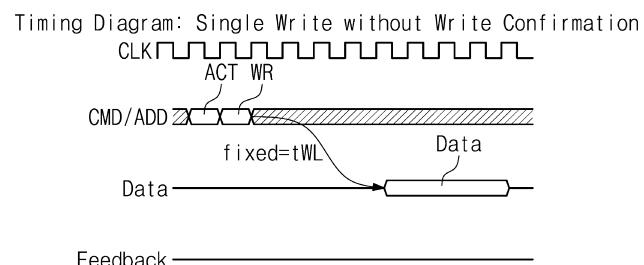

도 11은 본 발명의 실시 예에 따른 쓰기 확인 없이 싱글 쓰기 동작을 나타내는 타이밍 다이어그램이다.

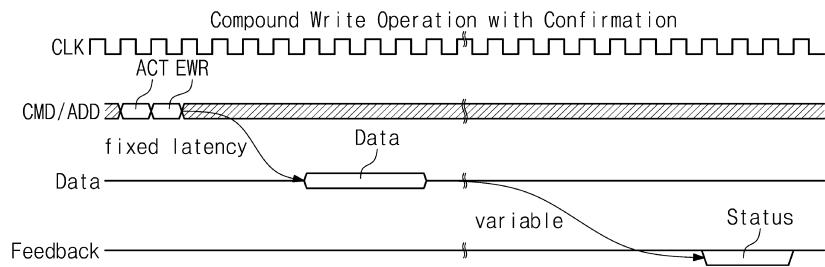

도 12는 본 발명의 실시 예에 따른 쓰기 확인을 갖는 컴파운드 쓰기 동작을 나타내는 타이밍 다이어그램이다.

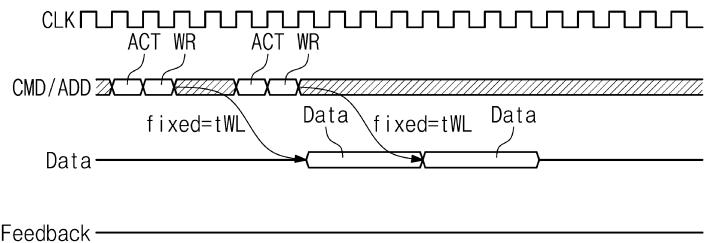

도 13은 본 발명의 실시 예에 따른 쓰기 크레딧 카운터(write credit counter)를 이용하는 연속적인 쓰기 동작들을 나타내는 타이밍 다이어그램이다.

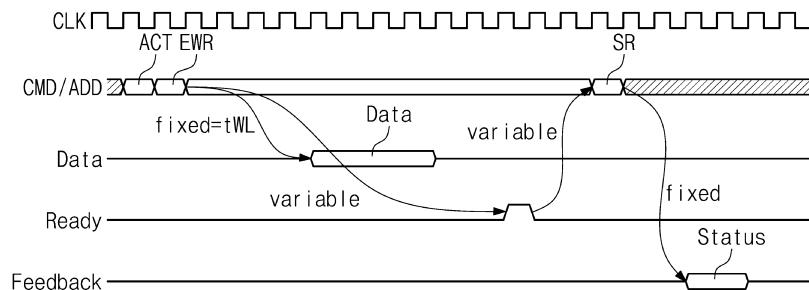

도 14는 본 발명의 실시 예에 따른 호스트가 메모리 모듈의 상태를 읽는 피드백 제어를 위한 방법을 나타내는 타이밍 다이어그램이다.

도 15는 본 발명의 실시 예에 따른 비휘발성 메모리(NVM)에 사용되지 않는 현재의 커맨드 셋을 재사용하는 새로운 커맨드 셋의 실시 예이다.

도 16은 본 발명의 실시 예에 따른 현재의 DDR 프로토콜에 사용되지 않는 새로운 커맨드 셋의 다른 예이다.

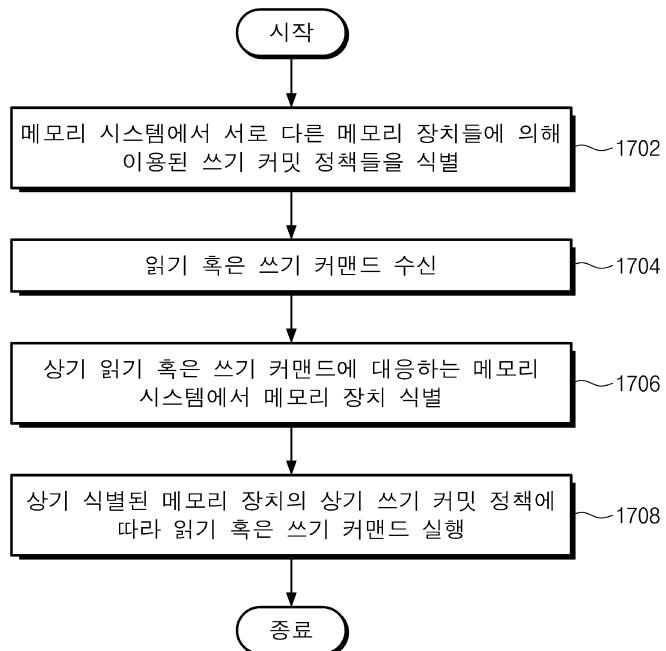

도 17은 본 발명의 실시 예에 따른 서로 다른 쓰기 커밋 정책들을 갖는 복수의 비휘발성 메모리 장치들을 갖는 메모리 시스템을 제어하는 처리 과정을 나타내는 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0028]

이하, 본 발명의 실시 예들은, 유사한 구성 요소들을 지칭하는 유사한 참조 번호들 및 첨부 도면들을 참조하여 상세히 설명할 것이다. 하지만, 본 발명은 여러 가지 상이한 형태로 구현될 수 있고, 본 명세서에서 단지 예시된 실시 예에 한정되는 것은 아니다. 이 개시가 철저하고 완전하게 되도록 오히려, 이들 실시 예는 예로서 제공되며, 완전하게 당업자에게 본 발명의 특징 및 기능을 전달할 것이다. 따라서, 양태 및 본 발명의 특징의 완전한 이해를 위해, 본 기술 분야에서 통상의 지식을 가진 자에게 필요하지 않은 프로세스 요소 및 기술들이 설명되지 않을 것이다. 특별히 언급하지 않는 한, 부호들은 첨부된 도면들 및 쓰여진 명세서를 통해 소자들로 지칭되고, 그것들의 설명들은 반복되지 않을 수 있다.

[0029]

본 발명의 실시 예들은 메모리 장치 및 그것을 제어하는 방법에 관한 것이다.

[0030]

차세대 메모리 인터페이스들의 경향에 따라서, NVM(nonvolatile memory)을 위한 트랜잭션(transaction) 기반의 인터페이스들은 메인 메모리 모듈에서 이용될 수 있다. 하지만, 서로 다른 NVM 기술들은 서로 다른 쓰기 커밋 매커니즘들을 이용한다. 예를 들어, 일부 NVM 장치들에서, 메모리 셀들에 직접적으로 쓴 후에 쓰기들이 확인된

다. 다른 말로, 입출력(I/O) 쓰기 인스트럭션(명령)이, NVM 제어기 혹은 RCD(register clock driver) 칩에 의해 NVM에 제공되면, NVM 장치는 답신(acknowledgment)을 전송한다.

[0031] 다른 NVM 장치들에서는, 휘발성 데이터 버퍼에 쓴 후에 쓰기들이 확인된다. 그리고 추가적인 하드웨어가 플래시 메모리와 유사한 방법처럼 버퍼 라이트 백(buffer write back)을 제어한다. 다른 말로, I/O 쓰기 인스트럭션이 NVM 제어기 혹은 RCD 칩에 의해 NVM에 제공되면, 휘발성 데이터 버퍼(예, 휘발성 메모리)는 I/O 쓰기 인스트럭션을 NVM 장치로 포워드하고, 답신을 전송한다. 또 다른 NVM 장치들에서는, 페이지 오픈 후에 쓰기 확인들이 필요하지 않는다. 하지만 하드웨어는 DRAM과 유사한 방식으로 페이지 라이트 백(page write back)을 제어한다.

[0032] 따라서, 싱글 쓰기 동작 프로토콜은, 서로 다른 쓰기 매커니즘들을 이용하는 다양한 NVM 기술들 모두를 이용하는데 효율적일 수 없다. 예를 들어, 즉각(immediate) 쓰기 확인을 요구하는 통신 프로토콜을 가진 DRAM 향 장치들을 이용하는 것은 메모리 대역을 낭비한다. 반면에, 플래시 메모리 향 장치들은, 피드백(예, 확인 혹은 답신)의 부족 때문에 표준 DDR4(double data rate generation 4) 프로토콜과 직접적으로 이용될 수 없다.

[0033] 따라서, 본 발명의 실시 예에 있어서, 비동기 쓰기 동작 프로토콜(asynchronized write operation)은, 즉각적인 쓰기 확인(immediate write confirmation) 및 비 쓰기 확인 (no write confirmation)동작들 모두를 이용할 수 있다.

[0034] 본 발명의 실시 예들에 있어서, 프로토콜은, 제한되지 않지만, 하나 이상의 다음의 특징들을 포함할 수 있다. 1) 구성 가능한 쓰기 확인(configurable confirmation) 정책; 2) DDR 프로토콜들과 호환성; 3) 서로 다른 NVM 장치들에 의해 이용되는 쓰기 확인 정책들(예, 확인을 갖는 쓰기, 확인 없는 쓰기)은 메모리 모듈의 부트 업 동안에 SPD(serial presence detect)을 통하여 메모리 제어기에 의해 읽혀진다; 4) 메모리 제어기 정책은 통신 프로토콜로부터 디커플드(decoupled) 되고, 오픈 및 클로즈 정책들을 지원한다; 5) 디바이스 라이트 백(device write back) 매커니즘들 정책은 통신 프로토콜로부터 디커플드 되고, 라이트 백 버퍼들(write back buffers) 혹은 라이트 트루 버퍼들(write through buffers)을 갖는 장치들을 지원한다; 6) 확인(confirmation)을 갖는 EWR(extended write) 커맨드는 NVM 기술에 따라 이용될 수 있다; 7) EWR 커맨드는 DDR4 프로토콜(예, 현재 DDR4 프로토콜)에 RFU(reserved for used) 커맨드를 사용하거나 혹은 DDR4 커맨드 셋으로부터 커맨드들을 재사용한다; 및 8) 메모리 장치는 타이밍 파라미터들에 변화 없이 이용될 수 있다.

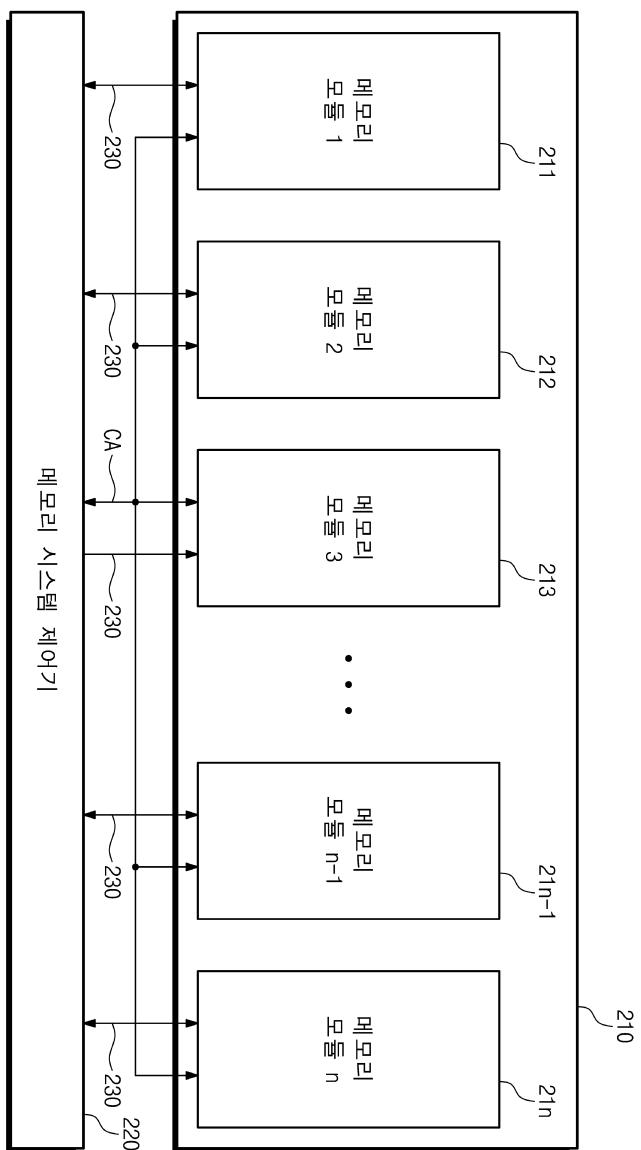

[0035] 도 1은 본 발명의 실시 예에 따른 컴퓨팅 시스템의 블록 다이어그램을 예시적으로 보여주는 도면이다. 도 2a 및 도 2b는 본 발명의 실시 예에 따른 메모리 시스템의 블록 다이어그램들을 예시적으로 보여주는 도면들이다.

[0036] 도 1을 참조하면, 컴퓨팅 시스템(10)은 메모리 시스템(100), 저장 장치(200), 프로세서(300), 및 시스템 버스(400)를 포함할 수 있다. 저장 장치(200)는 컴퓨팅 시스템(10)의 동작에 필요한/사용되는 임의의 데이터를 저장할 수 있다. 예를 들어, 저장 장치(200)는 시스템 소프트웨어, 애플리케이션 소프트웨어, 사용자 데이터 및/혹은 컴퓨팅 시스템(10)의 동작을 위해 필요한/사용되는 임의의 다른 적합한 데이터를 저장하는 데 사용될 수 있다. 본 발명의 실시 예들에 있어서, 저장 장치(200)는 HDD(hard disk drive), SSD(solid state drive), 플래시 메모리와 같은 비휘발성 메모리, PRAM(phase change RAM), MRAM(magnetic RAM), RRAM(resistive RAM), FRAM(ferroelectric RAM) 및/혹은 그와 같은 것을 포함할 수 있다.

[0037] 메모리 시스템(100)은 컴퓨팅 시스템(10)의 위킹 메모리 혹은 메인 메모리로서 이용될 수 있다. 따라서, 일부 실시 예들에 있어서, 메모리 시스템(100)의 구성들은 싱글 구성으로 집적화될 수 있다. 메모리 시스템(100)은 프로세서(300)에 의해 처리된 데이터를 저장하거나/및, 프로세서(300)에 의해 처리될 데이터를 저장하도록 구현될 수 있다.

[0038] 일부 실시 예들에 있어서, 메모리 시스템(100)은 NVM 모듈(110) 및 메모리 모듈 제어기(120)를 포함할 수 있다. 메모리 모듈 제어기(120)는 프로세서(300)의 제어 신호들에 따라 NVM 모듈(110)을 제어하도록 구현될 수 있다. 예를 들어, 메모리 모듈 제어기(120)는 프로세서(300)로부터 쓰기 커맨드 및 쓰기 데이터를 수신할 수 있고, 쓰기 데이터를 저장하도록 NVM 모듈(110)을 제어할 수 있다. 추가로, 메모리 모듈 제어기(120)는 프로세서(300)로부터 읽기 커맨드를 수신할 수 있고, NVM 모듈(110)에 저장된 데이터 중에서 요청된 데이터에 대응하는 읽기 동작을 수행하기 위하여 NVM 모듈(110)을 제어할 수 있다.

[0039] 아래에서 좀 더 자세하게 설명된 바와 같이, NVM 모듈(110)은 서로 다른 NVM 기술들을 이용하는 복수의 NVM 장치들을 포함할 수 있다. 도 1에 도시된 바와 같이, NVM 모듈(110)은 SPD(serial presence detect) 정보가 저장된 SPD 영역(130)을 포함할 수 있다. 일부 실시 예들에 있어서, SPD 영역(130)은, 데디케이티드(dedicated, 전용) 통신 패스를 갖는 메모리 시스템(100)에서 데디케이티드 칩에 저장될 수 있다. 컴퓨팅 시스템(10) 및/혹은 메

모리 시스템(100)의 부트(예, 파워 업) 동안에, NVM 모듈(110) 내부에 포함된 NVM 장치들의 종류를 검출하기 위하여 SPD 정보는 메모리 모듈 제어기(120) 및/혹은 프로세서(300)에 의해 읽혀진다.

[0040] 본 발명의 실시 예에 따른 메모리 모듈 제어기(120)는 적어도 즉각 쓰기 확인 및 비 쓰기 확인 동작들을 갖는 구성 가능한 쓰기 동작 프로토콜을 포함할 수 있다. 예를 들어, 메모리 모듈 제어기(120)는 서로 다른 NVM 장치들의 서로 다른 읽기/쓰기 요구사항들을 어떻게 제어하는지를 판별하기 위하여 NVM 모듈(110)의 서로 다른 NVM 장치들로부터 SPD 리드아웃(readout) 정보를 이용할 수 있다.

[0041] 도 2a을 참조하면, NVM 모듈(110)은 복수의 NVM 장치들(111, 112, 113, ..., 11(n-1), 11n)을 포함할 수 있다. NVM 모듈(110)의 일부로 포함된 NVM 장치들의 개수는, NVM 모듈(110)의 설계 및 기능에 따라 가변 할 수 있다. NVM 장치들(111, ..., 11n)의 각각은 메모리 모듈 제어기(120)의 커맨드(CA)에 응답하여 메모리 모듈 제어기(120)와 데이터(130)를 교환할 수 있다. NVM 장치들(111 ~ 11n)의 각각은 메모리 모듈 제어기(120)의 커マン드(CA)에 응답하여 읽기 혹은 쓰기 동작을 수행할 수 있다.

[0042] 예를 들어, NVM 장치들(111 ~ 11n)은 별별로 읽기 혹은 쓰기 동작을 수행할 수 있다. 즉, NVM 장치들(111 ~ 11n)은 독립적으로 및/혹은 동시적으로 읽기 혹은 쓰기 동작을 수행할 수 있다. 다른 실시 예들에 있어서, NVM 장치들(111 ~ 11n)의 읽기 혹은 쓰기 동작들은 순차적으로 수행될 수 있다.

[0043] 예시적인 실시 예들에서, SPD 정보는 NVM 장치들(111 ~ 11n)의 각각에서 저장될 수 있다. 예를 들어, 도 1의 SPD 영역(130)은 복수의 SPD 영역들(130\_1, 130\_2, 130\_3, ..., 130\_(n-1), 130\_n)을 포함함으로써, NVM 장치들(111 ~ 11n)의 각각은 대응하는 각각의 SPD 영역(혹은 SPD 서브 영역)을 포함할 수 있다. 따라서, 분리하고 구분한 SPD 정보는 NVM 장치들(111 ~ 11n)의 각각에 저장될 수 있다. 그래서, 예를 들어, 메모리 모듈 제어기(120)는 각각의 SPD 영역들에 저장된 SPD 정보를 얻을 수 있다. 여기서 각각의 SPD 정보는 대응하는 NVM 장치들(111 ~ 11n)에 고유하다(is specific). 일부 실시 예들에서, NVM 장치들(111 ~ 11n)의 각각을 위한 SPD 정보는 메모리 모듈(110)에 대응하는 하나 이상의 SPD 칩들에 저장될 수 있다. 여기서 SPD 칩들은 NVM 장치들(111 ~ 11n)으로부터 분리될 수 있다. 일부 실시 예들에서, 이러한 SPD 정보는 컴퓨터 시스템(10) 혹은 메모리 시스템(100)의 스타트업(startup) 혹은 부트 업(boot up)일 때 메모리 모듈 제어기(120)에 의해 획득될 수 있다. 따라서, 메모리 모듈 제어기(120)는 NVM 장치들(111 ~ 11n)을 위한 설정 동작을 수행하고 NVM 장치들(111 ~ 11n)을 제어할 수 있다. 이에 따라, 특정한 쓰기 및/혹은 읽기 동작들은, 각각의 대응하는 NVM 장치의 NVM 기술 그리고 NVM 장치들(111 ~ 11n)의 각각에 저장된 SPD 정보, 혹은 메모리 모듈에 대응하는 하나 이상의 SPD 칩들에 저장된 SPD 정보에 따라 수행될 수 있다.

[0044] NVM 장치들(111 ~ 11n)의 각각에서 SPD 정보를 갖는 메모리 모듈 제어기(120)를 설정함으로써, 서로 다른 쓰기 및/혹은 읽기 동작들은 NVM 기술에 의존하는 서로 다른 NVM 장치들(111 ~ 11n)을 위해 수행될 수 있다. 예를 들어, 하나 이상의 실시 예들에서, 서로 다른 NVM 장치들에 의해 쓰기 인스트럭션(write instruction)이 확인되는 방식 혹은 방법은 서로 다르게 설정될 수 있다. 메모리 모듈 제어기(120)는, 예를 들어, SPD 리드아웃을 통해 획득된 DIMM(dual in-line memory module) 정보에 따라 "확인을 갖는 쓰기"(write with confirmation) 커マン드 혹은 "확인 없는 쓰기(write without confirmation) 커マン드를 스케줄링 할 수 있다.

[0045] 일부 실시 예들에서, 메모리 시스템(210, 예, 도 1의 메모리 시스템(100)의 일부로써 포함된)은, 도 2b에 도시된 바와 같이, 복수의 메모리 모듈들(211, 212, 212, ..., 21(n-1), 21n)을 포함할 수 있다. 메모리 시스템(210)의 일부로써 포함된 메모리 모듈들의 개수는 메모리 시스템(210)의 설계 및 기능에 따라 가변 할 수 있다. 메모리 모듈들(211 ~ 21n)의 각각은 복수의 메모리 장치들(예, 도 2a에 도시된 메모리 모듈과 유사하거나 동일한 복수의 메모리 모듈들, 각각의 메모리 모듈들은 복수의 NVM 장치들(111 ~ 11n)을 포함)을 포함할 수 있다. 그리고 메모리 모듈들(211 ~ 21n)의 각각은 메모리 시스템 제어기(220)의 커マン드(CA)에 응답하여 메모리 시스템 제어기(220)와 데이터(230)를 교환할 수 있다. 일부 실시 예들에서, 메모리 시스템 제어기(220)는 호스트(예, 도 1 프로세서(300))의 일부로써 포함될 수 있다. 복수의 메모리 모듈들을 포함하는 메모리 시스템을 갖는 실시 예들에서, 서로 다른 메모리 모듈은 서로 다른 쓰기 확인 정책들을 가질 수 있다 하지만, 동일한 메모리 모듈의 NVM 장치들은 모두 동일한 쓰기 확인 정책을 가질 수 있다.

[0046] 하나 이상의 예시적인 실시 예들에서, 메모리 제어기 정책은 페이지 오픈 정책(page open policy)과 분리됨(be decoupled) 수 있다. 그래서, 시스템이 오픈/클로즈 페이지 정책을 결정할 것이다. 즉, 일부 실시 예들에서, 메모리 제어기는, 메모리 장치에서 이용되는 쓰기 확인 정책과 상관없이, 오픈 페이지 혹은 클로즈 페이지 정책 중 어느 하나를 선택할 수 있다. 추가로, 하나 이상의 실시 예들에서, 커マン드 세트 변경들(command set changes)은 최소값으로 유지될 수 있다. 이에 따라, 현재 커マン드들이 재사용되거나 하나의 커マン드가 추가 될 수 있다.

타이밍 파라미터 변화들이 없고, 현존하는 DDR 프로토콜과 호환성이 유지될 수 있다.

[0047] 이후에, 본 발명의 하나 이상의 실시 예들에 따른 쓰기 확인(write confirmation)의 구성(configuration)은 아래에서 자세하게 설명될 것이다. 메모리 모듈 제어기(120)는 부팅 동안에 SPD를 통하여 DIMM(dual in-line memory module)으로부터 쓰기 확인 요구사항(write confirmation requirement)을 읽을 수 있다. 여기서, DIMM은 요구되는 쓰기 확인 정책을 특정할 수 있다. 예를 들어, 만일 하드웨어가 신뢰할만한 버퍼 라이트 백(buffer write back)을 보장하면, 활성화 후에, 확인(confirmation)이 요구되지 않을 수 있다. 반면에, 하드웨어가 버퍼 라이트 백에 대한 지원을 제공하지 않으면, 모든 쓰기 트랜잭션은 쓰기 확인을 필요로 할 수 있다.

[0048] 본 발명의 하나 이상의 예시적인 실시 예들에서, 메모리 제어기 스케줄러(예, 메모리 모듈 제어기(120)내의)는 SPD 리드아웃에 따라 "확인을 갖는 쓰기"(write with confirmation) 커맨드 혹은 "확인 없는 쓰기"(write without confirmation) 커맨드를 스케줄링 하는데 이용될 수 있다. 서로 다른(혹은 서로 다른 종류의) NVM 장치들은 서로 다른 채널들에 연관되어 있기 때문에, 서로 다른 채널들은 서로 다른 쓰기 확인 정책들(write confirmation policies)을 가질 수 있다. 추가로, 동일 채널 혹은 서로 다른 채널들 내의 서로 다른 랭크(rank) 혹은 랭크들(ranks)은 서로 다른 쓰기 확인 정책들을 가질 수 있다. 추가로, 동일 랭크 혹은 서로 다른 랭크들 내의 서로 다른 뱅크(bank) 혹은 뱅크들(banks)은 서로 다른 쓰기 확인 정책들을 가질 수 있다.

[0049] 도 3은 본 발명의 실시 예에 따른 쓰기 확인 없이 NVM 장치를 이용하기 위한 쓰기 동작을 나타내는 타이밍 다이어그램이다.

[0050] 예를 들어, 메모리 모듈 제어기(120)는 본 발명의 예시적인 실시 예들에 따라 대응하는 쓰기 커밋 매커니즘들(write commit mechanism)을 갖는 하나 이상의 NVM 장치들에 쓰기 확인 없이 쓰기 동작 커맨드(write operation command)를 발행할 수 있다. 도 3에 도시된 바와 같이, 메모리 모듈 제어기(120)는 특별한 메모리 어드레스(예, NVM 장치 혹은 NVM 장치들의 특정 한 뱅크)에 ACT(activation operation) 커맨드를 발행하고, 활성화 동작이 성공했는지를 나타내는 DIMM으로부터 상태 피드백(status feedback, 예, Status)을 요구한다. 성공적인 활성화 상태를 수신한 후에, 데이터는 데이터 버퍼에 유지될 수 있고, DRAM처럼 동일한 타이밍으로 동작될 수 있다. 그러면, 메모리 모듈 제어기(120)는 NVM 장치에 데이터를 쓰기 위하여 통상의(regular) 쓰기 동작(WR) 커맨드를 발생한다. 고정된 레이턴시 이후에, 데이터는 메모리 시스템(100)의 데이터 버스로 전송되고, 대응하는 NVM 장치의 대응하는 셀들에 쓰여 진다. 그 후에, 이러한 프로토콜 기술을 사용하는 NVM 장치들이 쓰기 확인을 요구하지 않기 때문에, 쓰기 동작은 완료된다.

[0051] 도 4는 본 발명의 실시 예에 따른 쓰기 확인을 갖는 NVM 장치를 이용하기 위한 쓰기 동작을 나타내는 타이밍 다이어그램이다.

[0052] 예를 들어, 메모리 모듈 제어기(120)는 대응하는 쓰기 커밋 매커니즘들(write commit mechanisms)을 갖는 하나 이상의 NVM 장치들로 쓰기 확인(write confirmation)을 갖는 EWR(extended write operation) 커맨드를 발행할 수 있다. 도 4에 도시된 바와 같이, 활성화는 도 3의 경우처럼 실질적 동일하다. 활성화는 활성화를 위한 상태 피드백(예, Status(A))을 요구한다. 그 후, 메모리 모듈 제어기(120)는 특별한 메모리 어드레스(예, NVM 장치 혹은 NVM 장치들의 특정한 뱅크들)에 데이터를 쓰기 위하여 EWR 커맨드를 발행(예, 커맨드를 전송)한다. 가변 레이턴시 이후에, DIMM은 메모리 모듈 제어기(120)로 쓰기 확인(write confirmation)을 되돌려 전송한다. 따라서 도 4에 도시된 프로토콜에 따라, 메모리 모듈 제어기(120)는 동일한 뱅크 혹은 DIMM에 임의의 다른 동작(혹은 커맨드)을 발행하기 전에 성공적인 쓰기 확인(예, Status(W))을 기다린다.

[0053] 도 5는 본 발명의 실시 예에 따른 쓰기 확인없이 컴파운드(compound) 쓰기 동작을 나타내고, 도 6은 본 발명의 실시 예에 따른 쓰기 확인을 갖는 컴파운드 쓰기 동작을 나타내는 타이밍 다이어그램들이다.

[0054] 도 5 및 도 6에서 메모리 모듈 제어기(120)에 의해 발행된 커맨드들은, 각각 도 3 및 도 4에서 발행된 그것들과 실질적으로 유사하다. 다만, 도 5 및 도 5의 커맨드들은 각각의 컴파운드 쓰기 동작들(compound write operations)을 위해 존재한다. 여기서 컴파운드 쓰기 동작들에서, 각각의 쓰기 동작 커맨드들(WR)은 각각의 쓰기 커밋 매커니즘들에 따라 활성화 동작(activation operation, ACT) 커맨드와 컴파운드(흔합) 된다.

[0055] 도 5에 도시된 바와 같이, 활성화 및 쓰기 동작들의 컴파운드 커맨드는 특별한 메모리 어드레스(예, NVM 장치 혹은 NVM 장치들의 특정한 뱅크)에 발행된다. 그리고 데이터 쓰기는 고정된 레이턴시 이후에 개시된다. 그 후, 메모리 모듈 제어기(120)는 성공적인 활성화 확인(예, Status(A))을 기다린다. 도 6에서 메모리 모듈 제어기(120)에 의해 발행된 커맨드는 도 5에 발생된 하나와 실질적으로 동일하다. 다만, 도 6의 메모리 모듈 제어기(120)는 동일 뱅크에 임의의 다른 동작(혹은 커맨드)을 발행하기 전에 성공적인 활성화에 쓰기 확인을 더한 컴

파운드 상태 피드백(예, Status(AW))을 기다린다.

[0056] 도 7은 본 발명의 실시 예에 따른 쓰기 확인을 이용하는 것 없이 오픈 페이지 정책을 갖는 NVM 장치로 데이터를 쓰고 읽기 위한 동작들의 순서를 나타내는 예시적인 타이밍 다이어그램이다.

[0057] 도 7의 타이밍 다이어그램 및 쓰기 커밋 매커니즘은 실질적으로 도 5에 도시된 그것과 유사하다. 다만, 추가적인 WR(write) 및 RD(read) 동작들은 오픈 페이지 정책 아래에서 동일한 뱅크로 명령될 것이다. 감지 증폭기들은 오픈 페이지 정책 아래에서 항상 열려 있기 때문에, 오픈 페이지 정책 아래에서 동일한 뱅크에서 요구되는 추가의 ACT 커맨드들은 없다. 따라서, 단지 WR 및 RD 커맨드들만이 초기화 활성 상태 피드백(예, Status(A)) 수신된 이후에 발행된다. 추가적으로, 쓰기 동작 및 읽기 동작 커맨드들은 확인 없이 연속적으로 발행될 수 있다.

[0058] 도 8은 본 발명의 실시 예에 따른 쓰기 확인을 갖는 오픈 페이지 정책을 갖는 NVM 장치로 데이터를 쓰고 읽기 위한 동작들의 순서를 나타내는 타이밍 다이어그램이다.

[0059] 도 8의 타이밍 다이어그램 및 쓰기 커밋 매커니즘은 도 6의 그것과 실질적으로 유사한다. 다만, 추가적으로 EWR(extended write) 및 RD(read) 동작들은 오픈 페이지 정책 아래에서 동일 뱅크로 명령될 것이다. 감지 증폭기들은 오픈 페이지 정책 아래에서 항상 열려있기 때문에, 오픈 페이지 정책 아래에서 동일한 뱅크에 요구되는 추가적인 활성화 커맨드들은 없다. 따라서, 단지 EWR 및 RD 커맨드들만이 초기 활성화에 쓰기 상태 피드백(예, Status(AW))을 더한 것이 수신된 이후에 발행된다. 도 7에 설명된 쓰기 확인 동작이 없는 것과 달리, 메모리 모듈 제어기(120)는 동일 뱅크에 임의 다른 동작(혹은 커맨드)을 발행하기 전 각각의 EWR 커맨드를 발행 후에 상태 피드백(예, Status(W))을 기다린다는 것에 주목해야 된다.

[0060] 도 9는 본 발명의 실시 예에 따른 쓰기 확인을 이용하지 않는 클로즈 페이지 정책을 갖는 NVM 장치를 위해 데이터를 쓰고 읽기 위한 동작들의 순서를 나타내는 타이밍 다이어그램이다. 도 9에 도시된 바와 같이, 메모리 모듈 제어기(120)는 컴파운드 활성화 및 쓰기 동작 커맨드를 발행하고, 고정된 레이턴시 이후에, 데이터는 NVM 장치의 데이터 버스로 제공된다. 그 후, 성공적인 활성화 상태 확인(예, Status(A))이 DIMM에 의해, 쓰기 확인을 제공하지 않고 메모리 모듈 제어기(120)로 제공된다. 다른 쓰기 동작을 수행하기 위해서, 다른 활성화 커맨드가 발행되고, 대응하는 활성화 상태 확인이 뒤따른다. 도 9에 도시된 바와 같이, 메모리 모듈 제어기(120)는 동일 뱅크에 활성화 동작 커맨드를 발행하고, 감지 증폭기들이 항상 열리지 않은 클로즈 페이지 정책 때문에 RD 커맨드를 발행하기 전에 활성화 상태 피드백(예, Status(A))을 기다린다.

[0061] 도 10은 본 발명의 실시 예에 따른 쓰기 확인을 갖는 클로즈 페이지 정책을 갖는 NVM 장치를 위한 데이터를 쓰고 읽기 위한 동작들의 순서를 나타내는 예시적인 타이밍 다이어그램이다.

[0062] 도 10의 타이밍 다이어그램 및 쓰기 커밋 매커니즘은 도 8의 그것과 유사하다. 다만 메모리 모듈 제어기(120)는 클로즈 페이지 정책 아래에서 RD 동작 커맨드를 발행하기 전 EWR 동작 후에 ACT 커맨드를 발행한다. 도 10에 도시된 바와 같이, 메모리 모듈 제어기(120)는 활성화에 쓰기 상태 피드백을 더한 것(예, Status(AW))을 수신한 후에 동일 뱅크에 다른 ACT 커맨드를 발행하고, 감지 증폭기들이 항상 열리지 않는 클로즈 페이지 정책 때문에 RD 커맨드 발행 전에 활성화 상태 피드백(예, Status(A))을 기다린다.

[0063] 도 11은 본 발명의 실시 예에 따른 쓰기 확인 커맨드 없이 싱글 쓰기 동작을 나타내는 타이밍 다이어그램이다. 메모리 장치가 NVM 장치처럼 플래시 메모리 혹은 비휘발성 메모리 익스프레스(NVMe)인 실시 예들에서, 쓰기 베퍼는 쓰기 동작들의 인커밍(incoming)을 제어할 수 있다. 쓰기 동작이 수행되기 전에 페이지 오픈이 요구되지 않을 수 있다. 따라서, 도 11에 도시된 바와 같이, 활성화 커맨드의 확인을 획득할 필요가 없다. 추가적으로, 호스트 혹은 메모리 제어기(혹은 메모리 시스템 제어기)는 모듈 쓰기 베퍼 내에 가용한 엔트리들을 트래킹 할 수 있고, 모든 쓰기 동작들이 대응하는 메모리 모듈 내에서 베퍼링 될 수 있도록 보장할 수 있다. 이러한 구성들에서, 도 11에 도시된 바와 같이, 활성화 및 쓰기 동작들의 컴파운드 커맨드는 특별한 메모리 어드레스(예, 메모리 장치 혹은 메모리 장치들의 특정한 뱅크)에 발행된다. 그리고, 데이터 쓰기 커맨드는, 도 5 도시된 과정과 유사하게 고정된 레이턴시 이후에 개시된다. 활성화 커맨드의 확인이 필요하지 않기 때문에, 그러나, 도 5와는 상반되게, 활성화 확인은 발행되지 않을 수 있다.

[0064] 도 12는 본 발명의 실시 예에 따른 쓰기 확인 커맨드를 갖는 컴파운드 쓰기 동작을 나타내는 타이밍 다이어그램이다. 도 12의 타이밍 다이어그램은 도 11의 그것과 실질적으로 유사하다. 다만, 쓰기 커맨드는 확인 커맨드(confirmation command)을 갖는 EWR(extended write)이다. 반복해서, NVM 장치들처럼 플래시 혹은 NVMe의 경우에 있어서, 페이지 오픈 커맨드는 쓰기 동작이 수행되기 전에 요구되지 않을 수 있다. 따라서, 활성화 확인은 제공되지 않을 수 있다. 이러한 구성들에서, 도 12에 도시된 바와 같이, 컴파운드 활성화 및 EWR 커맨드는 발행

될 수 있고, 고정된 레이턴시 이후에, 쓰기 동작은 수행된다. EWR 커맨드가 쓰기 확인을 이용하기 때문에, 가변적인 레이턴시 이후에, 쓰기 확인 상태는 활성화 확인 없이 발생될 수 있다.

[0065] 도 13은 본 발명의 실시 예에 따른 쓰기 크레딧 카운터(write credit counter)를 이용하는 연속적인 쓰기 동작들을 나타내는 타이밍 다이어그램이다. 일부 실시 예들에 있어서, 호스트 혹은 메모리 모듈 제어기(120, 혹은 메모리 시스템 제어기)는 쓰기 크레딧 카운터를 이용할 수 있다. 쓰기 동작을 발생된 후에, 쓰기 크레딧 카운터는 하나의 크레딧을 감소시킨다. 쓰기 크레딧 카운터가 0보다 크기만 하면, 호스트는 쓰기 커맨드들을 발생하는 것을 계속한다. 일부 실시 예들에서, 호스트는 특정한 커맨드를 이용하여 메모리 모듈로부터 쓰기 크레딧을 풀(pull)할 수 있다. 예를 들어, 도 13에 도시된 바와 같이, 쓰기 커맨드를 발생하기 전에, 쓰기 크레딧 카운터는 0보다 큰 정수로 설정될 수 있다(예, 2). 따라서, 쓰기 크레딧 카운트가 더 이상 0보다 크지 않을 때까지, 각각의 쓰기 커맨드 후에 쓰기 크레딧 카운터로부터 하나의 크레딧을 빼주면서, 호스트는 컴파운드 활성화 및 쓰기 커맨드들을 발생할 수 있다.

[0066] 도 14는 본 발명의 실시 예에 따른 호스트가 메모리 모듈의 상태를 읽는 피드백 제어를 위한 매커니즘을 나타내는 타이밍 다이어그램이다. 본 발명의 일부 실시 예들에서, 메모리 모듈들 혹은 메모리 장치들은, 커맨드의 실행에 뒤이어 호스트 혹은 메모리 모듈 제어기(120, 혹은 메모리 시스템 제어기)에 자동적으로 피드백을 제공할 수 없다. 반면에, 메모리 모듈들 혹은 메모리 장치들은 호스트에 준비 알림(ready notification) 혹은 신호를 발생할 수 있다. 그리고, 호스트는 대응하는 메모리 모듈 혹은 메모리 장치로부터 상태를 풀링(pulling)하도록 제어할 수 있다. 도 14에 도시된 바와 같이, 활성화 및 EWR의 컴파운드 커맨드는 메모리 어드레스에 발생될 수 있다. 데이터 쓰기는 고정된 레이턴시 이후에 시작된다. 그 후에, EWR 동작에 뒤따르는, 가변적인 레이턴시 이후에, 메모리 장치 혹은 메모리 모듈이 상태 정보(쓰기 확인 정보, 쓰기 크레딧 업데이트들, 및 그와 같은 것)를 제공하도록 준비되었다는 것을 나타내면서 준비 알림(ready notification)은 호스트 혹은 메모리 모듈 제어기(120, 혹은 메모리 시스템 제어기)로 전송될 수 있다. 따라서, 가변적인 시간이 지난 후에, 호스트는 대응하는 메모리 장치 혹은 메모리 모듈로부터 상태 정보를 요청하는 SR(status read) 커맨드를 발생할 수 있다. 그리고, 고정적인 레이턴시 이후에, 상태 정보는 메모리 모듈 혹은 메모리 장치로부터 호스트로 제공될 수 있다.

[0067] 상술 된 바와 같이 임의의 커맨드들 및 동작들이 도 2a 및 메모리 모듈(110)에 대해서 설명될지라도, 본 발명의 실시 예들이, 메모리 시스템 제어기(220)가 다양한 메모리 모듈들(211 ~ 211n)과 데이터 및 커맨드들을 교환 할 수 있는 도 2b에 도시된 메모리 시스템(210)에 적용될 수 있다는 것이, 당업자에게 이해될 것이다. 상술된 바와 같이, 일부 실시 예들에서, 메모리 모듈들(211 ~ 211n)의 각각은 복수의 메모리 장치들(예, NVM 장치들)을 포함하고, 복수의 메모리 장치들 각각은 동일한 메모리 모듈에서 동일한 쓰기 확인 정책들을 가질 수 있다.

[0068] 본 발명의 일부 예시적인 실시 예들에서, 새로운 커맨드는 메모리 모듈 제어기에 의해 NVM 장치들에 발생될 수 있다. 예를 들어, 새로운 커맨드는 상술 된 다양한 타이밍 다이어그램들에서 도시된 바와 같이 확인(confirmation)을 갖는 EWR(extended write) 커맨드일 수 있다. 일부 실시 예들에서, EWR 커맨드는, 제한 되지 않지만, 1) 칩 ID ( $C_2$ ,  $C_1$ ,  $C_0$  등), 2) 뱅크 및 뱅크 그룹 ID ( $BA[1:0]$ ,  $BG[1:0]$ ), 3) 컬럼 어드레스 ( $A13-11*$ ,  $A9-0$ 중 하나 이상) 갖는 정보를 포함할 수 있다. 예를 들어, 컬럼 어드레스는 서로 다른 로우 버퍼 크기(예, 디바이스 페이지 크기)를 지원하도록 프로그래머블 될 수 있다.

[0069] 도 15는 본 발명의 실시 예에 따른 비휘발성 메모리(NVM) 장치들에 사용되지 않는 현재의 커맨드 셋을 재사용하는 새로운 커맨드 셋의 실시 예이다. 재사용될 수 있는 커맨드들은, 예를 들어, 제한되지 않지만, WRA(write with auto precharge) 커맨드, WRS4(write with burst chop) 커맨드, 및/혹은 그와 같은 것을 포함할 수 있다. 도 15에 도시된 바와 같이, 예를 들어, WRA(Fixed BL8 혹은 BC4) 커맨드는 EWR(extended write) 커맨드로써 재사용될 수 있다.

[0070] 도 16은 본 발명의 실시 예에 따른 현재의 DDR 프로토콜에 사용되지 않는 새로운 커맨드 셋의 다른 예이다. 예를 들어, 현재의 RFU(reserved for future use) 셋들은 도 16에 도시된 바와 같이 EWR를 위한 새로운 커맨드로써 사용될 수 있다.

[0071] 도 17은 본 발명의 실시 예에 따른 서로 다른 쓰기 커밋 정책들을 갖는 복수의 비휘발성 메모리 장치들을 갖는 메모리 시스템을 제어하는 처리 과정을 나타내는 흐름도이다. 일부 실시 예들에서, 메모리 시스템을 제어하는 동작들의 개수 및 동작들의 순서는 가변 할 수 있다. 즉, 일부 실시 예들에서, 처리 과정은 추가 동작들을 포함하거나 동작들의 순서는 가변 할 수 있다.

[0072] 도 17에 도시된 바와 같이, 처리 과정이 시작되어, 1702 단계에서, 메모리 시스템은 메모리 시스템에 포함된 서

로 다른 메모리 장치들(예, NVM 장치들)의 각각에 의해 이용되는 쓰기 커밋 정책들을 식별한다. 즉, 본 발명의 실시 예들에서, 상술 된 바와 같이, 메모리 시스템은 서로 다른 메모리(예, NVM) 기술들에 따라 구현된 서로 다른 메모리 장치들(예, NVM 장치들)을 포함할 수 있다. 서로 다른 메모리 장치들은 상술된 서로 다른 쓰기 커밋 정책들을 가진다. 메모리 시스템 및/혹은 메모리 시스템에 포함된 메모리 모듈 제어기는 각각의 메모리 장치들(예, NVM 장치들)의 SPD 영역 혹은 메모리 모듈(들)의 하나 이상의 SPD 칩들로부터 리드아웃에 의해 다양한 메모리 장치들(예, NVM 장치들)의 쓰기 커밋 정책들을 식별할 수 있다. 일부 실시 예들에서, 이러한 쓰기 커밋 정책들은 컴퓨터 시스템 및/혹은 메모리 시스템의 스타트업 혹은 부팅에서 식별될 수 있다.

[0073] 1704 단계에서, 메모리 시스템은, 예를 들어 외부 프로세서 혹은 제어기로부터 읽기 혹은 쓰기 커맨드를 수신한다. 그 후에, 1706 단계에서, 메모리 시스템은 읽기 혹은 쓰기 커맨드에 대응하는 메모리 장치 혹은 메모리 장치들(예, NVM 장치 혹은 NVM 장치들)을 식별한다. 1708 단계에서, 메모리 시스템은 대응하는 메모리 장치(예, NVM 장치(들))의 쓰기 커밋 정책에 따라 읽기 혹은 쓰기 커맨드를 실행한다.

[0074] 따라서, 본 발명의 실시 예들에서, 메모리 시스템은 동일한 메모리 시스템 혹은 구성으로 결합된 서로 다른 쓰기 정책들을 갖는 복수의 메모리 장치들(예, NVM 장치들)을 포함할 수 있다. 그리고, 메모리 시스템은 시스템 안에 각 메모리 장치(예, NVM 장치)의 쓰기 커밋 정책들에 따라 읽기 혹은 쓰기 동작들을 수행할 수 있다.

[0075] 도면들에서, 구성 요소, 층 및 영역들의 상대적인 크기는 과장되고 및/혹은 명확성을 위해 단순화 된 것이다. "제 1", "제 2", "제 3" 등의 용어들이 다양한 구성 요소, 성분, 영역, 층 및/혹은 섹션들을 설명하기 위해 사용될 수 있는 용어이지만, 이러한 구성 요소, 성분, 영역, 층 및/혹은 섹션들은 이들 용어들에 의해 제한되지 않을 것이다. 이들 용어는 다른 구성 요소, 성분, 영역, 층 또는 섹션에서 하나의 구성 요소, 성분, 영역, 층 또는 섹션과 구별하기 위해 사용된다. 따라서, 후술하는 제 1 구성 요소, 성분, 영역, 층 또는 섹션은 본 발명의 사상 및 범위를 벗어나지 않고, 제 2 구성 요소, 성분, 영역, 층 또는 섹션을 지칭 할 수 있다.

[0076] 본원에 사용된 용어는 특정 실시 예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 본원에 사용된 바와 같이, 단수 형태 "a"와 "an"는 문맥상 명백하게 다르게 뜻하지 않는 복수형도 포함하는 것으로 의도된다. 또한 명세서에 사용된 "구성한다"(comprise), "구성하는"(comprising) "포함한다"(include), "포함하는"(including) 용어들은, 언급된 특징들, 숫자들, 단계들, 동작들, 구성 요소들, 및/혹은 성분들의 존재를 상세하게 하고, 이들의 하나 이상의 다른 특징들, 숫자들, 단계들, 동작들, 구성 요소들, 및/혹은 성분들의 추가를 배제하지 않는다고 이해되어야 할 것이다. 본원에서 사용된 용어 "및/혹은"은 관련된 열거 항목의 하나 이상의 임의의 모든 조합을 포함한다. 구성 요소들을 진행할 때 "적어도 하나의" 같은 표현들은 구성 요소들의 전체 목록을 변조하고, 목록의 개별적인 구성 요소들을 변조하지 않는다.

[0077] 본원에서 사용된 용어 "실질적으로", "대략", "정보" 및 유사한 용어들은 근사도의 용어로 사용되지 정도의 용어로 사용되지 않으며, 당업자에게 있어서 인식될 수 있는 측정된 혹은 계산된 값들로 고유한 변동을 고려하기 위해 의도될 것이다. 추가로, 본 실시 예들에서 설명하는 "할 수 있다"(may)의 사용은 "본 발명의 하나 이상의 실시 예들"로 언급한다. 여기서 사용된, "사용하다"(use), "사용하는"(using), 및 "사용된"(used)이라는 용어들은, 각각 "이용하다"(utilize), "이용하는"(utilizing), 및 "이용된"(utilized) 용어들로 동의어로 간주될 것이다. 또한, "예시적인"(exemplary)이라는 용어는 예시(example) 혹은 도면(illustration)으로 간주된다.

[0078] 다르게 정의되지 않는 한, 본원에서 사용된 기술적이거나 과학적인 용어를 포함하는 모든 용어는 일반적으로 본 발명이 속하는 당업자에 의해 이해되는 동일한 의미를 갖는다. 이는 일반적으로 사용되는 사전에 정의되어 있는 용어들은 관련 기술 및/혹은 본 명세서의 문맥에서 그들의 의미와 일치하는 의미를 가지는 것으로 해석되도록 이해되며, 본 출원에서 명백하게 정의하지 않는 한, 이상화된 혹은 지나치게 형식적인 감각으로 해석되지 말아야 한다.

[0079] 본 명세서에 설명된 본 발명의 실시 예에 따른 전자 혹은 전기 장치들 및/혹은 임의의 다른 적절한 장치들 혹은 구성 요소들은, 임의의 적합한 하드웨어, 펌웨어 (예를 들어, 애플리케이션 특수 집적 회로), 소프트웨어, 혹은 소프트웨어의 조합, 펌웨어 및 하드웨어를 이용하여 구현될 수 있다. 추가로 다양한 동작들은, 여기서 설명된 다양한 기능들을 수행하기 위한 컴퓨터 프로그램을 실행하기 위하여 다른 시스템 구성 요소들과 상호 작용하고, 컴퓨터 프로그램 인스트럭션들을 실행하는 프로세서 혹은 제어기에서 동작하는 프로세스 혹은 쓰레드(thread)일 수 있다. 컴퓨터 프로그램 인스트럭션들은 프로세서 혹은 제어기에 연결되고, 메모리 혹은 비-일시적 컴퓨터 읽기 가능 매체에 저장될 수 있다. 프로세서 및 제어기에 의해 컴퓨터 프로그램 인스트럭션들이 실행될 때, 프로세서 및 제어기는 여기에서 설명된 동작들 혹은 기능들을 수행할 것이다. 본 발명의 일부 실시 예들에서, 메모리 시스템의 다양한 구성 요소들은 싱글 구성요소, 칩, 혹은 장치의 일부로서 집적화되거나 혹은 결합될 수 있

다.

[0080]

본 발명은 예시적인 실시 예들을 참조하여 설명하였지만, 당업자라면 본 발명의 사상 및 범위를 벗어나지 않고 실시 예에 다양한 변화 및 변형이 수행될 수 있다는 것을 인식할 것이다. 또한, 다양한 기술 분야의 당업자는 본 명세서에 설명 된 본 발명은 다른 응용 프로그램에 대한 다른 작업과 응용에 대한 해결책을 제안 할 것을 인식할 것이다. 또한, 출원인의 의도는 여기에 첨부된 청구항들에 의해 커버될 것이다. 본 발명의 이러한 사용들 및 그것들의 변화들과 변조들은 본 발명의 사상 및 범위를 벗어나지 않는 한 본 발명의 목적을 위해 선택된 본 발명의 예시적인 실시 예들에 의해 이루어질 수 있다. 따라서, 본 발명의 실시 예들은 모두 첨부 된 청구항 및 그것들의 등가에 의해 지시되는 발명의 사상 및 범위를 제한하지 않으면서 모든 면에서 예시하는 것으로 간주되어야 한다.

### 부호의 설명

[0081]

10: 컴퓨터 시스템

100: 메모리 시스템

200: 저장 장치

300: 프로세서

120: 메모리 모듈 제어기

110: 비휘발성 메모리 모듈

130: SPD 영역

### 도면

#### 도면1

도면2a

도면2b

도면3

## 도면4

## 도면5

## 도면6

## 도면7

**도면8****도면9****도면10****도면11**

도면12

도면13

도면14

## 도면15

| Function                                           | CKE<br>Pre | CKE<br>Cur | CAS<br>n | ACT<br>n | RAS<br>n/<br>A16 | CAS<br>n/<br>A15 | WE<br>- | BG0<br>BA0 | BG0<br>BA0 | C2-<br>C0 | BC<br>n/<br>A12 | A17 | A13 | A11 | A10/<br>AP | A9-<br>A0 |

|----------------------------------------------------|------------|------------|----------|----------|------------------|------------------|---------|------------|------------|-----------|-----------------|-----|-----|-----|------------|-----------|

| Bank Activate(ACT)                                 | H          | H          | L        | L        |                  | RA               |         | BG         | BA         | V         |                 |     |     |     |            | RA        |

| Write w Auto Precharge<br>(Fixed BL8 or BC4) (WRA) | H          | H          | L        | H        | H                | L                | L       | BG         | BA         | V         | V               | V   | V   | V   | V          | H         |

↓

| Function            | CKE<br>Pre | CKE<br>Cur | CAS<br>n | ACT<br>n | RAS<br>n/<br>A16 | CAS<br>n/<br>A15 | WE<br>- | BG0<br>BA0 | BG0<br>BA0 | C2-<br>C0 | BC<br>n/<br>A12 | A17 | A13 | A11 | A10/<br>AP | A9-<br>A0 |

|---------------------|------------|------------|----------|----------|------------------|------------------|---------|------------|------------|-----------|-----------------|-----|-----|-----|------------|-----------|

| Bank Activate(ACT)  | H          | H          | L        | L        |                  | RA               |         | BG         | BA         | V         |                 |     |     |     |            | RA        |

| Extended Write(EWR) | H          | H          | L        | H        | L                | L                | BG      | BA         | C          | V         | V               | V   | V   | V   | H          | CA        |

도면16

| Function           | CKE<br>Pre | CKE<br>Cur | CS<br>n | ACT<br>n | RAS<br>n/<br>A16 | CAS<br>n/<br>A15 | WE<br>- | BG0 | BA0 | C2-<br>CO | BC<br>n<br>/A12 | A17 | A13 | A11 | A10/<br>AP | A9/<br>A0 |

|--------------------|------------|------------|---------|----------|------------------|------------------|---------|-----|-----|-----------|-----------------|-----|-----|-----|------------|-----------|

| Bank Activate(ACT) | H          | H          | L       | L        | RA               | BG               | BA      | V   |     |           |                 |     |     |     | RA         |           |

| RFU                | H          | H          | L       | H        | L                | H                | H       |     |     |           |                 |     |     |     | RFU        |           |

| Function            | CKE<br>Pre | CKE<br>Cur | CS<br>n | ACT<br>n | RAS<br>n/<br>A16 | CAS<br>n/<br>A15 | WE<br>- | BG0 | BA0 | C2-<br>CO | BC<br>n<br>/A12 | A17 | A13 | A11 | A10/<br>AP | A9/<br>A0 |

|---------------------|------------|------------|---------|----------|------------------|------------------|---------|-----|-----|-----------|-----------------|-----|-----|-----|------------|-----------|

| Bank Activate(ACT)  | H          | H          | L       | L        | RA               | BG               | BA      | V   |     |           |                 |     |     |     | RA         |           |

| Extended Write(EWR) | H          | H          | L       | H        | L                | H                | BG      | BA  | V   | V         | L               | V   | V   | H   | CA         |           |

| RFU                 | H          | H          | L       | H        | L                | H                |         |     |     |           |                 |     |     |     | L          | RFU       |

**도면17**