(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5301554号

(P5301554)

(45) 発行日 平成25年9月25日(2013.9.25)

(24) 登録日 平成25年6月28日(2013.6.28)

(51) Int.Cl.

G06F 9/42 (2006.01)

G06F 9/38 (2006.01)

F 1

G06F 9/42 320A

G06F 9/42 330A

G06F 9/38 330F

請求項の数 25 (全 22 頁)

(21) 出願番号 特願2010-533174 (P2010-533174)

(86) (22) 出願日 平成20年10月31日 (2008.10.31)

(65) 公表番号 特表2011-503718 (P2011-503718A)

(43) 公表日 平成23年1月27日 (2011.1.27)

(86) 國際出願番号 PCT/US2008/081947

(87) 國際公開番号 WO2009/059100

(87) 國際公開日 平成21年5月7日 (2009.5.7)

審査請求日 平成22年6月23日 (2010.6.23)

(31) 優先権主張番号 11/934,264

(32) 優先日 平成19年11月2日 (2007.11.2)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔡田 昌俊

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】プロシージャリターンシーケンスを加速するための方法およびシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

パイプラインプロセッサの中のプロシージャから戻るときにリンクスタックからリターンアドレスを取り出すための方法であって、

ソフトウェアスタックから情報を取り出すための検索命令を識別することと、

前記検索命令に基づいて取り出された情報を分岐先アドレスとして用いて前記リターンアドレスへと分岐するためのブランチ命令を識別することと、

前記検索命令と前記ブランチ命令を識別することに応じて、前記リンクスタックから前記リターンアドレスを取り出すこと、

前記リターンアドレスを使用して第2の命令をフェッチすることと、

を備える方法。

## 【請求項 2】

前記検索命令は、POP命令である、請求項1に記載の方法。

## 【請求項 3】

前記検索命令は、ロード命令である、請求項1に記載の方法。

## 【請求項 4】

前記ブランチ命令は、BX命令である、請求項1に記載の方法。

## 【請求項 5】

前記ブランチ命令は、MOV命令である、請求項1に記載の方法。

## 【請求項 6】

10

20

前記の前記検索命令を識別することは、前記情報を格納するレジスタを識別することをさらに備える、請求項 1 に記載の方法。

**【請求項 7】**

レジスタリストを保持することをさらに備え、前記レジスタリストは、前記情報を格納するレジスタを識別するためのものである、請求項 1 に記載の方法。

**【請求項 8】**

前記レジスタリストを保持することは、前記レジスタリストで識別された第 2 のレジスタの内容が上書きされたことを決定すること、および、

前記レジスタリストから前記第 2 のレジスタを取り除くことを備える、請求項 7 に記載の方法。 10

**【請求項 9】**

前記ブランチ命令を識別することは、検出口ジック回路によって実行される、請求項 1 に記載の方法。

**【請求項 10】**

前記検出口ジック回路は、プリデコードロジック回路に含まれる、請求項 9 に記載の方法。

**【請求項 11】**

前記検出口ジック回路は、デコードロジック回路に含まれる、請求項 9 に記載の方法。

**【請求項 12】**

前記ブランチ命令を識別することは、命令キャッシュの中の前記ブランチ命令にフラグ付けすることをさらに備える、請求項 1 に記載の方法。 20

**【請求項 13】**

命令キャッシュに結合されたラインバッファであって、前記ラインバッファから前記命令キャッシュへ命令がロードされるものである、ラインバッファと；

前記命令キャッシュに結合され、予測リターンアドレスを記憶するリンクスタックを有するフェッチロジック回路とであって、前記命令キャッシュから命令を取り出すためのフェッチロジック回路と；

前記ラインバッファと通信するプリデコードロジック回路とであって、前記プリデコードロジック回路は、プロシージャリターンシーケンスを識別するための検出口ジック回路をさらに備えるものあり、前記プロシージャリターンシーケンスは、ソフトウェアスタックから情報を取り出すための検索命令と、前記検索命令に基づいて取り出された情報を分岐先アドレスとして用いて分岐するためのブランチ命令とを備えるものである、プリデコードロジック回路と； 30

前記プロシージャリターンシーケンスの前記識別に応じて前記リンクスタックから前記予測リターンアドレスの 1 つの予測されたリターンアドレスを取り出す手段と；

を備えるパイプラインプロセッサ。

**【請求項 14】**

前記検出口ジック回路は、前記ブランチ命令が、前記ラインバッファから前記命令キャッシュへとロードされるときに、前記プロシージャリターンシーケンスの前記ブランチ命令にフラグ付けする、請求項 13 に記載のパイプラインプロセッサ。 40

**【請求項 15】**

前記フェッチロジック回路は、前記ブランチ命令から前記プロシージャリターンシーケンスを識別する、請求項 14 に記載のパイプラインプロセッサ。

**【請求項 16】**

前記フェッチロジック回路内のリターンセレクタロジック回路をさらに備え、前記リターンセレクタロジック回路は、前記ブランチ命令から前記プロシージャリターンシーケンスを識別する、請求項 15 に記載のパイプラインプロセッサ。

**【請求項 17】**

前記検索命令は、POP 命令である、請求項 13 に記載のパイプラインプロセッサ。

**【請求項 18】**

前記検索命令は、ロード命令である、請求項 13 に記載のパイプラインプロセッサ。

**【請求項 19】**

前記プランチ命令は、BX 命令である、請求項 13 に記載のパイプラインプロセッサ。

**【請求項 20】**

予測されたリターンアドレスを記憶するリンクスタックを有し、命令キャッシュから命令をフェッチするように構成されたフェッチロジック回路と、

前記フェッチロジック回路に結合されたデコードロジック回路と、

を備え、前記フェッチされた命令は、前記デコードロジック回路によって復号可能であり、前記デコードロジック回路は、検出口ロジック回路をさらに備え、前記検出口ロジック回路は、ソフトウェアスタックから情報を取り出すための検索命令と、前記検索命令に基づいて取り出された情報を分岐先アドレスとして用いて分岐するためのプランチ命令とを備えるプロシージャリターンシーケンスを識別するように構成され、パイプラインプロセッサは、前記プロシージャリターンシーケンスの前記識別に応じて前記リンクスタックから前記予測されたリターンアドレスのうちの 1 つの予測されたリターンアドレスを取り出すように構成される、パイプラインプロセッサ。

**【請求項 21】**

前記フェッチロジック回路は、前記リンクスタックから取り出された前記予測されたリターンアドレスを使用して命令をフェッチする、請求項 20 に記載のパイプラインプロセッサ。

**【請求項 22】**

前記検索命令は、POP 命令である、請求項 20 に記載のパイプラインプロセッサ。

**【請求項 23】**

前記検索命令は、ロード命令である、請求項 20 に記載のパイプラインプロセッサ。

**【請求項 24】**

前記プランチ命令は、前記検索命令に基づいて識別されるアドレスへと分岐するためのものである、請求項 20 に記載のパイプラインプロセッサ。

**【請求項 25】**

前記プランチ命令は、移動命令である、請求項 20 に記載のパイプラインプロセッサ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、一般にコンピュータシステムに関し、そしてより詳細にはプロセッサ内のポッププランチ命令シーケンスを識別することにより、リターンシーケンスを加速するための方法およびシステムに関する。

**【背景技術】**

**【0002】**

プロセッサによって実行される大部分のプログラムは、サブルーチンまたはプロシージャを含んでいる。プロシージャは、プロシージャ呼び出しシーケンスによってアクセスされるコードのモジュールである。ひとたびプロシージャが、完了された後には、命令実行は、プロシージャリターンシーケンス(procedure return sequence)の実行によって呼び出し側(caller)に戻される。

**【0003】**

いくつかのプロセッサアーキテクチャ内において、プロシージャのコールおよびリターンのシーケンスは、一連の命令へとコンパイルされることができる。例えば、プロシージャ呼び出しシーケンスは、プランチおよびリンクの命令によって追隨される PUSH 命令から成ることができる。PUSH 命令(单数または複数)は、プロシージャ内の命令によって使用されるパラメータをソフトウェアスタック(software stack)上に保存することができる。PUSH 命令の後に、プロセッサは、プランチおよびリンクの命令を実行することができる。プランチおよびリンクの命令は、命令のフェッチおよび実行が、プロシージャの開始アドレスにおいて開始するようにさせ、そしてリターンアドレスまたはリンクア

10

20

30

40

50

ドレスとして知られている、プランチおよびリンクの命令に続く次の逐次命令のアドレスをリンクレジスタ(link register)に保存する。リンクレジスタは、プロセッサによって使用される専用レジスタ、あるいは汎用レジスタ(general purpose registers)(GPR)のうちの1つとすることができます。プロシージャ内において、リンクレジスタ内容は、一般的にソフトウェアスタック上へと PUSHされ、その結果、その値は、別のプロシージャが、元の呼び出し側に戻る前に呼び出される場合には、上書きされないようになる。

#### 【0004】

プロシージャがそのファンクションを完了した後に、プロセッサは、リンクアドレス(プロシージャ呼び出し命令に続く次の逐次命令アドレス)において命令実行を再開するためにプロシージャリターンシーケンスを実行する。リターンアドレスは、多くの場合にソフトウェアスタック上に保存されるので、プロシージャリターンシーケンスは、最初に、フェッチされるべき次のグループの命令を決定するそのアドレスを使用するために、リターンアドレスをソフトウェアスタックから取り出す必要がある。

#### 【0005】

プロシージャリターンシーケンスは、1つまたは複数の命令から成ることができる。いくつかのプロセッサーアーキテクチャにおいては、プロシージャリターンシーケンスは、次のリターンアドレスをソフトウェアスタックから読み取り、そしてプログラムカウンタ(program counter)(PC)をアップデートすることができる、POP命令やロード命令などの単一命令とすることができます。あるいは、プロセッサは、プロシージャリターンシーケンスを完了するためにその値をプログラムカウンタへと移動する前に、ソフトウェアスタックからGPRなどの中間レジスタへとリンクアドレスを読み取るためにPOP命令またはロード命令を使用することもできる。他の例示的な例においては、プロセッサは、プロシージャからのリターンが、リンクレジスタ(link register)(LR)に保存される値をPCへと移動する命令とすることを決定することができる。プロセッサが、プロシージャコールの後にこれらのプロシージャリターンシーケンスのうちのどれかに合うときに、プロセッサは、ソフトウェアスタックから取り出されるリターンアドレス値を使用してプロシージャ呼び出し命令に続く次の逐次命令へと後方にジャンプする。

#### 【0006】

追加のロジックは、命令処理の効率を改善するためにプロセッサのハードウェアに追加されることができる。例えば、リンクスタックは、命令フェッチを高速化するためにプロセッサのフェッチロジックに追加されることができる。当業者は、リンクスタックが、ソフトウェアスタック上にやはり存在することもできるリターンアドレスを含むことができることを認識する。しかしながら、リンクスタックは、ソフトウェアスタックとは独立して動作する。リンクスタックに関連するハードウェアロジックは、プロシージャのコールとリターンとを識別する。プロシージャコール命令が、実行に先立って識別されるときには、関連するリターンアドレスは、リンクスタック上へとロードされる。逆に、プロシージャリターンが、識別されるときには、関連するリターンアドレスは、リンクスタックから取り出され、そして命令フェッチを再開するために使用される。実行すべき命令を待つこと、ソフトウェアスタックからのリターンアドレスを取り出すこととの代わりに、プロセッサは、リンクスタックに記憶されるアドレスを使用して推測的に(speculatively)命令をフェッチすることができる。

#### 【0007】

プロセッサが進化するにつれて、プロシージャリターンシーケンスは、変化し続いている。いくつかのプロセッサーアーキテクチャにおいては、プロシージャリターンは、複数の命令から成ることができます。リンクスタックをサポートするハードウェアロジックが、これらの命令をプロシージャリターンシーケンスとして認識しない場合、リターンアドレスは、リンクスタックから取り出されなくともよく、そして結果としてリンクスタックは、命令シーケンスと同期が合わなくなる可能性がある。リンクスタックが同期が合わなくなるときに、リンクスタックは、複数のアドレス予測ミスを引き起こし得る誤ったリターンアドレス情報を提供する可能性がある。

10

20

30

40

50

**【発明の概要】**

**【0008】**

したがって、ある種の命令シーケンス、より詳細にはPOP(またはロード)およびブランチの命令シーケンスをプロシージャリターンシーケンスとして認識するプロセッサ回路を有する必要性が、産業界において存在している。本開示は、この必要性を認識し、そして命令パイプラインの中で早期にプロシージャリターンに対応する命令を識別する回路を有するプロセッサを開示している。プロシージャリターンを識別した後に、プロセッサは、リンクスタックからの次のリターンアドレスを使用することにより次のグループの命令をフェッチする。POPおよびブランチの命令シーケンスをプログラムリターンとして認識することにより、プロセッサは、リンクスタックから取り出される正しいアドレスに基づいて命令をフェッチすることを継続することができる。

**【0009】**

パイプラインプロセッサにおいてプロシージャから戻るときにリンクスタックからリターンアドレスを取り出すための方法が、開示される。本方法は、リンクスタックからリターンアドレスを取り出すように動作する検索命令(retrieve instruction)を識別する。本方法は、リターンアドレスへと分岐するように動作するブランチ命令を識別する。本方法は、識別される命令とブランチ命令との両方に応じてリンクスタックからリターンアドレスを取り出す。本方法は、リターンアドレスを使用して後続の命令をフェッチする。

**【0010】**

パイプラインプロセッサが、開示される。パイプラインプロセッサは、ラインバッファ(line buffer)を有する。ラインバッファは、命令キャッシュに結合される。プロセッサは、命令キャッシュに結合されるフェッチロジック回路も有する。フェッチロジック回路は、予測リターンアドレスを記憶するリンクスタックを有し、そこで命令は、ラインバッファから命令キャッシュへとロードされる。フェッチロジック回路は、命令キャッシュから命令を取り出す。パイプラインプロセッサは、ラインバッファと通信するプリデコードロジック回路(pre-decode logic circuitry)も有し、そこでプリデコードロジック回路は、プロシージャリターンシーケンスを識別するための検出口ロジック回路を有する。プロシージャリターンシーケンスは、ソフトウェアスタックからリターンアドレスを取り出すように動作する検索命令と、取り出されたリターンアドレスへと分岐するブランチ命令として識別される。パイプラインプロセッサは、プロシージャリターンシーケンスの識別に応じてリンクスタックから予測されたリターンアドレスを取り出す。

**【0011】**

パイプラインプロセッサが、開示される。パイプラインプロセッサは、フェッチロジック回路を有する。フェッチロジック回路は、予測されたリターンアドレスを記憶するリンクスタックを有する。フェッチロジック回路は、命令キャッシュから命令をフェッチする。パイプラインプロセッサは、フェッチロジック回路に結合されるデコードロジック回路も有し、そこでフェッチされた命令は、デコードロジック回路によって復号される。デコードロジック回路は、さらに検出口ロジック回路を有し、そこで検出口ロジック回路は、プロシージャリターンシーケンスを識別する。プロシージャリターンシーケンスは、ソフトウェアスタックからアドレスを取り出す検索命令と、取り出されたアドレスへと分岐するように動作するブランチ命令とである。パイプラインプロセッサは、プロシージャリターンシーケンスの識別に応じてリンクスタックから予測されたリターンアドレスを取り出す。パイプラインプロセッサは、プロシージャリターンの識別に応じてリンクスタックから予測されたリターンアドレスを取り出す。

**【0012】**

本発明のより完全な理解、ならびに本発明のさらなる特徴および利点は、以下の詳細な説明と、添付の図面とから明らかであろう。

**【図面の簡単な説明】**

**【0013】**

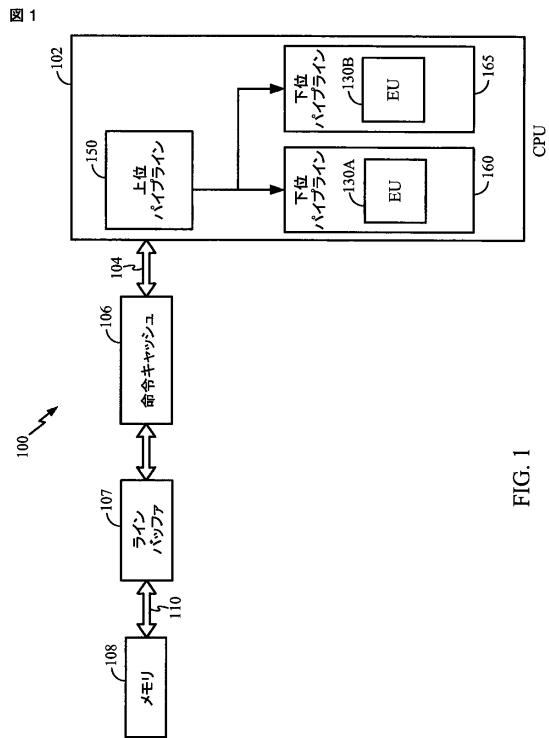

【図1】図1は、本発明の一実施形態を使用したプロセッサのハイレベルのロジックハー

10

20

30

40

50

ドウェアブロック図を示している。

【図2】図2は、図1のプロセッサによって実行される1つの例示のグループの命令を示している。

【図3】図3は、本発明の一実施形態に従って検出口ジック回路を組み込んだ、図1のCPUの上位パイプラインと下位パイプラインとのより詳細なブロック図を示している。

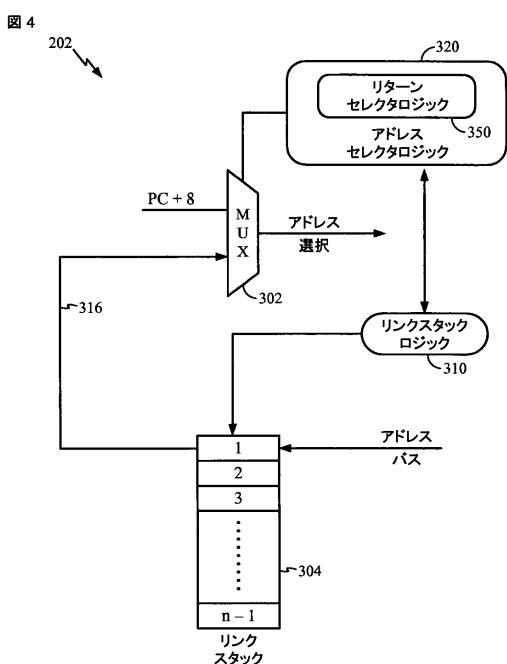

【図4】図4は、図3のフェッチロジック回路のより詳細な図を示している。

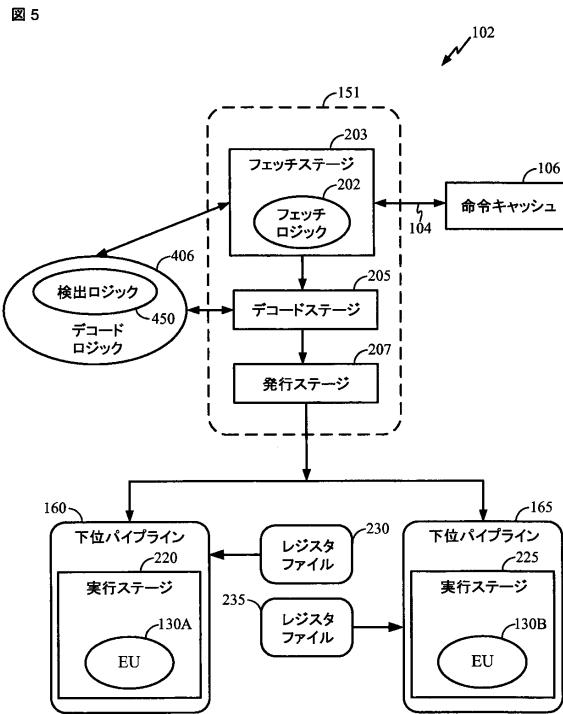

【図5】図5は、検出口ジック回路を利用した上位パイプラインと下位パイプラインとの代替実施形態を示している。

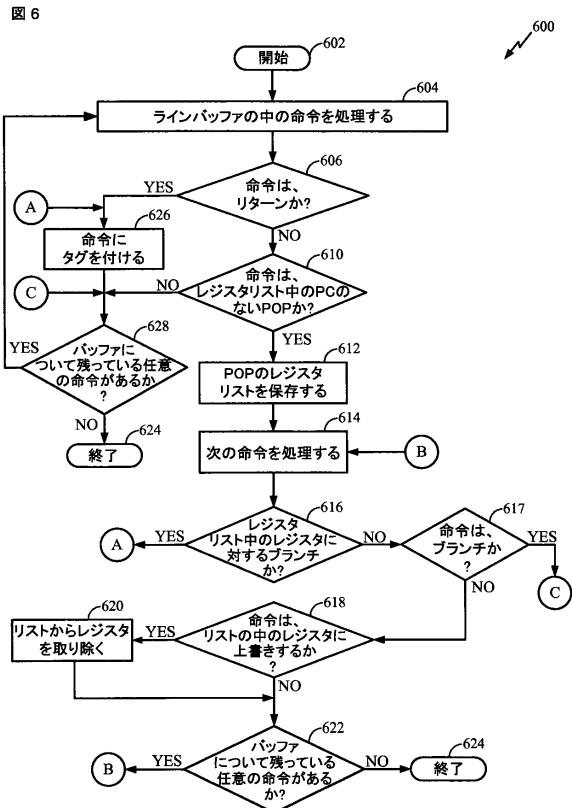

【図6】図6は、プログラムリターンを認識して、そして命令をフェッチするためにリンクスタックを使用して、図1のプロセッサによって実行される命令プロセスフローを示す10 フローチャートを示している。

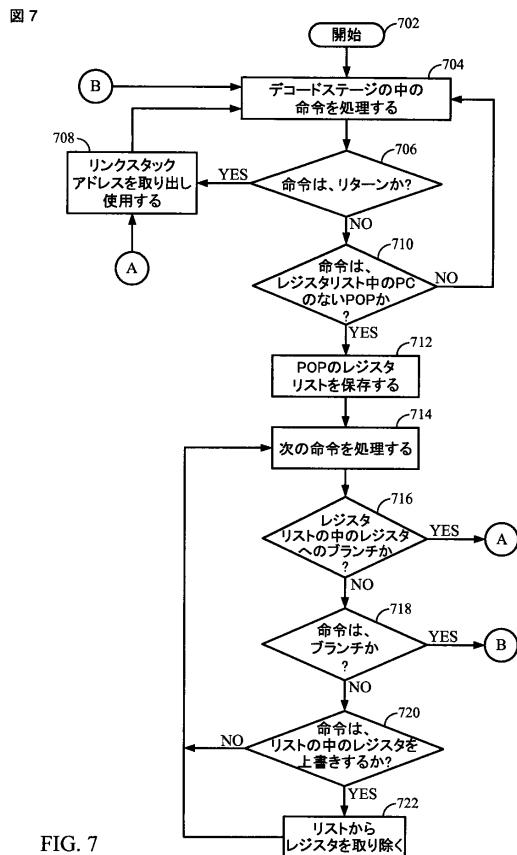

【図7】図7は、図4の上位パイプラインを使用してプロセッサによって実行される代替命令プロセスフローを示すフローチャートを示している。

【詳細な説明】

【0014】

添付の図面に関連して以下で述べられる詳細な説明は、本発明の様々な例示の実施形態の説明として意図され、そして本発明が実行されることができる唯一の実施形態を表すように意図されてはいない。詳細な説明は、本発明の完全な理解を提供する目的のための特定の詳細を含んでいる。しかしながら、本発明が、これらの特定の詳細なしに実行されることができるることは、当業者にとって明らかであろう。いくつかの例においては、よく知られている構造およびコンポーネントは、本発明の概念をあいまいにすることを回避するためにブロック図形式で示される。頭字語と、他の説明的な専門用語とは、単に便宜上、そして明快にするために使用されることができ、そして本発明の範囲を限定するように意図されてはいない。

【0015】

図1は、以下に説明されるように本発明の一実施形態を利用したスーパースカラプロセッサ(superscalar processor)100のハイレベル図を示している。プロセッサ100は、制御信号104を経由して命令キャッシュ106に結合される中央演算処理装置(central processing unit)(CPU)102を有する。命令キャッシュ106はまた、ラインバッファ107に、そして汎用バス110によってメモリ108にも結合される。CPU102は、ラインバッファ107を経由してメモリ108から命令キャッシュ106への命令のローディング/loading)を制御する。CPU102は、下位パイプライン160および165に結合された上位パイプライン150を有する。下位パイプライン160および165内には、実行ステージ220および225がある。実行ステージ220内には、実行ユニット(execution units)(EU)130Aがあり、そして実行ステージ225内には、EU130Bがある。

【0016】

当業者が理解するように、命令キャッシュ106は、メモリ108と、プロセッサ100との間の速度ギャップを埋めるように設計された専用メモリとすることができます。メモリ108からフェッチされる命令は、プロセッサのクロック速度で読み取られることができるより高速な命令キャッシュ106に配置される。命令が、命令キャッシュ106の中に存在しない場合、プロセッサ100は、メモリ108から命令を取り出す。命令が、メモリ108から取り出されるときに、それは、最初にラインバッファ107にロードされ、そして最終的には命令キャッシュ106へと書き込まれる。

【0017】

命令キャッシュ106が、命令でロードされた後に、CPU102は、制御信号104を経由してそれらにアクセスする。命令は、命令キャッシュ106から上位パイプライン150へとロードされる。命令は、上位パイプライン150の中で処理され、次いでさらなる処理のために下位パイプライン160または165へと送られる。図3～5の考察に関連して説明されるように、プロセッサは、特定の命令シーケンスを検出するように設計

10

20

30

40

50

されたロジック回路を有することができる。これらの特定の命令シーケンスは、プロシージャリターンに対応することができる。プロシージャリターン命令シーケンスが識別された後に、プロセッサ100は、本発明の複数の実施形態に従ってこれらの命令に基づいてファンクションを実行することができる。

#### 【0018】

上位パイプライン150の中の命令上で実行されるいくつかの例示の処理ファンクションは、命令をフェッチすることと、命令を位置合わせすること(alining)と、命令を復号することと、命令を下位パイプライン160または165に対して発行することなどを含むことができる。下位パイプライン160および165内において、命令は、実行ユニット130Aおよび130Bによって実行されることができ、それらの結果が、記録される。10

#### 【0019】

POPおよびブランチの命令シーケンスを使用したプロシージャリターンを有する実例のグループの命令200が、図2に示される。命令260と、命令のオペレーション270と、命令を実行するモジュール280とが、示されている。明確にする目的のために、プロシージャそれら自体による使用のためにソフトウェアスタック上でパラメータをプッシュすることになるどのような命令も、このグループの命令200から省略されている。プロシージャが実行する実際のファンクションを構成することになるどのような命令もまた、省略されている。図2に示される命令は、プロシージャを呼び出し、リターンアドレスをリンクレジスタ(この例においてはGPR R<sub>14</sub>)に保存し、リターンアドレスをソフトウェアスタック上に記憶し、ソフトウェアスタックからリターンアドレスを取り出し、そしてリターンアドレスに位置する命令を処理することを継続する命令である。グループの命令200は、それらが命令実行のトレース中にそうであるようなプログラム順序で図2に示されている。当業者は、トレースされた命令が、プロセッサがフェッチしている可能性がある実際のコードのサブセットであり、それらが実行されるべきであるように示されることを理解する。グループの命令200は、3つのネストされたプロシージャから成る。20

#### 【0020】

グループの命令200内には、3つのプロシージャコールと、それらの関連するリターンとがある。最初のプロシージャコールは、命令Aであり、この命令は、プロシージャPROC1を呼び出す。命令Bは、プロシージャPROC1内の準備命令(preparatory instruction)であり、現在のリターンアドレスをソフトウェアスタック上へと保存する。命令Cは、第2のプロシージャコール命令であり、プロシージャPROC2を呼び出す。命令Dは、プロシージャPROC2内の別の準備命令であり、PROC2に関連するリターンアドレスをソフトウェアスタック上へと保存する。最後のプロシージャコール命令は、命令Eであり、この命令は、プロシージャPROC3を呼び出す。30

#### 【0021】

プロシージャコール命令に対応してプロシージャリターン命令がある。最初のプロシージャリターン命令は、命令Fである。以前のプロセッサーアーキテクチャにおいては、命令Fは、プロシージャリターン命令として認識される。次の2つの命令、組み合わされた命令GおよびHは、別のプロシージャリターンを表す。一般に、以前のプロセッサーアーキテクチャにおいては、POP命令とブランチ命令との命令の組合せは、ハードウェアリンクスタックによる使用のためのプロシージャリターンとして適切に識別されない可能性がある。これらの以前のプロセッサにおける結果として、リンクスタック上の次のリターンアドレスは、命令GおよびHが識別されるときに取り出されない可能性がある。一実施形態を使用したプロセッサは、この可能なリンクスタック破損を軽減することができる。一実施形態においては、命令Hが、プロシージャリターン命令として識別された後に、プロセッサ100は、リンクスタックから次のアドレスを取り出し、そして命令をフェッチすることを継続するために取り出されたアドレスを使用することができる。この例においては、リンクスタック上の次のアドレスは、プロシージャPROC1を戻って指示し、そし4050

てより詳細には、それは命令 C に続く次の逐次命令（命令 I）を指示する。命令 H は、暗黙ブランチ命令 (implicit branch instruction) と称されることもできる。

#### 【0022】

次の 2 つの命令、命令 I および J はまた、プロシージャリターンシーケンスとしても解釈される。命令 J が、プロセッサ 100 によってプロシージャリターン命令として識別されるときに、リンクスタック上の次のアドレスは、取り出され、そして命令フェッチを継続するために使用される。命令 J は、明示ブランチ命令 (explicit branch instruction) である。この例においては、リンクスタックポイントを離れた次のアドレスは、プログラム実行を主プログラムへと逆に戻す。以前のプロセッサアーキテクチャにおいては、命令 I と J との組合せは、ハードウェアリンクスタックによる使用のためのプロシージャリターンシーケンスとして適切に識別されていない可能性がある。図 3 ~ 7 の考察においても 10 つと詳細に説明されるように、本発明の様々な実施形態は、POP とブランチとの命令の組合せをプロシージャリターンシーケンスとして識別する。

#### 【0023】

図 3 は、本発明の一実施形態を利用した CPU 102 のより詳細なブロック図を示している。CPU 102 内において、上位パイプライン 150 は、制御信号 104 によって命令キャッシュ 106 に結合された、フェッチロジック回路 202 を含むフェッチステージ 203 を有する。また CPU 102 の中には、検出口ロジック回路 250 を有するプリデコードロジック回路 201 がある。プリデコードロジック回路 201 は、命令キャッシュ 106 に結合されたラインバッファ 107 に結合される。フェッチステージ 203 は、順に発行ステージ 207 に結合されたデコードステージ 205 に結合される。デコードステージ 205 に結合されて、命令についての特有の情報を復号するデコードロジック回路（説明図を簡単にするために示されず）がある。発行ステージ 207 内には、下位パイプライン 160 および 165 に対して発行される命令に先立って命令を保持するいくつかの命令待ち行列（図示の容易のために図示せず）があつてもよい。

#### 【0024】

当業者が理解しうるよう、パイプラインステージは、命令を保持するように設計されたレジスタ、または 1 グループのレジスタを有することができる。命令が特定のステージに入ると、プロセッサ 100 は、その命令をそのステージにリンクされたレジスタ、または 1 グループのレジスタにロードする。命令が、各ステージ内のレジスタまたは 1 グループのレジスタに保持されるときに、ロジック回路は、命令に応じてある種のオペレーションを実行することができる。ロジック回路が、意図されたオペレーションを実行した後に、次いで命令は、次の逐次ステージへと渡される。さらに、命令が、上位パイプライン 150 の中にある間、それらは、様々なロジック回路によって「処理され」る。命令を処理することは、命令をフェッチすることと、命令を復号することと、命令を位置合わせすることと、命令を発行することなどを含むことができる。

#### 【0025】

命令は、上位パイプライン 150 に入り、そしてフェッチステージ 203 から発行ステージ 207 を通して移動する。命令は、フェッチステージ 203 中においてフェッチロジック回路 202 によってフェッチされる。命令がフェッチされた後に、それらは、デコードステージ 205 中においてデコードロジック回路によって復号される。デコードステージ 205 の後に、命令は、発行ステージ 207 の中で処理される。命令が、発行ステージ 207 を離れた後に、命令は、下位パイプライン 160 または下位パイプライン 165 のいずれかの中で実行される。上記に論じられるように、下位パイプライン 160 内には、実行ステージ 220 と EU130A とがある。下位パイプライン 165 内には、実行ステージ 225 と EU130B とがある。下位パイプライン 160 および 165 は、それぞれレジスタファイル 230 または 235 にアクセスする。

#### 【0026】

プリデコードロジック回路 201 は、命令が命令キャッシュ 106 に保存されるのに先立って命令についての情報を部分的に復号し、そして識別するためにプロセッサ 100 に

10

20

30

40

50

よって使用されることがある。プリデコードされた情報は、命令が命令キャッシュ 106 に記憶されるときに、命令と一緒に保存されることがある。プリデコードロジック回路 201 内において、検出口ロジック回路 250 は、命令の間の相互依存性を識別することができる。例えば、検出口ロジック回路 250 は、いつ P O P 命令とプランチ命令とが同じレジスタを利用するかを識別するように設計されることがある。図 4 の考察において説明されるように、検出口ロジック回路 250 が、P O P 命令とプランチ命令とから成る命令シーケンスをプロシージャコールからのリターンとして識別した後に、フェッчロジック回路 202 は、プランチ命令が命令キャッシュ 106 からフェッчされるときに、この情報を解釈する。

## 【0027】

プリデコードされた情報を命令に関連づけることは、命令が命令キャッシュ 106 にコードされるときに、命令に関連する情報フィールド内の特定のロケーションの中の 1 ビットを設定することによって遂行されることがある。プリデコードされた情報を命令キャッシュ 106 に保存することはまた、命令にフラグ付けすること(flagging)と称されることもできる。例えば、命令がプロシージャリターン命令であることを決定した後に、命令がプロシージャリターン命令であることを識別する命令ヘッダの中の 1 つのロケーションの中で、1 ビットが、設定されることがある。あるいは、プロセッサ 100 は、プリデコードされた情報を識別された 1 つまたは複数の命令についての命令ヘッダへと符号化することもできる。このようにして、プロセッサ 100 は、選択された、またはあらかじめ決定された判断基準に基づいて異なる命令についての異なる情報を符号化するために多ビットを使用することができる。プリデコードされた情報は、命令が命令キャッシュ 106 からフェッчされるときに、取り出されることがある。次いでプロセッサ 100 は、識別された情報に基づいてある種のファンクションを実行することができる。

## 【0028】

図 4 は、本発明の一実施形態によるフェッчロジック回路 202 を示している。フェッчロジック回路 202 は、アドレス選択  $m_{u \times}$  (マルチブレクサ) 302 を制御するアドレスセレクタロジック回路 320 を含んでいる。アドレスセレクタロジック回路 320 は、リターンセレクタロジック回路 350 を含んでいる。アドレス選択  $m_{u \times} 302$  の入力に結合されて、リンクスタック 304 に由来するリンクスタック出力 316 がある。リンクスタックロジック回路 310 は、アドレスセレクタロジック回路 320 と通信し、そしてリンクスタック 304 の入力と出力との両方を制御する。リンクスタック 304 は、プロシージャコールが識別されるときに、アドレスバスからリターンアドレスを受け取る。

## 【0029】

リンクスタック 304 内に、予測リターンアドレスは、保存されることがある。リンクスタック 304 は、プロシージャリターンに関連するリターンアドレスに対応する命令アドレスを記憶するメモリの後入れ先出し(last in first out) (LIFO) 部分とすることができる。リンクスタック 304 は、ソフトウェアスタックとは独立に動作する。命令が、命令パイプラインの中で早期にプロシージャリターン命令として識別されるときに、プロセッサ 100 は、下位パイpline 160 または 165 の中で実行すべきプロシージャリターンを待つ代わりに、リンクスタック上に記憶されるリターンアドレスを使用して命令を先んじてフェッчすることができる。

## 【0030】

図 4 に示されるように、アドレス選択  $m_{u \times} 302$  は、次の逐次プログラムアドレスを受け取ることができる。次の逐次プログラムアドレスは、8 つのアドレスロケーションだけ増分された現在のプログラムカウンタ (PC + 8) とすることができる。本実施形態においては、命令は、各命令が 4 バイトの長さである場合の一度に 2 命令を命令キャッシュ 106 からフェッчされる。他のプロセッサ実施形態において、次の逐次プログラムアドレスは、異なる量だけ増分されたプログラムカウンタとすることができる。上述されるように、アドレス選択  $m_{u \times} 302$  は、リンクスタック 304 から予測アドレス情報を受け取ることもできる。プロセッサ 100 が、プロシージャリターンが起こっていることを決

10

20

30

40

50

定するときに、リンクスタック 304 の中の次のアドレスは、取り出され、そして次のグループの命令をフェッチすべき開始ロケーションとして使用される。

#### 【0031】

アドレス選択  $m_u \times 302$  は、他のソースからアドレス情報を受け取ることができる。例えば、ブランチターゲットアドレスキャッシュ(branch target address cache) (BTAC) は、命令をフェッチするために使用されるアドレスを提供することができる。あるいは、割込みアドレス(interrupt address)が、命令をフェッチするために使用されることもできる。図示を容易にするために、アドレスのこれらの他のソースは、示されていない。

#### 【0032】

アドレスセレクタロジック回路 320 は、その入力のうちのどれが、アドレス選択  $m_u \times 302$  を通して渡され、そして次のグループの命令をフェッチするために使用されることになるかを決定する。アドレスセレクタロジック回路 320 が、フェッチされるべき次のグループのアドレスが次の逐次アドレス (PC + 8) であることを決定する場合、PC + 8 の入力が、選択される。あるいは、アドレスセレクタロジック回路 320 内のリターンセレクタロジック回路 350 が、リンクスタック 304 が次のフェッチアドレスを含むことを決定する場合には、リンクスタック出力 316 が、選択される。

#### 【0033】

リンクスタック 304 を利用するために、プロセッサ 100 は、いつプロシージャコールと対応するリターンとが、上位パイプライン 150 内の命令処理シーケンス中に識別されるかを決定する必要がある。リンクスタック 304 が、予測的に命令をフェッチするために使用されるので、プロセッサ 100 は、後続の命令をフェッチする前に実行すべき命令を待つことはない。その代わりに、プロセッサ 100 が、上位パイプライン 150 の中でプロシージャコール命令として識別した後に、プロセッサ 100 は、プロシージャコールに関連するリターンアドレスをアドレスバスを経由してリンクスタック 304 へとロードする。次いで、プロセッサ 100 は、プロシージャの命令をフェッチする。

#### 【0034】

プロシージャの終わりに、プロセッサ 100 は、プロシージャリターンシーケンスに出合う。プロシージャリターンシーケンスの結果として、プロセッサは、対応するリターンアドレスを取り出し、そして命令フェッチを再開するそのリターンアドレスへと分岐するように、リンクスタック 304 を「ポップする(pop)」ことになる。プロセッサ 100 は、プロシージャリターン命令を識別し、そしてリンクスタックから次のリターンアドレスを取り出す。プロシージャリターン命令は、ソフトウェアスタックを読み取り、そして PC を書き込む POP 命令またはロード命令とすることができます。リターンセレクタロジック回路 350 が、特定の POP 命令がプロシージャリターンであることを識別する場合、そのときにはリターンセレクタロジック回路 350 は、アドレスセレクタロジック回路 320 に、リンクスタック出力 316 が、アドレス選択  $m_u \times 302$  を通して方向づけられるようにするようにさせる。次いで、リンクスタック 304 から取られるリターンアドレスは、次の組の命令をフェッチするために使用される。

#### 【0035】

上記に説明されたように、プロシージャリターンシーケンスは、1つまたは複数の命令から成ることができる。例えば、いくつかの ARM インプリメンテーションにおいては、リンクレジスタ (R<sub>14</sub>) に記憶される値に対するブランチ命令は、プロシージャリターンとして解釈されることができる。代わりに、リンクレジスタ (R<sub>14</sub>) の値をプログラムカウンタ (R<sub>15</sub>) へと移動する移動命令は、プロシージャリターンとして解釈されることもできる。プロセッサ 100 が、正確にプロシージャリターンを識別することが、重要である。プロセッサ 100 が、正確にプロシージャリターンを識別しない場合には、リンクスタック 304 は、プロシージャリターン命令に関して同期が合わなくなることになる。リンクスタック 304 が、同期が合わなくなる場合、プロセッサ 100 は、ブランチ補正シーケンスへと進む必要がある可能性があり、そして実行性能は、影響を受ける可

10

20

30

40

50

性がある。

#### 【0036】

プロセッサ命令セットが、進化しているので、代替命令シーケンスは、プロシージャリターンシーケンスとして識別することができる。例示の一実施形態においては、特定のレジスタに記憶される値に対するブランチ命令によって追隨される特定のレジスタに対するリターンアドレスをポップするPOP命令またはロード命令（PCをアップデートしない）は、プロシージャリターンシーケンスとして解釈されることができる。ブランチ命令は、POP命令に続く次の逐次命令であってもよく、あるいはそうでなくてもよい。

#### 【0037】

POPおよびブランチの命令から成るプロシージャリターンシーケンスの識別を容易にするために、両方の命令に関連した情報が、集められる。プロシージャリターンのPOP命令は、1つまたは複数のレジスタに関与する可能性がある。POP命令が識別されるときに、POP命令のレジスタリストは、保存され、そして任意の後続の命令のレジスタターゲットと比較されることができる。レジスタリストの保存することと、比較することは、POP命令が、識別されていることを維持することと称されることもできる。非ブランチ命令が、そのレジスタに対するブランチが出合われる前に、POP命令に関連するレジスタリストの中で識別されるレジスタを利用する場合、そのレジスタは、保存済みのレジスタリスト(saved register list)から無視される(discounted)。保存済みのレジスタリストの中のレジスタを使用しないブランチ命令が、保存済みのレジスタリストの中のレジスタを使用するブランチ命令の前に出合われる場合、以前のPOPについてのPOP-ブランチリターンシーケンスについての探索(search)は、終了される。レジスタリストの中のレジスタを使用するブランチ命令が、出合われるときに、次いでプロセッサ100は、プロシージャリターンが、処理されていることを決定することができる。結果として、次いで、リンクスタック304の最上部におけるアドレスが、取り出され、そして次のグループの命令をフェッチするために使用されることができる。

#### 【0038】

前述のように、プリデコードロジック回路201(図3)は、同じレジスタを利用するPOPおよびブランチの命令シーケンスを識別している可能性があり、そして結果として、ブランチ命令は、プロシージャリターン命令として識別される。プロセッサ100は、ブランチ命令が、命令キャッシュ106に記憶されたときに、この情報を命令ヘッダに保存している可能性がある。フェッチロジック回路202が、ブランチ命令を用いて保存されたプリデコードされた情報を取り出すときに、プロセッサ100は、ブランチ命令がプロシージャリターンであることを識別するためにリターンセレクタロジック回路350を使用する。リターンセレクタロジック回路350が、ブランチ命令がプロシージャリターンであることを決定した後に、リターンセレクタロジック回路350は、アドレス選択ロジック回路320が、アドレス選択mux302を通してリンクスタック出力316を方向づけるようにする。リターンセレクタロジック回路350はまた、リンクスタックの中の次の値が、戻されるようにするリンクスタックロジック回路310と通信する。結果として、リンクスタックアドレスは、次の組の命令をフェッチするために使用される。

#### 【0039】

図5は、POP/ブランチ命令シーケンスから成るプロシージャリターンを検出することができるデコードロジック回路を有する代替実施形態に従って、上位パイプライン151を有するCPU102を示している。より詳細には、CPU102は、検出口ロジック回路450を有するデコードロジック回路406を含んでいる。命令が、デコードロジック回路406によって復号されるので、命令に関連した情報は、識別される。検出口ロジック回路450は、いつプロシージャリターンが識別されるかを決定するために復号された命令を監視することができる。以上で論じられるように、プロシージャリターンシーケンスは、1つまたは複数の命令から成る。検出口ロジック回路450は、POP命令と後続のブランチ命令とが復号されるときに、プロシージャリターンシーケンスが起こることを決定することができる。

10

20

30

40

50

## 【0040】

検出口ジック回路450が、プロシージャリターンが識別されていることを決定するときに、検出口ジック回路450は、この情報をリターンセレクタロジック回路350に対して伝え、このリターンセレクタロジック回路は、次にこの情報をリンクスタックロジック回路310に対して伝える(図4)。次いでリターンセレクタロジック回路350は、アドレスセレクタロジック回路320が、アドレス選択m<sub>UX302</sub>を通してリンクスタック出力316を方向づけるようとする。次いで、リンクスタック304から取られるリターンアドレスは、次の組の命令をフェッチするために使用される。

## 【0041】

実施形態に関連する発明の概念は、図2の中のグループの命令200を戻って参照することにより、さらに説明されることができる。命令Aは、プロシージャPROC1のコールである。命令Aが、PROC1へと分岐するときに、プロセッサ100は、次の逐次アドレスをリンクレジスタ(R<sub>14</sub>)に記憶する。次の逐次アドレスは、主プログラムに戻ることに関連するリターンアドレスである。命令Aが、プロシージャコールとして識別されるときに、リンクスタックロジック回路310は、命令Aに関連するリターンアドレスが、リンクスタック304へとロードされるようとする。図2に示されるように、命令Aは、主プログラムの一部分である。命令Aは、PROC1へと分岐し、そして次の処理された命令は、命令Bである。

10

## 【0042】

命令Bは、PROC1内の最初の命令であり、そしてプロシージャPROC2のコールのための準備命令である。命令Bは、R<sub>14</sub>の値をソフトウェアスタック上へとプッシュすることにより、現在のリターンアドレスを保存する。次に、命令Cが、処理される。命令Cは、プロシージャPROC2のコールである。命令Cが、プロシージャコールとして識別されるときに、リンクスタックロジック回路310は、命令Cに関連するリターンアドレスをリンクスタック304上へと保存する。命令Cは、プロシージャPROC2へと分岐し、そして処理される次の命令は、命令Dである。

20

## 【0043】

命令Dは、プロシージャPROC2内の最初の命令であり、そしてR<sub>14</sub>の値をソフトウェアスタック上へとプッシュすることにより現在のリターンアドレスを保存する。命令Dは、別の準備命令であり、次のプロシージャコール命令(命令E)についての準備を行う。命令Eが、プロシージャコールとして識別されるときに、リンクスタックロジック回路310は、命令Eに関連するリターンアドレスが、リンクスタック304上へとロードされるようとする。命令Eは、プロシージャPROC2内の2番目の命令であり、そしてプロシージャPROC3を呼び出す。命令Eは、命令F、プロシージャPROC3内の最初の命令、に関連するアドレスへと分岐する。命令Fは、プロシージャPROC3内の唯一の命令であり、そしてリターンである。特に、命令Fは、現在、リンクレジスタ(R<sub>14</sub>)の中の値へと分岐する。一般に、既存のプロセッサーアーキテクチャにおいては、命令Fは、命令リターンとして認識される。命令Fが処理されるときに、検出口ジック回路450は、命令Fがプロシージャリターンであることを決定し、そしてリンクスタック304上の次のリターンアドレスが、取り出されるようとする。プロセッサは、プロシージャPROC2へと戻すためにリターンアドレスを使用する。

30

## 【0044】

プロシージャPROC2内において、処理されるべき次の命令は、ソフトウェアスタックから現在の値を「ポップ」して出し、そしてそれをレジスタR<sub>12</sub>に保存する命令Gである。説明図を簡単にするために、命令Gは、単一のレジスタを「ポップ」する。しかしながら、代替実施形態においては、POP命令は、複数のレジスタについての複数の値を戻すことができる。この代替実施形態においては、プロセッサ100は、レジスタリストの中のこれらのレジスタのうちの1つをプランチターゲットアドレスとして使用して、レジスタリストを後続のプランチ命令と比較するために、「ポップされた」レジスタのリストを保持することができる。一実施形態においては、検出口ジック回路450は、「ポッ

40

50

プされた」レジスタのリストを記憶することができる。

#### 【0045】

命令Hは、今やR<sub>1,2</sub>の中にある取り出されたアドレスへと分岐する。たとえ命令Hが、明示プランチ命令(BX)でないとしても、それは同等なプランチ命令である。当業者が理解するように、MOV、PC、RNはまた、暗黙プランチ命令として解釈されることもできる。図6および7の命令フローチャート600および700の中で説明されるように、検出口ジック回路250、450は、「ポップされた」レジスタ(命令HのR<sub>1,2</sub>)に対するプランチ命令と一緒にPOP命令(命令G)が、プロシージャリターンシーケンスを構成することを決定する。結果として、プロセッサ100は、次のフェッチアドレスを提供するためにリンクスタック304を使用し、そして命令フェッチは、プロシージャPROC1へと戻る。10

#### 【0046】

命令Hを処理した後に、命令フェッチは、プロシージャPROC1へと戻り、そして命令Iを識別する。命令Iは、ソフトウェアスタックからの次の値をR<sub>2</sub>へとポップする。依然としてプロシージャPROC1内において、命令Jは、R<sub>2</sub>に記憶されるアドレスへと分岐する。命令Hと同様に、命令Jは、以前に「ポップされた」レジスタに記憶されるアドレスへと分岐する。結果として、検出口ジック回路250、450は、命令Jがプロシージャリターン命令であることを決定し、そしてリンクスタック304からの次の値が、次のグループの命令をフェッチするために使用される。この例においては、命令Jが処理された後に、命令Kが、フェッチされる。命令Kは、図3に示されるように、主プログラム内の任意の命令とすることができます。20

#### 【0047】

一実施形態においては、プロセッサ100は、命令Fと、命令GおよびHと、IおよびJとのシーケンスが、プロシージャリターンとして解釈されるべきであることを識別するために検出口ジック回路250を使用する。結果として、1組の命令200が、検出口ジック回路250によってラインバッファ107の中で出合われるときに、命令F、H、およびJは、命令キャッシュ106に保存されるプリデコードされた情報を用いてプロシージャリターン命令であるものとしてプリデコードされる。したがって、命令F、H、およびJが、フェッチロジック回路202によって命令キャッシュ106からフェッチされるときに、リターン選択ロジック回路350は、リターンアドレスが、次のグループの命令をフェッチするために使用されるリンク304から取り出されるようになる。30

#### 【0048】

代替実施形態においては、検出口ジック回路450は、命令Fと、命令GおよびHと、IおよびJとのシーケンスが、プロシージャリターンとして解釈されるべきであることを識別するように設計されることもできる。この場合には、グループの命令200が、デコードステージ205において復号されるときに、検出口ジック回路450は、命令F、H、およびJが、プロシージャリターン命令であることを識別し、そしてこれをリターンセレクタロジック回路350に伝える。次いでリターンセレクタロジック回路350は、リンクスタック304内の次のリターンアドレスが、次のフェッチアドレスを決定するために使用されるようになる。40

#### 【0049】

図6は、図3のCPU102内の検出口ジック回路250を有するプロセッサ100によって実行されるステップを示す命令フロー600を示している。図示を容易にするために、フローチャート600は、CPU102内のラインバッファ107が、単一の命令幅にすぎず、そしてそれらの命令は、キャッシュラインアドレスの開始からのシーケンスの中で戻されることを仮定している。当業者は、いくつかのプロセッサが、逐次順序を外れた複数の命令を処理することができるラインバッファを有することができることを理解する。ここにおいて説明されるような発明の概念は、いずれのタイプのプロセッサにも適用されることがある。

#### 【0050】

命令フロー 600 は、開始ブロック 602 から開始される。ブロック 602 から、命令フローは、ブロック 604 へと進み、ここでラインバッファ 107 の中の最初の命令は、検出口ジック回路 250 によって処理される。次いで、命令フロー 600 は、決定ブロック 606 へと進む。決定ブロック 606 において、検出口ジック回路 250 は、命令が知られているプロシージャリターンであるかどうかを決定する。前述のように、知られているプロシージャリターンは、POP / プランチシーケンスを除外して先に識別されたプロシージャリターンのうちのどれにすることもできる。決定ブロック 606 において、検出口ジック回路 250 が、命令が以上で知られているプロシージャリターンであることを決定する場合、命令フロー 600 は、ブロック 626 へと進み、ここで命令は、プロシージャリターンとして識別され、あるいはフラグ付けされる。決定ブロック 606 において、検出口ジック回路 250 が、命令が以上で知られているプロシージャリターンでないことを決定する場合には、命令フローは、決定ブロック 610 へと進む。

#### 【0051】

決定ブロック 610 において、検出口ジック回路 250 は、命令が、ポップされたレジスクリストの中にプログラムカウンタ (PC) を有さないPOP 命令であるかどうかを決定する。命令が、レジスクリストの中に PC のない POP 命令でない場合、命令フロー 600 は、決定ブロック 628 へと進む。そうでなくて命令がレジスクリストの中に PC を含まない POP 命令である場合には、命令フロー 600 は、ブロック 612 へと進む。ブロック 612 において、検出口ジック回路 250 は、任意の後続の命令を分析する際に使用のための POP 命令のレジスクリストをラインバッファ 107 に保存する。

#### 【0052】

ブロック 612 から、命令フローは、ブロック 614 へと進む。ブロック 614 において、検出口ジック回路 250 は、ラインバッファ 107 から次の命令を取り出す。プロセスフローは、ブロック 614 から決定ブロック 616 へと続く。決定ブロック 616 において、検出口ジック回路 250 は、ラインバッファ 107 の中の次の命令が、レジスクリストに保存されるレジスタのうちのどれかに対するプランチ命令であるかどうかを決定する。命令が、レジスクリストの中のレジスタに対するプランチである場合、命令フローは、ブロック 626 へと進み、ここで命令は、プロシージャリターン命令としてフラグ付けされる。決定ブロック 616 において、検出口ジック回路 250 が、命令が保存済みのレジスクリストの中のプランチ命令でないことを決定する場合、命令フロー 600 は、決定ブロック 617 へと続く。

#### 【0053】

決定ブロック 617 において、検出口ジック回路 250 は、命令が、プランチ命令であるかどうかを決定する。命令が、プランチ命令である場合、命令フローは、決定ブロック 628 へと進む。決定ブロック 617 において、検出口ジック回路 250 が、命令がプランチ命令でないことを決定する場合、命令フローは、決定ブロック 618 へと進む。決定ブロック 618 において、検出口ジック回路 250 は、命令が、保存済みのレジスクリストの中のレジスタのうちのどれかを上書きするかどうかを決定する。命令が、保存済みのレジスクリストの中のレジスタのうちのどれかを上書きする場合、命令フロー 600 は、ブロック 620 へと続き、ここで上書きされたレジスタは、保存済みのレジスクリストから取り除かれる。ブロック 620 から、命令フロー 600 は、決定ブロック 622 へと続く。

#### 【0054】

決定ブロック 618 において、検出口ジック回路 250 は、命令が、保存済みのレジスクリストの中の任意のレジスタを上書きしなかったことを決定する場合、命令フロー 600 は、決定ブロック 622 へと進む。決定ブロック 622 において、検出口ジック回路 250 は、ラインバッファ 107 について残っている任意の命令があるかどうかを決定する。ラインバッファについて残っている命令がない場合、命令フロー 600 は、ブロック 624 で終了する。ラインバッファ 107 の中に残っている命令がある場合、命令フロー 600 は、ブロック 614 へと戻って進み、ここでラインバッファ 107 の中の次の命令が

10

20

30

40

50

処理される。

#### 【0055】

ブロック626において、検出口ジック回路は、リターン命令として命令にタグを付ける。前述のように、リターン命令にタグを付けることは、フェッチロジック回路202が、命令が命令キャッシュ106からフェッチされるとときにリターン命令を識別することを可能にする。ブロック626から、命令フロー600は、決定ブロック628へと進む。決定ブロック628において、検出口ジック回路250は、ラインバッファ107の中に処理されるように残っている任意の命令があるかどうかを決定する。ラインバッファ107の中に処理されるように残っている命令がない場合、命令フロー600は、ブロック624において終了する。処理されるように残っている追加の命令がある場合には、命令フロー600は、ブロック604へと進み、ここで次の命令が、検出口ジック回路250によって処理される。

10

#### 【0056】

図7は、図4の上位パイプライン151に結合されたデコードロジック回路406の中に検出口ジック回路450を有するCPU102によって実行されるステップを示す命令フロー700を示している。図示を容易にするために、命令フロー700の中で概説される命令の処理は、デコードロジック回路406が、プロセッササイクル当たりに単一の命令を処理することを仮定している。当業者は、いくつかのプロセッサが、プロセッササイクル当たりに複数の命令を処理することができるデコードロジック回路を有することができることを理解する。ここにおいて説明される発明の概念は、いずれのタイプのプロセッサにも適用されることができる。

20

#### 【0057】

命令フロー700は、開始ブロック702から開始される。ブロック702から、命令フローは、ブロック704へと進み、ここで命令は、デコードロジック回路406によってデコードステージ205の中で処理される。ブロック704から、命令フローは、決定ブロック706へと続く。決定ブロック706において、検出口ジック回路450は、命令がプロシージャリターンであるかどうかを決定する。この例においては、検出口ジック回路450は、命令がPOP/プランチケンス以外の前もって知られているプロシージャリターンのうちのどれかである場合に、命令がプロシージャリターンであることを決定する。検出口ジック回路450が、命令がプロシージャリターンであることを決定する場合、命令フロー700は、ブロック708へと続く。検出口ジック回路450が、命令がプロシージャリターンでないことを決定する場合には、命令フローは、決定ブロック710へと続く。

30

#### 【0058】

決定ブロック710において、検出口ジック回路450は、命令が、レジスタリストの中にプログラムカウンタ(PC)を有さないPOP命令であるかどうかを決定する。命令が、そのレジスタリストの中にPCのないPOP命令でない場合、プロセスフローは、ブロック704へと後方に戻る。決定ブロック710において、検出口ジック回路450が、復号された命令が、そのレジスタリストの中にPCを含まないPOP命令であることを決定する場合、命令フロー700は、ブロック712へと続く。プロセッサ100は、ソフトウェアスタックから複数のレジスタをポップすることができる可能性があるので、ブロック712において、検出口ジック回路450は、ポップされたレジスタリストを保存する。ブロック712から、命令フロー700は、ブロック714へと進む。

40

#### 【0059】

ブロック714において、プロセッサ100は、次の命令をデコードステージ205へとロードし、そしてデコードロジック回路406は、その命令を処理する。命令が、ブロック714においてロードされた後に、命令フロー700は、決定ブロック716へと進む。決定ブロック716において、検出口ジック回路450は、命令が、保存済みのレジスタリストの中のレジスタに対するプランチであるかどうかを決定する。検出口ジック回路450が、命令が保存済みのレジスタリストの中のレジスタに対するプランチであるこ

50

とを決定する場合、プロセスフローは、ブロック708へと続く。検出口ジック回路450が、命令が保存済みのレジスタリストの中のレジスタに対するプランチ命令でなかったことを決定する場合には、命令フロー700は、決定ブロック718へと進む。

#### 【0060】

決定ブロック718において、検出口ジック回路450は、命令が、プランチ命令であるかどうかを決定する。命令が、プランチ命令である場合、命令フローは、ブロック704へと後方に戻り、ここで次の命令は、デコードステージ205へとロードされる。命令が、決定ブロック718においてプランチ命令でない場合には、命令フロー700は、決定ブロック720へと進む。決定ブロック720において、検出口ジック回路450は、命令が、保存済みのレジスタリストの中のレジスタを上書きするかどうかを決定する。

10

#### 【0061】

命令が、保存済みのレジスタリストの中のレジスタを上書きしない場合、命令フロー700は、ブロック714へと戻り、ここで次の命令は、デコードステージ205へとロードされ、そしてデコードロジック回路406によって処理される。命令が、決定ブロック720において保存済みのレジスタリストの中のレジスタを上書きする場合、命令フロー700は、ブロック722へと続き、ここで上書きされたレジスタは、保存済みのレジスタリストから取り除かれる。ブロック722から、命令フロー700は、ブロック714へと戻り、ここで次の命令は、デコードステージ205へとロードされ、そしてデコードロジック回路406によって処理される。

#### 【0062】

ここにおいて開示される実施形態に関連して説明される様々な例示の論理ブロック、モジュール、回路、要素、および／またはコンポーネントは、ここにおいて説明される機能を実行するように設計された汎用プロセッサ、デジタル信号プロセッサ(digital signal processor) (DSP)、特定用途向け集積回路(application specific integrated circuit) (ASIC)、フィールドプログラマブルゲートアレイ(field programmable gate array) (FPGA) または他のプログラマブルロジックコンポーネント、ディスクリートゲート(discrete gate) またはトランジスタロジック、ディスクリートハードウェアコンポーネント(discrete hardware components)、あるいはそれらの任意の組合せを用いてインプリメントされ、または実行されることができる。汎用プロセッサは、マイクロプロセッサとすることができるが、代替案においてはプロセッサは、従来の任意のプロセッサ、コントローラ、マイクロコントローラ、または状態機械とすることもできる。プロセッサは、コンピューティングコンポーネントの組合せ、例えば、DSPとマイクロプロセッサとの組合せ、複数のマイクロプロセッサ、DSPコアと組み合わされた1つまたは複数のマイクロプロセッサ、あるいは他のそのような任意のコンフィギュレーション、としてインプリメントされることもできる。

20

#### 【0063】

特定の実施形態が、ここにおいて示され、そして説明されているが、当業者は、同じ目的を達成するように予測される任意の構成が、示される特定の実施形態の代わりにされることができることと、本発明が、他の環境において他のアプリケーションを有することとを理解する。本願は、本発明の任意の適応または変形をカバーするように意図される。添付の特許請求の範囲は、ここにおいて説明される特定の実施形態だけに本発明の範囲を限定するように決して意図されない。

30

下記に出願時の請求項1 - 25に対応する記載を付記1 - 25として表記する。

#### 付記1

パイプラインプロセッサの中のプロシージャから戻るときにリンクスタックからリターンアドレスを取り出すための方法であって、

ソフトウェアスタックからリターンアドレスを取り出すように動作可能な検索命令を識別することと、

前記リターンアドレスへと分岐するように動作可能なプランチ命令を識別することと、

識別される前記命令と前記プランチ命令との両方に応じて、前記リンクスタックから前

40

50

記リターンアドレスを取り出すことと、

前記リターンアドレスを使用して後続の命令をフェッチすることと、

を備える方法。

付記 2

前記検索命令は、POP命令である、付記1に記載の方法。

付記 3

前記検索命令は、ロード命令である、付記1に記載の方法。

付記 4

前記ブランチ命令は、BX命令である、付記1に記載の方法。

付記 5

前記ブランチ命令は、MOV命令である、付記1に記載の方法。

10

付記 6

前記の前記検索命令を識別することは、前記リターンアドレスを含むレジスタを識別する

ことをさらに備える、付記1に記載の方法。

付記 7

前記検索命令を識別することは、レジスタリストを保持することをさらに備え、前記レ

ジスタリストは、複数のレジスタを有し、前記複数のレジスタの中の少なくとも1つのレ

ジスタは、前記リターンアドレスを含む、付記1に記載の方法。

付記 8

前記レジスタリストを保持することは、前記複数のレジスタのうちのどれかが、後続の

命令によって上書きされる場合に、前記レジスタリストからレジスタを取り除くことを備

える、付記7に記載の方法。

20

付記 9

前記ブランチ命令を識別することは、検出口ロジック回路によって実行される、付記1に

記載の方法。

付記 10

前記検出口ロジック回路は、プリデコードロジック回路と共に含まれる、付記9に記載の

方法。

付記 11

前記検出口ロジック回路は、デコードロジック回路と共に含まれる、付記9に記載の方法

30

。付記 12

前記ブランチ命令を識別することは、命令キャッシュの中の前記ブランチ命令にフラグ

付けすることをさらに備える、付記1に記載の方法。

付記 13

命令キャッシュに結合されたラインバッファと；

前記命令キャッシュに結合され、予測リターンアドレスを記憶するリンクスタックを有

するフェッチロジック回路と、なお命令は、前記ラインバッファから前記命令キャッシュ

へとロードされ、前記フェッチロジック回路は、前記命令キャッシュから命令を取り出

す；

40

前記ラインバッファと通信するプリデコードロジック回路と、なお前記プリデコードロ

ジック回路は、プロシージャリターンシーケンスを識別するための検出口ロジック回路をさ

らに備え、前記プロシージャリターンシーケンスは、ソフトウェアスタックからリターン

アドレスを取り出すように動作可能な検索命令と前記取り出されたリターンアドレスに分

岐するブランチ命令とを備え、前記バイラインプロセッサは、前記プロシージャリタ

ーンシーケンスの前記識別に応じて前記リンクスタックから前記予測されたリターンアドレ

スを取り出す；

を備えるバイラインプロセッサ。

付記 14

前記検出口ロジック回路は、前記ブランチ命令が、前記ラインバッファから前記命令キヤ

50

ツシュヘとロードされるときに、前記プロシージャリターンシーケンスの前記プランチ命令にフラグ付けする、付記 13 に記載のパイプラインプロセッサ。

付記 15

前記フェッチロジック回路は、前記フラグ付けされた情報から前記プロシージャリターンシーケンスを識別する、付記 14 に記載のパイプラインプロセッサ。

付記 16

前記フェッチロジック回路内のリターンセレクタロジック回路は、前記フラグ付けされた情報から前記リターンシーケンスを識別する、付記 15 に記載のパイプラインプロセッサ。

付記 17

10

前記検索命令は、POP 命令である、付記 13 に記載のパイプラインプロセッサ。

付記 18

前記検索命令は、ロード命令である、付記 13 に記載のパイプラインプロセッサ。

付記 19

前記プランチ命令は、BX 命令である、付記 13 に記載のパイプラインプロセッサ。

付記 20

予測されたリターンアドレスを記憶するリンクスタックを有し、命令キャッシュから命令をフェッチするフェッチロジック回路と、

前記フェッチロジック回路に結合されたデコードロジック回路と、

を備え、前記フェッチされた命令は、前記デコードロジック回路によって復号され、前記デコードロジック回路は、検出口ロジック回路をさらに備え、前記検出口ロジック回路は、ソフトウェアスタックからアドレスを取り出すように動作可能な検索命令と、前記取り出されたアドレスに分岐するように動作可能なプランチ命令とを備えるプロシージャリターンシーケンスを識別し、パイプラインプロセッサは、前記プロシージャリターンシーケンスの前記識別に応じて前記リンクスタックから前記予測されたリターンアドレスを取り出す、パイプラインプロセッサ。

20

付記 21

前記フェッチロジック回路は、前記取り出されたアドレスを使用して命令をフェッチする、付記 20 に記載のパイプラインプロセッサ。

付記 22

30

前記検索命令は、POP 命令である、付記 20 に記載のパイプラインプロセッサ。

付記 23

前記検索命令は、ロード命令である、付記 20 に記載のパイプラインプロセッサ。

付記 24

前記プランチ命令は、前記検索命令によって識別されるアドレスへと分岐する、付記 20 に記載のパイプラインプロセッサ。

付記 25

前記プランチ命令は、MOV 命令である、付記 20 に記載のパイプラインプロセッサ。

【図1】

【図2】

図2

| 命令:    | オペレーション:                | モジュール: |

|--------|-------------------------|--------|

| 260    | 270                     | 280    |

| A:     | BL PROC1                | MAIN   |

| PROC1: | B: PUSH R <sub>14</sub> | PROC1  |

|        | C: BL PROC2             | PROC1  |

| PROC2: | D: PUSH R <sub>14</sub> | PROC2  |

|        | E: BL PROC3             | PROC2  |

| PROC3: | F: BX R <sub>14</sub>   | PROC3  |

|        | G: POP R <sub>12</sub>  | PROC2  |

| H:     | MOV PC, R <sub>12</sub> | PROC2  |

| I:     | POP R <sub>2</sub>      | PROC1  |

| J:     | BX R <sub>2</sub>       | PROC1  |

| K:     | ANY                     | MAIN   |

FIG. 2

【図3】

【図4】

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

---

フロントページの続き

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 モロウ、マイケル・ウイリアム

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ディーフエンダーファー、ジェームズ・ノリス

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 清木 泰

(56)参考文献 特開2001-100993(JP,A)

特開平07-281892(JP,A)

特開平07-239782(JP,A)

特開2003-256197(JP,A)

米国特許第05812813(US,A)

米国特許第06374350(US,B1)

本永朝雄, 6809アセンブリプログラミング, 日本, 株式会社サイエンス社, 1986年11月2

5日, Pages:62-68

Stephen B. Furber, VLSI RISC Architecture and Organization, 米国, Marcel Dekker Inc.,

1989年, Pages:231-233

(58)調査した分野(Int.Cl. , DB名)

G 0 6 F 9 / 3 0 - 9 / 4 2