(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-45370

(P2018-45370A)

(43) 公開日 平成30年3月22日(2018.3.22)

(51) Int.Cl.

**G06F 9/38 (2006.01)**

**G06F 9/30 (2018.01)**

**G06F 9/318 (2006.01)**

F 1

GO6F 9/38

GO6F 9/38

GO6F 9/30

GO6F 9/30

テーマコード(参考)

5B013

5B033

審査請求 未請求 請求項の数 12 O L (全 35 頁)

(21) 出願番号

(22) 出願日

特願2016-178608 (P2016-178608)

平成28年9月13日 (2016.9.13)

(71) 出願人 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100072718

弁理士 古谷 史旺

(74) 代理人 100151002

弁理士 大橋 剛之

(74) 代理人 100201673

弁理士 河田 良夫

(72) 発明者 坂下 聰太

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

F ターム(参考) 5B013 AA12 CC10

5B033 BB00 BE05

(54) 【発明の名称】演算処理装置および演算処理装置の制御方法

## (57) 【要約】

【課題】複合命令を実行する演算処理装置の性能を向上する。

【解決手段】演算処理装置は、命令をデコードするデコード部と、デコード部がデコードした命令を保持し、保持した命令を実行可能な順に出力する実行制御部と、実行制御部が出力する命令を順次転送する命令転送部と、命令転送部が転送する命令が複数の個別命令を組み合わせた複合命令である場合、複合命令から生成した個別命令を命令転送部に出力する命令生成部と、命令転送部が転送した個別命令を実行する演算実行部を有する。

【選択図】 図 1

**【特許請求の範囲】****【請求項 1】**

命令をデコードするデコード部と、

前記デコード部がデコードした命令を保持し、保持した命令を実行可能な順に出力する実行制御部と、

前記実行制御部が出力する命令を順次転送する命令転送部と、

前記命令転送部が転送する命令が複数の個別命令を組み合わせた複合命令である場合、前記複合命令から生成した個別命令を前記命令転送部に出力する命令生成部と、

前記命令転送部が転送した個別命令を実行する演算実行部を有することを特徴とする演算処理装置。

10

**【請求項 2】**

前記命令生成部が前記複合命令に含まれる個別命令を前記命令転送部に出力する場合、前記実行制御部に命令の出力を抑止させる抑止情報を出力する抑止制御部を有することを特徴とする請求項 1 記載の演算処理装置。

**【請求項 3】**

前記実行制御部が出力する前記複合命令は、前記複合命令であることを識別する識別情報を含み、

前記抑止制御部は、前記実行制御部が出力する前記識別情報を基づいて、前記抑止情報を出力することを特徴とする請求項 2 記載の演算処理装置。

20

**【請求項 4】**

前記命令転送部は、前記抑止制御部が前記抑止情報を出力しない場合、前記実行制御部が出力する前記識別情報を選択し、前記抑止制御部が前記抑止情報を出力する場合、命令が前記複合命令でないことを示す識別情報を選択する第 1 の選択部を有し、前記第 1 の選択部で選択した識別情報を転送することを特徴とする請求項 3 記載の演算処理装置。

**【請求項 5】**

前記命令転送部は、前記抑止制御部が前記抑止情報を出力しない場合、前記実行制御部が出力する命令を選択し、前記抑止制御部が前記抑止情報を出力する場合、前記命令生成部が出力する個別命令を選択する第 2 の選択部を有し、前記第 2 の選択部で選択した命令を転送することを特徴とする請求項 2 ないし請求項 4 のいずれか 1 項記載の演算処理装置。

30

**【請求項 6】**

前記実行制御部が出力する命令は、命令が有効であることを示す有効情報を含み、

前記命令転送部は、前記実行制御部が出力する有効情報を前記抑止情報を有効情報として前記演算実行部に転送する論理和部を有することを特徴とする請求項 2 ないし請求項 5 のいずれか 1 項記載の演算処理装置。

**【請求項 7】**

前記命令生成部は、前記実行制御部が前記複合命令を出力する場合、前記複数の個別命令のうち、前記演算実行部による実行順が 2 番目以降の個別命令を生成し、

前記命令転送部は、前記実行制御部が前記複合命令を出力する場合、前記複合命令の転送に続いて、前記命令生成部が生成する実行順が 2 番目以降の個別命令を転送し、

40

前記演算実行部は、前記複合命令を受信した場合、前記複数の命令のうち実行順が最初の命令を実行することを特徴とする請求項 1 ないし請求項 6 のいずれか 1 項記載の演算処理装置。

**【請求項 8】**

前記命令転送部は、

前記実行制御部が出力する命令を受信する第 1 のステージと、

前記第 1 のステージから転送される命令を前記演算実行部に出力する第 2 のステージを有し、

前記命令生成部は、前記第 2 のステージに転送される命令が前記複合命令の場合、前記実行順が 2 番目以降の個別命令を前記第 1 のステージに出力することを特徴とする請求項

50

7 記載の演算処理装置。

【請求項 9】

前記実行制御部が順次出力する先行命令および後続命令が、前記先行命令の演算結果を前記後続命令で使用する所定の組み合わせの特定命令であることを検出する依存検出部を有し、

前記命令転送部は、前記実行制御部が出力する命令が前記複合命令の場合、または、前記依存検出部が前記特定命令を検出した場合、前記実行制御部の出力の選択を停止し、前記命令生成部の出力を選択する選択部を有し、

前記命令生成部は、前記実行制御部が出力する命令が前記複合命令の場合、前記複合命令に含まれる個別命令を前記命令転送部に出力し、前記実行制御部が出力する命令が前記複合命令でない場合、前記命令転送部で転送された命令を前記命令転送部に出力することを特徴とする請求項 1 記載の演算処理装置。 10

【請求項 10】

前記命令生成部が前記複合命令に含まれる個別命令を前記命令転送部に出力する場合、または前記依存検出部が前記特定命令を検出した場合、前記実行制御部に命令の出力を抑止させる抑止情報を出力する抑止制御部を有し、

前記選択部は、前記抑止制御部が前記抑止情報を出力しない場合、前記実行制御部が出力する命令を選択し、前記抑止制御部が前記抑止情報を出力する場合、前記命令生成部が出力する命令を選択することを特徴とする請求項 9 記載の演算処理装置。 20

【請求項 11】

前記実行制御部が出力する命令は、命令が有効であることを示す有効情報を含み、

前記命令転送部は、前記依存検出部が前記特定命令を検出した場合、前記実行制御部が出力した前記後続命令に含まれる有効情報を無効状態に設定する無効設定部を有することを特徴とする請求項 9 または請求項 10 記載の演算処理装置。 20

【請求項 12】

演算処理装置の制御方法において、

前記演算処理装置が有するデコード部が、命令をデコードし、

前記演算処理装置が有する実行制御部が、前記デコード部がデコードした命令を保持し、保持した命令を実行可能な順に出力し、

前記演算処理装置が有する命令転送部が、前記実行制御部が出力する命令を順次転送し、 30

前記命令転送部が転送する命令が複数の個別命令を組み合わせた複合命令である場合、前記演算処理装置が有する命令生成部が、前記複合命令から生成した個別命令を前記命令転送部に出力し、

前記演算処理装置が有する演算実行部が、前記命令転送部が転送した個別命令を実行することを特徴とする演算処理装置の制御方法。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、演算処理装置および演算処理装置の制御方法に関する。 40

【背景技術】

【0002】

プロセッサ等の演算処理装置は、デコード部がデコードした命令をリザベーションステーションに保持し、演算実行部で実行する命令の順序をデータの依存関係に応じて入れ換えるアウトオブオーダ処理を実行する。実行可能な順に命令を実行することで、デコードされた順に命令を実行する場合に比べて、命令の実行効率は向上する。ところで、乗算、減算に加えて加算、減算が実行可能な乗算器に命令を投入する第1のリザベーションステーションと、加算、減算のみが実行可能な加算器に命令を投入する第2のリザベーションステーションとを有する演算処理装置が提案されている。演算処理装置は、第1および第2のリザベーションステーションのそれぞれに対応して、デコードした命令をリザベシ 50

ヨンステーションに投入する前に保持する第1のレジスタと第2のレジスタとを有する。

#### 【0003】

第1および第2のレジスタのいずれかから出力される乗算命令または除算命令は、専用のレジスタに格納する先行フローと、専用のレジスタに格納された乗算命令または除算命令を第1のリザベーションステーションに投入する後続フローとに展開される。これにより、第1および第2のレジスタに加算命令または減算命令のみが保持される場合、デコードサイクルでのリザベーションステーションへの命令の投入に掛かる時間は、命令を複数のフローに展開しない場合に比べて短縮される（例えば、特許文献1参照）。

#### 【0004】

また、デコードした命令に対応するマイクロプログラムの制御情報を、フロー毎に保持する制御リザベーションステーションを設けることで、アウトオブオーダで実行される命令は、マイクロプログラムにより制御可能になる（例えば、特許文献2参照）。

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

【特許文献1】特開2004-38751号公報

【特許文献2】特開2000-181702号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

命令をデコードするデコード部が、複数の個別命令を組み合わせた複合命令を複数の個別命令に分解する機能を有する場合、分解された複数の個別命令は、リザベーションステーションに投入される。この場合、リザベーションステーションの使用率は、複合命令をリザベーションステーションに投入する場合に比べて上昇し、アウトオブオーダの効率は低下する。

#### 【0007】

1つの側面では、本発明は、複合命令を実行する演算処理装置の性能を向上することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

一つの観点によれば、演算処理装置は、命令をデコードするデコード部と、デコード部がデコードした命令を保持し、保持した命令を実行可能な順に出力する実行制御部と、実行制御部が出力する命令を順次転送する命令転送部と、命令転送部が転送する命令が複数の個別命令を組み合わせた複合命令である場合、複合命令から生成した個別命令を命令転送部に出力する命令生成部と、命令転送部が転送した個別命令を実行する演算実行部を有する。

#### 【0009】

別の観点によれば、演算処理装置の制御方法は、演算処理装置が有するデコード部が、命令をデコードし、演算処理装置が有する実行制御部が、デコード部がデコードした命令を保持し、保持した命令を実行可能な順に出力し、演算処理装置が有する命令転送部が、実行制御部が出力する命令を順次転送し、命令転送部が転送する命令が複数の個別命令を組み合わせた複合命令である場合、演算処理装置が有する命令生成部が、複合命令から生成した個別命令を命令転送部に出力し、演算処理装置が有する演算実行部が、命令転送部が転送した個別命令を実行する。

#### 【発明の効果】

#### 【0010】

複合命令を実行する演算処理装置の性能を向上することができる。

#### 【図面の簡単な説明】

#### 【0011】

【図1】演算処理装置および演算処理装置の制御方法の一実施形態を示す図である。

10

20

30

40

50

【図2】図1に示す演算処理装置の動作の一例を示す図である。

【図3】演算処理装置および演算処理装置の制御方法の別の実施形態を示す図である。

【図4】図3に示すレジスタ管理部およびレジスタ部の一例を示す図である。

【図5】図3に示す演算処理装置における固定小数点演算器に対応する命令パイプラインの概要を示す図である。

【図6】図5に示す命令パイプラインにおいて、ステージPからステージXまでに関連する回路要素の一例を示す図である。

【図7】図5および図6に示す命令パイプラインにおいて、オペランドデータをバイパスさせるタイミングの一例を示す図である。

【図8】図3に示す演算処理装置の動作の一例を示す図である。

10

【図9】図3に示す演算処理装置の動作の別の例を示す図である。

【図10】図6に示す命令パイプラインにおけるPサイクルおよびPTサイクルでの動作フローの一例を示す図である。

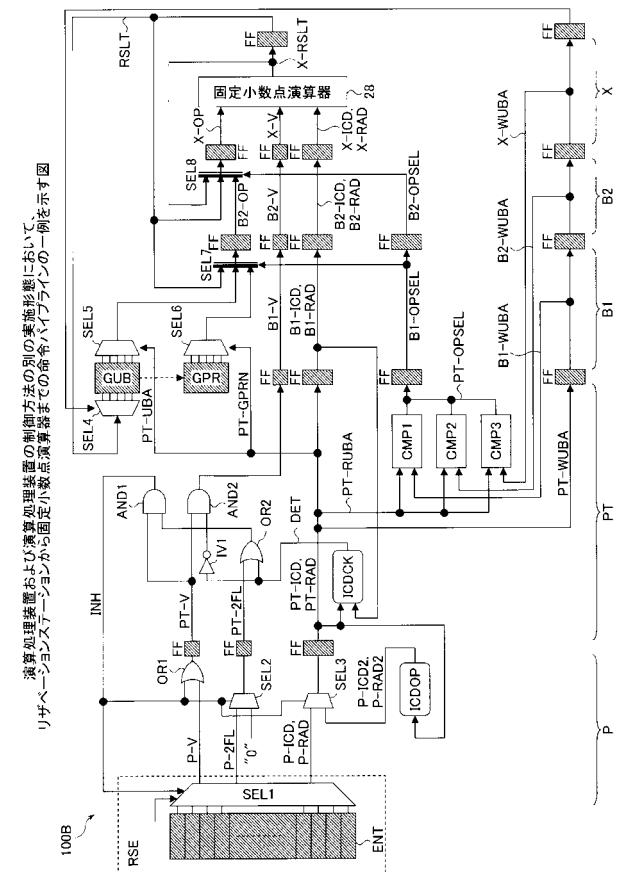

【図11】演算処理装置および演算処理装置の制御方法の別の実施形態において、リザベーションステーションから固定小数点演算器までの命令パイプラインの一例を示す図である。

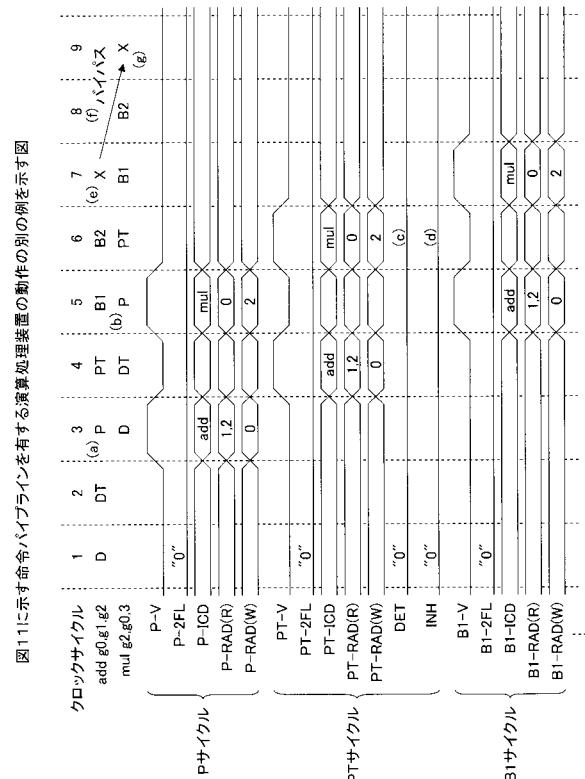

【図12】図11に示す命令パイプラインを有する演算処理装置の動作の一例を示す図である。

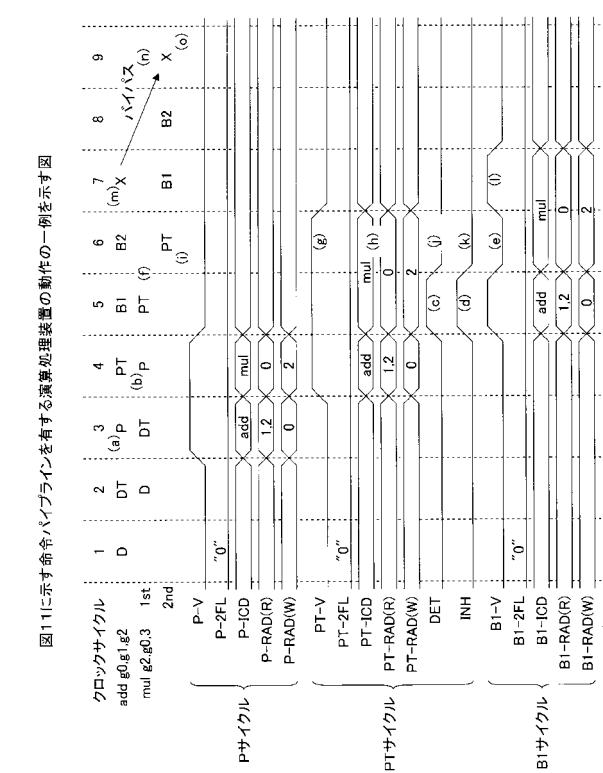

【図13】図11に示す命令パイプラインを有する演算処理装置の動作の別の例を示す図である。

20

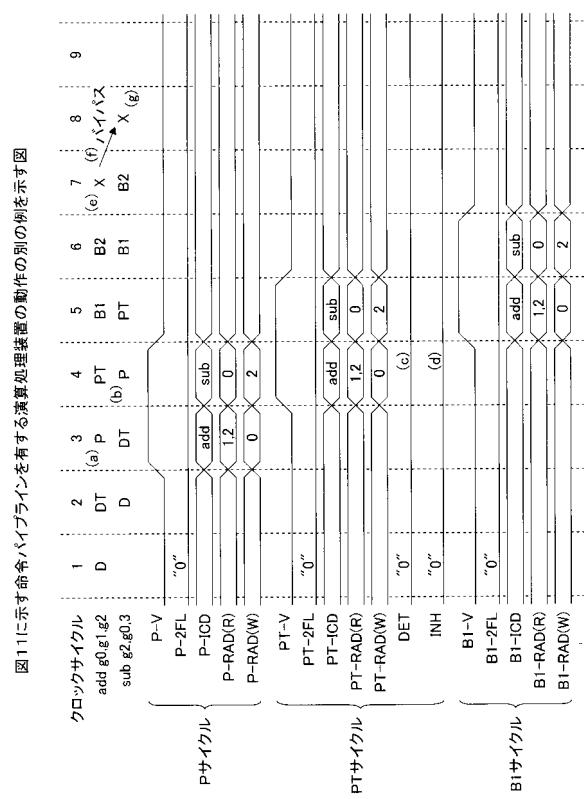

【図14】図11に示す命令パイプラインを有する演算処理装置の動作の別の例である。

【図15】図11に示す命令パイプラインにおけるPサイクルおよびPTサイクルでの動作フローの一例を示す図である。

【発明を実施するための形態】

【0012】

以下、図面を用いて実施形態を説明する。

【0013】

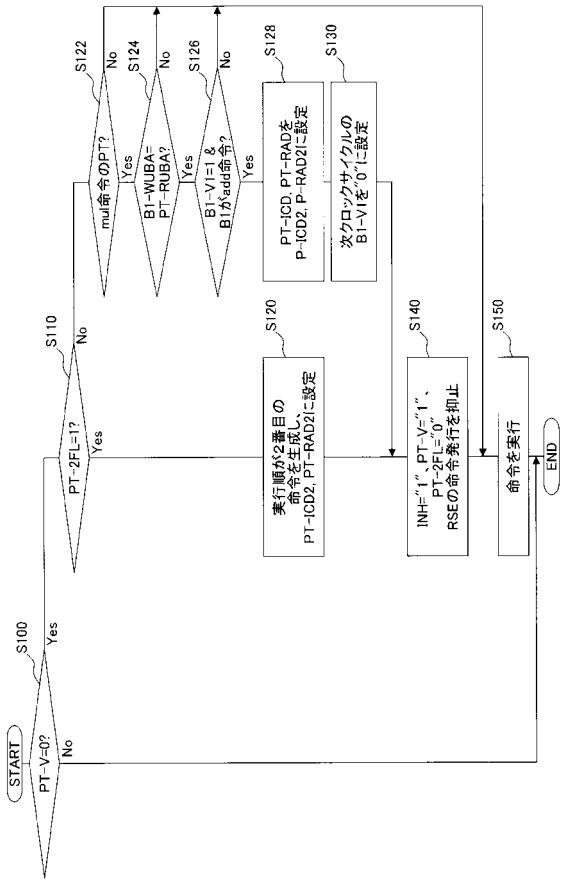

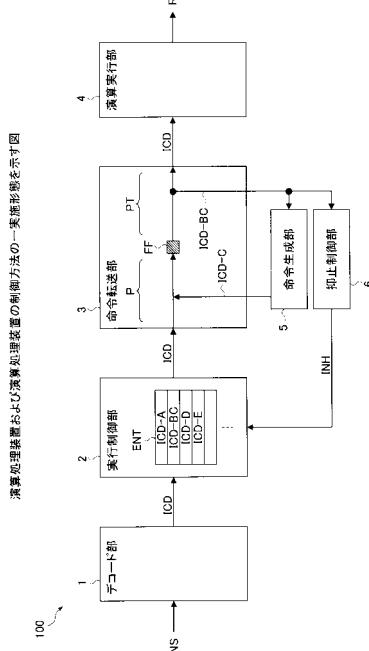

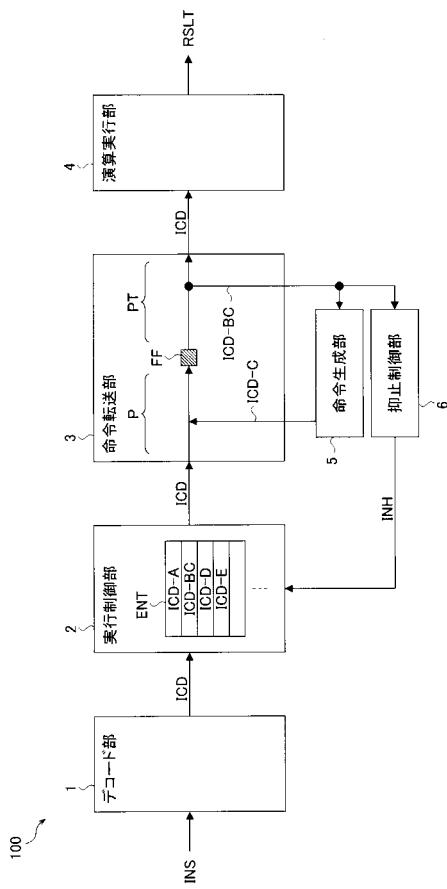

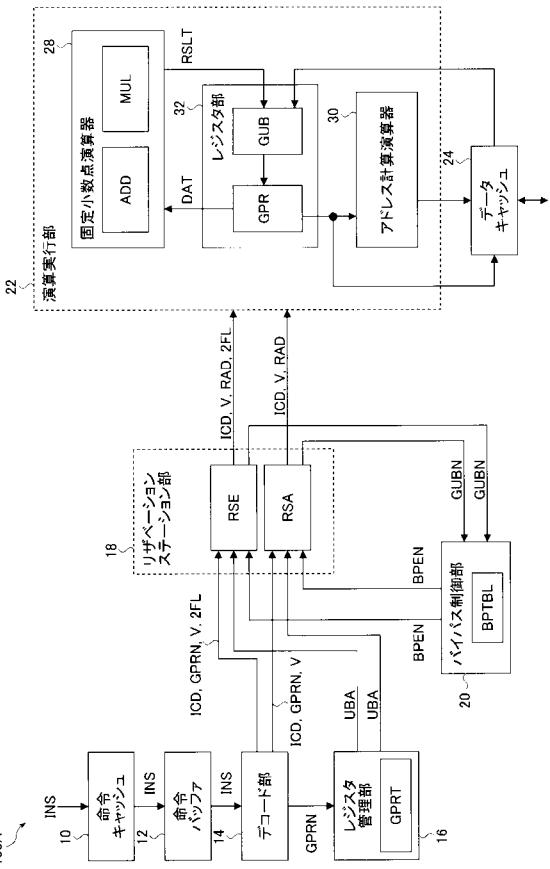

図1は、演算処理装置および演算処理装置の制御方法の一実施形態を示す。図1に示す演算処理装置100は、CPU(Central Processing Unit)等のプロセッサであり、デコード部1、実行制御部2、命令転送部3、演算実行部4、命令生成部5および抑止制御部6を有する。

30

【0014】

デコード部1は、命令キャッシュ等から出力される命令INSをデコードし、デコードにより得られた命令コードICDおよびレジスタ番号等を実行制御部2に出力する。以下の説明では、デコードにより得られた命令コードICDおよびレジスタ番号等の情報は、命令ICDとも称される。実行制御部2は、デコード部1から出力される命令ICDを保持する複数のエントリENTを有し、エントリENTに保持した命令ICDを実行可能な順に出力するアウトオブオーダ処理を実行する。但し、実行制御部2は、抑止情報INHを受けている間、命令ICDの出力を抑止する。

【0015】

命令転送部3は、実行制御部2が出力する命令ICDを順次転送し、演算実行部4に出力する。例えば、命令転送部3は、クロックに同期して命令ICDを保持するフリップフロップFFFを挟んで、ステージPの処理部とステージPTの処理部とを有し、命令パイプラインの一部として機能する。以下の説明では、ステージPの処理部とステージPTの処理部とは、ステージP、ステージPTとも称される。ステージPは、実行制御部2から出力される命令ICDを受信してフリップフロップFFFに出力する。ステージPTは、フリップフロップFFFに命令を保持し、保持した命令ICDを演算実行部4に出力する。

【0016】

命令生成部5は、命令転送部3で転送される命令ICDが複数の個別命令ICD-B、ICD-Cを組み合わせた複合命令ICD-BCであることを検出した場合、複合命令I

40

50

C D - B C に含まれる個別命令 I C D - C を生成する。個別命令 I C D - C は、複合命令 I C D - B C に含まれる個別命令 I C D - B 、 I C D - C のうち、演算実行部 4 による実行順が 2 番目の命令である。命令生成部 5 は、生成した個別命令 I C D - C を命令転送部 3 に出力する。例えば、命令生成部 5 は、ステージ P T で転送される複合命令 I C D - B C を検出した場合、複合命令 I C D - B C に含まれる個別命令 I C D - C を生成し、生成した個別命令 I C D - C をステージ P に出力する。なお、デコード部 1 は、複合命令 I N S を複数の個別命令 I C B - B 、 I C B - C に分解する機能を持たないため、複合命令 I N S を受信した場合、複合命令 I N S を示す命令コード I C D を生成して実行制御部 2 に出力する。

## 【 0 0 1 7 】

10

演算実行部 4 は、命令転送部 3 から転送される命令 I C D が示す演算を実行し、演算結果 R S L T を出力する。但し、演算実行部 4 は、複合命令 I C D - B C を受信した場合、複合命令 I C D - B C に含まれる複数の個別命令 I C D - B 、 I C D - C のうち実行順が最初の個別命令 I C D - B を実行する。なお、図 1 では、演算結果 R S L T を格納するレジスタと、演算結果 R S L T をレジスタに格納する前に演算実行部 4 内の演算器にバイパスする経路とは省略される。

## 【 0 0 1 8 】

20

抑止制御部 6 は、命令転送部 3 のステージ P T で転送される命令 I C D が複合命令 I C D - B C であることを検出した場合、実行制御部 2 に命令の出力を抑止させる抑止情報 I N H を、実行制御部 2 に出力する。すなわち、抑止制御部 6 は、命令生成部 5 が複合命令 I C D - B C に含まれる個別命令 I C D - C を命令転送部 3 に出力する場合、抑止情報 I N H を出力する。

## 【 0 0 1 9 】

30

なお、命令生成部 5 は、ステージ P における命令 I C D が複合命令 I C D - B C であることを検出した場合、複合命令 I C D - B C に含まれる個別命令 I C D - B と個別命令 I C D - C とをステージ P に順次出力してもよい。この場合、抑止制御部 6 は、命令転送部 3 のステージ P で転送される命令 I C D が複合命令 I C D - B C であることを検出した場合、抑止情報 I N H を 2 クロックサイクルにわたり出力する。また、命令転送部 3 のステージ P は、抑止情報 I N H の出力中、実行制御部 2 からの命令 I C D の受信を停止し、命令生成部 5 からの個別命令 I C D - B 、 I C D - C を選択してフリップフロップ F F に出力する選択部を有する。これにより、演算実行部 4 は、複合命令 I C D - B C を命令 I C D - B として解釈することなく、受信した個別命令 I C D - B 、 I C D - C の演算を順次実行することができる。

## 【 0 0 2 0 】

40

図 2 は、図 1 に示す演算処理装置 1 0 0 の動作の一例を示す。すなわち、図 2 は、演算処理装置 1 0 0 の制御方法の一例を示す。図 2 に示す例では、複合命令でない通常の単一の命令 I N S - A 、複合命令 I N S - B C および通常の単一の命令 I N S - D 、 I N S - E が、デコード部 1 に順次供給される(図 2 ( a ) )。デコード部 1 は、受信した命令 I N S - A 、 I N S - B C 、 I N S - D 、 I N S - E を順次デコードする。そして、デコード部 1 は、デコードにより得られた命令 I C D - A 、 I C D - B C 、 I C D - D 、 I C D - E (命令コード I C D およびレジスタ番号等の情報)を実行制御部 2 に順次出力する(図 2 ( b ) )。

## 【 0 0 2 1 】

50

実行制御部 2 は、デコード部 1 から受信した命令 I C D - A 、 I C D - B C 、 I C D - D 、 I C D - E を空いているエントリ E N T に保持し、エントリ E N T に保持した命令 I C D を実行可能な順に出力する(図 2 ( c ) )。図 2 に示す例では、説明を分かりやすくするため、実行制御部 2 は、エントリ E N T に保持した順に命令 I C D を出力する。実行制御部 2 は、複合命令 I C D - B C を分解した個別命令 I C D - B 、 I C D - C ではなく、複合命令 I C D - B C をエントリ E N T に保持する。このため、デコード部 1 で分解された個別命令 I C D - B 、 I C D - C を実行制御部 2 に保持する場合に比べて、エントリ

ENTの使用効率を向上することができ、アウトオブオーダの効率を向上することができ、演算処理装置100Aの性能を向上することができる。また、エントリENTの使用効率を向上できるため、エントリENTの数を抑制することができ、実行制御部2の回路規模の増大を抑制することができる。

#### 【0022】

命令転送部3は、実行制御部2から受信する命令ICD-A、ICD-BCを、ステージP、PTに順次転送し、ステージPTは、命令ICD-A、ICD-BCを演算実行部4に出力する(図2(d))。命令生成部5は、命令転送部3のステージPTで転送される複合命令ICD-BCを検出し、複合命令ICD-BCに含まれる実行順が2番目の個別命令ICD-Cを生成し、生成した個別命令ICD-Cを命令転送部3のステージPに出力する(図2(e))。

10

#### 【0023】

抑止制御部6は、命令転送部3のステージPTで転送される命令ICDが複合命令ICD-BCであることを検出した場合、抑止情報INHを実行制御部2に出力する(図2(f))。実行制御部2は、抑止情報INHの受信に基づいて、命令ICDの出力を停止する(図2(g))。図2に示す例では、実行制御部2は、命令ICD-Dを出力中に抑止情報INHを受信し、命令ICD-Dの出力を停止する。抑止制御部6により抑止情報INHを出力することで、命令生成部5が出力する命令と実行制御部2が出力する命令とが衝突することを抑止することができ、演算処理装置100の誤動作を抑止することができる。

20

#### 【0024】

命令転送部3のステージPは、実行制御部2からの命令ICD-Dの代わりに、命令転送部3からの個別命令ICD-Cを受信し、受信した個別命令ICD-CをステージPTに転送する(図2(h))。そして、個別命令ICD-Cは、演算実行部4に出力される。抑止制御部6は、ステージPTに個別命令ICD-Cが転送され、ステージPTから複合命令ICD-BCが追い出されたことに基づいて、抑止情報INHの出力を停止する。これにより、実行制御部2は、出力を停止していた命令ICD-D、ICD-Eを順次出力する(図2(i))。

#### 【0025】

演算実行部4は、命令ICD-Aを受信し、演算を実行し、演算結果RSLT-Aを出力する(図2(j))。演算実行部4は、複合命令ICD-BCを受信した場合、複合命令ICD-BCに含まれる複数の個別命令ICD-B、ICD-Cのうち実行順が最初の個別命令ICD-Bを実行する(図2(k))。例えば、複合命令ICD-BCの命令コードと個別命令ICD-Bの命令コードとは、ビット列の一部が共通である。演算実行部4は、複合命令ICD-BCの命令コードに含まれる共通のビット列に基づいて、復号命令ICD-BCを個別命令ICD-Bと解釈して実行する。これにより、演算実行部4は、複合命令ICD-BCの受信に基づいて、複合命令ICD-BCに含まれる実行順が最初の個別命令ICD-Bを実行することができる。換言すれば、命令生成部5により個別命令ICD-Bを生成することなく、個別命令ICD-Bを実行することができる。なお、上述したように、命令生成部5により、複合命令ICD-BCに含まれる個別命令ICD-Bと個別命令ICD-CとをステージPに順次生成してもよい。

30

#### 【0026】

この後、演算実行部4は、命令ICD-C、ICD-D、ICD-Eを順次に受信し、それぞれの演算を実行し、演算結果RSLT-C、RSLT-D、RSLT-Eを出力する(図2(l))。このように、複合命令ICD-BCは、2つの個別命令ICD-B、ICD-Cに分解されて実行される。

40

#### 【0027】

以上、図1に示す実施形態では、デコード部1で分解された個別命令ICD-B、ICD-Cを実行制御部2に保持する場合に比べて、エントリENTの使用効率を向上することができ、アウトオブオーダの効率を向上することができる。この結果、デコード部1で

50

分解された個別命令 I C D - B、I C D - C を実行制御部 2 に保持する場合に比べて、複合命令 I C D - B C を実行する演算処理装置 100 の性能を向上することができる。

#### 【0028】

抑止制御部 6 により抑止情報 I N H を出力することで、命令生成部 5 が output する個別命令と実行制御部 2 が output する命令とが衝突することを抑止することができ、演算処理装置 100 の誤動作を抑止することができる。演算実行部 4 は、複合命令 I C D - B C の受信に基づいて個別命令 I C D - B を実行するため、命令生成部 5 により個別命令 I C D - B を生成することなく、個別命令 I C D - B を実行することができる。

#### 【0029】

ステージ P T で検出した複合命令 I C D - B C に基づいて、2 番目に実行される個別命令 I C D - C をステージ P に出力することで、複合命令 I C D - B C と複合命令 I C D - B C に含まれる個別命令 I C D - C とを演算実行部 4 に連続して転送することができる。複合命令 I C D - B C と個別命令 I C D - C とを不可分に演算実行部 4 に転送できるため、演算実行部 4 は、複合命令 I C D - B C に含まれる個別命令 I C D - B、I C D - C を、クロックサイクルを空けることなく連続して実行できる。例えば、個別命令 I C D - B の演算結果を個別命令 I C D - C による演算で使用する場合、演算結果を演算実行部 4 に転送する複数のバイパス経路のうち、最短のバイパス経路を使用することができる。この結果、個別命令 I C D - B、I C D - C が連続して実行されず、最短のバイパス経路が使用されない場合に比べて、演算処理装置 100 の性能を向上することができる。

10

#### 【0030】

複合命令 I C D - B C を個別命令 I C D - B、I C D - C に分解し、演算実行部 4 で順次実行することで、複合命令 I C D - B C を実行する専用の演算器を演算実行部 4 に設けることなく、複合命令 I C D - B C を実行することができる。これにより、複合命令 I C D - B C を実行する専用の演算器を演算実行部 4 に設ける場合に比べて、演算実行部 4 および演算処理装置 100 の回路規模を削減することができる。

20

#### 【0031】

これに対して、複合命令がデコード部 1 により分解され、分解された個別命令が実行制御部 2 に投入される場合、実行制御部 2 は、分解した複数の個別命令を発行する間に他の命令を発行する場合がある。分解した個別命令間に他の命令が挿入され、かつ、分解した個別命令間にデータの依存性がある場合、分解した個別命令間でのデータが受け渡しは、レジスタ等を介して実行される。このため、分解した個別命令を不可分に実行する場合に比べて、レジスタ等の使用率が高くなり、アウトオブオーダ用に割り当て可能なレジスタが減るため、アウトオブオーダの効率は低下する。さらに、デコード部 1 により分解された個別命令を不可分に実行する場合、他の命令の発行を止めて、分解した複数の個別命令を連続して発行する機能が、実行制御部 2 に追加されるため、実行制御部 2 の回路規模が増大する。換言すれば、実行制御部 2 から発行される複合命令を分解する機能を命令転送部 3 に対応して設けることで、デコード部 1 により複合命令を分解する場合に比べて、実行制御部 2 の回路規模の増大を抑止することができる。

30

#### 【0032】

図 3 は、演算処理装置および演算処理装置の制御方法の別の実施形態を示す。図 1 に示す実施形態で説明した要素と同一または同様の要素については、同一の符号を付し、これ等については、詳細な説明は省略する。

40

#### 【0033】

図 3 に示す演算処理装置 100 A は、命令キャッシュ 10、命令バッファ 12、デコード部 14、レジスタ管理部 16、リザベーションステーション部 18、バイパス制御部 20、演算実行部 22 およびデータキャッシュ 24 を有する。演算処理装置 100 A は、C P U 等のプロセッサであり、図 2 では、プロセッサに搭載されるプロセッサコアの一部が示される。なお、演算処理装置 100 A は、命令 I N S を複数のステージに分けて実行する命令パイプラインを有する。命令パイプラインの例は、図 5 および図 6 に示される。

#### 【0034】

50

命令キャッシュ10は、二次キャッシュまたはメインメモリ等から転送される命令INSを格納する一次命令キャッシュである。命令バッファ12は、命令キャッシュ10から転送される命令INSを順次保持し、保持した命令INSをデコード部14に順次出力する。

#### 【0035】

デコード部14は、命令バッファ12から転送される命令INSを解読し、解読した命令INSに含まれる命令コードICD、レジスタ番号GPRNおよびバリッドフラグVをリザベーションステーション部18に投入する。レジスタ番号GRPNは、オペランドデータの格納用のレジスタGPRを示す。デコード部14は、固定小数点の演算命令をリザベーションステーションRS E(Reservation Station for Execution)に投入する。デコード部14は、メモリアクセス命令(ロード命令またはストア命令)をリザベーションステーションRSA(Reservation Station for Address)に投入する。10

#### 【0036】

さらに、デコード部14は、解読した命令INSが複数の演算命令を組み合わせた複合命令の場合、複合命令の命令コードICDとともにセカンドフローフラグ2FLの値をリザベーションステーションRS Eに投入する。複合命令が、加算命令addと減算命令subとを組み合わせた加減算命令addsubの場合、加減算命令addsubを示す命令コードICDに基づいて、加算命令addが固定小数点演算器28により実行される。そして、固定小数点演算器28は、図6に示す命令コード操作部ICDOPが加減算命令addsubに基づいて生成する減算命令subを、例えば、加算命令addの演算結果を用いて実行する。このように、複合命令は、固定小数点演算器28を複数回使用する命令である。加減算命令addsubに含まれる加算命令addおよび減算命令subは、個別命令の一例である。20

#### 【0037】

デコード部14は、複合命令を複数の演算命令に分解することなくリザベーションステーションRS Eに投入する。これにより、デコード部14で分解した複数の演算命令をリザベーションステーションRS Eに投入する場合に比べて、リザベーションステーションRS Eの使用効率を向上することができる。すなわち、デコード部14で分解した複数の演算命令をリザベーションステーションRS Eに投入する場合に比べて、アウトオブオーダの効率を向上することができ、演算処理装置100Aの性能を向上することができる。30

#### 【0038】

レジスタ管理部16は、命令INSの実行により得られる演算結果等を格納するレジスタGPRと、演算結果等を一時的に格納するレジスタGUB(GPR Update Buffer)との対応関係を保持するテーブルGPR T(GPR Pending Register Table)を有する。レジスタ管理部16は、デコード部14からのレジスタ番号GPRNに基づいてテーブルGPR Tを参照し、未使用的レジスタGUBのいずれかをレジスタGPRに対応して割り当てる。

#### 【0039】

そして、レジスタ管理部16は、割り当てたレジスタGUBとレジスタGPRとの対応関係を示す情報をテーブルGPR Tに記録し、割り当てたレジスタGUBを示すレジスタアドレスUBA(Update Buffer Address)を出力する。テーブルGPR Tに記録されるレジスタGUBとレジスタGPRとの対応関係を示す情報は、命令INSの実行が完了したことに基づいて破棄される。テーブルGPR Tの例は、図4に示される。なお、演算実行部22が浮動小数点演算器と、浮動小数点演算に使用するレジスタを有する場合、レジスタ管理部16は、浮動小数点演算に使用するレジスタに対応してテーブルGPR Tと同様のテーブルを有する。40

#### 【0040】

リザベーションステーション部18は、固定小数点の演算命令を保持するリザベーションステーションRS Eと、ロード命令およびストア命令を保持するリザベーションステー50

ション R S A とを有する。なお、演算実行部 2 2 が浮動小数点演算器を有する場合、リザベーションステーション部 1 8 は、浮動小数点の演算命令が保持されるリザベーションステーションを有する。リザベーションステーション R S E は、デコード部 1 4 から出力される固定小数点データの演算命令用の情報を保持する複数のエントリ（例えば、6 4 エントリ）を有する。リザベーションステーション R S E は、デコード部 1 4 がデコードした演算命令を保持し、保持した命令を実行可能な順に出力することで、アウトオブオーダ実行を制御する実行制御部の一例である。リザベーションステーション R S A は、デコード部 1 4 から出力されるメモリアクセス命令（ストア命令またはロード命令）用の情報を保持する複数のエントリ（例えば、6 4 エントリ）を有する。

## 【0 0 4 1】

10

例えば、リザベーションステーション R S E、R S A は、デコード部 1 4 から出力されるバリッドフラグ V の値、命令コード I C D およびレジスタ番号 G P R N と、レジスタ管理部 1 6 から出力されるレジスタアドレス U B A をエントリに保持する。さらに、リザベーションステーション R S E は、セカンドフローフラグ 2 F L の値をエントリに保持する。

## 【0 0 4 2】

リザベーションステーション R S E は、レジスタ管理部 1 6 から出力されるレジスタアドレス U B A およびバイパス制御部 2 0 から出力されるバイパスイネーブル信号 B P E N に基づいて、エントリに保持した演算命令の依存関係を判定する。そして、リザベーションステーション R S E は、エントリに保持した演算命令の中から実行可能な演算命令を選択し、選択した演算命令の情報を演算実行部 2 2 に投入する。演算実行部 2 2 に投入される情報は、命令コード I C D、バリッドフラグ V の値、レジスタアドレス R A D およびセカンドフローフラグ 2 F L の値を含む。レジスタアドレス R A D は、データを読み出すレジスタ G P R を示すアドレスと、データを読み出すレジスタ G U B を示すアドレスと、データを書き込むレジスタ G U B を示すアドレスとを含む。以下の説明では、バリッドフラグ V は、バリッド信号 V とも称され、セカンドフローフラグ 2 F L は、セカンドフロー信号 2 F L とも称される。

## 【0 0 4 3】

同様に、リザベーションステーション R S A は、レジスタ管理部 1 6 から出力されるレジスタアドレス U B A およびバイパス制御部 2 0 から出力されるバイパスイネーブル信号 B P E N に基づいて、エントリに保持したメモリアクセス命令の依存関係を判定する。そして、リザベーションステーション R S A は、エントリに保持したメモリアクセス命令の中から実行可能なロード命令またはストア命令を選択し、選択したストア命令の情報を演算実行部 2 2 に投入する。演算実行部 2 2 に投入される情報は、命令コード I C D、バリッド信号 V およびレジスタアドレス R A D を含む。

## 【0 0 4 4】

バイパス制御部 2 0 は、バイパス管理テーブル B P T B L を有する。バイパス管理テーブル B P T B L は、各レジスタ G U B に対応するバイパスフラグを有する。バイパス制御部 2 0 は、リザベーションステーション R S E（または R S A）から出力されるレジスタ番号 G U B N に対応するバイパスフラグをセットする。そして、バイパス制御部 2 0 は、セットしたバイパスフラグに対応するバイパスイネーブル信号 B P E N を、レジスタ番号 G U B N を出力したリザベーションステーション R S E（または R S A）に出力する。リザベーションステーション R S E（または R S A）は、バイパスイネーブル信号 B P E N の受信に基づいて、先行の命令の実行により得られるデータを後続の命令にバイパスさせることが可能であると判断し、後続の命令を発行する。

## 【0 0 4 5】

演算実行部 2 2 は、固定小数点演算器 2 8、アドレス計算演算器 3 0 およびレジスタ部 3 2 を有する。なお、演算実行部 2 2 は、論理演算器を有してもよい。固定小数点演算器 2 8 は、加算または減算を実行する加算器 A D D と、乗算または除算を実行する乗算器 M U L とを有する。加算器 A D D および乗算器 M U L は、リザベーションステーション R S

10

20

30

40

50

E から投入される演算命令に基づいて、レジスタ G P R に保持されたデータ D A T を用いて演算を実行し、演算結果 R S L T を次のクロックサイクルでレジスタ G U B に格納する。レジスタ G U B に格納された演算結果 R S L T は、演算命令の完了時にレジスタ G P R に格納される。

#### 【 0 0 4 6 】

アドレス計算演算器 3 0 は、リザベーションステーション R S A から投入されるメモリアクセス命令に基づいて、レジスタ G P R に保持されたデータ D A T を用いてアクセスアドレスを計算し、計算したアクセスアドレスをデータキャッシュ 2 4 に出力する。アドレス計算演算器 3 0 は、ロード命令では、データキャッシュ 2 4 から出力されるデータ（ロードデータ）をレジスタ G U B に格納する。アドレス計算演算器 3 0 は、ストア命令では、レジスタ G P R から出力されるデータ（ストアデータ）を、アクセスアドレスとともにデータキャッシュ 2 4 に出力する。データキャッシュ 2 4 は、二次キャッシュまたはメインメモリ等に保持されるデータを一時的に保持する一次データキャッシュである。

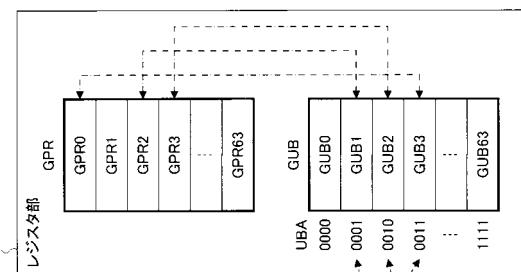

#### 【 0 0 4 7 】

レジスタ部 3 2 は、命令 I N S で指定される複数のレジスタ G P R (General-Purpose Register) と、演算結果等を一時的に格納する複数のレジスタ G U B (GPR Update Buffer) とを有する。各レジスタ G P R 、 G U B には、固定小数点データが格納される。例えば、レジスタ G P R およびレジスタ G U B の数は、それぞれ 6 4 個であり、レジスタ G U B を識別するレジスタアドレス U B A は、6 ビットである。

#### 【 0 0 4 8 】

図 4 は、図 3 に示すレジスタ管理部 1 6 およびレジスタ部 3 2 の一例を示す。レジスタ管理部 1 6 のテーブル G P R T は、6 4 個のレジスタ G P R にそれぞれ対応する 6 4 個のエントリ G P ( G P 0 - G P 6 3 ) を有する。各エントリ G P は、フラグ G P R - V およびレジスタアドレス U B A を格納する領域を有する。各フラグ G P R - V は、レジスタ G P R へのレジスタ G U B の割り当て時に “ 0 ” に設定され、レジスタ G P R を指定した命令の実行の完了時に “ 1 ” に設定される。レジスタ G P R へのレジスタ G U B の割り当ては、テーブル G P R T にレジスタアドレス U B A を格納することにより実行される。

#### 【 0 0 4 9 】

図 4 に示す例では、レジスタ G P R 0 に対応するエントリ G P 0 に 2 進数で “ 0 0 1 1 ” のレジスタアドレス U B A が格納され、レジスタアドレス U B A = “ 0 0 1 1 ” に対応するレジスタ G U B 3 がレジスタ G P R 0 に割り当てられる。レジスタ G P R 2 に対応するエントリ G P 2 に 2 進数で “ 0 0 0 1 ” のレジスタアドレス U B A が格納され、レジスタアドレス U B A = “ 0 0 0 1 ” に対応するレジスタ G U B 1 がレジスタ G P R 2 に割り当てられる。レジスタ G P R 3 に対応するエントリ G P 3 に 2 進数で “ 0 0 1 0 ” のレジスタアドレス U B A が格納され、レジスタアドレス U B A = “ 0 0 1 0 ” に対応するレジスタ G U B 2 がレジスタ G P R 3 に割り当てられる。

#### 【 0 0 5 0 】

レジスタ管理部 1 6 は、レジスタアドレス U B A をテーブル G P R T に格納したクロックサイクルで、格納したレジスタアドレス U B A をリザベーションステーション R S E ( または R S A ) に出力する。各リザベーションステーション R S E 、 R S A は、デコード部 1 4 から出力されるレジスタ番号 G P R N と、テーブル G P R T から出力されるレジスタアドレス U B A とに基づいて、図 4 に一点鎖線で示すレジスタ G P R 、 G U B の対応付けを検出する。

#### 【 0 0 5 1 】

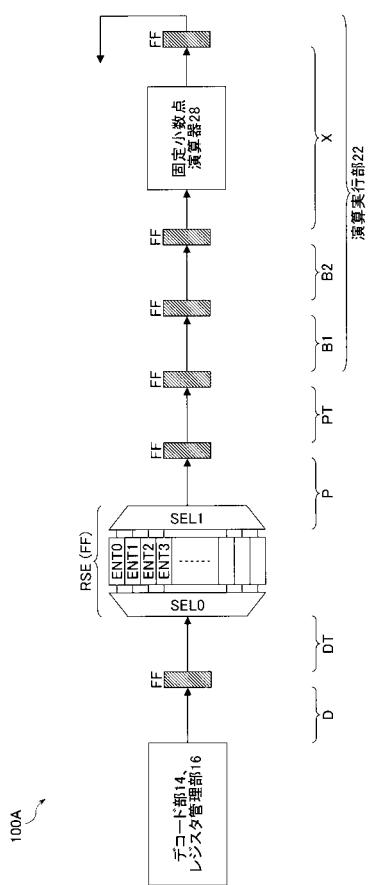

図 5 は、図 3 に示す演算処理装置 1 0 0 A における固定小数点演算器 2 8 に対応する命令パイプラインの概要を示す。命令パイプラインは、命令が順次転送される複数のステージ D 、 D T 、 P 、 P T 、 B 1 、 B 2 、 X を有する。リザベーションステーション R S E は、ステージ D T とステージ P の間に設けられ、フリップフロップ F F の機能を有する。ステージ X は、固定小数点演算器 2 8 を含む。ステージ P 、 P T は、リザベーションステーション R S E が出力する命令を順次転送する命令転送部の一例である。

10

20

30

40

50

## 【0052】

固定小数点の演算命令を実行する命令パイプラインのステージは以下の通りである。なお、以下では、命令パイプラインの各ステージは、サイクルとも称される。

(a) ステージ D (Decode) : デコード部 14 が命令をデコードし、デコードした命令コード ICD およびレジスタ番号 GPRN 等を出力する。また、デコード部 14 からレジスタ番号 GPRN を受信したレジスタ管理部 16 が、レジスタ GPR にレジスタ GUB を割り当て、割り当てたレジスタ GUB を示すレジスタアドレス UBA を出力する。

(b) ステージ DT (Decode Transfer) : D サイクルの実行により得られた命令コード ICD、レジスタ番号 GPRN およびレジスタアドレス UBA 等をリザベーションステーション RSE に格納する。リザベーションステーション RSE は、空いているエントリ ENT (ENT0、ENT1、ENT2、...) をセレクタ SEL0 により選択し、選択したエントリ ENT に、受信した命令コード ICD、レジスタ番号 GPRN およびレジスタアドレス UBA 等を格納する。以下の説明では、命令コード ICD、レジスタ番号 GPRN およびレジスタアドレス UBA 等は、命令とも称される。

(c) ステージ P (Priority) : リザベーションステーション RSE から演算実行部 22 に投入する命令を決定する。リザベーションステーション RSE は、エントリ ENT に保持された命令の中から実行可能な命令をセレクタ SEL1 により選択し、選択した命令を出力する。

(d) ステージ PT (Priority Transfer) : P サイクルで投入を決定した命令を演算実行部 22 に投入する。

(e) ステージ B1、B2 (Buffer) : 演算の実行に必要なデータを決定し、レジスタ GPR からデータを読み出す。

(f) ステージ X (Execute) : 固定小数点演算器 28 で命令を実行し、演算結果を得る。

## 【0053】

図 6 は、図 5 に示す命令パイプラインにおいて、ステージ P からステージ X までに関連する回路要素の一例を示す。図 5 に示すフリップフロップ FF は、図 6 においても斜線の矩形で示される。リザベーションステーション RSE のエントリ ENT およびレジスタ GPR、GUB は、ラッチの機能を有するため、フリップフロップ FF と同様に斜線の矩形で示される。なお、レジスタ GUB からレジスタ GPR にオペランドデータを転送する経路は、破線の矢印で示される。また、各ステージ P、PT、B1、B2、X 内で伝送される信号は、各信号の前にステージ P、PT、B1、B2、X を示す符号 "P - "、"PT - "、"B1 - "、"B2 - "、"X - " が付けられる。

## 【0054】

命令パイプラインは、命令コード操作部 ICDOP と、ステージ P に設けられるリザベーションステーション RSE のセレクタ SEL1、オアゲート OR1 およびセレクタ SEL2、SEL3 とを有する。なお、命令コード操作部 ICDOP は、ステージ P 内に設けられてもよい。また、命令パイプラインは、ステージ PT に設けられるアンドゲート AND1、セレクタ SEL4 および比較器 CMP1、CMP2、CMP3 を有する。さらに、命令パイプラインは、ステージ B1 に設けられるセレクタ SEL5、SEL6、SEL7 と、ステージ B2 に設けられるセレクタ SEL8 と、ステージ X に設けられる固定小数点演算器 28 とを有する。

## 【0055】

ステージ P において、リザベーションステーション RSE のセレクタ SEL1 は、リザベーションステーション RSE のエントリ ENT に保持された実行可能な命令のいずれかを選択し、選択した命令を出力する。セレクタ SEL1 から出力される命令は、バリッド信号 P-V、セカンドフロー信号 P-2FL、命令コード P-ICD およびレジスタアドレス P-RAD を含む。

## 【0056】

バリッド信号 P-V 等のバリッド信号 V は、論理 1 の場合、命令 (セカンドフロー信号 2FL、命令コード ICD およびレジスタアドレス RAD) が有効であることを示す。バ

リッド信号 V は、命令が有効であることを示す有効情報の一例である。論理 1 のセカンドフロー信号 P T - 2 F L は、リザベーションステーション R S E から複合命令が出力されたことを示し、論理 0 のセカンドフロー信号 P T - 2 F L は、リザベーションステーション R S E から複合命令以外の命令が出力されたことを示す。図 3 に示すデコード部 14 によりセカンドフロー信号 2 F L を生成し、リザベーションステーション R S E から出力することで、P サイクルまたは P T サイクルにおいて複合命令を検出する回路を設けることなく、複合命令を検出することができる。セカンドフロー信号 2 F L は、複数の命令を組み合わせた複合命令を識別する識別情報の一例である。レジスタアドレス P - R A D は、レジスタ G P R を示すレジスタ番号 G P R N 、オペランドデータを書き込むレジスタ G U B を示すレジスタアドレス W U B A およびオペランドデータを読み出すレジスタ G U B を示すレジスタアドレス R U B A を含む。

10

## 【0057】

アンドゲート A N D 1 は、バリッド信号 P T - V とセカンドフロー信号 P T - 2 F L とがともに論理 1 の場合、抑止信号 I N H を論理 1 ( 有効レベル ) に設定する。すなわち、アンドゲート A N D 1 は、リザベーションステーション R S E のセレクタ S E L 1 から複合命令が出力された場合、複合命令の P T サイクルで論理 1 の抑止信号 I N H を出力する。アンドゲート A N D 1 は、バリッド信号 P T - V とセカンドフロー信号 P T - 2 F L とのいずれかが論理 0 の場合、抑止信号 I N H を論理 0 ( 無効レベル ) に設定する。アンドゲート A N D 1 は、命令コード操作部 I C D O P が複合命令に含まれる命令を示す命令コード P - I C D 2 を出力する場合、リザベーションステーション R S E に命令の出力を抑止させる抑止信号 I N H を出力する抑止制御部の一例である。抑止信号 I N H は、抑止情報の一例である。

20

## 【0058】

命令コード操作部 I C D O P は、ステージ P T の命令コード P T - I C D が複合命令を示す場合、2 番目に実行される命令を示す命令コード P - I C D 2 と、2 番目に実行される命令に使用されるレジスタアドレス P - R A D 2 とを生成する。命令コード操作部 I C D O P は、複合命令に含まれる命令を生成し、生成した命令をステージ P に出力する命令生成部の一例である。

30

## 【0059】

複合命令が加算と減算とを順次実行する加減算命令 a d d s u b の場合、最初に実行される命令は加算命令 a d d であり、2 番目に実行される命令は減算命令 s u b である。複合命令が 2 つの加算を順次実行する a d d a d d 命令の場合、最初に実行される命令と 2 番目に実行される命令は、加算命令 a d d である。

## 【0060】

なお、命令コード操作部 I C D O P は、ステージ P T における命令コード P - I C D が複合命令であることを検出した場合、複合命令に含まれる複数の命令の命令コード P T - I C D をステージ P に順次出力してもよい。この場合、複合命令に含まれる命令の数に対応するクロックサイクルの期間に抑止信号 I N H を生成する信号生成部が、アンドゲート A N D 1 の出力に設けられる。これにより、固定小数点演算器 28 は、複合命令を 1 番目に実行される命令として解釈することなく、受信した命令を実行することができる。

40

## 【0061】

例えば、式 (1) に示す加減算命令 a d d s u b を実行する場合、加減算命令 a d d s u b は、式 (2) に示す a d d 命令と式 (3) に示す s u b 命令とに分解される。そして、式 (2) に示す a d d 命令が実行された後、式 (3) に示す s u b 命令が実行される。式 (1) から式 (3) において、符号 g は、レジスタ G P R を示す。式 (1) は、( g 1 + g 2 ) - g 3 の演算結果を g 0 に格納することを示す。式 (2) は、g 1 + g 2 の演算結果を g 0 に格納することを示す。式 (3) は、g 0 - g 3 の演算結果を g 0 に格納することを示す。

a d d s u b g 0 , g 1 , g 2 , g 3 (1)

50

a d d g 0 , g 1 , g 2 (2)

s u b g 0 , g 0 , g 3 ( 3 )

複合命令を分解した複数の命令において、命令パイプライン内に転送される最初に実行される命令はファーストフローと称され、命令パイプライン内に転送される 2 番目に実行される命令は、セカンドフローと称される。

#### 【 0 0 6 2 】

式(3)に示すように、命令コード操作部 I C D O P は、減算命令 s u b の演算結果を格納するレジスタ g 0 に対応するレジスタアドレス W U B A を、元の複合命令 a d d s u b の演算結果を格納するレジスタ g 0 に対応するレジスタアドレス W U B A に設定する。また、命令コード操作部 I C D O P は、減算命令 s u b の被減数( g 0 )に対応するレジスタアドレス R U B A を、加算命令 a d d のレジスタアドレス W U B A ( g 0 )と同じ値に設定する。これにより、ファーストフローとして実行される加算命令 a d d の演算結果を、セカンドフローとして実行される減算命令 s u b に最短のバイパス経路を使って引き継ぐことができる。

#### 【 0 0 6 3 】

オアゲート O R 1 は、バリッド信号 P - V または抑止信号 I N H を、フリップフロップ F F を介してバリッド信号 P T - V として出力する。オアゲート O R 1 により、複合命令の P T サイクルの次のクロックサイクルにおけるバリッド信号 P T - V は、バリッド信号 P - V の論理に拘わりなく論理 1 ( 有効レベル ) に設定される。これにより、リザベーションステーション R S E から出力されない減算命令 s u b ( セカンドフロー ) を命令パイプライン処理により実行することができる。オアゲート O R 1 は、リザベーションステーション R S E が output する論理 1 のバリッド信号 P T - V または論理 1 の抑止信号 I N H をバリッド信号 P T - V として演算実行部 2 2 に転送する論理和部の一例である。

#### 【 0 0 6 4 】

セレクタ S E L 2 は、抑止信号 I N H が無効レベル ( 論理 0 ) を示す場合、リザベーションステーション R S E からのセカンドフロー信号 P - 2 F L を、フリップフロップ F F を介してセカンドフロー信号 P T - 2 F L として出力する。セレクタ S E L 2 は、抑止信号 I N H が有効レベル ( 論理 1 ) を示す場合、論理 0 を、フリップフロップ F F を介してセカンドフロー信号 P T - 2 F L として出力する。これにより、複合命令に基づいてバリッド信号 P T - V が 2 クロックサイクルの期間に論理 1 に設定される場合にも、アンドゲート A N D 1 が抑止信号 I N H を論理 1 に設定し続けることを抑止することができる。この結果、論理 1 の抑止信号 I N H により誤った命令がセレクタ S E L 2 、 S E L 3 から出力されることを抑止することができ、演算処理装置 1 0 0 A の誤動作を抑止することができる。セレクタ S E L 2 は、抑止信号 I N H の論理に基づいて、リザベーションステーション R S E から出力されるセカンドフロー信号 P T - 2 F L 、または命令が複合命令でないことを示す論理 0 を選択する第 1 の選択部の一例である。

#### 【 0 0 6 5 】

セレクタ S E L 3 は、抑止信号 I N H が無効レベル ( 論理 0 ) を示す場合、命令コード P - I C D およびレジスタアドレス P - R A D を、フリップフロップ F F を介して命令コード P T - I C D およびレジスタアドレス P T - R A D として出力する。セレクタ S E L 3 は、抑止信号 I N H が有効レベル ( 論理 1 ) を示す場合、命令コード P T - I C D 2 およびレジスタアドレス P T - R A D 2 を、フリップフロップ F F を介して命令コード P T - I C D およびレジスタアドレス P T - R A D として出力する。すなわち、複合命令を示すセカンドフロー信号 P T - 2 F L により論理 1 の抑止信号 I N H が生成された場合、命令コード操作部 I C D O P が生成する命令が P サイクルに投入される。セレクタ S E L 3 により、リザベーションステーション R S E が output する命令と、命令コード操作部 I C D O P が output する命令とが衝突することを抑止することができ、演算処理装置 1 0 0 A の誤動作を抑止することができる。セレクタ S E L 3 は、抑止信号 I N H に基づいて、リザベーションステーション R S E から出力される命令または命令コード操作部 I C D O P から出力される命令を選択する第 2 の選択部の一例である。

#### 【 0 0 6 6 】

10

20

30

40

50

なお、リザベーションステーション R S E のセレクタ S E L 1 は、論理 1 の抑止信号 I N H を受けている間、命令の出力を停止し、バリッド信号 P - V を論理 0 に設定する。したがって、論理 1 の抑止信号 I N H によりセレクタ S E L 3 が命令コード操作部 I C D O P の出力を選択している間に、リザベーションステーション R S E から命令コード P - I C D およびレジスタアドレス P - R A D が出力されることを抑止することができる。これにより、命令コード P - I C D およびレジスタアドレス P - R A D がリザベーションステーション R S E から消失されることを抑止することができ、演算処理装置 1 0 0 A の誤動作を抑止することができる。

#### 【 0 0 6 7 】

比較器 C M P 1 、 C M P 2 、 C M P 3 は、オペランドデータを選択するためのオペランド選択信号 P T - O P S E L を生成する。比較器 C M P 1 は、先行する命令の B 1 サイクルのレジスタアドレス B 1 - W U B A と、後続の命令の P T サイクルのレジスタアドレス P T - R U B A とを比較する。比較器 C M P 2 は、先行する命令の B 2 サイクルのレジスタアドレス B 2 - W U B A と、後続の命令の P T サイクルのレジスタアドレス P T - R U B A とを比較する。比較器 C M P 3 は、先行する命令の X サイクルのレジスタアドレス X - W U B A と、後続の命令の P T サイクルのレジスタアドレス P T - R U B A とを比較する。

#### 【 0 0 6 8 】

そして、各比較器 C M P 1 - C M P 3 は、レジスタアドレス W U B A 、 R U B A の一致を検出した場合、先行の命令の演算結果（オペランドデータ）を、後続の命令を実行する固定小数点演算器 2 8 にバイパスさせるオペランド選択信号 P T - O P S E L を出力する。なお、各比較器 C M P 1 - C M P 3 は、レジスタアドレス P T - R U B A とともに、図 4 に示すフラグ G P R - V の値を受信し、フラグ G P R - V の値が論理 1 の場合に、上述したオペランド選択信号 P T - O P S E L を出力する。フラグ G P R - V の値が論理 1 の場合、命令の実行が完了し、レジスタ G U B 2 に保持されたデータはレジスタ G P R 3 に移動済みであり、レジスタ G U B 2 の割り当ては解除されている。この場合、比較器 C M P 1 - C M P 3 のいずれかは、セレクタ S E L 6 の出力をセレクタ S E L 7 に選択させるオペランド選択信号 P T - O P S E L と、セレクタ S E L 7 の出力をセレクタ S E L 8 に選択させるオペランド選択信号 P T - O P S E L とを生成する。

#### 【 0 0 6 9 】

X サイクルの次のクロックサイクルで演算結果はレジスタ G U B に書き込まれるため、バイパス処理は実行されない。このため、命令パイプラインは、先行の命令の X サイクル以降のレジスタアドレス W U B A と後続の命令の P T サイクルのレジスタアドレス P T - R U B A とを比較する比較器を持たない。比較器 C M P 1 - C M P 3 によるオペランドデータをバイパスさせる制御の例は、図 7 に示される。

#### 【 0 0 7 0 】

セレクタ S E L 4 は、レジスタアドレス X - W U B A を 1 クロックサイクル遅らせたレジスタアドレス X - W U B A 2 が示すレジスタ G U B のいずれかに、固定小数点演算器 2 8 による演算結果 R S L T を格納する。セレクタ S E L 5 は、レジスタアドレス P T - U B A が示すレジスタ G U B のいずれかから演算に使用するオペランドデータを読み出す。なお、セレクタ S E L 5 が読み出すオペランドデータの数は、命令のオペランドの数に依存する。

#### 【 0 0 7 1 】

セレクタ S E L 7 は、オペランド選択信号 B 1 - O P S E L に基づいて選択したオペランドデータを、フリップフロップ F F を介してオペランドデータ B 2 - O P としてセレクタ S E L 8 に出力する。セレクタ S E L 8 は、オペランド選択信号 B 2 - O P S E L に基づいて選択したオペランドデータを、フリップフロップ F F を介してオペランドデータ X - O P として固定小数点演算器 2 8 に出力する。

#### 【 0 0 7 2 】

なお、図 6 では省略されるが、セレクタ S E L 7 、 S E L 8 は、演算に使用する即値を

10

20

30

40

50

選択する機能と、固定小数点演算器 28 以外の演算器からバイパスされるデータを選択する機能を有する。また、セレクタ SEL7、SEL8 は、ロード命令により読み出されるデータを選択する機能を有する。

#### 【0073】

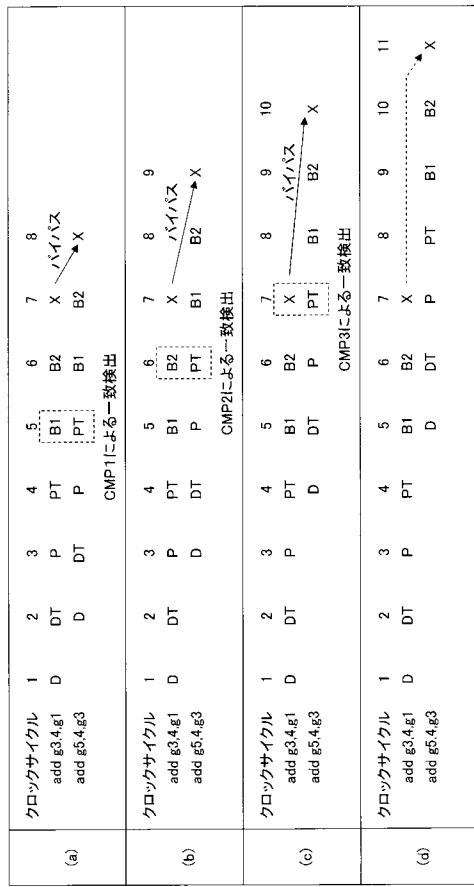

図 7 は、図 5 および図 6 に示す命令パイプラインにおいて、オペランドデータをバイパスさせるタイミングの一例を示す。クロックサイクルは、命令パイプラインを動作させるクロックのサイクルを示す。図 7 に示すタイミング (a)、(b)、(c)、(d) は、先行の命令が加算命令 "add g3, 4, g1" であり、後続の命令が加算命令 "add g5, 4, g3" である。先行の加算命令 add は、即値 (=4) とレジスタ GPR1 (g1) が保持する値とを加算し、加算結果をレジスタ GPR3 (g3) に書き込む命令である。後続の加算命令 add は、即値 (=4) とレジスタ GPR3 (g1) が保持する値とを加算し、加算結果をレジスタ GPR5 (g5) に書き込む命令である。

10

#### 【0074】

先行の加算命令 add の加算結果が書き込まれるレジスタ GPR3 と、後続の加算命令 add で加算に使用するレジスタ GPR3 とは同じであり、データの依存性がある。先行の加算命令 add および後続の加算命令 add で使用するレジスタ GRR3 には、共通のレジスタ GUB (例えば、GUB2) が割り当てられる。なお、図 7 では、各加算命令 add において、DT サイクルと P サイクルとが連続して実行されるが、DT サイクルでリザベーションステーション RSE に投入された命令が、次のクロックサイクルでリザベーションステーション RSE から発行されるとは限らない。

20

#### 【0075】

タイミング (a) では、図 6 に示す比較器 CMP1 は、クロックサイクル 5 において、先行の加算命令 add のレジスタアドレス B1 - WUBA (GUB2) と後続の加算命令 add のレジスタアドレス PT - RUBA (GUB2) との一致を検出する。そして、比較器 CMP1 は、固定小数点演算器 28 の出力をセレクタ SEL8 に選択させるオペランド選択信号 PT - OPSEL を生成する。オペランド選択信号 PT - OPSEL は、オペランド選択信号 B1 - OPSEL、B2 - OPSEL として順次伝達される。セレクタ SEL8 は、後続の加算命令 add の B2 サイクルにおいて、固定小数点演算器 28 の出力を選択することで、先行の加算命令 add の加算結果 (オペランドデータ) を後続の加算命令 add にバイパスさせる。これにより、先行の加算命令 add の実行が完了した次のクロックサイクルで、先行の加算命令 add の実行結果を用いて後続の加算命令 add を実行することができる。

30

#### 【0076】

タイミング (b) では、図 6 に示す比較器 CMP2 は、クロックサイクル 6 において、先行の加算命令 add のレジスタアドレス B2 - WUBA (GUB2) と、後続の加算命令 add のレジスタアドレス PT - RUBA (GUB2) との一致を検出する。そして、比較器 CMP2 は、固定小数点演算器 28 の出力をフリップフロップ FF で 1 クロックサイクル遅らせた加算結果をセレクタ SEL8 に選択させるオペランド選択信号 PT - OPSEL を生成する。セレクタ SEL8 は、後続の加算命令 add の B2 サイクルにおいて、固定小数点演算器 28 の出力に接続されたフリップフロップ FF の出力を選択することで、先行の加算命令 add の加算結果を後続の加算命令 add にバイパスさせる。これにより、先行の加算命令 add の実行が完了した 2 クロックサイクル後に、先行の加算命令 add の実行結果を用いて後続の加算命令 add を実行することができる。

40

#### 【0077】

タイミング (c) では、図 6 に示す比較器 CMP3 は、クロックサイクル 7 において、先行の加算命令 add のレジスタアドレス X - WUBA (GUB2) と、後続の加算命令 add のレジスタアドレス PT - RUBA (GUB2) との一致を検出する。そして、比較器 CMP3 は、固定小数点演算器 28 の出力をフリップフロップ FF で 1 クロックサイクル遅らせた加算結果を B1 サイクルでセレクタ SEL7 に選択させるオペランド選択信号 PT - OPSEL を生成する。また、比較器 CMP3 は、セレクタ SEL7 が選択した

50

加算結果をB2サイクルでセレクタSEL8に選択させるオペラント選択信号PT-OPSELを生成する。セレクタSEL7、SEL8は、後続の加算命令addのB1、B2サイクルにおいて、固定小数点演算器28の出力に接続されたフリップフロップFFの出力を順次選択することで、先行の加算命令addの加算結果を後続の加算命令addにバイパスさせる。これにより、先行の加算命令addの実行が完了した3クロックサイクル後に、先行の加算命令addの実行結果を用いて後続の加算命令addを実行することができる。

#### 【0078】

タイミング(d)では、各比較器CMP1-CMP3は、いずれのクロックサイクルにおいても先行の加算命令addのレジスタアドレスPT-RUBA(GUB2)と、後続の加算命令addのレジスタアドレスWUBAとの一致を検出しない。この場合、後続の加算命令addの加算結果をレジスタGUBに格納する前にバイパスさせる動作は実行されず、後続の加算命令addに使用する先行の加算命令addの加算結果は、レジスタGUBから読み出される。タイミング(d)では、比較器CMP1-CMP3のいずれかは、セレクタSEL5の出力(すなわち、レジスタGUB2に格納された加算結果)をセレクタSEL7に選択させるオペラント選択信号PT-OPSELを生成する。また、比較器CMP1-CMP3のいずれかは、セレクタSEL7が選択したオペラントデータをB2サイクルでセレクタSEL8に選択させるオペラント選択信号PT-OPSELを生成する。そして、セレクタSEL7、SEL8は、後続の加算命令addのB1、B2サイクルにおいて、レジスタGUB2に格納された先行の加算命令addの加算結果を順次選択する。

10

20

30

40

#### 【0079】

セレクタSEL7によるレジスタGUB2の出力の選択は、テーブルGPRT(図4)においてレジスタGUB2を割り当てたレジスタGPR3に対応するエントリGPR3のフラグGPR-Vが論理0であり、かつ、比較器CMP1-CMP3のいずれの比較結果も一致しない場合に実行される。テーブルGPRTのレジスタGPR3に対応するエントリGPR3のフラグGPR-Vが論理1の場合、命令の実行が完了し、レジスタGUB2に保持されたデータはレジスタGPR3に移動済みであり、レジスタGUB2の割り当ては解除されている。この場合、比較器CMP1-CMP3の比較結果に拘わらず、セレクタSEL6、SEL7、SEL8により、レジスタGPR3に格納されたオペラントデータが選択される。

30

40

#### 【0080】

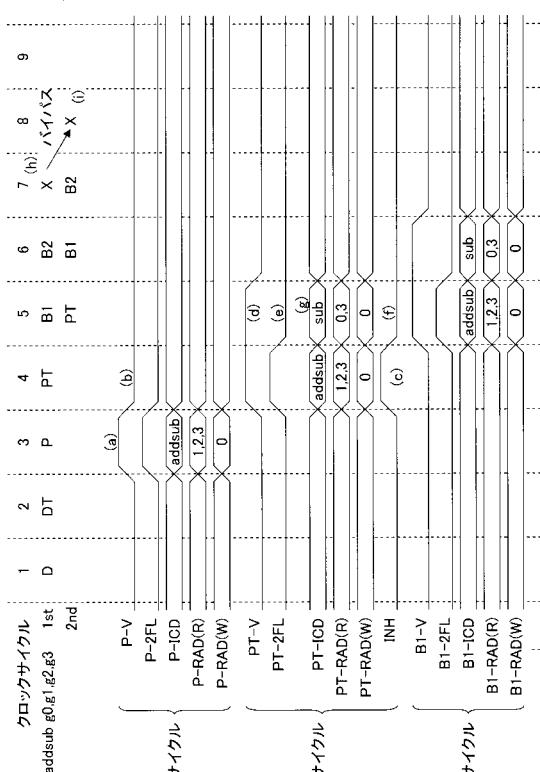

図8は、図3に示す演算処理装置100Aの動作の一例を示す。すなわち、図8は、演算処理装置100Aの制御方法の一例を示す。図8では、式(1)に示す加減算命令"addsub g0, g1, g2, g3"が実行される。命令パイプラインは、加減算命令addsubを、加算命令addを実行するファーストフロー1stと、減算命令subを実行するセカンドフロー2ndとに分解して処理する。図8では、説明を分かりやすくするために、レジスタアドレスRADは、レジスタGPRの番号が示され、レジスタアドレスUBA(レジスタGUBの番号)の記載は省略される。なお、図8ではDTサイクルとPサイクルとが連続して実行されるが、図7と同様に、DTサイクルでリザベーションステーションRSEに投入された命令が、次のクロックサイクルでリザベーションステーションRSEから発行されるとは限らない。

50

#### 【0081】

クロックサイクル3にリザベーションステーションRSEから加減算命令addsubが発行され、加減算命令addsubのPサイクルが実行される(図8(a))。バリッド信号P-Vはおよびセカンドフロー信号P-2FLは、論理1に設定され、命令コードP-ICDは、"addsub"に設定される。演算に使用するオペラントデータを読み出すレジスタGPRを示すリード用のレジスタアドレスP-RAD(R)は、レジスタGPR1、GPR2、GPR3を示す。演算結果を格納するレジスタGPRを示すライト用のレジスタアドレスP-RAD(W)は、レジスタGPR0を示す。

50

## 【0082】

クロックサイクル4において、図示は省略されるが、命令コード操作部ICDOPは、PTサイクルの加減算命令addsubに基づき、命令コードP-ICD2(sub)と、レジスタアドレスP-RAD2(P-RAD(R)、P-RAD(W))とを生成する。ここで、命令コード操作部ICDOPは、リード用のP-RAD(R)を(1,2)から(0,3)に変更するが、ライト用のレジスタアドレスP-RAD(W)は“0”的ままでする。

## 【0083】

クロックサイクル4のPTサイクルでは、クロックサイクル3のPサイクルの情報がそのまま転送される。クロックサイクル4では、リザベーションステーションRSEから命令が発行されないため、バリッド信号P-Vは論理0に設定される(図8(b))。バリッド信号PT-Vおよびセカンドフロー信号PT-2FLは、ともに論理1のため、図6に示すアンドゲートAND1は、抑止信号INHを論理1に設定する(図8(c))。これにより、図6に示すオアゲートOR1の出力は論理1に設定され、次のクロックサイクル5のバリッド信号PT-Vは論理1に設定される(図8(d))。リザベーションステーションRSEのセレクタSEL1は、論理1の抑止信号INHを受けている間、Pサイクルの命令の出力を停止する。

10

## 【0084】

論理1の抑止信号INHにより、セレクタSEL2は論理0を選択するため、次のクロックサイクル5のセカンドフロー信号PT-2FLおよび抑止信号INHは論理0に設定される(図8(e)、(f))。論理0の抑止信号INHにより、リザベーションステーションRSEのセレクタSEL1は、停止していたPサイクルの命令の出力を再開する。但し、図8に示す例では、リザベーションステーションRSEから出力される後続の命令の記載は省略される。

20

## 【0085】

図6に示すセレクタSEL3は、論理1の抑止信号INHに基づいて、命令コード操作部ICDOPが生成した命令コードP-ICD2とレジスタアドレスP-RAD2とを選択する。これにより、セカンドフローとして実行される減算命令subの情報が、クロックサイクル5のPTサイクルに転送され、減算命令subは、PTサイクルから開始される(図8(g))。この後、ファーストフローとして実行される加減算命令addsub中の加算命令addおよびセカンドフローとして実行される減算命令subは、クロックサイクル毎に後段のステージに順次転送される。

30

## 【0086】

クロックサイクル5において、図6に示す比較器CMP1は、B1サイクルのレジスタアドレスB1-RAD(W) = “0”が、PTサイクルのレジスタアドレスPT-RAD(R) = “0”に一致することを検出する。そして、比較器CMP1は、固定小数点演算器28の出力をセレクタSEL8に選択させるオペランド選択信号PT-OPSELを生成する。

## 【0087】

クロックサイクル7において、固定小数点演算器28は、図示しない命令コードX-IDC(addsub)と、レジスタアドレスX-RAD(R) = (1,2,3)とレジスタアドレスX-RAD(W) = “0”とを受ける。固定小数点演算器28の加算器ADDは、図1に示す演算実行部4と同様に、複合命令“addsub g0, g1, g2, g3”を加算命令“add g0, g1, g2”と解釈する機能を有する。すなわち、加算器ADDは、レジスタアドレスX-RAD(R) = (1,2,3)の最初の2つ(1,2)を、加算に使用するレジスタ番号と解釈する。そして、加算器ADDは、加算命令“add g0, g1, g2”を実行し、加算結果をレジスタGPR0に対応するレジスタGUBに格納する(図8(h))。

40

## 【0088】

クロックサイクル5に比較器CMP1が生成したオペランド選択信号PT-OPSEL

50

に基づいて、加算命令  $a\ dd$  による加算結果は、クロックサイクル 8 で固定小数点演算器 28 にバイパスされる(図 8 ( i ) )。そして、固定小数点演算器 28 は、加算命令  $a\ dd$  による加算結果を使用して、セカンドフローとして実行される減算命令  $s\ ub$  を実行し、リザベーションステーション RSE から投入された加減算命令  $a\ dd\ s\ ub$  の実行が完了する。

#### 【0089】

なお、複合命令は、3 以上の命令を含んでもよい。この場合、命令コード操作部 ICDOP は、2 番目以降に実行される命令を示す命令コード P-ICD2 およびレジスタアドレス P-RAD2 を順次に生成する。また、複合命令に含まれる 2 番目以降に実行される命令の数に対応するクロックサイクルの期間に抑止信号 INH を生成する信号生成部が、10 アンドゲート AND1 の出力に設けられる。

#### 【0090】

また、複合命令に含まれる 1 番目に実行される命令が、演算サイクル(X サイクル)を X1 サイクルと X2 サイクルとにより実行する命令であるとする。この場合、命令コード操作部 ICDOP は、複合命令を検出した次のクロックサイクルで命令コード P-ICD2 とレジスタアドレス P-RAD2 とを P サイクルに投入する。また、命令パイプラインは、抑止信号 INH を図 8 に対して 1 クロックサイクル遅れて生成する制御回路を有する。

#### 【0091】

図 9 は、図 3 に示す演算処理装置 100A の動作の別の例を示す。すなわち、図 9 は、演算処理装置 100A の制御方法の一例を示す。図 8 と同一または同様の動作については、詳細な説明は省略する。図 9 は、図 7 に示すタイミング(a)に示す命令の実行時における命令パイプライン内の状態を示す。

#### 【0092】

クロックサイクル 3 でリザベーションステーション RSE から加算命令  $a\ dd$  が発行され、P サイクルが実行され、クロックサイクル 4 でリザベーションステーション RSE から減算命令  $s\ ub$  が発行され、P サイクルが実行される(図 9 ( a )、( b ) )。クロックサイクル 3 およびクロックサイクル 4 において、バリッド信号 P-V は論理 1 に設定される。加算命令  $a\ dd$  および減算命令  $s\ ub$  は、複合命令ではないため、クロックサイクル 3 およびクロックサイクル 4 において、セカンドフロー信号 P-2FL は論理 0 に設定される(図 9 ( c ) )。

#### 【0093】

クロックサイクル 4 の PT サイクルでは、クロックサイクル 3 の P サイクルの情報がそのまま転送され、クロックサイクル 5 の PT サイクルでは、クロックサイクル 4 の P サイクルの情報がそのまま転送される(図 9 ( d )、( e ) )。クロックサイクル 4 およびクロックサイクル 5 において、命令コード操作部 ICDOP は、命令コード PT-ICD が複合命令でないため、命令コード P-ICD2 およびレジスタアドレス PT-RAD2 を生成しない。クロックサイクル 3 およびクロックサイクル 4 において、セカンドフロー信号 P-T-2FL は論理 0 であるため、抑止信号 INH は論理 0 に維持される(図 9 ( f ) )。これにより、図 6 に示すセレクタ SEL2 は、リザベーションステーション RSE からのセカンドフロー信号 P-2FL を選択し続ける。セレクタ SEL3 は、リザベーションステーション RSE からの命令コード P-ICD およびレジスタアドレス P-RAD を選択し続ける。

#### 【0094】

クロックサイクル 5 において、図 8 と同様に、比較器 CMP1 は、B1 サイクルのレジスタアドレス B1-RAD(W) = "3" が、PT サイクルのレジスタアドレス PT-RAD(R) = "3" に一致することを検出する。そして、比較器 CMP1 は、固定小数点演算器 28 の出力をセレクタ SEL8 に選択させるオペランド選択信号 P-T-OPSEL を生成する。

#### 【0095】

10

20

30

40

50

クロックサイクル 7において、固定小数点演算器 28は、加算命令 "add g3,4,g1" を実行し、加算結果をレジスタ GPR3 に対応するレジスタ GUB に向けて出力する(図9(g))。クロックサイクル 5に比較器 CMP1 が生成したオペランド選択信号 PT-OPSELに基づいて、加算命令 add による加算結果は、クロックサイクル 8で固定小数点演算器 28 にバイパスされる(図9(h))。減算命令 sub は、バイパスされた加算結果を用いて実行される。そして、リザベーションステーション RSE から投入された加算命令 add と減算命令 sub の実行が完了する。

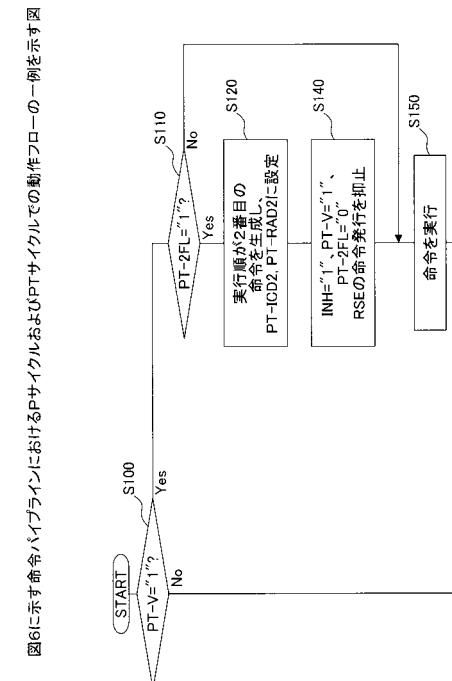

#### 【0096】

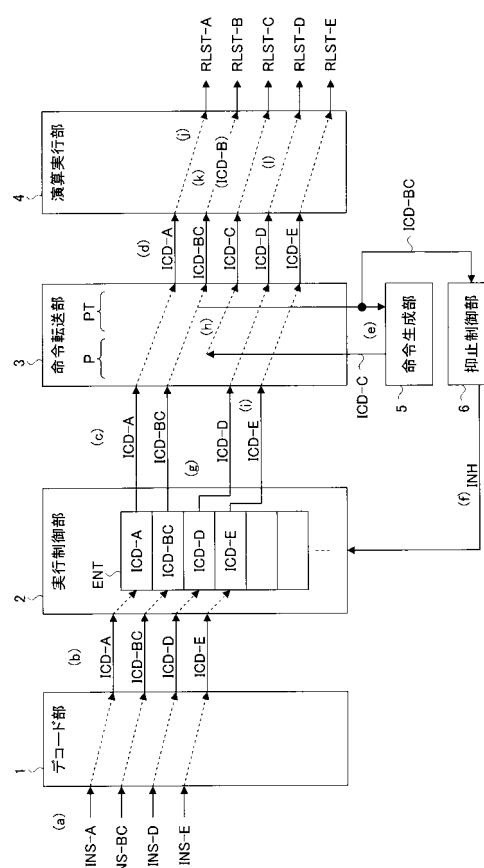

図10は、図6に示す命令パイプラインにおけるPサイクルおよびPTサイクルでの動作フローの一例を示す。すなわち、図10は、演算処理装置100Aの制御方法の一例を示す。

10

#### 【0097】

まず、ステップS100において、命令パイプラインは、バリッド信号PT-Vが論理1の場合、演算実行部22に対する命令が発行されたため、処理をステップS110に移行する。命令パイプラインは、バリッド信号PT-Vが論理0の場合、演算実行部22に対する命令が発行されていないため、処理を終了する。

#### 【0098】

ステップS110において、命令パイプラインは、セカンドフロー信号PT-2FLが論理1の場合、加減算命令addsub等の複合命令が発行されたと判定し、複合命令を2つのフローに分解して実行するために、処理をステップS120に移行する。命令パイプラインは、セカンドフロー信号PT-2FLが論理0の場合、複合命令以外の通常の命令が発行されたと判定し、処理をステップS150に移行する。

20

#### 【0099】

ステップS120において、命令パイプラインの命令コード操作部ICDOPは、複合命令を分解することで実行順が2番目の命令(図8では減算命令sub)を生成し、生成した命令を命令コードP-ICD2およびレジスタアドレスP-RAD2に設定する。次に、ステップS140において、命令パイプラインは、抑止信号INHを論理0に設定する。そして、命令パイプラインは、次のPTサイクルのバリッド信号PT-Vとセカンドフロー信号PT-2FLとを論理1、論理0にそれぞれ設定し、リザベーションステーションRSEに命令の発行を抑止させる。次に、ステップS150において、命令パイプラインは、リザベーションステーションRSEが発行した命令を実行し、処理を終了する。

30

#### 【0100】

以上、図3から図10に示す実施形態においても、図1および図2に示す実施形態と同様の効果を得ることができる。例えば、複合命令を複数の個別命令に分解してリザベーションステーションRSEに投入する場合に比べて、エントリENTの使用効率を向上することができ、アウトオブオーダの効率を向上することができる。この結果、複合命令を分解した複数の個別命令をリザベーションステーションRSEに投入する場合に比べて、複合命令を実行する演算処理装置100Aの性能を向上することができる。加算器ADDは、複合命令addsubを加算命令addと解釈するため、最初に実行する加算命令addを命令コード操作部ICDOP等により生成することなく、加算命令addを実行することができる。

40

#### 【0101】

複合命令を複数の個別命令に分解することで、複合命令を実行する専用の演算器を演算実行部22に設けることなく、複合命令を実行することができる。これにより、複合命令を実行する専用の演算器を演算実行部22に設ける場合に比べて、演算実行部22および演算処理装置100Aの回路規模を削減することができる。また、複合命令を分解した複数の個別命令をリザベーションステーションRSEに保持しないため、複合命令に含まれる複数の個別命令を不可分で実行するための制御機能は、リザベーションステーションRSEに搭載されない。これにより、リザベーションステーションRSEの回路規模の増大を抑止することができる。

50

## 【0102】

P T サイクルで検出した複合命令に基づいて、2番目に実行される個別命令をステージPに出力することで、複合命令に含まれる複数の個別命令を連続して実行することができる。このため、分解した個別命令間にデータの依存性がある場合にも、バイパス経路を使用してデータを受け渡すことができる。したがって、分解した個別命令間に他の命令が挿入される場合に比べて、先行の個別命令から後続の個別命令の受け渡すデータがレジスタG U Bに保持される期間を短縮することでレジスタG U Bの使用率を下げる事ができ、アウトオブオーダの効率を向上することができる。

## 【0103】

さらに、図3から図10に示す実施形態では、以下に示す効果を得ることができる。すなわち、図3に示すデコード部14によりセカンドフロー信号2F Lを生成し、リザベーションステーションR S Eから出力することで、PサイクルまたはP Tサイクルにおいて複合命令を検出する回路を設けることなく、複合命令を検出することができる。複合命令に基づいてバリッド信号P T - Vが2クロックサイクルの間に論理1に設定される場合にも、セレクタS E L 2により、アンドゲートA N D 1が抑止信号I N Hを論理1に設定し続けることを抑止することができる。この結果、誤った命令がセレクタS E L 2、S E L 3から出力されることを抑止することができ、演算処理装置100Aの誤動作を抑止することができる。

10

## 【0104】

セレクタS E L 3により、リザベーションステーションR S Eが出力する命令と、命令コード操作部I C D O Pが出力する命令とが衝突することを抑止することができる。演算処理装置100Aの誤動作を抑止することができる。オアゲートO R 1により、論理1の抑止信号I N Hをバリッド信号P T - Vとして転送することで、命令コード操作部I C D O Pが出力する命令コードP - I C D 2に対応するバリッド信号P T - Vを生成することができる。これにより、リザベーションステーションR S Eから出力されない2番目に実行される個別命令をパイプライン処理により実行することができる。

20

## 【0105】

なお、図3から図11に示す実施形態は、固定小数点演算器28が実行する複合命令をファーストフロー1s tとセカンドフロー2n dとに分解する命令パイプラインに適用する例について説明される。しかしながら、図3から図10に示す実施形態は、固定小数点演算器28と論理演算器とにより実行される複合命令をファーストフロー1s tとセカンドフロー2n dとに分解する命令パイプラインに適用されてもよい。また、図3から図11に示す実施形態は、浮動小数点演算器が実行する複合命令をファーストフロー1s tとセカンドフロー2n dとに分解する命令パイプラインに適用されてもよい。

30

## 【0106】

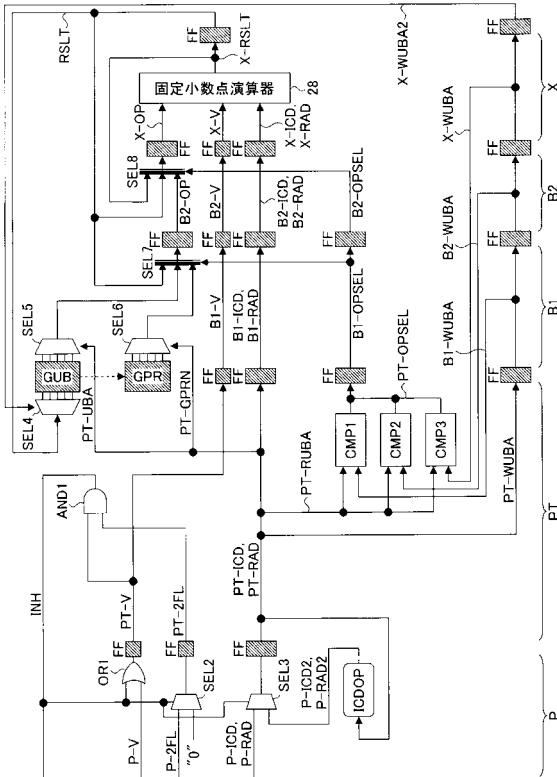

図11は、演算処理装置および演算処理装置の制御方法の別の実施形態において、リザベーションステーションR S Eから固定小数点演算器28までの命令パイプラインの一例を示す。図3から図6と同一または同様の要素については、同じ符号を付し、詳細な説明は省略する。

40

## 【0107】

図11に示す演算処理装置100Bの命令パイプラインは、オアゲートO R 2、インバータI V 1、アンドゲートA N D 2および命令依存チェック部I C D C Kが追加されたことを除き、図6に示す構成と同様である。オアゲートO R 2、インバータI V 1およびアンドゲートA N D 2は、ステージP Tに設けられる。命令依存チェック部I C D C Kは、ステージP Tの外に設けられるが、ステージP T内に設けられてもよい。演算処理装置100Bのその他の構成は、図3から図5に示す構成と同様である。

## 【0108】

なお、命令コード操作部I C D O Pは、図6で説明した機能に加えて、命令コードP T - I C DおよびレジスタアドレスP T - R A Dを、命令コードP - I C D 2およびレジスタアドレスP - R A D 2として出力する機能を有する。すなわち、命令コード操作部I C

50

DOPは、リザベーションステーションRSEが出力する命令が複合命令でない場合、ステージPTで転送された命令をステージPに出力する機能を有する。

#### 【0109】

ところで、図3に示す加算器ADDから乗算器MULへのデータの転送時間は、加算器ADDと乗算器MULとの物理的な距離の増加に依存して長くなる。ここで、物理的な距離は、加算器ADDの出力から乗算器MULの入力まで配線長に対応する。この実施形態では、加算器ADDと乗算器MULとの物理的な距離が、所定の制限値を超える。例えば、加算器ADDでの加算結果を、固定小数点演算器28内の加算器ADDの出力からセレクタSELおよびフリップフロップFFを介して固定小数点演算器28内の乗算器MULにバイパスするために掛かる時間は、1クロックサイクルを超える。このため、加算命令addと乗算命令mulとが連續して実行され、かつ、データの依存性がある場合、乗算器MULによる乗算命令mulの演算を1クロックサイクル後ろにずらす制御が命令パイプラインで実行される。固定小数点演算器28の出力からセレクタSELおよびフリップフロップFFを介して固定小数点演算器28にバイパス経路は、最短のバイパス経路である。最短のバイパス経路以外のバイパス経路では、乗算器MULによる乗算命令mulの演算を1クロックサイクル後ろにずらす制御を実行することなく、加算結果は正常にバイパスされる。

10

#### 【0110】

命令依存チェック部ICDCKは、例えば、PTサイクルの命令とB1サイクルの命令との依存性のチェックを実行し、所定の依存関係を検出した場合、依存検出信号DETを論理1に設定する。所定の依存関係は、先行の加算命令addのB1サイクルと後続の乗算命令mulのPTサイクルとが同じクロックサイクルで実行され、かつ、加算命令addの演算結果を乗算命令mulで使用する場合（データの依存性がある場合）に検出される。上記の所定の依存関係を有する一対の命令は、特定命令と称される。換言すれば、特定命令は、先行命令を実行する演算実行部22内の演算器が演算結果を出力してから、後続命令を実行する演算実行部22内の他の演算器に演算結果がバイパスされるまでの時間が、1クロックサイクルを超える組み合わせの命令である。命令依存チェック部ICDCKは、リザベーションステーションRSEが順次出力する先行命令および後続命令が所定の組み合わせ（addとmul）であり、かつ、先行命令の演算結果を後続命令で使用する特定命令であることを検出する依存検出部の一例である。

20

#### 【0111】

オアゲートOR2は、セカンドフロー信号PT-2FLまたは依存検出信号DETが論理1の場合、論理1をアンドゲートAND1に出力する。すなわち、アンドゲートAND1は、バリッド信号PT-Vが論理1でリザベーションステーションRSEから複合命令が出力された場合、または命令依存チェック部ICDCKが特定命令を検出した場合、論理1の抑止信号INHを出力する。オアゲートOR2およびアンドゲートAND1は、命令コード操作部ICDOPが複合命令に含まれる命令を出力する場合、または命令依存チェック部ICDCKが特定命令を検出した場合、抑止信号INHを出力する抑止制御部の一例である。

30

#### 【0112】

セレクタSEL2は、図6と同様に、抑止信号INHが論理0の場合、リザベーションステーションRSEから出力されるセカンドフロー信号PT-2FLを選択し、抑止信号INHが論理1の場合、論理0を選択する。セレクタSEL3は、図6と同様に、抑止信号INHが論理0の場合、リザベーションステーションRSEから出力される命令を選択し、抑止信号INHが論理1の場合、命令コード操作部ICDOPから出力される命令を選択する。但し、論理1の抑止信号INHは、命令コード操作部ICDOPが複合命令に含まれる個別命令を出力する場合、または命令依存チェック部ICDCKが特定命令を検出した場合に出力される。

40

#### 【0113】

インバータIV1は、依存検出信号DETの論理を反転し、反転した論理をアンドゲー

50

トAND2に出力する。アンドゲートAND2は、依存検出信号DETが論理0の場合、バリッド信号PT-Vを、フリップフロップFFを介してステージB1に転送し、依存検出信号DETが論理1の場合、バリッド信号PT-VのステージB1への転送を遮断する。すなわち、命令依存チェック部ICDCKにより特定命令が検出された次のクロックサイクルのバリッド信号B1-Vは、論理0に設定される。インバータIV1およびアンドゲートAND2は、命令依存チェック部ICDCKが特定命令を検出した場合、リザベーションステーションRSEが出力した後続命令に含まれるバリッド信号B1-Vを無効状態に設定する無効設定部の一例である。

#### 【0114】

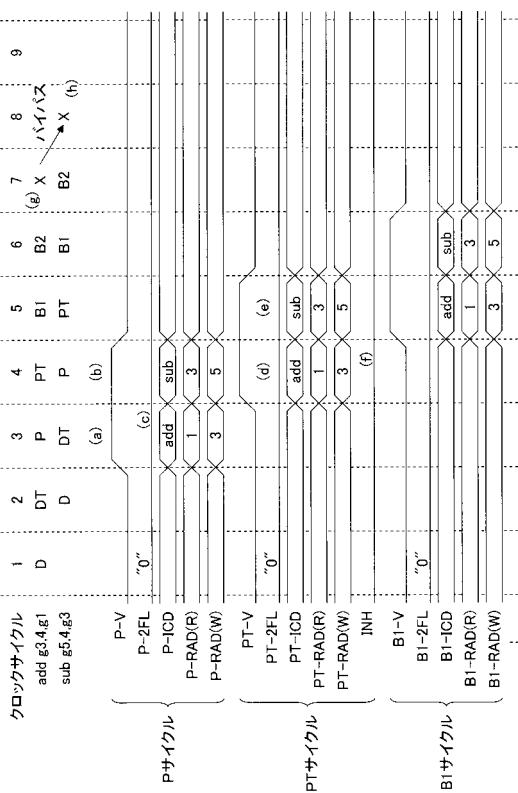

図12は、図11に示す命令パイプラインを有する演算処理装置100Bの動作の一例を示す。すなわち、図12は、図11に示す命令パイプラインを有する演算処理装置100Bの制御方法の一例を示す。図8と同一または同様の動作については、詳細な説明は省略する。図12では、加算命令"add g0, g1, g2"と乗算命令"mul g2, g0, 3"とが、リザベーションステーションRSEから命令パイプラインのPサイクルに連続して投入される。なお、リザベーションステーションRSEから命令パイプラインに複合命令が投入される場合の動作は、図8と同じである。また、図7および図9に示す動作は、図11に示す演算処理装置100Bでも実行される。

#### 【0115】

加算命令addは、レジスタGPR1(g1)が保持する値とレジスタGPR2(g2)が保持する値とを加算し、加算結果をレジスタGPR0(g0)に書き込む命令である。乗算命令mulは、レジスタGPR0(g0)が保持する値と即値(=3)とを乗算し、乗算結果をレジスタGPR2(g2)に書き込む命令である。乗算命令mulは、加算命令addの演算結果(g0)を用いて乗算を実行するため、加算命令addと乗算命令mulとの間にはデータの依存性がある。

#### 【0116】

演算処理装置100Bの性能を向上するため、データの依存性がある場合、演算結果を、レジスタGUBに書きこむ前に固定小数点演算器28に転送するバイパス制御が実行される。しかしながら、加算命令addを実行する加算器ADDと乗算命令mulを実行する乗算器MULとが物理的に離れているため、加算命令addと乗算命令mulとの間でのデータのバイパスは、2クロックサイクルを用いて実行される。この実施形態では、演算結果のバイパスのクロックサイクル数を増加する制御は、リザベーションステーションRSEによる命令の発行制御ではなく、命令パイプライン内で実行される。

#### 【0117】

クロックサイクル3でリザベーションステーションRSEから加算命令addが発行され、加算命令addのPサイクルが実行される(図12(a))。バリッド信号P-Vは論理1に設定される。加算命令addは、複合命令ではないため、セカンドフロー信号P-2FLは論理0に設定される。命令コードP-ICDは"add"に設定される。リード用のレジスタアドレスP-RAD(R)は、レジスタGPR1、GPR2を示し、ライト用のレジスタアドレスP-RAD(W)は、レジスタGPR0を示す。この後、図9に示す加算命令addと同様に、クロックサイクル3のPサイクルの情報が、クロックサイクル毎に次のサイクルに転送される。

#### 【0118】

クロックサイクル4でリザベーションステーションRSEから乗算命令mulが発行され、乗算命令mulのPサイクルが実行される(図12(b))。バリッド信号P-Vは論理1に設定される。乗算命令mulは、複合命令ではないため、セカンドフロー信号P-2FLが論理0に設定される。命令コードP-ICDは"mul"に設定される。リード用のレジスタアドレスP-RAD(R)は、レジスタGPR0を示し、ライト用のレジスタアドレスP-RAD(W)は、レジスタGPR2を示す。なお、命令パイプラインは、即値(= "3")も保持する。クロックサイクル4のPサイクルの情報は、次のクロックサイクル5でPTサイクルに転送される。

10

20

30

40

50

## 【0119】

クロックサイクル5において、図11に示す命令依存チェック部ICDCKは、命令コードB1-ICDの”add”と、命令コードPT-ICDの”mul”とを検出する。また、命令依存チェック部ICDCKは、レジスタアドレスB1-RAD(W)の”0”と、レジスタアドレスPT-RAD(R)の”0”との一致を検出する。命令依存チェック部ICDCKは、検出結果に基づいて、加算命令addと乗算命令mulとが、所定の依存関係を有する特定命令であると判定し、依存検出信号DETを論理1に設定する(図12(c))。

## 【0120】

クロックサイクル5において、比較器CMP1は、加算命令addのレジスタアドレスB1-RAD(W)の”0”と後続の加算命令addのレジスタアドレスPT-RAD(R)の”0”との一致を検出する。そして、比較器CMP1は、固定小数点演算器28の出力をセレクタSEL8に選択させるオペランド選択信号PT-OPSELを生成する。

10

## 【0121】

クロックサイクル5において、オアゲートOR2は、論理1の依存検出信号DETに基づいて論理1を出力する。アンドゲートAND1は、オアゲートOR2の出力とバリッド信号PT-Vとがともに論理1であるため、抑止信号INHを論理1に設定する(図12(d))。アンドゲートAND2は、インバータIV1の出力が論理0であるため、バリッド信号PT-Vの論理1に拘わらず、論理0を出力する。すなわち、アンドゲートAND2は、論理1の依存検出信号DETに基づいて、バリッド信号PT-Vの論理1の出力をマスクする。これにより、クロックサイクル6において、バリッド信号B1-Vは、論理0に設定される(図11(e))。論理0のバリッド信号B1-Vは、クロックサイクル毎に順次転送されるため、リザベーションステーションRSEから投入された乗算命令mulのファーストフロー(1st)は、B1、B2、Xサイクルを実行することなく終了する(図12(f))。

20

## 【0122】

オアゲートOR1は、論理1の抑止信号INHに基づいて論理1を出力するため、クロックサイクル6のバリッド信号PT-Vは論理1に設定される(図12(g))。命令コード操作部ICDOPは、クロックサイクル5で受信した命令コードPT-ICDおよびレジスタアドレスPT-RADを、そのまま命令コードP-ICD2およびレジスタアドレスP-RAD2として出力する。このため、PTサイクルのクロックサイクル6では、クロックサイクル5と同じ命令コードPT-ICDおよびレジスタアドレスPT-RADが出力される(図12(h))。すなわち、乗算命令mulのファーストフロー1stを1クロックサイクル後ろにずらしたセカンドフロー2ndがPTサイクルから開始される(図12(i))。

30

## 【0123】

クロックサイクル6において、命令依存チェック部ICDCKは、命令の依存関係を検出しないため、依存検出信号DETを論理0に設定する(図12(j))。アンドゲートAND1は、論理0の依存検出信号DETに基づいて、抑止信号INHを論理0に設定する(図12(k))。アンドゲートAND2は、論理1のバリッド信号PT-Vと、論理0の依存検出信号DETをインバータIV1で反転させた論理とにに基づいて、論理1を出力する。これにより、クロックサイクル7において、バリッド信号B1-Vは、論理1に設定される(図12(l))。この後、加算命令addおよびセカンドフロー2ndとして実行される乗算命令mulは、クロックサイクル毎に次のステージに順次転送される。

40

## 【0124】

クロックサイクル7において、固定小数点演算器28の加算器ADDは、図示しない命令コードX-ICD(add)と、レジスタアドレスX-RADとを受けて演算を実行し、演算結果を出力する(図12(m))。演算結果は、セレクタSEL8により選択され、2クロックサイクル後のクロックサイクル9に乗算器MULにバイパスされる(図12(n))。そして、クロックサイクル9において、乗算器MULは、バイパスされた演算

50

結果を用いてセカンドフロー 2 n d の乗算命令 m u l を実行する（図 12（o））。

#### 【0125】

図 13 は、図 11 に示す命令パイプラインを有する演算処理装置 100B の動作の別の例を示す。すなわち、図 13 は、図 11 に示す命令パイプラインを有する演算処理装置 100B の制御方法の一例を示す。図 8 および図 12 と同一または同様の動作については、詳細な説明は省略する。図 13 では、加算命令 "add g0, g1, g2" と乗算命令 "mul g2, g0, 3" とが、1 クロックサイクルの間隔を空けて、リザベーションステーション RSE から命令パイプラインのステージ P に投入される。図 12 と同様に、乗算命令 mul は、加算命令 add の演算結果 (g0) を用いて乗算を実行するため、加算命令 add と乗算命令 mul との間にはデータの依存性がある。

10

#### 【0126】

加算命令 add は、クロックサイクル 3 にリザベーションステーション RSE から発行され、乗算命令 mul は、クロックサイクル 5 にリザベーションステーション RSE から発行される（図 13（a）、（b））。命令依存チェック部 ICDCK は、乗算命令 mul の PT サイクル（クロックサイクル 6）において、所定の依存関係を検出しないため、依存検出信号 DET を論理 0 に維持する（図 13（c））。オアゲート OR2 は、セカンドフロー信号 PT-2FL と依存検出信号 DET とがともに論理 0 であるため、論理 0 をアンドゲート AND1 に出力する。アンドゲート AND1 は、オアゲート OR2 の出力が論理 0 であるため、抑止信号 INH を論理 0 に維持する（図 13（d））。

20

#### 【0127】

クロックサイクル 6 において、図 11 に示す比較器 CMP2 は、図示しない B2 サイクルのレジスタアドレス B2-RAD(W) = "0" が、PT サイクルのレジスタアドレス PT-RAD(R) = "0" に一致することを検出する。そして、比較器 CMP2 は、固定小数点演算器 28 の出力をフリップフロップ FF で 1 クロックサイクル遅らせた加算結果をセレクタ SEL8 に選択させるオペランド選択信号 PT-OPSEL を生成する。この後、加算命令 add および乗算命令 mul は、クロックサイクル毎に次のステージに順次転送される。

20

#### 【0128】

クロックサイクル 7 において、固定小数点演算器 28 の加算器 ADD は、図示しない命令コード X-ICD(add) と、レジスタアドレス X-RAD を受けて演算を実行し、演算結果を出力する（図 13（e））。セレクタ SEL8 は、比較器 CMP2 が生成したオペランド選択信号 PT-OPSEL に基づいて、フリップフロップ FF により 1 クロックサイクル遅らせた演算結果を選択することで、演算結果をバイパスする（図 13（f））。そして、クロックサイクル 9 において、乗算器 MUL は、バイパスされた加算命令 add の演算結果を用いて乗算命令 mul を実行する（図 13（g））。

30

#### 【0129】

図 14 は、図 11 に示す命令パイプラインを有する演算処理装置 100B の動作の別の例を示す。すなわち、図 14 は、図 11 に示す命令パイプラインを有する演算処理装置 100B の制御方法の一例を示す。図 8、図 12 および図 13 と同一または同様の動作については、詳細な説明は省略する。図 14 では、加算命令 "add g0, g1, g2" と減算命令 "sub g2, g0, 3" とが、リザベーションステーション RSE から命令パイプラインのステージ P に連続して投入される。減算命令 sub は、加算命令 add の演算結果 (g0) を用いて減算を実行するため、加算命令 add と減算命令 sub との間にはデータの依存性がある。

40

#### 【0130】

加算命令 add は、クロックサイクル 3 にリザベーションステーション RSE から発行され、減算命令 sub は、クロックサイクル 4 にリザベーションステーション RSE から発行される（図 14（a）、（b））。図 12 と同様に、命令依存チェック部 ICDCK は、PT サイクルにおいて、所定の依存関係を検出しないため、依存検出信号 DET を論理 0 に維持する（図 14（c））。これにより、抑止信号 INH は、論理 0 に維持される

50

(図14(d))。

【0131】

クロックサイクル5において、図11に示す比較器CMP1は、B1サイクルのレジスタアドレスB1-RAD(W) = "0"が、PTサイクルのレジスタアドレスPT-RAD(R) = "0"に一致することを検出する。そして、比較器CMP1は、固定小数点演算器28の出力をセレクタSEL8に選択させるオペランド選択信号PT-OPSELを生成する。この後、加算命令addおよび減算命令subは、クロックサイクル毎に次のステージに順次転送される。

【0132】

クロックサイクル7において、固定小数点演算器28の加算器ADDは、加算命令addを実行し、演算結果を出力する(図14(e))。セレクタSEL8は、比較器CMP1が生成したオペランド選択信号PT-OPSELに基づいて、固定小数点演算器28から出力された演算結果を選択することで、演算結果をバイパスする(図14(f))。そして、クロックサイクル8において、加算器ADDは、バイパスされた演算結果を用いて減算命令subを実行する(図14(g))。

【0133】

図15は、図11に示す命令パイプラインにおけるPサイクルおよびPTサイクルでの動作フローの一例を示す。すなわち、図15は、図11に示す命令パイプラインを有する演算処理装置100Bの制御方法の一例を示す。図10と同じ処理については、詳細な説明は省略する。図15は、ステップS110で否定判定(No)された場合、ステップS122、S124、S126、S128、S130が実行されることを除き、図10の処理と同様である。すなわち、ステップS110において、セカンドフロー信号PT-2FLが論理1の場合の処理は、図10と同じである。

【0134】

ステップS110において、セカンドフロー信号PT-2FLが論理0の場合、処理はステップS122に移行される。ステップS122、S124、S126では、連続する2つの命令間に所定の依存関係があるか否か(すなわち、特定命令であるか否か)が検出される。例えば、加算命令addのB1サイクルと乗算命令mulのPTサイクルとが同じクロックサイクルで実行され、かつ、加算命令addと乗算命令mulとの間にデータの依存性があるか否かが検出される。

【0135】

ステップS122において、命令パイプラインは、乗算命令mulのPTサイクルの場合、処理をステップS124に移行し、乗算命令mulのPTサイクルでない場合、処理をステップS150に移行する。ステップS124において、命令パイプラインは、B1サイクルのレジスタアドレスB1-WUBAとPTサイクルのレジスタアドレスPT-RUBAとが一致する場合、処理をステップS126に移行する。一方、命令パイプラインは、B1サイクルのレジスタアドレスB1-WUBAとPTサイクルのレジスタアドレスPT-RUBAとが一致しない場合、処理をステップS150に移行する。

【0136】

ステップS126において、命令パイプラインは、バリッド信号B1-V1が論理1で、サイクルB1の命令コードB-ICDが加算命令addである場合、特定命令を検出したため、処理をステップS128に移行する。命令パイプラインは、バリッド信号B1-V1が論理0、または、サイクルB1の命令コードB-ICDが加算命令addでない場合、処理をステップS150に移行する。

【0137】

ステップS128において、命令パイプラインは、命令コード操作部ICDOPにより、命令コードPT-ICDおよびレジスタアドレスPT-RAD2を、命令コードP-ICD2およびレジスタアドレスP-RAD2に設定する。次に、ステップS130において、命令パイプラインは、次のクロックサイクルのバリッド信号B1-Vを論理0に設定し、処理をステップS140に移行する。この後、ステップS140、S150では、図1

10

20

30

40

50

0と同じ処理が実行される。

#### 【0138】

以上、図11から図15に示す実施形態においても、図1から図10に示す実施形態と同様の効果を得ることができる。例えば、複合命令を命令パイプライン内で複数の個別命令に分解することで、分解された複数の個別命令をリザベーションステーションRSEに投入する場合に比べて、エントリENTの使用効率を向上することができ、アウトオブオーダの効率を向上することができる。この結果、分解された複数の個別命令をリザベーションステーションRSEに投入する場合に比べて、複合命令を実行する演算処理装置100Bの性能を向上することができる。複合命令に含まれる複数の個別命令を不可分で実行するための制御機能をリザベーションステーションRSEから省くことができるため、リザベーションステーションRSEの回路規模の増大を抑止することができる。アンドゲートAND1、オアゲートOR1およびセレクタSEL2、SEL3により、命令パイプライン内に誤った命令が転送されることを抑止することができ、演算処理装置100Bの誤動作を抑止することができる。10

#### 【0139】

さらに、図11から図15に示す実施形態では、以下に示す効果を得ることができる。すなわち、命令パイプライン内に命令依存チェック部ICDCKを設けることで、特定命令を検出する機能をリザベーションステーションRSEに設けることなく、特定命令を検出することができる。例えば、命令依存チェック部ICDCKは、B1、PTサイクルで転送される命令コードB1-ICD、PT-ICDを比較し、B1、PTサイクルでそれぞれ転送されるレジスタアドレスUBAを比較することで、特定命令を検出することができる。20

#### 【0140】

また、命令パイプライン内に命令依存チェック部ICDCKを設けることで、特定命令を検出する機能をリザベーションステーションRSEに設ける場合に比べて、演算処理装置100Bの回路規模の増大を抑止することができる。例えば、リザベーションステーションRSEにより特定命令を検出する場合、全てのエントリENTに保持された命令コードICDを相互にチェックする機能が、リザベーションステーションRSEに設けられる。また、特定命令を検出した場合、特定命令のうち後続の命令を先行の命令に対して所定のクロックサイクルを空けて命令パイプライン内に投入する機能が、リザベーションステーションRSEに設けられる。このため、特定命令を検出する機能を有するリザベーションステーションRSEの回路規模は、図11に示すリザベーションステーションRSEの回路規模に比べて増大する。30

#### 【0141】

複合命令において2番目に実行される個別命令を生成する命令コード操作部ICDOPを利用して、特定命令における2番目に実行される命令を1クロックサイクルずらす制御を実行することができる。このため、特定命令における2番目に実行される命令を1クロックサイクルずらす制御を実行する回路を新たに設ける場合に比べて、命令パイプラインの回路規模の増大を抑制することができる。

#### 【0142】

オアゲートOR2により、複合命令の投入時と特定命令の検出時に抑止信号INHを論理1に設定することで、セカンドフロー2ndの命令と、リザベーションステーションRSEから投入される命令とが衝突することを抑止することができる。これにより、命令パイプライン内に誤った命令が転送されることを抑止することができ、演算処理装置100Bの誤動作を抑止することができる。40

#### 【0143】

インバータIV1とアンドゲートAND2とにより、特定命令が検出された次のクロックサイクルのバリッド信号B1-Vを無効にすることで、乗算命令mulのファーストフロー1stのB1サイクル以降を無効にすることができます。これにより、命令コード操作部ICDOPが生成する1クロックサイクル遅らせた乗算命令mulのセカンドフロー2

10

20

30

40

50

$nd$  を乗算命令  $m u l$  のファーストフロー  $1st$  と衝突させることなく実行することができる。したがって、加算命令  $add$  の演算結果を、乗算命令  $m u l$  のセカンドフロー  $2nd$  を実行する乗算器  $MUL$  にバイパスすることができる。

#### 【0144】

なお、図11から図15に示す実施形態は、固定小数点演算器28が実行する複合命令および特定命令をファーストフロー  $1st$  とセカンドフロー  $2nd$  とに分解する命令パイプラインに適用する例について説明される。しかしながら、図11から図15に示す実施形態は、固定小数点演算器28と論理演算器とにより実行される複合命令および特定命令をファーストフロー  $1st$  とセカンドフロー  $2nd$  とに分解する命令パイプラインに適用されてもよい。また、図11から図15に示す実施形態は、浮動小数点演算器が実行する複合命令および特定命令をファーストフロー  $1st$  とセカンドフロー  $2nd$  とに分解する命令パイプラインに適用されてもよい。

10

#### 【0145】

以上の実施形態において説明した発明を整理して、付記として以下の通り開示する。

##### (付記1)

命令をデコードするデコード部と、

前記デコード部がデコードした命令を保持し、保持した命令を実行可能な順に出力する実行制御部と、

前記実行制御部が出力する命令を順次転送する命令転送部と、

前記命令転送部が転送する命令が複数の個別命令を組み合わせた複合命令である場合、前記複合命令から生成した個別命令を前記命令転送部に出力する命令生成部と、

20

前記命令転送部が転送した個別命令を実行する演算実行部を有することを特徴とする演算処理装置。

##### (付記2)

前記命令生成部が前記複合命令に含まれる個別命令を前記命令転送部に出力する場合、前記実行制御部に命令の出力を抑止させる抑止情報を出力する抑止制御部を有することを特徴とする付記1記載の演算処理装置。

##### (付記3)

前記実行制御部が出力する前記複合命令は、前記複合命令であることを識別する識別情報を含み、

30

前記抑止制御部は、前記実行制御部が出力する前記識別情報を基づいて、前記抑止情報を出力することを特徴とする付記2記載の演算処理装置。

##### (付記4)

前記命令転送部は、前記抑止制御部が前記抑止情報を出力しない場合、前記実行制御部が出力する前記識別情報を選択し、前記抑止制御部が前記抑止情報を出力する場合、命令が前記複合命令でないことを示す識別情報を選択する第1の選択部を有し、前記第1の選択部で選択した識別情報を転送することを特徴とする付記3記載の演算処理装置。

40

##### (付記5)

前記命令転送部は、前記抑止制御部が前記抑止情報を出力しない場合、前記実行制御部が出力する命令を選択し、前記抑止制御部が前記抑止情報を出力する場合、前記命令生成部が出力する個別命令を選択する第2の選択部を有し、前記第2の選択部で選択した命令を転送することを特徴とする付記2ないし付記4のいずれか1項記載の演算処理装置。

##### (付記6)

前記実行制御部が出力する命令は、命令が有効であることを示す有効情報を含み、

前記命令転送部は、前記実行制御部が出力する有効情報を前記抑止情報を有効情報として前記演算実行部に転送する論理和部を有することを特徴とする付記2ないし付記5のいずれか1項記載の演算処理装置。

##### (付記7)

前記命令生成部は、前記実行制御部が前記複合命令を出力する場合、前記複数の個別命令のうち、前記演算実行部による実行順が2番目以降の個別命令を生成し、

50

前記命令転送部は、前記実行制御部が前記複合命令を出力する場合、前記複合命令の転送に統一して、前記命令生成部が生成する実行順が2番目以降の個別命令を転送し、

前記演算実行部は、前記複合命令を受信した場合、前記複数の命令のうち実行順が最初の命令を実行することを特徴とする付記1ないし付記6のいずれか1項記載の演算処理装置。

#### (付記8)

前記命令転送部は、

前記実行制御部が出力する命令を受信する第1のステージと、

前記第1のステージから転送される命令を前記演算実行部に出力する第2のステージを有し、10

前記命令生成部は、前記第2のステージに転送される命令が前記複合命令の場合、前記実行順が2番目以降の個別命令を前記第1のステージに出力することを特徴とする付記7記載の演算処理装置。

#### (付記9)

前記実行制御部が順次出力する先行命令および後続命令が、前記先行命令の演算結果を前記後続命令で使用する所定の組み合わせの特定命令であることを検出する依存検出部を有し、

前記命令転送部は、前記実行制御部が出力する命令が前記複合命令の場合、または、前記依存検出部が前記特定命令を検出した場合、前記実行制御部の出力の選択を停止し、前記命令生成部の出力を選択する選択部を有し、20

前記命令生成部は、前記実行制御部が出力する命令が前記複合命令の場合、前記複合命令に含まれる個別命令を前記命令転送部に出力し、前記実行制御部が出力する命令が前記複合命令でない場合、前記命令転送部で転送された命令を前記命令転送部に出力することを特徴とする付記1記載の演算処理装置。

#### (付記10)

前記命令生成部が前記複合命令に含まれる個別命令を前記命令転送部に出力する場合、または前記依存検出部が前記特定命令を検出した場合、前記実行制御部に命令の出力を抑止させる抑止情報を出力する抑止制御部を有し、

前記選択部は、前記抑止制御部が前記抑止情報を出力しない場合、前記実行制御部が出力する命令を選択し、前記抑止制御部が前記抑止情報を出力する場合、前記命令生成部が出力する命令を選択することを特徴とする付記9記載の演算処理装置。30

#### (付記11)

前記実行制御部が出力する命令は、命令が有効であることを示す有効情報を含み、

前記命令転送部は、前記依存検出部が前記特定命令を検出した場合、前記実行制御部が出力した前記後続命令に含まれる有効情報を無効状態に設定する無効設定部を有することを特徴とする付記9または付記10記載の演算処理装置。

#### (付記12)

前記特定命令は、前記先行命令を演算する前記演算実行部内の演算器が演算結果を出力してから、前記後続命令を演算する前記演算実行部内の他の演算器に前記演算結果がバイパスされるまでの時間が、1クロックサイクルを超える組み合わせの命令であることを特徴とする付記9ないし付記11のいずれか1項記載の演算処理装置。40

#### (付記13)

演算処理装置の制御方法において、

前記演算処理装置が有するデコード部が、命令をデコードし、

前記演算処理装置が有する実行制御部が、前記デコード部がデコードした命令を保持し、保持した命令を実行可能な順に出力し、

前記演算処理装置が有する命令転送部が、前記実行制御部が出力する命令を順次転送し、50

前記命令転送部が転送する命令が複数の個別命令を組み合わせた複合命令である場合、前記演算処理装置が有する命令生成部が、前記複合命令から生成した個別命令を前記命令

転送部に出力し、

前記演算処理装置が有する演算実行部が、前記命令転送部が転送した個別命令を実行することを特徴とする演算処理装置の制御方法。

(付記 14)

前記演算処理装置が有する抑止制御部が、前記命令生成部が前記複合命令に含まれる命令を前記命令転送部に出力する場合、前記実行制御部に命令の出力を抑止させる抑止情報を出力することを特徴とする付記 13 記載の演算処理装置の制御方法。

(付記 15)

前記実行制御部が出力する前記複合命令は、前記複合命令であることを識別する識別情報10を含み、

前記抑止制御部は、前記実行制御部が出力する前記識別情報に基づいて、前記抑止情報を出力することを特徴とする付記 14 記載の演算処理装置の制御方法。

(付記 16)

前記演算処理装置が有する依存検出部が、前記実行制御部が順次出力する先行命令および後続命令が、前記先行命令の演算結果を前記後続命令で使用する所定の組み合わせの特定命令であることを検出し、

前記命令転送部は、前記実行制御部が出力する命令が前記複合命令の場合、または、前記依存検出部が前記特定命令を検出した場合、前記実行制御部の出力の選択を停止し、前記命令生成部の出力を選択する選択部を有し、

前記命令生成部は、前記実行制御部が出力する命令が前記複合命令の場合、前記複合命令に含まれる命令を前記命令転送部に出力し、前記実行制御部が出力する命令が前記複合命令でない場合、前記命令転送部で転送された命令を前記命令転送部に出力することを特徴とする付記 13 記載の演算処理装置の制御方法。20

(付記 17)

前記演算処理装置が有する抑止制御部が、前記命令生成部が前記複合命令に含まれる命令を前記命令転送部に出力する場合、または前記依存検出部が前記特定命令を検出した場合、前記実行制御部に命令の出力を抑止させる抑止情報を出力し、

前記選択部は、前記抑止制御部が前記抑止情報を出力しない場合、前記実行制御部が出力する命令を選択し、前記抑止制御部が前記抑止情報を出力する場合、前記命令生成部が出力する命令を選択することを特徴とする付記 16 記載の演算処理装置の制御方法。30

(付記 18)

前記実行制御部が出力する命令は、命令が有効であることを示す有効情報を含み、

前記命令転送部の無効設定部が、前記依存検出部が前記特定命令を検出した場合、前記実行制御部が出力した前記後続命令に含まれる有効情報を無効状態に設定することを特徴とする付記 16 または付記 17 記載の演算処理装置の制御方法。

**【0146】**

以上の詳細な説明により、実施形態の特徴点および利点は明らかになるであろう。これは、特許請求の範囲がその精神および権利範囲を逸脱しない範囲で前述のような実施形態の特徴点および利点にまで及ぶことを意図するものである。また、当該技術分野において通常の知識を有する者であれば、あらゆる改良および変更に容易に想到できるはずである。したがって、発明性を有する実施形態の範囲を前述したものに限定する意図はなく、実施形態に開示された範囲に含まれる適当な改良物および均等物に拡ることも可能である。40

**【符号の説明】**

**【0147】**

1 ... デコード部； 2 ... 実行制御部； 2 F L ... セカンドフローフラグ、セカンドフロー信号； 3 ... 命令転送部； 4 ... 演算実行部； 5 ... 命令生成部； 6 ... 抑止制御部； 1 0 ... 命令キャッシュ； 1 2 ... 命令バッファ； 1 4 ... デコード部； 1 6 ... レジスタ管理部； 1 8 ... リザベーションステーション部； 2 0 ... バイパス制御部； 2 2 ... 演算実行部； 2 4 ... データキャッシュ； 2 8 ... 固定小数点演算器； 3 0 ... アドレス計算演算器； 3 2 ... レジスタ部； 1 0 0 ... A、1 0 0 B ... 演算処理装置； AND 1、AND 2 ... アンドゲート； B 1、50

B 2 ... ステージ； B P T B L ... バイパス管理テーブル； C M P 1、C M P 2、C M P 3 ... 比較器； D ... ステージ； D A T ... データ； D T ... ステージ； E N T ... エントリ； F F ... フリップフロップ； G P ... エントリ； G P R ... レジスタ； G P R N ... レジスタ番号； G P R T ... テーブル； G P R - V ... フラグ； G U B ... レジスタ； G U B N ... レジスタ番号； I C D ... 命令コード； I C D - B C ... 複合命令； I C D C K ... 命令依存チェック部； I C D O P ... 命令コード操作部； I N H ... 抑止情報、抑止信号； I N S ... 命令； I V 1 ... インバータ； O P S E L ... オペランド選択信号； O R 1、O R 2 ... オアゲート； P、P T ... ステージ； R A D ... レジスタアドレス； R S A、R S E ... リザベーションステーション； R S L T ... 演算結果； R U B A ... レジスタアドレス； S E L 1、S E L 2、S E L 3、S E L 4、S E L 5、S E L 6、S E L 7、S E L 8 ... セレクタ； U B A ... レジスタアドレス； V ... バリッドフラグ、バリッド信号； W U B A ... レジスタアドレス； X ... ステージ

10

【図1】

演算処理装置および演算処理装置の制御方法の一実施形態を示す図

100

【図2】

図1に示す演算処理装置の動作の一例を示す図

【図3】

【 四 5 】

図3に示す演算処理装置における固定小数点演算器に対応する命令、パラインの概要を示す

【 四 4 】

図3に示すレジスタ管理部およびレジスタ部の一例を示す

【 四 6 】

図5に示す命令、バイオペイントにおいて、ステージPからステージXまでに関連する回路要素の一例を示す

100A

【図 7】

図5および図6に示す命令バイオペレーティングにおける、オペランドデータをバスさせるタイミングの一例を示す図

【図 8】

図3に示す演算処理装置の動作の一例を示す図

【図 9】

図3に示す演算処理装置の動作の一例を示す図

【図 10】

図6に示す命令バイオペレーティングにおけるPサイクルおよびPTサイクルでの動作フローの一例を示す図

〔 図 1 1 〕

( 四 1 3 )

図11に示す命令／バイオラインを有する演算処理装置の動作の別の例を示す図

〔 囮 1 2 〕

( 义 1 4 )

【図 15】

図11に示す命令バイオラインにおけるPサイクルにおけるPTサイクルの一例を示す図