(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6340190号

(P6340190)

(45) 発行日 平成30年6月6日(2018.6.6)

(24) 登録日 平成30年5月18日(2018.5.18)

|                |           |        |       |         |

|----------------|-----------|--------|-------|---------|

| (51) Int.Cl.   | F 1       |        |       |         |

| HO 1 L 21/336  | (2006.01) | HO 1 L | 29/78 | 6 1 8 Z |

| HO 1 L 29/786  | (2006.01) | HO 1 L | 29/78 | 6 1 8 B |

| HO 1 L 21/8242 | (2006.01) | HO 1 L | 29/78 | 6 1 8 E |

| HO 1 L 27/108  | (2006.01) | HO 1 L | 29/78 | 6 1 6 U |

| HO 1 L 27/10   | (2006.01) | HO 1 L | 29/78 | 6 1 6 T |

請求項の数 10 (全 55 頁) 最終頁に続く

|              |                               |           |                                                |

|--------------|-------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2013-246931 (P2013-246931)  | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成25年11月29日 (2013.11.29)      | (72) 発明者  | 松林 大介<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号    | 特開2014-131025 (P2014-131025A) | (72) 発明者  | 篠原 聰始<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成26年7月10日 (2014.7.10)        | (72) 発明者  | 関根 航<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| 審査請求日        | 平成28年11月18日 (2016.11.18)      |           |                                                |

| (31) 優先権主張番号 | 特願2012-261795 (P2012-261795)  |           |                                                |

| (32) 優先日     | 平成24年11月30日 (2012.11.30)      |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面を有する基板と、

前記基板上に前記基板側から第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層の順で積層した酸化物半導体層と、

前記酸化物半導体層と接するソース電極層およびドレイン電極層と、

前記酸化物半導体層上、前記ソース電極層上および前記ドレイン電極層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極層と、

を有し、

前記第1の酸化物半導体層は第1の領域を有し、前記ゲート絶縁膜は第2の領域を有し、前記第1の領域の膜厚を $T_{S1}$ 、前記第2の領域の膜厚を $T_{G1}$ とするとき、 $T_{S1} < T_{G1}$ であり、

前記ゲート電極層は、前記ゲート絶縁膜を介して前記第2の酸化物半導体層の側面の一部を覆うことを特徴とする半導体装置。

## 【請求項 2】

請求項1において、

前記第2の酸化物半導体層のチャネル幅方向の長さが40nm以下であることを特徴とする半導体装置。

## 【請求項 3】

10

20

請求項 1 または 2 において、

前記第 2 の酸化物半導体層の膜厚が、前記第 2 の酸化物半導体層のチャネル幅方向の長さより大きいことを特徴とする半導体装置。

【請求項 4】

請求項 1 乃至 3 のいずれか一項において、

前記ソース電極層および前記ドレイン電極層のチャネル幅方向の長さは、前記第 2 の酸化物半導体層のチャネル幅方向の長さよりも小さく、前記ソース電極層および前記ドレイン電極層は、前記第 2 の酸化物半導体層のチャネル幅方向の端部を覆わないことを特徴とする半導体装置。

【請求項 5】

請求項 1 乃至 4 のいずれか一項において、

前記第 1 の酸化物半導体層乃至前記第 3 の酸化物半導体層は、 $In - M - Zn$  酸化物 (M は Al、Ti、Ga、Y、Zr、La、Ce、Nd または Hf) を有し、前記第 1 の酸化物半導体層および前記第 3 の酸化物半導体層は、In に対する M の原子数比が前記第 2 の酸化物半導体層よりも大きいことを特徴とする半導体装置。

【請求項 6】

請求項 1 乃至 5 のいずれか一項において、

前記ソース電極層は、前記酸化物半導体層に接する第 1 のソース電極層と、前記第 1 のソース電極層を覆うように設けられ、且つ、前記酸化物半導体層に接する第 2 のソース電極層と、を有し、

前記ドレイン電極層は、前記酸化物半導体層に接する第 1 のドレイン電極層と、前記第 1 のドレイン電極層を覆うように設けられ、且つ、前記酸化物半導体層に接する第 2 のドレイン電極層と、を有することを特徴とする半導体装置。

【請求項 7】

請求項 6 において、

前記第 1 のソース電極層および前記第 1 のドレイン電極層は、Al、Cr、Cu、Ta、Ti、Mo、W、またはこれらを主成分とする合金材料を有し、

前記第 2 のソース電極層および前記第 2 のドレイン電極層は、窒化タンタル、窒化チタン、またはルテニウムを含む材料を有することを特徴とする半導体装置。

【請求項 8】

絶縁表面を有する基板と、

前記基板上の第 1 の酸化物半導体層と、

前記第 1 の酸化物半導体層の第 2 の酸化物半導体層と、

前記第 2 の酸化物半導体層上の第 1 のソース電極層および第 1 のドレイン電極層と、

前記第 2 の酸化物半導体層上、前記第 1 のソース電極層上および前記第 1 のドレイン電極層上の第 3 の酸化物半導体層と、

前記第 1 のソース電極層を覆うように設けられた第 2 のソース電極層と、

前記第 1 のドレイン電極層を覆うように設けられた第 2 のドレイン電極層と、

前記第 3 の酸化物半導体層上、前記第 2 のソース電極層上および前記第 2 のドレイン電極層上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極層と、

を有し、

前記第 1 のソース電極層および前記第 1 のドレイン電極層は、前記第 1 の酸化物半導体層乃至前記第 3 の酸化物半導体層と接し、

前記第 2 のソース電極層および前記第 2 のドレイン電極層は、前記第 3 の酸化物半導体層と接し、

前記第 1 の酸化物半導体層は第 1 の領域を有し、前記ゲート絶縁膜は第 2 の領域を有し、

前記第 1 の領域の膜厚を  $T_{S1}$ 、前記第 2 の領域の膜厚を  $T_{G1}$  とするとき、 $T_{S1} = T_{G1}$  であることを特徴とする半導体装置。

10

20

30

40

50

## 【請求項 9】

請求項 8 において、

前記第 1 の酸化物半導体層乃至前記第 3 の酸化物半導体層は、  $In - M - Zn$  酸化物 (M は  $Al$ 、  $Ti$ 、  $Ga$ 、  $Y$ 、  $Zr$ 、  $La$ 、  $Ce$ 、  $Nd$  または  $Hf$  ) を有し、 前記第 1 の酸化物半導体層および前記第 3 の酸化物半導体層は、  $In$  に対する M の原子数比が前記第 2 の酸化物半導体層よりも大きいことを特徴とする半導体装置。

## 【請求項 10】

請求項 8 または 9 において、

前記第 1 のソース電極層および前記第 1 のドレイン電極層は、  $Al$ 、  $Cr$ 、  $Cu$ 、  $Ta$ 、  $Ti$ 、  $Mo$ 、  $W$ 、 またはこれらを主成分とする合金材料を有し、

前記第 2 のソース電極層および前記第 2 のドレイン電極層は、 窒化タンタル、 窒化チタン、 またはルテニウムを含む材料を有することを特徴とする半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、 物、 方法、 製造方法、 プロセス、 マシーン、 マニュファクチャー、 または、 組成物 (コンポジション オブ マター) に関する。特に、 本発明は、 例えば、 半導体装置、 表示装置、 発光装置、 それらの駆動方法、 または、 それらの製造方法に関する。特に、 本発明は、 例えば、 酸化物半導体を有する半導体装置、 表示装置、 または、 発光装置に関する。

## 【0002】

なお、 本明細書中において半導体装置とは、 半導体特性を利用することで機能しうる装置全般を指し、 電気光学装置、 半導体回路および電子機器は全て半導体装置である。

## 【背景技術】

## 【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタ (薄膜トランジスタ (TFT) ともいう) を構成する技術が注目されている。当該トランジスタは集積回路 (IC) や画像表示装置 (表示装置) のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、 その他の材料として酸化物半導体が注目されている。

## 【0004】

例えば、 トランジスタの活性層として、 インジウム ( $In$ )、 ガリウム ( $Ga$ )、 および亜鉛 ( $Zn$ ) を含む非晶質酸化物半導体を用いたトランジスタが特許文献 1 に開示されている。

## 【先行技術文献】

## 【特許文献】

## 【0005】

## 【特許文献 1】特開 2006 - 165528 号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

一般的に、 高集積化回路の形成においてトランジスタの微細化は必須技術である。一方、 トランジスタを微細化すると、 しきい値電圧や  $S$  値 (サブスレッショルド値) などのトランジスタの電気特性が悪化することが知られている。

## 【0007】

したがって、 本発明の一態様は、 微細化に伴い顕著となる電気特性の低下を抑制できる構成の半導体装置を提供することを目的の一つとする。または、 低消費電力の半導体装置を提供することを目的の一つとする。または、 信頼性の高い半導体装置を提供することを目的の一つとする。または、 本発明の一態様は、  $S$  値 (サブスレッショルド値) の悪化を低減した半導体装置を提供することを目的の一つとする。または、 本発明の一態様は、 しき

10

20

30

40

50

い値電圧の悪化を低減した半導体装置を提供することを目的の一つとする。または、本発明の一態様は、寄生チャネルを低減した半導体装置を提供することを目的の一つとする。または、本発明の一態様は、電源が遮断されてもデータが保持される半導体装置を提供することを目的の一つとする。

【0008】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

10

【0009】

本発明の一態様は、積層された酸化物半導体層を有する半導体装置に関する。

【0010】

本発明の一態様は、絶縁表面を有する基板と、基板上に基板側から第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層の順で積層した酸化物半導体層と、酸化物半導体層と接するソース電極層およびドレイン電極層と、酸化物半導体層、ソース電極層およびドレイン電極層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層と、を有し、第1の酸化物半導体層は第1の領域を有し、ゲート絶縁膜は第2の領域を有し、第1の領域の膜厚を $T_{S1}$ 、第2の領域の膜厚を $T_{G1}$ とするとき、 $T_{S1} < T_{G1}$ であることを特徴とする半導体装置である。

20

【0011】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0012】

上記構成において、第1の酸化物半導体層および第3の酸化物半導体層は、第2の酸化物半導体層よりも伝導帯下端のエネルギーが $0.05\text{ eV}$ 以上 $2\text{ eV}$ 以下の範囲で真空準位に近いことが好ましい。

【0013】

また、第1の酸化物半導体層乃至第3の酸化物半導体層は、 $\text{In-M-Zn}$ 酸化物（Mは $\text{Al}$ 、 $\text{Ti}$ 、 $\text{Ga}$ 、 $\text{Y}$ 、 $\text{Zr}$ 、 $\text{La}$ 、 $\text{Ce}$ 、 $\text{Nd}$ または $\text{Hf}$ ）であり、第1の酸化物半導体層および第3の酸化物半導体層は、 $\text{In}$ に対するMの原子数比が第2の酸化物半導体層よりも大きいことが好ましい。

30

【0014】

また、ソース電極層は、酸化物半導体層に接する第1のソース電極層と、第1のソース電極層を覆うように形成され、酸化物半導体層に接する第2のソース電極層を有し、ドレイン電極層は、酸化物半導体層に接する第1のドレイン電極層と、第1のドレイン電極層を覆うように形成され、酸化物半導体層に接する第2のドレイン電極層を有する構成としてもよい。

【0015】

また、ソース電極層は、酸化物半導体層に接する第2のソース電極層と、第2のソース電極層上に形成され、酸化物半導体層に接する第1のソース電極層を有し、ドレイン電極層は、酸化物半導体層に接する第2のドレイン電極層と、第2のドレイン電極層上に形成され、酸化物半導体層に接する第1のドレイン電極層を有する構成としてもよい。

40

【0016】

ここで、第1のソース電極層および第1のドレイン電極層は、 $\text{Al}$ 、 $\text{Cr}$ 、 $\text{Cu}$ 、 $\text{Ta}$ 、 $\text{Ti}$ 、 $\text{Mo}$ 、 $\text{W}$ 、またはこれらを主成分とする合金材料で形成され、第2のソース電極層および第2のドレイン電極層は、窒化タンタル、窒化チタン、またはルテニウムを含む材料で形成されていることが好ましい。

【0017】

また、本発明の他の一態様は、絶縁表面を有する基板と、基板上に形成された第1の酸化

50

物半導体層と、第1の酸化物半導体層に形成された第2の酸化物半導体層と、第2の酸化物半導体層上に形成された第1のソース電極層および第1のドレイン電極層と、第2の酸化物半導体層、第1のソース電極層および第1のドレイン電極層上に形成された第3の酸化物半導体層と、第1のソース電極層を覆うように形成された第2のソース電極層と、第1のドレイン電極層を覆うように形成された第2のドレイン電極層と、第3の酸化物半導体層、第2のソース電極層および第2のドレイン電極層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層と、を有し、第1のソース電極層および第1のドレイン電極層は、第1の酸化物半導体層乃至第3の酸化物半導体層と接し、第2のソース電極層および第2のドレイン電極層は、第3の酸化物半導体層と接し、第1の酸化物半導体層は第1の領域を有し、ゲート絶縁膜は第2の領域を有し、第1の領域の膜厚を  $T_{S_1}$  、第2の領域の膜厚を  $T_{G_1}$  とするとき、  $T_{S_1} > T_{G_1}$  であることを特徴とする半導体装置である。

10

#### 【0018】

上記構成において、第1の酸化物半導体層および第3の酸化物半導体層は、第2の酸化物半導体層よりも伝導帯下端のエネルギーが  $0.05\text{ eV}$  以上  $2\text{ eV}$  以下の範囲で真空準位に近いことが好ましい。

#### 【0019】

また、第1の酸化物半導体層乃至第3の酸化物半導体層は、  $\text{In-M-Zn}$  酸化物 (Mは  $\text{Al}$ 、 $\text{Ti}$ 、 $\text{Ga}$ 、 $\text{Y}$ 、 $\text{Zr}$ 、 $\text{La}$ 、 $\text{Ce}$ 、 $\text{Nd}$  または  $\text{Hf}$  ) であり、第1の酸化物半導体層および第3の酸化物半導体層は、  $\text{In}$  に対する M の原子数比が第2の酸化物半導体層よりも大きいことが好ましい。

20

#### 【0020】

また、第1のソース電極層および第1のドレイン電極層は、  $\text{Al}$ 、 $\text{Cr}$ 、 $\text{Cu}$ 、 $\text{Ta}$ 、 $\text{Ti}$ 、 $\text{Mo}$ 、 $\text{W}$ 、またはこれらを主成分とする合金材料であることが好ましい。

#### 【0021】

また、第2のソース電極層および第2のドレイン電極層は、窒化タンタル、窒化チタン、またはルテニウムを含む材料で形成されていることが好ましい。

#### 【発明の効果】

#### 【0022】

本発明の一態様を用いることにより、微細化に伴い顕著となる電気特性の低下を抑制できる構成の半導体装置を提供することができる。または、低消費電力の半導体装置を提供することができる。または、信頼性の高い半導体装置を提供することができる。または、S値(サブスレッショルド値)の悪化を低減した半導体装置を提供することができる。または、しきい値電圧の悪化を低減した半導体装置を提供することができる。または、寄生チャネルを低減した半導体装置を提供することができる。または、電源が遮断されてもデータが保持される半導体装置を提供することができる。

30

#### 【図面の簡単な説明】

#### 【0023】

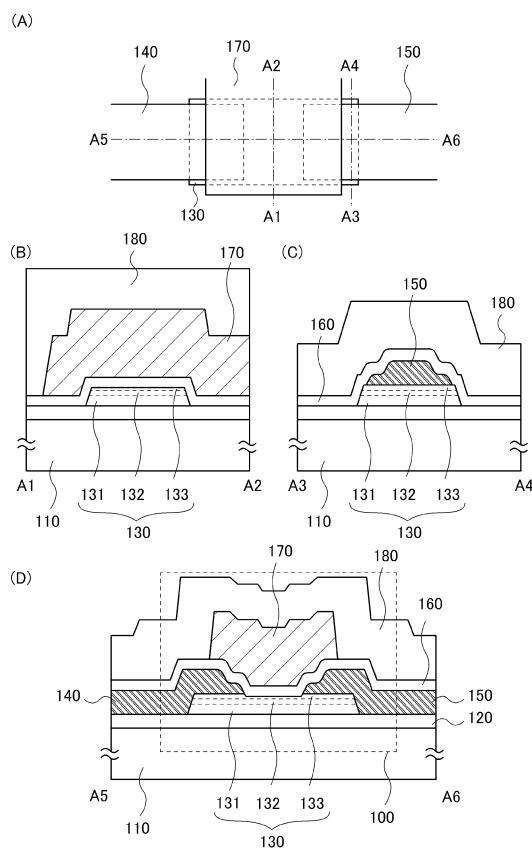

【図1】トランジスタを説明する上面図および断面図。

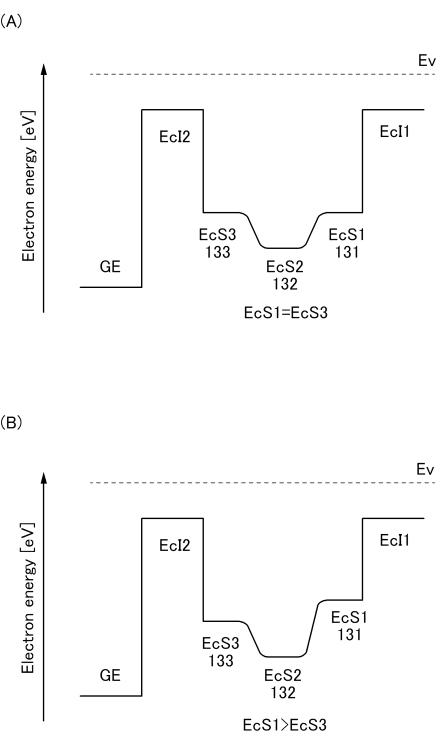

【図2】酸化物半導体層のバンド構造を説明する図。

40

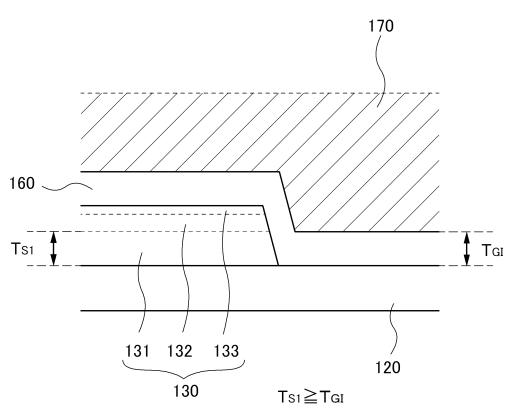

【図3】トランジスタの拡大断面図。

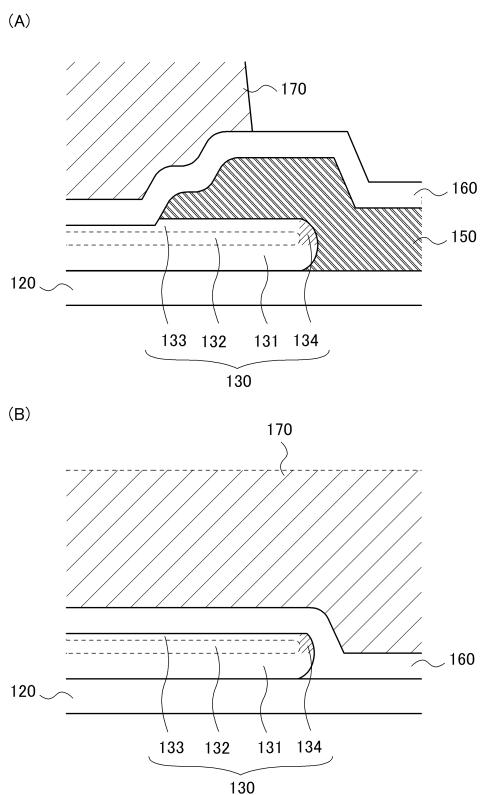

【図4】トランジスタの拡大断面図。

【図5】トランジスタを説明する上面図、断面図、および酸化物半導体層のバンド構造を説明する図。

【図6】トランジスタの拡大断面図。

【図7】トランジスタを説明する上面図および断面図。

【図8】デバイスシミュレーションに用いるモデルを説明する上面図および断面図。

【図9】デバイスシミュレーションに用いるモデルを説明する上面図および断面図。

【図10】デバイスシミュレーションに用いるモデルを説明する上面図および断面図。

【図11】デバイスシミュレーションに用いるモデルを説明する上面図および断面図。

50

- 【図12】デバイスシミュレーションの結果を説明する図。

- 【図13】デバイスシミュレーションに用いるモデルを説明する上面図および断面図。

- 【図14】デバイスシミュレーションに用いるモデルを説明する上面図および断面図。

- 【図15】デバイスシミュレーションの結果を説明する図。

- 【図16】デバイスシミュレーションの結果を説明する図。

- 【図17】デバイスシミュレーションの結果を説明する図。

- 【図18】デバイスシミュレーションに用いるモデルを説明する上面図および断面図。

- 【図19】デバイスシミュレーションの結果を説明する図。

- 【図20】トランジスタを説明する上面図および断面図。

- 【図21】トランジスタを説明する上面図および断面図。 10

- 【図22】トランジスタの作製方法を説明する図。

- 【図23】トランジスタの作製方法を説明する図。

- 【図24】トランジスタの作製方法を説明する図。

- 【図25】半導体装置の断面図および回路図。

- 【図26】半導体装置の回路図。

- 【図27】半導体装置のブロック図。

- 【図28】記憶装置を説明する回路図。

- 【図29】記憶装置の動作を説明するタイミングチャート。

- 【図30】半導体装置を適用することができる電子機器を説明する図。 20

- 【図31】ソース電極およびドレイン電極の形状を説明するトランジスタの断面図。

- 【図32】ソース電極およびドレイン電極の形状を説明するトランジスタの断面図。

- 【図33】デバイスシミュレーションの結果を説明する図。

- 【発明を実施するための形態】

- 【0024】

- 実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。 30

- 【0025】

- なお、本明細書等において、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とを含むものとする。ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

- 【0026】

- XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。 40

- 【0027】

- XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（DA変換回路、AD変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など） 50

、電圧源、電流源、切り替え回路、増幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動増幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。

#### 【0028】

なお、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟まずに接続されている場合）とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

10

#### 【0029】

なお、回路図上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、及び電極の機能の両方の構成要素の機能を併せ持っている。したがって、本明細書における電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

20

#### 【0030】

なお、本明細書等において、様々な基板を用いて、トランジスタを形成することが出来る。基板の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板又はシリコン基板）、SOI基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート（PET）、ポリエチレンナフタレート（PEN）、ポリエーテルサルファン（PES）に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。貼り合わせフィルムの一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。基材フィルムの一例としては、ポリエステル、ポリアミド、ポリイミド、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又はSOI基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。

30

#### 【0031】

なお、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

40

#### 【0032】

##### （実施の形態1）

本実施の形態では、本発明の一態様の半導体装置について図面を用いて説明する。

50

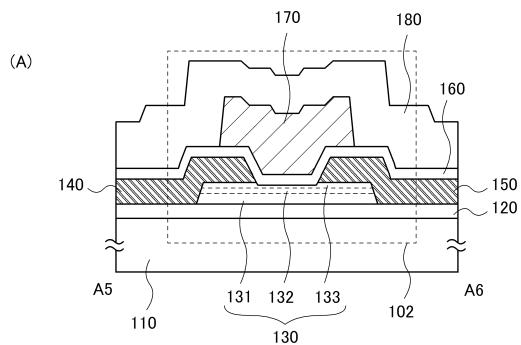

## 【0033】

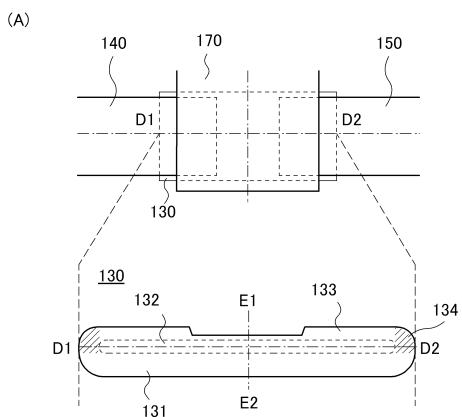

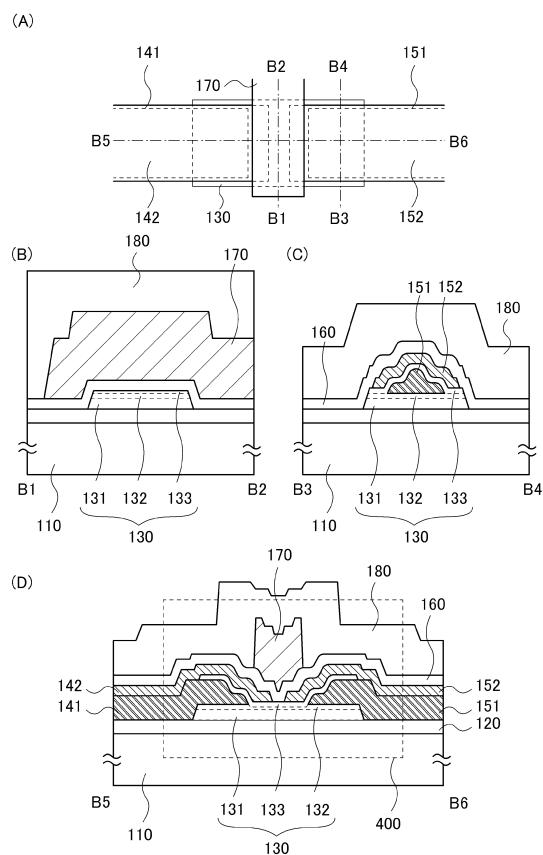

図1( A )、( B )、( C )、( D )は、本発明の一態様のトランジスタの上面図および断面図である。図1( A )は上面図であり、図1( A )に示す一点鎖線A1-A2の断面が図1( B )、一点鎖線A3-A4の断面が図1( C )、一点鎖線A5-A6の断面が図1( D )に相当する。なお、図1( A )の上面図では、図の明瞭化のために一部の要素を省いて図示している。また、一点鎖線A1-A2方向をチャネル幅方向、一点鎖線A5-A6方向をチャネル長方向と呼称する場合がある。

## 【0034】

図1( A )、( B )、( C )、( D )に示すトランジスタ100は、基板110上に形成された下地絶縁膜120と、該下地絶縁膜120上に形成された酸化物半導体層130と、該酸化物半導体層130上に形成されたソース電極層140およびドレイン電極層150と、該ソース電極層140、該ドレイン電極層150および酸化物半導体層130上に形成されたゲート絶縁膜160と、該ゲート絶縁膜160上に形成されたゲート電極層170を有する。また、該ゲート絶縁膜160および該ゲート電極層170上に酸化物絶縁層180が形成されていてもよい。当該酸化物絶縁層180は必要に応じて設ければよく、さらにその上部に他の絶縁層を形成してもよい。

10

## 【0035】

なお、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

20

## 【0036】

基板110は、単なる支持材料に限らず、他のトランジスタなどのデバイスが形成された基板であってもよい。この場合、トランジスタ100のゲート電極層170、ソース電極層140、およびドレイン電極層150の少なくとも一つは、上記の他のデバイスと電気的に接続されていてもよい。

## 【0037】

下地絶縁膜120は、基板110からの不純物の拡散を防止する役割を有するほか、酸化物半導体層130に酸素を供給する役割を担うことができるため、酸素を含む絶縁膜であることが好ましく、過剰な酸素を含む絶縁膜がより好ましい。また、上述のように基板110が他のデバイスが形成された基板である場合、下地絶縁膜120は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるようにCMP (Chemical Mechanical Polishing) 法等で平坦化処理を行うことが好ましい。

30

## 【0038】

また、酸化物半導体層130は、基板110側から第1の酸化物半導体層131、第2の酸化物半導体層132、および第3の酸化物半導体層133が積層された構造を有している。ここで、一例としては、第2の酸化物半導体層132には、第1の酸化物半導体層131および第3の酸化物半導体層133よりも電子親和力(真空準位から伝導帯下端までのエネルギー)が大きい酸化物半導体を用いる。電子親和力は、真空準位と価電子帯上端とのエネルギー差(イオン化ポテンシャル)から、伝導帯下端と価電子帯上端とのエネルギー差(エネルギーギャップ)を差し引いた値として求めることができる。

40

## 【0039】

なお、本実施の形態では、酸化物半導体層130が三層の積層である場合について説明するが、酸化物半導体層130が一層、二層または四層以上であってもよい。一層の場合は、例えば、第2の酸化物半導体層132に相当する層を用いればよい。二層の場合は、例えば、基板110側に第2の酸化物半導体層132に相当する層を用い、ゲート絶縁膜160側に第1の酸化物半導体層131または第3の酸化物半導体層133に相当する層を用いる構造、または、基板110側に第1の酸化物半導体層131または第3の酸化物半導体層133に相当する層を用い、ゲート絶縁膜160側に第2の酸化物半導体層132に相当する層を用いる構造とすればよい。四層以上である場合は、例えば、本実施の形態

50

の説明と同じように第2の酸化物半導体層132が第1の酸化物半導体層131または第3の酸化物半導体層133に相当する層で挟まれる構造とすればよい。

【0040】

第1の酸化物半導体層131および第3の酸化物半導体層133は、第2の酸化物半導体層132を構成する金属元素を一種以上含み、例えば、伝導帯下端のエネルギーが第2の酸化物半導体層132よりも、0.05eV、0.07eV、0.1eV、0.15eVのいずれか以上であって、2eV、1eV、0.5eV、0.4eVのいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

【0041】

このような構造において、ゲート電極層170に電界を印加すると、酸化物半導体層130のうち、伝導帯下端のエネルギーが最も小さい第2の酸化物半導体層132にチャネルが形成される。すなわち、第2の酸化物半導体層132とゲート絶縁膜160との間に第3の酸化物半導体層133が形成されていることによって、トランジスタのチャネルをゲート絶縁膜160と接しない構造とすることができます。

【0042】

また、第1の酸化物半導体層131は、第2の酸化物半導体層132を構成する金属元素を一種以上含んで構成されるため、第2の酸化物半導体層132と第1の酸化物半導体層131の界面に界面準位を形成しにくくなる。該界面準位はチャネルを形成することができるため、トランジスタのしきい値電圧が変動することがある。したがって、第1の酸化物半導体層131を設けることにより、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。

【0043】

また、第3の酸化物半導体層133は、第2の酸化物半導体層132を構成する金属元素を一種以上含んで構成されるため、第2の酸化物半導体層132と第3の酸化物半導体層133との界面ではキャリアの散乱が起こりにくくなる。したがって、第3の酸化物半導体層133を設けることにより、トランジスタの電界効果移動度を高くすることができる。

【0044】

第1の酸化物半導体層131および第3の酸化物半導体層133には、例えば、Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHfを第2の酸化物半導体層132よりも高い原子数比で含む材料を用いることができる。具体的には、当該原子数比を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。前述の元素は酸素と強く結合するため、酸素欠損が酸化物半導体層に生じることを抑制する機能を有する。すなわち、第1の酸化物半導体層131および第3の酸化物半導体層133は、第2の酸化物半導体層132よりも酸素欠損が生じにくいことができる。

【0045】

なお、第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133が、少なくともインジウム、亜鉛およびM(Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物であるとき、第1の酸化物半導体層131をIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub> [原子数比]、第2の酸化物半導体層132をIn:M:Zn=x<sub>2</sub>:y<sub>2</sub>:z<sub>2</sub> [原子数比]、第3の酸化物半導体層133をIn:M:Zn=x<sub>3</sub>:y<sub>3</sub>:z<sub>3</sub> [原子数比]とすると、y<sub>1</sub>/x<sub>1</sub>およびy<sub>3</sub>/x<sub>3</sub>がy<sub>2</sub>/x<sub>2</sub>よりも大きくなることが好ましい。y<sub>1</sub>/x<sub>1</sub>およびy<sub>3</sub>/x<sub>3</sub>はy<sub>2</sub>/x<sub>2</sub>よりも1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。このとき、第2の酸化物半導体層132において、y<sub>2</sub>がx<sub>2</sub>以上であるとトランジスタの電気特性を安定させることができる。ただし、y<sub>2</sub>がx<sub>2</sub>の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、y<sub>2</sub>はx<sub>2</sub>の3倍未満であることが好ましい。

【0046】

また、第1の酸化物半導体層131および第3の酸化物半導体層133のInとMの原子

10

20

30

40

50

数比率は、InおよびMの和を100 atomic %としたとき、好ましくはInが50 atomic %未満、Mが50 atomic %以上、さらに好ましくはInが25 atomic %未満、Mが75 atomic %以上とする。また、第2の酸化物半導体層132のInとMの原子数比率は、InおよびMの和を100 atomic %としたとき、好ましくはInが25 atomic %以上、Mが75 atomic %未満、さらに好ましくはInが34 atomic %以上、Mが66 atomic %未満とする。

#### 【0047】

第1の酸化物半導体層131および第3の酸化物半導体層133の厚さは、3 nm以上100 nm以下、好ましくは3 nm以上50 nm以下とする。また、第2の酸化物半導体層132の厚さは、3 nm以上200 nm以下、好ましくは3 nm以上100 nm以下、さらに好ましくは3 nm以上50 nm以下とする。

10

#### 【0048】

第1の酸化物半導体層131、第2の酸化物半導体層132、および第3の酸化物半導体層133には、例えば、インジウム、亜鉛およびガリウムを含んだ酸化物半導体を用いることができる。特に、第2の酸化物半導体層132にインジウムを含ませると、キャリア移動度が高くなるため好ましい。

#### 【0049】

なお、酸化物半導体層をチャネルとするトランジスタに安定した電気特性を付与するためには、酸化物半導体層中の不純物濃度を低減し、酸化物半導体層を真性または実質的に真性にすることが有効である。ここで、実質的に真性とは、酸化物半導体層のキャリア密度が、 $1 \times 10^{17} / \text{cm}^3$ 未満であること、好ましくは $1 \times 10^{15} / \text{cm}^3$ 未満であること、さらに好ましくは $1 \times 10^{13} / \text{cm}^3$ 未満であることを指す。

20

#### 【0050】

また、酸化物半導体層において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素は、ドナー準位の形成に寄与し、キャリア密度を増大させてしまう。また、シリコンは、酸化物半導体層中で不純物準位を形成する。当該不純物準位はトラップとなり、トランジスタの電気特性を劣化させることがある。したがって、第1の酸化物半導体層131、第2の酸化物半導体層132および第3の酸化物半導体層133の層中や、それぞれの界面において不純物濃度を低減させることが好ましい。

30

#### 【0051】

酸化物半導体層を真性または実質的に真性とするとには、SIMS (Secondary Ion Mass Spectrometry) 分析において、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms} / \text{cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms} / \text{cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms} / \text{cm}^3$ 未満とする部分を有していることが好ましい。また、水素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $2 \times 10^{20} \text{ atoms} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{19} \text{ atoms} / \text{cm}^3$ 以下、より好ましくは $1 \times 10^{19} \text{ atoms} / \text{cm}^3$ 以下、さらに好ましくは $5 \times 10^{18} \text{ atoms} / \text{cm}^3$ 以下とする部分を有していることが好ましい。また、窒素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $5 \times 10^{19} \text{ atoms} / \text{cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms} / \text{cm}^3$ 以下、より好ましくは $1 \times 10^{18} \text{ atoms} / \text{cm}^3$ 以下、さらに好ましくは $5 \times 10^{17} \text{ atoms} / \text{cm}^3$ 以下とする部分を有していることが好ましい。

40

#### 【0052】

また、酸化物半導体層が結晶を含む場合、シリコンや炭素が高濃度で含まれると、酸化物半導体層の結晶性を低下させことがある。酸化物半導体層の結晶性を低下させないためには、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms} / \text{cm}^3$ 未満、好ましくは $5 \times 10^{18}$

50

$^{8}$  atoms /  $\text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{18}$  atoms /  $\text{cm}^3$  未満とする部分を有していればよい。また、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、炭素濃度を  $1 \times 10^{19}$  atoms /  $\text{cm}^3$  未満、好ましくは  $5 \times 10^{18}$  atoms /  $\text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{18}$  atoms /  $\text{cm}^3$  未満とする部分を有していればよい。

#### 【0053】

また、上述のように高純度化された酸化物半導体層をチャネル形成領域に用いたトランジスタのオフ電流は極めて小さく、トランジスタのチャネル幅で規格化したオフ電流は、数  $y \text{ A} / \mu\text{m} \sim$  数  $z \text{ A} / \mu\text{m}$  にまで低減することが可能となる。なお、その場合のソースとドレインとの間の電圧は、例えば、0.1V、5V、または、10V程度である。

10

#### 【0054】

なお、トランジスタのゲート絶縁膜としては、シリコンを含む絶縁膜が多く用いられるため、上記理由により酸化物半導体層のチャネルとなる領域はゲート絶縁膜と接しないことが好ましいということができる。また、ゲート絶縁膜と酸化物半導体層との界面にチャネルが形成される場合、該界面でキャリアの散乱が起こり、トランジスタの電界効果移動度が低くなることがある。このような観点からも、酸化物半導体層のチャネルとなる領域はゲート絶縁膜から離すことが好ましい。

#### 【0055】

したがって、酸化物半導体層130を第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133の積層構造とすることで、トランジスタのチャネルが形成される第2の酸化物半導体層132をゲート絶縁膜から離すことができ、高い電界効果移動度を有し、安定した電気特性のトランジスタを形成することができる。

20

#### 【0056】

次に、酸化物半導体層130のバンド構造を説明する。バンド構造の解析は、第1の酸化物半導体層131および第3の酸化物半導体層133に相当する層としてエネルギーギャップが3.5eVであるIn-Ga-Zn酸化物、第2の酸化物半導体層132に相当する層としてエネルギーギャップが3.15eVであるIn-Ga-Zn酸化物を用い、酸化物半導体層130に相当する積層を作製して行っている。なお、便宜的に当該積層を酸化物半導体層130、当該積層を構成するそれぞれの層を第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133と称して説明する。

30

#### 【0057】

第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133の膜厚はそれぞれ10nmとし、エネルギーギャップは、分光エリプソメータ(HORIBA JOBIN YVON社 UT-300)を用いて測定した。また、真空準位と価電子帯上端のエネルギー差は、紫外線光電子分光分析(UPS: Ultraviolet Photoelectron Spectroscopy)装置(PHI社 Versa Probe)を用いて測定した。

#### 【0058】

図2(A)は、真空準位と価電子帯上端のエネルギー差と、各層のエネルギーギャップとの差分として算出される真空準位と伝導帯下端のエネルギー差(電子親和力)から模式的に示されるバンド構造の一部である。図2(A)は、第1の酸化物半導体層131および第3の酸化物半導体層133と接して、酸化シリコン膜を設けた場合のバンド図である。ここで、Evは真空準位のエネルギー、EcI1およびEcI2は酸化シリコン膜の伝導帯下端のエネルギー、EcS1は第1の酸化物半導体層131の伝導帯下端のエネルギー、EcS2は第2の酸化物半導体層132の伝導帯下端のエネルギー、EcS3は第3の酸化物半導体層133の伝導帯下端のエネルギーである。また、トランジスタを構成する場合、ゲート電極層(トランジスタ100ではゲート電極層170に相当)はEcI2を有する酸化シリコン膜に接するものとする。

40

#### 【0059】

図2(A)に示すように、第1の酸化物半導体層131、第2の酸化物半導体層132、

50

第3の酸化物半導体層133において、伝導帯下端のエネルギーが連続的に変化する。これは、第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133の組成が近似することにより、酸素が相互に拡散しやすい点からも理解される。したがって、第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133は組成が異なる層の積層体ではあるが、物性的に連続であるということもでき、本明細書の図面において、当該積層体のそれぞれの界面は点線で表している。

#### 【0060】

主成分を共通として積層された酸化物半導体層130は、各層を単に積層するのではなく連続接合（ここでは特に伝導帯下端のエネルギーが各層の間で連続的に変化するU字型の井戸構造（U Shape Well））が形成されるように作製する。すなわち、各層の界面にトラップ中心や再結合中心のような欠陥準位を形成するような不純物が存在しないように積層構造を形成する。仮に、積層された酸化物半導体層の層間に不純物が混在していると、エネルギーバンドの連続性が失われ、界面でキャリアがトラップあるいは再結合により消滅してしまう。

10

#### 【0061】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタ装置）を用いて各層を大気に触れさせることなく連続して積層することが必要となる。スパッタ装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべく、クライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $1 \times 10^{-4}$  Pa ~  $5 \times 10^{-7}$  Pa程度まで）できること、かつ、成膜される基板を100以上、好ましくは500以上に加熱できることが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に炭素成分や水分等を含む気体が逆流しないようにしておくことが好ましい。

20

#### 【0062】

高純度真性酸化物半導体を得るために、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100以下にまで高純度化したガスを用いることで酸化物半導体層に水分等が取り込まれることを可能な限り防ぐことができる。

30

#### 【0063】

なお、図2(A)では、ECS1とECS3が同様である場合について示したが、それらが異なっていてもよい。例えば、ECS3よりもECS1が高いエネルギーを有する場合、バンド構造の一部は、図2(B)のように示される。

#### 【0064】

例えば、ECS1 = ECS3である場合は、第1の酸化物半導体層131および第3の酸化物半導体層133にIn:Ga:Zn = 1:3:2、1:6:4または1:9:6（原子数比）、第2の酸化物半導体層132にIn:Ga:Zn = 1:1:1または3:1:2（原子数比）のIn-Ga-Zn酸化物などを用いることができる。また、ECS1 > ECS3である場合は、第1の酸化物半導体層131にIn:Ga:Zn = 1:6:4または1:9:6（原子数比）、第2の酸化物半導体層132にIn:Ga:Zn = 1:1:1または3:1:2（原子数比）、第3の酸化物半導体層133にIn:Ga:Zn = 1:3:2（原子数比）のIn-Ga-Zn酸化物などを用いることができる。

40

#### 【0065】

図2(A)、(B)より、酸化物半導体層130における第2の酸化物半導体層132がウェル（井戸）となり、酸化物半導体層130を用いたトランジスタにおいて、チャネルが第2の酸化物半導体層132に形成されることがわかる。なお、酸化物半導体層130は伝導帯下端のエネルギーが連続的に変化しているため、U字型井戸とも呼ぶことができる。また、このような構成で形成されたチャネルを埋め込みチャネルということもできる。

#### 【0066】

50

なお、第1の酸化物半導体層131および第3の酸化物半導体層133と、酸化シリコン膜などの絶縁膜との界面近傍には、不純物や欠陥に起因したトラップ準位が形成され得る。第1の酸化物半導体層131および第3の酸化物半導体層133があることにより、第2の酸化物半導体層132と当該トラップ準位とを遠ざけることができる。ただし、ECS1またはECS3と、ECS2とのエネルギー差が小さい場合、第2の酸化物半導体層132の電子が該エネルギー差を越えてトラップ準位に達することができる。トラップ準位に電子が捕獲されることで、絶縁膜界面にマイナスの電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。

## 【0067】

したがって、ECS1およびECS3と、ECS2とのエネルギー差を、それぞれ0.1eV以上、好ましくは0.15eV以上とすることで、トランジスタのしきい値電圧の変動が低減され、安定した電気特性を得ることができる。

## 【0068】

なお、第1の酸化物半導体層131、第2の酸化物半導体層132および第3の酸化物半導体層133のいずれか一つ以上の層には、結晶部が含まれることが好ましい。例えば、第1の酸化物半導体層131を非晶質とし、第2の酸化物半導体層132および第3の酸化物半導体層133を結晶部が含まれる層とする。チャネルが形成される第2の酸化物半導体層132が結晶部を含むことにより、トランジスタに安定した電気特性を付与することができる。

## 【0069】

特に、第2の酸化物半導体層132および第3の酸化物半導体層133に含まれる結晶部は、表面と略垂直な方向にc軸が配向した結晶を有することが好ましい。

## 【0070】

また、図1の構造のトランジスタにおいて、第3の酸化物半導体層133はソース電極層140およびドレイン電極層150に接しており、電流を効率良く取り出すにはエネルギー・ギャップが絶縁体のように大きくないこと、および膜厚が薄いことが好ましい。また、酸化物半導体層130にIn-Ga-Zn酸化物を用いる場合は、Inのゲート絶縁膜への拡散を防ぐために、第3の酸化物半導体層133は第2の酸化物半導体層132よりもInを少なくする組成とすることが好ましい。

## 【0071】

低消費電力の半導体装置を形成するには、トランジスタのオフ電流、特にゲート電圧が0V時の電流(icutともいう)を低減させることができ有効である。しかしながら、トランジスタを微細化するとしきい値電圧やS値(サブスレッショルド値)などのトランジスタの電気特性が悪化することが知られており、微細化と低消費電力化との両立が望まれていた。

## 【0072】

本発明の一態様のトランジスタでは、図3に示す図1(B)の拡大断面図のように、第1の酸化物半導体層131の一部である第1の領域の膜厚をT<sub>S1</sub>、ゲート絶縁膜160の一部である第2の領域の膜厚をT<sub>G1</sub>としたとき、T<sub>S1</sub> > T<sub>G1</sub>(T<sub>S1</sub>はT<sub>G1</sub>以上)として形成する。このようにすることで、ゲート電極層170がゲート絶縁膜160を介して第2の酸化物半導体層132の側面を覆うようになる。

## 【0073】

第2の酸化物半導体層132はチャネルが形成される層であり、第2の酸化物半導体層132の側面にゲート電極層170から電界を印加しやすい構造にすることによって、第2の酸化物半導体層132に対して全体的に電界が印加されるようになり、トランジスタのしきい値電圧やS値を向上させることができる。当該構造を有するトランジスタでは、W長が短い場合に特に有効であるため、トランジスタを微細化してもicutを下げることができ、消費電力を低減させることができる。また、トランジスタのしきい値電圧が安定化することから、半導体装置の長期信頼性を向上させることができる。

## 【0074】

10

20

30

40

50

また、本発明の一態様のトランジスタでは、図1(A)のトランジスタの上面図に示すように、ソース電極層140およびドレイン電極層150のチャネル幅方向の長さは、酸化物半導体層130のチャネル幅方向の長さよりも小さく、当該酸化物半導体層のチャネル長方向の端部を覆うように形成することが好ましい。このような構造とすることで、ゲート電極層170から第2の酸化物半導体層132の側面への電界印加に対する障害物が減少するため、上述したT<sub>S1</sub> - T<sub>G1</sub>によるトランジスタのしきい値電圧やS値を向上させる効果を助長させることができる。

【0075】

また、図4(A)のトランジスタの拡大断面図(チャネル長方向の断面の一部)に示すように、酸化物半導体層130の端部に曲面を有する領域134を設けても良い。酸化物半導体層130をIn-M-Zn酸化物(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)で形成する場合、第2の酸化物半導体層132を構成するM(M<sub>S2</sub>)と領域134を構成するM(M<sub>S4</sub>)の量的関係は、M<sub>S4</sub> > M<sub>S2</sub>であることが好ましい。より好ましくは、M<sub>S4</sub>は第1の酸化物半導体層131を構成するM(M<sub>S1</sub>)と同等とする。このような構成にすることによって、第2の酸化物半導体層132を保護することができる。

10

【0076】

酸化物半導体層130の端部における領域134は、ドライエッチング法にて第1の酸化物半導体層131の成分を再付着させる、所謂ラビットイヤーを利用して形成することができる。さらに酸化処理によりラビットイヤー形成時に付着するエッチングガス成分を除去し、M成分を酸化することで領域134の絶縁性を高めることができる。

20

【0077】

また、ゲート電極層が重畠する酸化物半導体層130の端部は、外的要因による不純物の混入や酸素欠損の発生などによりn型化しやすく、寄生チャネルとなることがある。特にエネルギーギャップの小さい第2の酸化物半導体層132ではn型化が顕著に起こりやすい。したがって、図4(B)に示すトランジスタの拡大断面図(チャネル幅方向の断面の一部)のように領域134が形成されることによって、寄生チャネルの発生を抑制することができる。

【0078】

図5(A)は、領域134を有するトランジスタの上面図および酸化物半導体層130の断面図である。第1の酸化物半導体層131と領域134の主成分が同一であるとき、第2の酸化物半導体層132の伝導帯下端のエネルギー(EcS2)と領域134の伝導帯下端のエネルギー(EcS4)の差分(ΔE)が大きいほど寄生チャネルの発生を抑える効果が高い。また、領域134の厚みは、第1の酸化物半導体層131または第3の酸化物半導体層133よりも厚いことが好ましく、厚いほど第2の酸化物半導体層132端部のn型化による寄生チャネルの発生を抑えることができる。

30

【0079】

また、領域134は、第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133と組成が近似することにより、酸化物半導体層のバンド構造の一部を示す図5(B)のように伝導帯下端のエネルギーが連続的に変化する。すなわち、第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133、および領域134は連続接合であるということができる。なお、図5(B)に示すD1-D2は、図5(A)の酸化物半導体層130の断面図に示す一点鎖線D1-D2方向に相当し、図5(B)に示すE1-E2は図5(A)に示す一点鎖線E1-E2方向に相当する。

40

【0080】

ソース電極層140およびドレイン電極層150には、酸素と結合し易い導電材料を用いることが好ましい。例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどを用いることができる。上記材料において、特に酸素と結合し易いTiや、後のプロセス温度が比較的高くできることなどから、融点の高いWを用いることがより好ましい。なお、酸素と結合

50

し易い導電材料には、酸素が拡散し易い材料も含まれる。

【0081】

酸素と結合し易い導電材料と酸化物半導体層を接触させると、酸化物半導体層中の酸素が、酸素と結合し易い導電材料側に拡散する現象が起こる。当該現象は、温度が高いほど顕著に起こる。トランジスタの作製工程には、いくつかの加熱工程があることから、上記現象により、酸化物半導体層のソース電極層またはドレイン電極層と接触した近傍の領域に酸素欠損が発生し、当該領域はn型化する。したがって、n型化した当該領域はトランジスタのソースまたはドレインとして作用させることができる。

【0082】

上記n型化した領域は、図6のトランジスタの拡大断面図（チャネル長方向の断面）に示される。酸化物半導体層130中に点線で示される境界135は、真性半導体領域とn型半導体領域の境界であり、酸化物半導体層130におけるソース電極層140またはドレイン電極層150と接触した近傍の領域がn型化した領域となる。なお、境界135は模式的に示したものであり、実際には明瞭ではない場合がある。また、図6では、境界135が第2の酸化物半導体層132中で横方向に延びているように位置している状態を示したが、境界135は、第1の酸化物半導体層131中、または第3の酸化物半導体層133中で横方向に延びるように位置することもある。また、酸化物半導体層130のソース電極層140またはドレイン電極層150と下地絶縁膜120との間に挟まれた領域の膜厚方向全体がn型化することもある。

【0083】

しかしながら、チャネル長が極短いトランジスタを形成する場合、上記酸素欠損の発生によってn型化した領域がトランジスタのチャネル長方向に延在してしまうことがある。この場合、トランジスタの電気特性には、しきい値電圧のシフトやゲート電圧でオンオフの制御ができない状態（導通状態）が現れる。そのため、チャネル長が極短いトランジスタを形成する場合は、ソース電極層およびドレイン電極層に酸素と結合し易い導電材料を用いることが必ずしも好ましいとはいえない。

【0084】

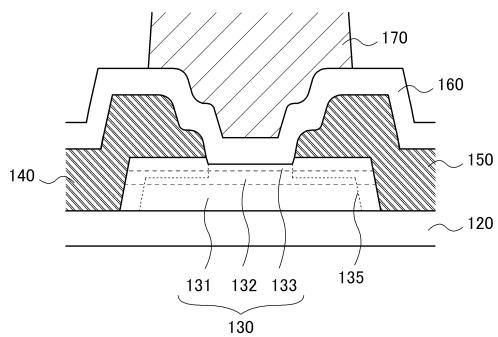

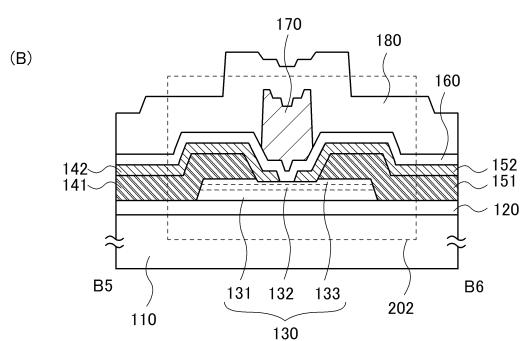

したがって、図7（A）、（B）、（C）、（D）に示すトランジスタ200のようにソース電極層およびドレイン電極層を積層とする構造としてもよい。図7（A）は上面図であり、図7（A）に示す一点鎖線B1-B2の断面が図7（B）、一点鎖線B3-B4の断面が図7（C）、一点鎖線B5-B6の断面が図7（D）に相当する。また、一点鎖線B1-B2方向をチャネル幅方向、一点鎖線B5-B6方向をチャネル長方向と呼称する場合がある。

【0085】

第1のソース電極層141および第1のドレイン電極層151には、上述したチタン膜を用い、チャネル長を定める第2のソース電極層142および第2のドレイン電極層152には、酸素と結合しにくい導電材料を用いる。当該導電材料としては、例えば、窒化タンタル、窒化チタン、またはルテニウムを含む材料などを用いることが好ましい。なお、酸素と結合しにくい導電材料には、酸素が拡散しにくい材料も含まれる。

【0086】

なお、図7の構造のトランジスタにおいて、チャネル長とは、第2のソース電極層142と第2のドレイン電極層152の間隔のことをいう。

【0087】

また、図7の構造のトランジスタにおいて、チャネルとは、第2のソース電極層142と第2のドレイン電極層152の間ににおける第2の酸化物半導体層132のことをいう。

【0088】

また、図7の構造のトランジスタにおいて、チャネル形成領域とは、第2のソース電極層142と第2のドレイン電極層152の間ににおける第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133のことをいう。

【0089】

10

20

30

40

50

上記酸素と結合しにくい導電材料を第2のソース電極層142および第2のドレイン電極層152に用いることによって、酸化物半導体層130に形成されるチャネル形成領域に酸素欠損が形成されることを抑制することができ、チャネルのn型化を抑えることができる。したがって、チャネル長が極短いトランジスタであっても良好な電気特性を得ることができる。

【0090】

なお、上記酸素と結合しにくい導電材料のみでソース電極層およびドレイン電極層を形成すると、酸化物半導体層130とのコンタクト抵抗が高くなりすぎることから、図7(C)に示すように、第1のソース電極層141および第1のドレイン電極層151を酸化物半導体層130上に形成し、第1のソース電極層141および第1のドレイン電極層151を覆うように第2のソース電極層142および第2のドレイン電極層152を形成することが好ましい。

10

【0091】

このとき、第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130との接触面積を大として、第2のソース電極層142および第2のドレイン電極層152と酸化物半導体層130との接触面積は小とすることが好ましい。第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130の接触した領域は、酸素欠損の生成によってn型化した領域となる。該n型化した領域により第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130のコンタクト抵抗を下げることができる。したがって、第1のソース電極層141および第1のドレイン電極層151と酸化物半導体層130の接触面積を大とすることで、n型化した領域の面積も大とすることが可能となる。

20

【0092】

ただし、第2のソース電極層142および第2のドレイン電極層152に窒化タンタルや窒化チタンなどの窒化物を用いる場合はその限りではない。窒化物中の窒素が酸化物半導体層130との界面近傍に僅かに拡散し、酸化物半導体層130中で窒素がドナーとして作用してn型領域を形成し、コンタクト抵抗を低下させることができる。

30

【0093】

ここで、第1のソース電極層141と第1のドレイン電極層151との間隔は、0.8μm以上、好ましくは1.0μm以上とする。当該間隔が0.8μmより小さいとチャネル形成領域において発生する酸素欠損の影響を排除できなくなり、トランジスタの電気特性が低下してしまう。

【0094】

一方、第2のソース電極層142と第2のドレイン電極層152との間隔は、例えば、30nm以下としても良好なトランジスタの電気特性を得ることができる。

【0095】

また、ゲート-ドレイン間およびゲート-ソース間の寄生容量を小さくし、半導体装置の周波数特性を向上させるため、ゲート電極層とソース電極層またはドレイン電極層とが極力重ならない構造とすることが好ましい。

40

【0096】

また、トランジスタ100のソース電極層140およびドレイン電極層150の端部、トランジスタ200の第1のソース電極層141および第1のドレイン電極層151の端部は、階段状に複数の段を設けた形状とすることが好ましい。このような複数の段を設けた形状とすることで、それらの上方に形成される膜の被覆性が向上し、トランジスタの電気特性や長期信頼性を向上させることができる。なお、図31(A)に示すトランジスタ102、図31(B)に示すトランジスタ202のように、ソース電極層140およびドレイン電極層150の端部、または第1のソース電極層141および第1のドレイン電極層151の端部は、階段状の段を設けない形状であってもよい。

【0097】

ゲート絶縁膜160には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒

50

化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、ゲート絶縁膜160は上記材料の積層であってもよい。

【0098】

ゲート電極層170は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、TaおよびWなどの導電膜を用いることができる。また、当該ゲート電極層は、上記材料の積層であってもよい。

【0099】

ゲート絶縁膜160、およびゲート電極層170上には酸化物絶縁層180が形成されていてもよい。当該酸化物絶縁層180には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、当該酸化物絶縁層180は上記材料の積層であってもよい。

10

【0100】

ここで、酸化物絶縁層180は過剰酸素を有することが好ましい。過剰酸素を含む酸化物絶縁層とは、加熱処理などによって酸素を放出することができる酸化物絶縁層をいう。好ましくは、昇温脱離ガス分光法分析にて、酸素原子に換算しての酸素の放出量が $1.0 \times 10^{19}$  atoms/cm<sup>3</sup>以上である膜とする。当該酸化物絶縁層180から放出される酸素はゲート絶縁膜160を経由して酸化物半導体層130のチャネル形成領域に拡散させることができることから、不本意に形成された酸素欠損に酸素を補填することができる。したがって、安定したトランジスタの電気特性を得ることができる。

20

【0101】

以上が本発明の一態様におけるトランジスタである。当該トランジスタは電気特性が良好であり、長期信頼性の高い半導体装置を提供することができる。

【0102】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0103】

30

(実施の形態2)

本実施の形態では、実施の形態1で説明した本発明の一態様のトランジスタの構成について、シミュレーションを行った結果を説明する。

【0104】

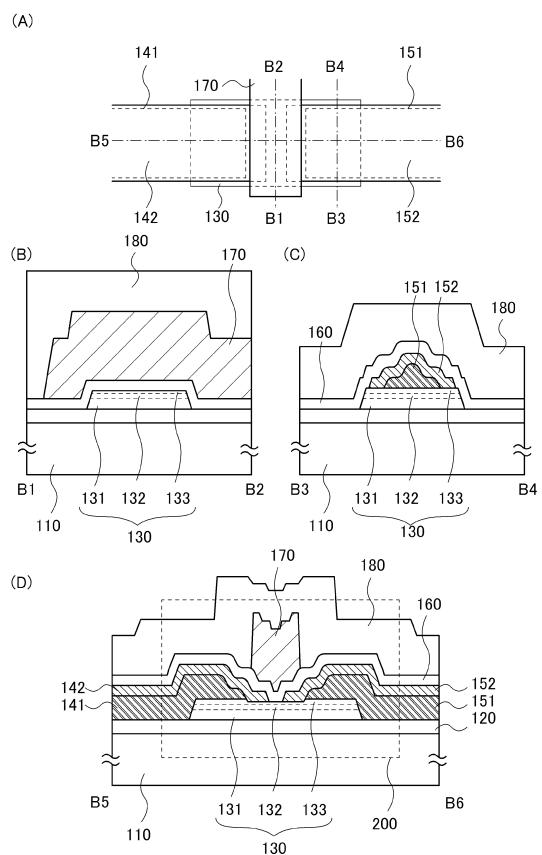

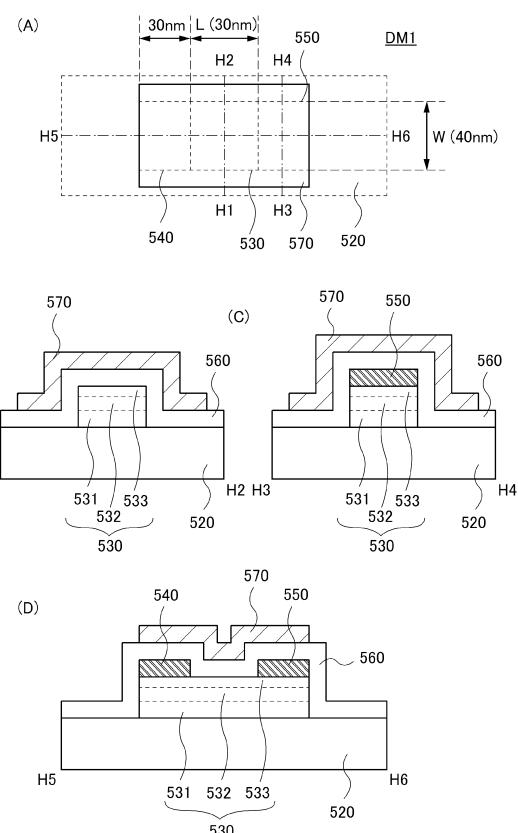

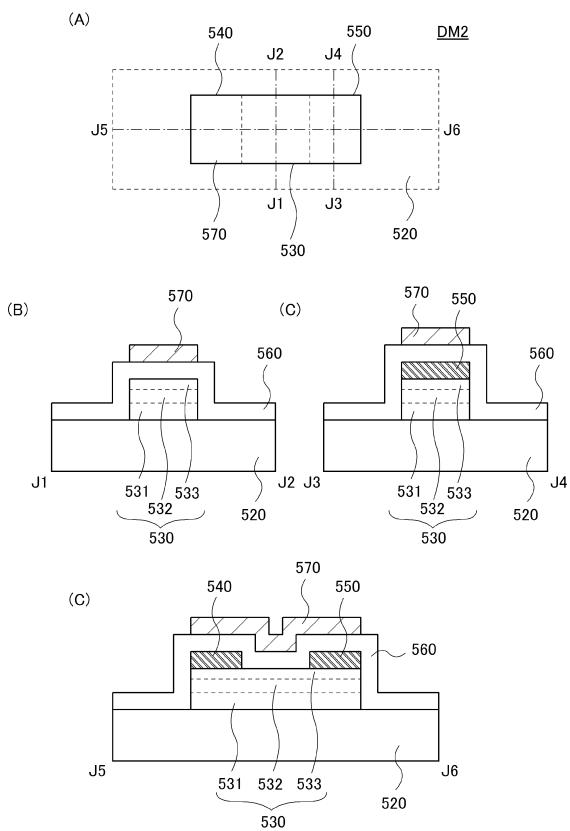

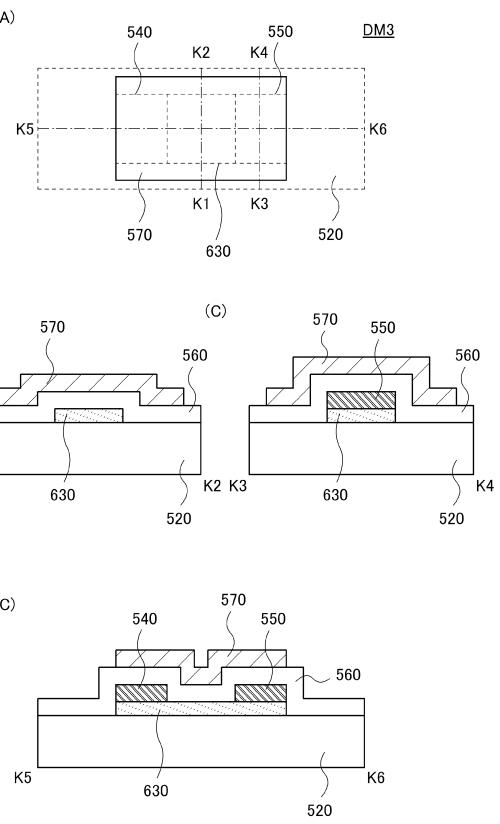

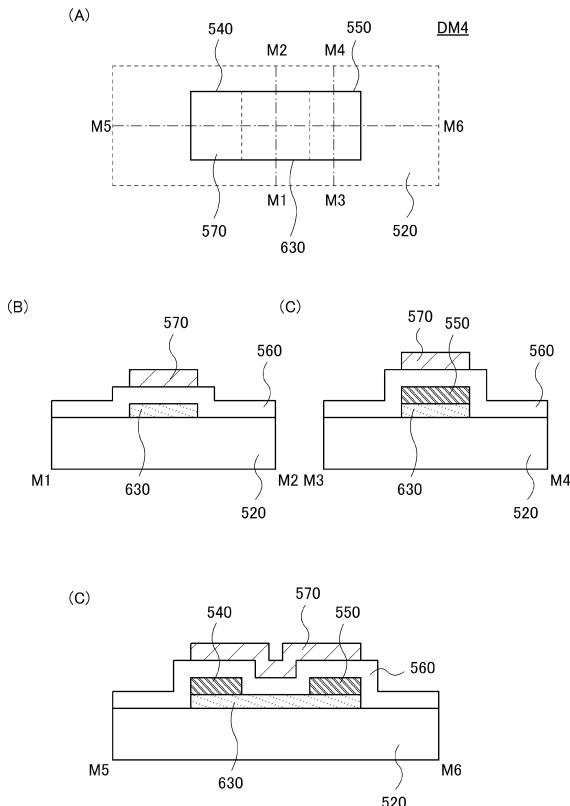

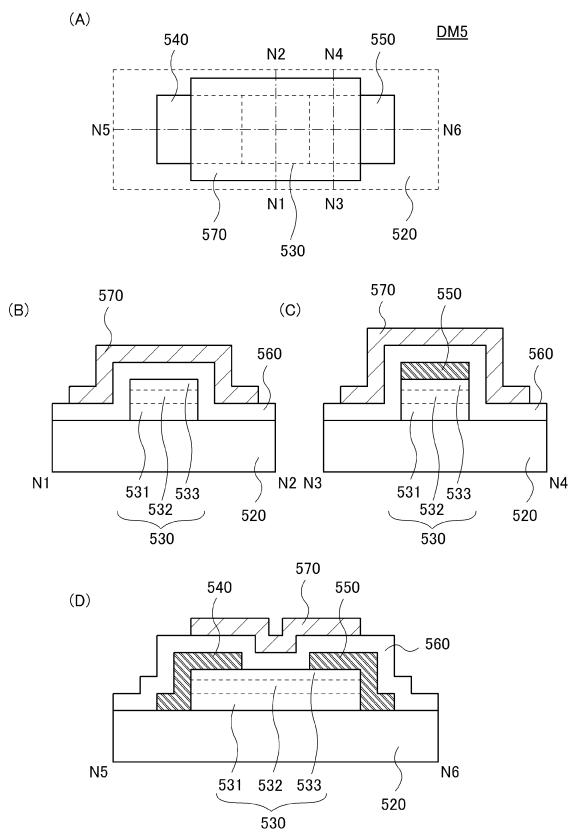

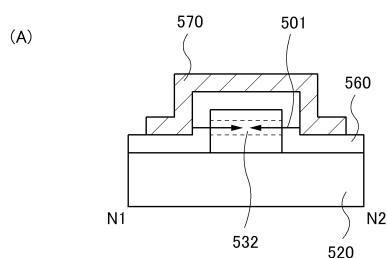

図8(A)、(B)、(C)、(D)、図9(A)、(B)、(C)、(D)、図10(A)、(B)、(C)、(D)、図11(A)、(B)、(C)、(D)は、第1のシミュレーションに用いたデバイスモデルを説明する図である。図8(A)は上面図であり、図8(A)に示す一点鎖線H1-H2の断面が図8(B)、一点鎖線H3-H4の断面が図8(C)、一点鎖線H5-H6の断面が図8(D)に相当する。また、図9(A)は上面図であり、図9(A)に示す一点鎖線J1-J2の断面が図9(B)、一点鎖線J3-J4の断面が図9(C)、一点鎖線J5-J6の断面が図9(D)に相当する。また、図10(A)は上面図であり、図10(A)に示す一点鎖線K1-K2の断面が図10(B)、一点鎖線K3-K4の断面が図10(C)、一点鎖線K5-K6の断面が図10(D)に相当する。また、図11(A)は上面図であり、図11(A)に示す一点鎖線M1-M2の断面が図11(B)、一点鎖線M3-M4の断面が図11(C)、一点鎖線M5-M6の断面が図11(D)に相当する。また、一点鎖線H1-H2、J1-J2、K1-K2、M1-M2方向をチャネル幅方向、一点鎖線H5-H6、J5-J6、K5-K6、M5-M6方向をチャネル長方向と呼称する場合がある。

40

【0105】

図8(A)、(B)、(C)、(D)に示すデバイスモデル1(以降、DM1)は、下地

50

絶縁膜 520 上に第1の酸化物半導体層 531、第2の酸化物半導体層 532、第3の酸化物半導体層 533 からなる酸化物半導体層 530、ソース電極層 540、ドレイン電極層 550、ゲート絶縁膜 560、ゲート電極層 570 を有する。また、ゲート電極層 570 は、チャネル幅方向において酸化物半導体層 530 の端部を覆う構成となっている。

【0106】

DM 1 では、トランジスタのチャネル長 L を 30 nm、チャネル幅 W を 40 nm、酸化物半導体層 530 と、ソース電極層 540 またはドレイン電極層 550 がチャネル長方向に重なる長さを 30 nm、下地絶縁膜 520 の膜厚を 300 nm、ゲート絶縁膜 560 の比誘電率を 4.1、膜厚を 20 nm、ゲート電極層の仕事関数を 4.9 eV、ソース電極層 540 およびドレイン電極層 550 の仕事関数を 4.4 eV とした。また、第1の酸化物半導体層 531 (S1)、第2の酸化物半導体層 532 (S2)、第3の酸化物半導体層 533 (S3) として用いる In-Ga-Zn 酸化物の原子数比 (In : Ga : Zn) およびシミュレーションに用いる数値は、表1に示すとおりである。なお、シミュレーションには、シノブシス社製 Sentaurus Device を用いた。また、各層や界面に局在する固定電荷や電子トラップ等は仮定していない。

【0107】

【表1】

|    | 原子数比  | 電子親和力 [eV] | Eg [eV] | 比誘電率 | Nd [cm <sup>-3</sup> ] | 電子移動度 [cm <sup>2</sup> /Vs] | 正孔移動度 [cm <sup>2</sup> /Vs] | 膜厚 [nm] |

|----|-------|------------|---------|------|------------------------|-----------------------------|-----------------------------|---------|

| S1 | 1:3:2 | 4.4        | 3.4     | 15   | 1.00E+13               | 2                           | 0.1                         | 20      |

| S2 | 1:1:1 | 4.6        | 3.15    | 15   | 1.00E+13               | 10                          | 0.1                         | 15      |

| S3 | 1:3:2 | 4.4        | 3.4     | 15   | 1.00E+13               | 2                           | 0.1                         | 5       |

【0108】

図9(A)、(B)、(C)、(D)に示すデバイスモデル2(以降、DM 2)は、DM 1 とゲート電極層 570 の形状が異なり、チャネル幅方向において酸化物半導体層 530 の端部を覆わない構成、すなわち、上面形状は酸化物半導体層 530 と同等なっている。その他の条件は DM 1 と同じである。

【0109】

図10(A)、(B)、(C)、(D)に示すデバイスモデル3(以降、DM 3)は、酸化物半導体層 580 を表1に示す S2 と同条件の単層とし、その他の条件は DM 1 と同じ(ゲート電極層 570 がチャネル幅方向において酸化物半導体層 530 の端部を覆う構成)である。

【0110】

図11(A)、(B)、(C)、(D)に示すデバイスモデル4(以降、DM 4)は、酸化物半導体層 580 を表1に示す S2 と同条件の単層とし、その他の条件は DM 2 と同じ(ゲート電極層 570 がチャネル幅方向において酸化物半導体層 530 の端部を覆わない構成)である。

【0111】

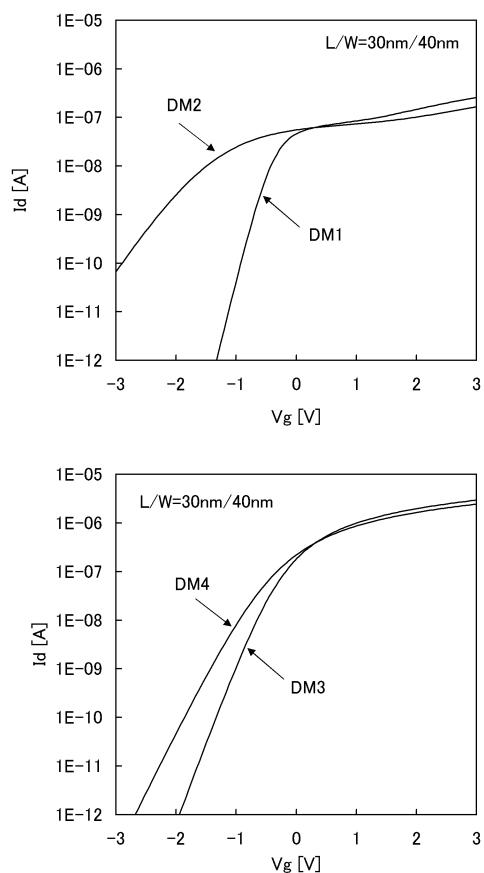

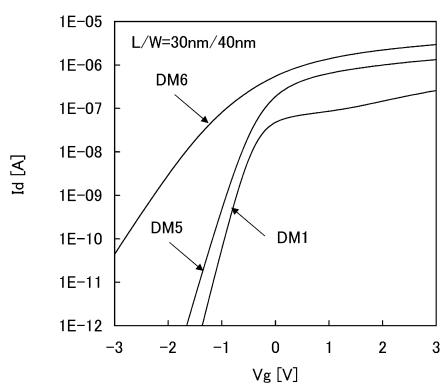

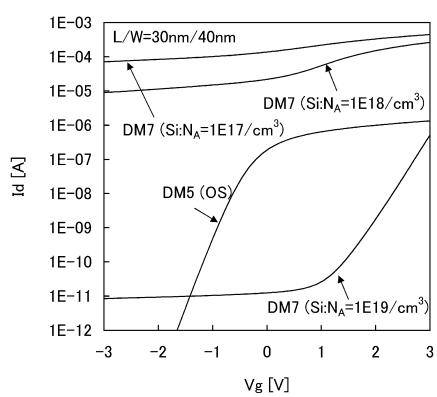

図12(A)、(B)に上記条件のデバイスモデル(DM 1、DM 2、DM 3、DM 4)を用いたシミュレーションにより得られた Id - Vg 特性を示す。

【0112】

まず、酸化物半導体層が積層構造を有する DM 1 と DM 2 の比較では、ゲート電極層 570 がチャネル幅方向において酸化物半導体層 530 の端部を覆う構成である DM 1 の特性が良好となった(図12(A)参照)。また、酸化物半導体層が単層構造を有する DM 3 と DM 4 の比較では、ゲート電極層 570 がチャネル幅方向において酸化物半導体層 580 の端部を覆う構成である DM 3 の特性が良好となった(図12(B)参照)。ここで、DM 1 と DM 3 の比較においては、DM 1 のほうが、S 値およびしきい値電圧が良好である。したがって、I cut を小さくする目的においては、DM 1 の構造、すなわち、酸化物半導体層が積層構造であって、ゲート電極層がチャネル幅方向において酸化物半導体層の端部を覆う構成が優位といえる。

10

20

30

40

50

## 【0113】

これは、DM1における第1の酸化物半導体層531の一部の領域とゲート絶縁膜560の一部の領域の膜厚を同じに設定したことに起因する。この場合、酸化物半導体層530において、チャネルが形成される第2の酸化物半導体層532の相対位置が高くなり、第2の酸化物半導体層532の端部がゲート絶縁膜560を介してゲート電極層570で覆われるため、第2の酸化物半導体層532の全体に対してゲート電極層570からの電界印加がされやすくなる。一方、DM2、DM3、DM4では、酸化物半導体層530、580の端部がゲート絶縁膜560を介してゲート電極層570で覆われる構造とはならぬいため、いずれも不十分な  $I_d - V_g$  特性となってしまう。

## 【0114】

10

したがって、第1のシミュレーション結果から、酸化物半導体層を積層構造とし、当該積層構造においてチャネルとなる層の相対位置を高くすること、そして当該チャネルとなる層に対して横方向からもゲート電極層からの電界が印加されやすい構成にすることが有効であることがわかった。具体的には、チャネルとなる層の下層に位置する層の一部の領域の膜厚をゲート絶縁膜の一部の領域の膜厚と同等以上とし、酸化物半導体層端部を覆うようにゲート電極層を形成すればよい。

## 【0115】

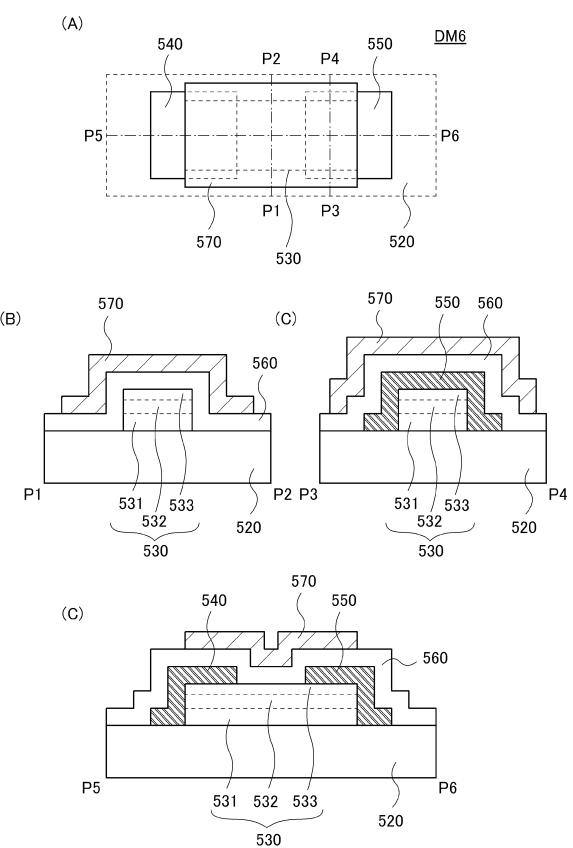

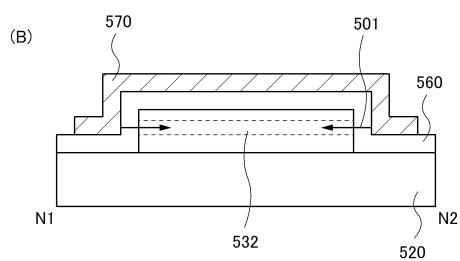

図13(A)、(B)、(C)、(D)、図14(A)、(B)、(C)、(D)は、第2のシミュレーションに用いたデバイスモデルを説明する図である。図13(A)は上面図であり、図13(A)に示す一点鎖線N1-N2の断面が図13(B)、一点鎖線N3-N4の断面が図13(C)、一点鎖線N5-N6の断面が図13(D)に相当する。また、図14(A)は上面図であり、図14(A)に示す一点鎖線P1-P2の断面が図14(B)、一点鎖線P3-P4の断面が図14(C)、一点鎖線P5-P6の断面が図14(D)に相当する。また、一点鎖線N1-N2、P1-P2方向をチャネル幅方向、一点鎖線N5-N6、P5-P6方向をチャネル長方向と呼称する場合がある。

20

## 【0116】

図13(A)、(B)、(C)、(D)に示すデバイスモデル5(以降、DM5)は、DM1とソース電極層540またはドレイン電極層550の形状が異なり、ソース電極層540またはドレイン電極層550が酸化物半導体層530のチャネル長方向の端部を覆う構成となっている。その他の条件はDM1と同じである。

30

## 【0117】

図14(A)、(B)、(C)、(D)に示すデバイスモデル6(以降、DM6)は、DM1とソース電極層540またはドレイン電極層550の形状が異なり、ソース電極層540またはドレイン電極層550が酸化物半導体層530のチャネル長方向の端部およびチャネル幅方向の端部の一部を覆う構成となっている。その他の条件はDM1と同じである。つまり、DM5とDM6では、ソース電極層540またはドレイン電極層550がチャネル幅方向の端部の一部を覆うか否かが異なる。

## 【0118】

図15は、上記条件のデバイスモデル(DM1、DM5、DM6)を用いたシミュレーションにより得られた  $I_d - V_g$  特性である。図15におけるDM5とDM6の比較では、ソース電極層540またはドレイン電極層550が酸化物半導体層530のチャネル幅方向の端部を覆わない構成であるDM5の特性が良好となった。また、DM5はDM1と比較して若干しきい値電圧がマイナス側にあるものの、S値は同等であり、高いオン電流を示した。したがって、オン電流を含めた特性向上を目的にする場合においては、DM5の構造、すなわち、ソース電極層またはドレイン電極層が酸化物半導体層のチャネル長方向の端部を覆い、チャネル幅方向の端部を覆わない構成が好ましいといえる。

40

## 【0119】

これは、酸化物半導体層530のチャネル幅方向の端部をソース電極層540またはドレイン電極層550で覆うことにより、ゲート電極層570からの電界の一部が遮断され、酸化物半導体層530、特にチャネルが形成される第2の酸化物半導体層532に当該電

50

界が印加されにくくなるためである。

【0120】

したがって、第2のシミュレーション結果から、酸化物半導体層を積層構造とし、チャネルとなる層へのゲート電極層からの電界印加を妨げない構成にすることが有効であることがわかった。具体的には、ソース電極層またはドレイン電極層が酸化物半導体層のチャネル長方向の端部を覆い、チャネル幅方向の端部を覆わない構成とすればよい。または、ソース電極層またはドレイン電極層のチャネル幅方向の長さが酸化物半導体層のチャネル幅方向の長さと同じ、または小さくなるような構成ということもできる。

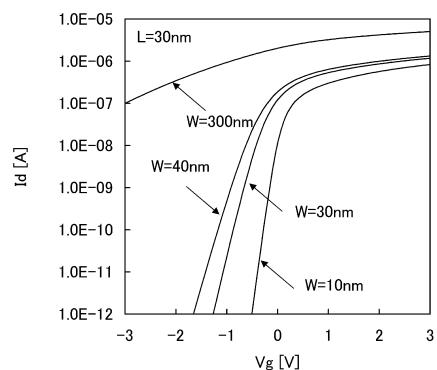

【0121】

次に、DM5の構成を基本とするデバイスモデルを用いて、トランジスタのW長に関する第3のシミュレーションを行った。第3のシミュレーションのデバイスモデルにおいては、酸化物半導体層530のチャネル幅方向の長さ、およびソース電極層またはドレイン電極層のチャネル幅方向の長さを一致させ、当該長さをW長として定義した。そして、W=300nm、40nm、30nm、10nmをシミュレーションの条件とした。その他の条件はDM5と同じである。

10

【0122】

図16は、上記条件のデバイスモデルを用いたシミュレーションにより得られたId-Vg特性である。W長が300nmの場合、オフ特性が非常に悪いが、W長を40nm以下とすることでS値が著しく改善することわかる。

【0123】

20

これは、第2の酸化物半導体層532のチャネルが形成される領域に対して、第2の酸化物半導体層532の側面からの電界印加の寄与度がW長が小さいほど大きいためである。図33(A)、(B)は、図13(B)に相当するDM5のチャネル幅方向の断面であり、第2の酸化物半導体層532が横方向から受ける電界強度を模式的にベクトルで表した図である。図33(A)に示すように、W長が小さい場合は、第2の酸化物半導体層532に対して横方向に印加される電界はチャネル全体に及ぶが、図33(B)に示すように、W長が長い場合は当該電界はチャネル全体に及ばない。したがって、DM5の構成における効果は、W長が小さいトランジスタほど有効であるといえる。

【0124】

次に、DM5の構成を基本とするデバイスモデルを用いて、酸化物半導体層530に含まれる第2の酸化物半導体層532の膜厚に関して、第4のシミュレーションを行った。第4のシミュレーションでは、L/W=30nm/40nmのデバイスモデルにおいて、第2の酸化物半導体層532の膜厚を5nm乃至90nmとするシミュレーション条件を用いた。また、L/W=30nm/300nmのデバイスモデルにおいては、第2の酸化物半導体層532の膜厚を5nm乃至50nmとするシミュレーション条件を用いた。その他の条件はDM5と同じである。

30

【0125】

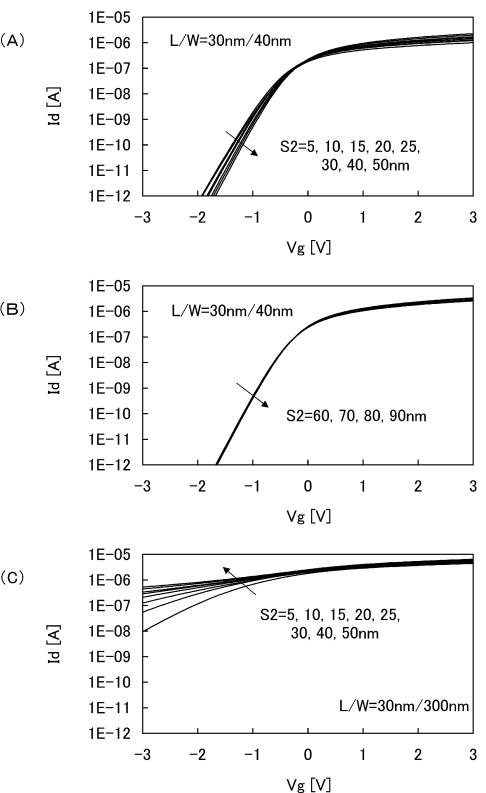

図17(A)、(B)、(C)は、上記条件のデバイスモデルを用いたシミュレーションにより得られたId-Vg特性である。図17(A)、(B)は、L/W=30nm/40nmのデバイスモデルにおけるId-Vg特性のシミュレーション結果であり、図17(A)に第2の酸化物半導体層532の膜厚が5nm、10nm、15nm、20nm、25nm、30nm、40nm、50nmの結果を示し、図17(B)に第2の酸化物半導体層532の膜厚が60nm、70nm、80nm、90nmの結果を示している。また、図17(C)は、L/W=30nm/300nmのデバイスモデルにおけるId-Vg特性のシミュレーション結果であり、第2の酸化物半導体層532の膜厚が5nm、10nm、15nm、20nm、25nm、30nm、40nm、50nmの結果を示している。それぞれの図において、矢印の始点側から終点側にかけて膜厚が順次増加する条件となっている。

40

【0126】

図17(A)に示されるように、L/W=30nm/40nmのデバイスモデルにおいて

50

は、第2の酸化物半導体層532の膜厚が50nm程度までは膜厚が厚いほどS値およびオン電流が改善される結果となった。そして、図17(B)に示されるように、第2の酸化物半導体層532の膜厚が60nm以上となるとS値およびしきい値電圧はほとんど変化がなくなり、オン電流のみ膜厚とともに増加する傾向となった。

【0127】

一方、図17(C)に示されるように、 $L/W = 30\text{nm}/300\text{nm}$ のデバイスモデルにおいては、第2の酸化物半導体層532の膜厚が5nm乃至50nmのいずれであってもS値およびしきい値電圧は向上せず、それらの膜厚の依存においては $L/W = 30\text{nm}/40\text{nm}$ のデバイスモデルとは逆の傾向となった。

【0128】

これは、第2の酸化物半導体層532の膜厚が厚いほど側面の面積が大きくなり、第2の酸化物半導体層532全体に対するゲート電極層570からの電界印加がされやすくなるためである。一方、W長が長い場合は、第3のシミュレーションの結果と同様に第2の酸化物半導体層532の側面側から印加されるゲート電極層570からの電界が第2の酸化物半導体層532に形成されるチャネル全体にまで及ばないため、 $I_d - V_g$ 特性は向上しない。

【0129】

したがって、W長を極短くすること、および第2の酸化物半導体層532の膜厚を厚くすることが有効なため、DM5の構造は、トランジスタの構造をフィン型(酸化物半導体層530の膜厚>W長)にすることに対しても適しているといえ、微細化とともにうるうる電流の減少の抑制にも効果を奏する。

【0130】

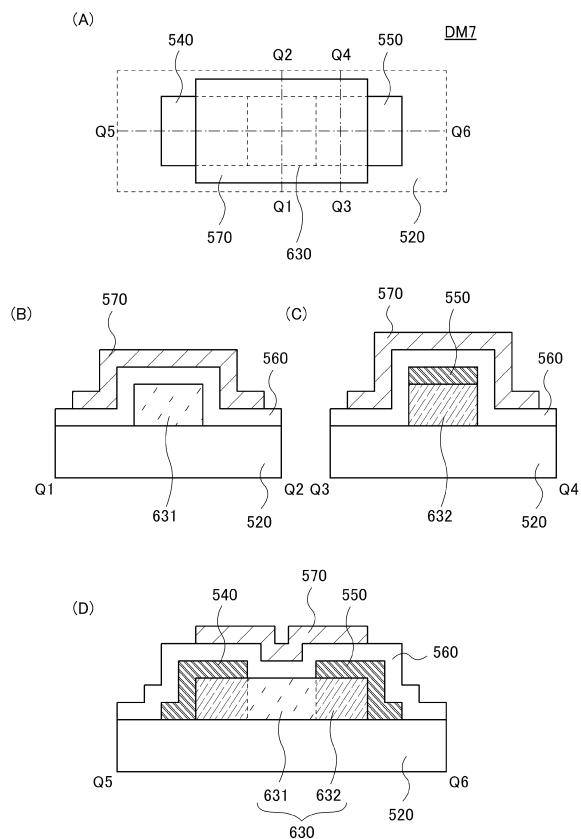

次に、トランジスタの活性層を酸化物半導体(OS)とするデバイスモデルとシリコン(Si)とするデバイスモデルの比較を第5のシミュレーションとして行った。活性層をシリコンとするデバイスモデル7(以降、DM7)は、図18(A)、(B)、(C)、(D)に示すように、DM5を基本とし、シリコン活性層630は $n^+$ 型領域632、 $p^-$ 型領域631を有する構成とした。ここで、 $n^+$ 型領域632のドナー不純物密度( $N_D$ )を $1E20/\text{cm}^3$ とし、 $p^-$ 型領域631のアクセプタ不純物密度( $N_A$ )を $1E17/\text{cm}^3$ 、 $1E18/\text{cm}^3$ 、 $1E19/\text{cm}^3$ としてシミュレーションを行った。

【0131】

図19は、活性層をシリコンとするDM7を用いたシミュレーションにより得られた $I_d - V_g$ 特性である。また、比較として、図15で示した活性層を酸化物半導体層とするDM5の $I_d - V_g$ 特性を図示している。

【0132】

DM7では、 $N_A$ が比較的小さい場合、オフ特性が非常に悪く、ほとんどオンオフ比がとれない結果となった。また、 $N_A$ が比較的大きい場合は、オンオフ比がとれるようになるが、オフ電流はDM5と比べて十分に下がりきらない結果となった。

【0133】

以上の本実施の形態で説明した、第1乃至第5のシミュレーション結果より、活性層を酸化物半導体層の積層とする構成であること、当該積層においてチャネルとなる中間層の相対位置を高くし、当該中間層の側面からもゲート電極層からの電界が印加しやすい構成とすること、ソース電極層またはドレイン電極層で活性層のチャネル幅方向の端部を覆わず、ゲート電極層から活性層に印加される電界を遮蔽しない構成とすることがトランジスタの特性向上に対して有意であることが明らかとなった。また、当該構成において、W長を小さくすること、およびチャネルとなる中間層を厚くすることも有意であることも明らかとなった。したがって、他の実施の形態で説明する本発明の一態様における半導体装置は、微細構造であっても電気特性が良好であり、信頼性が高いということができる。

【0134】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

10

20

30

40

50

## 【0135】

(実施の形態3)

本実施の形態では、実施の形態1で説明したトランジスタとは異なる構造のトランジスタについて説明する。

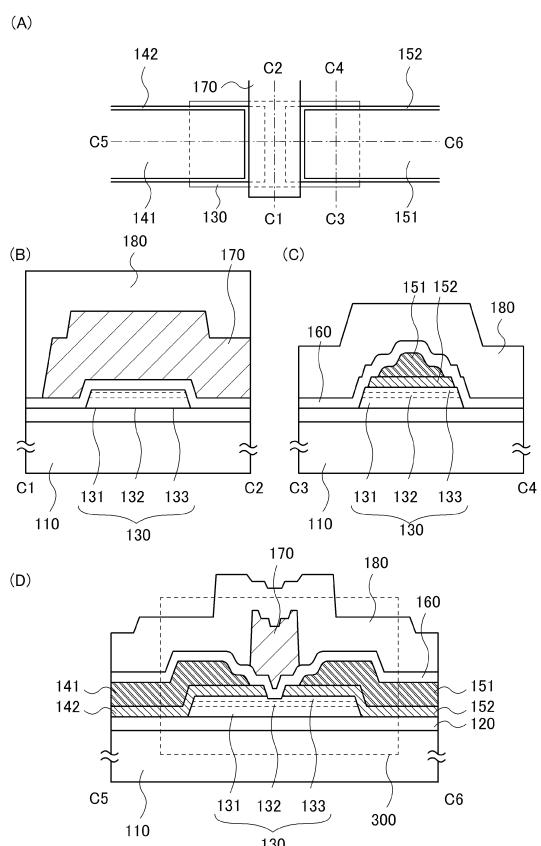

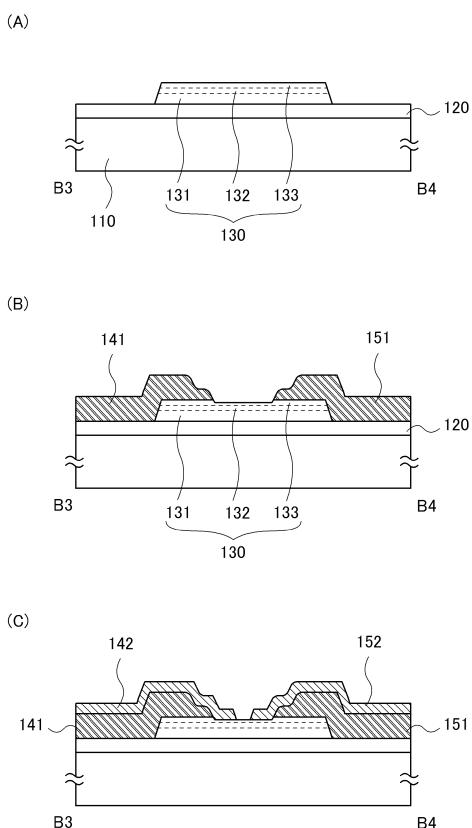

## 【0136】

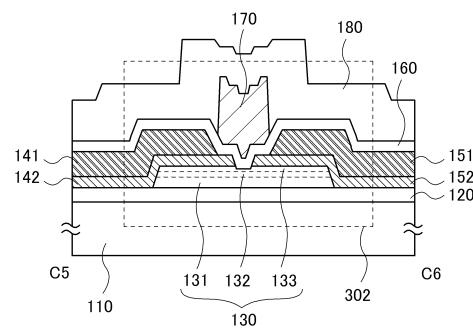

図20(A)、(B)、(C)、(D)は、本発明の一態様のトランジスタの上面図および断面図である。図20(A)は上面図であり、図20(A)に示す一点鎖線C1-C2の断面が図20(B)、一点鎖線C3-C4の断面が図20(C)、一点鎖線C5-C6の断面が図20(D)に相当する。なお、図20(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。また、一点鎖線C1-C2方向をチャネル幅方向、一点鎖線C5-C6方向をチャネル長方向と呼称する場合がある。

10

## 【0137】

図20(A)、(B)、(C)、(D)に示すトランジスタ300は、基板110上に形成された下地絶縁膜120と、該下地絶縁膜120上に形成された酸化物半導体層130と、該酸化物半導体層130上に形成された第2のソース電極層142および第2のドレイン電極層152と、該第2のソース電極層142および該第2のドレイン電極層152のそれぞれの上に形成された第1のソース電極層141および第1のドレイン電極層151と、該第1のソース電極層141、該第2のソース電極層142、該第1のドレイン電極層151、該第2のドレイン電極層152、および酸化物半導体層130上に形成されたゲート絶縁膜160と、該ゲート絶縁膜160上に形成されたゲート電極層170と、該ゲート絶縁膜160および該ゲート電極層170上に形成された酸化物絶縁層180を有する。なお、酸化物絶縁層180は必要に応じて設ければよく、さらにその上部に他の絶縁層を形成してもよい。

20

## 【0138】

図7(A)、(B)、(C)、(D)に示すトランジスタ200と図20(A)、(B)、(C)、(D)に示すトランジスタ300とは、第1のソース電極層141と第2のソース電極層142との積層順序、および第1のドレイン電極層151と第2のドレイン電極層152との積層順序が異なり、その他の点では同じである。

## 【0139】

トランジスタ300では、酸化物半導体層130と、第1のソース電極層141および第1のドレイン電極層151とが接していないことから、第1のソース電極層141および第1のドレイン電極層151が起因した酸化物半導体層130における酸素欠損の発生は起こらない。そのため、当該酸素欠損によってソースまたはドレインとして作用するn型領域は形成されない。

30

## 【0140】

トランジスタ300においては、第2のソース電極層142および第2のドレイン電極層152に実施の形態1で説明した導電性の窒化物(窒化タンタルまたは窒化チタン)を用いる。したがって、当該窒化物から酸化物半導体層130の界面近傍にドナーとなる窒素を拡散させることができ、窒素を拡散させた領域をソースまたはドレインとして作用させることができる。なお、窒素はチャネル長方向にも拡散することができ、図示してあるようにチャネル形成領域の一部を取り除くことが好ましい。当該チャネル形成領域の一部は、第2のソース電極層142および第2のドレイン電極層152の形成時のエッチング工程によっても取り除くことができる。なお、窒素は酸化物半導体層130中に深く拡散させる必要はなく、界面近傍に拡散させるのみで十分にソースまたはドレインとして作用させることができる。

40

## 【0141】

また、トランジスタ300では、第1のソース電極層141および第1のドレイン電極層151が起因した酸化物半導体層130における酸素欠損の発生は起こらないことから、第1のソース電極層141と第1のドレイン電極層151の距離をトランジスタ100よりも短くすることができる。例えば、第2のソース電極層142の端面と第1のソース電

50

極層 141 の端面、および第 2 のドレイン電極層 152 の端面と第 1 のドレイン電極層 151 の端面とを一致させててもよい。このようにすることで、ソース電極層およびドレイン電極層全体としての抵抗を低下させることができる。

【 0142 】

また、トランジスタ 300 の第 1 のソース電極層 141 および第 1 のドレイン電極層 151 の端部は、階段状に複数の段を設けた形状とすることが好ましい。このような複数の段を設けた形状とすることで、それらの上方に形成される膜の被覆性が向上し、トランジスタの電気特性や長期信頼性を向上させることができる。なお、図 32 (A) に示すトランジスタ 302 のように、第 1 のソース電極層 141 および第 1 のドレイン電極層 151 の端部は、階段状の段を設けない形状であってもよい。

10

【 0143 】

低消費電力の半導体装置を形成するには、トランジスタのオフ電流、特にゲート電圧が 0 V 時の電流 (  $I_{cut}$  ともいう) を低減させることができることが有効である。しかしながら、トランジスタを微細化するとしきい値電圧や S 値 ( サブスレッショルド値 ) などのトランジスタの電気特性が悪化することが知られており、微細化と低消費電力化との両立が望まれていた。

【 0144 】

本発明の一態様のトランジスタでは、第 1 の酸化物半導体層 131 の一部である第 1 の領域の膜厚を  $T_{S1}$  、ゲート絶縁膜 160 の一部である第 2 の領域の膜厚を  $T_{GI}$  としたとき、 $T_{S1} = T_{GI}$  ( $T_{S1}$  は  $T_{GI}$  以上) として形成する。このようにすることで、ゲート電極層 170 がゲート絶縁膜 160 を介して第 2 の酸化物半導体層 132 の側面を覆うようになる。

20

【 0145 】

第 2 の酸化物半導体層 132 はチャネルが形成される層であり、第 2 の酸化物半導体層 132 の側面にゲート電極層 170 から電界を印加しやすい構造にすることによって、第 2 の酸化物半導体層 132 に対して全体的に電界が印加されるようになり、トランジスタのしきい値電圧や S 値を向上させることができる。当該構造を有するトランジスタでは、W 長が短い場合に特に有効であるため、トランジスタを微細化しても  $I_{cut}$  を下げることができ、消費電力を低減させることができる。また、トランジスタのしきい値電圧が安定化することから、半導体装置の長期信頼性を向上させることができる。

30

【 0146 】

また、本発明の一態様のトランジスタでは、図 20 (A) のトランジスタの上面図に示すように、ソース電極層 140 およびドレイン電極層 150 のチャネル幅方向の長さは、酸化物半導体層 130 のチャネル幅方向の長さよりも小さく、当該酸化物半導体層のチャネル長方向の端部を覆うように形成することが好ましい。このような構造とすることで、ゲート電極層 170 から第 2 の酸化物半導体層 132 の側面への電界印加に対する障害物が減少するため、上述した  $T_{S1} = T_{GI}$  によるトランジスタのしきい値電圧や S 値を向上させる効果を助長させることができる。

【 0147 】

以上が本発明の一態様におけるトランジスタである。当該トランジスタは電気特性が良好であり、長期信頼性の高い半導体装置を提供することができる。

40

【 0148 】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【 0149 】

( 実施の形態 4 )

本実施の形態では、実施の形態 1 および実施の形態 3 で説明したトランジスタとは異なる構造のトランジスタについて説明する。

【 0150 】

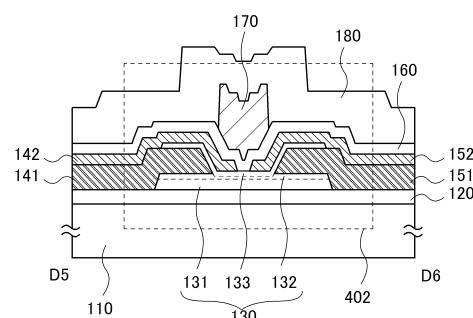

図 21 (A) 、 (B) 、 (C) 、 (D) は、本発明の一態様のトランジスタの上面図およ

50

び断面図である。図21(A)は上面図であり、図21(A)に示す一点鎖線D1-D2の断面が図21(B)、一点鎖線D3-D4の断面が図21(C)、一点鎖線D5-D6の断面が図21(D)に相当する。なお、図21(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。また、一点鎖線D1-D2方向をチャネル幅方向、一点鎖線D5-D6方向をチャネル長方向と呼称する場合がある。

#### 【0151】

図21(A)、(B)、(C)、(D)に示すトランジスタ400は、基板110上に形成された下地絶縁膜120と、該下地絶縁膜120上に形成された第1の酸化物半導体層131および第2の酸化物半導体層132と、該第2の酸化物半導体層132上に形成された第1のソース電極層141および第1のドレイン電極層151と、該第2の酸化物半導体層132、該第1のソース電極層141、および該第1のドレイン電極層151上に形成された第3の酸化物半導体層133と、第1のソース電極層141を覆うように重畠し、該第1のソース電極層141および第3の酸化物半導体層133のそれぞれと接する第2のソース電極層142と、第1のドレイン電極層151を覆うように重畠し、該第1のドレイン電極層151および第3の酸化物半導体層133のそれぞれと接する第2のドレイン電極層152と、第3の酸化物半導体層133、第2のソース電極層142、および第2のドレイン電極層152上に形成されたゲート絶縁膜160と、該ゲート絶縁膜160上に形成されたゲート電極層170と、該ゲート絶縁膜160および該ゲート電極層170上に形成された酸化物絶縁層180を有する。なお、酸化物絶縁層180は必要に応じて設ければよく、さらにその上部に他の絶縁層を形成してもよい。

10

20

#### 【0152】

図7(A)、(B)、(C)、(D)に示すトランジスタ200と図21(A)、(B)、(C)、(D)に示すトランジスタ400とは、第3の酸化物半導体層133が第1のソース電極層141上および第1のドレイン電極層151上に形成されている点が異なり、その他の点は同じである。

#### 【0153】

トランジスタ400では、チャネルが形成される第2の酸化物半導体層132と第1のソース電極層141上および第1のドレイン電極層151が接しており、第2の酸化物半導体層132に高密度の酸素欠損が生成し、n型領域が形成される。したがって、キャリアのパスに抵抗成分が少なく、効率良くキャリアを移動させることができる。

30

#### 【0154】

また、第3の酸化物半導体層133は、第1のソース電極層141および第1のドレイン電極層151形成後に形成するため、該第1のソース電極層141および該第1のドレイン電極層151形成時の第3の酸化物半導体層133のオーバーエッチングが無い。したがって、チャネルが形成される第2の酸化物半導体層132をゲート絶縁膜160から十分離すことができ、界面からの不純物拡散の影響を抑える効果を大きくすることができる。

#### 【0155】

また、トランジスタ400の第1のソース電極層141および第1のドレイン電極層151の端部は、階段状に複数の段を設けた形状とすることが好ましい。このような複数の段を設けた形状とすることで、それらの上方に形成される膜の被覆性が向上し、トランジスタの電気特性や長期信頼性を向上させることができる。なお、図32(B)に示すトランジスタ402のように、第1のソース電極層141および第1のドレイン電極層151の端部は、階段状の段を設けない形状であってもよい。

40

#### 【0156】

低消費電力の半導体装置を形成するには、トランジスタのオフ電流、特にゲート電圧が0V時の電流(I<sub>cut</sub>ともいう)を低減させることが有効である。しかしながら、トランジスタを微細化するとしきい値電圧やS値(サブスレッショルド値)などのトランジスタの電気特性が悪化することが知られており、微細化と低消費電力化との両立が望まれていた。

50

## 【0157】

本発明の一態様のトランジスタでは、第1の酸化物半導体層131の一部である第1の領域の膜厚を $T_{S1}$ 、ゲート絶縁膜160の一部である第2の領域の膜厚を $T_{GI}$ としたとき、 $T_{S1} = T_{GI}$  ( $T_{S1}$ は $T_{GI}$ 以上)として形成する。このようにすることで、ゲート電極層170がゲート絶縁膜160を介して第2の酸化物半導体層132の側面を覆うようになる。

## 【0158】

第2の酸化物半導体層132はチャネルが形成される層であり、第2の酸化物半導体層132の側面にゲート電極層170から電界を印加しやすい構造にすることによって、第2の酸化物半導体層132に対して全体的に電界が印加されるようになり、トランジスタのしきい値電圧やS値を向上させることができる。当該構造を有するトランジスタでは、W長が短い場合に特に有効であるため、トランジスタを微細化しても $ICut$ を下げることができ、消費電力を低減させることができる。また、トランジスタのしきい値電圧が安定化することから、半導体装置の長期信頼性を向上させることができる。

10

## 【0159】

また、本発明の一態様のトランジスタでは、図21(A)のトランジスタの上面図に示すように、第1のソース電極層141、第2のソース電極層142、第1のドレイン電極層151、および第2のドレイン電極層152のチャネル幅方向の長さは、酸化物半導体層130のチャネル幅方向の長さよりも小さく、当該酸化物半導体層のチャネル長方向の端部を覆うように形成することが好ましい。このような構造とすることで、ゲート電極層170から第2の酸化物半導体層132の側面への電界印加に対する障害物が減少するため、上述した $T_{S1} = T_{GI}$ によるトランジスタのしきい値電圧やS値を向上させる効果を助長させることができる。

20

## 【0160】

以上が本発明の一態様におけるトランジスタである。当該トランジスタは電気特性が良好であり、長期信頼性の高い半導体装置を提供することができる。

## 【0161】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

## 【0162】

30

## (実施の形態5)

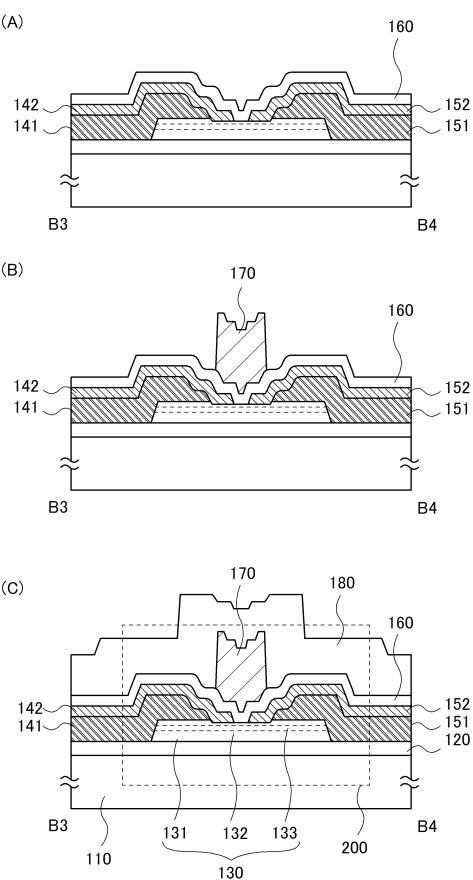

本実施の形態では、実施の形態1で説明した図7に示すトランジスタ200の作製方法について、図22乃至図24を用いて説明する。

## 【0163】

基板110には、ガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI (Silicon On Insulator) 基板などを用いることも可能であり、これらの基板上に半導体素子が設けられたものを用いてもよい。

## 【0164】

40

下地絶縁膜120は、プラズマCVD法またはスパッタ法等により、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニアム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、または上記材料を混合した膜を用いて形成することができる。また、上記材料の積層であってもよく、少なくとも酸化物半導体層130と接する上層は酸化物半導体層130への酸素の供給源となりえる酸素を含む材料で形成することができる。

## 【0165】

なお、基板110の表面が絶縁体であり、後に設ける酸化物半導体層130への不純物拡

50

散の影響が無い場合は、下地絶縁膜 120 を設けない構成とすることができる。

【0166】

次に、下地絶縁膜 120 上に第1の酸化物半導体層 131、第2の酸化物半導体層 132、第3の酸化物半導体層 133 をスパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜し、選択的にエッチングを行うことで酸化物半導体層 130 を形成する(図22(A)参照)。なお、エッチングの前に加熱工程を行ってもよい。

【0167】

第1の酸化物半導体層 131、第2の酸化物半導体層 132、および第3の酸化物半導体層 133 には、実施の形態1で説明した材料を用いることができる。例えば、第1の酸化物半導体層 131 に  $In : Ga : Zn = 1 : 3 : 2$  [原子数比] の  $In - Ga - Zn$  酸化物、第2の酸化物半導体層 132 に  $In : Ga : Zn = 1 : 1 : 1$  [原子数比] の  $In - Ga - Zn$  酸化物、第3の酸化物半導体層 133 に  $In : Ga : Zn = 1 : 3 : 2$  [原子数比] の  $In - Ga - Zn$  酸化物を用いることができる。

【0168】

また、第1の酸化物半導体層 131、第2の酸化物半導体層 132、および第3の酸化物半導体層 133 として用いることのできる酸化物半導体は、少なくともインジウム( $In$ )もしくは亜鉛( $Zn$ )を含むことが好ましい。または、 $In$ と $Zn$ の双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

【0169】

スタビライザーとしては、ガリウム( $Ga$ )、スズ( $Sn$ )、ハフニウム( $Hf$ )、アルミニウム( $Al$ )、またはジルコニウム( $Zr$ )等がある。また、他のスタビライザーとしては、ランタノイドである、ラントン( $La$ )、セリウム( $Ce$ )、プラセオジム( $Pr$ )、ネオジム( $Nd$ )、サマリウム( $Sm$ )、ユウロピウム( $Eu$ )、ガドリニウム( $Gd$ )、テルビウム( $Tb$ )、ジスプロシウム( $Dy$ )、ホルミウム( $Ho$ )、エルビウム( $Er$ )、ツリウム( $Tm$ )、イッテルビウム( $Yb$ )、ルテチウム( $Lu$ )等がある。

【0170】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、 $In - Zn$  酸化物、 $Sn - Zn$  酸化物、 $Al - Zn$  酸化物、 $Zn - Mg$  酸化物、 $Sn - Mg$  酸化物、 $In - Mg$  酸化物、 $In - Ga$  酸化物、 $In - Ga - Zn$  酸化物、 $In - Al - Zn$  酸化物、 $In - Sn - Zn$  酸化物、 $Sn - Ga - Zn$  酸化物、 $Al - Ga - Zn$  酸化物、 $Sn - Al - Zn$  酸化物、 $In - Hf - Zn$  酸化物、 $In - La - Zn$  酸化物、 $In - Ce - Zn$  酸化物、 $In - Pr - Zn$  酸化物、 $In - Nd - Zn$  酸化物、 $In - Sm - Zn$  酸化物、 $In - Eu - Zn$  酸化物、 $In - Gd - Zn$  酸化物、 $In - Tb - Zn$  酸化物、 $In - Dy - Zn$  酸化物、 $In - Ho - Zn$  酸化物、 $In - Er - Zn$  酸化物、 $In - Tm - Zn$  酸化物、 $In - Yb - Zn$  酸化物、 $In - Lu - Zn$  酸化物、 $In - Sn - Ga - Zn$  酸化物、 $In - Hf - Ga - Zn$  酸化物、 $In - Al - Ga - Zn$  酸化物、 $In - Sn - Al - Zn$  酸化物、 $In - Sn - Hf - Zn$  酸化物、 $In - Hf - Al - Zn$  酸化物を用いることができる。

【0171】

なお、ここで、例えば、 $In - Ga - Zn$  酸化物とは、 $In$ と $Ga$ と $Zn$ を主成分として有する酸化物という意味であり、 $In$ と $Ga$ と $Zn$ の比率は問わない。また、 $In$ と $Ga$ と $Zn$ 以外の金属元素が入っていてもよい。また、本明細書においては、 $In - Ga - Zn$  酸化物で構成した膜をIGZO膜とも呼ぶ。

【0172】

また、 $InMO_3 (ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない)で表記される材料を用いてもよい。なお、Mは、 $Ga$ 、 $Fe$ 、 $Mn$ および $Co$ から選ばれた一つの金属元素または複数の金属元素を示す。また、 $In_2SnO_5 (ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数)で表記される材料を用いてもよい。

10

20

30

40

50

## 【0173】

ただし、実施の形態1に詳細を記したように、第1の酸化物半導体層131および第3の酸化物半導体層133は、第2の酸化物半導体層132よりも電子親和力が大きくなるように材料を選択する。

## 【0174】

なお、酸化物半導体層の成膜には、スパッタ法を用いることが好ましい。スパッタ法としては、RFスパッタ法、DCスパッタ法、ACスパッタ法等を用いることができる。特に、成膜時に発生するゴミを低減でき、かつ膜厚分布も均一とすることからDCスパッタ法を用いることが好ましい。

## 【0175】

第1の酸化物半導体層131、第2の酸化物半導体層132、第3の酸化物半導体層133としてIn-Ga-Zn酸化物を用いる場合、In、Ga、Znの原子数比としては、例えば、In:Ga:Zn = 1:1:1、In:Ga:Zn = 2:2:1、In:Ga:Zn = 3:1:2、In:Ga:Zn = 1:3:2、In:Ga:Zn = 1:4:3、In:Ga:Zn = 1:5:4、In:Ga:Zn = 1:6:6、In:Ga:Zn = 2:1:3、In:Ga:Zn = 1:6:4、In:Ga:Zn = 1:9:6、In:Ga:Zn = 1:1:4、In:Ga:Zn = 1:1:2のいずれかの材料を用い、第1の酸化物半導体層131および第3の酸化物半導体層133の電子親和力が第2の酸化物半導体層132よりも大きくなるようにすればよい。

## 【0176】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn = a:b:c (a+b+c = 1)である酸化物の組成が、原子数比がIn:Ga:Zn = A:B:C (A+B+C = 1)の酸化物の組成の近傍であるとは、a、b、cが、(a-A)2+(b-B)2+(c-C)2 = r2を満たすことをいう。rとしては、例えば、0.05とすればよい。他の酸化物でも同様である。

## 【0177】

また、第2の酸化物半導体層132は、第1の酸化物半導体層131および第3の酸化物半導体層133よりもインジウムの含有量を多くするとよい。酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることにより、より多くのs軌道が重なるため、InがGaよりも多い組成となる酸化物はInがGaと同等または少ない組成となる酸化物と比較して移動度が高くなる。そのため、第2の酸化物半導体層132にインジウムの含有量が多い酸化物を用いることで、高い移動度のトランジスタを実現することができる。

## 【0178】

以下では、酸化物半導体膜の構造について説明する。

## 【0179】

なお、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

## 【0180】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

## 【0181】

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜などをいう。

## 【0182】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸

10

20

30

40

50

化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

【0183】

微結晶酸化物半導体膜は、例えば、1 nm以上10 nm未満の大きさの微結晶（ナノ結晶ともいう。）を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

【0184】

CAAC-OS膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が100 nm未満の立方体内に収まる大きさである。従って、CAAC-OS膜に含まれる結晶部は、一辺が10 nm未満、5 nm未満または3 nm未満の立方体内に収まる大きさの場合も含まれる。CAAC-OS膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、CAAC-OS膜について詳細な説明を行う。

【0185】

CAAC-OS膜を透過型電子顕微鏡（TEM: Transmission Electron Microscope）によって観察すると、結晶部同士の明確な境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、CAAC-OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

【0186】

CAAC-OS膜を、試料面と概略平行な方向からTEMによって観察（断面TEM観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OS膜の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、CAAC-OS膜の被形成面または上面と平行に配列する。

【0187】

一方、CAAC-OS膜を、試料面と概略垂直な方向からTEMによって観察（平面TEM観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

【0188】

断面TEM観察および平面TEM観察より、CAAC-OS膜の結晶部は配向性を有していることがわかる。

【0189】

CAAC-OS膜に対し、X線回折（XRD: X-Ray Diffraction）装置を用いて構造解析を行うと、例えば $InGaZnO_4$ の結晶を有するCAAC-OS膜のout-of-plane法による解析では、回折角（2θ）が31°近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$ の結晶の（009）面に帰属されることから、CAAC-OS膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

【0190】

一方、CAAC-OS膜に対し、c軸に概略垂直な方向からX線を入射させるin-plane法による解析では、2θが56°近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$ の結晶の（110）面に帰属される。 $InGaZnO_4$ の単結晶酸化物半導体膜であれば、2θを56°近傍に固定し、試料面の法線ベクトルを軸（c軸）として試料を回転させながら分析（スキャン）を行うと、（110）面と等価な結晶面に帰属されるピークが6本観察される。これに対し、CAAC-OS膜の場合は、2θを56°近傍に固定してスキャンした場合でも、明瞭なピークが現れない。

【0191】

以上のことから、CAAC-OS膜では、異なる結晶部間ではa軸およびb軸の配向は不規則であるが、c軸配向性を有し、かつc軸が被形成面または上面の法線ベクトルに平行

10

20

30

40

50

な方向を向いていることがわかる。従って、前述の断面TEM観察で確認された層状に配列した金属原子の各層は、結晶のa b面に平行な面である。

【0192】

なお、結晶部は、CAAC-OS膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、CAAC-OS膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、CAAC-OS膜の形状をエッチングなどによって変化させた場合、結晶のc軸がCAAC-OS膜の被形成面または上面の法線ベクトルと平行にならないこともある。

【0193】

また、CAAC-OS膜中の結晶化度が均一でなくてもよい。例えば、CAAC-OS膜の結晶部が、CAAC-OS膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、CAAC-OS膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

【0194】

なお、 $InGaZnO_4$ の結晶を有するCAAC-OS膜のout-of-plane法による解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、CAAC-OS膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAAC-OS膜は、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さないことが好ましい。

【0195】

CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

【0196】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、CAAC-OS膜のうち、二種以上を有する積層膜であってもよい。

【0197】

CAAC-OS膜は、例えば、多結晶である酸化物半導体スパッタ用ターゲットを用い、スパッタ法によって成膜することができる。

【0198】

また、CAAC-OS膜を成膜するために、以下の条件を適用することが好ましい。

【0199】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。

【0200】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタ粒子のマイグレーションが起こる。具体的には、基板加熱温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタ粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタ粒子の平らな面が基板に付着する。

【0201】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

【0202】

スパッタ用ターゲットとしては、例えば、In-Ga-Zn-O化合物ターゲットを用いることができる。In-Ga-Zn-O化合物ターゲットは、 $InO_x$ 粉末、 $GaO_y$ 粉末および $ZnO_z$ 粉末を所定のモル数比で混合し、加圧処理後、1000以上1500

10

20

30

40

50

以下の温度で加熱処理をすることで多結晶体とする。なお、X、YおよびZは任意の正数である。また、当該多結晶体の粒径は、例えば1 μm以下など、小さいほど好ましい。ここで、粉末の種類、およびその混合するモル数比は、作製するスパッタ用ターゲットによって適宜変更すればよい。

#### 【0203】

次に、第1の加熱処理を行うことが好ましい。第1の加熱処理は、250以上650以下、好ましくは300以上500以下の温度で、不活性ガス雰囲気、酸化性ガスを10 ppm以上含む雰囲気、または減圧状態で行えばよい。また、第1の加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10 ppm以上含む雰囲気で行ってもよい。第1の加熱処理によって、第2の酸化物半導体層132の結晶性を高め、さらに下地絶縁膜120、第1の酸化物半導体層131、および第3の酸化物半導体層133から水素や水などの不純物を除去することができる。なお、酸化物半導体層130を形成するエッティングの前に第1の加熱工程を行ってもよい。

#### 【0204】

なお、酸化物半導体層130を積層とする場合、下層に非晶質を形成すると、上層にはCACOS膜が形成しやすくなる。したがって、第1の酸化物半導体層131を非晶質とし、第2の酸化物半導体層132をCACOS膜としてもよい。

#### 【0205】

次に、酸化物半導体層130上に第1のソース電極層141および第1のドレイン電極層151となる第1の導電膜を形成する。第1の導電膜としては、Al、Cr、Cu、Ta、Ti、Mo、W、またはこれらを主成分とする合金材料を用いることができる。例えば、スパッタ法などにより100nmのチタン膜を形成する。

#### 【0206】

次に、第1の導電膜を酸化物半導体層130上で分断するようにエッティングし、第1のソース電極層141および第1のドレイン電極層151を形成する(図22(B)参照)。ここで、第1のソース電極層141および第1のドレイン電極層151の端部は図示するように階段状に形成することが好ましい。当該端部の加工は、アッシングによってレジストマスクを後退させる工程とエッティングの工程を交互に複数回行うことで形成することができる。

#### 【0207】

このとき、第1の導電膜のオーバーエッティングによって、図示したように酸化物半導体層130の一部がエッティングされた形状となる。ただし、第1の導電膜と酸化物半導体層130のエッティングの選択比が大きい場合は、酸化物半導体層130がほとんどエッティングされない形状となる。

#### 【0208】

次に、酸化物半導体層130、第1のソース電極層141および第1のドレイン電極層151上に、第2のソース電極層142および第2のドレイン電極層152となる第2の導電膜800(図22Cには示さず)を形成する。第2の導電膜800としては、窒化タンタル、窒化チタン、ルテニウム、またはこれらを主成分とする合金材料を用いることができる。例えば、スパッタ法などにより20nmの窒化タンタル膜を形成する。

#### 【0209】

次に、第2の導電膜800を酸化物半導体層130上で分断するようにエッティングし、第2のソース電極層142および第2のドレイン電極層152を形成する(図22(C)参照)。このとき、酸化物半導体層130の一部がエッティングされてもよい。

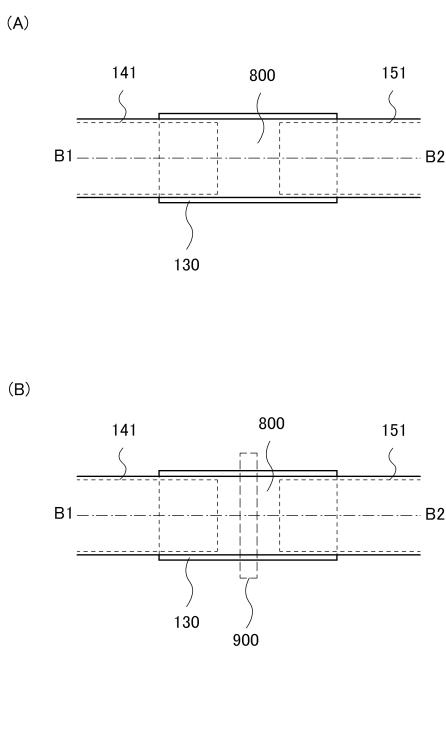

#### 【0210】

なお、チャネル長(第2のソース電極層142と第2のドレイン電極層152との間)が極短いトランジスタを形成する場合は、図24(A)に示す上面図のように、まず、第1のソース電極層141および第1のドレイン電極層151を覆うような形状に第2の導電膜800をエッティングする。

#### 【0211】

10

20

30

40

50

そして、図24(B)に示す第2の導電膜800を分断する領域900に対して、電子ビーム露光などの細線加工に適した方法を用いてレジストマスク加工を行い、エッチング工程によって領域900をエッチングし、第2のソース電極層142および第2のドレイン電極層152を形成する。なお、当該レジストマスクとしては、ポジ型レジストを用いれば、露光領域を最小限にすることことができ、スループットを向上させることができる。このような方法を用いれば、チャネル長を30nm以下とするトランジスタを形成することができる。

#### 【0212】

次に、第2の加熱処理を行うことが好ましい。第2の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第2の加熱処理により、酸化物半導体層130から、さらに水素や水などの不純物を除去することができる。

10

#### 【0213】

次に、酸化物半導体層130、第2のソース電極層142および第2のドレイン電極層152上にゲート絶縁膜160を形成する(図23(A)参照)。ゲート絶縁膜160には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどを用いることができる。なお、ゲート絶縁膜160は、上記材料の積層であってもよい。ゲート絶縁膜160は、スパッタ法、CVD法、MBE法、ALD法またはPLD法などを用いて形成することができる。

20

#### 【0214】

次に、ゲート絶縁膜160上に第3の導電膜を形成する。第3の導電膜としては、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Ta、W、またはこれらを主成分とする合金材料を用いることができる。第3の導電膜は、スパッタ法などにより形成することができる。そして、チャネル形成領域と重畳するようにエッチングし、ゲート電極層170を形成する(図23(B)参照)。

#### 【0215】

次に、ゲート絶縁膜160、ゲート電極層170上に酸化物絶縁層180を形成する(図23(C)参照)。酸化物絶縁層180は、下地絶縁膜120と同様の材料、方法を用いて形成することができる。酸化物絶縁層180としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタル、もしくは窒素を含む酸化物絶縁層を用いるとい。酸化物絶縁層180は、スパッタ法、CVD法、MBE法、ALD法またはPLD法を用いて形成することができ、酸化物半導体層130に対し酸素を供給できるよう過剰に酸素を含む膜とすることが好ましい。

30

#### 【0216】

また、酸化物絶縁層180にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて酸素を添加してもよい。酸素を添加することによって、酸化物絶縁層180から酸化物半導体層130への酸素の供給をさらに容易にすることができます。

40

#### 【0217】

次に、第3の加熱処理を行うことが好ましい。第3の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第3の加熱処理により、下地絶縁膜120、ゲート絶縁膜160、酸化物絶縁層180から過剰酸素が放出されやすくなり、酸化物半導体層130の酸素欠損を低減することができる。

#### 【0218】

以上の工程で、図7に示すトランジスタ200を作製することができる。

#### 【0219】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる

50

。

## 【0220】

(実施の形態6)

本実施の形態では、本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置（記憶装置）の一例を、図面を用いて説明する。

## 【0221】

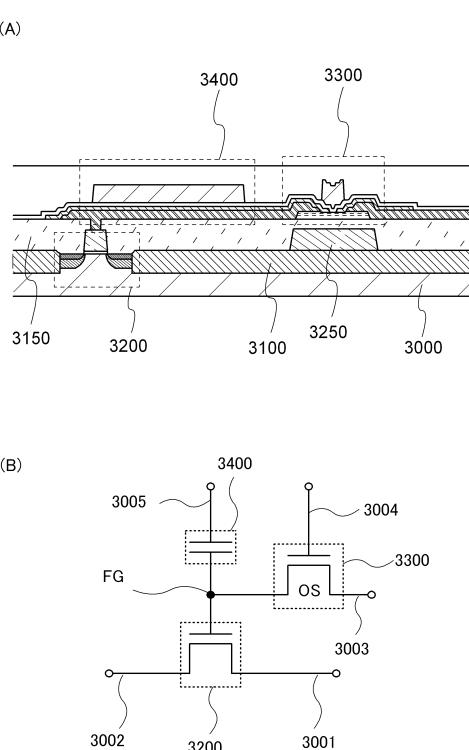

図25（A）に半導体装置の断面図、図25（B）に半導体装置の回路図をそれぞれ示す。

## 【0222】

10

図25（A）および図25（B）に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ3200を有し、上部に第2の半導体材料を用いたトランジスタ3300、および容量素子3400を有している。なお、トランジスタ3300としては、実施の形態1、3、4で説明したトランジスタを用いることができ、本実施の形態では、実施の形態1の図7に示すトランジスタ200を適用する例を示している。なお、図25（A）には、図7（A）に示す一点鎖線B5-B6で示された位置の断面が含まれる。

## 【0223】

また、容量素子3400は、一方の電極をトランジスタ3300のソース電極層またはドレイン電極層、他方の電極をトランジスタ3300のゲート電極層、誘電体をトランジスタ3300のゲート絶縁膜160と同じ材料を用いる構造とすることで、トランジスタ3300と同時に形成することができる。

20

## 【0224】

ここで、第1の半導体材料と第2の半導体材料は異なる禁制帯幅を持つ材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料（シリコンなど）とし、第2の半導体材料を実施の形態1で説明した酸化物半導体とができる。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、オフ電流が低い電気特性により長時間の電荷保持を可能とする。

## 【0225】

30

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、pチャネル型トランジスタを用いることができるはいうまでもない。また、情報を保持するために酸化物半導体を用いた実施の形態1、3、4に示すようなトランジスタを用いる他は、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

## 【0226】

図25（A）におけるトランジスタ3200は、半導体材料（例えば、結晶性シリコンなど）を含む基板3000に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、不純物領域に接する金属間化合物領域と、チャネル形成領域上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極層と、を有する。なお、図において、明示的にはソース電極層やドレイン電極層を有しない場合があるが、便宜上、このような状態を含めてトランジスタと呼ぶ場合がある。また、この場合、トランジスタの接続関係を説明するために、ソース領域やドレイン領域を含めてソース電極層やドレイン電極層と表現することがある。つまり、本明細書において、ソース電極層との記載には、ソース領域が含まれうる。

40

## 【0227】

基板3000上にはトランジスタ3200を囲むように素子分離絶縁層3100が設けられており、トランジスタ3200を覆うように絶縁層3150が設けられている。なお、素子分離絶縁層3100は、LOCOS（Local Oxidation of Silicon）や、STI（Shallow Trench Isolation）などの素子分離技術を用いて形成することができる。

50

## 【0228】

例えば、結晶性シリコン基板を用いた場合、トランジスタ3200は高速動作が可能となる。このため、当該トランジスタを読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。

## 【0229】

絶縁層3150上にはトランジスタ3300が設けられ、そのソース電極層またはドレイン電極層の一方は延在して、容量素子3400の一方の電極として作用する。また、当該電極は、トランジスタ3200のゲート電極層と電気的に接続される。

## 【0230】

図25(A)に示すトランジスタ3300は、酸化物半導体層にチャネルが形成されるトップゲート型トランジスタである。トランジスタ3300は、オフ電流が低いため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。 10

## 【0231】

また、トランジスタ3300と重畳するように絶縁層3150を介して電極3250が設けられている。当該電極に適切な電位を供給することで、トランジスタ3300のしきい値電圧を制御することができる。また、トランジスタ3300の長期信頼性を高めることができる。なお、電極3250を設けない構成とすることもできる。

## 【0232】

図25(A)に示すように、トランジスタ3200とトランジスタ3300または容量素子3400は重畳するように形成することができるため、その占有面積を低減することができる。したがって、半導体装置の集積度を高めることができる。 20

## 【0233】

図25(A)に対応する回路構成の一例を図25(B)に示す。

## 【0234】

図25(B)において、第1の配線3001はトランジスタ3200のソース電極層と電気的に接続され、第2の配線3002はトランジスタ3200のドレイン電極層と電気的に接続されている。また、第3の配線3003はトランジスタ3300のソース電極層またはドレイン電極層の一方と電気的に接続され、第4の配線3004はトランジスタ3300のゲート電極層と電気的に接続されている。そして、トランジスタ3200のゲート電極層、およびトランジスタ3300のソース電極層またはドレイン電極層の他方は、容量素子3400の電極の一方と電気的に接続され、第5の配線3005は容量素子3400の電極の他方と電気的に接続されている。 30

## 【0235】

図25(B)に示す半導体装置では、トランジスタ3200のゲート電極層の電位が保持可能という特徴を活かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

## 【0236】

情報の書き込みおよび保持について説明する。まず、第4の配線3004の電位を、トランジスタ3300がオン状態となる電位にして、トランジスタ3300をオン状態とする。これにより、第3の配線3003の電位が、トランジスタ3200のゲート電極層、および容量素子3400に与えられる。すなわち、トランジスタ3200のゲート電極層には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という)のいずれかが与えられるものとする。その後、第4の配線3004の電位を、トランジスタ3300がオフ状態となる電位にして、トランジスタ3300をオフ状態とすることにより、トランジスタ3200のゲート電極層に与えられた電荷が保持される(保持)。 40

## 【0237】

トランジスタ3300のオフ電流は極めて低いため、トランジスタ3200のゲート電極

50

層の電荷は長時間にわたって保持される。

【0238】

次に情報の読み出しについて説明する。第1の配線3001に所定の電位(定電位)を与えた状態で、第5の配線3005に適切な電位(読み出し電位)を与えると、トランジスタ3200のゲート電極層に保持された電荷量に応じて、第2の配線3002は異なる電位をとる。一般に、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲート電極層にHighレベル電荷が与えられている場合の見かけのしきい値電圧 $V_{th\_H}$ は、トランジスタ3200のゲート電極層にLowレベル電荷が与えられている場合の見かけのしきい値電圧 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ3200を「オン状態」とするために必要な第5の配線3005の電位をいうものとする。したがって、第5の配線3005の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ3200のゲート電極層に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0$ ( $> V_{th\_H}$ )となれば、トランジスタ3200は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0$ ( $< V_{th\_L}$ )となっても、トランジスタ3200は「オフ状態」のままである。このため、第2の配線3002の電位を判別することで、保持されている情報を読み出すことができる。10

【0239】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極層の状態にかかわらずトランジスタ3200が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を第5の配線3005に与えればよい。または、ゲート電極層の状態にかかわらずトランジスタ3200が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線3005に与えればよい。20

【0240】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて低いトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合(ただし、電位は固定されていることが望ましい)であっても、長期にわたって記憶内容を保持することが可能である。30

【0241】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁膜の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。40

【0242】

以上のように、微細化および高集積化を実現し、かつ高い電気的特性を付与された半導体装置を提供することができる。

【0243】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0244】

(実施の形態7)

本実施の形態では、本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について50

、実施の形態 6 に示した構成と異なる半導体装置の説明を行う。

【0245】

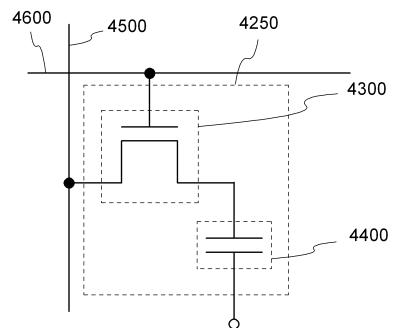

図 26 は、半導体装置の回路構成の一例である。当該半導体装置において、第 1 の配線 4500 とトランジスタ 4300 のソース電極層とは電気的に接続され、第 2 の配線 4600 とトランジスタ 4300 の第 1 のゲート電極層とは電気的に接続され、トランジスタ 4300 のドレイン電極層と容量素子 4400 の一方の端子とは電気的に接続されている。なお、当該半導体装置に含まれるトランジスタ 4300 としては、実施の形態 1、3、4 で説明したトランジスタを用いることができる。なお、第 1 の配線 4500 はビット線、第 2 の配線 4600 はワード線としての機能を有することができる。

【0246】

10

当該半導体装置（メモリセル 4250）は、図 25 に示すトランジスタ 3300 および容量素子 3400 と同様の接続形態とすることができます。したがって、容量素子 4400 は、実施の形態 6 で説明した容量素子 3400 と同様に、トランジスタ 4300 の作製工程にて同時に作製することができる。

【0247】

次に、図 26 に示す半導体装置（メモリセル 4250）に、情報の書き込みおよび保持を行う場合について説明する。

【0248】

20

まず、第 2 の配線 4600 にトランジスタ 4300 がオン状態となる電位を供給し、トランジスタ 4300 をオン状態とする。これにより、第 1 の配線 4500 の電位が、容量素子 4400 の第 1 の端子に与えられる（書き込み）。その後、第 2 の配線 4600 の電位を、トランジスタ 4300 がオフ状態となる電位として、トランジスタ 4300 をオフ状態とすることにより、容量素子 4400 の第 1 の端子の電位が保持される（保持）。

【0249】

酸化物半導体を用いたトランジスタ 4300 は、オフ電流が極めて低いという特徴を有している。このため、トランジスタ 4300 をオフ状態とすることで、容量素子 4400 の第 1 の端子の電位（あるいは、容量素子 4400 に蓄積された電荷）を極めて長時間にわたって保持することが可能である。

【0250】

30

次に、情報の読み出しについて説明する。トランジスタ 4300 がオン状態となると、浮遊状態である第 1 の配線 4500 と容量素子 4400 とが導通し、第 1 の配線 4500 と容量素子 4400 の間で電荷が再分配される。その結果、第 1 の配線 4500 の電位が変化する。第 1 の配線 4500 の電位の変化量は、容量素子 4400 の第 1 の端子の電位（あるいは容量素子 4400 に蓄積された電荷）によって、異なる値をとる。

【0251】

例えば、容量素子 4400 の第 1 の端子の電位を  $V$ 、容量素子 4400 の容量を  $C$ 、第 1 の配線 4500 が有する容量成分を  $C_B$ 、電荷が再分配される前の第 1 の配線 4500 の電位を  $V_B 0$  とすると、電荷が再分配された後の第 1 の配線 4500 の電位は、 $(C_B \times V_B 0 + C \times V) / (C_B + C)$  となる。したがって、メモリセル 4250 の状態として、容量素子 4400 の第 1 の端子の電位が  $V 1$  と  $V 0$  ( $V 1 > V 0$ ) の 2 状態をとるとすると、電位  $V 1$  を保持している場合の第 1 の配線 4500 の電位 ( $= (C_B \times V_B 0 + C \times V 1) / (C_B + C)$ ) は、電位  $V 0$  を保持している場合の第 1 の配線 4500 の電位 ( $= C_B \times V_B 0 + C \times V 0) / (C_B + C)$ ) よりも高くなることがわかる。

40

【0252】

そして、第 1 の配線 4500 の電位を所定の電位と比較することで、情報を読み出すことができる。

【0253】

このように、図 26 に示す半導体装置（メモリセル 4250）は、トランジスタ 4300 のオフ電流が極めて低いという特徴から、容量素子 4400 に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リ

50

フレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

【0254】

図26に示したメモリセル4250は、メモリセル4250を駆動させるための駆動回路が形成された基板を積層することが好ましい。メモリセル4250と駆動回路を積層することで、半導体装置の小型化を図ることができる。なお、積層するメモリセル4250および駆動回路の数は限定しない。

【0255】

駆動回路に含まれるトランジスタは、トランジスタ4300とは異なる半導体材料を用いることが好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることがより好ましい。このような半導体材料を用いたトランジスタは、酸化物半導体を用いたトランジスタよりも高速動作が可能であり、メモリセル4250の駆動回路の構成に用いることが適している。

【0256】

以上のように、微細化および高集積化を実現し、かつ高い電気的特性を付与された半導体装置を提供することができる。

【0257】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0258】

(実施の形態8)

本実施の形態では、少なくとも実施の形態1、3、4で説明したトランジスタを用いることができ、実施の形態6で説明した記憶装置を含むCPUについて説明する。

【0259】

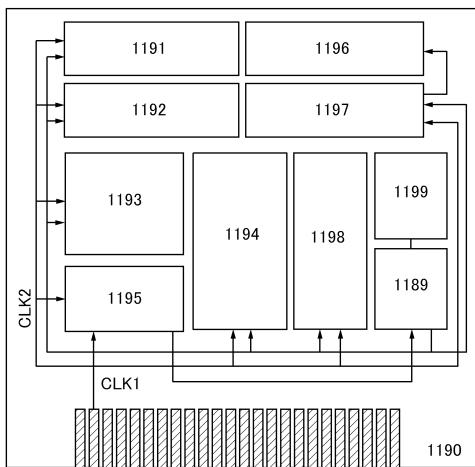

図27は、実施の形態1、3、4で説明したトランジスタを少なくとも一部に用いたCPUの一例の構成を示すブロック図である。

【0260】

図27に示すCPUは、基板1190上に、ALU1191(ALU: Arithmetic logic unit、演算回路)、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198、書き換え可能なROM1199、およびROMインターフェース1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。書き換え可能なROM1199およびROMインターフェース1189は、別チップに設けてよい。もちろん、図27に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。例えば、図27に示すCPUまたは演算回路を含む構成を一つのコアとし、当該コアを複数含み、それぞれのコアが並列で動作するような構成としてもよい。また、CPUが内部演算回路やデータバスで扱えるビット数は、例えば8ビット、16ビット、32ビット、64ビットなどとすることができます。

【0261】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0262】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制

10

20

30

40

50

御を行なう。具体的に A L U コントローラ 1192 は、A L U 1191 の動作を制御するための信号を生成する。また、インタラプトコントローラ 1194 は、C P U のプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ 1197 は、レジスタ 1196 のアドレスを生成し、C P U の状態に応じてレジスタ 1196 の読み出しや書き込みを行なう。

【 0 2 6 3 】

また、タイミングコントローラ 1195 は、A L U 1191、A L U コントローラ 1192、インストラクションデコーダ 1193、インタラプトコントローラ 1194、およびレジスタコントローラ 1197 の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ 1195 は、基準クロック信号 C L K 1 を元に、内部クロック信号 C L K 2 を生成する内部クロック生成部を備えており、内部クロック信号 C L K 2 を上記各種回路に供給する。

【 0 2 6 4 】

図 27 に示す C P U では、レジスタ 1196 に、メモリセルが設けられている。レジスタ 1196 のメモリセルとして、先の実施の形態に示したトランジスタを用いることができる。

【 0 2 6 5 】

図 27 に示す C P U において、レジスタコントローラ 1197 は、A L U 1191 からの指示に従い、レジスタ 1196 における保持動作の選択を行う。すなわち、レジスタ 1196 が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ 1196 内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ 1196 内のメモリセルへの電源電圧の供給を停止することができる。

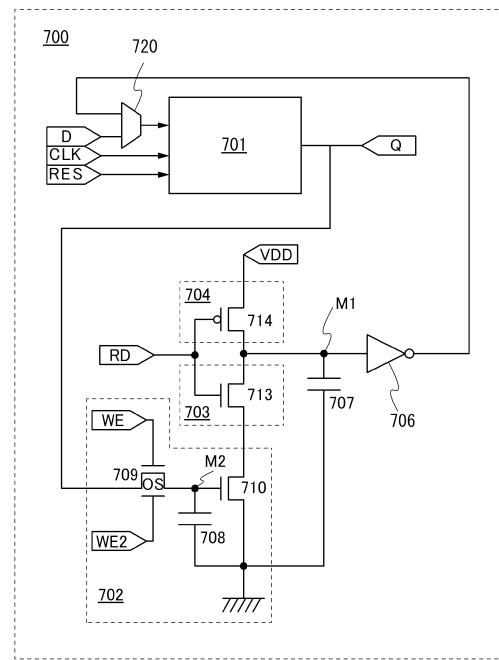

【 0 2 6 6 】

図 28 は、レジスタ 1196 として用いることのできる記憶素子の回路図の一例である。記憶素子 700 は、電源遮断で記憶データが揮発する回路 701 と、電源遮断で記憶データが揮発しない回路 702 と、スイッチ 703 と、スイッチ 704 と、論理素子 706 と、容量素子 707 と、選択機能を有する回路 720 と、を有する。回路 702 は、容量素子 708 と、トランジスタ 709 と、トランジスタ 710 と、を有する。なお、記憶素子 700 は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の素子をさらに有していても良い。

【 0 2 6 7 】

ここで、回路 702 には、実施の形態 6 で説明した記憶装置を用いることができる。記憶素子 700 への電源電圧の供給が停止した際、回路 702 のトランジスタ 709 の第 1 ゲートには接地電位 (0 V)、またはトランジスタ 709 がオフする電位が入力され続ける構成とする。例えば、トランジスタ 709 の第 1 ゲートが抵抗等の負荷を介して接地される構成とする。

【 0 2 6 8 】

スイッチ 703 は、一導電型（例えば、n チャネル型）のトランジスタ 713 を用いて構成され、スイッチ 704 は、一導電型とは逆の導電型（例えば、p チャネル型）のトランジスタ 714 を用いて構成した例を示す。ここで、スイッチ 703 の第 1 の端子はトランジスタ 713 のソースとドレインの一方に対応し、スイッチ 703 の第 2 の端子はトランジスタ 713 のソースとドレインの他方に対応し、スイッチ 703 はトランジスタ 713 のゲートに入力される制御信号 R D によって、第 1 の端子と第 2 の端子の間の導通または非導通（つまり、トランジスタ 713 のオン状態またはオフ状態）が選択される。スイッチ 704 の第 1 の端子はトランジスタ 714 のソースとドレインの一方に対応し、スイッチ 704 の第 2 の端子はトランジスタ 714 のソースとドレインの他方に対応し、スイッチ 704 はトランジスタ 714 のゲートに入力される制御信号 R D によって、第 1 の端子

10

20

30

40

50

と第2の端子の間の導通または非導通（つまり、トランジスタ714のオン状態またはオフ状態）が選択される。

【0269】

トランジスタ709のソースとドレインの一方は、容量素子708の一対の電極のうちの一方、およびトランジスタ710のゲートと電気的に接続される。ここで、接続部分をノードM2とする。トランジスタ710のソースとドレインの一方は、低電位電源を供給することのできる配線（例えばGND線）に電気的に接続され、他方は、スイッチ703の第1の端子（トランジスタ713のソースとドレインの一方）と電気的に接続される。スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）はスイッチ704の第1の端子（トランジスタ714のソースとドレインの一方）と電気的に接続される。スイッチ704の第2の端子（トランジスタ714のソースとドレインの他方）は電源電位VDDを供給することのできる配線と電気的に接続される。スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）と、スイッチ704の第1の端子（トランジスタ714のソースとドレインの一方）と、論理素子706の入力端子と、容量素子707の一対の電極のうちの一方と、は電気的に接続される。ここで、接続部分をノードM1とする。容量素子707の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND等）または高電源電位（VDD等）が入力される構成とすることができます。容量素子707の一対の電極のうちの他方は、低電位電源を供給することのできる配線（例えばGND線）と電気的に接続される。容量素子708の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位（GND等）または高電源電位（VDD等）が入力される構成とすることができます。容量素子708の一対の電極のうちの他方は、低電位電源を供給することのできる配線（例えばGND線）と電気的に接続される。

10

20

【0270】

なお、容量素子707および容量素子708は、トランジスタや配線の寄生容量等を積極的に利用することによって省略することも可能である。

【0271】

トランジスタ709の第1ゲート（第1のゲート電極層）には、制御信号WEが入力される。スイッチ703およびスイッチ704は、制御信号WEとは異なる制御信号RDによって第1の端子と第2の端子の間の導通状態または非導通状態を選択され、一方のスイッチの第1の端子と第2の端子の間が導通状態のとき他方のスイッチの第1の端子と第2の端子の間は非導通状態となる。

30

【0272】

トランジスタ709のソースとドレインの他方には、回路701に保持されたデータに対応する信号が入力される。図28では、回路701から出力された信号が、トランジスタ709のソースとドレインの他方に入力される例を示した。スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）から出力される信号は、論理素子706によってその論理値が反転された反転信号となり、回路720を介して回路701に入力される。

【0273】

40

なお、図28では、スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）から出力される信号は、論理素子706および回路720を介して回路701に入力する例を示したがこれに限定されない。スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）から出力される信号が、論理値を反転させられることなく、回路701に入力されてもよい。例えば、回路701内に、入力端子から入力された信号の論理値が反転した信号が保持されるノードが存在する場合に、スイッチ703の第2の端子（トランジスタ713のソースとドレインの他方）から出力される信号を当該ノードに入力することができる。

【0274】

図28におけるトランジスタ709は、実施の形態1、3、4で説明したトランジスタを

50

用いることができる。また、実施の形態 6 で説明したように第 2 ゲート（第 2 のゲート電極層）を有する構成とすることが好ましい。第 1 ゲートには制御信号 W E を入力し、第 2 ゲートには制御信号 W E 2 を入力することができる。制御信号 W E 2 は、一定の電位の信号とすればよい。当該一定の電位には、例えば、接地電位 G N D やトランジスタ 7 0 9 のソース電位よりも小さい電位などが選ばれる。制御信号 W E 2 は、トランジスタ 7 0 9 のしきい値電圧を制御するための電位信号であり、トランジスタ 7 0 9 の I c u t をより低減することができる。なお、トランジスタ 7 0 9 としては、第 2 ゲートを有さないトランジスタを用いることもできる。

#### 【 0 2 7 5 】

また、図 2 8 において、記憶素子 7 0 0 に用いられるトランジスタのうち、トランジスタ 7 0 9 以外のトランジスタは、酸化物半導体以外の半導体でなる層または基板 1 1 9 0 にチャネルが形成されるトランジスタとすることができる。例えば、シリコン層またはシリコン基板にチャネルが形成されるトランジスタとすることができる。また、記憶素子 7 0 0 に用いられるトランジスタ全てを、チャネルが酸化物半導体層で形成されるトランジスタとすることもできる。または、記憶素子 7 0 0 は、トランジスタ 7 0 9 以外にも、チャネルが酸化物半導体層で形成されるトランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板 1 1 9 0 にチャネルが形成されるトランジスタとすることもできる。

#### 【 0 2 7 6 】

図 2 8 における回路 7 0 1 には、例えばフリップフロップ回路を用いることができる。また、論理素子 7 0 6 としては、例えばインバータやクロックドインバータ等を用いることができる。

#### 【 0 2 7 7 】

以上が、記憶素子 7 0 0 の構成の説明である。次いで、記憶素子 7 0 0 の駆動方法について説明する。

#### 【 0 2 7 8 】

記憶素子 7 0 0 において、電源電圧の供給の後、データの保持時における消費電力を削減するために電源電圧の供給を停止し、再び電源電圧を供給する場合の駆動方法を図 2 9 のタイミングチャートを参照して説明する。図 2 9 のタイミングチャートにおいて、7 0 1 は回路 7 0 1 に保持されているデータを示し、W E は制御信号 W E の電位を示し、W E 2 は制御信号 W E 2 の電位を示し、R D は制御信号 R D の電位を示し、S E L は回路 7 2 0 における一経路の制御信号 S E L の電位を示し、V D D は電源電位 V D D を示す。また、M 1 はノード M 1 の電位を示し、M 2 はノード M 2 の電位を示す。なお、上記回路 7 2 0 における一経路とは、回路 7 0 2 の出力側と回路 7 0 1 の入力側を接続する経路である。

#### 【 0 2 7 9 】

なお、以下に示す駆動方法では、図 2 8 に示した構成において、スイッチ 7 0 3 を n チャネル型トランジスタとし、スイッチ 7 0 4 を p チャネル型トランジスタとして、制御信号 R D がハイレベル電位の場合に、スイッチ 7 0 3 の第 1 の端子と第 2 の端子の間が導通状態となり、且つスイッチ 7 0 4 の第 1 の端子と第 2 の端子の間が非導通状態となり、制御信号 R D がローレベル電位の場合に、スイッチ 7 0 3 の第 1 の端子と第 2 の端子の間が非導通状態となり、且つスイッチ 7 0 4 の第 1 の端子と第 2 の端子の間が導通状態となる例を示す。また、制御信号 S E L がハイレベル電位の場合に回路 7 2 0 の一経路における第 1 の端子と第 2 の端子の間が導通状態となり、制御信号 S E L がローレベル電位の場合に第 1 の端子と第 2 の端子の間が非導通状態となる例を示す。また、トランジスタ 7 0 9 を n チャネル型トランジスタとして、制御信号 W E がハイレベル電位の場合に、トランジスタ 7 0 9 がオン状態となり、制御信号 W E がローレベル電位の場合に、トランジスタ 7 0 9 がオフ状態となる例を示す。

#### 【 0 2 8 0 】

しかしながら、本発明の一態様の半導体装置の駆動方法はこれに限定されず、以下の説明における、スイッチ 7 0 3 、スイッチ 7 0 4 、回路 7 2 0 、トランジスタ 7 0 9 の状態が

10

20

30

40

50

同じとなるように、各制御信号の電位を定めることができる。

【0281】

まず、図29におけるT1の期間の動作について説明する。T1では、電源電圧VDDが記憶素子700に供給されている。記憶素子700へ電源電圧が供給されている間は、回路701がデータ（図29中、dataXと表記）を保持する。この際、制御信号SELをローレベル電位として、回路720の一経路における第1の端子と第2の端子の間は非導通状態とされる。なお、スイッチ703およびスイッチ704の第1の端子と第2の端子の間の状態（導通状態、非導通状態）はどちらの状態であってもよい。即ち、制御信号RDはハイレベル電位であってもローレベル電位であってもよい（図29中、Aと表記）。また、トランジスタ709の状態（オン状態、オフ状態）はどちらの状態であってもよい。即ち、制御信号WEはハイレベル電位であってもローレベル電位であってもよい（図29中、Aと表記）。T1において、ノードM1はどのような電位であってもよい（図29中、Aと表記）。T1において、ノードM2はどのような電位であってもよい（図29中、Aと表記）。T1の動作を通常動作と呼ぶ。また、制御信号WE2は期間を問わず定電位とし、例えば接地電位などのローレベル電位とする。

【0282】

次に、図29におけるT2の期間の動作について説明する。記憶素子700への電源電圧の供給の停止をする前に、制御信号WEをハイレベル電位として、トランジスタ709をオン状態とする。こうして、回路701に保持されたデータ（dataX）に対応する信号が、トランジスタ709を介してトランジスタ710のゲートに入力される。トランジスタ710のゲートに入力された信号は、容量素子708によって保持される。こうして、ノードM2の電位は、回路701に保持されたデータに対応する信号電位（図29中、VXと表記）となる。その後、制御信号WEをローレベル電位としてトランジスタ709をオフ状態とする。こうして、回路701に保持されたデータに対応する信号が回路702に保持される。T2の間も、制御信号SELによって、回路720の一経路における第1の端子と第2の端子の間は非導通状態とされる。スイッチ703およびスイッチ704の第1の端子と第2の端子の間の状態（導通状態、非導通状態）はどちらの状態であってもよい。即ち、制御信号RDはハイレベル電位であってもローレベル電位であってもよい（図29中、Aと表記）。T2において、ノードM1はどのような電位であってもよい（図29中、Aと表記）。T2の動作を電源電圧供給停止前の動作と呼ぶ。

【0283】

次に、図29におけるT3の期間の動作について説明する。電源電圧供給停止前の動作を行った後、T3のはじめに、記憶素子700への電源電圧の供給を停止する。電源電圧の供給が停止すると、回路701に保持されていたデータ（dataX）は消失する。しかし、記憶素子700への電源電圧の供給が停止した後においても、容量素子708によって回路701に保持されていたデータ（dataX）に対応する信号電位（VX）がノードM2に保持される。ここで、トランジスタ709は、チャネルが酸化物半導体層で形成され、リーコ電流（オフ電流）が極めて小さい、エンハンスマント型（ノーマリオフ型）のnチャネル型のトランジスタである。したがって、記憶素子700への電源電圧の供給が停止した際、トランジスタ709のゲートには接地電位（0V）またはトランジスタ709がオフとなる電位が入力され続ける構成であるため、記憶素子700への電源電圧の供給が停止した後も、トランジスタ709のオフ状態を維持することができ、容量素子708によって保持された電位（ノードM2の電位VX）を長期間保つことができる。こうして、記憶素子700は電源電圧の供給が停止した後も、データ（dataX）を保持する。T3は、記憶素子700への電源電圧の供給が停止している期間に対応する。

【0284】

次に、図29におけるT4の期間の動作について説明する。記憶素子700への電源電圧の供給を再開した後、制御信号RDをローレベル電位として、スイッチ704の第1の端子と第2の端子の間を導通状態とし、スイッチ703の第1の端子と第2の端子の間を非導通状態とする。この際、制御信号WEはローレベル電位であり、トランジスタ709は

オフ状態のままである。また、制御信号 S E L はローレベル電位であり、回路 720 の一経路における第1の端子と第2の端子の間は非導通状態である。こうして、スイッチ 703 の第2の端子およびスイッチ 704 の第1の端子に、電源電圧 V D D が入力される。したがって、スイッチ 703 の第2の端子およびスイッチ 704 の第1の端子の電位（ノード M1 の電位）を、一定の電位（ここでは V D D ）にすることができる。T4 の動作をプリチャージ動作と呼ぶ。なお、ノード M1 の電位は、容量素子 707 によって保持される。

#### 【 0285 】

上記プリチャージ動作の後、T5 の期間において、制御信号 R D をハイレベル電位とすることによって、スイッチ 703 の第1の端子と第2の端子の間を導通状態とし、スイッチ 704 の第1の端子と第2の端子の間を非導通状態とする。この際、制御信号 W E はローレベル電位のままであり、トランジスタ 709 はオフ状態のままである。また、制御信号 S E L はローレベル電位であり、回路 720 の一経路における第1の端子と第2の端子の間は非導通状態である。容量素子 708 に保持された信号（ノード M2 の電位 V X ）に応じて、トランジスタ 710 のオン状態またはオフ状態が選択され、スイッチ 703 の第2の端子およびスイッチ 704 の第1の端子の電位、即ちノード M1 の電位が定まる。トランジスタ 710 がオン状態の場合、ノード M1 には低電源電位（例えば、G N D ）が入力される。一方、トランジスタ 710 がオフ状態の場合には、ノード M1 の電位は、上記プリチャージ動作によって定められた一定の電位（例えば、V D D ）のまま維持される。こうして、トランジスタ 710 のオン状態またはオフ状態に対応して、ノード M1 の電位は V D D または G N D となる。例えば、回路 701 に保持されていた信号が「1」であり、ハイレベルの電位（V D D ）に対応する場合、ノード M1 の電位は、信号「0」に対応するローレベルの電位（G N D ）となる。一方、回路 701 に保持されていた信号が「0」であり、ローレベルの電位（G N D ）に対応する場合、ノード M1 の電位は、信号「1」に対応するハイレベルの電位（V D D ）となる。つまり、回路 701 に記憶されていた信号の反転信号がノード M1 に保持されることとなる。図 29において、この電位を V X b と表記する。つまり、T2において回路 701 から入力されたデータ（data X ）に対応する信号が、ノード M1 の電位（V X b ）に変換される。

#### 【 0286 】

その後、T6 の期間において、制御信号 S E L をハイレベル電位として、回路 720 の一経路における第1の端子と第2の端子の間を導通状態とする。この際、制御信号 R D はハイレベル電位のままである。また、制御信号 W E はローレベル電位のままであり、トランジスタ 709 はオフ状態のままである。すると、スイッチ 703 の第2の端子およびスイッチ 704 の第1の端子の電位（ノード M1 の電位（V X b ））に対応する信号を、論理素子 706 を介して反転信号とし、当該反転信号を回路 701 に入力することができる。こうして、回路 701 は、記憶素子 700 への電源電圧の供給停止前に保持していたデータ（data X ）を再び保持することができる。

#### 【 0287 】

また、ノード M1 の電位は、T4 におけるプリチャージ動作によって一定の電位（図 29 では、V D D ）にされた後、T5において、データ（data X ）に対応する電位 V X b となる。プリチャージ動作を行っているため、ノード M1 の電位が所定の電位 V X b に定まるまでの時間を短くすることができる。こうして、電源電圧供給再開後に、回路 701 が元のデータを保持しなおすまでの時間を短くすることができる。

#### 【 0288 】

以上が、記憶素子の駆動方法の説明である。

#### 【 0289 】

本発明の一態様における半導体装置の駆動方法では、記憶素子 700 に電源電圧が供給されない間は、回路 701 に記憶されていたデータを、回路 702 に設けられた容量素子 708 によって保持することができる。

#### 【 0290 】

10

20

30

40

50

また、酸化物半導体層にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体層にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、当該トランジスタをトランジスタ709として用いることによって、記憶素子700に電源電圧が供給されない間も容量素子708に保持された信号は長期間にわたり保たれる。こうして、記憶素子700は電源電圧の供給が停止した間も記憶内容（データ）を保持することが可能である。

#### 【0291】

また、スイッチ703およびスイッチ704を設けることによって、上述したプリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、回路701が元のデータを保持しなおすまでの時間を短くすることができる。

10

#### 【0292】

また、回路702において、容量素子708によって保持された信号はトランジスタ710のゲートに入力される。そのため、記憶素子700への電源電圧の供給が再開された後、容量素子708によって保持された信号を、トランジスタ710の状態（オン状態、またはオフ状態）に変換して、回路702から読み出すことができる。それ故、容量素子708に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。

#### 【0293】

このような記憶素子700を、プロセッサが有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、プロセッサ全体、もしくはプロセッサを構成する一つ、または複数の論理回路において、短い時間でも電源停止を行うことができるため、消費電力を抑えることができる。

20

#### 【0294】

ここでは、CPUを例に挙げて説明したが、DSP（Digital Signal Processor）、カスタムLSI、FPGA（Field Programmable Gate Array）等のLSIにも応用可能である。

#### 【0295】

30

#### （実施の形態9）

本実施の形態では、実施の形態1、3、4で説明したトランジスタ、実施の形態6、7で説明した記憶装置、または実施の形態8で説明したCPUを用いることのできる電子機器の例について説明する。

#### 【0296】

実施の形態1、3、4で説明したトランジスタ、実施の形態6、7で説明した記憶装置、または実施の形態8で説明したCPUは、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、テレビ、モニタ等の表示装置、照明装置、パーソナルコンピュータ、ワードプロセッサ、画像再生装置、ポータブルオーディオプレーヤ、ラジオ、テープレコーダ、ステレオ、電話、コードレス電話、携帯電話、自動車電話、トランシーバ、無線機、ゲーム機、電卓、携帯情報端末、電子手帳、電子書籍、電子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、電気シェーバ、ICチップ、電子レンジ等の高周波加熱装置、電気炊飯器、電気洗濯機、電気掃除機、エアコンディショナーなどの空調設備、食器洗い機、食器乾燥機、衣類乾燥機、布団乾燥機、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA保存用冷凍庫、放射線測定器、透析装置、X線診断装置等の医療機器、などが挙げられる。また、煙感知器、熱感知器、ガス警報装置、防犯警報装置などの警報装置も挙げられる。さらに、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレータ、産業用ロボット、電力貯蔵システム等の産業機器も挙げられる。また、燃料を用いたエンジンや、非水系二次電池からの電力を用いて電動機により推進する移動体なども、電子機器の範疇に含まれるものとする。上記移動体として、例えば、電気

40

50

自動車（EV）、内燃機関と電動機を併せ持ったハイブリッド車（HEV）、プラグインハイブリッド車（PHEV）、これらのタイヤ車輪を無限軌道に変えた装軌車両、電動アシスト自転車を含む原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、小型または大型船舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船が挙げられる。これらの電子機器の一部の具体例を図30に示す。

【0297】

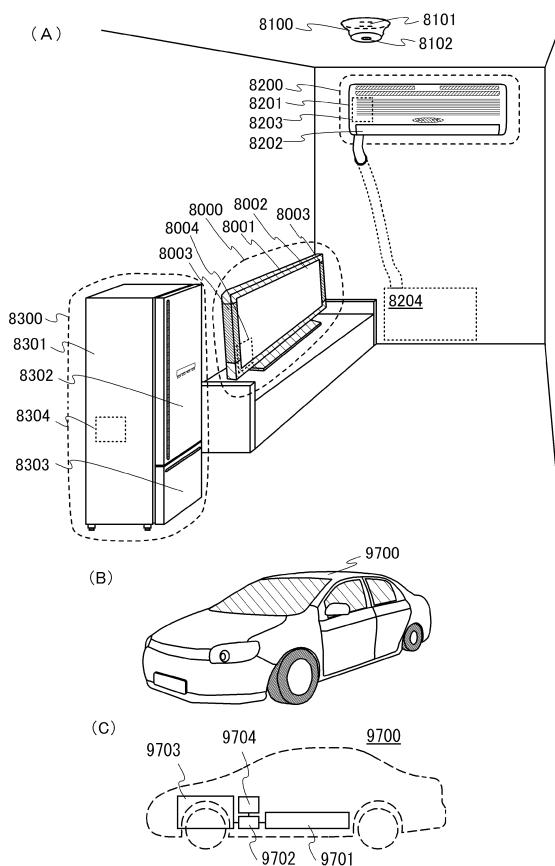

図30（A）に示す警報装置8100は、住宅用火災警報器であり、煙または熱の検出部8102と、マイクロコンピュータ8101を用いた電子機器の一例である。マイクロコンピュータ8101は、先の実施の形態に示したトランジスタ、記憶装置、またはCPUを含む。

10

【0298】

また、図30（A）に示す室内機8200および室外機8204を有するエアコンディショナーは、先の実施の形態に示したトランジスタ、記憶装置、またはCPUを含む電子機器の一例である。具体的に、室内機8200は、筐体8201、送風口8202、CPU8203等を有する。図30（A）においては、CPU8203が、室内機8200に設けられている場合を例示しているが、CPU8203は室外機8204に設けられていてもよい。または、室内機8200と室外機8204の両方に、CPU8203が設けられていてもよい。先の実施の形態に示したトランジスタをエアコンディショナーのCPUに用いることによって省電力化を図ることができる。

【0299】

20

また、図30（A）に示す電気冷凍冷蔵庫8300は、先の実施の形態に示したトランジスタ、記憶装置、またはCPUを含む電子機器の一例である。具体的に、電気冷凍冷蔵庫8300は、筐体8301、冷蔵室用扉8302、冷凍室用扉8303、CPU8304等を有する。図30（A）では、CPU8304が、筐体8301の内部に設けられている。先の実施の形態に示したトランジスタを電気冷凍冷蔵庫8300のCPU8304に用いることによって省電力化が図れる。

【0300】