(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5562172号

(P5562172)

(45) 発行日 平成26年7月30日(2014.7.30)

(24) 登録日 平成26年6月20日(2014.6.20)

|                   |                  |            |     |

|-------------------|------------------|------------|-----|

| (51) Int.Cl.      | F 1              |            |     |

| <b>H04N 5/378</b> | <b>(2011.01)</b> | H04N 5/335 | 780 |

| <b>H04N 5/374</b> | <b>(2011.01)</b> | H04N 5/335 | 740 |

| <b>G05F 1/10</b>  | <b>(2006.01)</b> | G05F 1/10  | R   |

請求項の数 12 (全 13 頁)

(21) 出願番号 特願2010-179744 (P2010-179744)

(22) 出願日 平成22年8月10日 (2010.8.10)

(65) 公開番号 特開2012-39526 (P2012-39526A)

(43) 公開日 平成24年2月23日 (2012.2.23)

審査請求日 平成25年8月9日 (2013.8.9)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 高木 誠

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 山崎 和男

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】定電流回路及びそれを用いた固体撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電流を出力する第1の電流源回路と、

第2の電流を出力する第2の電流源回路と、

前記第1の電流及び前記第2の電流の大きさを比較する電流比較回路と、

前記電流比較回路の比較の結果に応じて、前記第1の電流源回路が出力する前記第1の

電流の電流値を調整する電流調整部とを有し、

前記第2の電流源回路は、前記第2の電流を流す第1のMOSトランジスタと、定電圧を出力する基準電圧生成部と、

非反転入力端子が前記基準電圧生成部の出力端子に接続され、反転入力端子が前記第1

のMOSトランジスタのソースに接続され、出力端子が前記第1のMOSトランジスタの

ゲートに接続されるオペアンプとを有することを特徴とする定電流回路。

## 【請求項 2】

前記第1の電流源回路は、可変抵抗と、ダイオード接続されたMOSトランジスタとを

有し、前記可変抵抗及び前記MOSトランジスタは直列に接続され、

前記電流調整部は、前記可変抵抗の抵抗値を調整することを特徴とする請求項1記載の

定電流回路。

## 【請求項 3】

前記電流調整部は、前記電流比較回路の比較の結果が条件を満たすと、前記第1の電流

10

20

の電流値の調整を固定することを特徴とする請求項 1 又は 2 記載の定電流回路。

**【請求項 4】**

前記第 1 の電流源回路は、抵抗値の異なる複数の抵抗を有する可変抵抗を有し、

前記電流調整部は、前記複数の抵抗を選択的に接続するように制御することを特徴とする請求項 1 記載の定電流回路。

**【請求項 5】**

前記電流調整部は、前記可変抵抗を最大抵抗値に初期設定し、前記第 1 の電流が前記第 2 の電流より大きくなるまで前記可変抵抗を小さくし、前記第 1 の電流が前記第 2 の電流より大きくなつた場合には前記可変抵抗を固定することを特徴とする請求項 4 記載の定電流回路。

10

**【請求項 6】**

前記電流比較回路は、

前記第 1 の電流に応じた第 3 の電流を流す第 1 のカレントミラー回路と、

前記第 2 の電流に応じた第 4 の電流を流す第 2 のカレントミラー回路と、

前記第 3 の電流に応じた電圧及び前記第 4 の電流に応じた電圧を比較するコンパレータとを有することを特徴とする請求項 1 ~ 5 のいずれか 1 項に記載の定電流回路。

**【請求項 7】**

2 次元行列状に配置され、光電変換素子及びアンプを有する複数の画素と、

前記 2 次元行列状の各列の画素に共通に接続される複数の出力線と、

第 1 の電流を出力する第 1 の定電流回路と、

前記第 1 の電流に応じた電流を前記複数の出力線に流すためのカレントミラー回路とを有し、

前記カレントミラー回路により前記画素の前記アンプには前記出力線を介して前記第 1 の電流に応じた電流が供給され、

前記第 1 の定電流回路は、

前記第 1 の電流を出力する第 1 の電流源回路と、

第 2 の電流を出力する第 2 の電流源回路と、

前記第 1 の電流及び前記第 2 の電流の大きさを比較する電流比較回路と、

前記電流比較回路の比較の結果に応じて、前記第 1 の電流源回路が出力する前記第 1 の電流の電流値を調整する電流調整部とを有し、

30

前記第 2 の電流源回路は、

前記第 2 の電流を流す第 1 の M O S ドラゴンジスタと、

定電圧を出力する基準電圧生成部と、

非反転入力端子が前記基準電圧生成部の出力端子に接続され、反転入力端子が前記第 1 の M O S ドラゴンジスタのソースに接続され、出力端子が前記第 1 の M O S ドラゴンジスタのゲートに接続されるオペアンプとを有することを特徴とする固体撮像装置。

**【請求項 8】**

2 次元行列状に配置され、光電変換素子及びアンプを有する複数の画素と、

前記 2 次元行列状の各列の画素に共通に接続される複数の出力線と、

前記複数の出力線にそれぞれ接続される複数の信号処理回路と、

第 1 の電流を出力する第 1 の定電流回路と、

前記第 1 の定電流回路と同じ構成の第 2 の定電流回路と、

前記第 1 の電流に応じた電流を前記複数の出力線に流すためのカレントミラー回路とを有し、

前記カレントミラー回路により前記画素の前記アンプには前記出力線を介して前記第 1 の電流に応じた電流が供給され、

前記第 1 の定電流回路は、

前記第 1 の電流を出力する第 1 の電流源回路と、

第 2 の電流を出力する第 2 の電流源回路と、

前記第 1 の電流及び前記第 2 の電流の大きさを比較する電流比較回路と、

40

50

前記電流比較回路の比較の結果に応じて、前記第1の電流源回路が出力する前記第1の電流の電流値を調整する電流調整部とを有し、

前記第2の電流源回路は、

前記第2の電流を流す第1のMOSトランジスタと、

定電圧を出力する基準電圧生成部と、

非反転入力端子が前記基準電圧生成部の出力端子に接続され、反転入力端子が前記第1のMOSトランジスタのソースに接続され、出力端子が前記第1のMOSトランジスタのゲートに接続されるオペアンプとを有し、

前記複数の信号処理回路は、前記第2の定電流回路によりバイアスされることを特徴とする固体撮像装置。 10

#### 【請求項9】

前記第1の電流源回路は、可変抵抗と、ダイオード接続されたMOSトランジスタとを有し、前記可変抵抗及び前記MOSトランジスタは直列に接続され、

前記電流調整部は、前記可変抵抗の抵抗値を調整することを特徴とする請求項7又は8記載の固体撮像装置。 20

#### 【請求項10】

前記第1の定電流回路及び前記第2の定電流回路は、共通の1個の回路であることを特徴とする請求項8記載の固体撮像装置。

#### 【請求項11】

前記複数の信号処理回路は、それぞれアナログ/デジタル変換器を有することを特徴とする請求項8又は10記載の固体撮像装置。 20

#### 【請求項12】

前記電流比較回路は、

前記第1の電流に応じた第3の電流を流す第1のカレントミラー回路と、

前記第2の電流に応じた第4の電流を流す第2のカレントミラー回路と、

前記第3の電流に応じた電圧及び前記第4の電流に応じた電圧を比較するコンパレータとを有することを特徴とする請求項7~11のいずれか1項に記載の固体撮像装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、定電流回路及びそれを用いた固体撮像装置に関するものである。 30

##### 【背景技術】

##### 【0002】

固体撮像装置として、近年、CMOS型固体撮像装置（以下、CMOSセンサという）が広く利用されている。CMOSセンサは、光電変換部で発生した光電荷を一行毎にフローティングディフュージョンに転送し、各列毎のソースフォロアを用いて、垂直読み出し線から行単位で信号を同時に信号処理部に読み出す。各ソースフォロアを駆動する各列の定電流回路は、一般的に共通の電流源回路でバイアスされる。各定電流回路の出力電流に、相關のある電流ノイズ成分があると、各列共通の出力信号ノイズを発生し、画像では横スジ状のノイズとして認識される。したがって、CMOSセンサに用いられる定電流回路は低ノイズであることが必要で、共通の電流源回路で発生するノイズを低減する必要がある。 40

##### 【0003】

特許文献1においては、外来ノイズによる垂直読み出し線の電位変動を低減するために、定電流回路を構成するMOSトランジスタの共通ゲート線（図1、符号5）に容量（図1、符号7）を接続する技術が開示されている。この技術は、同時に共通の電流源回路（図1、符号4）で発生するノイズも低減する。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

【特許文献 1】特開 2007 - 129473 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献 1 で示されている共通の電流源回路は抵抗値やトランジスタの特性ばらつきと、使用する電源電圧に応じて、電流値が変動する。半導体プロセスで製造する CMOS センサでは、抵抗値に関して一般的に数 10 %、トランジスタの閾値では数 10 mV から 100 mV 程度のばらつきがある。また CMOS センサを使用する際に、製品毎に異なる電源電圧を設定する場合もあるため、定電流回路の電流値のばらつきは大きい。定電流回路の電流が大きくなると消費電流の増大を招く。逆に小さくなるとソースフォロアの駆動力を低下させ、画素の読み出しスピードを低下させる。10

【0006】

本発明の目的は、低ノイズで電流値の精度が高い定電流回路及びそれを用いた固体撮像装置を提供することである。

【課題を解決するための手段】

【0007】

本発明の定電流回路は、第 1 の電流を出力する第 1 の電流源回路と、第 2 の電流を出力する第 2 の電流源回路と、前記第 1 の電流及び前記第 2 の電流の大きさを比較する電流比較回路と、前記電流比較回路の比較の結果に応じて、前記第 1 の電流源回路が出力する前記第 1 の電流の電流値を調整する電流調整部とを有し、前記第 2 の電流源回路は、前記第 2 の電流を流す第 1 の MOS トランジスタと、定電圧を出力する基準電圧生成部と、非反転入力端子が前記基準電圧生成部の出力端子に接続され、反転入力端子が前記第 1 の MOS トランジスタのソースに接続され、出力端子が前記第 1 の MOS トランジスタのゲートに接続されるオペアンプとを有することを特徴とする。20

【発明の効果】

【0008】

ノイズが少なく、かつ電流値の精度を高くした定電流回路を実現することができる。また、定電流回路を固体撮像装置に用いることにより、横スジ状のノイズが少ない良好な画像を得ることができる。

【図面の簡単な説明】30

【0009】

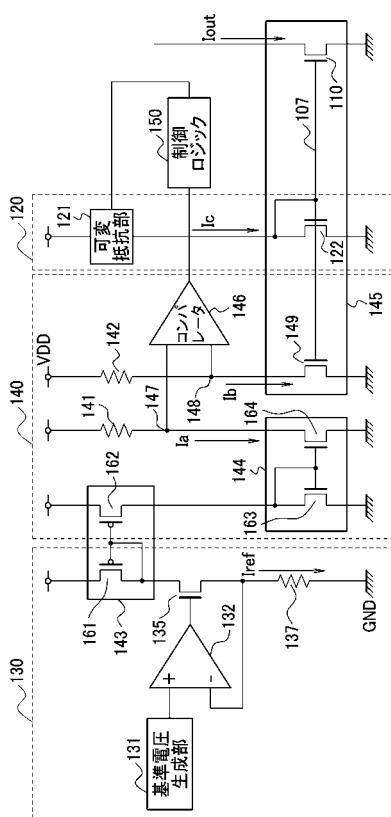

【図 1】本発明の第 1 の実施形態による定電流回路の構成例を示す図である。

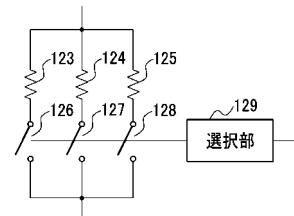

【図 2】第 1 の実施形態の可変抵抗部の構成の一例を示す図である。

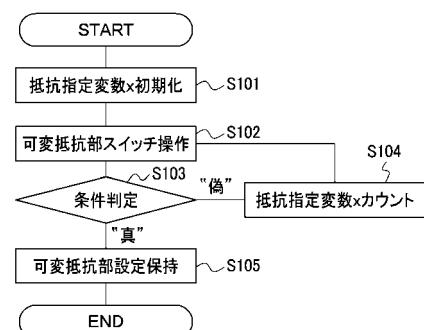

【図 3】第 1 の実施形態の定電流回路の処理を示すフローチャートである。

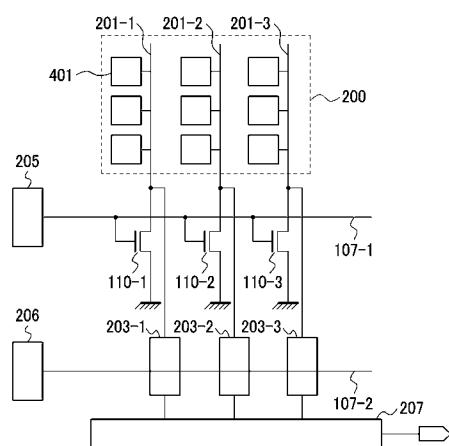

【図 4】本発明の第 2 の実施形態による固体撮像装置の構成例を示す図である。

【図 5】図 4 の列読み出し回路の構成例を示す図である。

【発明を実施するための形態】

【0010】

(第 1 の実施形態)

図 1 は、本発明の第 1 の実施形態による定電流回路の構成例を示す図である。定電流回路は、複数の出力を持つ定電流回路を構成する NMOS トランジスタ 110 (図 1 では 1 つのトランジスタのみ図示)、第 1 の電流源回路 120、第 2 の電流源回路 130、電流比較回路 140、及び制御ロジック回路 150 を有する。制御ロジック回路 150 は第 1 の電流源回路 120 の電流値を調整する電流調整部である。第 1 の電流源回路 120 は可変抵抗部 121、カレントミラー回路 145 を構成する NMOS トランジスタ 122 を有する。また、第 2 の電流源回路 130 は、基準電圧生成部 131、オペアンプ 132、PMOS トランジスタ 135、抵抗 137、カレントミラー回路 143 の PMOS トランジスタ 161 を有する。また、電流比較回路 140 は、抵抗 141、142、カレントミラー回路 144、カレントミラー回路 145 を構成する NMOS トランジスタ 149、コンパレータ 146 を有する。カレントミラー回路 145 では、第 1 の電流源回路 120 の N

4050

MOSトランジスタ122と電流比較回路140のNMOSトランジスタ149及び定電流回路を構成するNMOSトランジスタ110のゲートが電圧供給配線107に接続されている。カレントミラー回路143は、PMOSトランジスタ161及び162を有する。カレントミラー回路144は、NMOSトランジスタ163及び164を有する。

#### 【0011】

まず、第1の電流源回路120の構成を説明する。可変抵抗部121は、電源電圧VDDのノード及びNMOSトランジスタ122のドレイン間に接続される。NMOSトランジスタ122は、ドレインがゲートに接続され、ゲートが電圧供給配線107に接続され、ソースがグランド電位ノードに接続される。すなわち、NMOSトランジスタ122は、ダイオード接続され、可変抵抗部121と直列に接続される。

10

#### 【0012】

次に、第2の電流源回路130の構成を説明する。PMOSトランジスタ161は、ソースが電源電圧VDDのノードに接続され、ゲートがドレインに接続され、ドレインがNMOSトランジスタ135のドレインに接続される。抵抗137は、NMOSトランジスタ135のソース及びグランド電位ノード間に接続される。基準電圧生成部131は、一定電圧Vbを出力する。オペアンプ132は、非反転入力端子が基準電圧生成部131の出力端子に接続され、反転入力端子がNMOSトランジスタ135のソースに接続され、出力端子がNMOSトランジスタ135のゲートに接続される。

#### 【0013】

次に、電流比較回路140の構成を説明する。PMOSトランジスタ162は、ソースが電源電圧VDDのノードに接続され、ゲートがPMOSトランジスタ161のゲートに接続され、ドレインがNMOSトランジスタ163のドレインに接続される。NMOSトランジスタ163は、ドレインがゲートに接続され、ソースがグランド電位ノードに接続される。抵抗141は、電源電圧VDDのノード及びノード147間に接続される。NMOSトランジスタ164は、ドレインがノード147に接続され、ゲートがNMOSトランジスタ163のゲートに接続され、ソースがグランド電位ノードに接続される。抵抗142は、電源電圧VDDのノード及びノード148間に接続される。NMOSトランジスタ149は、ドレインがノード148に接続され、ゲートが電圧供給配線107に接続され、ソースがグランド電位ノードに接続される。コンパレータ146は、ノード147及び148の電圧を比較する。

20

#### 【0014】

制御ロジック回路150は、コンパレータ146の出力信号を基に可変抵抗部121の抵抗値を制御する。NMOSトランジスタ110は、ゲートが電圧供給配線107に接続され、ソースがグランド電位ノードに接続される。

30

#### 【0015】

以下の説明では、抵抗137に流れる電流をIrefと呼ぶ。また、抵抗141を流れる電流をIa、抵抗142を流れる電流をIb、NMOSトランジスタ122を流れる電流をIc、定電流回路を構成するNMOSトランジスタ110を流れる電流をIoutと呼ぶ。

#### 【0016】

第2の電流源回路130では、基準電圧生成部131からオペアンプ132の非反転入力端子に、製造上のばらつきや周囲環境の変化によらずほぼ一定の電圧Vbが供給される。オペアンプ132の反転入力端子に電圧帰還することにより、NMOSトランジスタ135のソース端子電圧もVbになる。この電圧Vbと抵抗137の抵抗値により、電流Irefが決まる。第2の電流源回路130は、基準電圧Vbに応じた第2の電流Irefを出力する。電流Irefはカレントミラー回路143、144により設定されたゲインで複製され、電流Iaが決定される。基準電圧生成部131は一例としてバンドギャップ回路で構成できる。抵抗137は精度が高く、温度変化が小さい抵抗を選択することで、環境及びばらつきによらずその値はほぼ一定である。電流Irefは、基準電圧生成部131で生成された電圧Vbと抵抗137の抵抗値で決定されるため精度は高い。

40

50

## 【0017】

しかし、基準電圧生成部131をバンドギャップ回路で構成した場合、回路を構成する素子数が多くなるため電圧V<sub>b</sub>のノイズは大きい。電流I<sub>ref</sub>には、電圧V<sub>b</sub>のノイズに加え、オペアンプ132、NMOSトランジスタ135、抵抗137で発生するノイズが二乗和平方根で積算されるため、そのノイズはさらに大きくなる。電流I<sub>ref</sub>をカレントミラー回路143、144にて設定されたゲインで複製した、抵抗141を流れる電流I<sub>a</sub>も電流I<sub>ref</sub>と同様に電流値の精度は高い。ノイズに関しては、カレントミラー回路143、144を構成するトランジスタで発生するノイズが加算されるため、さらに悪化する。このように第2の電流源回路130ではノイズは大きくても、そのノイズは電流よりも非常に小さいので問題にならない。電流値の精度が重要である。

10

## 【0018】

第1の電流源回路120では、可変抵抗部121の抵抗値とNMOSトランジスタ122のゲート・ソース間電圧、電源電圧VDDによって、電流I<sub>c</sub>の値が決まる。第1の電流源回路120は、第1の電流I<sub>c</sub>を出力する。可変抵抗部121は制御ロジック回路150の制御により抵抗値を変化させることで電流I<sub>c</sub>を調整する。本実施形態では抵抗137以外の構成要素は、半導体プロセスによって同一半導体基板上に形成される。そのため可変抵抗部121の抵抗値やNMOSトランジスタ122のゲート・ソース間電圧にも製造上のばらつきがある。その結果、電流I<sub>c</sub>の値もばらつく。一方で、第1の電流源回路120は抵抗部121及びNMOSトランジスタ122が1個ずつという単純な回路構成であり、ノイズ源となる素子数が少ないとから、電流I<sub>c</sub>のノイズを小さく抑えることが可能である。また、電流I<sub>c</sub>をカレントミラー回路145で設定されたゲインで複製した、抵抗142を流れる電流I<sub>b</sub>及び定電流回路出力電流I<sub>out</sub>も電流I<sub>c</sub>と同様の特性を持つ。

20

## 【0019】

電流比較回路140では、電流I<sub>a</sub>と電流I<sub>b</sub>を抵抗141、142により電圧に変換したノード147、148の電圧をコンパレータ146で比較する。電流比較回路140は、電流I<sub>b</sub>及びI<sub>a</sub>の大きさを比較、すなわち第1の電流I<sub>c</sub>及び第2の電流I<sub>ref</sub>の大きさを比較する。比較結果は制御ロジック回路150に出力される。制御ロジック回路150は、調整期間に電流比較回路140の比較の結果に応じて、電流I<sub>a</sub>と電流I<sub>b</sub>の差を小さくする様に第1の電流源回路120の可変抵抗部121の抵抗値を調整する。可変抵抗部121の抵抗値を調整することにより、第1の電流I<sub>c</sub>の電流値が調整される。調整期間以外は、調整期間に調整した値を保持する。定電流回路を構成するNMOSトランジスタ110は第1の電流源回路120でバイアスされ、ノイズが小さく精度が高い電流を出力する。なお、本実施形態では抵抗137に外部抵抗を使用する例を示したが、特性的に許容できるのであれば、同一基板上に形成される内部抵抗を用いてもよい。

30

## 【0020】

図2は、図1の可変抵抗部121の構成の一例を示す図である。以下では、図2を用いて、抵抗切り替えによる可変抵抗部121の動作を詳細に述べる。本実施形態の可変抵抗部121は、それぞれ抵抗値の異なる抵抗123、124、125及びスイッチ126、127、128、選択部129を有する。抵抗123及びスイッチ126、抵抗124及びスイッチ127、抵抗125及びスイッチ128はそれぞれを直列に接続したものを、並列に接続している。また、選択部129は制御ロジック回路150に接続され、制御ロジック回路150の出力に応じてスイッチ126、127、128の導通／非導通を切り替える。選択部129は、ロジック回路を組み合わせた選択回路で構成する。可変抵抗部121は、図2に示すものに限定されず、例えばMOSトランジスタの抵抗値を制御することで電流量を制御するもののように、連続的に変化させることができるのも含む。電源電圧VDDを3.3V、電流調整後の電流I<sub>c</sub>の目標値を100μA、可変抵抗部121を構成する抵抗値のばらつき量を±10%とする。また、NMOSトランジスタ122のゲート・ソース間電圧V<sub>gs</sub>を0.7V、電圧V<sub>gs</sub>のばらつきを±0.1Vとする。また、抵抗123、124、125の抵抗値の相対精度は十分高いとする。可変抵抗部1

40

50

21の抵抗値をRとしたとき、電流Icは以下で表される。

【0021】

$$I_c = (3.3 - V_{gs}) / R$$

【0022】

すなわち、電圧Vgsにばらつきが無い場合の抵抗値Rは26kとなる。抵抗値が10%大きくなり、電圧Vgsが0.8Vであった場合、電流Icを100μAとするために必要な抵抗値Rの設計値は22.7kとなる。また、抵抗値が10%小さくなり、電圧Vgsが0.6Vであった場合、電流Icを100μAとするために必要な抵抗値Rの設計値は30kとなる。抵抗値及び電圧Vgsのばらつきを抵抗の切り替えによって吸収し、電流Icを100μAに近い値に合わせこむために、起こりうる抵抗値の誤差率を最も小さくなるように3つの抵抗の値を次のように設定する。

10

【0023】

$$\text{抵抗 } 123 : 22.7 + (30 - 22.7) \times 5 / 6 = 28.8 \text{ k}$$

$$\text{抵抗 } 124 : 22.7 + (30 - 22.7) \times 3 / 6 = 26.4 \text{ k}$$

$$\text{抵抗 } 125 : 22.7 + (30 - 22.7) \times 1 / 6 = 23.9 \text{ k}$$

【0024】

抵抗123、124、125の値を上記のように設定し、電流Icが最も100μAに近くなるように抵抗を選択することで、電流Icの最大誤差を、調整を行わない場合の14%程度から5%程度に低減できる。本実施形態では可変抵抗部121を構成する抵抗の数を3つとしたが、抵抗の数を増加させることにより、電流Icを更に精度良く調整することが可能となる。また、抵抗を切り替えるのではなく、直列に接続した抵抗の一部をスイッチでショートしたり、抵抗をスイッチで並列に接続することで、可変抵抗部121の抵抗値を調整することも可能である。可変抵抗部121の構成は抵抗とスイッチを用いる方法に限らない。例えば可変抵抗部121をMOSトランジスタで構成し、選択部129の出力をアナログ電圧として、ゲート電圧を操作して電流量を調整するような構成も考えられる。さらには電流Icの値を調整する方法として、抵抗部を固定抵抗値とし、抵抗部に与える電圧を電源電圧VDDとせず、可変電圧を印加することで調整することも可能である。

20

【0025】

図3は、定電流回路の電流値合わせこみのシーケンスに係るフローチャートである。なお、本実施形態では可変抵抗部121が電流調整のための抵抗をn本有する場合を例として説明を行う。

30

【0026】

ステップS101では、制御ロジック回路150は、電流Icの調整を開始するにあたり、可変抵抗部121で選択する抵抗を指定する抵抗指定変数xの値を0に初期化する。

【0027】

次に、ステップS102では、選択部129は、制御ロジック回路150の出力に基づき、可変抵抗部121のスイッチの一つを、導通状態にする。抵抗指定変数xの値が0の時、抵抗値が最も大きい抵抗を初期の抵抗として導通状態にする。この結果、電流Icの初期値は電源電圧VDDと、最も大きい抵抗値と、NMOSトランジスタ122のゲート・ソース間電圧Vgsに応じた電流となる。コンパレータ146はノード147とノード148の電圧を比較し、その大小関係を制御ロジック回路150に対して出力する。

40

【0028】

次に、ステップS103では、制御ロジック回路150は、コンパレータ146の出力及び抵抗指定変数xの値を検証し、次の2つの条件(1)及び(2)のどちらかを満たすかどうかの判定を行う。ここで、電圧V(147)はノード147の電圧、電圧V(148)はノード148の電圧である。

【0029】

$$(1) V(148) < V(147)$$

$$(2) x = n - 1$$

## 【0030】

上記のように、可変抵抗部121の初期値は最大抵抗値である。その時、電流Icは最小になり、電圧供給配線107の電圧も最低になる。その結果、カレントミラー回路145により電流Ibも最小になり、ノード148の電圧V(148)も最高になる。初期時には、多くの場合、ノード148の電圧V(148)はノード147の電圧V(147)より高くなり、上記の条件(1)を満たさない。また、初期時には、抵抗指定変数xの値が0であるので、上記の条件(2)も満たさない。ステップS103において、判定結果が“偽”的な場合、ステップS104に遷移し、“真”的な場合、ステップS105に遷移する。条件(1)及び(2)の両方を満たさない場合には、ステップS104に遷移する。

## 【0031】

ステップS104では、制御ロジック回路150は抵抗指定変数xの値を1つ増加させ、次のステップS102で可変抵抗部121の抵抗の値が1段階小さな値の抵抗を導通状態にする。可変抵抗121の値が小さくなるので、電流Icが増加し、電圧供給配線107の電圧も増加になる。その結果、カレントミラー回路145により電流Ibも増加する。ステップS102～S104のループ処理により、可変抵抗121が徐々に小さくなっている、ノード148の電圧V(148)は徐々に低くなっていく。やがて、ノード148の電圧V(148)はノード147の電圧V(147)より低くなり、上記の条件(1)を満たし、ステップS105へ進む。また、条件(2)を満たす場合には、これ以上、可変抵抗121の抵抗値を小さくすることができないので、ステップS105に遷移する。

10

## 【0032】

ステップS105では、制御ロジック回路150は、抵抗指定変数xの値を保持し、電流Icの合わせこみシーケンスを終了する。すなわち、制御ロジック回路150は、電流比較回路140の比較の結果が上記の条件を満たすと、可変抵抗部121の抵抗値(第1の電流Icの電流値)の調整を固定する。

## 【0033】

以上のシーケンスを行うことにより、製造上のはらつきを受けにくい第2の電流源回路130の電流値Irefに対して、第1の電流源回路120の電流値Icを近づけることが可能となる。制御ロジック回路150が可変抵抗部121の設定を保持する構成により、第1の電流源回路120は、第2の電流源回路130のノイズの影響を受けない。定電流回路を構成するNMOSトランジスタ110は第1の電流源回路120によりバイアスされることから、電流Ioutも電流値の精度が高く、ノイズが小さい。

20

## 【0034】

なお、本実施形態では抵抗値の高い抵抗から、抵抗値の低い抵抗へと切り替えることとしたが、これに限るものではなく、電流Icを設定目標に近い電流値に調整出来ればよい。その場合、電流値合わせこみシーケンスに係るフロー及び各ステップの動作が実施形態と異なってもよい。なお、電流値の合わせこみのシーケンスは、電源投入時のような固体撮像装置の動作開始時の動作に組み込んで実行するか、一定時間毎に実行するかなど、使用上の必要にあわせて実行すればよい。また、定電流回路を組み込む固体撮像装置の動作モードの変更に合わせ、設定目標の電流値を変更して、電流値合わせこみシーケンスを実行することも可能である。

30

## 【0035】

以上説明したように、定電流回路は、ノイズは大きいが電流値の精度に優れる第2の電流源回路130に対して、ノイズは小さいが電流値の精度に劣る第1の電流源回路120の電流値を合わせこみ、可変抵抗部121の設定を保持する構成となっている。定電流回路を構成するNMOSトランジスタ110の電流IoutはNMOSトランジスタ122の電流Icをカレントミラー回路145で設定したゲインで複製して得られることから、電流Ioutについても電流値の精度が高くノイズが小さい。以上の構成により、定電流回路では、低いノイズ特性と高い電流値精度を有する定電流回路を実現することが可能となる。

40

50

## 【0036】

(第2の実施形態)

図4は、本発明の第2の実施形態による固体撮像装置の構成例を示す図である。本実施形態の固体撮像装置は、第1の実施形態の定電流回路を用いる。200は画素アレイ(例えば3画素×3画素)を示す。画素アレイ200は、2次元行列状に配置された複数の画素401を有する。画素401は、光電変換により画素信号を生成する光電変換素子と、生成された画素信号を増幅するソースフォローアンプとを有する。複数の垂直出力線201-1～201-3は、2次元行列状の各列の画素401に共通に接続される。選択された行の画素401は、垂直出力線201-1～201-3に画素信号を行単位で出力する。垂直出力線201-1～201-3には、それぞれ定電流回路を構成するNMOSトランジスタ110-1～110-3が接続される。NMOSトランジスタ110-1～110-3は、それぞれ図1のNMOSトランジスタ110に対応し、垂直出力線201-1～201-3及びグランド電位ノード間に接続される。定電流回路205及び206は、図1の定電流回路のうちのNMOSトランジスタ110及び電圧供給配線107以外の部分であり、同じ構成を有する。電圧供給配線107-1及び107-2は、図1の電圧供給配線107に対応する。NMOSトランジスタ110-1～110-3のゲートは、電圧供給配線107-1を介して、第1の定電流回路205に接続される。NMOSトランジスタ110-1～110-3は、図1に示すように、第1の電流源回路120の第1の電流 $I_c$ に応じた電流 $I_{out}$ を複数の垂直出力線201-1～201-3に流すためのカレントミラー回路145を構成する。

## 【0037】

列読み出し回路(信号処理回路)203-1～203-3は、それぞれ、垂直出力線201-1～201-3及び水平読み出し回路207間に接続される。第2の定電流回路206は、電圧供給配線107-2を介して、列読み出し回路203-1～203-3に接続される。水平読み出し回路207は、列読み出し回路203にて信号処理された各画素401の出力信号を行毎に転送し、固体撮像装置外部へ出力する。

## 【0038】

本実施形態の構成では、画素401から出力された信号は列読み出し回路203-1～203-3でサンプルホールドされ、水平読み出し回路207を経て固体撮像装置外部に出力される。定電流回路を構成するNMOSトランジスタ110-1～110-3の電流は画素401の出力信号レベルに影響を与えるため、本発明の定電流回路を用いることにより、定電流回路で発生するノイズに起因する画素401の出力信号の時間的な変動を低減できる。この結果、画像に発生する横スジ状のノイズを低減することができる。また、定電流回路206では、各列の読み出し回路203-1～203-3にバイアス電圧を供給し、各列の読み出し回路203-1～203-3の動作点を保ち、読み出し動作を安定させることができる。

## 【0039】

本実施形態で示した列読み出し回路203-1～203-3をアナログ信号処理回路で構成した場合、水平読み出し回路207はアナログ信号の転送回路となる。また、列読み出し回路203-1～203-3がアナログ/デジタル変換器(A/D変換器)を備える場合、水平読み出し回路207はデジタル信号の転送回路となる。また、本実施形態は、定電流回路206を用いてバイアス電圧を供給する構成としたが、実施形態はこれに限らない。定電流回路が列読み出し回路203-1～203-3に電流そのものを供給する構成としてもよい。また、定電流回路で生成される電流を用いて所望の電圧を規定し、列読み出し回路203-1～203-3の動作点を定めるバイアス電圧として供給する構成としても良い。定電流回路を組み込んで固体撮像装置を構成することで、列読み出し回路203-1～203-3のノイズを低減し、画像に発生する横スジ状のノイズを低減することが可能になる。

## 【0040】

以上の説明は、2個の定電流回路205及び206を持つ例を示したが、共通の1個の

10

20

30

40

50

定電流回路が電圧供給配線 107-1 及び 107-2 を共通にバイアスすることも可能である。定電流回路を固体撮像装置に用いる場合、定電流回路の電流値の合わせこみシーケンスを必要とする動作モード変更の例として、動画モード / 静止画モードの変更、アンプゲインの変更などが挙げられる。また、少なくとも 1 フレームを撮像中に、定電流回路の制御ロジック回路 150 が設定を保持し続けることで、1 フレーム内で取得する出力レベルを一定に保つことができる。このように固体撮像装置の動作時に必要に応じて電流調整のシーケンスを実行することにより、動作モードの変更や周囲環境によらず電流源の出力を安定させるとともに、横スジ状のノイズの発生を低減できる。

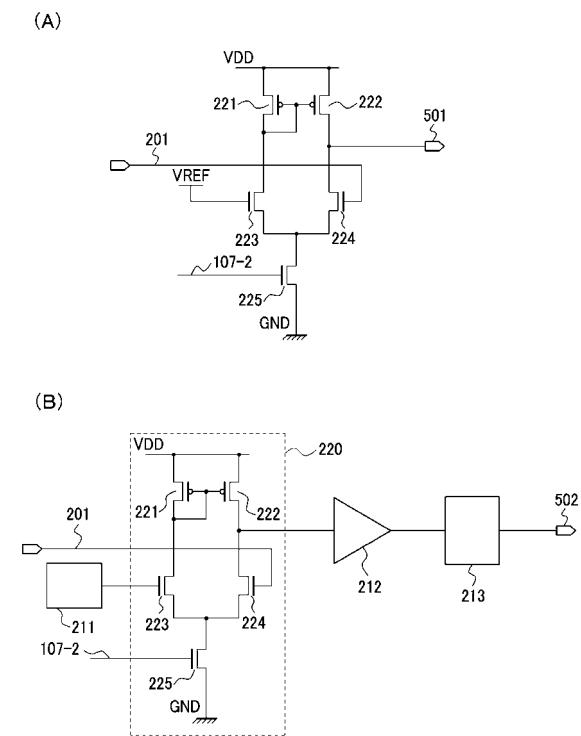

#### 【0041】

次に、図 4 の列読み出し回路 203-1 ~ 203-3 の構成例を図 5 (A) 及び (B) を用いて説明する。図 5 (A) は、アナログ処理回路の差動増幅器を有する列読み出し回路 203-1 ~ 203-3 の構成例を示す図である。差動増幅器では、垂直出力線 201 の信号電圧と所定の電圧 VREF との差電圧を増幅し、出力端子 501 から出力する。NMOS トランジスタ 223 及び 224 は入力 MOS トランジスタとして機能し、PMOS トランジスタ 221 及び 222 は能動負荷として機能する。電流源トランジスタ 225 のゲートには、電圧供給配線 107-2 が接続される。この差動増幅器は、電流源 225 で決まる電流で動作しており、そのために必要なバイアス電圧を電圧供給配線 107 を通じて外部から供給する。定電圧回路 206 によりバイアス電圧を低ノイズにすることにより、電流源 225 の電流の電流変動を小さくすることができるので、差動増幅回路の増幅率が安定する。

10

#### 【0042】

図 5 (B) は、ランプ電圧比較型 A/D 変換器を利用した列読み出し回路 203-1 ~ 203-3 の構成例を示す図である。ランプ電圧比較型 A/D 変換器は、参照電圧源 211、コンパレータ 220、バッファ 212、及びカウンタ 213 を有し、アナログ信号をデジタル信号に変換する。参照電圧源 211 は、一定周期のランプ波形の電圧信号を生成する。コンパレータ 220 は、図 5 (A) に示した差動増幅器と同一の構成である。垂直出力線 201 から出力された電圧信号は、コンパレータ 220 に入力され、参照電圧源 211 の電圧と比較される。その比較結果はコンパレータ 220 の出力として、バッファ回路 212 を経てカウンタ 213 へ出力される。カウンタ 213 は、参照電圧源 211 のランプ信号の周期毎に、コンパレータ 220 の出力が反転するまでの時間を基準クロック (不図示) のパルス数で計数し、これをデジタル変換結果として出力端子 502 から出力する。ここで、コンパレータ 220 は、電流源 225 で決まる電流で動作しており、そのために必要なバイアス電圧を電圧供給配線 107-2 を通じて回路の外部から供給している。電流源 225 の電流量は、コンパレータ 220 が比較を行い、コンパレータ 220 の出力を得るまでの時間にも影響する。従来の A/D 変換器では電流源 225 の変動によりコンパレータ 220 の出力を得るまでの時間がばらついていたので、A/D 変換結果もばらついていた。定電圧回路 206 によりバイアス電圧を低ノイズにすることにより、電流源 225 の電流の変動が小さくなり安定した A/D 変換結果を得ることが可能になった。本実施形態では A/D 変換器の一例としてランプ電圧比較型 A/D 変換器をあげたが、本発明の実施形態はこれに限らない。

20

30

40

#### 【0043】

以上のように、第 1 の電流源回路 120 は、ノイズは少ないが、精度が低い電流  $I_c$  を生成することができる。第 2 の電流源回路 130 は、精度は高いが、ノイズが多い電流  $I_{ref}$  を生成することができる。第 1 及び第 2 の実施形態の定電流回路は、第 1 の電流源回路 120 及び第 2 の電流源回路 130 を組み合わせることにより、ノイズが少なくかつ精度の高い電流を生成することができる。また、定電流回路を固体撮像装置に用いることにより、横スジ状のノイズが少ない良好な画像を得ることができる。

#### 【0044】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものであ

50

る。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

### 【符号の説明】

【 0 0 4 5 】

120 第1の電流源回路、130 第2の電流源回路、140 電流比較回路、150

制御ロジック回路

【 义 1 】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開2006-018663(JP,A)

特開2001-211380(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |           |

|--------|-----------|

| G 05 F | 1 / 1 0   |

| H 04 N | 5 / 3 7 8 |

| H 04 N | 5 / 3 7 4 |