(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4679058号

(P4679058)

(45) 発行日 平成23年4月27日(2011.4.27)

(24) 登録日 平成23年2月10日(2011.2.10)

(51) Int.Cl.

F 1

H01L 21/205 (2006.01)

H01L 21/205

H01L 29/786 (2006.01)

H01L 29/78 618 A

H01L 21/336 (2006.01)

H01L 29/78 616 K

請求項の数 2 (全 32 頁)

(21) 出願番号

特願2004-9820 (P2004-9820)

(22) 出願日

平成16年1月16日 (2004.1.16)

(65) 公開番号

特開2005-203638 (P2005-203638A)

(43) 公開日

平成17年7月28日 (2005.7.28)

審査請求日

平成19年1月12日 (2007.1.12)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 古野 誠

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 掛端 哲弥

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 神保 安弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

(57) 【特許請求の範囲】

## 【請求項 1】

金属配線上に形成された絶縁膜と、

前記絶縁膜上に形成された結晶構造を含む半導体層と、

前記半導体層上に形成された導電層と、

前記半導体層と前記導電層との間に形成され、かつ前記半導体層のエッジをカバーする

絶縁材料または導電材料からなる層と、を有する構造を形成し、

前記導電層上に導電性部材からなる凸状部を形成し、

前記導電層及び前記凸状部上に層間絶縁膜を形成し、

前記凸状部上の前記層間絶縁膜を除去して前記凸状部を露出させ、

前記層間絶縁膜上に、前記露出した凸状部と電気的に接続する電極を形成し、

前記半導体層は、成膜室の圧力を0.133Pa～133Pa、成膜温度を80～300、高周波電源の電源周波数を10MHz～500MHz、とした状態において、前記成膜室に珪化物気体とフッ素或いはフッ化ハロゲンガスとを含むガスを原料ガスとして導入し、プラズマを発生させることにより形成することを特徴とする半導体装置の作製方法。

## 【請求項 2】

請求項1において、

前記凸状部は、液滴吐出法を繰り返し行い前記導電性部材を積み重ねて形成することを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、プラズマCVD法による導体膜の作製方法、及び、この半導体膜を用いた薄膜トランジスタ（以下、TFTという）で構成された回路を有する半導体装置およびその作製方法に関する。例えば、太陽電池やセンサに代表される光電変換装置、液晶表示パネルに代表される電気光学装置、または発光装置を部品として搭載した電子機器に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、発光装置、半導体回路および電子機器は全て半導体装置である。

10

**【背景技術】****【0003】**

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。TFTはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置（表示パネル）のスイッチング素子として開発が急がれている。

**【0004】**

TFTの活性層に用いる材料は、主としてシリコンが用いられている。従来では非晶質シリコン膜（アモルファスシリコン膜）を用いてTFTが形成されてきた。

20

**【0005】**

また、これまで、一枚のマザーガラス基板から複数のパネルを切り出して、大量生産を効率良く行う生産技術が採用されてきた。マザーガラス基板のサイズは、1990年初頭における第1世代の300×400mmから、2000年には第4世代となり680×880mm若しくは730×920mmへと大型化して、一枚の基板から多数の表示パネルが取れるように生産技術が進歩してきた。

**【0006】**

また、基板サイズの大面積化と同時に、生産性の向上や低コスト化の要求も高まっている。

**【0007】**

30

近年、より高性能を求めるために、アモルファスシリコン膜に代えて、ポリシリコン膜を活性層にしたTFT（以下、ポリシリコンTFTとも記す）を作製することが試みられている。このポリシリコンTFTは、電界効果移動度が高いことから、いろいろな機能を備えた回路を形成することも可能である。

**【0008】**

従来の技術において、ポリシリコン膜は、プラズマCVD法や減圧CVD法で堆積した非晶質半導体膜を、加熱処理やレーザーアニール法（レーザー光の照射により半導体膜を結晶化させる技術）により作製されている。プラズマCVD法では、比較的低温（400程度）で非晶質半導体膜を成膜することが可能である。

**【0009】**

40

加熱処理により作製する場合には、非晶質シリコン膜を結晶化するために600以上の温度で10時間以上の加熱処理が必要とされ、この処理温度は、耐熱性の低いガラス基板の使用を困難なものとしている。この処理温度と処理時間は、TFTの生産性を考慮すると必ずしも適切な方法とは考えられていない。

**【0010】**

また、レーザーアニール法により作製する場合には、非晶質シリコン膜中の水素を熱処理によって低減する脱水素化を行った後、レーザー光の照射を行っている。処理温度の問題はないものの、大面積基板に対応するためのレーザー照射装置は、精密な光学設計や大がかりな光学系（レンズ等）が必要とされ、設備コストがかかってしまう。また、大面積基板に均一なレーザー光を照射することは困難であるため、広い面積に渡って一様な結晶

50

を得ることが困難となる。従って、大面積基板を用いた際の生産性を考慮すると必ずしも適切な方法とは考えられていない。

#### 【0011】

また、本出願人は、ポリシリコン膜をガラス基板上に得る一つの技術として特許文献1に記載の技術を開示している。同公報記載の技術は、非晶質シリコン膜に対して結晶化を助長する金属元素（代表的にはニッケル）を選択的に添加し、加熱処理を行うことで添加領域を起点として広がるポリシリコン膜を形成するものであり、得られる結晶粒のサイズは非常に大きい。また、上記公報技術は、金属元素を用いないで結晶化を行う場合と比べて金属元素の作用により非晶質シリコン膜の結晶化温度を50～100程度下げることが可能であり、結晶化に要する時間も金属元素を用いないで結晶化を行う場合と比べ1/5～1/10に低減することができ、生産性においても優れたものである。10

【特許文献1】特開平8-78329号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0012】

特許文献1に記載の記述を用いれば、ガラス基板の使用が可能となるが、結晶化を助長する金属元素を添加する故に、ポリシリコン膜の膜中或いは膜表面には、当該金属元素が残存し、得られる素子の特性をばらつかせるなどの問題がある。従って、結晶化を助長する金属元素を除去するための手法としてゲッタリング処理を行わなくてはならず、工程数が増加してしまっていた。20

#### 【0013】

安価な大面積の透明絶縁性基板上に、上記従来の方法で作製されるポリシリコン膜を低温で形成するには、量産の上で不向きであった。

#### 【0014】

また、膜中の水素濃度を低減するために480以上 加熱を行いながら成膜するプラズマCVD法を用いようとすると、下地膜として耐熱性の低い材料で形成される膜、代表的にはアクリルなどの有機樹脂、アルミニウム配線等を用いた場合、従来では、これらの上に直接、プラズマCVD法を用いて結晶構造を含む半導体膜を形成することはできなかった。30

#### 【0015】

また、スパッタリング法を用いると低温での成膜が可能であるため、耐熱温度の低い有機樹脂基板または有機樹脂部材上に、直接成膜することができる。

#### 【0016】

しかし、スパッタリング法には、大面積基板対応のターゲットの作製が困難であり且つ高価である点、チャンバー内のセルフクリーニングができず、チャンバー内を開放してメンテナンスを行わなければならないため、生産効率が低下する点、成膜時、雰囲気中の不純物が膜内に混入しやすい点、ターゲット中の不純物が生成物中に混入する点等の問題がある。

#### 【0017】

そこで、本発明では、安価な大面積の透明絶縁性基板上に、結晶構造を含む半導体膜を低温で直接堆積させる成膜方法を提供する技術を課題とする。また、工程数を増加させることなく、短い処理時間で結晶構造を含む半導体膜を成膜する技術も課題とする。40

#### 【0018】

加えて、本発明は、得られた結晶構造を含む半導体膜を用いた半導体装置と、その作製方法も提供する。

#### 【課題を解決するための手段】

#### 【0019】

本発明は、プラズマCVD法により、成膜室に珪化物気体（モノシラン、ジシラン、トリシランなど）とフッ素（或いはフッ化ハロゲンガス）を原料ガスとして導入し、プラズマを発生させて結晶構造を含む半導体膜を被処理基板に直接成膜する。高温加熱により膜50

中の水素濃度を低減して、結晶構造を含む半導体膜を成膜するのではなく、本発明では、 $\text{SiH}_3$ ラジカルの堆積による膜成長反応と、Fラジカルによる引き抜き（エッティング）反応とを競争的に起こさせて結晶構造を含む半導体膜を成膜している。本発明の成膜方法は、非晶質半導体膜よりも特性の優れた膜を被処理基板に直接得ることができ、且つ、タクトタイムが短く、量産に適した成膜方法である。

#### 【0020】

本発明により、安価な大面積の透明絶縁性基板上に、結晶構造を含む半導体膜を低温で成膜することができる。ここでの低温とは、安価なガラス基板が耐えうる範囲の温度を指している。さらに、下地膜として耐熱性の低い材料で形成される膜、代表的にはアクリルなどの有機樹脂、アルミニウム配線等を用いた場合でも直接、結晶構造を含む半導体膜を成膜できる。得られた膜は、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち、格子歪みを有する結晶質な領域を含んでいるセミアモルファス半導体膜（微結晶半導体膜、マイクロクリスタル半導体膜とも呼ばれる）である。

10

#### 【0021】

また、本発明は、TFTの活性層として、セミアモルファス半導体膜（微結晶半導体膜、マイクロクリスタル半導体膜とも呼ばれる）を用い、さまざまな半導体装置を実現する。

20

#### 【0022】

本明細書で開示する発明の構成は、

成膜室に珪化物気体と、フッ素或いはフッ化ハロゲンガスとを原料ガスとして導入し、プラズマを発生させて結晶構造を含む半導体膜を被処理基板表面上に成膜することを特徴とする半導体膜の成膜方法である。

#### 【0023】

また、希ガス（He、Ne、Ar、Kr、Xeから選ばれた一種または複数種）をキャリアガスや原料ガスの希釈に用いてもよく、他の発明の構成は、

成膜室に珪化物気体と、希ガスと、フッ素或いはフッ化ハロゲンガスとを原料ガスとして導入し、プラズマを発生させて結晶構造を含む半導体膜を被処理基板表面上に成膜することを特徴とする半導体膜の成膜方法である。

30

#### 【0024】

また、水素を原料ガスの希釈に用いてもよく、他の発明の構成は、成膜室に珪化物気体と、水素と、フッ素或いはフッ化ハロゲンガスとを原料ガスとして導入し、プラズマを発生させて結晶構造を含む半導体膜を被処理基板表面上に成膜することを特徴とする半導体膜の成膜方法である。

#### 【0025】

また、水素と希ガスとをキャリアガスや原料ガスの希釈に用いてもよく、他の発明の構成は、

成膜室に珪化物気体と、希ガスと、水素と、フッ素或いはフッ化ハロゲンガスとを原料ガスとして導入し、プラズマを発生させて結晶構造を含む半導体膜を被処理基板表面上に成膜することを特徴とする半導体膜の成膜方法である。

40

#### 【0026】

ただし、水素を用いる場合、前記フッ素或いはフッ化ハロゲンガスの流量に対する水素の流量の比率（ $\text{H}_2 / \text{F}_2$ ）を0.1以下に制御して結晶構造を含む半導体膜を成膜することを特徴としている。

#### 【0027】

また、上記各構成において、前記珪化物気体は、モノシラン、ジシラン、またはトリシリランのいずれかのガスであることを特徴としている。また、上記各構成において、前記フッ化ハロゲンガスは、 $\text{ClF}$ 、 $\text{ClF}_3$ 、 $\text{BrF}$ 、 $\text{BrF}_3$ 、 $\text{IF}$ 、または $\text{IF}_3$ のいずれかのガスであることを特徴としている。

#### 【0028】

50

また、上記各構成において、前記成膜は、平行平板型プラズマCVD装置を用いることを特徴としている。

#### 【0029】

また、他の発明の構成は、

成膜室にモノシランガスと、フッ素或いはフッ化ハロゲンガスとを原料ガスとして導入し、

モノシランガス流量に対するフッ素或いはフッ化ハロゲンガス流量の比率( $F_2 / SiH_4$ )を0.1以上とし、

平行平板型の電極間隔を25mm以上、且つ、

R Fパワー密度を0.2W/cm<sup>2</sup>以上とした条件のもとでプラズマを発生させて成膜を行うことを特徴とする結晶構造を含む半導体膜の成膜方法である。 10

#### 【0030】

また、本発明により得られる半導体膜も本発明の一つであり、その発明の構成は、

平行平板型プラズマCVD装置を用いて、珪化物気体と、フッ素或いはフッ化ハロゲンガスとのプラズマ反応により被処理基板表面上に堆積されたことを特徴とする結晶構造を含む半導体膜である。 20

#### 【0031】

また、本発明により得られる半導体装置も本発明の一つであり、その発明の構成は、

絶縁表面を有する基板上に、ゲート電極と、該上にゲート絶縁膜とを有し、

ゲート絶縁膜上には、珪化物気体と、フッ素或いはフッ化ハロゲンガスとのプラズマ反応により堆積された結晶構造を含む半導体膜を活性層として有するTFTを備えたことを特徴とする半導体装置である。 20

#### 【0032】

また、TFTのしきい値電圧の制御を行うため、活性層にボロンなどの半導体にp型を付与する元素を添加してもよく、他の発明の構成は、

絶縁表面を有する基板上に、ゲート電極と、該上にゲート絶縁膜とを有し、

ゲート絶縁膜上には、珪化物気体と、フッ素或いはフッ化ハロゲンガスとのプラズマ反応により堆積された結晶構造を含む半導体膜を活性層として有し、且つ、前記半導体膜にはp型を付与する元素がしきい値電圧を制御するために添加されているTFTを備えたことを特徴とする半導体装置である。 30

#### 【0033】

上記構成において、前記ゲート電極は、Ag、Al、Cu、Au、または樹脂を含むことを特徴としている。これらの耐熱性の低い材料でゲート電極を形成した後でも、SiH<sub>4</sub>とF<sub>2</sub>を原料ガスに用いたプラズマCVD法により低温での結晶構造を含む半導体膜の成膜を可能としている。

#### 【0034】

また、前記半導体装置は、図17(D)にその一例を示す映像音声双方向通信装置、または汎用遠隔制御装置である。

#### 【0035】

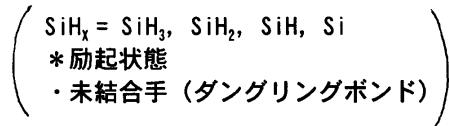

セミアモルファス半導体膜は、少なくとも膜中の一部の領域には、0.5~20nmの結晶粒を含んでいる。セミアモルファス半導体膜については、ラマンスペクトルが単結晶に特有の520cm<sup>-1</sup>よりも低波数側にシフトしている。また、セミアモルファス半導体膜は、X線回折ではSi結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。また、セミアモルファス半導体膜は、未結合手(ダンギングボンド)の中和剤として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。セミアモルファス半導体膜の作製方法としては、珪化物気体をグロー放電分解(Plasma CVD)して形成する。圧力は概略0.1Pa~133Paの範囲、電源周波数は1MHz~120MHz、好ましくは13MHz~60MHzとする。基板加熱温度は300℃以下でよく、好ましくは100~250℃とする。膜中の不純物元素として、酸素、窒素、炭素などの大気成分の不純物は1×10<sup>-20</sup>cm<sup>-1</sup>以下とすることが望ましく、特に、酸素濃度 40

度は  $5 \times 10^{19}/\text{cm}^3$  以下、好ましくは  $1 \times 10^{19}/\text{cm}^3$  以下とする。なお、セミアモルファス半導体膜を活性層とした TFT の電界効果移動度  $\mu$  は、 $5 \sim 50 \text{ cm}^2/\text{Vsec}$  である。

#### 【0036】

また、TFT 構造に関係なく本発明を適用することが可能であり、例えば、ボトムゲート型（逆スタガ型）TFT や、順スタガ型 TFT を用いることが可能である。また、シングルゲート構造の TFT に限定されず、複数のチャネル形成領域を有するマルチゲート型 TFT、例えばダブルゲート型 TFT としてもよい。

#### 【発明の効果】

#### 【0037】

本発明により、安価な大面積の透明絶縁性基板上に、高速の成膜速度で特性の優れた結晶構造を含む半導体膜を低温で直接成膜することができる。特に、耐熱性の低い材料、例えば樹脂を含む金属配線をゲート電極とする TFT を作製する際、ゲート電極の耐熱温度を超えることなく、ゲート電極の上方に特性の優れた結晶構造を含む半導体膜を成膜し、TFT の活性層とすることができる。また、プラスチック基板にも結晶構造を含む半導体膜を直接成膜することができる。

10

#### 【発明を実施するための最良の形態】

#### 【0038】

本発明の実施形態について、以下に説明する。

#### 【0039】

#### (実施の形態 1 )

20

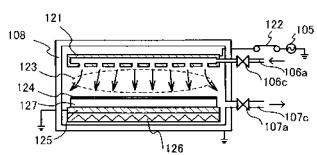

図 1 を用いて本発明で用いる平行平板型のプラズマ CVD 装置の処理室（チャンバーとも呼ぶ）の断面図を説明する。図 1 において、接地されたチャンバー 108 内には、高周波電源 105 に接続された第 1 の電極（上部電極、シャワー電極、高周波電極）121 及び接地されている第 2 の電極（下部電極、接地電極）125 が設けられている。第 2 の電極上に被処理基板 127 が設置される。

#### 【0040】

第 1 の電極 121 は、中空構造であって、供給系 106a から供給される原料ガスが電極内を通過し、電離されチャンバー内に供給される。ここでは供給系が 1 系統しか図示していないが、必要に応じて複数のガス供給系を設けることが可能である。

#### 【0041】

30

また、チャンバーには、排気系 107a が設けられ、反応後の排気ガスを排出する。なお、本実施の形態では、電極構造が中空構造（複数のシャワー板が重なりガスを分散する構造、いわゆるシャワーヘッド構造）となっているが、この構造に限られない。供給系が第 1 の電極と別に設けられていてもよい。また、供給系 106a 及び排気系 107a には、バルブ（106c、107c）が設けられており、供給するガス圧及びチャンバー内の圧力を制御する。

#### 【0042】

ヒータ 126 は、第 2 の電極 125 と接して設けられているが、この構造に限られない。また、第 1 の電極 121 にヒータ（図示しない）を設けてもよい。また、チャンバーの外壁にヒータを設け、チャンバー内をホットウォール構造としてもよい。

40

#### 【0043】

また、チャンバーの側面には窓（図示しない）が設けられ、この窓を開閉して基板が収納されているカセット室からロボットアーム等の搬送機構を経由して基板をチャンバー内に移送することができる。

#### 【0044】

次に、図 1 を用いて、成膜方法を述べる。本実施の形態においては、ガラス基板に直接、結晶構造を有する珪素膜の成膜方法を説明する。

#### 【0045】

原料ガスに珪化物気体（モノシリコン、ジシリコン、トリシリコンなど）とフッ素（或いはフッ化ハロゲンガス）を用いる。フッ化ハロゲンガスとしては、 $\text{ClF}_3$ 、 $\text{BrF}_3$

50

、 $\text{BrF}_3$ 、 $\text{IF}$ 、 $\text{IF}_3$ などが挙げられる。中でも、モノシランガスとフッ素ガスとの組み合わせが安価なガスの組み合わせであり、量産に適している。ここでは、原料ガスにモノシランガスとフッ素ガスを用いた例で説明を行う。

#### 【0046】

また、他のフッ素系ガスとして、フッ素化モノシラン ( $\text{SiH}_m\text{F}_n$ : ただし、 $m + n = 4$ )、四フッ化シリコン ( $\text{SiF}_4$ ) を用いることもできるが、高価なガスとなる。また、 $\text{Si}-\text{H}$  の結合(解離)エネルギーは  $76 \text{ kcal/mol}$  であるのに比べ、 $\text{Si}-\text{F}$  の結合(解離)エネルギーは  $142 \text{ kcal/mol}$  と高いため、成膜に必要なエネルギーが高くなり、生産工程における消費エネルギーが増大してしまう。

#### 【0047】

また、成膜条件は、チャンバー内の圧力を  $1.33 \times 10^1 \sim 1.33 \times 10^3 \text{ Pa}$  ( $1 \times 10^{-1} \sim 1 \times 10^1 \text{ torr}$ )、成膜温度を  $80 \sim 600$  とし、高周波電源の電源周波数を  $10 \sim 500 \text{ MHz}$  とする。なお、被処理基板または下地膜として耐熱性の低い材料で形成されている場合には  $80 \sim 300$  とする。

#### 【0048】

図1に示すように、チャンバー内に珪化物気体とフッ素を供給系より導入し、電源のスイッチ122を接続し、電極に高周波電圧を印加し、プラズマ123を発生させる。このプラズマ中で生成される珪化物又はフッ素のイオン、ラジカルなどの化学的に活性な励起種が反応して生成物である結晶構造を有する珪素膜124を形成する。

#### 【0049】

$\text{SiH}_3$ ラジカルの堆積による膜成長反応と、Fラジカルによる引き抜き(エッチング)反応とが競争的に起こることにより、 $\text{Si}$ 膜ネットワークの再構成が起こり、結晶構造を含むシリコン膜が形成されると考えられる。

#### 【0050】

実際には多種多様な反応が存在するが、ここで、チャンバー内で生じる反応の一例を示す。

#### 【0051】

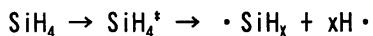

高周波による気体の分解反応は、数1と数2で表せる。

#### 【0052】

#### 【数1】

#### 【0053】

#### 【数2】

#### 【0054】

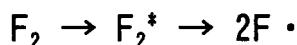

また、気相中の反応は、数3で表せる。

#### 【0055】

#### 【数3】

10

20

30

40

50

## 【0056】

なお、数3で発生するSiH<sub>3</sub>ラジカルは一般にSi膜成長の主たる化学種と言われている。また、数3では、HFのような腐食性が高いフッ素系ガスが形成されるため、プラズマCVD装置においては、優れた耐腐食性を有する材料で装置内表面を覆うことが望ましい。

## 【0057】

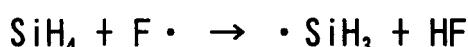

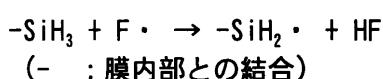

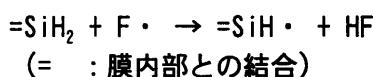

また、シリコン膜表面での水素原子引き抜き反応は、数4、数5、数6で表せる。

## 【0058】

## 【数4】

10

## 【0059】

## 【数5】

## 【0060】

## 【数6】

20

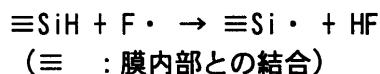

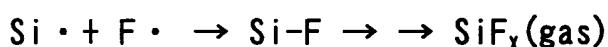

## 【0061】

また、シリコン膜表面のダングリングボンドへの結合（エッチング反応）は、数7で表せる。

## 【0062】

## 【数7】

30

## 【0063】

実際に成膜条件（ガス流量、RFパワー、電極間ギャップ）を振ってそれぞれ成膜を行い、それらの実験結果（膜厚速度、ラマン光学特性（ラマンピーク（Pc、Pa）、ラマン半値幅（Wc、Wa）、積分強度（Ic、Ia）など））を表1に示す。表面にはLPCVD法による酸化珪素膜100nmが予め形成されている被処理基板を用いた。なお、電極面積は380cm<sup>2</sup>、RF電源周波数は27MHz、上部ヒータ設定温度を65°、下部ヒータ設定温度を300°として成膜を行っている。

40

## 【0064】

【表1】

| サンプル名 | SiH4<br>sccm | F2/He(10%)<br>sccm | Ar<br>sccm | RF Power<br>W | Pressure<br>Torr | Gap<br>mm | 膜厚<br>Å | Depo.Rate<br>Å/min | Ic<br>CPS | Ia<br>CPS | Pc<br>cm <sup>-1</sup> | Pa<br>cm <sup>-1</sup> | Wc<br>cm <sup>-1</sup> | Wa<br>cm <sup>-1</sup> |

|-------|--------------|--------------------|------------|---------------|------------------|-----------|---------|--------------------|-----------|-----------|------------------------|------------------------|------------------------|------------------------|

| 試料1   | 4            | 4                  | 500        | 100           | 1.0              | 25        | 905     | 90.5               | 55.6951   | 14.0837   | 515.46                 | 490.0                  | 10.03                  | 43.3                   |

| 試料2   | 4            | 4                  | 100        | 100           | 1.0              | 25        | 1351    | 135.1              | 143.52    | 37.0672   | 514.99                 | 488.5                  | 10.53                  | 45.4                   |

| 試料3   | 4            | 8                  | 500        | 100           | 1.0              | 25        | 1042    | 104.2              | 58.661    | 13.5501   | 515.97                 | 490.9                  | 9.596                  | 43.0                   |

| 試料4   | 8            | 4                  | 500        | 100           | 1.0              | 25        | 2063    | 206.3              | 96.448    | 28.209    | 514.95                 | 487.9                  | 10.53                  | 45.9                   |

| 試料5   | 4            | 4                  | 500        | 200           | 1.0              | 25        | 971     | 97.1               | 34.3052   | 8.84875   | 514.89                 | 490.1                  | 12.75                  | 42.0                   |

| 試料6   | 4            | 4                  | 500        | 300           | 1.0              | 25        | 1013    | 101.3              | 31.4214   | 9.82769   | 514.59                 | 489.1                  | 14.71                  | 44.8                   |

| 試料7   | 2            | 8                  | 500        | 100           | 1.0              | 25        | 579     | 57.9               | 57.1155   | 14.0169   | 515.49                 | 490.2                  | 10.99                  | 43.6                   |

| 試料8   | 4            | 8                  | 500        | 100           | 1.0              | 20        | 1429    | 142.9              | 68.3614   | 19.6263   | 515.66                 | 488.0                  | 9.812                  | 47.3                   |

| 試料9   | 4            | 8                  | 500        | 100           | 1.0              | 30        | 634     | 63.4               | 116.768   | 24.5778   | 516.01                 | 490.9                  | 9.708                  | 43.1                   |

| 試料10  | 1            | 8                  | 500        | 100           | 1.0              | 25        | 210     | 21                 | 12.0454   | 2.7597    | 517.07                 | 490.3                  | 10.83                  | 41.3                   |

10

## 【0065】

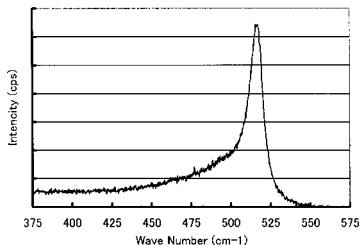

表1において、ラマン散乱分光法により得られたスペクトルを2つの指数関数型曲線に分離した際に低波数側曲線のピーク（曲線の中心位置）をP a、低波数側曲線のラマン半値幅をW a、低波数側曲線の積分強度をI aとしている。また、高波数側曲線のピークをP c、高波数側曲線のラマン半値幅をW c、高波数側曲線の積分強度をI cとしている。

## 【0066】

表1より、300 の低温でセミアモルファスシリコン膜、或いは微結晶シリコン膜、或いはマイクロクリスタルシリコン膜と呼べる結晶構造を含むシリコン膜が形成されていることが確認できる。得られた結晶構造を含むシリコン膜のP aは、487～490 cm<sup>-1</sup>、P cは514～517 cm<sup>-1</sup>、且つ、W aは42～47.3 cm<sup>-1</sup>、W cは9.6～14.7 cm<sup>-1</sup>にある薄膜である。また、成膜速度（堆積速度）も5 nm/min～20 nm/minが得られている。なお、膜厚は10分間の成膜後ものである。

20

## 【0067】

また、モノシランガスは100%、フッ素ガスはHeで希釈された混合ガスを用いており、フッ素含有率は10.1%、不純物（CF<sub>4</sub>、HF、空気など）のトータル含有率は0.1%未満であり、純度は99.9%である。

## 【0068】

また、最も結晶化率が高いサンプル（試料9）のラマンスペクトルデータを図2に示す。

30

## 【0069】

また、比較例として、成膜条件のうち、圧力を0.3 Torrとしてアモルファスシリコン膜が形成された実験結果（比較試料1～3）を表2に示す。これらの結果から、F<sub>2</sub>分圧、全圧、RFパワーはいずれも高くなるほど結晶化しやすい傾向が見られる。

## 【0070】

## 【表2】

| サンプル名 | SiH4<br>sccm | F2/He(10%)<br>sccm | Ar<br>sccm | RF Power<br>W | Pressure<br>Torr | Gap<br>mm | 膜質     |

|-------|--------------|--------------------|------------|---------------|------------------|-----------|--------|

| 比較試料1 | 4            | 4                  | 100        | 20            | 0.3              | 25        | アモルファス |

| 比較試料2 | 4            | 4                  | 500        | 20            | 0.3              | 25        | アモルファス |

| 比較試料3 | 4            | 4                  | 500        | 100           | 0.3              | 25        | アモルファス |

40

## 【0071】

また、ここではキャリアガスとしてArを用いて3系統のガス供給を行っているが、特にキャリアガスを用いなくともよく、2系統のガス供給のみで成膜を行うこともできる。数の少ないガス系統とすることで成膜条件を調節しやすくすることができる。

50

## 【0072】

また、水素ガスを供給して3系統のガス供給を行ってもよいし、さらにキャリアガスを供給して4系統のガス供給を行ってもよい。ただし、水素ガスを供給する場合には、水素とフッ素の流量比( $H_2 : F_2$ )を1:10に制御、或いは、この比率よりも下げる水素の流量を少なくすることが好ましい。

## 【0073】

本発明により、安価な大面積の透明絶縁性基板上に、高速の成膜速度で特性の優れた結晶構造を含む半導体膜を低温で直接成膜することができる。

## 【0074】

(実施の形態2)

10

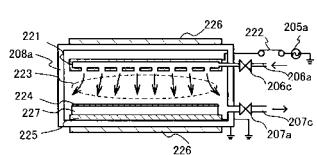

タクトタイムの向上や、膜厚の均一性向上を図るため、チャンバーの外壁にヒータを設け、チャンバー内をホットウォール構造としたチャンバーを縦方向に重ねて配置したプラズマCVD装置を用いても同様にして成膜を行うことができる。

## 【0075】

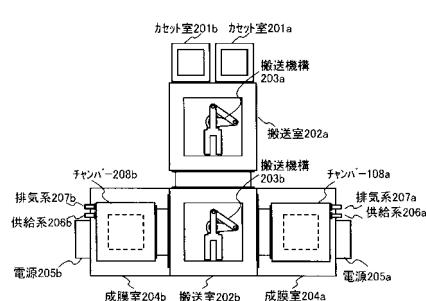

図3にホットウォール構造としたチャンバーの一例を示す。図3に示すチャンバー208aは、実施の形態1とヒータの設置位置が異なっており、チャンバーの外壁にヒータ226を設け、チャンバー内をホットウォール構造としている。

## 【0076】

図3において、208aは接地されたチャンバー、205aは高周波電源、221は原料ガスが電極内を通過する中空構造の第1の電極(上部電極、シャワー電極、高周波電極)、225は接地されている第2の電極(下部電極、接地電極)、106aは供給系、107aは排気系、106c、107cはバルブである。

20

## 【0077】

なお、チャンバー構成に関する説明は、実施の形態1でも一部述べているので、同じ箇所は同一であるのでここでは詳細な説明を省略する。

## 【0078】

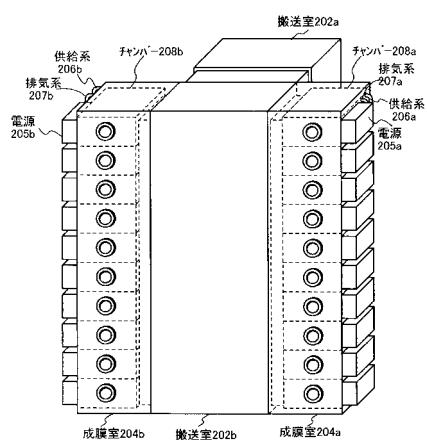

図3に示したチャンバーを縦方向に重ねて配置したプラズマCVD装置の一例の斜視図を図4に示し、上面図を図5に示す。

## 【0079】

図4および図5に示す成膜装置は、成膜室及び搬送室を有し、成膜室204a、204bの間に搬送室202bが配置され、搬送室202a、202bが隣接して配置された構造を有する。各成膜室には、縦方向に重ねて配置された10個のチャンバー208a、208bを具備し、各チャンバー208a、208bには、成膜ガスを供給する供給系206a、206b、排気ガスを排気する排気系207a、207b及び電源205a、205bを具備する。

30

## 【0080】

本装置は、各成膜室204a、204bにおいて、複数のチャンバー208a、208bの全ての供給系は、一つの供給源に接続されていることを特徴とする。同様に、複数のチャンバー208a、208bの全ての排気系は、一つの排気口に接続されていることを特徴とする。本特徴により、本装置では複数のチャンバー208a、208bを縦方向に重ねて配置しているにもかかわらず、供給系206a、206bと排気系207a、207bとを簡単に配置することができる。また、成膜室204a、204bには、各成膜室の圧力を減圧するための排気系(図示しない)が設けられている。チャンバー内の圧力と成膜室内の圧力を制御することにより、成膜、及びチャンバー内のクリーニングを交互に行うことができ、効率良く成膜を行うことができる。

40

## 【0081】

実施の形態1と同様に、珪化物気体(モノシリラン、ジシリラン、トリシリランなど)とフッ素(或いはフッ化ハロゲンガス)を原料ガスとして導入し、プラズマを発生させて結晶構造を含む半導体膜を被処理基板に直接成膜することができる。

## 【0082】

50

図5において、カセット室201a、201bには所望のサイズのガラス基板、プラスチック基板に代表される樹脂基板等の絶縁表面を有する基板がセットされる。基板の搬送方式として、図示する装置では水平搬送を採用するが、第五世代以降のメータ角の基板を用いる場合、搬送機の占有面積の低減を目的として、基板を縦置きにした縦形搬送を行ってもよい。

#### 【0083】

搬送室202a、202bの各々には、搬送機構(ロボットアーム)203a、203bが具備されている。搬送機構により、カセット室201a、201bにセットされた基板が各成膜室204a、204bに搬送される。そして、成膜室204a、204bのチャンバー208a、208bにおいて、搬送された基板の被処理面に対して所定の処理が行われる。また、図5において、搬送室が複数設けられているが、これは一つでもよい。

10

#### 【0084】

ここでは、数十枚の基板を一度に処理するバッチ式装置を例示したが、基板を一枚ずつ処理する枚葉式装置に本発明を適用することもできる。

#### 【0085】

図4に示すように、複数のチャンバーを有する成膜装置で成膜することにより、同時に多数の基板に同条件で形成される膜を形成することができる。このため、基板間のバラツキを低減することが可能となり、歩留まりを向上させることができる。また、スループットを向上することもできる。

#### 【0086】

20

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

#### 【実施例1】

#### 【0087】

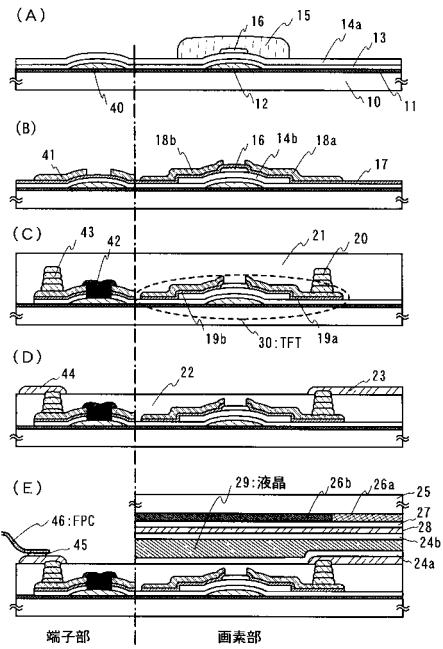

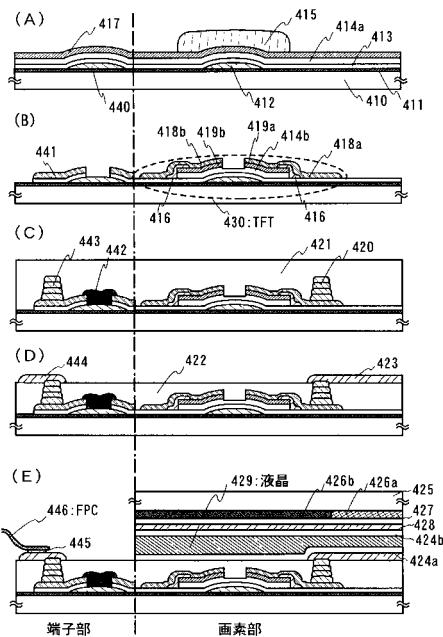

本実施例では、逆スタガ型TFTをスイッチング素子とするアクティブマトリクス型液晶表示装置の作製方法を示す。なお、図6は作製工程の断面を示している。

#### 【0088】

まず、基板10上に後に形成する液滴吐出法による材料層と密着性を向上させるための下地膜11を形成する。下地膜11は、極薄く形成すれば良いので、必ずしも層構造を持っていなくても良く、下地前処理とみなすこともできる。スプレーによって光触媒物質(酸化チタン( $TiO_x$ )、チタン酸ストロンチウム( $SrTiO_3$ )、セレン化カドミウム( $CdSe$ )、タンタル酸カリウム( $KTaO_3$ )、硫化カドミウム( $CdS$ )、酸化ジルコニウム( $ZrO_2$ )、酸化ニオブ( $Nb_2O_5$ )、酸化亜鉛( $ZnO$ )、酸化鉄( $Fe_2O_3$ )、酸化タンクステン( $WO_3$ ))を全面に滴下、またはインクジェット法やゾルゲル法を用いて有機材料(ポリイミド、アクリル、或いは、シリコン(Si)と酸素(O)との結合で骨格構造が構成され、置換基に水素、フッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いた塗布絶縁膜)を選択的に形成してもよい。

30

#### 【0089】

光触媒物質は、光触媒機能を有する物質を指し、紫外光領域の光(波長400nm以下、好ましくは380nm以下)を照射し、光触媒活性を生じさせるものである。光触媒物質上に、インクジェット法により、溶媒に混入された導電体を吐出すると、微細な描画を行うことができる。

40

#### 【0090】

例えば、 $TiO_x$ に光照射する前、親油性はあるが、親水性はない、つまり撥水性の状態にある。光照射を行うことにより、光触媒活性が起こり、親水性にかわり、逆に親油性がない状態、つまり撥油性となる。なお光照射時間により、親水性と親油性を共に有する状態にもなりうる。

#### 【0091】

なお、親水性とは、水に濡れやすい状態を指し、接触角が30度以下、特に接触角が5度以下を超親水性という。一方撥水性とは、水に濡れにくい状態を指し、接触角が90度

50

以上のものを指す。同様に親油性とは、油に濡れやすい状態を指し、撥油性とは油に濡れにくい状態を指す。なお接触角とは、滴下したドットのふちにおける、形成面と液滴の接線がなす角度のことを指す。

#### 【0092】

すなわち、光照射を行った領域（以下、照射領域と表記する）は、親水性領域、又は超親水性（合わせて単に親水性と表記する）となる。このとき、照射領域の幅を所望の配線幅となるように光照射を行う。その後、インクジェット法により、照射領域上から又は照射領域にむかって、水系の溶媒に導電体が混入したドットを吐出する。すると、単にインクジェット法により吐出されたドットの径より小さな、つまり幅の狭い配線を形成することができる。これは所望の配線幅となるように照射領域が形成されるため、吐出されたドットが形成表面で広がることを抑制できるからである。更に、ドットが多少ずれて吐出された場合であっても、照射領域に沿って配線を形成することができ、配線形成の正確な位置制御が可能となる。10

#### 【0093】

なお、水系の溶媒を用いる場合、インクジェットのノズルからスムーズに吐出できるよう界面活性剤を添加すると好ましい。

#### 【0094】

また、油（アルコール）系の溶媒に混入された導電体を吐出する場合、光照射が行われない領域（以下、非照射領域と表記する）に導電体を吐出し、非照射領域上から又は非照射領域にむかってドットを吐出することにより、同様に配線を形成することができる。すなわち、配線を形成したい領域の両端、つまり配線を形成したい領域を囲むような周囲に光照射を行い、照射領域を形成すればよい。このとき照射領域は撥油性を有するため、油（アルコール）系の溶媒に混入された導電体を有するドットは、選択的に非照射領域に形成されるからである。すなわち、非照射領域の幅を所望の配線幅となるように光照射を行う。20

#### 【0095】

なお、油（アルコール）系の溶媒は、非極性溶剤又は低極性溶剤を用いることができる。例えば、テルピネオール、ミネラルスピリット、キシレン、トルエン、エチルベンゼン、メシチレン、ヘキサン、ヘプタン、オクタン、デカン、ドデカン、シクロヘキサン、又はシクロオクタンを用いることができる。30

#### 【0096】

更に光触媒物質へ遷移金属（Pd、Pt、Cr、Ni、V、Mn、Fe、Ce、Mo、W等）をドーピングすることにより、光触媒活性を向上させたり、可視光領域（波長400nm～800nm）の光により光触媒活性を起こすことができる。遷移金属は、広いバンドギャップを持つ活性な光触媒の禁制帯内に新しい準位を形成し、可視光領域まで光の吸収範囲を拡大しうるからである。例えば、CrやNiのアクセプター型、VやMnのドナー型、Fe等の両性型、その他Ce、Mo、W等をドーピングすることができる。このように光の波長は光触媒物質によって決定することができるため、光照射とは光触媒物質の光触媒活性化させる波長の光を照射することを指す。

#### 【0097】

また、光触媒物質を真空中又は水素環流中で加熱し還元させると、結晶中に酸素欠陥が発生する。このように遷移元素をドーピングしなくても、酸素欠陥は電子ドナーと同等の役割を果たす。特に、ゾルゲル法により形成する場合、酸素欠陥が最初から存在するため、還元しなくともよい。またN<sub>2</sub>等のガスをドープすることにより、酸素欠陥を形成することができる。40

#### 【0098】

また、ここでは基板上に導電性材料を吐出する場合に密着性を良くする下地前処理を行う例を示したが、特に限定されず、材料層（例えば、有機層、無機層、金属層）、或いは、吐出した導電性層の上にさらに液滴吐出法で材料層（例えば、有機層、無機層、金属層）を形成する場合において、材料層と材料層との密着性向上のためのTiO<sub>x</sub>成膜処理を50

行っても良い。つまり、液滴吐出法で導電性材料を吐出して描画する場合、その導電性材料層の上下界面で下地前処理を挟み、その密着性を良くすることが望ましい。

#### 【0099】

なお、基板10は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス若しくはアルミノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板等を用いることができる。また、反射型の液晶表示装置とする場合、単結晶シリコンなどの半導体基板、ステンレスなどの金属基板、またはセラミック基板の表面に絶縁層を設けた基板を適用しても良い。

#### 【0100】

次いで、液滴吐出法、代表的にはインクジェット法により滴下した後、酸素雰囲気で焼成を行い、ゲート電極またはゲート配線となる金属配線12を形成する。また、同様に端子部に伸びる配線40も形成する。なお、ここでは図示しないが、保持容量を形成するための容量電極または容量配線をも形成する。

#### 【0101】

これらの配線材料としては、金(Au)、銀(Ag)、銅(Cu)、白金(Pt)、パラジウム(Pd)、タンゲステン(W)、ニッケル(Ni)、タンタル(Ta)、ビスマス(Bi)、鉛(Pb)、インジウム(Ind)、錫(Sn)、亜鉛(Zn)、チタン(Ti)、若しくはアルミニウム(Al)、これらからなる合金、これらの分散性ナノ粒子、又はハロゲン化銀の微粒子を用いる。特に、ゲート配線は、低抵抗化することが好ましいので、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。但し、銀、銅を用いる場合には、不純物拡散防止対策のため、合わせてバリア膜を設けるとよい。溶媒は、酢酸ブチル等のエステル類、イソプロピルアルコール等のアルコール類、アセトン等の有機溶剤等に相当する。表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

#### 【0102】

液滴吐出法において用いるノズルの径は、0.02~100μm(好適には30μm以下)に設定し、該ノズルから吐出される組成物の吐出量は0.001pl~100pl(好適には10pl以下)に設定することが好ましい。液滴吐出法には、オンデマンド型とコンティニュアス型の2つの方式があるが、どちらの方式を用いてもよい。さらに液滴吐出法において用いるノズルには、圧電体の電圧印加により変形する性質を利用した圧電方式、ノズル内に設けられたヒータにより組成物を沸騰させ該組成物を吐出する加熱方式があるが、そのどちらの方式を用いてもよい。被処理物とノズルの吐出口との距離は、所望の箇所に滴下するために、出来る限り近づけておくことが好ましく、好適には0.1~3mm(好適には1mm以下)程度に設定する。ノズルと被処理物は、その相対的な距離を保ちながら、ノズル及び被処理物の一方が移動して、所望のパターンを描画する。また、組成物を吐出する前に、被処理物の表面にプラズマ処理を施してもよい。これは、プラズマ処理を施すと、被処理物の表面が親水性になったり、疎水性になったりすることを活用するためである。例えば、純水に対しては親水性になり、アルコールを溶媒したペーストに対しては疎水性になる。

#### 【0103】

組成物を吐出する工程は、減圧下で行っても良い。これは、組成物を吐出して被処理物に着弾するまでの間に、該組成物の溶媒が揮発し、後の乾燥と焼成の工程を省略又は短くすることができるためである。組成物の吐出後は、常圧下又は減圧下で、レーザ光の照射や瞬間熱アーナー、加熱炉等により、乾燥と焼成の一方又は両方の工程を行う。乾燥と焼成の工程は、両工程とも加熱処理の工程であるが、例えば、乾燥は100度で3分間、焼成は200~350度で15分間~120分間で行うもので、その目的、温度と時間が異なるものである。乾燥と焼成の工程を良好に行うためには、基板を加熱しておいてもよく、そのときの温度は、基板等の材質に依存するが、100~800度(好ましくは200

10

20

30

40

50

~350度)とする。本工程により、組成物中の溶媒の揮発又は化学的に分散剤を除去し、周囲の樹脂が硬化収縮することで、融合と融着を加速する。雰囲気は、酸素雰囲気、窒素雰囲気又は空気で行う。但し、金属元素を分解又は分散している溶媒が除去されやすい酸素雰囲気下で行うことが好適である。

#### 【0104】

上記下地膜の形成または下地前処理を行うことによって、後に形成する液滴吐出法での金属層の密着性が大幅に向上され、希フッ酸(1/100希釈)に浸けても1分以上耐えることができ、テープ剥がし試験でも十分な密着性が確保されている。

#### 【0105】

次いで、プラズマCVD法やスパッタリング法を用いて、ゲート絶縁膜13を単層又は積層構造で形成する。望ましくは、ゲート絶縁膜13として、窒化珪素からなる絶縁体層、酸化珪素からなる絶縁体層、窒化珪素からなる絶縁体層の3層の積層とする。ただし、ゲート絶縁膜13の成膜温度で金属配線12がダメージを受けないようにする。なお、ゲートリーク電流が少ない緻密な絶縁膜を低い成膜温度で形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。10

#### 【0106】

次いで、半導体膜14aを形成する。本実施例では、SiH<sub>4</sub>とF<sub>2</sub>を原料ガスに用いたPCVD法により得られるセミアモルファス半導体膜を形成する。高速の成膜速度でセミアモルファス半導体膜を低温で直接成膜することができる。実施の形態1に示す成膜方法に従って、金属配線12の耐熱温度を超えることなく、金属配線12の上方に特性の優れた結晶構造を含む半導体膜を成膜する。なお、セミアモルファスシリコン膜は、下地との界面により結晶性を持たせることができるので好ましい。20

#### 【0107】

次いで、絶縁体層16をプラズマCVD法やスパッタリング法で形成する。なお、パターニングは、液滴吐出法で形成されたマスクを用いたエッチング、またはフォトリソグラフィ技術を用いればよい。この絶縁体層16は、ゲート電極層と相対して半導体層上に残存させて、チャネル保護層とするものである。また、絶縁体層16としては、界面の清浄性を確保して、有機物や金属物、水蒸気などの不純物で半導体層が汚染されることを防ぐ効果を得るために、緻密な膜で形成することが好ましい。グロー放電分解法においても、珪化物気体をアルゴンなどの珪化物気体で100倍~500倍に希釈して形成された窒化珪素膜は、100以下ので成膜温度でも緻密な膜を形成可能であり好ましい。30

#### 【0108】

次いで、絶縁体層16を覆うマスク15を液滴吐出法で形成する。(図6(A))マスク15は、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、透過性を有するポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いて液滴吐出法で形成する。或いは、感光剤を含む市販のレジスト材料を用いてよく、例えば、代表的なポジ型レジストである、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物、ネガ型レジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤などを用いてよい。いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。40

#### 【0109】

次いで、マスク15で覆われた領域以外の半導体膜14aをドライエッチングまたはウェットエッチングにより除去して活性層となる半導体層14bを形成する。

#### 【0110】

次いで、マスク15を除去した後、n型の半導体膜17を全面に形成する。なおn型の半導体膜を設ける場合、半導体膜と電極とのコンタクト抵抗が低くなり好ましいが、必要に応じて設ければよい。n型の半導体膜17は、シランガスとフォスフィンガスを用いたPCVD法で形成すれば良く、アモルファス半導体膜、或いはセミアモルファス半導体膜50

で形成することができる。

#### 【0111】

次いで、液滴吐出法により導電性材料（Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等）を含む組成物を選択的に吐出して、ソース配線またはドレイン配線18a、18bを形成する。なお、同様に、端子部において接続配線41も形成する。（図6（B））

#### 【0112】

次いで、ソース配線またはドレイン配線18a、18bをマスクとして自己整合的にn型の半導体膜17をエッティングして、ソース領域またはドレイン領域19a、19bを形成する。この段階でチャネルストップ型のTFT30が完成する。絶縁体層16は、n型の半導体膜のエッティングストッパーとして機能させる。10

#### 【0113】

次いで、シャドーマスクを用いて端子部以外をレジストなどの樹脂で覆い、端子部においては、接続配線41をマスクとしたゲート絶縁膜13のエッティングを行って配線40の一部を露呈させる。また、シャドーマスクに代えてスクリーン印刷法によりレジストマスクを形成してエッティングマスクとしてもよい。なお、端子部以外をレジストで覆うことなくゲート絶縁膜13のエッティングを行ってもよいが、画素部において、ソース配線またはドレイン配線18a、18bと重ならない領域のゲート絶縁膜がエッティングされてしまう点と、絶縁体層16がエッティングされて半導体層が露呈してしまう恐れがある点で問題がある。20

#### 【0114】

次いで、端子部に伸びる配線40と接続配線41との接続を行うための導電物42を形成する。導電物42は印刷法または液滴吐出法により形成すればよい。液滴吐出法を用いる場合、導電性材料（Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等）を含む組成物を選択的に吐出して導電物42を形成する。

#### 【0115】

次いで、ソース配線またはドレイン配線18a上的一部分に導電性部材からなる凸状部（ピラー）20を形成する。凸状部（ピラー）20は、導電性材料（Ag（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等）を含む組成物の吐出と焼成を繰り返すことによって積み重ねる。また、同様に接続配線41上にも凸状部（ピラー）43を形成する。或いは、凸状部（ピラー）20は、スパッタ法により得た金属膜をパターニングすることで形成してもよく、この場合、凸状部（ピラー）は柱状となる。30

#### 【0116】

次いで、塗布法による平坦な層間絶縁膜21を形成する。（図6（C））塗布法による平坦な層間絶縁膜とは、液状の組成物を塗布して形成する層間絶縁膜を指す。塗布法による平坦な層間絶縁膜としては、アクリル、ポリイミドなどの有機樹脂、有機溶媒中に溶かされた絶縁膜材料を塗布した後熱処理により被膜を形成する所謂、塗布珪素酸化膜（Spin on Glass、以下「SOG」ともいう。）、シロキサンポリマーなどの焼成によりシロキサン結合を形成する材料などが挙げられる。また、層間絶縁膜21は、塗布法に限定されず、気相成長法やスパッタリング法により形成された酸化珪素膜などの無機絶縁膜も用いることができる。また、保護膜として窒化珪素膜をPCVD法やスパッタ法で形成した後、塗布法による平坦な絶縁膜を積層してもよい。40

#### 【0117】

また、液滴吐出法により層間絶縁膜21を形成してもよい。また、凸状部（ピラー）20、43を本焼成する前に層間絶縁膜21を液滴吐出法により形成し、同時に本焼成してもよい。

#### 【0118】

なお、塗布法や液滴吐出法による平坦な層間絶縁膜21を形成する際、スキージではなく、エアナイフで表面におけるミクロの凹凸を平坦化させた後、本焼成を行うことが好ましい。50

## 【0119】

次いで、全面エッチバックにより凸状部（ピラー）20、43上の層間絶縁膜を除去して凸状部（ピラー）20、43を露出させる。また、他の方法としては、化学的機械研磨（CMP）により、層間絶縁膜を研削し、その後、層間絶縁膜を全面エッチバックすることにより、凸状部（ピラー）20、43を露出させることができる。

## 【0120】

次いで、層間絶縁膜22上に凸状部（ピラー）20と接する画素電極23を形成する。（図6（D））なお、同様に凸状部（ピラー）43と接する端子電極44も形成する。透過型の液晶表示パネルを作製する場合には、液滴吐出法または印刷法によりインジウム錫酸化物（ITO）、酸化珪素を含むインジウム錡酸化物（ITSO）、酸化亜鉛（ZnO）、酸化スズ（SnO<sub>2</sub>）などを含む組成物からなる所定のパターンを形成し、焼成して画素電極23および端子電極44を形成しても良い。また、反射型の液晶表示パネルを作製する場合には、画素電極23および端子電極44を液滴吐出法によりAg（銀）、Au（金）、Cu（銅）、W（タンゲステン）、Al（アルミニウム）等の金属の粒子を主成分とした組成物を用いて形成することができる。他の方法としては、スパッタリング法により透明導電膜、若しくは光反射性の導電膜を形成して、液滴吐出法によりマスクパターンを形成し、エッチングを組み合わせて画素電極を形成しても良い。なお、エッチバックやCMPにより層間絶縁膜22の表面は平坦化されており、平坦な画素電極23を形成することができる。

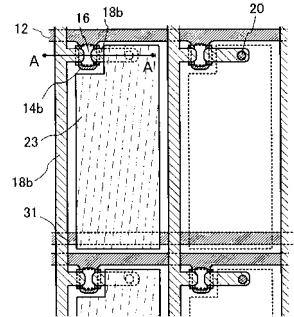

## 【0121】

なお、図7に画素部の一部を拡大した上面図を示す。また、図7は画素電極の形成途中を示しており、左側の画素においては画素電極が形成されているが、右側の画素においては画素電極を形成していない状態を示している。図7において、実線A-A'で切断した図が、図6（D）の画素部の断面と対応しており、図6（D）と対応する箇所には同じ符号を用いている。また、容量配線31が設けてあり、保持容量は、ゲート絶縁膜を誘電体とし、画素電極23と、該画素電極と重なる容量配線31とで形成されている。

## 【0122】

以上の工程により、基板10上にボトムゲート型（逆スタガ型ともいう。）のTFTおよび画素電極が形成された液晶表示パネル用のTFT基板が完成する。

## 【0123】

次いで、画素電極23を覆うように、配向膜24aを形成する。なお、配向膜24aは、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いればよい。その後、配向膜24aの表面にラビング処理を行う。

## 【0124】

そして、対向基板25には、着色層26a、遮光層（ブラックマトリクス）26b、及びオーバーコート層27からなるカラーフィルタを設け、さらに透明電極からなる対向電極と、その上に配向膜24bを形成する。そして、閉パターンであるシール材（図示しない）を液滴吐出法により画素部と重なる領域を囲むように形成する。ここでは液晶を滴下するため、閉パターンのシール材を描画する例を示すが、開口部を有するシールパターンを設け、TFT基板を貼りあわせた後に毛細管現象を用いて液晶を注入するディップ式（汲み上げ式）を用いてもよい。

## 【0125】

次いで、気泡が入らないように減圧下で液晶の滴下を行い、両方の基板を貼り合わせる。閉ループのシールパターン内に液晶を1回若しくは複数回滴下する。液晶の配向モードとしては、液晶分子の配列が光の入射から出射に向かって90°ツイスト配向したTNモードを用いる場合が多い。TNモードの液晶表示装置を作製する場合には、基板のラビング方向が直交するように貼り合わせる。

## 【0126】

なお、一対の基板間隔は、球状のスペーサを散布したり、樹脂からなる柱状のスペーサを形成したり、シール材にフィラーを含ませることによって維持すればよい。上記柱状の

10

20

30

40

50

スペースは、アクリル、ポリイミド、ポリイミドアミド、エポキシの少なくとも1つを主成分とする有機樹脂材料、もしくは酸化珪素、窒化珪素、酸化窒化珪素のいずれか一種の材料、或いはこれらの積層膜からなる無機材料であることを特徴としている。

#### 【0127】

次いで、必要でない基板の分断を行う。多面取りの場合、それぞれのパネルを分断する。また、1面取りの場合、予めカットされている対向基板を貼り合わせることによって、分断工程を省略することもできる。

#### 【0128】

そして、異方性導電体層45を介し、公知の技術を用いてFPC46を貼りつける。以上の工程で液晶モジュールが完成する。(図6(E))また、必要があれば光学フィルムを貼り付ける。透過型の液晶表示装置とする場合、偏光板は、アクティブマトリクス基板と対向基板の両方に貼り付ける。10

#### 【0129】

以上示したように、本実施例では、活性層となるセミアモルファスシリコン膜をプラズマCVD法で成膜温度300°C、成膜速度5nm/min~20nm/minを実現し、低温、且つ、短時間で成膜することによりコストの低減、および工程時間の短縮を図ることができる。また、凸状部(ピラー)43を用いてフォトマスクを利用した光露光工程を削減することにより、工程を単純化するとともに、工程時間を短縮することができる。また、液滴吐出法を用いて基板上に直接的に各種のパターンを形成することにより、1辺が1000mmを超える第5世代以降のガラス基板を用いても、容易に液晶表示パネルを製造することができる。20

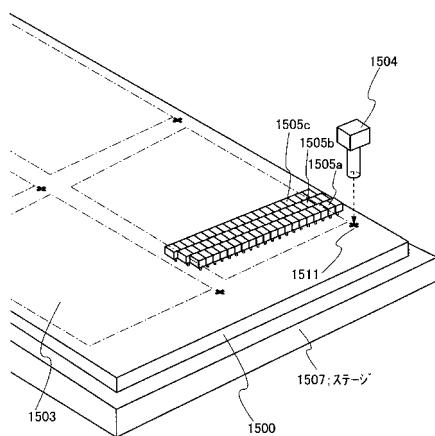

#### 【0130】

走査方向に対して3列とし、大型基板に対応させた液滴吐出装置(代表的にはインクジェット装置)の一例を図8に示す。図8において、1500は大面積基板、1504は撮像手段、1507はステージ、1511はマーカー、1503は1つのパネルが形成される領域を示している。1つのパネルの幅と同じ幅のヘッド1505a、1505b、1505cを備え、このヘッドをジグザグまたは往復させたりして適宜、材料層のパターンを形成する。

#### 【0131】

個々のヘッド1505a、1505b、1505cは制御手段(図示しない)に接続され、それがコンピュータ(図示しない)で制御することにより予めプログラミングされたパターンを描画することができる。描画するタイミングは、例えば、大面積基板1500上に形成されたマーカー1511を基準に行えば良い。或いは、大面積基板1500の縁を基準にして基準点を確定させても良い。これをCCDなどの撮像手段1504で検出し、画像処理手段(図示しない)にてデジタル信号に変換したものをコンピュータで認識して制御信号を発生させて制御手段に送る。勿論、大面積基板1500上に形成されるべきパターンの情報は記憶媒体(図示しない)に格納されたものであり、この情報を基にして制御手段に制御信号を送り、個々のヘッド1505a、1505b、1505cを個別に制御することができる。30

#### 【0132】

図8において、走査方向に対して3列としたヘッド1505a、1505b、1505cはそれぞれ異なる材料層を形成することを可能としてもよいし、同一材料を吐出してもよい。3つのヘッドで同一材料を吐出して層間絶縁膜をパターン形成する場合にはスループットが向上する。

#### 【0133】

なお、図8に示す装置は、ヘッド部を固定し、大面積基板1500を移動させて走査させることも、大面積基板1500を固定し、基板1500を固定させて走査させることも可能である。

#### 【0134】

また、本実施例では、フォトマスクを利用した光露光工程を用いていない工程を示した

10

20

30

40

50

が、特に限定されず、一部のパターニングをフォトマスクを利用した光露光工程により行つてもよい。

**【実施例 2】**

**【0135】**

本実施例では、チャネルエッチ型の TFT を用いたアクティブマトリクス型液晶表示装置の作製例を示す。なお、図 9 は本実施例の作製工程の断面を示している。

**【0136】**

まず、実施例 1 と同様に、基板 410 上に下地膜 411、金属配線 412、端子部に伸びる配線 440 を形成し、さらにゲート絶縁膜 413 を形成する。

**【0137】**

次いで、半導体膜 414a、n 型の半導体膜 417 を積層形成する。半導体膜 414a は、実施の形態 1 または実施の形態 2 に示した成膜方法で得られるセミアモルファス半導体膜を用いる。また、n 型の半導体膜 417 は、シランガスとフォスフィンガスを用いた P C V D 法で形成すれば良く、アモルファス半導体膜、或いはセミアモルファス半導体膜で形成することができる。なお、P C V D 法を用いてゲート絶縁膜 413、半導体膜 414a、n 型の半導体膜 417 を大気にさらすことなく連続的に成膜することも可能である。大気に曝さないようにすることで不純物の混入を防止できる。

**【0138】**

次いで、半導体層をパターニングするためのマスク 415 を液滴吐出法で形成する。（図 9 (A)）マスク 415 は、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

**【0139】**

次いで、マスク 415 で覆われた領域以外の半導体膜 414a および n 型の半導体膜 417 をドライエッチングまたはウェットエッチングにより除去して活性層となる半導体層を形成する。

**【0140】**

次いで、液滴吐出法により、カバレッジを良好にするため、半導体層のエッジをカバーする絶縁材料または導電材料からなる層 416 を形成する。

**【0141】**

次いで、液滴吐出法により、導電性材料 (Ag (銀)、Au (金)、Cu (銅)、W (タンゲステン)、Al (アルミニウム) 等) を含む組成物を選択的に吐出して、ソース配線またはドレイン配線 418a、418b を形成する。

**【0142】**

次いで、ゲート電極である金属配線 412 とゲート絶縁膜 413 を介して重なる半導体層の一部を除去するためのマスクを液滴吐出法で形成する。エッチングにより、金属配線 412 とゲート絶縁膜 413 を介して重なる一部が除去された半導体層 414b を形成すると同時に n 型の半導体膜 419a、419b を形成する。この段階でチャネルエッチ型の TFT が完成する。

**【0143】**

次いで、シャドーマスクを用いて端子部以外をレジストなどの樹脂で覆い、端子部においては、接続配線 441 をマスクとしたゲート絶縁膜 413 のエッチングを行って配線 440 の一部を露呈させる。（図 9 (B)）また、シャドーマスクに代えてスクリーン印刷法によりレジストマスクを形成してエッチングマスクとしてもよい。

**【0144】**

以降の工程は、実施例 1 と同様に行えばよい。本実施例は実施例 1 と TFT 構造が異なるだけで他の構成は同一である。

**【0145】**

次いで、端子部に伸びる配線 440 と接続配線 441 との接続を行うための導電物 44

10

20

30

40

50

2を形成する。導電物442は印刷法または液滴吐出法により形成すればよい。

**【0146】**

次いで、ソース配線またはドレイン配線418a上の一<sup>10</sup>部に導電性部材からなる凸状部(ピラー)420を形成する。また、同様に接続配線441上にも凸状部(ピラー)443を形成する。

**【0147】**

次いで、塗布法による平坦な層間絶縁膜421を形成する。(図4(C))また、層間絶縁膜421は、塗布法に限定されず、気相成長法やスパッタリング法により形成された酸化珪素膜などの無機絶縁膜も用いることができる。また、保護膜として窒化珪素膜をPCVD法やスパッタ法で形成した後、塗布法による平坦な絶縁膜を積層してもよい。

**【0148】**

また、液滴吐出法により層間絶縁膜421を形成してもよい。また、凸状部(ピラー)420、443を本焼成する前に層間絶縁膜421を液滴吐出法により形成し、同時に本焼成してもよい。

**【0149】**

次いで、全面エッチバックにより凸状部(ピラー)420、443上の層間絶縁膜を除去して凸状部(ピラー)420、443を露出させる。また、他の方法としては、化学的機械研磨(CMP)により、層間絶縁膜を研削し、その後、層間絶縁膜を全面エッチバックすることにより、凸状部(ピラー)420、443を露出させることができる。

**【0150】**

次いで、凸状部(ピラー)420と接する画素電極423を形成する。(図9(D))なお、同様に凸状部(ピラー)443と接する端子電極444も形成する。透過型の液晶表示パネルを作製する場合には、液滴吐出法または印刷法によりインジウム錫酸化物(ITO)、酸化珪素を含むインジウム錡酸化物(ITSO)、酸化亜鉛(ZnO)、酸化スズ(SnO<sub>2</sub>)などを含む組成物からなる所定のパターンを形成し、焼成して画素電極423および端子電極444を形成しても良い。また、反射型の液晶表示パネルを作製する場合には、画素電極423および端子電極444を液滴吐出法によりAg(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いて形成することができる。

**【0151】**

以上の工程により、基板410上にボトムゲート型(逆スタガ型ともいう。)のTFTおよび画素電極が形成された液晶表示パネル用のTFT基板が完成する。

**【0152】**

次いで、画素電極423を覆うように、配向膜424aを形成する。なお、配向膜424aは、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いればよい。その後、配向膜424aの表面にラビング処理を行う。

**【0153】**

そして、対向基板425には、着色層426a、遮光層(ブラックマトリクス)426b、及びオーバーコート層427からなるカラーフィルタを設け、さらに透明電極からなる対向電極と、その上に配向膜424bを形成する。そして、閉パターンであるシール材(図示しない)を液滴吐出法により画素部と重なる領域を囲むように形成する。本実施例では液晶を滴下するため、閉パターンのシール材を描画する例を示すが、開口部を有するシールパターンを設け、TFT基板を貼りあわせた後に毛細管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いてもよい。

**【0154】**

次いで、気泡が入らないように減圧下で液晶の滴下を行い、両方の基板を貼り合わせる。閉ループのシールパターン内に液晶を1回若しくは複数回滴下する。

**【0155】**

なお、一対の基板間隔は、球状のスペーサを散布したり、樹脂からなる柱状のスペーサを形成したり、シール材にフィラーを含ませることによって維持すればよい。

10

20

30

40

50

**【0156】**

次いで、必要でない基板の分断を行う。多面取りの場合、それぞれのパネルを分断する。また、1面取りの場合、予めカットされている対向基板を貼り合わせることによって、分断工程を省略することもできる。

**【0157】**

そして、異方性導電体層445を介し、公知の技術を用いてFPC446を貼りつける。以上の工程で液晶モジュールが完成する。(図9(E))また、必要があれば光学フィルムを貼り付ける。透過型の液晶表示装置とする場合、偏光板は、アクティブマトリクス基板と対向基板の両方に貼り付ける。

**【0158】**

また、本実施例では、フォトマスクを利用した光露光工程を用いていない工程を示したが、特に限定されず、一部のパターニングをフォトマスクを利用した光露光工程により行ってもよい。例えば、チャネル形成領域のサイズが決定する半導体層の一部を除去するパターニング工程でフォトマスクを利用すると、精密にサイズを決定することができる。

**【0159】**

本実施例では、実施の形態1、実施の形態2、または実施例1と自由に組み合わせることができる。

**【実施例3】****【0160】**

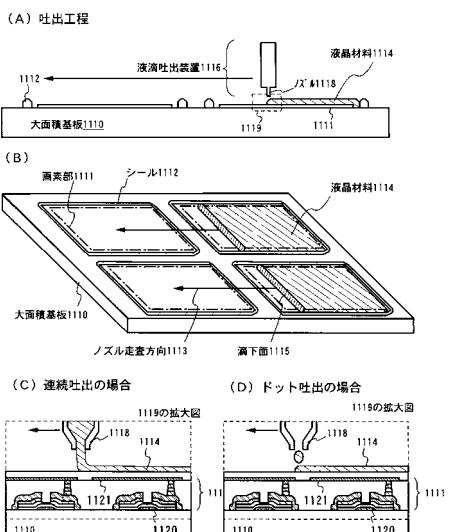

本実施例では、液晶滴下に液滴吐出法を用いる例を示す。本実施例では、大面積基板を用い、パネル4枚取りの作製例を図10に示す。

**【0161】**

図10(A)は、ディスペンサ(またはインクジェット)による液晶層形成の途中の断面図を示しており、シール材112で囲まれた画素部111を覆うように液晶材料114を液滴吐出装置116のノズル118から吐出、噴射、または滴下させている。液滴吐出装置116は、図10(A)中の矢印方向に移動させる。なお、ここではノズル118を移動させた例を示したが、ノズルを固定し、基板を移動させることによって液晶層を形成してもよい。

**【0162】**

また、図10(B)には斜視図を示している。シール1112で囲まれた領域のみに選択的に液晶材料1114を吐出、噴射、または滴下させ、ノズル走査方向1113に合わせて滴下面1115が移動している様子を示している。

**【0163】**

また、図10(A)の点線で囲まれた部分1119を拡大した断面図が図10(C)、図10(D)である。液晶材料の粘性が高い場合は、連続的に吐出され、図10(C)のように繋がったまま付着される。一方、液晶材料の粘性が低い場合には、間欠的に吐出され、図10(D)に示すように液滴が滴下される。

**【0164】**

なお、図10(C)中、1120は逆スタガ型TFT、1121は画素電極をそれぞれ指している。画素部1111は、マトリクス状に配置された画素電極と、該画素電極と接続されているスイッチング素子、ここでは逆スタガ型TFTと、保持容量(図示しない)とで構成されている。

**【0165】**

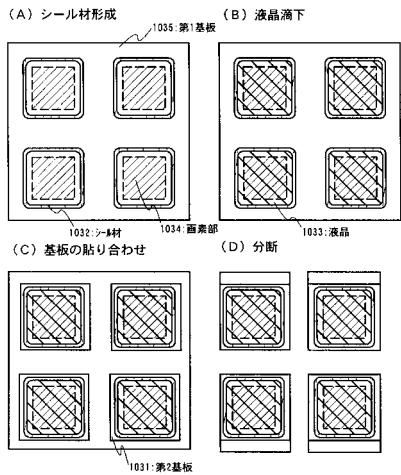

ここで、図11(A)～図11(D)を用いて、パネル作製の流れを以下に説明する。

**【0166】**

まず、絶縁表面に画素部1034が形成された第1基板1035を用意する。第1基板1035は、予め、配向膜の形成、ラビング処理、球状スペーサ散布、或いは柱状スペーサ形成、またはカラーフィルタの形成などを行っておく。次いで、図11(A)に示すように、不活性気体雰囲気または減圧下で第1基板1035上にディスペンサ装置またはインクジェット装置でシール材1032を所定の位置(画素部1034を囲むパターン)に

10

20

30

40

50

形成する。半透明なシール材 1032 としてはフィラー（直径 6 μm ~ 24 μm）を含み、且つ、粘度 40 ~ 400 Pa·s のものを用いる。なお、後に接する液晶に溶解しないシール材料を選択することが好ましい。シール材としては、アクリル系光硬化樹脂やアクリル系熱硬化樹脂を用いればよい。また、簡単なシールパターンであるのでシール材 32 は、印刷法で形成することもできる。

#### 【0167】

次いで、シール材 1032 に囲まれた領域に液晶 1033 をインクジェット法により滴下する。（図 11 (B)）液晶 1033 としては、インクジェット法によって吐出可能な粘度を有する公知の液晶材料を用いればよい。また、液晶材料は温度を調節することによって粘度を設定することができるため、インクジェット法に適している。インクジェット法により無駄なく必要な量だけの液晶 1033 をシール材 1032 に囲まれた領域に保持することができる。10

#### 【0168】

次いで、画素部 1034 が設けられた第 1 基板 1035 と、対向電極や配向膜が設けられた第 2 基板 1031 とを気泡が入らないように減圧下で貼りあわせる。（図 11 (C)）ここでは、貼りあわせると同時に紫外線照射や熱処理を行って、シール材 1032 を硬化させる。なお、紫外線照射に加えて、熱処理を行ってもよい。

#### 【0169】

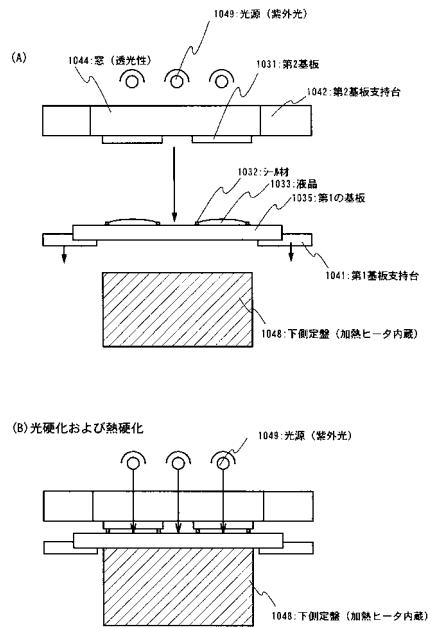

また、図 12 に貼り合わせ時または貼り合わせ後に紫外線照射や熱処理が可能な貼り合わせ装置の例を示す。20

#### 【0170】

図 12 中、1041 は第 1 基板支持台、1042 は第 2 基板支持台、1044 は窓、1048 は下側定盤、1049 は光源である。なお、図 12 において、図 11 と対応する部分は同一の符号を用いている。

#### 【0171】

下側定盤 1048 は加熱ヒータが内蔵されており、シール材を硬化させる。また、第 2 基板支持台には窓 1044 が設けられており、光源 1049 からの紫外光などを通過させるようになっている。ここでは図示していないが窓 1044 を通して基板の位置アライメントを行う。また、対向基板となる第 2 の基板 1031 は予め、所望のサイズに切断しておき、台 1042 に真空チャックなどで固定しておく。図 12 (A) は貼り合わせ前の状態を示している。30

#### 【0172】

貼り合わせ時には、第 1 基板支持台と第 2 基板支持台とを下降させた後、圧力をかけて第 1 基板 1035 と第 2 基板 1031 を貼り合わせ、そのまま紫外光を照射することによって硬化させる。貼り合わせ後の状態を図 12 (B) に示す。

#### 【0173】

次いで、スクライバー装置、ブレイカー装置、ロールカッターなどの切断装置を用いて第 1 基板 1035 を切断する。（図 11 (D)）こうして、1 枚の基板から 4 つのパネルを作製することができる。そして、公知の技術を用いて FPC を貼りつける。40

#### 【0174】

なお、第 1 基板 1035、第 2 基板 1034 としてはガラス基板、またはプラスチック基板を用いることができる。

#### 【0175】

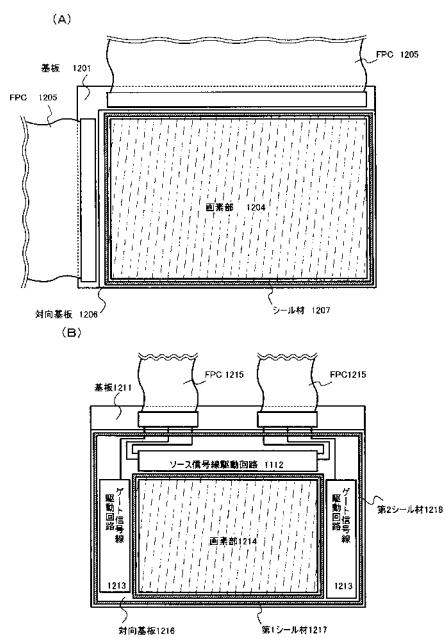

以上の工程によって得られた液晶モジュールの上面図を図 13 (A) に示すとともに、他の液晶モジュールの上面図の例を図 13 (B) に示す。

#### 【0176】

図 13 (A) 中、1201 は、アクティブマトリクス基板、1206 は対向基板、1204 は画素部、1207 はシール材、1205 は FPC である。なお、液晶を液滴吐出法により吐出させ、減圧下で一対の基板 1201、1206 をシール材 1207 で貼り合わせている。50

## 【0177】

セミアモルファスシリコン膜からなる活性層を有するTFTを用いた場合、駆動回路の一部を作製することもでき、図13(B)のような液晶モジュールを作製することができる。なお、セミアモルファスシリコン膜からなる活性層を有するTFTで形成できない駆動回路は、ICチップ(図示しない)を実装する。

## 【0178】

図13(B)中、1211は、アクティブマトリクス基板、1216は対向基板、1212はソース信号線駆動回路、1213はゲート信号線駆動回路、1214は画素部、1217は第1シール材、1215はFPCである。なお、液晶を液滴吐出法により吐出させ、一対の基板1211、1216を第1シール材1217および第2シール材で貼り合わせている。駆動回路部1212、1213には液晶は不要であるため、画素部1214のみに液晶を保持させており、第2シール材1218はパネル全体の補強のために設けられている。

10

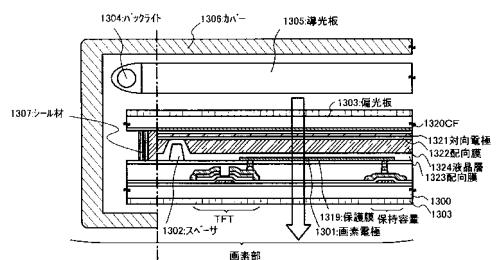

## 【0179】

また、得られた液晶モジュールにバックライト1304、導光板1305を設け、カバー1306で覆えば、図14にその断面図の一部を示したようなアクティブマトリクス型液晶表示装置(透過型)が完成する。なお、カバーと液晶モジュールは接着剤や有機樹脂を用いて固定する。また、透過型であるので偏光板1303は、アクティブマトリクス基板と対向基板の両方に貼り付ける。

20

## 【0180】

なお、図14中、1300は基板、1301は画素電極、1302は柱状スペーサ、1307はシール材、1320は着色層、遮光層が各画素に対応して配置されたカラーフィルタ、1321は対向電極、1322、1323は配向膜、1324は液晶層、1319は保護膜である。

## 【0181】

また、本実施例は、実施の形態1、実施の形態2、実施例1乃至2のいずれか一と自由に組み合わせることができる。

## 【実施例4】

## 【0182】

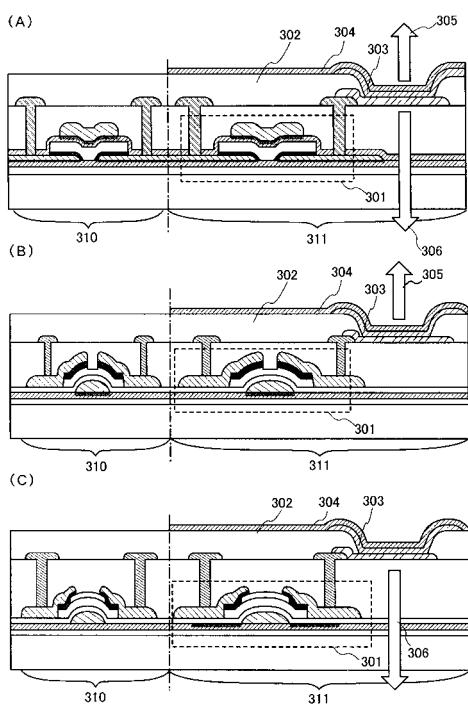

本実施例では、薄膜トランジスタを有する発光装置について図15に説明する。

30

## 【0183】

図15(A)に示すように、駆動回路部310及び画素部311に、セミアモルファスシリコン膜を活性層とするトップゲート型のNチャネル型TFTを形成する。特に、画素部311に形成された発光素子と接続されるNチャネル型TFTは、駆動用TFT301と表記する。駆動用TFT301が有する電極(第1の電極と表記する)の端部を覆うように、土手や隔壁と呼ばれる絶縁膜302を形成する。絶縁膜302には、無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコンなど)、感光性又は非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン)、珪素(Si)と酸素(O)との結合で骨格構造が構成され、置換基に少なくとも水素を含む、又は置換基にフッ素、アルキル基、又は芳香族炭化水素のうち少なくとも1種を有する材料、いわゆるシロキサン、及びそれらの積層構造を用いることができる。有機材料として、ポジ型感光性有機樹脂又はネガ型感光性有機樹脂を用いることができる。

40

## 【0184】

第1の電極上において、絶縁膜302に開口部を形成する。開口部には、電界発光層303が設けられ、電界発光層及び絶縁膜302を覆うように発光素子の第2の電極304が設けられる。

## 【0185】

なお電界発光層が形成する分子励起子の種類としては一重項励起状態と三重項励起状態が可能であり、基底状態は通常一重項状態であるため、一重項励起状態からの発光は蛍光、三重項励起状態からの発光は燐光と呼ばれる。電界発光層からの発光とは、どちらの励

50

起状態が寄与する場合も含まれる。更には、蛍光と燐光を組み合わせて用いてもよく、各RGBの発光特性（発光輝度や寿命等）により選択することができる。

#### 【0186】

電界発光層303は、第1の電極215側から順に、HIL（ホール注入層）、HTL（ホール輸送層）、EML（発光層）、ETL（電子輸送層）、EIL（電子注入層）の順に積層されている。なお電界発光層は、積層構造以外に単層構造、又は混合構造をとることができる。

#### 【0187】

また、電界発光層303として、フルカラー表示とする場合、赤色（R）、緑色（G）、青色（B）の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法、又はインクジェット法などによって選択的に形成すればよい。

#### 【0188】

具体的には、HILとしてCuPcやPEDOT、HTLとして-NPD、ETLとしてBCPやAlq<sub>3</sub>、EILとしてBCP:LiやCaF<sub>2</sub>をそれぞれ用いる。また例えばEMLは、R、G、Bのそれぞれの発光色に対応したドーパント（Rの場合DCM等、Gの場合DMQD等）をドープしたAlq<sub>3</sub>を用いればよい。なお、電界発光層は上記積層構造の材料に限定されない。例えば、CuPcやPEDOTの代わりに酸化モリブデン（MoO<sub>x</sub>:x=2~3）等の酸化物と-NPDやルブレンを共蒸着して形成し、ホール注入性を向上させることもできる。このような材料は、有機材料（低分子又は高分子を含む）、又は有機材料と無機材料の複合材料を用いることができる。

10

20

#### 【0189】

また白色の発光を示す電界発光層を形成する場合、カラーフィルター、又はカラーフィルター及び色変換層などを別途設けることによってフルカラー表示を行うことができる。カラーフィルターや色変換層は、例えば第2の基板（封止基板）に設けた後、張り合わせればよい。カラーフィルターや色変換層はインクジェット法により形成することができる。勿論、白色以外の発光を示す電界発光層を形成して単色の発光装置を形成してもよい。また単色表示が可能なエリアカラータイプの表示装置を形成してもよい。

#### 【0190】

また第1の電極及び第2の電極304は仕事関数を考慮して材料を選択する必要がある。但し第1の電極及び第2の電極は、画素構成によりいずれも陽極、又は陰極となりうる。本実施例では、駆動用TFTの極性がNチャネル型であるため、第1の電極を陰極、第2の電極を陽極とすると好ましい。また駆動用TFTの極性がpチャネル型である場合、第1の電極を陽極、第2の電極を陰極とするとよい。

30

#### 【0191】

特に本実施例では、駆動用TFTの極性がNチャネル型であるため、電子の移動方向を考慮すると、第1の電極を陰極、EIL（電子注入層）、ETL（電子輸送層）、EML（発光層）、HTL（ホール輸送層）、HIL（ホール注入層）、第2の電極を陽極とすると好ましい。

#### 【0192】

その後、窒素を含むパッシベーション膜又は DLC 等をスパッタリング法や CVD 法により形成するとよい。その結果、水分や酸素の侵入を防止することができる。また第1の電極、第2の電極、その他の電極により、表示手段の側面を覆って酸素や水分の侵入を防ぐことができる。次いで、封止基板を張り合わせる。封止基板により形成される空間には、窒素を封入したり、乾燥剤を配置してもよい。また透光性を有し、吸水性の高い樹脂を充填してもよい。

40

#### 【0193】

またコントラストを高めるため、偏光板又は円偏光板を設けてもよい。例えば、表示面の一面又は両面に偏光板、若しくは円偏光板を設けることができる。

#### 【0194】

このように形成された構造を有する発光装置において、本実施例では第1の電極及び第

50

2の電極に透光性を有する材料（ITO若しくはITSO）を用いる。そのため、信号線から入力されるビデオ信号に応じた輝度で電界発光層から光が両矢印方向305、306に出射する。

#### 【0195】

また、図15(A)とは一部構成が異なる他の構造例を図15(B)に示す。

#### 【0196】

図15(B)に示す発光装置の構造は、駆動回路部310及び画素部311に、チャネルエッチ型のNチャネル型TFTを形成する。図15(A)と同様に、画素部311に形成された発光素子と接続されるNチャネル型TFTは、駆動用TFT301と表記する。第1の電極は非透光性、好ましくは反射性の高い導電膜とし、第2の電極304は透光性を有する導電膜とする点が図15(A)と異なる。そのため、光の射出方向305は封止基板側のみである。10

#### 【0197】

また、図15(A)とは一部構成が異なる他の構造例を図15(C)に示す。

#### 【0198】

図15(C)に示す発光装置の構造は、駆動回路部310及び画素部311に、チャネル保護型のNチャネル型TFTを形成する。図15(A)と同様に、画素部311に形成された発光素子と接続されるNチャネル型TFTは、駆動用TFT301と表記する。第1の電極は透光性を有する導電膜とし、第2の電極304は非透光性、好ましくは反射性の高い導電膜とする点が図15(A)と異なる。そのため、光の射出方向306が基板側のみである。20

#### 【0199】

以上、各薄膜トランジスタを用いて発光装置の構造について説明したが、薄膜トランジスタの構成と、発光装置の構造はどのように組み合わせてもよい。

#### 【0200】

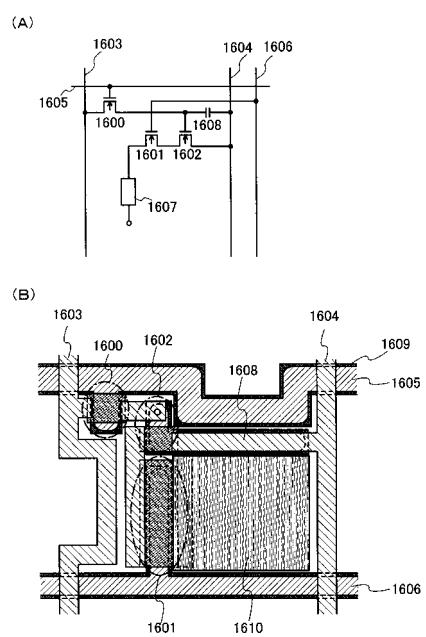

また、発光装置の等価回路図及び上面図を図16に説明する。TFTはゲート、ソース、ドレインの3端子を有するが、ソース端子（ソース電極）、ドレイン端子（ドレイン電極）に関しては、トランジスタの構造上、明確に区別が出来ない。よって、素子間の接続について説明する際は、ソース電極、ドレイン電極のうち一方を第1の電極、他方を第2の電極と表記する。30

#### 【0201】

図16(A)には、発光装置の画素部の等価回路図を示す。一画素は、スイッチング用のTFT（スイッチ用TFT）1600、駆動用のTFT（駆動用TFT）1601、電流制御用のTFT（電流制御用TFT）1602を有し、これらTFTはNチャネル型を有する。スイッチング用TFT1601の一方の電極及びゲート電極は、それぞれ信号線1603及び走査線1605に接続されている。電流制御用TFT1602の一方の電極は第1の電源線1604に接続され、ゲート電極はスイッチング用TFTの他方の電極に接続されている。

#### 【0202】

容量素子1608は、電流制御用TFTのゲート・ソース間の電圧を保持するように設ければよい。本実施例において、例えば第1の電源線の電位を低電位とし、発光素子を高電位とすると、電流制御用TFTはNチャネル型を有するため、ソース電極と第1の電源線とが接続する。そのため、容量素子は電流制御用TFTのゲート電極と、ソース電極、つまり第1の電源線との間に設けることができる。なお、スイッチング用TFT、駆動用TFT、又は電流制御用TFTのゲート容量が大きく、各TFTからのリーキ電流が許容範囲である場合、容量素子1608は設ける必要はない。40

#### 【0203】

駆動用TFT1601の一方の電極は、電流制御用TFTの他方の電極に接続され、ゲート電極は第2の電源線1606に接続されている。第2の電源線1606は、固定電位を有する。そのため、駆動用TFTのゲート電位を固定電位とすることができる、寄生容量や50

配線容量によるゲート・ソース間の電圧  $V_{g_s}$  が変化しないように動作させることができる。

#### 【0204】

そして駆動用 TFT の他方の電極に発光素子 1607 が接続されている。本実施の形態において、例えば第 1 の電源線の電位を低電位とし、発光素子を高電位とすると、駆動用 TFT のドレイン電極に発光素子の陰極が接続される。そのため、上述したように、陰極、電界発光層、陽極の順に積層すると好ましい。このように、セミアモルファス半導体膜を有する TFT であって、N チャネル型を有する場合、TFT のドレイン電極と陰極とを接続し、EIL、ETL、EML、HTL、HIL、陽極の順に積層すると好適である。

#### 【0205】

以下に、このような画素回路の動作について説明する。

#### 【0206】

走査線 1605 が選択されるとき、スイッチング用 TFT がオンとなると、容量素子 1608 に電荷が蓄積されはじめる。容量素子 1608 の電荷は、電流制御用 TFT のゲート・ソース間電圧と等しくなるまで蓄積される。等しくなると、電流制御用 TFT がオンとなり、直列に接続された駆動用 TFT がオンとなる。このとき、駆動用 TFT のゲート電位が固定電位となっているため、発光素子へ寄生容量や配線容量によらない一定のゲート・ソース間電圧  $V_{g_s}$  を印加する、つまり一定のゲート・ソース間電圧  $V_{g_s}$  分の電流を供給することができる。

#### 【0207】

このように、発光素子は電流駆動型の素子であるため、画素内の TFT の特性バラツキ、特に  $V_{th}$  バラツキが少ない場合アナログ駆動を用いることが好適である。本実施の形態のように、非晶質半導体膜を有する TFT は、特性バラツキが低いため、アナログ駆動を用いることができる。一方デジタル駆動でも、駆動用 TFT を飽和領域 ( $|V_{g_s} - V_{th}| < |V_{ds}|$  を満たす領域) で動作させることで、一定の電流値を発光素子に供給することができる。

#### 【0208】

図 16 (B) には、上記等価回路を有する発光装置の画素部における上面図の一例を示す。

#### 【0209】

まずインクジェット法により、各 TFT のゲート電極、走査線、及び第 2 の電源線を同一層で形成する。このとき撥油性を高めるため、少なくともゲート電極及び走査線を形成する領域の両端に形成されている TiO<sub>2</sub> に、光触媒活性化させる波長の光を照射する照射領域 1609 を形成する。

#### 【0210】

図示しないが、その後ゲート絶縁膜を形成する。

#### 【0211】

そしてゲート絶縁膜上に各 TFT の半導体膜を形成する。本実施例では SiH<sub>4</sub> と F<sub>2</sub> を原料ガスに用いたプラズマ CVD 法により全面にセミアモルファス半導体膜を形成し、マスクを用いてエッチャリングを行い、各 TFT の活性層とする。そして一導電型を有する半導体膜をプラズマ CVD 法により形成し、マスクを用いてエッチャリングを行い、各 TFT のソース領域またはドレイン領域とする。

#### 【0212】

そしてソース電極、ドレイン電極、信号線及び第 1 の電源線を同一層で形成する。ソース電極、ドレイン電極、信号線及び第 1 の電源線は、液滴吐出法、又はスパッタ法等により形成することができる。

#### 【0213】

スイッチング用 TFT の一方の配線と、電流制御用 TFT のゲート電極を接続するために、ゲート絶縁膜にコンタクトホールを形成する。

#### 【0214】

10

20

30

40

50

本実施例において、容量素子 1608 は、ゲート絶縁膜を介して設けられたゲート配線、及びソース・ドレイン配線により形成されている。

【0215】

駆動用 TFT の一方の電極と接続するように発光素子 1607 の電極 1610 を形成する。

【0216】

駆動用 TFT は非晶質半導体膜を有するため、駆動用 TFT のチャネル幅 (W) が広くなるように設計する。

【0217】

このようにして、発光装置の画素部を形成することができる。

10

【0218】

本発明により、低い成膜温度で SiH<sub>4</sub> と F<sub>2</sub> を原料ガスに用いた PCVD 法により得られるセミアモルファス半導体膜を TFT の活性層とすることによって、比較的安価な発光装置を実現できる。

【0219】

本実施例は、実施の形態 1 または実施の形態 2 と自由に組み合わせることができる。

【実施例 5】

【0220】

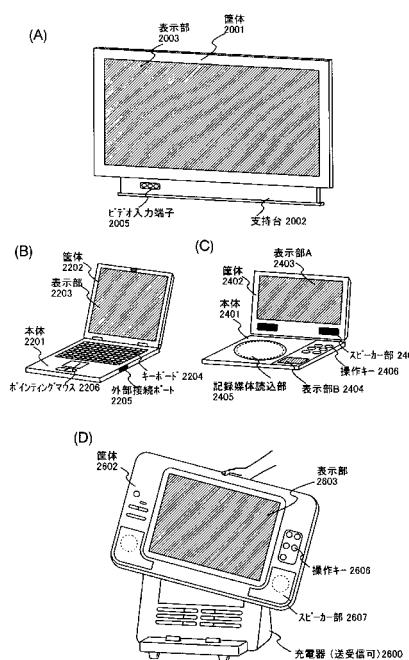

本発明の液晶表示装置、発光装置、及び電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等）、記録媒体を備えた画像再生装置（具体的には Digital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。特に、大型画面を有する大型テレビ等に本発明を用いることが望ましい。それら電子機器の具体例を図 17 に示す。

20

【0221】

図 17 (A) は 22 インチ～50 インチの大画面を有する大型の表示装置であり、筐体 2001、支持台 2002、表示部 2003、ビデオ入力端子 2005 等を含む。なお、表示装置は、パソコン用、TV 放送受信用、双方向 TV 用などの全ての情報表示用表示装置が含まれる。本発明により、1 辺が 1000 mm を超える第 5 世代以降のガラス基板を用いても、低い成膜温度で SiH<sub>4</sub> と F<sub>2</sub> を原料ガスに用いた PCVD 法により得られるセミアモルファス半導体膜を TFT の活性層とすることによって、比較的安価な大型表示装置を実現できる。

30

【0222】

図 17 (B) はノート型パーソナルコンピュータであり、本体 2201、筐体 2202、表示部 2203、キーボード 2204、外部接続ポート 2205、ポインティングマウス 2206 等を含む。本発明により、低い成膜温度で SiH<sub>4</sub> と F<sub>2</sub> を原料ガスに用いた PCVD 法により得られるセミアモルファス半導体膜を TFT の活性層とすることによって、比較的安価なノート型パーソナルコンピュータを実現できる。

40

【0223】

図 17 (C) は記録媒体を備えた携帯型の画像再生装置（具体的には DVD 再生装置）であり、本体 2401、筐体 2402、表示部 A 2403、表示部 B 2404、記録媒体（DVD 等）読み込み部 2405、操作キー 2406、スピーカー部 2407 等を含む。表示部 A 2403 は主として画像情報を表示し、表示部 B 2404 は主として文字情報を表示する。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明により、低い成膜温度で SiH<sub>4</sub> と F<sub>2</sub> を原料ガスに用いた PCVD 法により得られるセミアモルファス半導体膜を TFT の活性層とすることによって、比較的安価な画像再生装置を実現できる。

【0224】

50

図17(D)は、ワイヤレスディスプレイのみを持ち運び可能なTVである。筐体2602にはバッテリー及び信号受信器が内蔵されており、そのバッテリーで表示部2604やスピーカ部2607を駆動させる。バッテリーは充電器2600で繰り返し充電が可能となっている。また、充電器2600は映像信号を送受信することが可能で、その映像信号をディスプレイの信号受信器に送信することができる。筐体2602は操作キー2606によって制御する。また、図17(D)に示す装置は、操作キー2606を操作することによって、筐体2602から充電器2600に信号を送ることも可能であるため映像音声双方向通信装置とも言える。また、操作キー2606を操作することによって、筐体2602から充電器2600に信号を送り、さらに充電器2600が送信できる信号を他の電子機器に受信させることによって、他の電子機器の通信制御も可能であり、汎用遠隔制御装置とも言える。本発明により、低い成膜温度でSiH<sub>4</sub>とF<sub>2</sub>を原料ガスに用いたP C V D法により得られるセミアモルファス半導体膜をTFTの活性層とすることによって、比較的大型(22インチ～50インチ)の持ち運び可能なTVを安価な製造プロセスで提供できる。

#### 【0225】

以上の様に、本発明を実施して得た液晶表示装置や発光装置は、あらゆる電子機器の表示部として用いても良い。

#### 【0226】

また、本実施例は、実施の形態1、実施の形態2、実施例1乃至4のいずれか一と自由に組み合わせることができる。

#### 【産業上の利用可能性】

#### 【0227】

本発明により、結晶構造を含む半導体膜の形成に必要なトータルエネルギーを低減し、生産工程における消費エネルギーを大幅に抑制することができる。

#### 【0228】

また、下地膜として耐熱性の低い材料で形成される膜、代表的にはアクリルなどの有機樹脂、アルミニウム配線等を用いた場合にも直接、プラズマCVD法を用いて結晶構造を含む半導体膜を形成することを実現可能とする。

#### 【図面の簡単な説明】

#### 【0229】

【図1】プラズマCVD装置を示す断面図である。

【図2】ラマンスペクトルデータを示すグラフである。

【図3】プラズマCVD装置を示す断面図である。(実施の形態2)

【図4】プラズマCVD装置を示す斜視図である。

【図5】プラズマCVD装置を示す上面図である。

【図6】液晶表示装置の作製工程の断面図である。(実施例1)

【図7】液晶表示装置の画素上面図を示す図である。(実施例1)

【図8】液滴吐出装置の斜視図である。(実施例1)

【図9】液晶表示装置の作製工程の断面図である。(実施例2)

【図10】液晶滴下を液滴吐出法で行う斜視図および断面図である。

【図11】プロセス上面図を示す図。

【図12】貼りあわせ装置および貼りあわせ工程を示す断面図。

【図13】液晶モジュールの上面図。

【図14】アクティブマトリクス型液晶表示装置を示す断面図。

【図15】発光装置の断面構造を示す図。(実施例4)

【図16】発光装置の画素における回路図および画素上面図を示す図。(実施例4)

【図17】電子機器の一例を示す図。

#### 【符号の説明】

#### 【0230】

105：高周波電源

123：プラズマ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

審査官 山本 雄一

(56)参考文献 特開2003-318401(JP,A)

特開平06-168883(JP,A)

特開平02-077116(JP,A)

特開平02-272774(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/205

H01L 21/336

H01L 29/786

C23C 16/00 - 16/56