(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3934417号

(P3934417)

(45) 発行日 平成19年6月20日(2007.6.20)

(24) 登録日 平成19年3月30日(2007.3.30)

(51) Int.C1.

F 1

|             |           |            |   |

|-------------|-----------|------------|---|

| HO1L 21/822 | (2006.01) | HO1L 27/04 | C |

| HO1L 27/04  | (2006.01) | HO1L 27/04 | H |

| HO1P 3/02   | (2006.01) | HO1P 3/02  |   |

請求項の数 2 (全 6 頁)

(21) 出願番号

特願2001-397488 (P2001-397488)

(22) 出願日

平成13年12月27日 (2001.12.27)

(65) 公開番号

特開2003-197758 (P2003-197758A)

(43) 公開日

平成15年7月11日 (2003.7.11)

審査請求日

平成16年7月26日 (2004.7.26)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100078765

弁理士 波多野 久

(74) 代理人 100078802

弁理士 関口 俊三

(72) 発明者 高須 英樹

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 小向工場内

審査官 大嶋 洋一

最終頁に続く

(54) 【発明の名称】マイクロ波集積回路

(57) 【特許請求の範囲】

【請求項1】

コプレーナ構造で構成されたインタデジタル型キャパシタを備えたマイクロ波集積回路において、前記インタデジタル型キャパシタの対向するコプレーナ電極の外側の接地導体間に、前記コプレーナ電極を跨ぐ橋状接地導体を設置し、この橋状接地導体でコプレーナ電極を覆う様にしたことを特徴とするマイクロ波集積回路。

【請求項2】

前記インタデジタル型キャパシタが有する前記橋状接地導体は対向するコプレーナ電極の外側の接地導体間を半筒状に形成することを特徴とする請求項1に記載のマイクロ波集積回路。

10

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、マイクロ波集積回路に係り、特にコプレーナ構造で構成されたインタデジタル型キャパシタにおいて、コプレーナ電極上方を橋状接地導体で覆うマイクロ波集積回路に関する。

【0002】

【従来の技術】

マイクロ波集積回路はマイクロ波の伝送特性からマイクロ波信号の一部が外部に放射してしまう。このため、外部に放射したマイクロ波信号がマイクロ波集積回路と近接する外部

20

回路と漏話（クロストーク）を起こすことがある。この外部回路から見れば、放射されたマイクロ波信号はノイズである。このノイズが回路特性に影響を与えることがある。また、これとは逆に近接する外部回路からのノイズがマイクロ波集積回路の回路特性に影響を与えることもある。そこで、マイクロ波信号の一部が近接する外部回路とクロストークすることのない様に対策を施す。一般的には、マイクロ波集積回路全体に銅板等の金属板のシールドが設けられる。

【0003】

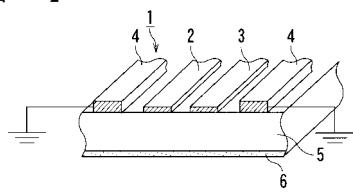

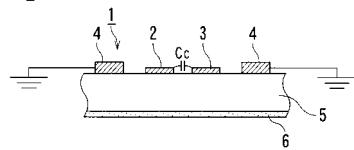

図4にマイクロ波集積回路に使用されるコプレーナ構造で構成されたインタデジタル型キャパシタ1を示す。また、このインタデジタル型キャパシタ1の等価回路を図5に示す。尚、図5中のC<sub>c</sub> (C<sub>c</sub> > 0)は、結合電荷容量値を示す。

10

【0004】

図4によれば、マイクロ波集積回路に備えられるインタデジタル型キャパシタ1は、コプレーナ電極2, 3と、接地導体4とを誘電体基板5の上面に備える。また、誘電体基板5の下面には下部接地導体6を備えている。インタデジタル型キャパシタ1のコプレーナ電極2, 3は互いに対面させて設けることで、キャパシタを形成している。コプレーナ電極2, 3がキャパシタを形成している外側には接地導体4が存在する。

【0005】

一方、図5によればインタデジタル型キャパシタ1の電荷容量値は、コプレーナ電極2とコプレーナ電極3との間のC<sub>c</sub>、即ち、結合電荷容量値のみで決定される。

20

【0006】

【発明が解決しようとする課題】

しかしながら、マイクロ波集積回路の小型化および集積化が進み、マイクロ波集積回路と外部回路とがシールドで必ずしも遮蔽されるとは限らない状況がある。この場合、マイクロ波集積回路に用いられるインタデジタル型キャパシタ1は、インタデジタル型キャパシタ1のコプレーナ電極2, 3と外部回路とがシールド無しで近接する。従って、インタデジタル型キャパシタ1はコプレーナ電極2, 3間の結合電荷容量の他にも外部回路の部品との間にも結合電荷容量を持ち得る。つまり、マイクロ波集積回路は外部回路と結合し易く、クロストークを生じ易い。

【0007】

また、従来のインタデジタル型キャパシタは電荷容量値が少なく、マイクロ集積回路設計における回路設計の自由度を狭めている。

30

【0008】

本発明は、上述した事情を考慮してなされたもので、マイクロ波集積回路と近接する外部回路とのクロストークを減少させると共に、マイクロ波集積回路に備えられるインタデジタル型キャパシタの電荷容量値を増加させたマイクロ波集積回路を提供することを目的とする。

【0009】

【課題を解決するための手段】

本発明に係るマイクロ波集積回路は上述した課題を解決するため、請求項1に記載した様に、コプレーナ構造で構成されたインタデジタル型キャパシタを備えたマイクロ波集積回路において、前記インタデジタル型キャパシタの対向するコプレーナ電極の外側の接地導体間に、前記コプレーナ電極を跨ぐ橋状接地導体を設置し、この橋状接地導体でコプレーナ電極を覆う様にしたことを特徴とする。

40

【0010】

上述した課題を解決するため、本発明に係るマイクロ波集積回路は、請求項2に記載した様に、前記インタデジタル型キャパシタが有する前記橋状接地導体は対向するコプレーナ電極の外側の接地導体間を半筒状に形成することを特徴とする。

【0011】

この様に構成されたマイクロ波集積回路においては、外部回路とのクロストークを減少させると共に、インタデジタル型キャパシタの電荷容量値を大きくすることが出来、マイク

50

口波集積回路および外部回路に与える影響を小さくすることが出来る。

【0012】

【発明の実施の形態】

以下、本発明に係るマイクロ波集積回路の実施形態を添付図面を参照して説明する。

【0013】

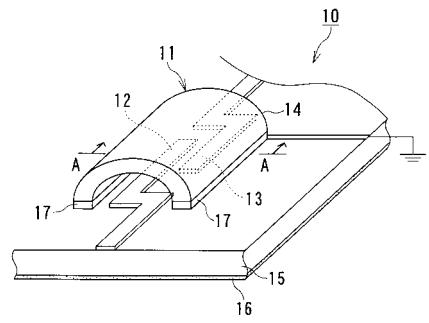

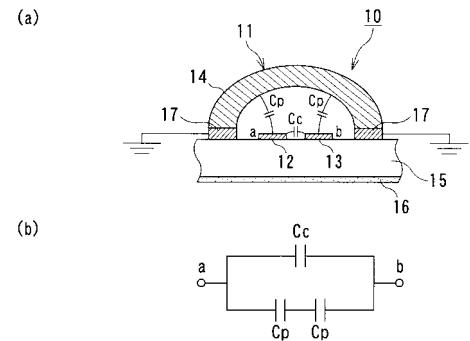

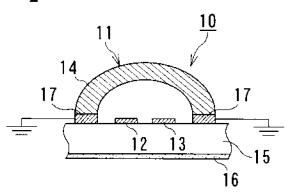

図1に本発明の実施形態を示すマイクロ波集積回路10に用いられるコプレーナ構造で構成されたインタデジタル型キャパシタ11の斜視図を示す。また、図2に図1のA-A線に沿う断面図を示す。

【0014】

図1および図2によれば、インタデジタル型キャパシタ11は、コプレーナ電極12, 13と、橋状接地導体14とを誘電体基板15の上面に備える。一方、誘電体基板15の下面には下部接地導体16を備える。誘電体基板15の上面には、コプレーナ電極12, 13が互いに対向して設けられる。また、コプレーナ構造で構成されたインタデジタル型キャパシタ11のため、コプレーナ電極12, 13が対向する外側には、接地導体17が存在する。コプレーナ電極12, 13の上方には、半楕円筒(半筒)状のシート部材で形成された橋状接地導体14がコプレーナ電極12, 13を覆う様に跨設され、両接地導体17と電気的に接続される。即ち、橋状接地導体14は接地導体17, 17間をブリッジ結合しており、コプレーナ電極12, 13に跨設される。

【0015】

インタデジタル型キャパシタ11は、コプレーナ電極12, 13の上方に橋状接地導体14を橋を架ける様にして設けることで、橋状接地導体14がシールド板と同じ効果を果たしている。この橋状接地導体14のシールド効果によって、インタデジタル型キャパシタ11は、クロストークの要因となる外部回路の素子と間の結合電荷容量をほとんど持たない。従って、クロストークをはるかに低減出来る。

【0016】

また、マイクロ波集積回路10において、近接する外部回路との間に結合電荷容量を持ち得るのは、キャパシタ成分なので、インタデジタル型キャパシタ11において、外部回路との結合電荷容量を小さく抑えられれば、マイクロ波集積回路10全体としてのクロストーク低減を図ることが出来る。

【0017】

図3に本発明のマイクロ波集積回路10に備えられるインタデジタル型キャパシタ11の電荷容量値を表す等価回路を示す。図5に示される従来のインタデジタル型キャパシタ1の電荷容量値はコプレーナ電極2とコプレーナ電極3との間の結合電荷容量値、つまり $C_c$ のみで決定していた。しかし、図3(A)によれば、インタデジタル型キャパシタ11は、コプレーナ電極12, 13との間の結合電荷容量値 $C_c$ の他に、それぞれのコプレーナ電極12, 13と橋状接地導体14との間の電荷容量値 $C_p$ ( $C_p > 0$ )、接地電極間電荷容量値を持つ。

【0018】

図3(A)の等価回路をより具体化した等価回路が図3(B)である。この図によれば、インタデジタル型キャパシタ11の電荷容量値は、 $C_c$ の電荷容量値のキャパシタと、 $C_p$ の電荷容量値のキャパシタを2つ直列接続したキャパシタとを並列接続したキャパシタの電荷容量値と等しくなる。従って、インタデジタル型キャパシタ11の電荷容量値は、従来のインタデジタル型キャパシタ1の電荷容量値よりも大きくなる。

【0019】

本発明の実施形態によれば、橋状接地導体14をコプレーナ電極12, 13の上方に跨設したインタデジタル型キャパシタ11を備えるマイクロ波集積回路10は、橋状接地導体14がシールドの役目を果たすので、外部回路とのクロストークをはるかに減少させ、マイクロ波集積回路10および外部回路に与える影響を低減出来る。また、インタデジタル型キャパシタ11の電荷容量値は、従来のインタデジタル型キャパシタ1の電荷容量値と比べて大きくなり、回路設計上の自由度が拡がる。

10

20

30

40

50

**【0020】**

尚、本実施形態におけるマイクロ波集積回路10において、橋状接地導体14は半楕円筒状で形成されているが、半楕円筒状に限定されない。あらゆる半筒状を包含する。即ち、橋状接地導体14は半円状で形成されても良いし、半角筒状で形成されても良い。

**【0021】**

また、この橋状接地導体14をコプレーナ電極12, 13の上方に跨設したインタデジタル型キャパシタの数量は少なくとも1つ以上存在すれば良い。

**【0022】**

さらに、本実施形態におけるマイクロ波集積回路10に備えられるインタデジタル型キャパシタ11は、誘電体基板15の下面に下部接地導体16を備えているが、この下部接地導体16は無くても良い。

10

**【0023】****【発明の効果】**

本発明に係るマイクロ波集積回路では、マイクロ波集積回路に使用されるコプレーナ構造で構成されたインタデジタル型キャパシタにおいて、コプレーナ電極上方に橋状接地導体を跨設することで、外部回路とのクロストークを減少させ、マイクロ波集積回路および外部回路に与える影響を低減させ、かつ、インタデジタル型キャパシタの電荷容量値の増加を図ったマイクロ波集積回路を提供することが出来る。

**【図面の簡単な説明】**

【図1】本発明に係るマイクロ波集積回路に備えられるインタデジタル型キャパシタの斜視図。

20

【図2】本発明に係るマイクロ波集積回路に備えられるインタデジタル型キャパシタの斜視図におけるA-A線に沿う断面図。

【図3】本発明に係るマイクロ波集積回路に備えられるインタデジタル型キャパシタの電荷容量値を表す等価回路。

【図4】従来のマイクロ波集積回路に備えられるインタデジタル型キャパシタの構成概要図。

【図5】従来のマイクロ波集積回路に備えられるインタデジタル型キャパシタの電荷容量値を表す等価回路。

**【符号の説明】**

30

10 マイクロ波集積回路

11 インタデジタル型キャパシタ

12, 13 コプレーナ電極

14 橋状接地導体

15 誘電体基板

16 下部接地導体

17 接地導体

【図1】

【図3】

【図2】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開平03-211870(JP, A)

特開平04-180402(JP, A)

特開平06-224562(JP, A)

特開2001-223504(JP, A)

特開2001-274325(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04

H01P 3/02