(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-134598

(P2007-134598A)

(43) 公開日 平成19年5月31日(2007.5.31)

(51) Int.CI.

F 1

テーマコード(参考)

**HO1L 21/8247 (2006.01)**

**HO1L 27/115 (2006.01)**

**HO1L 29/792 (2006.01)**

**HO1L 29/788 (2006.01)**

**HO1L 21/304 (2006.01)**

HO1L 27/10 434

HO1L 29/78 371

HO1L 21/304 622X

5FO83

5F1O1

審査請求 未請求 請求項の数 5 O L (全 18 頁)

(21) 出願番号

特願2005-327899(P2005-327899)

(22) 出願日

平成17年11月11日(2005.11.11)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

110000408

特許業務法人高橋・林アンドパートナーズ

(72) 発明者 平沢 信一

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72) 発明者 重田 厚

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72) 発明者 宮野 清孝

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】成膜不良を改善しつつ、デバイス特性のばらつきを低減させ、歩留を向上させる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1のシリコン膜及びストッパー膜を順に形成する工程と、前記半導体基板上的一部領域にある前記ストッパー膜及び前記第1のシリコン膜を少なくとも除去してトレンチを形成する工程と、前記トレンチの内部を含んで前記ストッパー膜上に絶縁膜を形成し、前記ストッパー膜が露出するように前記第2の絶縁膜の一部を除去する工程と、前記ストッパー膜を除去し、前記第1のシリコン膜を露出する工程と、前記第1のシリコン膜上に第2のシリコン膜を選択的に形成する工程と、前記第2のシリコン膜及び前記絶縁膜上に第3のシリコン膜を形成する工程と、前記第3のシリコン膜をCMPにより研磨する工程と、を具備することを特徴としている。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

半導体基板上に第1のシリコン膜及びストッパー膜を順に形成する工程と、前記半導体基板上の一領域にある前記ストッパー膜及び前記第1のシリコン膜を少なくとも除去してトレンチを形成する工程と、前記トレンチの内部を含んで前記ストッパー膜上に絶縁膜を形成し、前記ストッパー膜が露出するように前記第2の絶縁膜の一部を除去する工程と、前記ストッパー膜を除去し、前記第1のシリコン膜を露出する工程と、前記第1のシリコン膜上に第2のシリコン膜を選択的に形成する工程と、前記第2のシリコン膜及び前記絶縁膜上に第3のシリコン膜を形成する工程と、

前記第3のシリコン膜をC M Pにより研磨する工程と、

を具備することを特徴とする半導体装置の製造方法。

10

**【請求項 2】**

前記研磨する工程は、前記絶縁膜を露出するように行われることを特徴とする請求項1に記載の半導体装置の製造方法。

20

**【請求項 3】**

前記第2のシリコン膜は、前記ストッパー膜を除去した部分の段差に対して±0~+100 nmの範囲で形成されることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

**【請求項 4】**

前記第3のシリコン膜は、前記絶縁膜の表面に対して+50~+150 nmの範囲で形成されることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

30

**【請求項 5】**

前記半導体装置は、不揮発性半導体記憶装置であることを特徴とする請求項1乃至4の何れか一に記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置の製造方法に関する。特に、ダマシン加工プロセスを用いた半導体装置の製造方法に関する。

30

**【背景技術】****【0002】**

フラッシュメモリは、電源の供給がなくても記憶を保持できるため、マルチメディアカード用の記憶素子として広く普及している。近年、フラッシュメモリの更なる大容量化が望まれており、大容量化を実現するためにフラッシュメモリをさらに高集積化する必要がある。

40

**【0003】**

フラッシュメモリの高集積化の方法の一つとして、下記特許文献1及び特許文献2に記載されているように、フローティングゲートのシリコン層を二層に分けて成膜し、一層目のシリコン層の形成後に素子分離を行い、続いて二層目のシリコン層を形成する工程において、一層目のシリコン層上にのみ、二層目のシリコン層を自己整合的且つ選択的に堆積させる方法が提案されている。

**【0004】**

これら特許文献1及び特許文献2に開示されている方法は、選択成長によって二層目のシリコン層を素子分離用絶縁膜上に横方向に拡張させて成長させ、フローティングゲートを形成することを特徴としている。これらの方法を用いれば、フローティングゲートをトンネル絶縁膜の幅よりも大きく、且つ隣接するフローティングゲート間の距離を最小線幅よりも小さくすることができ、結果的に大きなカップリング比を実現することができる。また、これらの方法を用いることにより、必然的にフローティングゲート端が丸みを帯びる構造を有することになるため、フローティングゲートに電界集中が起こりにくくなる。

50

**【 0 0 0 5 】**

しかしながらこの場合、各セル間で選択成長したシリコン層の表面積を均等にすることが難しく、その結果、カップリング比に基づくデバイス特性のばらつきが生じやすいという問題がある。一方、下記特許文献3には、二層目のシリコン層を一層目のシリコン層及び素子分離用絶縁膜上の全面に非選択的に形成した後、エッチバック又は研磨を行うことで一層目のシリコン層上に残すダマシン加工プロセスが提案されている。然るに、二層目のシリコン層を非選択的に形成すると、一層目のシリコン層上と素子分離用絶縁膜との段差に起因し、今後更なるメモリセルの微細化が進むと、二層目のシリコン層の成膜不良が発生する懸念がある。

【特許文献1】特開2001-118944号公報 10

【特許文献2】特開2003-7869号公報

【特許文献3】特開2001-284556号公報

**【発明の開示】****【発明が解決しようとする課題】****【 0 0 0 6 】**

本発明は、成膜不良を改善しつつ、デバイス特性のばらつきを低減させ、歩留を向上させる半導体装置の製造方法を提供することを目的とする。

**【課題を解決するための手段】****【 0 0 0 7 】**

本発明の一態様によると、

半導体基板上に第1のシリコン膜及びストッパー膜を順に形成する工程と、

前記半導体基板上の一領域にある前記ストッパー膜及び前記第1のシリコン膜を少なくとも除去してトレンチを形成する工程と、

前記トレンチの内部を含んで前記ストッパー膜上に絶縁膜を形成し、前記ストッパー膜が露出するよう前記第2の絶縁膜の一部を除去する工程と、

前記ストッパー膜を除去し、前記第1のシリコン膜を露出する工程と、

前記第1のシリコン膜上に第2のシリコン膜を選択的に形成する工程と、

前記第2のシリコン膜及び前記絶縁膜上に第3のシリコン膜を形成する工程と、

前記第3のシリコン膜をCMPにより研磨する工程と、

を具備することを特徴とする半導体装置の製造方法が提供される。

**【発明の効果】****【 0 0 0 8 】**

本発明の一態様の半導体装置の製造方法によれば、成膜を改善しつつ、デバイス特性のばらつきを低減させ、歩留を向上させることが可能となる。

**【発明を実施するための最良の形態】****【 0 0 0 9 】**

以下、本発明の実施例に係る半導体装置の製造方法について、図面を参照しながら詳細に説明する。なお、実施例においては、本発明の半導体装置の製造方法の例を示しており、本発明の半導体装置の製造方法は、それら実施例に限定されるわけではない。

**【実施例1】****【 0 0 1 0 】**

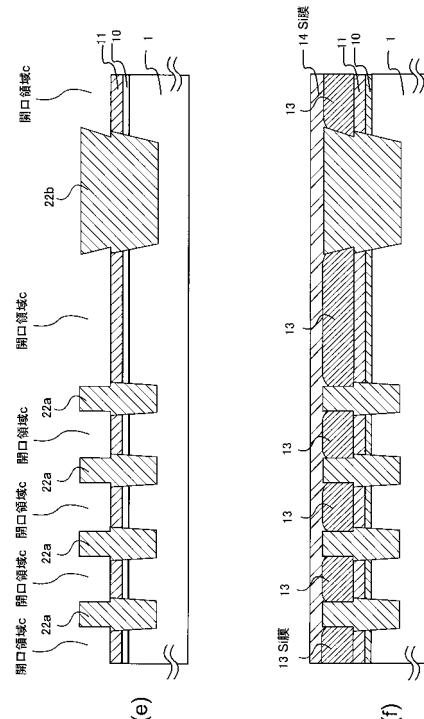

図1乃至図6には、本発明の一実施例に係る半導体装置の製造工程が示されている。本実施例においては、図1乃至図6を参照して不揮発性半導体記憶装置を製造する例について説明する。

**【 0 0 1 1 】**

まず、図1(a)に示すとおり、シリコン基板1上にトンネル絶縁膜となる熱酸化膜10を厚さ9nmで形成した後、第1のシリコン膜(Si膜)11を厚さ40nmで形成し、続いてストッパー膜として、例えば、窒化珪素膜(SiN膜)12を厚さ150nmで形成する。なお、この第1のシリコン膜11は燐が添加されていても、されていなくてもよい。また、この第1のシリコン膜11は、アモルファスシリコンであってもポリシリコン

10

20

30

40

50

であってもよい。第1のシリコン膜11がアモルファスシリコンの場合には、表面の凹凸が少なく、その表面上に形成したストッパー膜12の表面も平坦にできるため、ラインエッジラフネス(Line Edge Roughness: LER)などの後工程での加工端におけるゆらぎを低減することができる。一方、第1のシリコン膜11がポリシリコンの場合には、アモルファスシリコンに比較して密度が高いため、後工程での高精度の加工が可能である。また、第1のシリコン膜11がアモルファスシリコンであった場合でも、ストッパー膜12であるSiN膜を堆積する際の熱工程で結晶化し、ポリシリコン膜となり得る。また、第1のシリコン膜は、単結晶シリコン膜であってもよい。

#### 【0012】

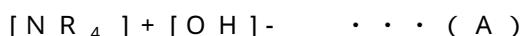

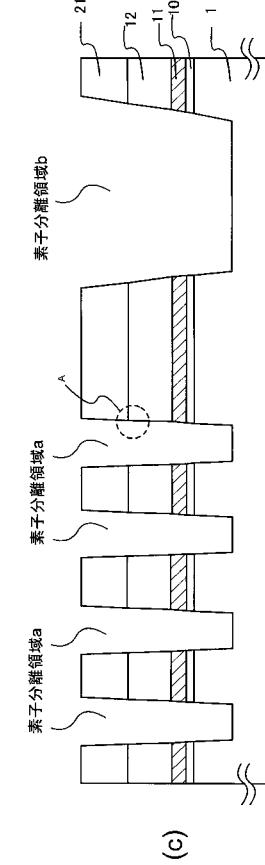

次に、図1(b)に示すとおり、マスク材21を堆積する。その後、図2(c)に示すとおり、マスク材21のパターニングを行い、更にマスク材21のパターンから露出した領域にあるストッパー膜としてのSiN膜12、第1のシリコン膜11、トンネル絶縁膜10、シリコン基板1を反応性イオンエッチング(Reactive Ion Etching; RIE)によりエッチング除去し、素子分離領域a及びbとなる部分にトレンチを形成する。この素子分離領域a及びbは非活性領域となり、それ以外のトランジスタとして機能する領域が活性領域となる。ここで、図2(c)において、「A」で示す部分の拡大図を図3に示す。図2(c)に示す工程において、次の工程における素子分離用絶縁膜の埋め込み特性を良くするため、SiN膜12、第1のシリコン膜11及びシリコン基板1には、順テーパー( $= 0.3^\circ \sim 5^\circ$ 、代表的には約 $3^\circ$ )を設けてもよい。

#### 【0013】

次に、マスク材21を剥離した後、素子分離領域a及びbとなるトレンチ部分を含めSiN膜12上に絶縁膜を堆積する。本実施例においては、この絶縁膜は、テトラエトキシシラン(TEOS)から形成した。また、このとき、ハイデンシティプラズマ(HDP)CVDを用いて絶縁膜を形成するようにしてもよい。

#### 【0014】

その後、図2(d)に示すとおり、SiN膜12をストッパーとしてCMP等の研磨技術やエッチャック等の方法によって、トレンチ外の絶縁膜を除去し、素子分離用絶縁膜22a及び22bを形成する。本実施例においては、CMPを用いた。特に研磨技術を用いる方法としてCMPを用いる場合には、ストッパー膜12が露出するまで研磨を行うことで、研磨後の表面を平滑かつストッパー膜12の表面とほぼ同じ高さにそろえることができるため、セル間のばらつきを小さくできるという利点がある。このとき、セル外における素子分離用絶縁膜22bの表面は余分に削られるため、所謂ディッシングが生じる場合がある。ディッシングは素子分離領域bの面積が大きければ大きいほど顕著に現れる。また、この図2(d)に示す工程でSiN膜12も約10nm削られることになる。

#### 【0015】

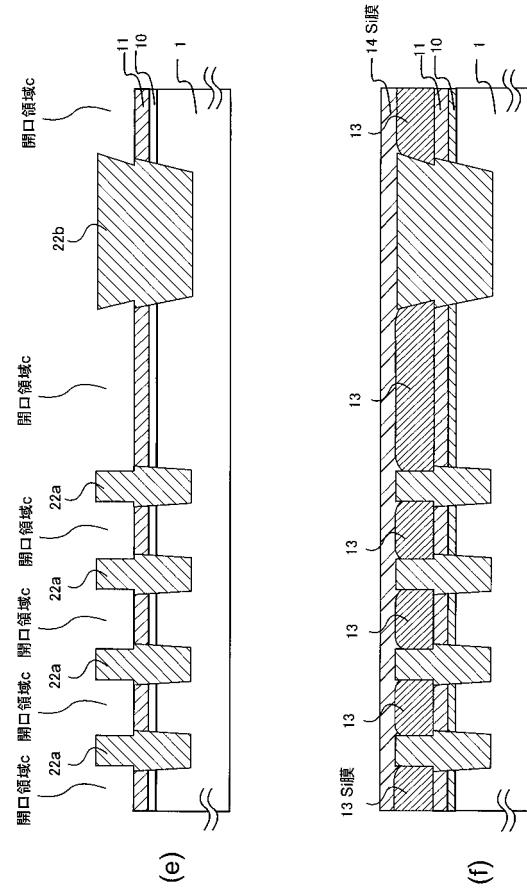

次に、図4(e)に示すとおり、SiN膜12をリン酸ウェットエッチングにより除去する。素子分離領域a及びbに順テーパー(代表的には $= 約 3^\circ$ )が設けられている場合、SiN膜12が除去された部分である開口領域cは逆テーパーになっている。なお、開口領域cの深さは、SiN膜12の厚さと同じ140nmであった。

#### 【0016】

次に、第1のシリコン膜11の表面に形成された(自然)酸化膜を除去するため、フッ酸(HF)を純水で希釀した希フッ酸(DHF)溶液でエッチング処理を行なう。本実施例においては、200倍希釀のDHFを用い、酸化膜を5~10nmエッチングする。この酸化膜除去処理によって、第1のシリコン膜11の表面には、シリコンの結晶が現れる。

#### 【0017】

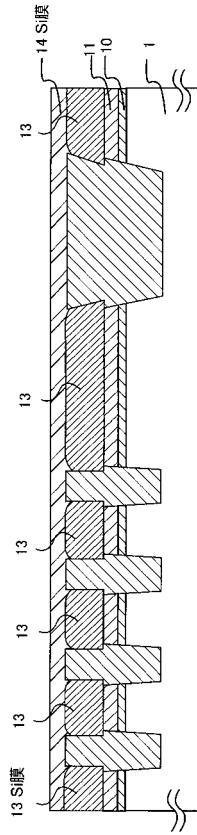

次に、図4(f)に示すとおり、第1のシリコン膜11を核としたエピタキシャル成長によりポリシリコン膜13を選択成長させる。本実施例においては、まず、基板をLPCVDによる成膜装置内に搬送し、チャンバー内を850まで昇温後、圧力240Torrの下、水素(H<sub>2</sub>)雰囲気でベークする。その後、チャンバー内を815まで降温し、圧力52.8Torrで、原料ガスとしてジクロルシラン(DCS)、塩化水素(HCl)、

10

20

30

40

50

水素(  $H_2$  )及びフォスフィン(  $PH_3$  )を供給し、所望の膜厚まで第2のシリコン膜13を成膜する。なお、このポリシリコン膜(第2のシリコン膜)13の成膜において、キャリアガスとして、水素(  $H_2$  )に代えて窒素(  $N_2$  )を用いてもよい。第2のシリコン膜13を選択成長によって第1のシリコン膜11上に成長させることで、メモリセルの微細化が進んで開口領域cのアスペクト比が増大しても、空洞等の成膜不良が生じることなく、開口領域c内を埋め込むことができる。

## 【0018】

第2のシリコン膜13の成膜後、引き続き同一成膜装置内にてポリシリコンを非選択成長させ、図4(f)に示すように、非選択的な第3のシリコン膜14を形成する。本実施例においては、第2のシリコン膜13の成膜後、チャンバー内を700まで降温し、圧力80 Torrでシランガスを導入し、基板全体に非選択的なポリシリコン膜(第3のシリコン膜)14を所望の膜厚で形成する。

## 【0019】

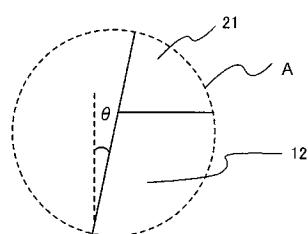

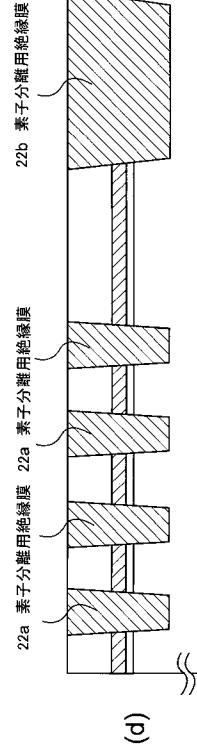

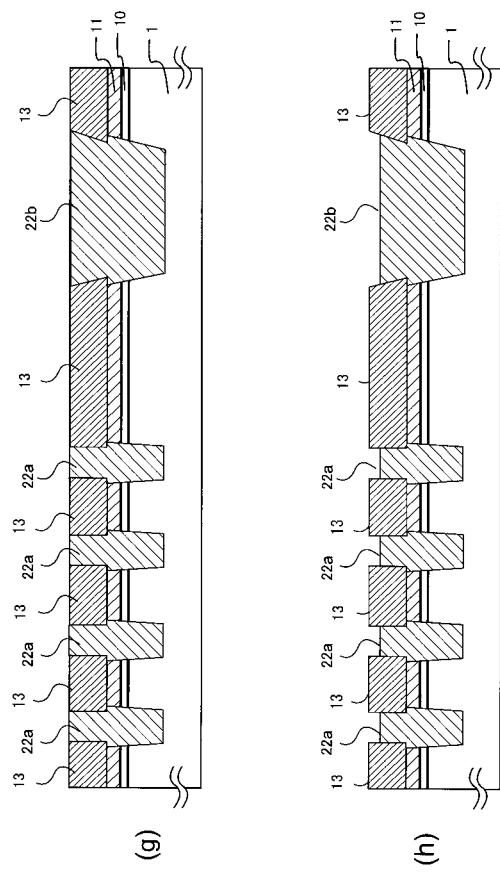

次に、図5(g)に示すとおり、CMPによって表面を研磨し平坦化する。基板全面が非選択的な第3のシリコン膜14となる被研磨対象膜で覆われているため、素子分離用絶縁膜22a及び22bが必要以上に研磨され過ぎることを防止することができる。すなわち素子分離用絶縁膜22a及び22bにおける局部的な研磨ヤラレの発生を防止することができ、第2のシリコン膜13の表面は均一に平坦化されており、第1のシリコン膜11及び第2のシリコン膜13からなる電極(後に、フローティングゲートとなる)の均一な特性を得ることができる。

## 【0020】

本実施例においては、CMP装置(荏原製作所製EPO-222)を用い、多孔質ポリウレタン製の研磨パッド(ロデール社製IC1000/Suba400)、スラリーにはコロイダルシリカ、ピペラジンの水系分散体(A)とコロイダルシリカ、トリエタノールアミン、ヒドロキシエチルセルロースの水系分散体(B)を研磨パッド上で混合したものを用いて被研磨対象膜を研磨する。

## 【0021】

また、CMP装置の研磨条件として、研磨圧力300g/cm<sup>2</sup>、ウエハー回転数55rpm、テーブル回転数50rpm、総スラリー流量300ml/min(水系分散体(A)50ml/min、水系分散体(B)250ml/min)、研磨時間TCM(Table Current Monitor)を用い終点の検出を行い、オーバー研磨時間設定として終点検出時間+25%の条件にて研磨を行った。

## 【0022】

次に、図5(h)に示すとおり、素子分離用絶縁膜22a及び22bを反応性イオンエッティングにより約100nm後退させる。その後、第2のシリコン膜13の角部に対して、その曲率半径を増加させるために、ケミカルドライエッティングにより角部のみをエッティングしてもよい。また、その角部をエッティングする代わりに、例えば酸化などの方法によって、その曲率半径を増加させてもよい。本実施例においては、第2のシリコン膜13の角の丸みの曲率半径は、500nmであった。本実施例における第2のシリコン膜13の形状によると、デバイス動作時の電界集中を緩和することができ、メモリセルの安定動作を実現することができる。

## 【0023】

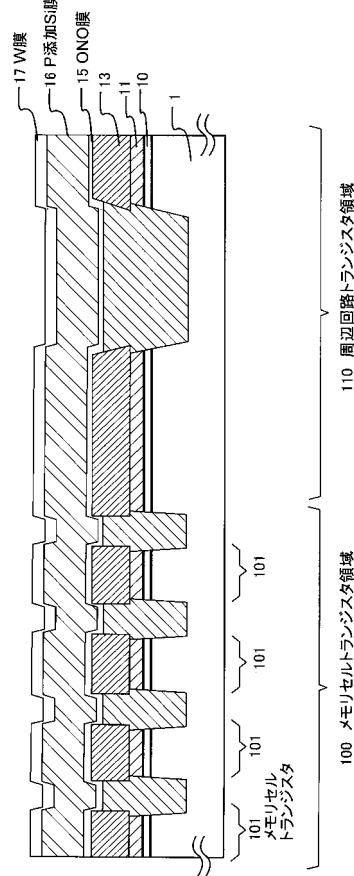

次に、図6に示すとおり、第1のシリコン膜11及び第2のシリコン膜13から成るフローティングゲートと、後に形成するコントロールゲート(制御ゲート)との間の電極間絶縁膜15を形成する。この絶縁膜15としては酸化珪素膜/窒化珪素膜/酸化珪素膜からなる所謂ONO膜、窒化珪素膜/酸化珪素膜/窒化珪素膜/酸化珪素膜/窒化珪素膜からなる所謂NONON膜あるいはシリコン酸化膜よりも高い誘電率を有する、所謂高誘電体絶縁膜を用いる。

## 【0024】

10

20

30

40

50

次に、燐が添加されたポリシリコン膜（P添加Si膜）16を厚さ100nmで形成し、続いて、タンゲステン膜（W膜）17を厚さ85nmで形成する。これらポリシリコン膜16及びタンゲステン膜17は、制御ゲートとなる。なお、必要に応じ、セル外における電極間絶縁膜15に予め開口を設けておくことで、第2のシリコン膜13とポリシリコン膜16間を短絡させる。

#### 【0025】

次に、フローティングゲートをメモリセルごとに孤立させ、また制御ゲート用のシリコン膜16及びタンゲステン膜17をワード線パターンにパターニングするための反応性イオンエッチャリングを行った後、得られたパターンと自己整合的にシリコン基板1内に不純物をイオン注入して、ソース／ドレイン領域を形成する（図示せず）。 10

#### 【0026】

以上の工程をもって、メモリセルトランジスタ領域100には、メモリセルトランジスタ101が形成され、周辺回路トランジスタ領域110には、メモリセルトランジスタ101を制御するための回路を形成する素子等が形成される。この後、通常の方法により、層内絶縁膜やビット線等を形成することで不揮発性半導体記憶装置が完成する。

#### 【0027】

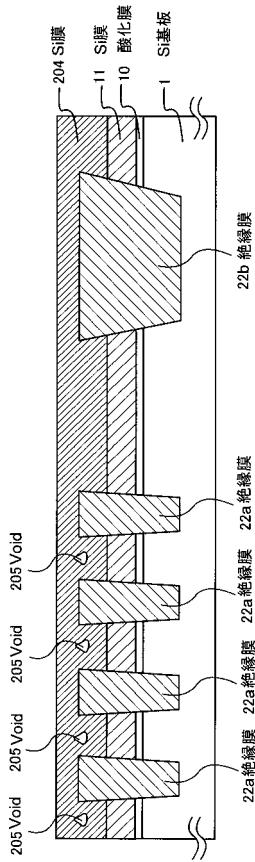

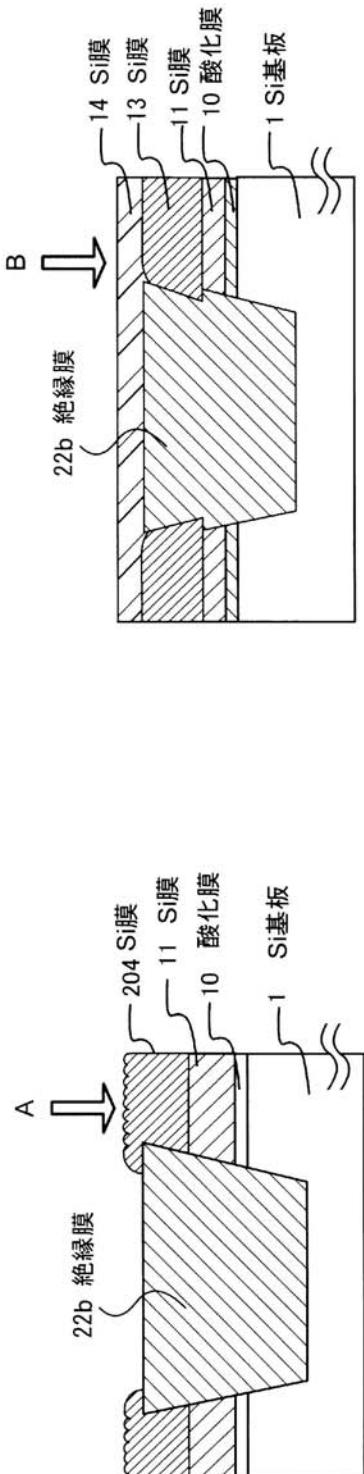

次に、フローティングゲートとなるシリコン膜の成膜方法が異なる背景技術の不揮発性半導体記憶装置と本実施例の不揮発性半導体記憶装置とを比較検討する。フローティングゲートに用いる二層目のポリシリコン膜を非選択成長によって一層目のポリシリコン膜及び素子分離領域上に直接形成すると、メモリセルの微細化に伴い、フローティングゲートに用いる二層目のポリシリコン膜に空洞が残ってしまい、高品質のメモリセルを作製することができないという問題があった。即ち、ダマシン加工プロセスを用いて二層目のポリシリコン膜を形成する工程において、特に、図7に示すように素子分離用絶縁膜22a及び22bと下地の第1のシリコン膜11とでなる溝の開口領域形状が逆テーパーになつていると、減圧化学的気相成長（Low Pressure Chemical Vapor Deposition、以下「LPCVD」という。）法を用いてポリシリコン（又はアモルファスシリコン）膜204を埋め込む際に、埋め込み部分で埋め込み不良（Void）205が発生する場合がある。このような二層目のポリシリコン膜中の空洞をなくすためには、素子分離領域の端をエッチャリングにより丸める、あるいは二層目のポリシリコン膜を堆積した後に、一旦、二層目のポリシリコン膜をエッチャリングしてから三層目のポリシリコン膜を堆積させる、等の方法が考えられるが、何れの方法もプロセスが長時間化・複雑化してしまう。また、従来、二層目のポリシリコン膜の堆積後、その表面をエッチャリング除去することにより、二層目のポリシリコン膜と素子分離領域との高さを揃えていたが、この工程によっては、面積の大きい素子分離領域上に堆積したポリシリコン膜を完全に取り除くことが困難で、隣り合うメモリセル同士で互いのフローティングゲートが短絡（ショート）してしまうという問題があった。 20

#### 【0028】

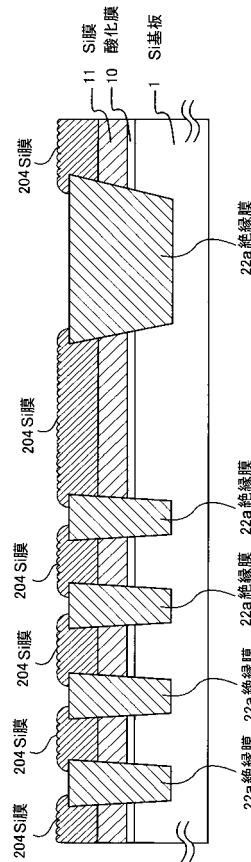

これらの問題を解決するため、図8に示すように、第1のシリコン膜11上の開口領域のみに選択的にポリシリコンを成長させ、ポリシリコン膜204を成膜することによって埋め込み不良を改善する（Void Free）方法がある。しかし、図8に示すプロセスによると、選択成長によって成膜されるポリシリコン表面は、その材料が多結晶であるがゆえに必然的に凹凸が激しく、そのままでは個々のセルごとの電極間絶縁膜との対向面積にはらつきが生じるため、セルごとのカップリング比にもはらつきが生じてしまうという問題があった。また、この方法では、カップリング比の大きさとフローティングゲート間隔はトレードオフの関係にあり、素子密度が高くなるにつれてカップリング比を大きく取りにくくなり、カップリング比を増加させる限界が生じる。 30

#### 【0029】

これに対し、選択成長によってポリシリコン膜204を成膜した後、例えば、全面を研磨してポリシリコン膜204を開口領域内のみに残置させれば、各セル間でのポリシリコン膜204の表面積のはらつき抑制が期待できる。然るにこの場合は、ポリシリコン膜204が成膜されない素子分離用絶縁膜22a、22b上は、化学的機械的研磨（Chemical M 50

echanical Polishing) 法による平坦化を行った際、素子分離用絶縁膜 22a 及び 22b が必要以上に研磨され(研磨ヤラレ)、これが歩留低下の一つの要因となってしまう。

#### 【0030】

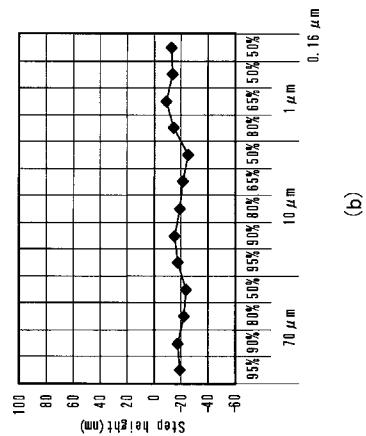

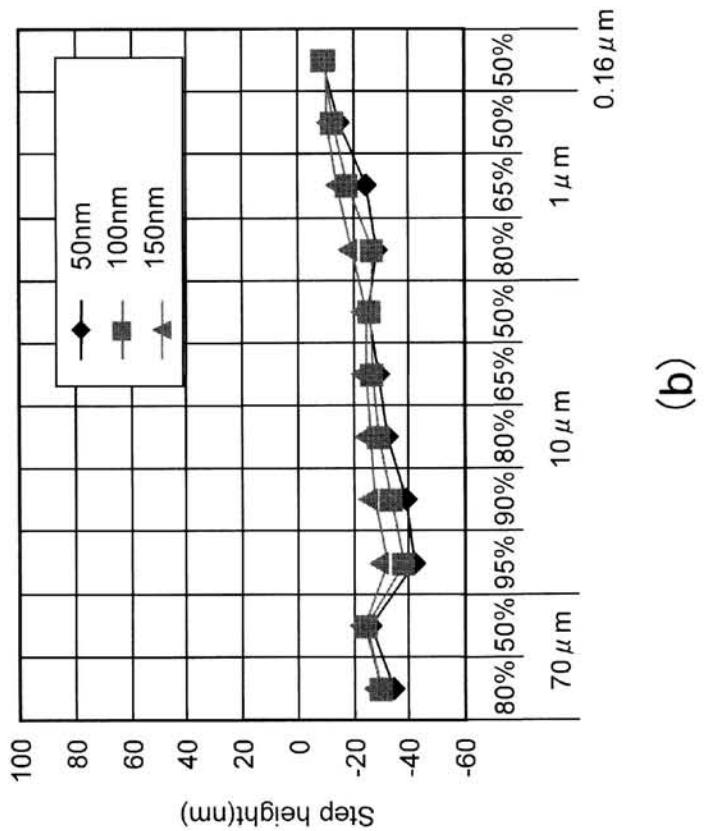

ここで、このような図 8 に示すプロセス及び本実施例における図 4(f) のプロセスについて、成膜方法の違いによる CMP 後の平坦性を比較した結果を図 9 に具体的に示す。即ち、図 9(a) は、図 8 に示すような選択成長させたポリシリコン膜 204 が表面に存在する構造(ここでは、説明の便宜上、「選択成長構造」と言う。)において CMP で研磨した場合の平坦化特性を示すグラフである。一方、図 9(b) は、本実施例の製造方法によって作製された図 4(f) に示すような構造、即ち、選択成長させたポリシリコン膜 13 の上に非選択成長させたポリシリコン膜 14 を基板全面に形成した構造(ここでは、説明の便宜上、「選択・非選択成長構造」と言う。)において CMP で研磨した場合の平坦化特性を示すグラフである。

#### 【0031】

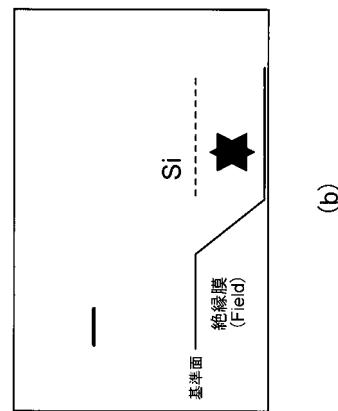

図 9(a) 及び(b) のグラフにおいて、横軸は、CMP 後の各線幅(70 μm, 10 μm, 1 μm, 0.16 μm)における被覆率(ポリシリコンの面積 / (ポリシリコンの面積 + 絶縁膜の面積))を示し、縦軸は、平坦性を表すステップ・ハイト(Step Height)を示している。なお、ステップ・ハイトは、図 10 に示すとおり、基準面からのポリシリコン膜の表面までの距離(高さ)であり、基準面よりもポリシリコン膜の表面が上にある場合を「+」として定義し(図 10(a))、基準面よりもポリシリコン膜の表面が下にある場合を「-」として定義している(図 10(b))。

#### 【0032】

選択成長構造の平坦化特性と選択・非選択成長構造の平坦化特性とを比較すると、選択成長構造においては、平坦化特性は線幅と被覆率に依存し、研磨によるポリシリコン膜の減衰(エロージョン: erosion)のばらつきが生じるのに対して、選択・非選択構造においては、線幅、被覆率に依存すること無く良好な平坦性が得られることが分かる。

#### 【0033】

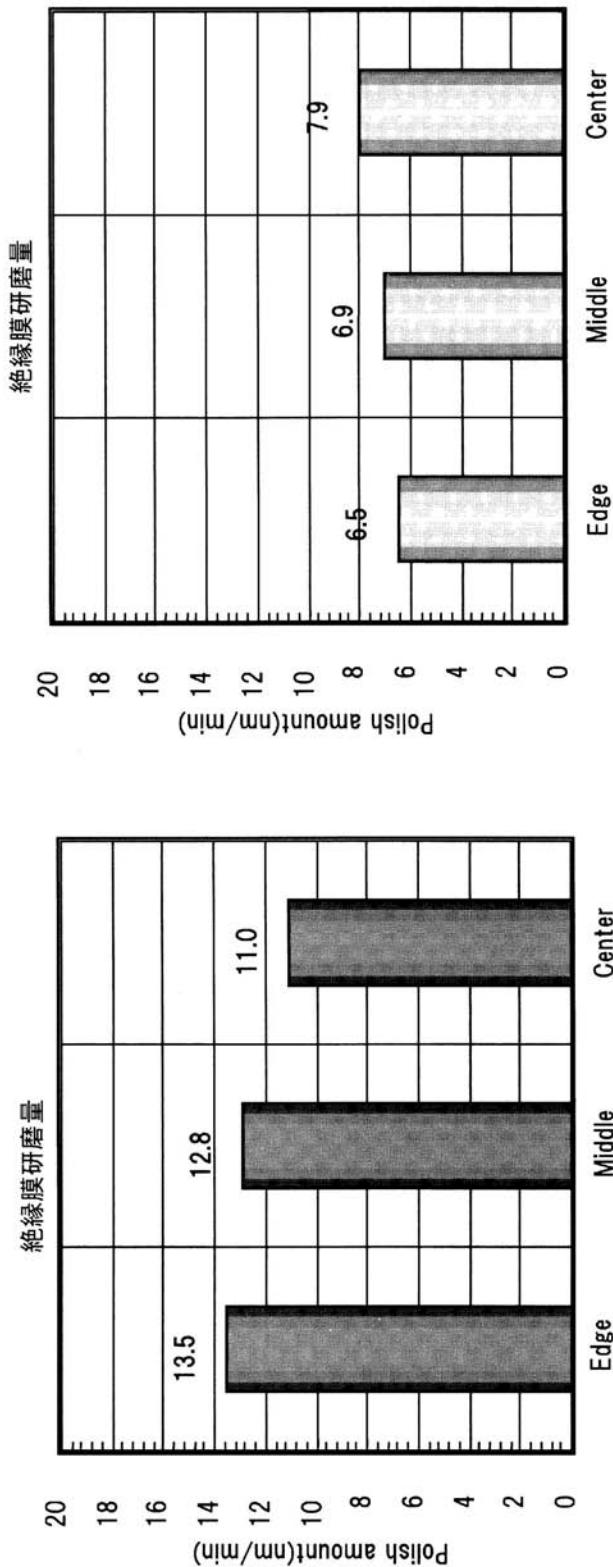

また、ポリシリコン膜の成膜方法の違いによる絶縁膜の研磨量比較結果を図 11(a) 及び(b) に示す。図 11(a) は、選択成長構造における絶縁膜研磨量の測定結果のグラフを示し、図 11(b) は、選択・非選択成長構造における絶縁膜研磨量の測定結果のグラフを示す。図 11(a) 及び(b) に示す測定においては、それぞれ、「A」と「B」で示す箇所を測定した上で、絶縁膜 22b の研磨量の 3 つの測定点を「センター」、「ミドル」及び「エッジ」とした。絶縁膜 22b が表面に現れている条件、即ち選択成長構造(図 11(a))では、センター、ミドル、エッジの研磨量がそれぞれ 11.0 nm/min, 12.8 nm/min, 13.5 nm/min と大きな値を示すのに対して、絶縁膜 22b が表面に現れておらずポリシリコン膜 14 で覆われている条件、即ち選択・非選択成長構造(図 11(b))では、それぞれ 7.9 nm/min, 6.9 nm/min, 6.5 nm/min と絶縁膜 22b の研磨量が大きく抑制されている。

#### 【0034】

よって、図 11(a) 及び(b) に示す絶縁膜研磨量の実験結果からも分かるように、本実施例の半導体装置の製造方法によれば、絶縁膜 22a 及び 22b の研磨量が大きく抑制されているので、絶縁膜 22a 及び 22b が研磨され過ぎることを防止することができ、成膜不良を改善しつつ、デバイス特性のばらつきを低減させ、歩留を向上させることが可能となる。

#### 【0035】

また、本実施例のように、不揮発性半導体記憶装置のフローティングゲートを CMP によって表面を研磨し平坦化することにより、フローティングゲートの均一な特性を得ることができる。

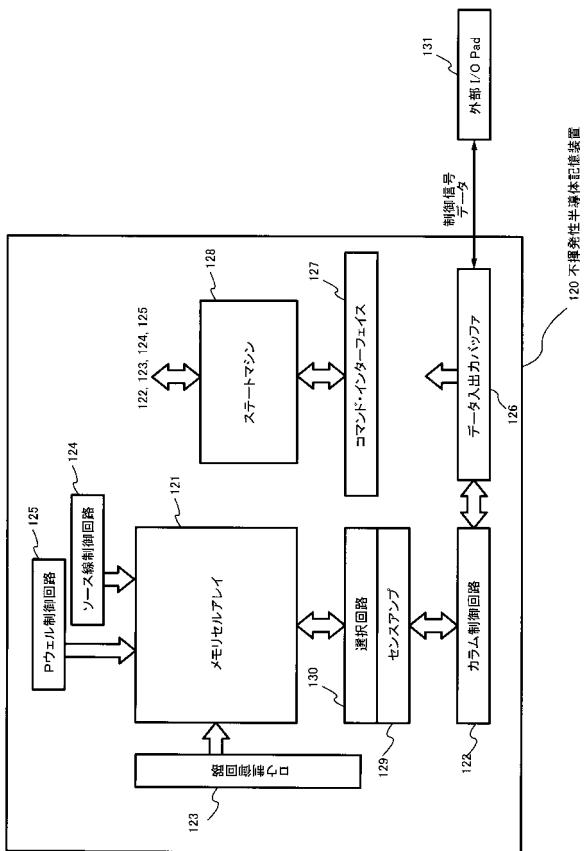

#### 【0036】

ここで、図 12 に、本実施例に係る不揮発性半導体記憶装置 120 の概略構成図を示す。本実施例に係る不揮発性半導体記憶装置 120 は、メモリセルアレイ 121, カラム制御

10

20

30

40

50

回路（カラムデコーダ）122，ロウ制御回路（ロウデコーダ）123，ソース線制御回路124，Pウェル制御回路125，データ入出力バッファ126，コマンド・インターフェイス127，ステートマシン128，センスアンプ129，選択回路130を有している。本実施例に係る不揮発性半導体記憶装置120は，外部I/Oパッド131とデータ及び制御信号（コマンド）の送受信を行う。

#### 【0037】

本実施例に係る不揮発性半導体記憶装置120においては，外部I/Oパッド131から，データ及び制御信号がデータ入出力バッファ126を通してコマンド・インターフェイス127及びカラム制御回路122に入力される。ステートマシン128は，制御信号及びデータに基づき，カラム制御回路122，ロウ制御回路123，ソース線制御回路124及びPウェル制御回路125を制御する。ステートマシン128は，カラム制御回路122及びロウ制御回路123に対してメモリセルアレイ121のメモリセルに対するアクセス情報を出力する。カラム制御回路122及びロウ制御回路123は，当該アクセス情報を及びデータに基づき，センスアンプ129及び選択回路130を制御し，メモリセルをアクティブにし，データの読み出し，書き込み，又は消去を行う。メモリセルアレイ121の各ビット線に接続されたセンスアンプ129は，ビット線へデータをロードし，またビット線の電位を検出しデータ・キャッシュで保持する。また，カラム制御回路122によって制御されたセンスアンプ129によりメモリセルから読み出したデータは，データ入出力バッファ126を通して外部I/Oパッド131へ出力される。選択回路130は，センスアンプを構成する複数のデータ・キャッシュのうち，ビット線に接続するデータ・キャッシュの選択を行う。10 20

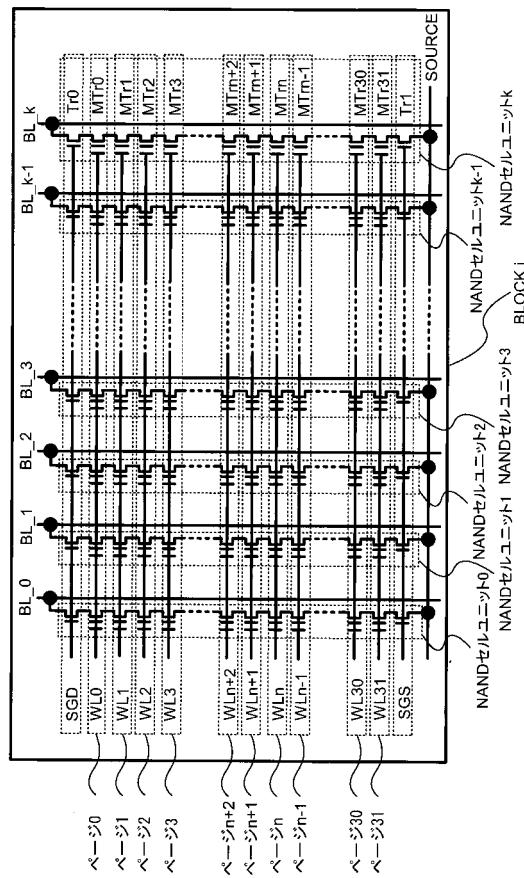

#### 【0038】

ここで、メモリセルアレイ121の概略回路構成を図13に示す。メモリセルアレイ121は、合計m個のブロック（BLOCK0、BLOCK1、BLOCK2、…、BLOCKi、…、BLOCKm）に分割されている。ここでは、「ブロック」とはデータ消去の最小単位である。

#### 【0039】

また、各ブロックBLOCK0～BLOCKmは、それぞれ、図13に代表的に示すブロックBLOCKiのように、k個のNANDセルユニット0～kで構成される。本実施例では、各NANDセルユニットは、32個のメモリセルMT<sub>r</sub>0～MT<sub>r</sub>31が直列に接続されて構成され、その一端は選択ゲート線SGDに接続された選択ゲートトランジスタTr0を介してビット線BL（BL\_0、BL\_1、BL\_2、BL\_3、…、BL\_k-1、BL\_k）に、他端は選択ゲート線SGSに接続された選択ゲートトランジスタTr1を介して共通ソース線（SOURCE）に接続されている。各々のメモリセルMT<sub>r</sub>の制御ゲートは、ワード線WL（WL0～WL31）に接続されている。1本のワード線WLに接続されるk個の各メモリセルMT<sub>r</sub>は1ビットのデータを記憶し、これらk個のメモリセルMT<sub>r</sub>が「ページ」という単位を構成する。30

#### 【0040】

また、本実施例は、メモリセルアレイを構成するブロックの数をm個とし、且つ1つのブロックが、32個のメモリセルMT<sub>r</sub>でなるNANDセルユニットをk個含むようにしたが、これに限定されるわけではなく、所望の容量に応じてブロックの数、メモリセルMT<sub>r</sub>の数及びNANDセルユニットの数を変更すればよい。また、本実施形態においては、各メモリセルMT<sub>r</sub>が1ビットのデータを記憶するようにしたが、各メモリセルMT<sub>r</sub>が電子注入量に応じた複数ビットのデータ（多値ビットデータ）を記憶するようにしてもよい。また、本実施例においては、1つのNANDセルユニットが1つのビット線BLに接続されたNAND型フラッシュメモリの例について説明しているが、複数のNANDセルユニットが1つのビット線BLを共有する所謂シェアードビット線（Shared Bit Line）型のNAND型フラッシュメモリに適用するようにしてもよい。40

#### 【実施例2】

#### 【0041】

本実施例においては、上述の実施例1におけるシリコン膜11としてアモルファスシリコン膜を成膜し、このアモルファスシリコン膜11を核とし、エピタキシャル成長によりポリシリコン膜13を選択成長させ、その後エピタキシャル成長により非選択的にポリシリコン膜14を成膜する。

#### 【0042】

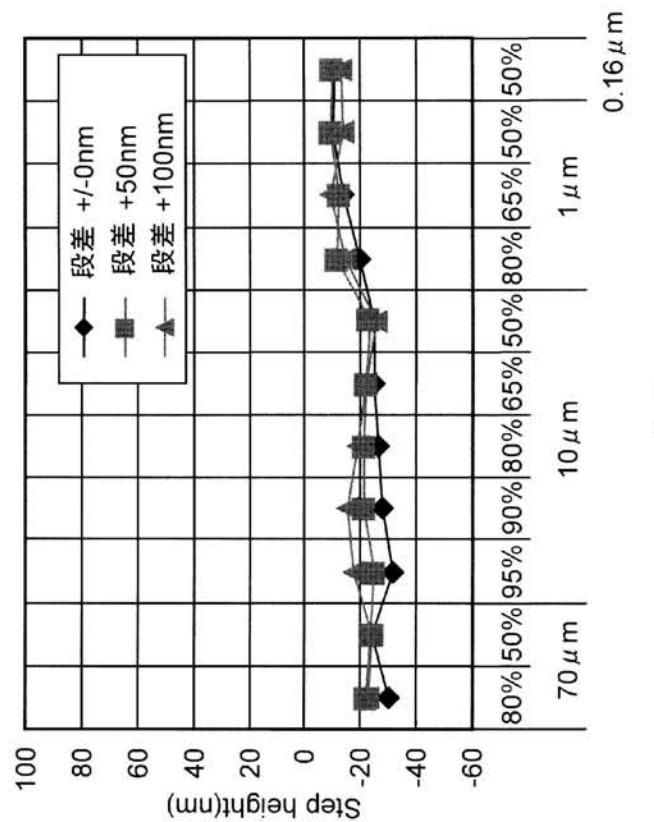

このとき、得られた各線幅及び各被覆率の電極の平坦化特性に関し、アモルファスシリコン膜11を核とし、開口領域c(図4(e)参照)に選択成長によって成膜されるポリシリコン膜13の膜厚依存を図14(a)に示す。また、ポリシリコン膜13と素子分離用絶縁膜22a及び22b上に非選択成長によって成膜されるポリシリコン膜14の膜厚依存を図14(b)に示す。

10

#### 【0043】

本実施例においては、図4(e)に示すような開口領域cの段差に対して±0nm( )、+50nm( )、+100nm( )のポリシリコン膜13の成膜を実施し、各線幅及び各被覆率に対する平坦化特性を図14(a)に示すとおり求めた。一般的に、ステップ・ハイトが+20~-40nmの範囲にあることが好ましいので、この結果よりポリシリコン膜13の膜厚は段差に対して±0nm~+100nmの範囲にあれば十分な平坦性が得られることがわかる。

#### 【0044】

次に、開口領域cに堆積するポリシリコン膜13の膜厚を段差+/-0nmで成膜し、上層の非選択的なポリシリコン膜14の膜厚条件を変化させて成膜を実施した場合の結果を図14(b)に示す。一般的に、ステップ・ハイトが+20~-40nmの範囲にあることが好ましいので、図14(b)に示す結果より、上層の非選択的なポリシリコン膜14の膜厚は絶縁膜22a及び22bの表面上50nm~150nmの範囲であれば十分に平坦性が得られることがわかる。

20

#### 【実施例3】

#### 【0045】

本実施例では、図5(g)に示すCMPにより被研磨対象を研磨する工程において、CMPのスラリーとして用いる2液混合型水系分散体又は各成分を配合して調整された成分配合型水素分数体の各成分の例について説明する。なお、以下に示す各成分は一例に過ぎず、研磨工程に用いることのできるスラリーは、以下の例に限定される訳ではない。

30

#### 【0046】

#### [成分配合型水系分散体]

成分配合型水系分散体としては、少なくとも水溶性第4級アンモニウム塩、水溶性第4級アンモニウム塩を除く塩基性有機化合物、無機酸塩、水溶性高分子、砥粒および水系媒体が配合されて得られた化学機械用水系分散体が好ましい。

40

#### 【0047】

#### [2液混合型水系分散体]

2液混合型水系分散体としては、少なくとも水溶性第4級アンモニウム塩、無機酸塩、および水系媒体が配合されて得られた水系分散体(I)とすくなくとも水溶性高分子、水溶性第4級アンモニウム塩を除く塩基性有機化合物および水系媒体が配合されて得られた水系分散体(II)とが、混合されてなり、かつ該水系分散体(I)、および該水系分散体(II)のすくなくとも一方に砥粒が配合されている化学機械用水系分散体が好ましい。

#### 【0048】

#### [水溶性第4級アンモニウム塩およびその他の塩基性有機化合物]

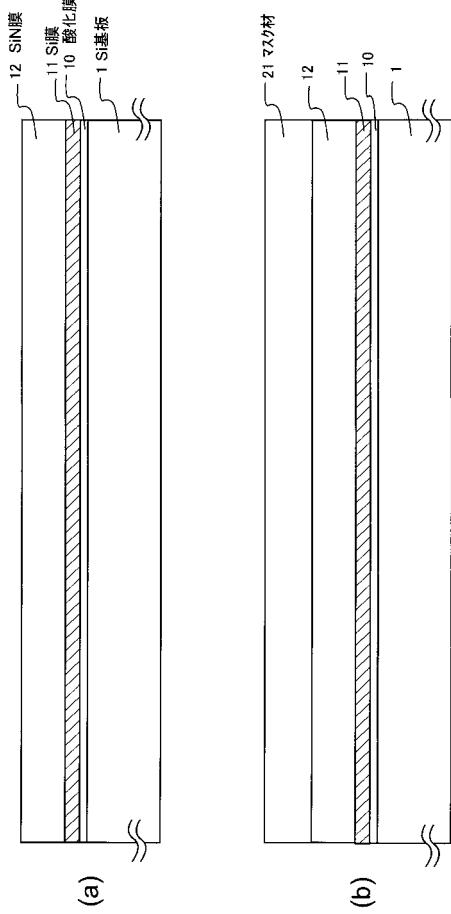

水溶性第4級アンモニウム塩としては第4級アルキルアンモニウム塩が好ましく、この水溶性第4級アルキルアンモニウム塩としては下記式(A)で表される化合物が好ましい。

[式(A)中、Rは炭素数1~4アルキル基を表す。これら4個のRは全てが同じであってもよいし、それぞれが異なっていてもよい。]

その具体例としてはテトラメチルアンモニウムヒドロキシド、テトラエチルアンモニウム

50

ヒドロキシド、テトラプロピルアンモニウムヒドロキシド、テトライソプロピルアンモニウムヒドロキシド、テトラブチルアンモニウムヒドロキシド、テトライソブチルアンモニウムヒドロキシド、およびテトラエチルアンモニウムヒドロキシドの化合物が例示され、これらのうちテトラメチルアンモニウムヒドロキシドが特に好ましく用いられる。これらの水溶性第4級アルキルアンモニウム塩は単独で使用することが出来、また、2種類以上を混合して使用することが出来る。

#### 【0049】

さらに、水溶性第4級アンモニウム塩を除く塩基性有機化合物として水溶性アミンが挙げられる。水溶性アミンとして(a)メチルアミン、ジメチルアミン、トリメチルアミン、エチルアミン、ジエチルアミン、トリエチルアミン等のアルキルアミン

(b)ジエタノールアミン、トリエタノールアミン、アミノエチルエタノールアミン等のアルカノ-ルアミン (c)ジエチレントリアミン、トリエチレンテトラミン、テトラエチレンペニタミン、ペンタエチレンヘキサミン、トリエチレンジアミン等のアルキレンアミン

(d)ピペラジン・六水和物、無水ピペラジン、アミノエチルピペラジン、N-メチルピペラジン等のペラジン類 (e)ポリエチレンイミン等のイミン類などが挙げられる。これらのうちではジエタノールアミン、トリエタノールアミン等が好ましい。上記水溶性アミンは単独で使用することが出来、また、2種類以上を混合して使用することが出来る。

#### 【0050】

[水溶性第4級アンモニウム塩およびその他の塩基性有機化合物 - 最適質量]

水溶性第4級アルキルアンモニウム塩、および水溶性第4級アルキルアンモニウム塩を除く塩基性有機化合物の配合量は、成分配合型および2液混合型水系分散体の各々の総量に対してそれぞれ0.005~10質量%とすることができ、0.005~8質量%が好ましく、さらに0.008~5質量%が好ましく、特に0.01~4質量%が好ましい。水溶性第4級アルキルアンモニウム塩、および水溶性第4級アルキルアンモニウム塩を除く塩基性有機化合物の配合量が0.005質量%未満であると十分な研磨速度が得られない場合がある。一方、塩基性有機化合物の配合量は10質量%であれば十分である。なお、水溶性第4級アンモニウム塩等の塩基性有機化合物は水系分散体の中で溶解し、すくなくとも一部はイオンとなって含有されている。

#### 【0051】

[無機酸塩]

無機酸塩としては塩酸、硝酸、硫酸、炭酸、磷酸の如き無機酸のナトリウム塩、カリウム塩、アンモニウム塩、硫酸水素イオン、炭酸水素イオン、および磷酸水素イオンを持つナトリウム塩、カリウム塩、アンモニウム塩が挙げられこれらのうち、アンモニウム塩が好ましくさらには炭酸アンモニウム、硝酸アンモニウム、硫酸アンモニウムである。これらの無機酸塩は、単独で使用することが出来、また、2種類以上を混合して使用することが出来る。

#### 【0052】

[無機酸塩-最適質量]

無機酸塩の配合量は、成分配合型および2液混合型水系分散体の各々の総量に対して0.005~8質量%とすることができ、0.005~6質量%が好ましく、さらに0.008~4質量%が好ましく、特に0.01~3質量%が好ましい。無機酸塩の配合量が0.005質量未満%であると、ディッシング、エロージョンの抑制効果は不十分となる場合があり、一方、この値は8質量%で十分である。

#### 【0053】

[水溶性高分子]

水溶性高分子としては、エチルセルロース、メチルヒドロキシエチルセルロース、メチルヒドロキシプロピルセルロース、ヒドロキシエチルセルロース、ヒドロキシプロピルセルロース、カルボキシメチルセルロース、カルボキシメチルヒドロキシエチルセルロース等のセルロース類、ポリエチレングリコール、ポリエチレンイミン、ポリビニルピロリドン

10

20

30

40

50

、ポリビニルアルコール、ポリアクリル酸およびその塩、ポリアクリルアミド、ポリエチレンオキシド等の水溶性高分子が挙げられ、これらのうち、セルロース類、およびポリアクリル酸およびその塩が好ましく、さらに好ましくはヒドロキシエチルセルロースおよびカルボキシメチルセルロースである。これらも水溶性高分子は単独で使用することが出来、また、2種類以上を混合して使用することが出来る。

#### 【0054】

##### [水溶性高分子-最適質量]

水溶性高分子の配合量は、成分配合型および2液混合型水系分散体の各々の総量に対して0.005~5質量%とすることができる、0.005~3質量%が好ましく、さらに0.008~2質量%が好ましく、特に0.01~1質量%が好ましい。水溶性高分子の配合量が、0.005質量未満%である場合、ディッシング、エロージョンの抑制効果は不十分となる場合があり、また、ウエハー表面欠陥が増加する場合があり、一方、この値が5質量%で十分である。

#### 【0055】

##### [砥粒]

砥粒としては、無機粒子、有機粒子および有機無機複合粒子が挙げられる。上記無機粒子としては、二酸化ケイ素、酸化アルミニウム、酸化セリウム、酸化チタン、酸化ジルコニアム、窒化ケイ素、および二酸化マンガン等が挙げられる。これらのうち、二酸化ケイ素が好ましい。このような二酸化ケイ素として具体的には、気相中に塩化ケイ素などを酸素および水素と反応させるヒュームド法により合成させたヒュームドシリカ、金属アルコキシドを加水分解し、縮合するゲルゾル法により合成させたコロイダルシリカ、精製により不純物を除去する無機コロイダル法等により合成させたコロイダルシリカなどが挙げられる。

#### 【0056】

上記有機粒子としては(1)ポリスチレンおよびスチレン系共重体、(2)ポリメチルメタクリレート等のアクリル樹脂、およびアクリル系共重体、(3)ポリ塩化ビニル、ポリアミド、ポリイミド、ポリカーボネード、フェノキシ樹脂ならびに(4)ポリエチレン、ポリプロピレン等の共重体からなる粒子を使用することが出来る。これらのうち(1)ポリスチレンおよびスチレン系共重体、(2)ポリメチルメタクリレート等のアクリル樹脂、およびアクリル系共重体が好ましい。

#### 【0057】

##### [砥粒-最適粒子径]

成分配合型および2液混合型水系分散体に用いる砥粒の好ましい粒子径に関して説明する。粒子は、例えばゲルゾル法またはコロイド法により合成されたコロイダルシリカなど、比較的小粒子径の場合は成分配合型および2液混合型水系分散体中で一次粒子が会合、または凝集した状態(二次粒子)で存在していることが多いと考えられている。このときの平均一次粒子径としては1~3000nmが好ましく、2~1000nmがさらに好ましい。また、平均二次粒子径は5~5000nmが好ましく、5~3000nmがさらに好ましく、特に10~1000nmである事が好ましい。平均二次粒子径が5nm未満であると、研磨速度が不十分となる場合がある。一方、この値が5000nmを超える場合、ディッシング、エロージョンの抑制効果が不十分となる場合がある。また、ウエハー表面にスクラッチ等が発生し表面欠陥増加の要因となる場合がある。

#### 【0058】

一方、ヒュームド法により合成されたシリカなどの粒子は元々二次粒子の形で製造されそれを成分配合型および2液混合型水系分散体中に一次粒子で分散させることは非常に困難なことから、上記同様一次粒子が凝集し二次粒子として存在すると考えられる。そのため、ヒュームド法により合成されたシリカなどの粒子については二次粒子径のみ規定すれば足りる。ヒュームド法により合成されたシリカなどの粒子の平均二次粒子径は10~10000nmが好ましく、20~7000nmがさらに好ましく、特に50~5000nmであることが好ましい。この範囲の平均二次粒子径とすることで研磨速度が速く、ディッ

10

20

30

40

50

シング、エロージョンの抑制効果が得られる。

【0059】

有機粒子は成分配合型および2液混合型水系分散体中ではほとんどが単独粒子として存在していると考えられる。有機粒子の平均粒子径は10~5000nmが好ましく、15~3000nmがさらに好ましく、特に20~1000nmである事が好ましい。この範囲を平均粒子径とすることで、研磨速度が速く、ディッシング、エロージョンの抑制効果が得られる。

【0060】

[pH]

混合型水系分散体の好ましいpHは、9~13でありさらに好ましくは9~12である。

10

pHが7より低い場合は十分な研磨性能が得られない場合があり、13を超える場合は混合型水系分散体の安定性が低下する場合があるため好ましくない。2液を混合して使用する場合の混合後の水系分散体全体のpHが上記と同様の範囲となればよく、それぞれの水系分散体のpHは限定されない。

【図面の簡単な説明】

【0061】

【図1】本発明の一実施例に係る半導体装置の製造プロセスを示す図である。

【図2】本発明の一実施例に係る半導体装置の製造プロセスを示す図である。

【図3】図2(c)において、「A」で示す部分の拡大図である。

【図4】本発明の一実施例に係る半導体装置の製造プロセスを示す図である。

【図5】本発明の一実施例に係る半導体装置の製造プロセスを示す図である。

【図6】本発明の一実施例に係る半導体装置の製造プロセスを示す図である。

【図7】素子分離用絶縁膜と下地の第1のシリコン膜とでなる溝形状の開口領域が逆テーパーになっている半導体装置の断面図である。

【図8】開口領域のみに選択的にポリシリコンを成長させ、ポリシリコン膜を成膜した半導体装置の断面図である。

【図9】ポリシリコン膜の成膜方法の違いによるCMP後の平坦性を比較した結果を示すグラフである。

【図10】ステップ・ハイトの定義を示す図である。

【図11】ポリシリコン膜の成膜方法の違いによる絶縁膜の研磨量比較結果を示すグラフである。

30

【図12】本発明の一実施例に係る不揮発性半導体記憶装置の概略構成図である。

【図13】図12に示す不揮発性半導体記憶装置のメモリセルアレイの概略回路構成を示す図である。

【図14】平坦化特性の膜厚依存を示す図である。

【符号の説明】

【0062】

- |             |          |

|-------------|----------|

| 1           | シリコン基板   |

| 1 0         | 酸化膜      |

| 1 1         | 第1のシリコン膜 |

| 1 2         | 窒化珪素膜    |

| 1 3         | 第2のシリコン膜 |

| 1 4         | 第3のシリコン膜 |

| 2 1         | マスク材     |

| 2 2 a、2 2 b | 絶縁膜      |

| 2 0 4       | シリコン膜    |

| 2 0 5       | v o i d  |

40

【図 1】

【図 3】

【図 2】

【図 4】

22b 素子分離用絶縁膜

13 Si膜

【図5】

【図6】

【図7】

【図8】

【 四 9 】

【 図 1 0 】

| $1/\mu\text{m}$ | Step height (nm) - Circles | Step height (nm) - Diamonds |

|-----------------|----------------------------|-----------------------------|

| 0.00            | 0                          | 0                           |

| 0.02            | -10                        | -10                         |

| 0.04            | -20                        | -20                         |

| 0.05            | -25                        | -25                         |

| 0.06            | -20                        | -20                         |

| 0.08            | -10                        | -10                         |

| 0.10            | 0                          | 0                           |

| 0.12            | 10                         | 10                          |

| 0.14            | 20                         | 20                          |

| 0.15            | 30                         | 30                          |

【 図 1 2 】

【 図 1 3 】

【図 1 1】

(a) (b)

【図14】

(b)

(a)

---

フロントページの続き

(72)発明者 松井 之輝

神奈川県横浜市磯子区新杉田町 8 番地 株式会社東芝横浜事業所内

(72)発明者 西岡 岳

神奈川県横浜市磯子区新杉田町 8 番地 株式会社東芝横浜事業所内

(72)発明者 矢野 博之

神奈川県横浜市磯子区新杉田町 8 番地 株式会社東芝横浜事業所内

F ターム(参考) 5F083 EP04 EP27 EP55 EP76 JA04 JA19 JA33 JA39 LA03 LA04

LA05 LA10 LA12 LA16 NA01 NA06 PR03 PR05 PR21 PR25

PR29 PR40

5F101 BA16 BA29 BA36 BB05 BD02 BD34 BD35 BH02 BH11 BH14

BH15 BH19