(19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2012-208804 (P2012-208804A)

(43) 公開日 平成24年10月25日(2012.10.25)

(51) Int.Cl.

FI

テーマコード (参考)

GO6F 1/06 (2006.01)

GO6F 1/04 31OA

5B079

審査請求 未請求 請求項の数 4 〇L (全 12 頁)

(21) 出願番号 (22) 出願日 特願2011-74838 (P2011-74838) 平成23年3月30日 (2011.3.30) (71) 出願人 308033711

ラピスセミコンダクタ株式会社

東京都八王子市東浅川町550番地1

(74)代理人 100079119

弁理士 藤村 元彦

(74)代理人 100109036

弁理士 永岡 重幸

(74)代理人 100147728

弁理士 高野 信司

(72) 発明者 夏目 賢一

東京都八王子市東浅川町550番地1 0

KIセミコンダクタ株式会社内

Fターム(参考) 5B079 BA15

(54) 【発明の名称】 クロック信号生成回路

# (57)【要約】

【目的】電源投入時点から高速に起動し且つ外乱が生じてもクロック信号の生成を継続することが可能なクロック信号生成回路を提供することを目的とする。

【構成】本発明においては、低速クロック信号及び高速クロック信号を夫々生成するにあたり、高速クロック信号の発振源となる第1発振回路において生成された第1発振クロック信号を上記高速クロック信号として出力する。また、低速クロック信号の発振源となる第2発振回路から第2発振クロック信号が送出されている場合にはこの第2発振クロック信号を上記低速クロック信号として出力する一方、第2発振クロック信号が送出されていない場合には、上記第1発振クロック信号を分周した分周クロック信号を低速クロック信号として出力する。

【選択図】図1

# 【特許請求の範囲】

### 【請求項1】

第 1 周波数を有する高速クロック信号及び前記第 1 周波数よりも低い第 2 周波数を有する低速クロック信号を夫々生成するクロック信号生成回路であって、

前記第1周波数を有する第1発振クロック信号を生成する第1発振回路と、

前記第2周波数を有する第2発振クロック信号を生成する第2発振回路と、

前記第1発振クロック信号を分周した分周クロック信号を生成する分周回路と、

前記第1発振クロック信号を前記高速クロック信号として出力すると共に、前記第2発振回路から前記第2発振クロック信号が送出されている場合には当該第2発振クロック信号を前記低速クロック信号として出力する一方、前記第2発振回路から前記第2発振クロック信号が送出されていない場合には前記分周クロック信号を前記低速クロック信号として出力するクロック選択回路と、を有することを特徴とするクロック信号生成回路。

### 【請求項2】

前記第2発振クロック信号に位相同期し且つ前記第1周波数を有する第3発振クロック信号を生成する第3発振回路を更に備え、

前記クロック選択回路は、電源投入時点から所定期間の経過前においては前記第1発振クロック信号を前記高速クロック信号として出力し、前記電源投入時点から前記所定期間が経過した後は、前記第1発振クロック信号に代えて前記第3発振クロック信号を前記高速クロック信号として出力することを特徴とする請求項1に記載のクロック信号生成回路

#### 【請求項3】

前記第2発振回路は水晶又はセラミック発振回路であり、前記第1発振回路は抵抗及びコンデンサからなるCR発振回路であり、前記第3発振回路はPLL発振回路であり、

前記所定期間は、前記電源投入に応じて前記第2発振回路が前記第2発振クロック信号の送出を開始し、当該第2発振クロック信号に応じて前記第3発振回路が前記第3発振クロック信号の送出を開始するまでの期間であることを特徴とする請求項2記載のクロック信号生成回路。

# 【請求項4】

前記第3発振回路は、前記第2発振回路から前記第2発振クロック信号が送出されている場合には前記第2発振クロック信号に位相同期し且つ前記第1周波数を有する前記第3発振クロック信号を生成する一方、前記第2発振回路から前記第2発振クロック信号が送出されていない場合には前記分周クロック信号に位相同期し且つ前記第1周波数を有する前記第3発振クロック信号を生成することを特徴とする請求項3記載のクロック信号生成回路。

# 【発明の詳細な説明】

# 【技術分野】

#### [00001]

本発明は、クロック信号生成回路、特に周波数が互いに異なる複数のクロック信号を生成するクロック信号生成回路に関する。

# 【背景技術】

#### [00002]

半導体集積装置(以下、LSIと称する)に構築される信号処理回路においては、高速処理が必要となる場合には高周波数のクロック信号で動作させる一方、高速処理が不要となる場合には低周波数のクロック信号で動作させることにより、低消費電力及び高速処理を実現するようにしている。

#### [0003]

このようなクロック信号を生成すべくこのLSI内に構築される発振回路としては、水晶/セラミック発振回路、PLL(Phase Locked Loop)発振回路、コンデンサ及び抵抗からなるCR発振回路が用いられる。CR発振回路は、電源投入時点からその発振周波数が安定するまでの待ち時間が水晶/セラミック発振回路、及びPLL発

10

20

30

30

40

振回路よりも短いという特長を有する。また、PLL発振回路は、発振安定待ち時間がCR発振回路より長いものの、比較的高い周波数まで発振可能であるという特長を有する。水晶/セラミック発振回路は、その発振周波数自体は水晶振動子の特性によって決まるため、基本的には変更できないが、高精度の発振信号を生成することが可能である。

[0004]

ここで、夫々の特長が有効となるように上記したCR発振回路、PLL発振回路、及び水晶発振回路を組み合わせることにより、低消費電力で且つ発振安定待ち時間を短縮したクロック信号生成回路が提案された(例えば、特許文献1の図9参照)。このクロック信号生成回路では、水晶発振回路で生成した低周波数のクロック信号CLK1を上記した信号処理回路に供給する。また、CR発振回路が、高周波数を有する第1のクロック信号CLK11を生成する。更に、水晶発振回路で生成された低周波数のクロック信号CLK1 に基づき、PLL発振回路が高周波数の第2のクロック信号CLK12を生成する。この際、動作開始時には、発振安定期間が比較的短いCR発振回路にて生成された第1のクロック信号CLK11を信号処理回路に供給し、この間、PLL発振回路が生成した第0つのクロック信号CLK12を信号処理回路に供給するのである(例えば、特許文献1の図15参照)。

[00005]

しかしながら、上記した如きクロック信号生成回路では、水晶発振回路における電源投入時点からその発振動作が安定するまでに費やされる発振安定期間が数百msと長いため、低周波数のクロック信号CLK1で動作する回路ブロックの起動時間が長くなってしまう

[0006]

また、水晶発振回路を動作させるべくLSIに外部接続されている水晶振動子は、電磁波や振動等の外部ノイズや、水分、埃・ゴミ等による端子間ショート等の外乱の影響を受け易く、この外乱によって水晶振動子が停止してしまうと、PLL発振回路において第2のクロック信号CLK12の生成が為されなくなる。よって、信号処理回路が用いるべきクロック信号が第1のクロック信号CLK11から第2のクロック信号CLK12に切り替わった途端、信号処理回路が動作停止状態になってしまう場合があった。

【先行技術文献】

【特許文献】

[0007]

【特許文献 1 】特開 2 0 0 1 - 3 4 4 0 3 9 号公報

【発明の概要】

【発明が解決しようとする課題】

[0008]

本発明は、かかる問題を解決すべく為されたものであり、電源投入時点から高速に起動し且つ外乱が生じてもクロック信号の生成を継続することが可能なクロック信号生成回路を提供することを目的とする。

【課題を解決するための手段】

[0009]

本発明によるクロック信号生成回路は、第1周波数を有する高速クロック信号及び前記第1周波数よりも低い第2周波数を有する低速クロック信号を夫々生成するクロック信号を生成する第1発振回路と、前記第1周波数を有する第1発振クロック信号を生成する第2発振回路と、前記第1発振クロック信号を分周した分周クロック信号を生成する分周回路と、前記第1発振クロック信号を分周した分周クロック信号を生成する分周回路と、前記第1発振クロック信号を前記高速クロック信号として出力すると共に、前記第2発振回路から前記第2発振クロック信号を前記低速クロック信号として出力するクロック信号として出力するクロック信号として出力するクロック信号として出力するクロックによい場合には前記分周クロック信号を前記低速クロック信号として出力するクロックに

10

20

30

40

ク選択回路と、を有する。

【発明の効果】

[0010]

本発明においては、第1発振回路で生成された高周波数の第1発振クロック信号を高速クロック信号、第2発振回路で生成された低周波数の第2発振クロック信号を低速クロック信号として夫々出力するにあたり、第2発振回路から第2発振クロック信号が送出されていない場合には、上記第1発振クロック信号を分周した分周クロック信号を低速クロック信号として出力するようにしている。ここで、第1発振回路をCR発振回路、第2発振回路を水晶又はセラミック発振回路で構築すると、電源投入直後は、第2発振回路に比して短期間で発振状態が安定する第1発振回路で生成された第1発振クロック信号を分周した分周クロック信号が低速クロック信号となる。

(4)

[0011]

これにより、電源投入後、水晶又はセラミック発振回路の発振動作が安定する前に、低速クロック信号を送出することが出来るので、この低速クロック信号で動作する信号処理回路を直ちに起動させることが可能となる。そして、第2発振回路の発振動作が安定したら、上記した分周クロック信号に代えてこの第2発振回路で生成された高精度な第2発振クロック信号が低速クロック信号として信号処理回路に供給されるようになる。

[0012]

また、第2発振回路の発振動作が安定した後、例え外乱の影響により水晶又はセラミック発振器が動作不能状態に陥っても、この際、上記第2発振クロック信号に代えて分周クロック信号が低速クロック信号となるので、この低速クロック信号で動作する信号処理回路を継続して動作させることが可能となる。

【図面の簡単な説明】

[ 0 0 1 3 ]

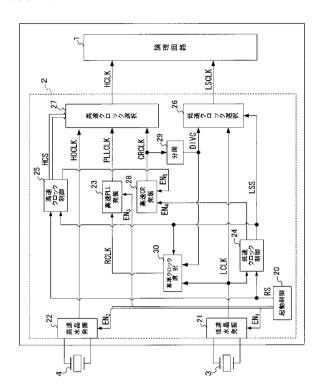

【図1】本発明に係るクロック信号生成回路が構築されているLSIの内部構成を示すブロック図である。

- 【図2】図1に示されるクロック信号生成回路の動作を示すタイムチャートである。

- 【図3】図1に示されるクロック信号生成回路の変形例を示すブロック図である。

- 【図4】図3に示されるクロック信号生成回路の動作を示すタイムチャートである。

【発明を実施するための形態】

[0014]

本発明によるクロック信号生成回路は、低速クロック信号及び高速クロック信号を夫々生成するにあたり、高速クロック信号の発振源となる第1発振回路において生成された第1発振クロック信号を上記高速クロック信号として出力する。また、低速クロック信号の発振源となる第2発振回路から第2発振クロック信号が送出されている場合にはこの第2発振クロック信号を上記低速クロック信号として出力する一方、第2発振クロック信号が送出されていない場合には、上記第1発振クロック信号を分周した分周クロック信号を低速クロック信号として出力する。

【実施例】

[0015]

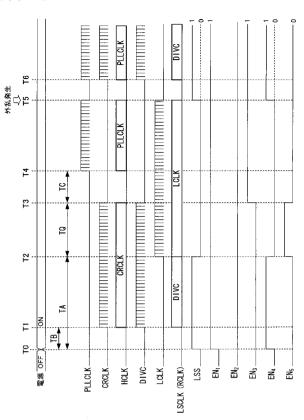

図1は、本発明に係るクロック信号生成回路が搭載されているLSIの内部構成を示すブロック図である。

[0016]

図1に示すように、かかるLSIには、このLSIの主となる各種信号処理を行う論理回路部1と、この論理回路部1を動作させる為の高速クロック信号HCLK及びこの高速クロック信号HCLKよりも低周波数の低速クロック信号LSCLKを生成して論理回路部1に供給するクロック信号生成部2と、が構築されている。尚、このLSIには、上記した低速クロック信号LSCLKの発振源となる低周波数の発振信号を発生する第1水晶発振器3と、かかる低速クロック信号LSCLKよりも高周波数の発振信号を生成する第2水晶発振器4と、が外部接続されている。

10

20

30

40

### [0017]

クロック信号生成部2において、起動制御回路20は、発振動作を実行させる場合には論理レベル1、発振動作を停止させる場合には論理レベル0を有する発振イネーブル信号EN1~EN3を夫々、低速水晶発振回路21、高速水晶発振回路22及び高速PLL(Phase Locked Loop)発振回路23の各々に供給する。また、起動制御回路20は、電源投入に応じてリセットパルス信号RSを生成しこれを低速クロック制御回路24及び高速クロック制御回路25の各々に供給する。

### [0018]

低速水晶発振回路21は、論理レベル1の発振イネーブル信号EN」が供給されている間は、第1水晶発振器3から供給された発振信号に基づき低周波数の発振クロック信号LCLKを生成し、これを高速PLL発振回路23、低速クロック制御回路24、及び低速クロック選択回路26の各々に供給する。尚、論理レベル0の発振イネーブル信号EN」が供給されている間は、低速水晶発振回路21は、その発振動作を停止して上記した発振クロック信号LCLKの生成動作を停止する。

#### [0019]

低速水晶発振回路 2 1 は、上記した如き発振イネーブル信号 E N <sub>1</sub> が論理レベル 0 から論理レベル 1 に推移したことによる起動開始指令に応じて発振動作を開始し、この起動開始指令が発令されてから発振安定期間 T A (後述する)の経過後、上記した発振クロック信号 L C L K を安定して送出し得る状態に到る。

# [0020]

高速水晶発振回路22は、論理レベル1の発振イネーブル信号EN2が供給されている間は、第2水晶発振器4から供給された発振信号に基づき高周波数の発振クロック信号HOCLKを生成し、これを高速クロック選択回路27に供給する。尚、論理レベル0の発振イネーブル信号EN2が供給されている間は、高速水晶発振回路22は、その発振動作を停止して上記した発振クロック信号HOCLKの生成動作を停止する。

### [0021]

高速PLL発振回路23は、論理レベル1の発振イネーブル信号EN<sub>3</sub>が供給されている間は、上記した発振クロック信号LCLKを基準クロックとし、その位相に同期させて、かかる発振クロック信号LCLKよりも高周波数の発振クロック信号PLLCLKを生成し、これを高速クロック選択回路27に供給する。尚、論理レベル0の発振イネーブル信号EN<sub>2</sub>が供給されている間は、高速PLL発振回路23は、その発振動作を停止して上記した発振クロック信号PLLCLKの生成動作を停止する。

#### [0022]

高速PLL発振回路23は、上記した如き発振イネーブル信号EN<sub>3</sub>が論理レベル0から論理レベル1に推移したことによる起動開始指令に応じて発振動作を開始し、この起動開始指令が発令されてから発振安定期間TC(後述する)の経過後、上記した発振クロック信号PLLCLKを安定して送出し得る状態に到る。

### [0023]

低速クロック制御回路24は、リセットパルス信号RSに応じて、先ず、分周クロック信号DIVC(後述する)を選択させるべき論理レベル1の低速クロック選択制御信号LSSを低速クロック選択回路26に供給する。次に、低速クロック制御回路24は、低速クロック信号LCLKの供給が為されている否かを検出し、発振クロック信号LCLKの供給が為されている。この発振クロック信号LCLKの供給が停止したら、低速クロック選択制御信号LSSを低速クロック選択回路26に供給する。この間、発振クロックに受してLKの供給が停止したら、低速クロックに受してLKの供給が停止したら、低速クロックに受してを選択させるべき論理レベル1の状態に切り替える。尚、低速クロック制御回路24は、上記した如き低速クロック制御回路24は、低速水晶発振回路21から発振クロック信号LCLKの供給が為されていない場合には、発振動作を実行させるべき論理レベル1の発振

10

20

30

40

イネーブル信号ENュを高速CR発振回路28に供給する。

#### [0024]

高速 C R 発振回路 2 8 は、低速クロック制御回路 2 4 から論理レベル 1 の発振イネーブル信号 E N 4 が供給されている間、又は高速クロック制御回路 2 5 から論理レベル 1 の発振イネーブル信号 E N 5 が供給されている間だけ、抵抗及びコンデンサによる発振動作を実行する。かかる発振動作により、高速 C R 発振回路 2 8 は、発振クロック信号 L C L K よりも高周波数の発振クロック信号 C R C L Kを生成し、これを高速クロック選択回路 2 7 及び分周回路 2 9 の各々に供給する。

### [0025]

高速CR発振回路28は、上記した如き発振イネーブル信号EN4が論理レベル0から論理レベル1に推移したことによる起動開始指令に応じて発振動作を開始し、この起動開始指令が発令されてから発振安定期間TB(後述する)の経過後、上記した発振クロック信号CRCLKを安定して送出し得る状態に到る。

#### [0026]

高速クロック制御回路25は、リセットパルス信号RSに応じて、先ず、高速CR発振回路28から供給された発振クロック信号CRCLKを選択させるべき高速クロック調打回路27に供給する。その後、高速クロック制御回路25は、クロック選択制御処理に従って、上記発振クロック信号CRCLK、発振クロック信号PLLCLK、及び発振クロック信号CRCLKの内から1つを選択させる。ただりロック選択制御信号HCSを生成し、高速クロック選択回路27に供給する。ただだ別御信号LSSが供給された場合、つまり発振クロック信号LCLKの供給が為された場合、つまり発振クロック信号LRCLKを選択には、高速クロック制御回路25は、発振クロック信号CRCLKを選択になる。更には治さの選択制御処理に従って、高速クロック制御回路25は、発振動作を実行させる場合には治理レベル1、その発振動作を停止させる場合には治理レベル0を有する発振イネーブル信号EN。を高速CR発振回路28に供給する。

#### [0027]

高速クロック選択回路27は、上記発振クロック信号CRCLK、発振クロック信号PLLCLK、及び発振クロック信号CRCLK各々の内から、上記した高速クロック選択制御信号HCSにて示される1つを選択し、これを高速クロック信号HCLKとして論理回路部1に供給する。

### [0028]

分周回路29は、高速CR発振回路28から供給された発振クロック信号CRCLKを1/N分周(Nは自然数)した分周クロック信号DIVCを生成し、これを低速クロック選択回路26に供給する。この際、分周回路29では、分周クロック信号DIVCの周波数が、上記した発振クロック信号LCLKの周波数と一致、又はその周波数に最も近い周波数となるように発振クロック信号CRCLKを分周する。例えば、発振クロック信号CRCLKの周波数が32.768KHzである場合には、上記分周Nを ″ 1 6 ″に設定する。これにより、分周クロック信号DIVCの周波数は、(500KHz/16)=31.25KHzとなる。

#### [0029]

低速クロック選択回路26は、上記した分周クロック信号DIVC、及び低速水晶発振回路21から供給された発振クロック信号LCLKの内から、上記した低速クロック選択制御信号LSSによって示される方を択一的に選択し、これを低速クロック信号LSCLKとして論理回路部1に供給する。

#### [0030]

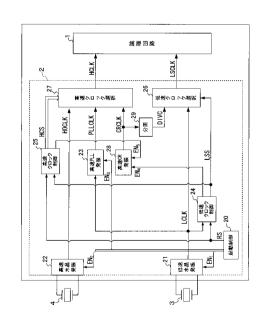

以下に、図1に示されるクロック信号生成部2の動作について、図2を参照しつつ説明する。

# [0031]

10

20

30

10

20

30

40

50

先ず、図2に示す如き時点T0において電源が投入されると、起動制御回路20は、発振動作を実行させるべき論理レベル1の発振イネーブル信号EN1を低速水晶発振回路21に供給すると共に、発振動作を停止させるべき論理レベル0の発振イネーブル信号EN22及びEN3を夫々高速水晶発振回路22及び高速PLL発振回路23の各々に供給する。時点T0にて供給された論理レベル1の発振イネーブル信号EN1に応じて低速水晶発振回路21は発振動作を開始し、発振安定期間TA(例えば数百ms)を経た時点T2において発振クロック信号LCLKの送出状態に到る。よっていないので、この間、低速日には、の分制御回路24は、発振動作を実行させるべき論理レベル1の発振イネーブル信号EN4を高速CR発振回路28に供給する。これにより、高速CR発振回路28は発振動作を開始し、発振安定期間TB(例えば数十μs)を経た時点T1において発振クロック信号NNAを高速CR発振回路28に供給する。11N分周した分周クロック信号DIVCを低速クロック選択回路26に供給する。

[0032]

更に、時点T0での電源投入に応じて、起動制御回路20は、リセットパルス信号RSを低速クロック制御回路24及び高速クロック制御回路25の各々に供給する。かかるリセットパルス信号RSに応じて、高速クロック制御回路25は、上記発振クロック信号CRCLKを選択させるべき高速クロック選択制御信号HCSを高速クロック選択回路27に供給し、低速クロック制御回路24は、上記分周クロック信号DIVCを選択させるべき論理レベル1の低速クロック選択制御信号LSSを低速クロック選択回路26に供給する。よって、図2に示す如く、時点T1以降、高速CR発振回路28によって生成された発振クロック信号CRCLKが高速クロック信号HCLKとして論理回路部1に供給される。

[0033]

ここで、図2に示す時点T2において発振クロック信号LCLKの生成が為されるようになると、低速クロック制御回路24は、低速クロック選択回路26に供給すべき低速クロック選択制御信号LSSの状態を、発振クロック信号LCLKを選択させるべき論理レベル0の状態に切り替える。更に、この際、低速クロック制御回路24は、発振イネーブル信号EN4の状態を発振動作を停止させるべき論理レベル0の状態に切り替える。これにより、上記した分周クロック信号DIVCに代えて、低速水晶発振回路21において生成された発振クロック信号LCLKが低速クロック信号LSCLKとして論理回路部1に供給される。尚、時点T2において、低速クロック選択制御信号LSSが論理レベル1の状態がら論理レベル0の状態に推移すると、これに応じて、高速クロック制御回路25は、発振動作を実行すべき論理レベル1の発振イネーブル信号EN5を高速CR発振回路28に供給する。よって、高速CR発振回路28は、時点T2以降も引き続き発振クロック信号CRCLKの生成動作を継続する。

[0034]

そして、時点T2において低速クロック選択制御信号LSSが論理レベル1の状態から論理レベル0の状態に切り替わってから所定期間TQだけ経過した時点T3において、高速クロック制御回路25は、高速CR発振回路28に供給する発振イネーブル信号EN5を論理レベル1の状態から、発振動作を停止させるべき論理レベル0の状態に切り替える。これにより、高速CR発振回路28における発振クロック信号CRCLKの生成が停止する。と共に、分周回路29による分周クロック信号DIVCの生成動作が停止する。更に、かかる時点T3では、起動制御回路20が、発振動作を実行させるべき論理レベル1の発振イネーブル信号EN3を高速PLL発振回路23に供給する。これにより、高速PLL発振回路23は発振動作を開始し、上記時点T3から発振安定期間TC(例えば数ms)を経た時点T4において発振クロック信号PLLCLKの送出状態に到る。更に、上記時点T3において、高速クロック制御回路25が、高速PLL発振回路23で生成された発振クロック信号PLLCLKを選択させるべき高速クロック選択制御信号HCSを高速

クロック選択回路27に供給する。よって、図2に示すように、時点T4以降、高速PLL発振回路23で生成された発振クロック信号PLLCLKが高速クロック信号HCLKとして論理回路部1に供給されるようになる。

### [0035]

ここで、時点T5において、電磁波や振動等の外部ノイズ、或いは水分、埃・ゴミ等による端子間ショート等の外乱が発生し、それに伴い、LSIに外付けされている第1クロの発振器3が停止してしまうと、低速水晶発振回路21では発振動作が停止し、発振発回路21では発振動作が停止し、発振発回路21から発振クロック信号LCLKの送出が為されなくなる。低速クロック制御回路24は、低速水晶発、図21から発振クロック信号LCLKの送出が為されなくなたことを検出すると、本場図2において、発振動作を開始し、発振回路28に供給する。これにより、高速CR発振回路2月は、発振動作を開始し、発振安定期間TB(例えば数十μs)を経た時点T6において信号LCLKの送出状態に到る。これにより、モポークにおいて生成とロック信号LCLKの周波数と同一又は略等しい周波数を有する分周クロック信号LCLKの周波数と同一又は略等しい周波数を有する分周クロック信号LCLKの周波数と同一又は略等しい周波数を有する分周クロック信号LCLKの周波数と同一又は略等しい周波数を有する分周クロック信号LCLKの周波数と同一又は略等しい周波数を有する分周クロックに受力ロックに対し、これを低速クロック選択回路26及び高速クロック制御回路25に供給する。

# [0036]

これにより、例え第1水晶発振器3が停止してしまっても、図2に示す時点T6以降、分周回路29にて生成された分周クロック信号DIVCが低速クロック信号LSCLKとして論理回路部1に供給されると共に、高速CR発振回路28にて生成された発振クロック信号PLLCLKが高速クロック信号HCLKとして論理回路部1に供給されるようになる。

### [0037]

以上の如く、上記したクロック信号生成部2では、電源投入時点T0から低速水晶発振回路21の発振動作が安定する時点T2までの発振安定期間TA中は、発振安定期間TBが比較的短い高速CR発振回路28にて生成された発振クロック信号CRCLKを、高速クロック信号HCLKとして論理回路部1に供給する。更に、この高速CR発振回路28において生成された発振クロック信号CRCLKを1/N分周することにより、低速水晶発振回路21で生成されるべき発振クロック信号LCLKの周波数と同一又は略等しい周波数を有する分周クロック信号DIVCを生成し、これを低速クロック信号LSCLKとして論理回路部1に供給するようにしている。

### [0038]

すなわち、電源投入後、水晶発振回路 2 1 の発振動作が安定するまでの間は、高速クロック信号 H C L K を生成すべく設けられた高速 C R 発振回路 2 8 で生成された発振クロック信号 C R C L K を 1 / N 分周して低周波数化したものを、低速クロック信号 L S C L K として論理回路部 1 に供給している。

### [0039]

よって、論理回路部 1 中において低速クロックのみ、或いは低速及び高速クロックの両方で動作する回路の起動時間を短縮することが可能となる。

# [0040]

また、上記したクロック信号生成部 2 では、低速水晶発振回路 2 1 の発振動作が安定する時点 T 2 以降は、上記分周クロック信号 D I V C に代えて、この低速水晶発振回路 2 1 において生成された発振クロック信号 L C L K を、低速クロック信号 L S C L K として論理回路部 1 に供給する。

# [0041]

その後、低速水晶発振回路 2 1 から発振クロック信号LCLKの送出が為されなくなったことを検出したとき(時点 T 5 )には、高速 C R 発振回路 2 8 及び分周回路 2 9 を再び

10

20

30

40

起動させる。そして、この分周回路 2 9 で生成された分周クロック信号 D I V C を低速クロック信号 L S C L K、この高速 C R 発振回路 2 8 で生成された発振クロック信号 C R C L K を高速クロック信号 H C L K として、夫々論理回路部 1 に供給する動作に自動的に切り替える(時点 T 6 )ようにしている。

### [0042]

これにより、例えLSIに外部接続されている低速クロック用の第1水晶発振器3、及び高速クロック用の第2水晶発振器4が外乱により振動停止してしまっても、低速クロック信号LSCLK及び高速クロック信号HCLKを継続して論理回路部1に供給することが可能となる。

# [0043]

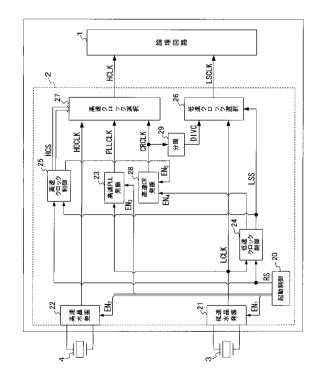

図3は、図1に示されるクロック信号生成部2の変形例を示す図である。

# [0044]

尚、図3に示されるクロック信号生成部2においては、基準クロック選択回路30を設けた点を除く他の構成は、図2に示されるものと同一である。

#### [0045]

よって、以下に、基準クロック選択回路30の動作を中心に、図3に示されるクロック信号生成部2の動作について説明する。

#### [0046]

基準クロック選択回路30は、低速水晶発振回路21から送出された上記発振クロック信号LCLK、及び分周回路29から送出された上記分周クロック信号DIVCの内から、上記低速クロック選択制御信号LSSによって示される方を択一的に選択し、これを基準発振クロック信号RCLKとして高速PLL発振回路23に供給する。よって、高速PLL発振回路23は、この基準発振クロック信号RCLKの位相に同期させて、かかる基準発振クロック信号RCLKよりも高周波数の発振クロック信号PLLCLKを生成し、これを高速クロック選択回路27に供給する。

### [0047]

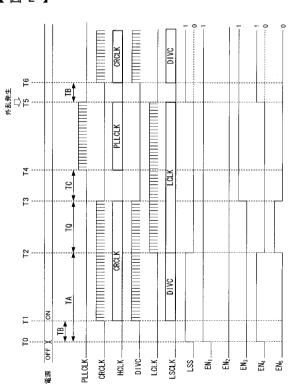

以下に、図3に示されるクロック信号生成部2の動作について、図4を参照しつつ説明する。

# [0048]

先ず、図4に示す如き時点T0において電源が投入されると、起動制御回路20は、発振動作を実行させるべき論理レベル1の発振イネーブル信号EN1を低速水晶発振回路21 は入び高速PLL発振回路23に夫々供給すると共に、発振動作を停止させるべき論理レベル0の発振イネーブル信号EN1に応じて低速水晶発振回路21は、発振動作を開始し、発振安定期間TAを経た時点T2において発振クロック信号LCLKが成場に到る。よって、時点T0~T2の期間中は、発振クロック信号LCLKが成成された状態とはなっていないので、この間、低速クロック制御回路24は、発振動作を成立れた状態とはなっていないので、この間、低速クロック制御回路28に供給する。これにより、高速CR発振回路28は発振動作を開始し、発振安定期間TBを経た時点T1において発振クロック信号CRCLKの送出状態に到る。この際、分周回路29は、発振クロック信号CRCLKを1/N分周した分周クロック信号DIVCを低速クロック選択回路26及び基準クロック選択回路30に供給する。

# [0049]

更に、時点T0での電源投入に応じて、起動制御回路20は、リセットパルス信号RSを低速クロック制御回路24及び高速クロック制御回路25の各々に供給する。かかるリセットパルス信号RSに応じて、高速クロック制御回路25は、上記発振クロック信号CRCLKを選択させるべき高速クロック選択制御信号HCSを高速クロック選択回路27に供給し、低速クロック制御回路24は、上記分周クロック信号DIVCを選択させるべき論理レベル1の低速クロック選択制御信号LSSを低速クロック選択回路26及び基準クロック選択回路30に供給する。よって、図4に示す如く、時点T1以降、高速CR発

10

20

30

40

振回路28によって生成された発振クロック信号CRCLKが高速クロック信号HCLKとして論理回路部1に供給されると共に、分周回路29によって生成された分周クロック信号DIVCが低速クロック信号LSCLKとして論理回路部1に供給される。尚、この際、図4に示す一例では高速PLL発振回路23を起動させていないが、ソフトウェア処理により高速PLL発振回路23を起動させ、この高速PLL発振回路23によって生成された発振クロック信号PLLCLKを高速クロック選択回路27で選択させることも可能である。

# [0050]

その後、図4に示す時点T5において前述した如き外乱が発生し、それに伴い、LSIに外付けされている第1水晶発振器3が停止してしまうと、低速水晶発振回路24は、このの発振クロック信号LCLKの生成が為されなくなる。低速クロック制御回路24は、5にまれて発振動作を実行させるべき論理レベル1の発振イネーブル信号EN4を開始し、おの路28に供給する。これにより、高速CR発振回路28は発振動作を開始し、発振の四路28に供給する。これにより、高速CRRCLKを送出するよりにより、低速のの別との関係との別とにより、の周辺数と同一又は略等のの別との別ののでは、分周クロック信号DIVCを生成し、これを低速クロック信号DIVCを生成し、これを低速クロック信号DIVCを生成し、これを低速クロック信号DIVCを生成し、これを低速クロック信号DIVCを選択させるべき論理レベル1の低速クロックとしたの選択回路26日の別とのののでで、高速PLL発振っての路26日の日ック信号DIVCを基準クロックとした発振動作を開始し、発振っての路26日の日ック信号DIVCを基準クロックにより、高速PLL発振っての路26日の日ック信号DIVCを基準クロックに発振動作を開始し、発振っての路3日のののでは、分周クロック信号DIVCを基準クロックに会り、高速PLLKの送出状態になる。

#### [0051]

よって、例え、水晶発振器(3、4)が外乱等により停止してしまっても、時点T6以降において引き続き分周クロック信号DIVCが低速クロック信号LSCLKとして論理回路部1に供給されると共に、高速PLL発振回路23で生成された発振クロック信号PLLCLKが高速クロック信号HCLKとして論理回路部1に供給される。

# [0052]

尚、低速クロック制御回路24では、低速水晶発振回路21から発振クロック信号LCLKが送出されているか否かに基づき、クロック(PLLCLK、CRCLK、DIVC、LCLK)の選択処理を実施しているが、高速水晶発振回路22が発振クロック信号HOCLKを送出しているか否かに基づきこの選択処理を実行するようにしても良い。また、上記実施例においては、低速クロック制御回路24によって発振クロック信号LCLKの停止状態の検出、及び低速クロックの選択処理を行うようにしているが、このような処理をソフトウェアによって実行することも可能である。

# [0053]

また、図2及び図3では、電源投入直後の動作を例にとってクロック信号生成部2の動作を説明したが、電源投入状態において、論理回路1の全部または一部のみが一時的に停止した状態から、通常動作に復帰する時にも同様に実施することが可能である。

# [ 0 0 5 4 ]

また、図1及び図3に示すLSIにおいては、外付けの発振器(3、4)として水晶発振器を用いているが、セラミック発振器を用いるようにしても良い。この際、低速水晶発振回路21に代えて低速セラミック発振回路を用いると共に、高速水晶発振回路22に代えて高速セラミック発振回路を用いる。

# 【符号の説明】

### [0055]

- 3 第 1 水 晶 発 振 器

- 4 第2水晶発振器

- 20 起動制御回路

10

20

30

40

- 2 1 低速水晶発振回路

- 2 2 高速水晶発振回路

- 23 高速 P L L 発振回路

- 2 4 低速クロック制御回路

- 25 高速クロック制御回路

- 2 6 低速クロック選択回路

- 27 高速クロック選択回路

- 28 高速CR発振回路

- 29 分周回路

- 3 0 基準クロック選択回路

# 【図1】

# 【図2】

【図3】

【図4】