(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6974446号

(P6974446)

(45) 発行日 令和3年12月1日(2021.12.1)

(24) 登録日 令和3年11月8日(2021.11.8)

(51) Int.Cl.

H01L 21/336 (2006.01)

H01L 29/78 (2006.01)

F 1

H01L 29/78

301H

請求項の数 13 (全 19 頁)

(21) 出願番号 特願2019-513978 (P2019-513978)

(86) (22) 出願日 平成29年8月11日 (2017.8.11)

(65) 公表番号 特表2019-530227 (P2019-530227A)

(43) 公表日 令和1年10月17日 (2019.10.17)

(86) 國際出願番号 PCT/US2017/046525

(87) 國際公開番号 WO2018/052591

(87) 國際公開日 平成30年3月22日 (2018.3.22)

審査請求日 令和2年7月17日 (2020.7.17)

(31) 優先権主張番号 15/266,840

(32) 優先日 平成28年9月15日 (2016.9.15)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ウクジン・ロー

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

最終頁に続く

(54) 【発明の名称】誘電体材料層を使用してチャネル領域に応力を加えるFinFET (Fin FET)

## (57) 【特許請求の範囲】

## 【請求項 1】

FinFET であって、

基板と、

前記基板の上に配設された第1のFin であって、

第1のソースと、

第1のドレインと、

前記第1のソースと前記第1のドレインとの間に配設された第1のチャネル領域とを備える第1のFin と、

前記第1のチャネル領域の周りに配設されたゲートと、

前記基板の上にかつ前記第1のFin の第1の側の前記第1のチャネル領域に隣接するよう配設された第1の誘電体材料層であって、前記第1のチャネル領域に応力を加える第1の誘電体材料層と、

前記基板の上にかつ前記第1の側とは異なる前記第1のFin の第2の側の前記第1のチャネル領域に隣接するよう配設された第2の誘電体材料層であって、前記第1のチャネル領域に応力を加える第2の誘電体材料層と、

前記基板の上にかつ前記第1のFin に平行に配設された第2のFin であって、

第2のソースと、

第2のドレインと、

前記第2のFin の前記第2のソースと前記第2のドレインとの間に配設された第2

10

20

のチャネル領域とを備える第2のフィンと、

前記第2のフィンの前記第2のチャネル領域の周りに配設された前記ゲートと、

前記基板の上にかつ前記第2のフィンの第2の側の前記第2のチャネル領域に隣接するよう配設された第3の誘電体材料層であって、前記第2のフィンの前記第2のチャネル領域に応力を加える第3の誘電体材料層と

を備え、

前記第2の誘電体材料層は、前記第2の誘電体材料層が前記第2のフィンの前記第2のチャネル領域に応力を加えるように、前記基板の上にかつ前記第2の側とは異なる前記第2のフィンの第1の側の前記第2のチャネル領域に隣接するよう配設され、

前記第1のフィンと前記第2のフィンとの間の距離が、32ナノメートル以下であり、

前記FinFETの活性層を囲む活性領域境界をさらに備え、前記活性層は、その上に前記ソースおよびドレインが形成された前記基板のドープ領域に対応し、前記第1の誘電体材料層、前記第2の誘電体材料層、および前記第3の誘電体材料層の各々は、前記活性領域境界内のみに配設される、FinFET。

#### 【請求項2】

前記第1の誘電体材料層の上面は、前記第1のフィンの上面よりも低く、

前記第2の誘電体材料層の上面は、前記第1のフィンの上面よりも低い、請求項1に記載のFinFET。

#### 【請求項3】

前記FinFETはN型FinFETを備え、

前記第1および第2の誘電体材料層は、前記第1および第2の誘電体材料層が前記第1のチャネル領域に引張応力を加えるように1つまたは複数の酸化物材料を含む、請求項1に記載のFinFET。

#### 【請求項4】

前記FinFETはP型FinFETを備え、

前記第1および第2の誘電体材料層は、前記第1および第2の誘電体材料層が前記第1のチャネル領域に圧縮応力を加えるように1つまたは複数の酸化物材料を含む、請求項1に記載のFinFET。

#### 【請求項5】

集積回路ICに組み込まれる、請求項1に記載のFinFET。

#### 【請求項6】

誘電体材料層を使用してチャネル領域に応力を加えるフィン電界効果トランジスタFinFETを製作するための方法であって、

第1のフィンおよび第2のフィンを備える基板を設けるステップであって、前記第1のフィンは、第1のソースと、第1のドレインと、前記第1のソースと前記第1のドレインとの間に配設された第1のチャネル領域とを備え、前記第2のフィンは、第2のソースと、第2のドレインと、前記第2のソースと前記第2のドレインとの間に配設された第2のチャネル領域とを備える、ステップと、

前記基板の上にかつ前記第1のフィンの第1の側の前記チャネル領域に隣接するよう第1の誘電体材料層を配設するステップと、

前記基板の上にかつ前記第1のフィンの第2の側の前記チャネル領域に隣接するよう第2の誘電体材料層を配設するステップであって、前記第2の側が前記第1の側とは異なる、ステップと、

前記第1のフィン、前記第2のフィン、前記第1の誘電体材料層、および前記第2の誘電体材料層の上のゲート領域内に、前記FinFETのゲート長に等しい幅を有するゲートを配設するステップとを含み、

前記第1のフィンと前記第2のフィンとの間の距離が、32ナノメートル以下であり、

前記第1の誘電体材料層を配設する前記ステップは、前記基板の上に、かつ前記FinFETの活性層を囲む活性領域境界内のみに、前記第1のフィンの第1の側の前記チャネル領域に隣接するよう前記第1の誘電体材料層を配設するステップであって、前記活性

10

20

30

40

50

層は、その上に前記ソースおよびドレインが形成された前記基板のドープ領域に対応する、ステップを含み、

前記第2の誘電体材料層を配設する前記ステップは、前記基板の上に、かつ前記活性領域境界内のみに、前記第1のフィンの前記第2の側の前記チャネル領域に隣接するよう前に前記第2の誘電体材料層を配設するステップを含む、方法。

**【請求項7】**

前記第1の誘電体材料層および前記第2の誘電体材料層をウェットアニールして前記Fin FETの前記チャネル領域に加えられる応力を調整するステップをさらに含む、請求項6に記載の方法。 10

**【請求項8】**

前記第1の誘電体材料層および前記第2の誘電体材料層をドライアニールして前記Fin FETのチャネル領域に加えられる応力を調整するステップをさらに含む、請求項7に記載の方法。 10

**【請求項9】**

前記ゲートを配設する前記ステップは、

前記Fin FETのゲート長に等しい幅を有するゲート酸化物層を前記第1のフィンおよび前記第2のフィンの上の前記ゲート領域内に配設するステップと、

前記ゲート酸化物層、前記第1の誘電体材料層、および前記第2の誘電体材料層の上のゲート領域内に、前記Fin FETの前記ゲート長に等しい幅を有するゲート誘電体材料層を配設するステップと、 20

前記ゲート誘電体材料層の上の前記ゲート領域内に、前記Fin FETの前記ゲート長に等しい幅を有する仕事関数層を配設するステップと、

前記仕事関数層の上の前記ゲート領域内に、前記Fin FETの前記ゲート長に等しい幅を有する導電層を配設するステップとを含む、請求項6に記載の方法。 20

**【請求項10】**

前記ゲート領域の第1の側の前記Fin FETのソース領域に対応する前記第1のフィンをエッチングするステップと、

前記ゲート領域の第1の側とは異なる前記ゲート領域の第2の側の前記Fin FETのドレイン領域に対応する前記第1のフィンをエッチングするステップと、

前記ソース領域においてソース材料を成長させるステップと、 30

前記ドレイン領域内でドレイン材料を成長させるステップとをさらに含む、請求項6に記載の方法。 30

**【請求項11】**

前記第1の誘電体材料層を配設する前記ステップは、流動化学気相堆積を使用して前記基板の上にかつ前記第1のフィンの前記第1の側の前記チャネル領域に隣接するように前記第1の誘電体材料層を配設するステップを含み、

前記第2の誘電体材料層を配設する前記ステップは、流動化学気相堆積を使用して前記基板の上にかつ前記第1のフィンの前記第2の側の前記チャネル領域に隣接するように前記第2の誘電体材料層を配設するステップを含む、請求項6に記載の方法。 40

**【請求項12】**

前記第1の誘電体材料層を配設する前記ステップは、流動化学気相堆積を使用して前記基板の上にかつ前記第1のフィンの前記第1の側に隣接するように1つまたは複数の酸化物材料を配設するステップを含み、

前記第2の誘電体材料層を配設する前記ステップは、流動化学気相堆積を使用して前記基板の上にかつ前記第1のフィンの前記第2の側に隣接するように1つまたは複数の酸化物材料を配設するステップを含む、請求項6に記載の方法。 40

**【請求項13】**

前記第1の誘電体材料層を配設する前記ステップは、高アスペクト比処理を使用して前記基板の上にかつ前記第1のフィンの前記第1の側の前記チャネル領域に隣接するように1つまたは複数の酸化物材料を配設するステップを含み、 50

前記第2の誘電体材料層を配設する前記ステップは、高アスペクト比処理を使用して前記基板の上にかつ前記第1のフィンの前記第2の側の前記チャネル領域に隣接するよう1つまたは複数の酸化物材料を配設するステップを含む、請求項6に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

優先権出願

本出願は、2016年9月15日に出願された「FIN FIELD EFFECT TRANSISTORS (FETs) (FINFETs) EMPLOYING DIE ELECTRIC MATERIAL LAYERS TO APPLY STRESS TO CHANNEL REGIONS」という名称の米国特許出願第15/266,840号の優先権を主張する。米国特許出願第15/266,840号は、その全体が参照により本明細書に組み込まれる。

【0002】

本開示の技術は、概してフィン電界効果トランジスタ(FET)(FinFET)に関し、詳細にはFinFETのチャネル領域に応力を加えることに関する。

【背景技術】

【0003】

トランジスタは、近代の電子デバイスにおいて本質的な構成要素である。多数のトランジスタが、多くの近代の電子デバイスにおける集積回路(IC)内に使用される。たとえば、中央処理装置(CPU)およびメモリシステムなどの構成要素はそれぞれ、論理回路およびメモリデバイス用に多数のトランジスタを使用する。

【0004】

電子デバイスの機能がより複雑になるにつれて、そのようなデバイスにより多くのトランジスタを含めることが必要になる。しかし、電子デバイスは、たとえば、メモリデバイスなどのますます小形化するパッケージ内に設けることが求められているので、より小形のICチップ内により多くのトランジスタを設ける必要がある。このようなトランジスタの数の増加は、IC内のトランジスタの小型化(すなわち、同じ空き容量内により多くのトランジスタを配置すること)に継続的に取り組むことによって実現される。具体的には、IC内の最小金属線幅を小さくすることによって(たとえば、65ナノメートル(nm)、45nm、28nm、20nmなど)ICにおけるノードサイズがスケールダウンされている。その結果、プレーナトランジスタのゲート長もスケーリング可能に短くされ、それによってトランジスタおよび相互接続部のチャネル長が短くされる。プレーナトランジスタにおけるチャネル長を短くすることには、駆動強度が高くなり(すなわち、ドレイン電流が増大し)、寄生容量が減って回路遅延が短くなるという利点がある。しかし、プレーナトランジスタにおけるチャネル長を、空乏層幅と同様な大きさに近くなるように小さくすると、性能を低下させる短チャネル効果が生じることがある。より具体的には、プレーナトランジスタにおけるSCEは、電流漏れの増大、しきい値電圧の低下、および/またはしきい値電圧ロールオフ(すなわち、より短いゲート長におけるしきい値電圧が低下する)を生じさせる。

【0005】

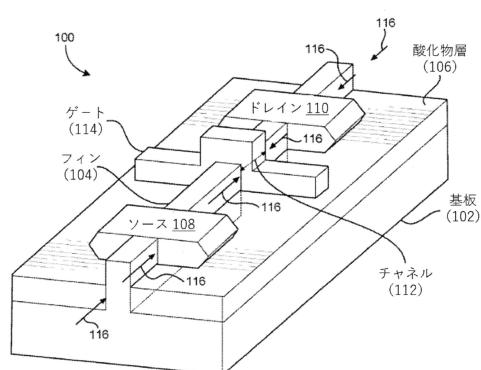

この点に関して、SCEを回避または軽減しつつトランジスタにおけるチャネル長をスケールダウンする必要に対処するために、プレーナトランジスタに代わるトランジスタ構成が開発されている。1つのそのような代替トランジスタ構成には、基板から形成された「フィン」を介して伝導チャネルを構成するフィン電界効果トランジスタ(FET)(FinFET)が含まれる。このフィンの周りを材料で包み込んでデバイスのゲートが形成される。たとえば、図1は例示的なFinFET100を示す。FinFET100は、基板102と、基板102から形成されたフィン104とを含む。フィン104のいずれかの側に酸化物層106が含まれる。FinFET100は、フィン104によって相互接続されたソース108とドレイン110とを含み、それによって、フィン104の内部

がソース 108 とドレイン 110 との間の伝導チャネル 112 として働く。フィン 104 は、「ラップアラウンド」ゲート 114 によって囲まれる。ゲート 114 のラップアラウンド構造は、チャネル 112 に対するより優れた静電制御を実現し、したがって、漏れ電流を低減させ、他の S C E を解消するのを助ける。

#### 【0006】

F i n F E T 100などのF i n F E Tは、プレーナトランジスタと比較して漏れ電流を低減させS C Eを回避または軽減するが、F i n F E Tを使用するI Cについては引き続き性能を向上させる必要がある。F i n F E T 100を含むF E Tの性能を向上させる1つの方法は、チャネル内のキャリア移動度を変更するようにチャネルに応力を加えることである。10たとえば、N型F i n F E Tとして使用されるF i n F E T 100のチャネル 112に応力 116 を加えると、対応する電子がより流れやすくなる。さらに、P型F i n F E Tとして使用されるF i n F E T 100のチャネル 112に応力 116 を加えると、対応する正孔がより流れやすくなる。いずれの場合も、チャネル 112に加えられる応力 116 は、チャネル 112における伝導性を高め、したがって、対応するF i n F E T 100の性能を向上させるようにキャリア移動度を変更するように設計される。20応力 116 は、圧縮圧力または引張圧力をチャネル 112に加えることによって実現される。応力 116 を加えるための従来の方法は、F i n F E T 100を含むF i n F E Tに使用するとより複雑になり、より効果が低くなる。たとえば、ソース 108 およびドレイン 110 に対応するエピタキシャル層（図示せず）を成長させるか、またはF i n F E T 100を他のデバイスから分離する分離トレンチ（図示せず）の組成を変更することによって、応力 116 をチャネル 112に加えることができる。さらに、F i n F E Tは引き続き面積が狭くなっているので、これらの従来の方法は特に効果が低い。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0007】

本明細書で開示される態様は、誘電体材料層を使用してチャネル領域に応力を加えるフィン電界効果トランジスタ（F E T）（F i n F E T）を含む。一態様では、F i n F E Tが提供される。F i n F E Tは、基板と、基板の上に配設されたフィンとを含む。30フィンは、ソースと、ドレインと、ソースとドレインとの間のチャネル領域とを含む。チャネル領域の周りにゲートが配設される。F i n F E Tのチャネル領域に応力を加えるために、基板の上にかつフィンの一方の側に隣接するように第1の誘電体材料層が配設される。さらに、基板の上にかつフィンの別の側に隣接するように第2の誘電体材料層が配設される。このようにして、第1の誘電体材料層と第2の誘電体材料層はどちらも、応力をチャネル領域に加えるとともにフィンに沿って加える。さらに、エピタキシャル層を成長させることによって誘起される応力とは異なり、第1および第2の誘電体材料層によって加えられる場合がある応力のレベルは、各層の体積に依存しない。したがって、第1および第2の誘電体材料層は、F i n F E Tの面積が狭くともチャネル領域上に一定のレベルの応力を加える場合がある。

#### 【0008】

この点に関して、一態様では、F i n F E Tが提供される。このF i n F E Tは基板を含む。F i n F E Tはまた、基板の上に配設されたフィンを含む。フィンは、ソースと、ドレインと、ソースとドレインとの間のチャネル領域とを含む。F i n F E Tはまた、チャネル基板の上に配設されたフィンを含む。F i n F E Tはまた、基板の上にかつフィンの第1の側に隣接するように配設された第1の誘電体材料層を含む。第1の誘電体材料層は、チャネル領域に応力を加える。F i n F E Tはまた、基板の上にかつ第1の側とは異なるフィンの第2の側に隣接するように配設された第2の誘電体材料層を含む。第2の誘電体材料層は、チャネル領域に応力を加える。

#### 【0009】

別の態様では、F i n F E Tが提供される。このF i n F E Tは、基板を提供するための手段を含む。F i n F E Tはまた、基板の上にフィンを設けるための手段を含む。フィ50

ンは、ソースと、ドレインと、ソースとドレインとの間のチャネル領域とを含む。Fin FETはまた、チャネル領域の周りにゲートを設けるための手段を含む。Fin FETはまた、基板の上にかつフィンの第1の側に隣接するように配設された第1の誘電体材料層を設けるための手段を含む。第1の誘電体材料層は、チャネル領域に応力を加える。Fin FETはまた、基板の上にかつ第1の側とは異なるフィンの第2の側に隣接するように配設された第2の誘電体材料層を向けるための手段を含む。第2の誘電体材料層は、チャネル領域に応力を加える。

#### 【0010】

別の態様では、誘電体材料層を使用してチャネル領域に応力を加えるFin FETを製作するための方法が提供される。この方法は、フィンを備える基板を設けるステップを含む。この方法はまた、基板の上にかつフィンの第1の側に隣接するように第1の誘電体材料層を配設するステップを含む。この方法はまた、基板の上にかつフィンの第2の側に隣接するように第2の誘電体材料層を配設するステップであって、第2の側が第1の側とは異なる、ステップを含む。この方法はまた、フィン、第1の誘電体材料層、および第2の誘電体材料層の上のゲート領域内に、Fin FETのゲート長にほぼ等しい幅を有するゲートを配設するステップを含む。

#### 【図面の簡単な説明】

#### 【0011】

【図1】例示的なフィン電界効果トランジスタ(FET)(Fin FET)の斜視図である。

20

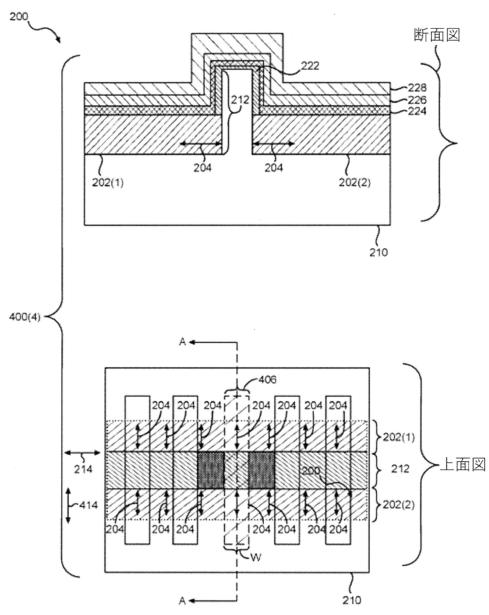

【図2A】誘電体材料層を使用してチャネル領域に応力を加える例示的なFin FETの断面図である。

【図2B】図2Aの例示的なFin FETの上面図である。

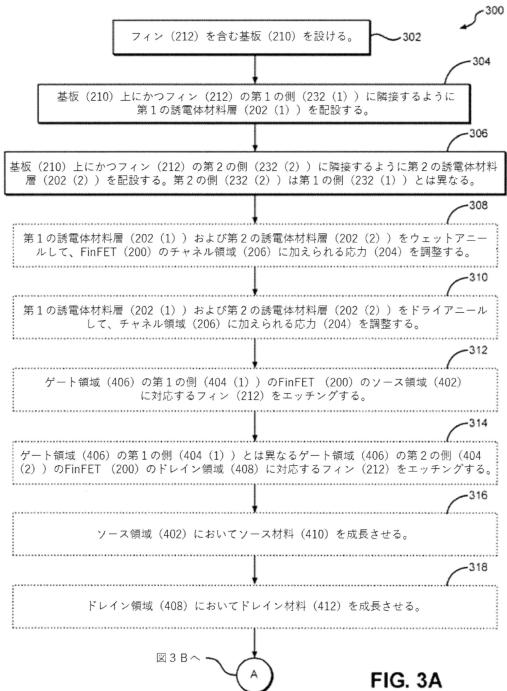

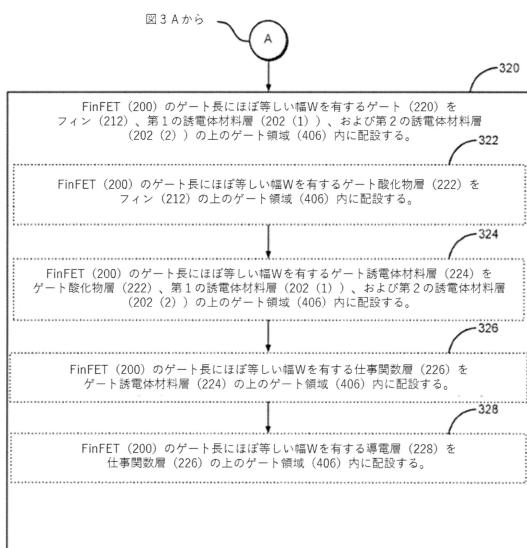

【図3A】誘電体材料層を使用して図2A、2Bにおけるチャネル領域に応力を加えるFin FETを製作する例示的なプロセスを示すフローチャートである。

【図3B】誘電体材料層を使用して図2A、2Bにおけるチャネル領域に応力を加えるFin FETを製作する例示的なプロセスを示すフローチャートである。

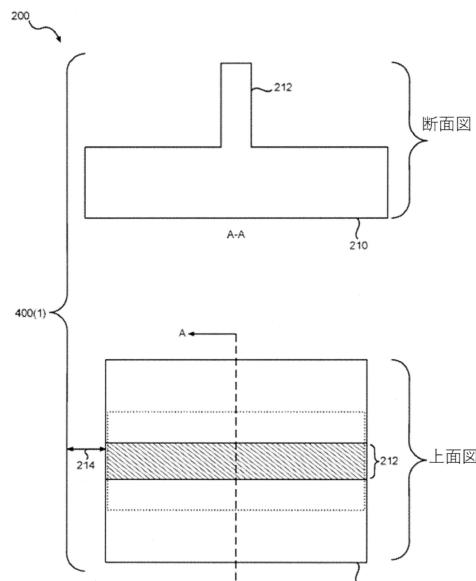

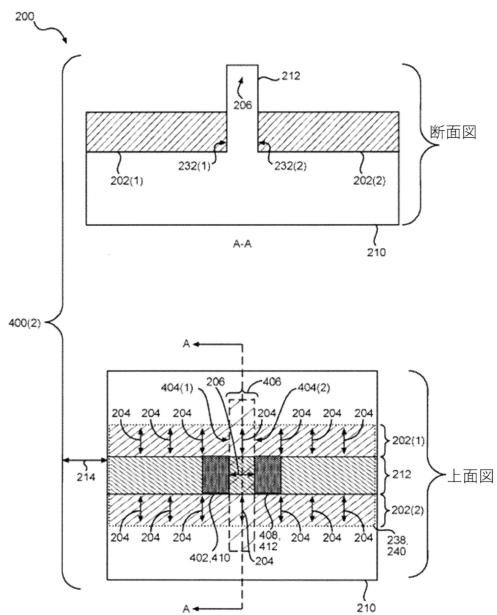

【図4A】図3の製作プロセスの各段階における図2BのFin FETを示す断面図および上面図である。

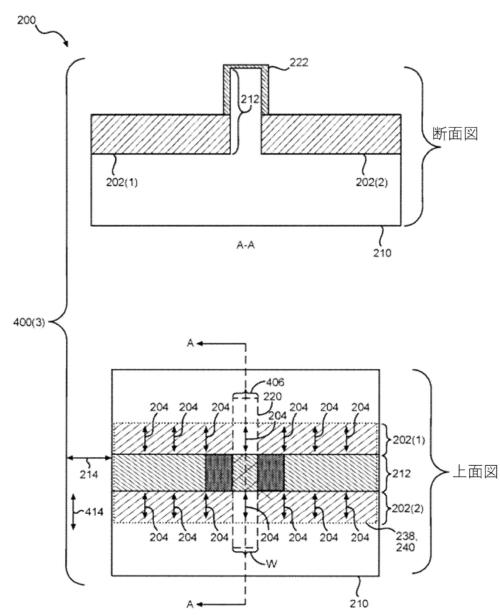

【図4B】図3の製作プロセスの各段階における図2BのFin FETを示す断面図および上面図である。

30

【図4C】図3の製作プロセスの各段階における図2BのFin FETを示す断面図および上面図である。

【図4D】図3の製作プロセスの各段階における図2BのFin FETを示す断面図および上面図である。

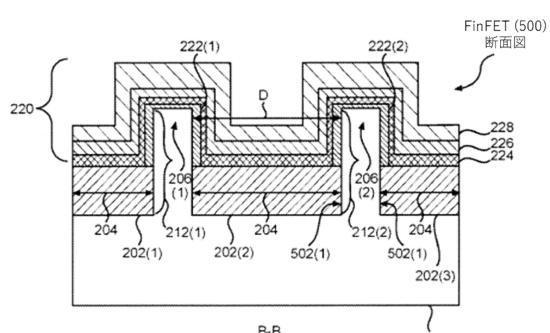

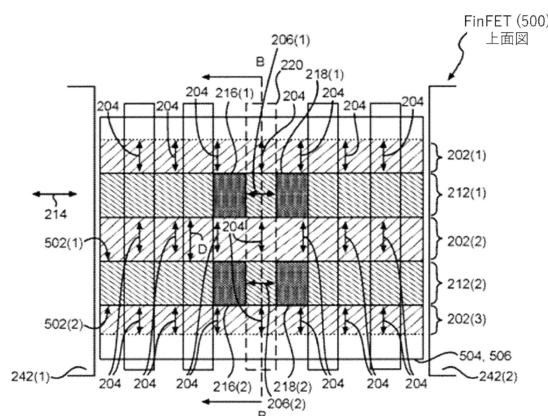

【図5A】複数のフィンに対応する誘電体材料層を使用して複数のチャネル領域に応力を加える例示的なFin FETの断面図である。

【図5B】図5Aにおける複数のフィンの例示的なFin FETの上面図である。

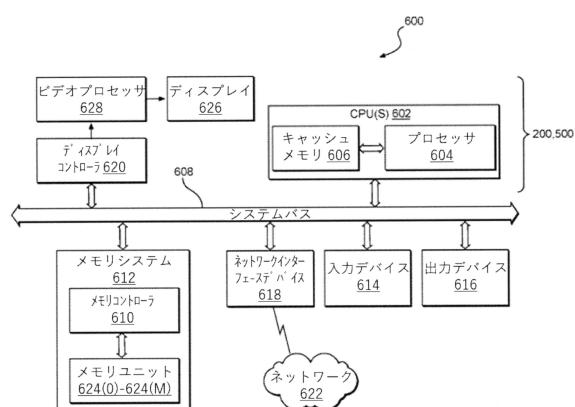

【図6】誘電体材料層を使用して図2A、図2B、図5A、および図5Bのチャネル領域に応力を加えるFin FETを含むことができる例示的なプロセッサベースシステムのブロック図である。

40

#### 【発明を実施するための形態】

#### 【0012】

ここで図面を参照して、本開示のいくつかの例示的な態様について説明する。「例示的な」という語は、本明細書では「例、事例、または例示として機能すること」を意味するために使用される。本明細書で「例示的」として説明するいかなる態様も、必ずしも他の態様よりも好ましいまたは有利なものと解釈されるべきではない。

#### 【0013】

本明細書で開示される態様は、誘電体材料層を使用してチャネル領域に応力を加えるフィン電界効果トランジスタ(FET)(Fin FET)を含む。一態様では、Fin F E

50

Tが提供される。FinFETは、基板と、基板の上に配設されたフィンとを含む。フィンは、ソースと、ドレインと、ソースとドレインとの間のチャネル領域とを含む。チャネル領域の周りにゲートが配設される。FinFETのチャネル領域に応力を加えるために、基板の上にかつフィンの一方の側に隣接するように第1の誘電体材料層が配設される。さらに、基板の上にかつフィンの別の側に隣接するように第2の誘電体材料層が配設される。このようにして、第1の誘電体材料層と第2の誘電体材料層はどちらも、応力をチャネル領域に加えるとともにフィンに沿って加える。さらに、エピタキシャル層を成長させることによって誘起される応力とは異なり、第1および第2の誘電体材料層によって加えられる場合がある応力のレベルは、各層の体積に依存しない。したがって、第1および第2の誘電体材料層は、FinFETの面積が狭くなてもチャネル領域上に一定のレベルの応力を加える場合がある。

#### 【0014】

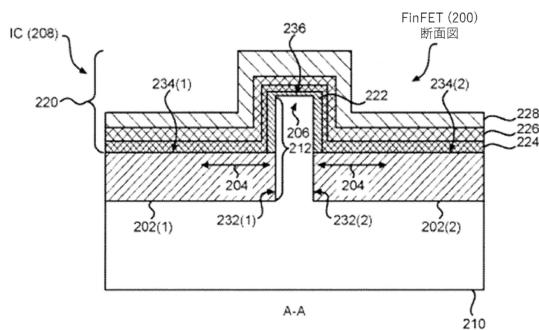

この点に関して、図2Aおよび図2Bは、第1および第2の誘電体材料層202(1)、202(2)を使用してチャネル領域206に応力204を加える例示的なFinFET200を示す。本明細書で説明するFinFET200は、集積回路(IC)208に組み込むことができる。図2AはFinFET200の断面図であり、図2BはFinFET200の上面図である。FinFET200の構成要素は、図2Aおよび図2Bでは共通の要素番号によって参照されている。

#### 【0015】

図2Aおよび図2Bを参照するとわかるように、FinFET200は、基板210と、基板210から形成されたフィン212とを含む。この例では、フィン212は第1の方向214に配設される。図2Bに示すように、フィン212は、ソース216とドレイン218とを含む。FinFET200のチャネル領域206は、フィン212においてソース216とドレイン218との間に配設される。さらに、チャネル領域206の周りにゲート220が配設される。この例では、ゲート220は、高誘電率金属ゲート(HKMG)として形成される。したがって、以下でより詳細に説明するように、ゲート酸化物層222、ゲート誘電体材料層224、仕事関数層226、および導電層228を使用してゲート220が形成される。しかし、FinFET200の他の態様は、本明細書で説明するHKMG以外のゲートタイプを使用してもよい。さらに、FinFET200はまた、ダミーゲートとして機能するように構成されたゲート構造230(1)～230(4)を使用することができる。

#### 【0016】

引き続き図2Aおよび図2Bを参照するとわかるように、チャネル領域206に応力204を加えるために、第1の誘電体材料層202(1)は、基板210の上にかつフィン212の第1の側232(1)に隣接するように配設される。さらに、第2の誘電体材料層202(2)は、基板210の上にかつ第1の側232(1)とは異なるフィン212の第2の側232(2)に隣接するように配設される。この例では、第1および第2の誘電体材料層202(1)、202(2)は第1の方向214に配設される。さらに、第1および第2の誘電体材料層202(1)、202(2)のそれぞれ上面234(1)、234(2)は、ゲート220を形成するための空間を残すようにフィン212の上面236よりも低い。さらに、第1および第2の誘電体材料層202(1)、202(2)は、FinFET200の活性層240を囲む活性領域境界238内に配設される。本明細書で使用するFinFET200の活性層240は、基板210のドープ領域に対応し、ドープ領域上に、FinFET200のソースおよびドレインなどの活性要素が形成される場合がある。このようにして、チャネル領域206に応力204を加え、一方、応力204が加えることができない不活性領域または非ドープ領域に材料を配設するのを回避するように、第1および第2の誘電体材料層202(1)、202(2)を活性領域境界238に限定することができる。

#### 【0017】

引き続き図2Aおよび図2Bを参照すると、以下でより詳細に説明するように、この態

10

20

30

40

50

様における第1および第2の誘電体材料層202(1)、202(2)は、流動化学気相堆積(F C V P)または高アスペクト比処理(H A R P)などのプロセスを使用して基板210の上に配設された(たとえば、堆積された)1つまたは複数の酸化物材料から形成される。第1および第2の誘電体材料層202(1)、202(2)の酸化物材料は、特定の種類または大きさの応力204を加えるように熱アニールされてもよい。たとえば、第1および第2の誘電体材料層202(1)、202(2)は、二酸化ケイ素またはシリコン窒化物から形成することができる。FinFET200がN型FinFETである場合、第1および第2の誘電体材料層202(1)、202(2)は、チャネル領域206に加えられる応力204が引張応力になるように熱アニールすることができる。FinFET200がP型FinFETである場合、第1および第2の誘電体材料層202(1)、202(2)は、チャネル領域206に加えられる応力204が圧縮応力になるように熱アニールすることができる。

10

#### 【0018】

図2Aおよび図2Bを引き続き参照するとわかるように、上述のように第1および第2の誘電体材料層202(1)、202(2)の酸化物材料を配設しアニールすることによって、チャネル領域206を含むフィン212に沿って応力204が加えられる。このようにして、エピタキシャル層を成長させることなど、他の方法によって誘起される応力とは異なり、第1および第2の誘電体材料層202(1)、202(2)によって加えられる応力204のレベルは、第1および第2の誘電体材料層202(1)、202(2)の体積に依存しない。より詳細には、第1および第2の誘電体材料層202(1)、202(2)の代わりにエピタキシャル層を使用する例示的なFinFETでは、エピタキシャル層によって加えられる応力の大きさはそのような層の体積と相關する。したがって、そのようなFinFETの面積が狭くなるにつれて、エピタキシャル層によって誘起される応力も弱くなる。このことは、結晶構造の体積が小さくなるにつれてより弱い応力を誘起するエピタキシャル層の結晶構造の特性に起因する。したがって、応力がエピタキシャル層によって誘起される場合とは異なり、第1および第2の誘電体材料層202(1)、202(2)は、FinFET200の面積が狭くなっても、チャネル領域206に一定のレベルの応力204を加えることがある。

20

#### 【0019】

さらに、応力が回路内の他のデバイスからFinFET200を電気的に絶縁するために使用されるシャロートレンチ分離(STI)構造242(1)、242(2)を使用することによって誘起される場合とは異なり、第1および第2の誘電体材料層202(1)、202(2)を使用して応力204を加えてもFinFET200の面積は大きくならない。たとえば、STI構造242(1)、242(2)は、各STI構造242(1)、242(2)の幅を大きくすることによって応力を誘起するように設計することができる。STI構造242(1)、242(2)の幅を小さくすると、FinFET200を使用する回路の面積が広くなる。さらに、STI構造242(1)、242(2)の幅を大きくすると、FinFET200に加えられる応力が弱くなる。より詳細には、STI構造242(1)、242(2)によって加えられる応力の大きさは、STI構造242(1)、242(2)の幅と反比例する。したがって、STI構造242(1)、242(2)が拡大すると、その結果加えられる応力が弱くなる。したがって、FinFET200の面積が狭くなっても一定の応力204を加えることに加えて、第1および第2の誘電体材料層202(1)、202(2)は、面積を広くすることなく一定の大きさの応力204を加える。

30

40

#### 【0020】

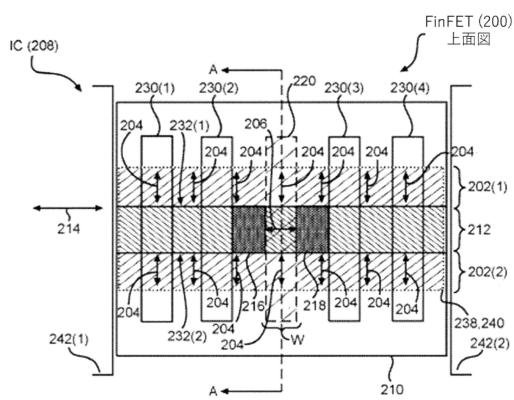

図3Aおよび図3Bは、図2Aおよび図2BにおけるFinFET200を製作するために使用される例示的な製作プロセス300を示す。さらに、図4A～図4Dは、製作プロセス300の間のFinFET200のそれぞれの段階400(1)～400(4)を示す断面図および上面図である。図4A～図4DにおけるFinFET200を示す断面図および上面図について、図3Aおよび図3Bにおける製作プロセス300の例示的な製

50

作ステップの説明に関連して説明する。

#### 【0021】

この点に関して、図3Aから始まる製作プロセス300は、フィン212を含む基板210を設ける（ブロック302、図4Aの段階400（1））ことを含む。この例では、フィン212は第1の方向214に配設される。製作プロセス300はまた、基板210の上にかつフィン212の第1の側232（1）に隣接するように第1の誘電体材料層202（1）を配設する（ブロック304、図4Bの段階400（2））ことを含む。製作プロセス300は、基板210の上にかつフィン212の第2の側232（2）に隣接するように第2の誘電体材料層202（2）を配設する（ブロック306、図4Bの段階400（2））ことをさらに含む。この例では、第1および第2の誘電体材料層202（1）、202（2）は第1の方向214に配設される。前述のように、第1および第2の誘電体材料層202（1）、202（2）は、ブロック304および306において流動化学気相堆積（FCVP）または高アスペクト比処理（HARP）などのプロセスを使用して基板210の上に配設することができる。さらに、第1および第2の誘電体材料層202（1）、202（2）は、活性領域境界238に限定されるように配設することができる。10

#### 【0022】

引き続き図3Aおよび図3Bを参照するとわかるように、熱アニールを使用して、第1および第2の誘電体材料層202（1）、202（2）によって加えられる応力204を調整することができる。より詳細には、製作プロセス300は、第1および第2の誘電体材料層202（1）、202（2）をウェットアニールして、FinFET200のチャネル領域206に加えられる応力204を調整することを含むことができる（ブロック308、図4Bの段階400（2））。たとえば、ブロック308において約600の低温ウェットアニールが使用されてもよい。製作プロセス300はまた、第1の誘電体材料層202（1）および第2の誘電体材料層202（2）をドライアニールして、FinFET200のチャネル領域206に加えられる応力204を調整することを含むことができる（ブロック310、図4Bの段階400（2））。たとえば、ブロック310において約1050の高温ウェットアニールを使用することができる。20

#### 【0023】

引き続き図3Aおよび図3Bを参照するとわかるように、製作プロセス300は、ゲート領域406の第1の側404（1）のFinFET200のソース領域402に対応するフィン212をエッティングすることを含むことができる（ブロック312、図4Bの段階400（2））。製作プロセス300はまた、第1の側404（1）とは異なるゲート領域406の第2の側404（2）のFinFET200のドレイン領域408に対応するフィン212をエッティングすることを含むことができる（ブロック314、図4Bの段階400（2））。さらに、製作プロセス300は、ソース領域402においてソース材料410を成長させることを含むことができる（ブロック316、図4Bの段階400（2））。製作プロセス300はまた、ドレイン領域408においてドレイン材料412を成長させることを含むことができる（ブロック318、図4Bの段階400（2））。30

#### 【0024】

引き続き図3Aおよび図3Bを参照するとわかるように、製作プロセス300はまた、FinFET200のゲート長にほぼ等しい幅Wを有するゲート220をゲート領域406内に配設することを含む（ブロック320、図4C、図4Dにおける段階400（3）、400（4））。たとえば、FinFET200が10ナノメートル（nm）技術において使用される場合、ゲート長はほぼ10nmに等しい。詳細には、ゲート220は、フィン212、第1の誘電体材料層202（1）、および第2の誘電体材料層202（2）の上に配設される。この例では、ゲート220は、第1の方向214に実質的に直交する第2の方向414に配設される。ゲート220は、ブロック320において、FinFET200のゲート長にほぼ等しい幅Wを有するゲート酸化物層222をフィン212の上のゲート領域406内に配設することによって配設することができる（ブロック322、4050

図4 Cの段階400(3)。ブロック320においてゲート220を配設することは、FinFET200のゲート長にほぼ等しい幅Wを有するゲート誘電体材料層224をゲート領域406内に配設することによって配設することができる(ブロック324、図4Dの段階400(4))。ゲート誘電体材料層224は、ブロック324において、ゲート酸化物層222、第1の誘電体材料層202(1)、および第2の誘電体材料層202(2)の上に配設される。ブロック320においてゲート220を配設することはまた、FinFET200のゲート長にほぼ等しい幅Wを有する仕事関数層226をゲート領域406内に配設することを含むことができる(ブロック326、図4Dの段階400(4))。仕事関数層226は、ゲート誘電体材料層224の上に配設される。さらに、ブロック320においてゲート220を配設することは、FinFET200のゲート長にほぼ等しい幅Wを有する導電層228を仕事関数層226の上のゲート領域406内に配設することを含むことができる(ブロック328、図4Dの段階400(4))。

#### 【0025】

製作プロセス300を使用してFinFET200を製造すると、FinFET200は、FinFET200の面積が狭くともチャネル領域206に一定のレベルの応力204を加えることができる。さらに、製作プロセス300は、従来のFinFET製作方法に含まれる様々なステップを含む。特定の種類または大きさの応力204を誘起するための上記の追加のステップを組み込むと、従来の方法と比較して1つの追加のマスクが含まれられる場合がある。したがって、上述のように応力204を加え、同時に、製造コストおよび複雑さの増大を最小限に抑えるようにFinFET200を製作することができる。

#### 【0026】

図2Aおよび図2BにおけるFinFET200に加えて、本明細書で説明する態様はまた、複数のフィンに対応する誘電体材料層を使用して複数のチャネル領域に応力を加えるFinFETを含むことができる。この点に関して、図5Aおよび図5Bは、第1、第2、および第3の誘電体材料層202(1)～202(3)を使用して第1および第2のチャネル領域206(1)、206(2)に応力204を加える例示的なFinFET500を示す。図5AはFinFET500の断面図であり、図5BはFinFET500の上面図である。FinFET500の構成要素は、図5Aおよび図5Bでは一般的な要素番号によって参照されている。さらに、FinFET500は、図2A、図2Bと図5A、図5Bとの間で同様の要素番号で示されるように、図2Aおよび図2BにおけるFinFET200と共にいくつかの構成要素を含み、したがって本明細書で再び説明されることはない。

#### 【0027】

引き続き図5Aおよび図5Bを参照するとわかるように、FinFET500は、基板210と、基板210の上に配設された第1および第2のフィン212(1)、212(2)とを含む。この例では、第1および第2の誘電体材料層212(1)、212(2)は第1の方向214に配設される。非制限的な例として、FinFET500が10nm技術(すなわち、10nmゲート長)において製作される場合、第1および第2のフィン212(1)、212(2)は、32nmにほぼ等しい距離Dだけ分離される。図5Bに示すように、第1および第2のフィン212(1)、212(2)の各々はそれぞれ、ソース216(1)、216(2)とドレイン218(1)、218(2)とを含む。FinFET500の第1および第2のチャネル領域206(1)、206(2)はそれぞれ、第1および第2のフィン212(1)、212(2)において、それぞれのソース216(1)、216(2)とドレイン218(1)、218(2)との間に配設される。さらに、ゲート220は、第1および第2のチャネル領域206(1)、206(2)の周りに配設される。FinFET200と同様に、それぞれ第1および第2のフィン212(1)、212(2)の上のゲート酸化物層222(1)、222(2)、ゲート誘電体材料層224、仕事関数層226、および導電層228を使用してゲート220が形成される。

## 【0028】

引き続き図5Aおよび図5Bを参照するとわかるように、FinFET500は、第1のチャネル領域206(1)に応力204を加える第1および第2の誘電体材料層202(1)、202(2)に加えて、チャネル領域206(2)にも応力204が加えられるように設計される。具体的には、第2のフィン212(2)のチャネル領域206(2)に応力204を加えるために、基板210の上にかつ第2のフィン212(2)の第2の側502(2)に隣接するように第3の誘電体材料層202(3)が配設される。さらに、第2の誘電体材料層202(2)は、基板210の上にかつ第2の側502(2)とは異なるフィン212(2)の第2の側502(1)に隣接するように配設される。この例では、第2および第3の誘電体材料層202(2)、202(3)は第1の方向214に配設される。このようにして、第2の誘電体材料層202(2)はまた、チャネル領域206(2)に応力204を加える。さらに、第1、第2、および第3の誘電体材料層202(1)～202(3)は、FinFET500の活性層506を囲む活性領域境界504内に配設される。<sup>10</sup> したがって、第1、第2、および第3の誘電体材料層202(1)～202(3)は、FinFET500の面積が狭くなても、第1および第2のチャネル領域206(1)、206(2)に一定のレベルの応力204を加える場合がある。たとえば、FinFET500の面積が狭くなると、第1のフィン212(1)と第2のフィン212(2)との間の距離Dも32nmよりも短くなる。しかし、上述の第1、第2、および第3の誘電体材料層202(1)～202(3)の特性に起因して、応力204は、エピタキシャル層によって誘起される応力とは異なり、距離Dが短くなつても一定のままである。<sup>20</sup>

## 【0029】

本明細書で説明する要素は、特定の特性を実現するための手段と呼ばれることがある。この点に関して、基板210は、本明細書では「基板を設けるための手段」と呼ばれることがある。フィン212は、本明細書では、「基板の上にフィンを設けるための手段」と呼ばれることがある。さらに、ゲート220は、本明細書では、「チャネル領域の周りにゲートを設けるための手段」と呼ばれることがある。第1の誘電体材料層202(1)は、本明細書では、「基板の上にかつフィンの第1の側に隣接するように第1の誘電体材料層を設けるための手段であつて、第1の誘電体材料層がチャネル領域に応力を加える手段」と呼ばれることがある。<sup>30</sup> 第2の誘電体材料層202(2)は、本明細書では、「基板の上にかつ第1の側とは異なるフィンの第2の側に隣接するように第2の誘電体材料層を設けるための手段であつて、第2の誘電体材料層がチャネル領域に応力を加える手段」と呼ばれることがある。

## 【0030】

本明細書で開示する態様による、誘電体材料層を使用してチャネル領域に応力を加えるFinFETは、任意のプロセッサベースのデバイス内に設けられるか、またはその中に組み込まれてもよい。例には、限定はしないが、セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、全地球測位システム(GPS)デバイス、モバイルフォン、セルラーフォン、スマートフォン、セッション開始プロトコル(SIP)<sup>40</sup>フォン、タブレット、ファブレット、サーバ、コンピュータ、ポータブルコンピュータ、モバイルコンピューティングデバイス、装着型コンピューティングデバイス(たとえば、スマートウォッチ、ヘルスまたはフィットネストラッカー、アイウェアなど)、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤ、自動車、車両構成要素、アビオニクスシステム、ドローン、およびマルチコプターが含まれる。

## 【0031】

この点に関して、図6は、図2Aおよび図2Bに示すFinFET200および図5A<sup>50</sup>

および図5Bに示すF i n F E T 5 0 0を用いることができる、プロセッサベースのシステム6 0 0の一例を示す。この例では、プロセッサベースシステム6 0 0は、それぞれが1つまたは複数のプロセッサ6 0 4を含む、1つまたは複数の中央処理装置(C P U)6 0 2を含む。C P U 6 0 2は、一時的に記憶されたデータへの高速アクセスのためにプロセッサ6 0 4に結合されたキャッシュメモリ6 0 6を有してもよい。C P U 6 0 2は、システムバス6 0 8に結合され、プロセッサベースシステム6 0 0内に含まれるマスタデバイスとスレーブデバイスとを相互結合することができる。よく知られているように、C P U 6 0 2は、アドレス情報、制御情報、およびデータ情報を、システムバス6 0 8を介して交換することによって、これらの他のデバイスと通信する。たとえば、C P U 6 0 2は、スレーブデバイスの一例として、メモリコントローラ6 1 0にバストランザクション要求を通信することができる。図6には示されていないが、複数のシステムバス6 0 8を設けることができ、各システムバス6 0 8は、異なるファブリックを構成する。

#### 【0032】

他のマスタデバイスおよびスレーブデバイスをシステムバス6 0 8に接続することができる。図6に示すように、これらのデバイスは、例として、メモリシステム6 1 2、1つまたは複数の入力デバイス6 1 4、1つまたは複数の出力デバイス6 1 6、1つまたは複数のネットワークインターフェースデバイス6 1 8、および1つまたは複数のディスプレイコントローラ6 2 0を含むことができる。入力デバイス6 1 4は、入力キー、スイッチ、音声プロセッサなどを含むが、これらに限定されない、任意のタイプの入力デバイスを含むことができる。出力デバイス6 1 6は、オーディオ、ビデオ、他の視覚インジケータなどを含むが、これらに限定されない、任意のタイプの出力デバイスを含むことができる。ネットワークインターフェースデバイス6 1 8は、ネットワーク6 2 2との間のデータの交換を可能にするように構成された任意のデバイスであってもよい。ネットワーク6 2 2は、限定はしないが、有線ネットワークまたはワイヤレスネットワーク、プライベートネットワークまたは公衆ネットワーク、ローカルエリアネットワーク(LAN)、ワイヤレスローカルエリアネットワーク(WLAN)、ワイドエリアネットワーク(WAN)、BLUE TOOTH(登録商標)ネットワーク、およびインターネットを含む、任意のタイプのネットワークであってもよい。ネットワークインターフェースデバイス6 1 8は、必要に応じて、任意のタイプの通信プロトコルをサポートするように構成されることが可能である。メモリシステム6 1 2は、1つまたは複数のメモリユニット6 2 4(0)~6 2 4(M)を含むことができる。

#### 【0033】

C P U 6 0 2はまた、システムバス6 0 8を介してディスプレイコントローラ6 2 0にアクセスして、1つまたは複数のディスプレイ6 2 6に送信される情報を制御するように構成されてもよい。ディスプレイコントローラ6 2 0は、1つまたは複数のビデオプロセッサ6 2 8を介して表示されるように情報をディスプレイ6 2 6へ送り、ビデオプロセッサ6 2 8は、表示すべき情報を処理してディスプレイ6 2 6に適したフォーマットにする。ディスプレイ6 2 6は、限定はしないが、陰極線管(CRT)、液晶ディスプレイ(LCD)、プラズマディスプレイ、発光ダイオード(LED)ディスプレイなどを含む、任意のタイプのディスプレイを含むことができる。

#### 【0034】

当業者は、本明細書で開示する態様について説明する様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムが、電子ハードウェア、メモリ内もしくは別のコンピュータ可読媒体内に記憶され、プロセッサもしくは他の処理デバイスによって実行される命令、または両方の組合せとして実装され得ることをさらに諒解されよう。本明細書で説明するマスタデバイスおよびスレーブデバイスは、例として、任意の回路、ハードウェア構成要素、集積回路(I C)、またはI Cチップにおいて採用され得る。本明細書で開示するメモリは、任意のタイプおよびサイズのメモリであってよく、任意のタイプの所望の情報を記憶するように構成され得る。この互換性について明確に例示するために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップについて、上記では

概してそれらの機能に関して説明した。そのような機能性がどのように実装されるのかは、特定の適用例、設計選択、および／またはシステム全体に課される設計制約によって決まる。当業者は、特定の適用例ごとに様々な方式で記載の機能を実装してもよいが、そのような実装の決定が、本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

#### 【0035】

本明細書で開示する態様に関する説明した様々な例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタル信号プロセッサ（D S P）、特定用途向け集積回路（A S I C）、フィールドプログラマブルゲートアレイ（F P G A）もしくは他のプログラマブル論理デバイス、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明する機能を実行するように設計されたそれらの任意の組合せを用いて実装または実施されてもよい。プロセッサは、マイクロプロセッサであってもよいが、代替としてプロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであってもよい。プロセッサはまた、コンピューティングデバイスの組合せ（たとえば、D S Pおよびマイクロプロセッサの組合せ、複数のマイクロプロセッサ、D S Pコアと連携する1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成）として実装されてもよい。10

#### 【0036】

本明細書で開示する態様は、ハードウェアにおいて具現化されてもよく、かつハードウェア内に記憶され、たとえば、ランダムアクセスメモリ（R A M）、フラッシュメモリ、読み取り専用メモリ（R O M）、電気的プログラマブルR O M（E P R O M）、電気的消去可能プログラマブルR O M（E E P R O M）、レジスタ、ハードディスク、リムーバブルディスク、C D - R O M、または当技術分野において知られている任意の他の形態のコンピュータ可読媒体の中に存在し得る命令において具現化されてもよい。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取るとともに記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替として、記憶媒体は、プロセッサと一体化してよい。プロセッサおよび記憶媒体は、A S I Cの中に存在する場合がある。A S I Cは、リモート局の中に存在する場合がある。代替として、プロセッサおよび記憶媒体は、個別構成要素としてリモート局、基地局、またはサーバの中に存在する場合がある。20

#### 【0037】

本明細書の例示的な態様のいずれかで説明した動作ステップが、例示および説明のために記載されていることにも留意されたい。説明した動作は、図示のシーケンス以外の数多くの異なるシーケンスにおいて実行される場合がある。さらに、単一の動作ステップにおいて説明する動作は、実際にはいくつかの異なるステップにおいて実行される場合がある。さらに、例示的な態様で説明した1つまたは複数の動作ステップは、組み合わせられてよい。当業者には容易に明らかになるように、フローチャート図に示される動作ステップが数多くの異なる変更を受ける場合があることを理解されたい。情報および信号が様々な異なる技術および技法のいずれかを使用して表される場合があることも当業者は理解されよう。たとえば、上記の説明全体に渡って参照される場合があるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁気粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表されてもよい。30

#### 【0038】

本開示の上記の説明は、あらゆる当業者が本開示を作成または使用することを可能にするために提供されている。本開示の様々な変更が当業者に容易に明らかになり、本明細書で定義する一般原理は、本開示の趣旨または範囲から逸脱することなく他の変形形態に適用されてもよい。したがって、本開示は、本明細書で説明した例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴と一致する最も広い範囲を与えるべきである。

#### 【符号の説明】

#### 【0039】

1020304050

|                           |                  |          |

|---------------------------|------------------|----------|

| 1 0 0                     | F i n F E T      |          |

| 1 0 2                     | 基板               |          |

| 1 0 4                     | フィン              |          |

| 1 0 6                     | 酸化物層             |          |

| 1 0 8                     | ソース              |          |

| 1 1 0                     | ドレイン             |          |

| 1 1 2                     | 伝導チャネル           |          |

| 1 1 4                     | ゲート              |          |

| 1 1 6                     | 応力               |          |

| 2 0 0                     | F i n F E T      | 10       |

| 2 0 2 ( 1 )               | 、 2 0 2 ( 2 )    | 誘電体材料層   |

| 2 0 4                     | 応力               |          |

| 2 0 6                     | チャネル領域           |          |

| 2 0 8                     | 集積回路             |          |

| 2 1 0                     | 基板               |          |

| 2 1 2                     | フィン              |          |

| 2 1 4                     | 第 1 の方向          |          |

| 2 1 6                     | ソース              |          |

| 2 1 8                     | ドレイン             |          |

| 2 2 0                     | ゲート              | 20       |

| 2 2 2                     | ゲート酸化物層          |          |

| 2 2 4                     | ゲート誘電体材料層        |          |

| 2 2 6                     | 仕事関数層            |          |

| 2 2 8                     | 導電層              |          |

| 2 3 0 ( 1 ) ~ 2 3 0 ( 4 ) | ゲート構造            |          |

| 2 3 2 ( 1 )               | 第 1 の側           |          |

| 2 3 2 ( 2 )               | 第 2 の側           |          |

| 2 3 4 ( 1 )               | 、 2 3 4 ( 2 )    | 上面       |

| 2 3 6                     | 上面               |          |

| 2 3 8                     | 活性領域境界           | 30       |

| 2 4 0                     | 活性層              |          |

| 2 4 2 ( 1 )               | 、 2 4 2 ( 2 )    | S T I 構造 |

| 4 0 4 ( 1 )               | 第 1 の側           |          |

| 4 0 4 ( 2 )               | 第 2 の側           |          |

| 4 0 6                     | ゲート領域            |          |

| 4 0 8                     | ドレイン領域           |          |

| 4 1 0                     | ソース材料            |          |

| 4 1 2                     | ドレイン材料           |          |

| 4 1 4                     | 第 2 の方向          |          |

| 5 0 0                     | F i n F E T      | 40       |

| 5 0 2 ( 1 )               | 第 1 の側           |          |

| 5 0 2 ( 2 )               | 第 2 の側           |          |

| 5 0 4                     | 活性領域境界           |          |

| 5 0 6                     | 活性層              |          |

| 6 0 0                     | プロセッサベースシステム     |          |

| 6 0 2                     | 中央処理装置 ( C P U ) |          |

| 6 0 4                     | プロセッサ            |          |

| 6 0 6                     | キャッシュメモリ         |          |

| 6 0 8                     | システムバス           |          |

| 6 1 0                     | メモリコントローラ        | 50       |

- 6 1 2 メモリシステム

6 1 4 入力デバイス

6 1 6 出力デバイス

6 1 8 ネットワークインターフェースデバイス

6 2 0 ディスプレイコントローラ

6 2 2 ネットワーク

6 2 4 (0) ~ 6 2 4 (M) メモリユニット

6 2 6 ディスプレイ

6 2 8 ビデオプロセッサ

【図1】

FIG. 1

【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図4A】

FIG. 4A

【図4B】

**FIG. 4B**

【図4C】

FIG. 4C

### 【図4D】

**FIG. 4D**

【図5A】

**FIG. 5A**

【図 5 B】

FIG. 5B

【 义 6 】

FIG. 6

---

フロントページの続き

(72)発明者 ヨン・ソン・チェ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライヴ・577

5

(72)発明者 シャシャンク・エクボテ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライヴ・577

5

審査官 市川 武宣

(56)参考文献 米国特許出願公開第2014/0225168(US,A1)

特開2014-110430(JP,A)

特開2011-181931(JP,A)

特開2011-097057(JP,A)

特開2014-013905(JP,A)

特開2013-093438(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/78