#### **CONFÉDÉRATION SUISSE**

OFFICE FÉDÉRAL DE LA PROPRIÉTÉ INTELLECTUELLE

① CH 648 452 G A3

(51) Int. Cl.4: G 04 G

3/02

Demande de brevet déposée pour la Suisse et le Liechtenstein Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

# (2) FASCICULE DE LA DEMANDE A3

21) Numéro de la demande: 2520/80

(7) Requérant(s): Kabushiki Kaisha Suwa Seikosha, Tokyo (JP)

Aizawa, Hitomi, Suwa-shi/Nagano-ken (JP)

22) Date de dépôt:

31.03.1980

30 Priorité(s):

29.03.1979 JP 54-37532

42 Demande publiée le:

29.03.1985

Mandataire: Bovard AG, Bern 25

(72) Inventeur(s):

Fascicule de la demande

publié le:

29.03.1985

66 Rapport de recherche au verso

### 64 Pièce d'horlogerie électronique, notamment montre-bracelet électronique.

(57) Afin de permettre un ajustement de marche dans un large domaine, sans affecter le fonctionnement de l'oscillateur de base de temps standard (5), la montre électronique comporte des moyens diviseurs de fréquence (6-9) dont certains étages (7, 8) peuvent être remis à l'état de travail ou de repos périodiquement, par des moyens à portes et à verrous (14, 15 18; 26, 27) qui fonctionnent sous la commande de bascules (10, 25) actionnée à différentes cadences régulières, relativement grande, par des sorties du diviseur de fréquence (9). Les connexions d'entrée (11, 12, 13) permettent de prévoir, lors de chaque impulsion de fonctionnement des moyens de correction (14, 15, 18; 26, 27), une remise en position de certains étages du diviseur, de façon à provoquer un retard ou une avance de un ou plusieurs pas dans le cycle de division de fréquence. Ces deux cadences de corrections permettent un ajustage grossier et un ajustage fin.

L'invention s'applique avantageusement à la réalisation d'une montre-bracelet électronique avantageuse et précise.

Eidgenössisches Amt für geistiges Eigentum Bureau fédéral de la propriété intellectuelle Ufficio federale della proprietà intellettuale

## RAPPORT DE RECHERCHE RECHERCHENBERICHT

Demande de brevet No.: Patentgesuch Nr.:

CH 2520/80

14182

|                        | Documents considérés comme pertinents<br>Einschlägige Dokumente                                                                                                                                                                |                                                                                                                                |                                                                                                                                                                                                                                                                                    |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catégorie<br>Kategorie | Citation du document avec indication, en cas de besoin, des parties pertinentes.<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile                                                      | Revendications con-<br>cernées<br>Betrifft Anspruch<br>Nr.                                                                     |                                                                                                                                                                                                                                                                                    |

| - <b>X</b>             | <u>DE - A - 2 349 508</u> (CITIZEN WATCH CO. LTD.)                                                                                                                                                                             |                                                                                                                                |                                                                                                                                                                                                                                                                                    |

|                        | <pre>* Page 8, dernier paragraphe; figures 1 à 5 et 15 *</pre>                                                                                                                                                                 | 1,2                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| Y                      | <u>CH - B - 558 559</u> (BULOVA WATCH CO. LTD.)                                                                                                                                                                                |                                                                                                                                |                                                                                                                                                                                                                                                                                    |

|                        | * Colonne 3, ligne 31 à colonne 4,<br>ligne 39; figures *                                                                                                                                                                      | 1                                                                                                                              | Domaines techniques recherchès<br>Recherchierte Sachgebiete<br>(INT. CL')                                                                                                                                                                                                          |

| Y                      | ELECTRONIC DESIGN, vol.19, no.3,<br>4 février 1971<br>ROCHELLE PARK (US)<br>R.W. BURHANS: "Divide frenquencies<br>by any integer", pages 42 et 43                                                                              |                                                                                                                                | G 04 G 3<br>H 03 K 21<br>G 04 F 5                                                                                                                                                                                                                                                  |

|                        | * Figures 2 et 3 *                                                                                                                                                                                                             | 1,2                                                                                                                            |                                                                                                                                                                                                                                                                                    |

| A                      | <u>US - A - 3 369 183</u> (U. MESTER)<br>* Figures *                                                                                                                                                                           | 1                                                                                                                              | Catégorie des documents cités Kategorie der genannten Dokumente X: particulièrement pertinent von besonderer Bedeutung A: arrière-plan technologique technologischer Hintergrund                                                                                                   |

| P                      | GB - A - 2 006 996 (K.K. SUWA<br>SEIKOSHA)                                                                                                                                                                                     |                                                                                                                                | O: divulgation non-écrite nichtschriftliche Offenbarung P: document intercalaire Zwischenliteratur T: théorie ou principe à la base de                                                                                                                                             |

|                        | * Figures *                                                                                                                                                                                                                    | 1                                                                                                                              | l'invention der Erfindung zugrunde liegende fheorien oder Grundsätze E: demande faisant interférence kollidierende Anmeldung D: document cité dans la demande in der Anmeldung angeführtes Dokument L: document cité pour d'autres raisons aus andern Gründen angeführtes Dokument |

| Rapport of<br>Der Rech | le recherche étabit sur la base des dernières revendications transmises avant le commencement de la recherche.<br>erchenbericht wurde mit Bezug auf die letzte, vor der Recherche übermittelte, Fassung der Patentansprüche er | &: membre de la même famille, document<br>correspondant.<br>Mitglied der gleichen Patentfamilie;<br>übereinstimmendes Dokument |                                                                                                                                                                                                                                                                                    |

Revendications ayant fait l'objet de recherches Recherchierte Patentansprüche:

ensemble

Revendications n'ayant pas fait l'objet de recherches Nicht recherchierte Patentanspruche:

Raison: Grund:

Dat. d'achèvement de la recherche/Abschlussdatum der Recherche 29 avril 1982

#### REVENDICATION

Pièce d'horlogerie électronique, notamment montrebracelet électronique, comprenant un circuit oscillateur pour engendrer un signal de temps standard, un circuit diviseur de fréquence qui divise la fréquence du signal de temps standard fourni par le dit oscillateur et dont au moins deux étages comprennent des moyens d'entrée (R+S) permettant leur présélection dans les deux états, des moyens gardetemps qui sont entraînés par un signal de sortie du dit circuit diviseur de fréquence, au moins un circuit de commande qui commande l'inscription de données sur les dits étages présélectionnables du diviseur de fréquence, et des moyens (11-13, 19-23) d'entrée de données qui déterminent les données à inscrire sur les dits étages présélectionnables du diviseur, caractérisée en ce qu'elle comprend deux circuits détecteurs qui détectent respectivement deux conditions spécifiques auxquelles passent les étages du diviseur et qui, sur détection de chaque dite condition spécifique, provoquent respectivement l'inscription, dans certains étages (7, 24) du diviprésentes sur certains (11-13; 19-23), respectivement présélectionnés, des dits moyens d'entrée en réponse au signal de sortie d'un dit circuit détecteur y relatif, de façon à permettre au moins un ajustage grossier et un ajustage fin de la marche de la montre.

La présente invention concerne une pièce d'horlogerie électronique, notamment une montre-bracelet électronique, dans laquelle les signaux provenant d'un oscillateur, source de signal de temps standard, sont divisés dans le circuit diviseur, dont le signal de sortie fait fonctionner des moyens garde-temps qui fournissent un affichage de temps. L'invention concerne d'une manière particulière un ensemble de circuits pour régler digitalement la fréquence du signal de sortie du diviseur à la valeur désirée.

La présente invention vise à permettre un ajustement de fréquence sur un large domaine, d'une façon n'exerçant aucune influence (ou n'exerçant que peu d'influence) sur le circuit oscillateur de temps standard, à l'aide d'un ajustement de fréquence pouvant être réalisé dans le circuit même de la montre.

Primitivement, les moyens de réglage de la fréquence aigssaient sur le circuit oscillateur lui-même. Un circuit oscillateur de type connu, apte à subir un certain ajustement de fréquence, est représenté à titre d'exemple à la fig. 1. Pour ajuster la fréquence d'oscillation, on faisait varier progressivement, jusqu'à obtention de la fréquence voulue, la valeur d'un condensateur trimmer (1), compris dans le circuit oscillateur. Cette méthode de réglage de la marche de la montre d'ajustage. En effet, la vibration d'un vibreur à cristal de quartz devant fonctionner à une fréquence décalée par rapport à sa fréquence naturelle d'oscillation risque de souffrir de défaut de stabilité. Par ailleurs, il était difficile de réduire notablement ce décalage de fréquence par des mesures prises en cours de fabrication en vue de mettre la fréquence naturelle du quartz en très bonne correspondance avec la fréquence désirée. Une telle mesure technologique était en effet fort coûteuse, tout en restant toujours techniquement impar-

Pour remédier à cet inconvénient, on a déjà proposé, par exemple dans les exposés DE-A-2 349 508, et CH-B-558 559. de même que dans un article intitulé «Divide frequencies by

any Integrer» paru dans la revue ELECTRONIC DESIGN, Vol. 19, no 3, février 1971, d'agir non plus sur l'oscillateur lui-même pour ajuster la fréquence mais d'agir sur le diviseur de fréquence, dont on règle le cycle à un nombre de pas cor-5 rigé, cette correction pouvant être faite en ajoutant ou en supprimant des impulsions de comptage, ces corrections intervenant lorsque l'on a détecté que le circuit diviseur de fréquence occupe une position prédéterminée. Une correction portant sur un certain nombre d'impulsions de comptage 10 peut par exemple être faite lorsque le circuit diviseur arrive à la fin de son cycle, en «préparant» alors un ou plusieurs des premiers étages du diviseur de façon qu'il soit remis en position de travail et non pas en position de repos. De cette façon, l'impulsion de comptage qui, sinon, aurait fait passer 15 cet étage-là, ou ces étages-là, à l'état de travail est pour ainsi dire «fournie à l'avance», ce qui raccourcit le cycle de comptage. Une solution de ce genre est illustrée à la fig. 2 annexée.

Il est à noter que si l'on tient à avoir une durée rigoureusement identique de toutes les secondes comptées par la seur, de données déterminées qui correspondent aux données 20 montre, la correction susindiquée doit se manifester régulièrement au moins une fois chaque seconde. Cela signifie qu'avec un oscillateur travaillant à une fréquence de l'ordre de 30 KHz, la plus petite correction que l'on puisse faire subir à la mesure de la seconde est de l'ordre de 30 microsecondes, ce 25 qui correspond à un écart de marche diurne d'approximativement 2 sec.

> En pratique, il n'est toutefois absolument pas gênant d'avoir de temps à autre une seconde (au sens de période mesurée par la montre comme étant la seconde) d'une trentaine 30 de microsecondes, voire d'une fraction de milliseconde, de plus que les autres. Ceci permet de n'effectuer la correction en question qu'après le comptage d'un certain nombre de secondes, par exemple, 10 sec. si chaque dixième de seconde comprend 30 microsecondes de plus que les autres, cela fait 35 en moyenne 3 microsecondes de plus pour chaque seconde, soit un écart de marche diurne notablement inférieur à 1 sec.

Jusqu'à présent, les publications antérieures qui ont adopté la méthode d'ajustement de marche diurne par action sur le cycle de comptage du diviseur, ou bien se sont conten-40 tées, avec une fréquence de base de l'ordre de 30 KHz, d'une définition de réglage dépassant une seconde par jour, toutes les secondes étant alors rigoureusement identiques et le réglage intermédiaire étant éventuellement effectué toujours à l'aide d'un trimmer agissant sur l'oscillateur, ou bien elles 45 ont prévu des corrections qui n'intervenaient pas chaque seconde, permettant une meilleure définition du réglage de la marche diurne, mais introduisant «de temps en temps» une seconde légèrement plus courte ou légèrement plus longue que les autres, ou bien encore on a cherché à améliorer la dé-50 finition de l'ajustage de la marche diurne tout en conservant des secondes qui sont toutes rigoureusement égales, mais en employant alors un oscillateur travaillant à une fréquence beaucoup plus élevée, s'approchant d'un Mégaherz, voire dépassant cette valeur. Toutefois, quelle qu'ait été la soluprésentait toutefois des limites en ce qui concerne le domaine 55 tion choisie, on n'a toujours jusqu'à présent prévu qu'un seul agencement de correction intervenant toutes les secondes ou alors par exemple toutes les 12 secondes, la définition de correction, c'est-à-dire la plus petite correction possible étant fournie par la période (l/f) de l'oscillateur de base divisée par 60 le nombre de secondes au bout duquel intervient chaque fois la correction (ceci rapporté à la durée moyenne d'une seconde, la valeur étant à multiplier par 86 400 pour avoir la définition minimum de la correction de la marche diurne). En fait, on se trouvait devant un dilemne semblable à celui d'un 65 constructeur de pendulette-réveil mécanique au dos de laquelle une pièce tournante permettait de régler non pas la position des aiguilles mais la marche de la pièce d'horlogerie. Ou bien l'on prévoyait une faible démultiplication, ce qui

donnait un large domaine de réglage pouvant être parcouru rapidement mais ce qui rendait difficile un réglage précis, ou bien on donnait une forte démultiplication, ce qui permettait un réglage précis, mais rendait onéreuse une correction de marche importante.

Le but de la présente invention est notamment de résoudre, dans le cas d'une pièce d'horlogerie électronique, typiquement une montre-bracelet électronique, munie d'un dispositif d'ajustage par action sur le cycle de division du diviseur, le problème (dilemne) qui vient d'être expliqué, et ceci sans que le circuit général de la montre électronique s'en trouve rendu notablement plus coûteux ou plus compliqué.

Conformément à l'invention, ce but est atteint par la présence des caractères énoncés dans la revendication annexée.

Le dessin annexé illustre, à titre d'exemple et comparativement à ce que connaissait l'art antérieur, une forme d'exécution de l'objet de l'invention; dans ce dessin:

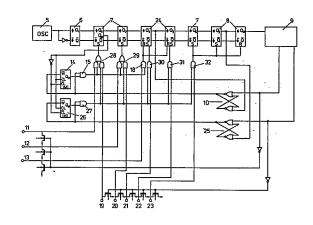

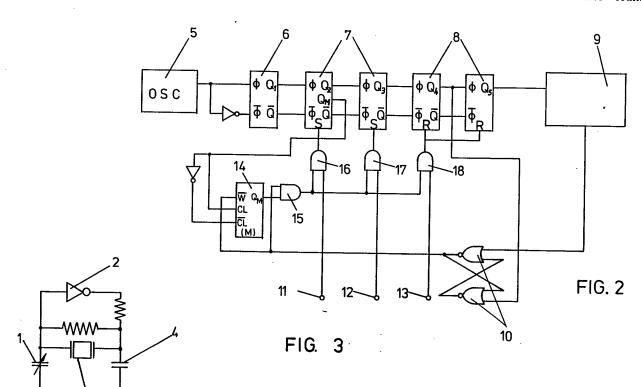

la fig. 1 est un schéma d'un circuit oscillateur classique, la fig. 2 est un schéma illustrant l'essentiel de l'ensemble de circuit de montre électronique à ajustage de marche par action sur le diviseur, d'un genre qui aurait pu être accessible.

la fig. 3 est une table illustrant les états logiques sur les sorties d'étages binaires de division et qu'on trouve aussi bien à la fig. 2 qu'à la fig. 4 illustrant l'invention, en fonction de divers états de conditionnement, rapport de division de telle façon que les écarts de la fréquence d'oscillation se trouvent compensés et que la fréquence de comptage de temps désirée se trouve ainsi présente à la sortie du diviseur de fréquence.

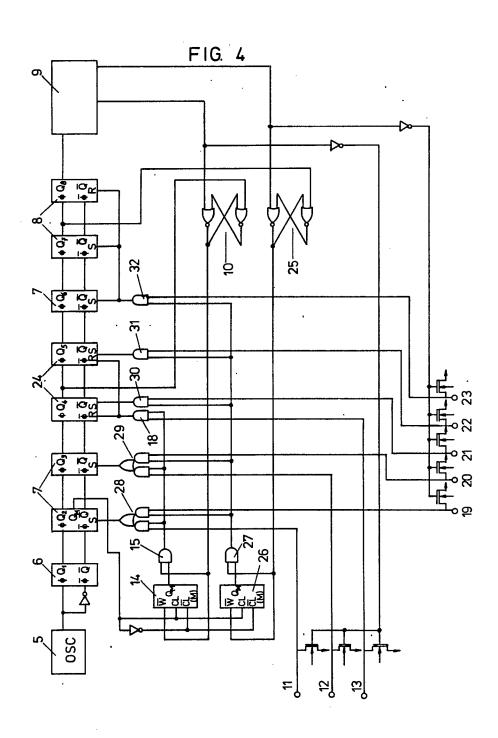

la fig. 4 est un schéma représentant une forme d'exécution d'un ensemble de circuits conforme à la conception particulière proposée, c'est-à-dire permettant des ajustements grossier et fin,

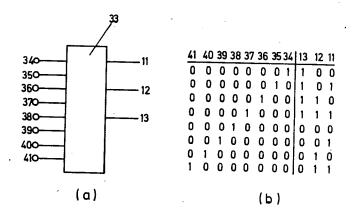

la fig. 5 (a) représente un agencement particulier grâce auquel l'état logique de chaque connexion de détermination de donnée est transformé en code,

La fig. 5 (b) est une «table de vérité» de la conversion de code réalisée avec l'agencement de la fig. 5 (a),

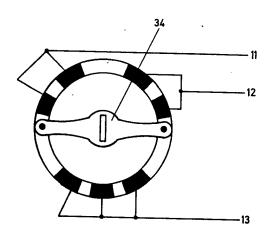

la fig. 6 est une vue schématique montrant comment, pour l'un ou pour chacun des deux ajustements fin et grossier proposés, une combinaison d'états logiques d'entrée peut être définie au moyen d'un commutateur rotatif relatif à l'ajustement correspondant,

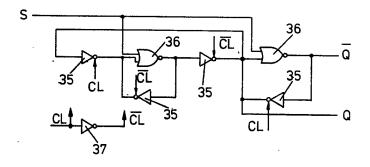

la fig. 7 est un schéma représentant un exemple d'un circuit diviseur par deux, muni d'une connexion d'entrée de mise en position de travail (set).

La fig. 1 montre le schéma d'un circuit oscillateur classique. On y voit, outre un amplificateur 2 et un résonateur 3, un condensateur ajustable 1 et un condensateur non ajustable 4. Classiquement, c'était à l'aide du condensateur ajustable 1 que la fréquence exacte de l'oscillateur était réglée.

Sur la fig. 2 qui représente un ensemble de circuits horloger qui aurait pu être accessible, on voit qu'un circuit oscillateur à fréquence standard 5 délivre son signal à un circuit diviseur de fréquence formé d'étages diviseurs par deux (flip-flop) 6, 7, 8, 9, l'étage diviseur par deux 7 comprenant une connexion de mise en position de travail (set).

Sur la fig. 2, le bloc 9 représente le reste d'une série d'étages diviseurs par deux constituant le diviseur de fréquence. Un circuit détecteur 10 détecte des états logiques spécifiques. Les positions d'entrée 11, 12 et 13 sont des connexions servant à l'établissement préalable de l'état logique des étages diviseurs 7 et 8. Sur la fig. 2, on voit encore un circuit de verrou 14, de même que des portes 15, 16, 17 et 18 du type ET. L'agencement d'un circuit diviseur par deux, muni d'une entrée de mise en position de travail, comme par exemple les étages de division 7 de la fig. 2, est montré à la fig. 7.

Sur cette fig. 7, on voit que la connexion d'entrée S (set) alimente une entrée de chacune de deux portes OU IN-VERSE 36. Lorsque le niveau logique sur cette connexion d'entrée S devient «1», la sortie Q de l'étage diviseur par 5 deux est amenée à l'état logique «0», tandis que la sortie Q du circuit est obligatoirement amenée à l'état «1». Un circuit diviseur par deux (flip-flop) comprenant une connexion de remise à zéro, est du reste établi d'une façon analogue, une ou plusieurs portes étant établies de façon à amener la sortie 10 Q à l'état «1» et la sortie Q à l'état «0».

Revenant à la fig. 2, on voit que le circuit-verrou 14, de même que les portes ET 15, 16, 17 et 18, constituent un circuit de commande qui conditionne les signaux d'inscription (ou de mise en position) sur les étages du diviseur. On admet qu'il existe une petite différence entre la fréquence du signal sortant du circuit oscillateur 5 et la fréquence qui serait essentiellement requise. C'est en vue de corriger cette différence que le circuit de commande de mise en position a été établi, de façon que des signaux de données déterminés par les niveaux logiques sur les entrées 11, 12, et 13, soient appliqués sur les étages 7 et 8 du circuit diviseur afin d'y établir des mises en position préalables qui modifient le rapport de division de telle façon que les écarts de la fréquence d'oscillation se trouvent compensés et que la fréquence de comptage de temps désirée se trouve ainsi présente à la sortie du diviseur de fréquence.

La théorie de l'avance ou du retard du signal de fréquence de sortie par l'intermédiaire de l'inscription de données dans certains étages du diviseur va maintenant être so expliquée en liaison avec la fig. 3. Cette dernière est une table représentant les états logiques des signaux de sortie des étages diviseurs 7 et 8 représentés à la fig. 2.

Si, dans le cas où les niveaux logiques sur les sorties Q<sub>2</sub>, Q<sub>3</sub>, Q<sub>4</sub>, Q<sub>5</sub> des étages diviseurs 7 et 8 sont détectés comme 35 étant «0», «0», «1», et «0», des données sont inscrites dans ces étages de façon telle que ces niveaux logiques deviennent «1», «1», «0» et «0», la situation logique de comptage est reculée d'un pas, ce qui provoque un retard du fonctionnement des étages de division. Si, par contre, des données sont introduites pour amener les niveaux logiques à «1», «0», «1», «0», l'état logique de comptage est avancé d'un pas, ce qui fait que le fonctionnement des étages du diviseur subit une avance. Ainsi, la fréquence du signal de sortie du diviseur peut être ajustée (augmentée ou diminuée) par le fait qu'un 45 état logique différent de celui qui est détecté par un détecteur se trouve inscrit dans le circuit diviseur. Ceci est réalisé par le schéma représenté à la fig. 2.

Lorsque le niveau de signal à la sortie du circuit diviseur 9 est «1», le circuit de détection 10 se trouve dans sa position 50 de repos. Lorsque le signal à la sortie du circuit diviseur 9 passe au niveau logique «0», le signal de détection est mis en attente. Dans ce cas, au moment où la sortie Q4 de l'étage diviseur 8 passe au niveau logique «1», le circuit détecteur 10 bascule et sa sortie passe au niveau «1». A cet instant, on 55 obtient à la sortie de la porte ET 15, un signal différentiel, c'est-à-dire un signal comprenant une impulsion dont le début coïncide avec le saut de la sortie du circuit 10 au niveau logique «1» et dont la fin correspond au basculement du circuit-verrou 14 que ce saut va produire peu après. Ce 60 signal différentiel constitue un signal de commande pour l'inscription des données dans les étages du diviseur. Lorsque ce signal différentiel présente son impulsion logique de niveau «1», les données provenant des connexions d'entrée 11, 12 et 13 sont transmises par les portes 16, 17 et 18, et 65 inscrites dans les quatre flip-flops (étages diviseurs par deux) 7 et 8 de l'ensemble diviseur.

Par exemple, des niveaux logiques «1», «1» et «1» sur les connexions d'entrée 11, 12 et 13 amènent des niveaux

logiques «1» sur les sorties des portes ET 16, 17 et 18. Dans ce cas, les sorties  $Q_2$  et  $Q_3$  des étages diviseurs 7 deviennent «1» et «1», respectivement, tandis que les sorties  $Q_4$  et  $Q_5$  des étages du diviseur 8 deviennent «0», «0», étant donné que le signal de sortie de la porte ET 18 est appliqué à l'entrée de remise à zéro de ces étages diviseurs 8. De cette façon, les niveaux logiques aux sorties des étages diviseur 7 et 8 changent de «0», «0», «1», «0» à «1», «1», «0», «0». Il s'agit du processus de recul d'un pas et, par ce processus, le signal de sortie de la division de fréquence est retardé d'un pas.

Le détecteur 10 est constitué d'un flip-flop R-S, formé de deux portes OU INVERSE. Une fois que l'état «1» de la sortie Q<sub>4</sub> de l'étage diviseur 8 a été détecté, le détecteur 10 ne revient pas à son état initial tant que la sortie du circuit diviseur à n étages 9 ne revient pas au niveau logique «1». En conséquence, le signal de commande d'inscription de données, délivré par la porte ET 15 détectera le prochain passage de la sortie Q<sub>4</sub> de l'étage diviseur 8 au niveau logique «1» seulement après que la sortie du circuit diviseur 9 aura repassé de l'état logique «1» à l'état logique «0».

Selon la fig. 2, la combinaison d'états logiques «0», «0», «1», «0», sur les sorties Q<sub>2</sub>, Q<sub>3</sub>, Q<sub>4</sub> et Q<sub>5</sub> peut être détectée simplement par une détection sur la sortie Q<sub>4</sub>, et ceci encore seulement à la condition que l'état de la sortie du diviseur 9 le permette. Naturellement, il est possible de détecter non seulement la combinaison d'états logiques spécifiée cidessus, mais également toute autre combinaison logique désirée, un certain nombre de sorties devant alors être réunies sur les entrées d'une porte ET dont la sortie est connectée à l'entrée du détecteur 10.

Selon la fig. 2, la valeur minimale pouvant être ajustée est 1/16384 × 86400 × 1/10 = 0,53 sec/jour, le signal de sortie du diviseur 9 à n étages étant un signal ayant une période de 10 sec et le signal de sortie du circuit diviseur par deux 6 étant d'une fréquence 16 384 Hz. Etant donné que cette forme d'exécution présente trois connexions d'entrée (11, 12, 13), l'ajustement de fréquence est possible dans un domaine situé entre 2,11 sec/jour de retard et 1,58 sec/jour d'avance.

On va considérer maintenant, en liaison avec la fig. 4, une forme d'exécution de l'objet de l'invention, comprenant cinq connexions d'entrée (19, 20, 21, 22, 23) qui, pour un ajustement plus précis, travaillent sur deux niveaux d'ajustement, l'un grossier, l'autre fin. L'ensemble de circuits de la fig. 4 fonctionne, pour certaines parties, de la même manière que celui de la fig. 2, de sorte que les explications concernant ces parties-là sont omises. Dans la forme d'exécution de l'invention, selon la fig. 4, un signal de sortie supplémentaire, est délivré par le circuit diviseur 9 à n étages et est appliqué à un circuit détecteur supplémentaire 25 pour un ajustement de précision, ce signal ayant une période de 120 sec, et résultant de la détection de la combinaison logique «0», «0», «0», «0», «0», «0» et «L», respectivement sur les sorties Q2, Q3, Q4, Q5, Q6 et Q7. Comme on le voit à la fig. 4, un signal ayant une période de 10 sec est également encore appliqué comme auparavant au détecteur 10, tandis que le signal à période de 120 sec est appliqué au détecteur 25. De cette façon, il est possible de réaliser indépendamment un ajustement grossier et un ajustement fin.

L'ajustement grossier, commandé par les niveaux logiques sur chacune des trois entrées 11, 12 et 13 intervient toutes les 10 sec, sur fonctionnement du flip-flop RS 10 et du flip-flop-bascule 14. Hormis, la présence de portes de collection 28 et 29, permettant la combinaison, à l'entrée S des étages de division 7, de la commande d'ajustement grossier 11, 12, 13 et de la commande d'ajustement fin 19–23, l'agencement d'ajustement grossier de la fig. 4 correspond à celui qui a été considéré en liaison avec la fig. 2.

Dans l'agencement de la fig. 4, on a de plus un agencement d'ajustage fin, commandé par les entrées 19-23, qui fait intervenir une correction toutes les 120 sec, sur fonctionnement du flip-flop RS 25 et du flip-flop-bascule 26. La 5 définition de la correction d'ajustage grossier, intervenant toutes les 10 sec, et de 0,53 sec/jour, tandis que la définition de la correction d'ajustage fin, intervenant toutes les 120 sec, est de 0,044 sec/jour. Le schéma de la fig. 4, considéré à la suite de celui de la fig. 2, sera aisément compris par l'homme 10 de métier. On note qu'à la fig. 4, une porte 27 joue, pour le flip-flop-bascule 26, le même rôle que la porte 15 pour le flip-flop-bascule 14, déjà présent à la fig. 2, et on note également que les simples portes ET 16 et 17 de la fig. 2 sont, à la fig. 4, remplacées par les portes combinées «de collec-15 tion» 28 et 29. De plus, à la fig. 4, trois portes 30, 31, 32 jouent, pour l'ajustement fin en fonction des entrées 19-23, un rôle analogue à celui de la porte 18 (fig. 2 et 4).

Dans l'ajustement fin, les niveaux sur les entrées 19 et 20 provoquent la même correction que les niveaux homologues 20 sur les entrées 11 et 12 de l'ajustage grossier, cette correction étant toutefois d'importance douze fois moindre, puisque la correction n'intervient que toutes les 120 sec au lieu d'intervenir toutes les 10 sec.

Pour la correction grossière, telle qu'elle a été expliquée 25 en liaison avec les fig. 2 et 3, on avait, selon l'exemple purement informatif représenté, sept possibilités d'action, résultant de deux possibilités d'action positives (+1), (+2) et d'une possibilité d'action négative (-4). Ces sept possibilités étaient appliquées aux flips-flops 7 et 24, les premiers 30 ajustés par leur entrée S, et les derniers par leur entrée R. Pour l'ajustement fin, qui agit de toute façon dans une mesure douze fois moindre que l'ajustement grossier, on a prévu uniquement des corrections positives, sur cinq flip-flops successifs, par l'intermédiaire des portes 28 à 32.

L'ajustement grossier et l'ajustement précis sont réalisés en alternance, en dépendance de celle des périodes des détecteurs qui est en fonction. Sur la fig. 4, les étages de division par deux 24 sont des flip-flops présentant à la fois une connexion d'entrée de remise à zéro (reset) et une connexion d'entrée de mise à l'état de travail (set), et on a en plus des portes ET-OU 28 et 29 qui conditionnent et assurent l'inscription des données pour chacun des deux ajustements, grossier et précis.

Les organes d'entrée pour déterminer les données déli-45 vrées aux étages du diviseur ne se limitent pas à ce qui est représenté (fig. 4: des transistors de commutation), mais peuvent être de différents autres types. Par exemple, il est avantageusement possible d'utiliser un commutateur rotatif comme celui que représente la fig. 6. Lorsque le rotor 34 50 vient en contact avec les connexions d'électrodes 11, 12 et 13, le niveau logique de chaque entrée est «1», tandis qu'il est «0» lorsque aucun contact n'est établi. Comme il existe plusieurs positions dans lesquelles le rotor 34 est en contact avec une connexion d'entrée, cela permet d'avoir différentes 55 combinaisons, le rotor pouvant être en même temps en connexion ou hors de connexion avec une autre entrée. Si un compteur est établi et si les signaux de sortie provenant des digits respectifs de ce compteur sont appliqués comme signaux d'entrée sur les connexions d'entré de détermination 60 de comptage, ce compteur entre en action chaque fois qu'une impulsion d'horloge est appliquée. Ceci permet différentes combinaisons de signaux d'entrée.

Par ailleurs, comme le montre la fig. 5, il est également possible que l'état de niveau logique des connexions de 65 détermination de données soit établi en réponse à un convertisseur de code 33.

Les niveaux logiques sur les trois entrées 11, 12 et 13 peuvent se combiner, selon huit combinaisons. Le convertis-

seur de code 33 de la fig. 5 (a), applicable aussi bien au schéma de la fig. 2 qu'au schéma de la fig. 4, permet de prévoir à choix huit corrections individuelles. Comme le montre la fig. 5 (b), les huit combinaisons différentes sur les entrées 11, 12, 13, permettent d'avoir chaque fois un niveau logique «1» sur une des sorties 34 à 41, alors que les sept autres ont un niveau logique «0». L'utilisation d'un tel décodeur permet «d'individualiser» les huit corrections d'ajustement possibles, lesquelles peuvent alors se répartir d'une façon non forcément linéaire (l'écart entre les corrections 40 et 41 peut par exemple être supérieur à l'écart entre les corrections 39 et 40, de même l'écart entre les corrections 35 pourrait être supérieur à l'écart entre les corrections 35 et 36, le convertisseur 33 supprimant l'obligation de respecter la progression binaire).

Le cadencement pour l'inscription des données dans les étages du diviseur est déterminé par un changement volontaire de l'état logique des étages de division conditionnant le circuit de détection, lequel détermine ce cadencement. Ceci rend possible un choix, au gré de l'opérateur parmi une grande quantité de possibilités de degrés de réglage.

Il ressort de ce que l'on vient de décrire que la conception particulière proposée permet de réaliser facilement une pièce d'horlogerie électronique, notamment une montre-bracelet électronique, aisément et rapidement ajustable avec une haute précision. On note que la méthode de régulation proposée pourrait également être combinée avec la méthode de régulation classique, à trimmer. La montre, objet de l'invention, peut être réalisée à l'aide d'un arrangement de circuits simples. Les connexions de détermination de données, pour chaque ajustement, fin et grossier, sont ajoutées à un arrangement de circuits classique. La conception particulière proposée est donc fort avantageuse.

20

25

30

35

40

45

50

55

60

65

|    | Q <sub>5</sub> | Q <sub>4</sub> | $Q_3$ | Q <sub>2</sub> |

|----|----------------|----------------|-------|----------------|

| -4 | 0              | 0              | 0     | 0              |

| -3 | 0              | 0              | 0     | 1              |

| -2 | 0              | 0              | 1     | 0              |

| -1 | 0              | 0              | 1     | 1              |

| 0  | 0              | 1              | 0     | 0              |

| +1 | 0              | 1              | 0     | 1              |

| +2 | 0              | 1              | 1     | 0              |

| +3 | 0              | 1              | 1     | . 1            |

|    | 1              | 0              | 0     | 0              |

|    | 1              | 0              | 0     | 1              |

|    | 1              | 0              | 1     | 0              |

|    | 1              | 0              | 1     | 1              |

|    | 1              | 1              | 0     | 0              |

|    | 1              | 1              | 0     | 1              |

|    | 1              | 1              | 1     | 0              |

|    | 1              | 1              | 1     | 1              |

| ł  | 0              | 0              | 0     | 0              |

FIG. 1

FIG. 5

FIG. 6

FIG. 7