(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7550614号

(P7550614)

(45)発行日 令和6年9月13日(2024.9.13)

(24)登録日 令和6年9月5日(2024.9.5)

(51)国際特許分類

|         |                 |         |       |         |

|---------|-----------------|---------|-------|---------|

| G 0 6 F | 12/00 (2006.01) | G 0 6 F | 12/00 | 5 6 0 F |

| G 0 6 F | 9/34 (2018.01)  | G 0 6 F | 9/34  | 3 5 0 A |

| G 0 6 F | 12/06 (2006.01) | G 0 6 F | 9/34  | 3 5 0 B |

| G 1 1 C | 5/04 (2006.01)  | G 0 6 F | 12/06 | 5 4 0 E |

| H 1 0 B | 12/00 (2023.01) | G 1 1 C | 5/04  | 2 2 0   |

請求項の数 22 (全32頁) 最終頁に続く

(21)出願番号 特願2020-191783(P2020-191783)

(22)出願日 令和2年11月18日(2020.11.18)

(65)公開番号 特開2021-128752(P2021-128752)

A)

(43)公開日 令和3年9月2日(2021.9.2)

審査請求日 令和5年9月22日(2023.9.22)

(31)優先権主張番号 62/975,577

(32)優先日 令和2年2月12日(2020.2.12)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 16/859,829

(32)優先日 令和2年4月27日(2020.4.27)

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 12

9

129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

(74)代理人 110000051

弁理士法人共生国際特許事務所

(72)発明者 マラディ, クリシュナ テジャ

アメリカ合衆国, 95135 カリフォ

ルニア州, サンノゼ, ロートレック ド

最終頁に続く

(54)【発明の名称】 インメモリコンピューティングに対するデータ配置のための方法及びその方法が適用されたメモリモジュール

## (57)【特許請求の範囲】

## 【請求項 1】

メモリモジュールであって、

ダイナミックランダムアクセスメモリ (DRAM) バンクを含むメモリダイと、

ホストプロセッサからオペランド及び命令を受信するメモリコントローラと、を備え、

前記 DRAM バンクは、

複数のページに配列された DRAM セルのアレイと、

算術論理ユニット (ALU) を含むインメモリコンピューティング (IMC) モジュールと、を含み、

前記メモリコントローラは、

前記命令に基づいて、複数のデータレイアウトの中から、前記 DRAM セルのアレイの前記複数のページから前記 IMC モジュールへの前記オペランドの配置を指定するためのデータレイアウトを決定し、

前記決定されたデータレイアウトに従って、前記 DRAM バンクに前記オペランドを供給し、

前記命令に従って、前記オペランドに対して前記 ALU による演算を実行するように、前記 DRAM バンクの前記 IMC モジュールを制御するように構成され、

前記 IMC モジュールは、オペランドレジスタを更に含み、

前記オペランドは、第 1 のオペランド及び第 2 のオペランドを含み、

前記複数のデータレイアウトの中から一つのオペランド (TOP) データレイアウトを

決定した場合、

前記第1のオペランドは、前記DRAMバンクの外部から前記IMCモジュールに供給され、

前記第2のオペランドは、前記DRAMセルから前記オペランドレジスタを介して前記IMCモジュールに供給されることを特徴とするメモリモジュール。

【請求項2】

前記第1のオペランドは、複数の第1のタイルに分割され、

前記第2のオペランドは、複数の第2のタイルに分割され、

各タイルは、複数の値を含み、

前記メモリコントローラは、

前記オペランドレジスタに前記第1のオペランドの第1のタイルを格納し、

前記オペランドレジスタに格納された前記第1のオペランドの第1のタイル、及び前記第2のオペランドの複数の第2のタイルの各々に対して、前記ALUによる演算を実行するように更に構成されることを特徴とする請求項1に記載のメモリモジュール。

【請求項3】

前記第1のオペランドは、複数の第1のタイルに分割され、

前記第2のオペランドは、複数の第2のタイルに分割され、

各タイルは、複数の値を含み、

前記複数のデータレイアウトの中から同じページ(SR)データレイアウトを決定した場合、

前記メモリコントローラは、前記DRAMセルの同じページに、一つ以上の前記第1のタイル及び一つ以上の前記第2のタイルを格納するように構成されることを特徴とする請求項1に記載のメモリモジュール。

【請求項4】

前記メモリコントローラは、

前記オペランドレジスタに前記一つ以上の前記第1のタイルの中の一つの第1のタイルを格納し、

前記オペランドレジスタに格納された前記第1のタイル、及び前記DRAMセルのアレイの前記第1のタイルと同じページに格納された前記一つ以上の前記第2のタイルのそれに対して、前記ALUによる演算を実行するように更に構成されることを特徴とする請求項3に記載のメモリモジュール。

【請求項5】

前記DRAMバンクの前記IMCモジュールは、アキュムレータを更に含み、

前記アキュムレータは、累積値を格納するように構成されたアキュムレータレジスタを含み、

前記アキュムレータは、

前記ALUによって演算された出力を受信し、

前記累積値と前記出力との合計で前記アキュムレータレジスタを更新するように構成され、

前記命令は、前記第1のオペランドと前記第2のオペランドとの内積を計算することを含み、

前記第1のタイルの中の一つの第1のタイルは、行データを格納し、

前記第2のタイルの中の一つの第2のタイルは、列データを含むことを特徴とする請求項4に記載のメモリモジュール。

【請求項6】

前記第1のタイルは、第1の数の値を有し、

前記第2のタイルは、第2の数の値を有し、

前記DRAMバンクの前記IMCモジュールは、出力バッファを含み、

前記出力バッファは、前記第1の数の値と前記第2の数の値との積以上を格納するためのサイズを有し、

10

20

30

40

50

前記命令は、前記第1のオペランドと前記第2のオペランドとの外積を計算することを含み、

前記第1のタイルの中の一つの第1のタイルは、行データを格納し、

前記第2のタイルの中の一つの第2のタイルは、列データを含むことを特徴とする請求項4に記載のメモリモジュール。

【請求項7】

前記第1のタイルは、第1の数の値を有し、

前記第2のタイルは、第2の数の値を有し、

前記DRAMバンクの前記IMCモジュールは、出力バッファを含み、

前記出力バッファは、前記第1の数の値及び前記第2の数の値の中の大きい方の値以上を格納するためのサイズを有し、

前記命令は、前記第1のオペランドと前記第2のオペランドとのテンソル積を計算することを含み、

前記第1のタイルの中の一つの第1のタイルは、行データを格納し、

前記第2のタイルの中の一つの第2のタイルは、列データを含むことを特徴とする請求項4に記載のメモリモジュール。

【請求項8】

前記第1のオペランドは、複数の第1のタイルに分割され、

前記第2のオペランドは、複数の第2のタイルに分割され、

各タイルは、複数の値を含み、

前記複数のデータレイアウトの中から異なるページ(DR)データレイアウトを決定した場合、

前記メモリコントローラは、

前記DRAMセルのアレイの第1のページに前記第1のタイルのサブセットを格納し、

前記DRAMセルのアレイの第2のページに前記第2のタイルのサブセットを格納するように構成されることを特徴とする請求項1に記載のメモリモジュール。

【請求項9】

前記メモリコントローラは、

前記オペランドレジスタに前記第1のページから前記第1のオペランドの第1のタイルを格納し、

前記オペランドレジスタに格納された前記第1のオペランドの第1のタイル、及び前記第2のページからの前記第2のオペランドの複数の第2のタイルのそれぞれに対して、前記ALUによる演算を実行するように更に構成されることを特徴とする請求項8に記載のメモリモジュール。

【請求項10】

前記DRAMバンクの前記IMCモジュールは、前記ALUによって演算された出力をバッファリングするように構成されたハードウェアのバッファを更に含むことを特徴とする請求項1に記載のメモリモジュール。

【請求項11】

前記ハードウェアのバッファは、前記IMCモジュールの結果レジスタのサイズの4倍以上のサイズを有することを特徴とする請求項10に記載のメモリモジュール。

【請求項12】

前記DRAMバンクの前記IMCモジュールは、アキュムレータを更に含み、

前記アキュムレータは、累積値を格納するように構成されたアキュムレタレジスタを含み、

前記アキュムレータは、

前記ALUによって演算された出力を受信し、

前記累積値と前記出力との合計で前記アキュムレタレジスタを更新するように構成されることを特徴とする請求項1に記載のメモリモジュール。

【請求項13】

10

20

30

40

50

前記メモリモジュールは、シリコン貫通電極によって接続されたメモリダイのスタックを含む高帯域幅メモリ（HBM）モジュールであり、

前記メモリダイのスタックは、前記メモリダイを含むことを特徴とする請求項1に記載のメモリモジュール。

【請求項14】

インメモリ（in-memory）計算を実行する方法であって、

メモリモジュールのメモリコントローラによって、ホストプロセッサからオペランド及び命令を受信する段階と、

前記メモリコントローラによって、前記命令に基づいて、複数のデータレイアウトの中からデータレイアウトを決定する段階と、

前記決定されたデータレイアウトに従って、前記メモリモジュールのダイナミックランダムアクセスメモリ（DRAM）バンクに前記オペランドを供給する段階と、

前記命令に従って、前記オペランドに対して算術論理ユニット（ALU）による演算を実行するように、前記DRAMバンクのインメモリコンピューティング（IMC）モジュールを制御する段階と、を有し、

前記DRAMバンクは、

複数のページに配列されたDRAMセルのアレイと、

前記ALUを含む前記IMCモジュールと、を含み、

前記データレイアウトは、前記DRAMセルのアレイの前記複数のページから前記IMCモジュールへの前記オペランドの配置を指定し、

前記IMCモジュールは、オペランドレジスタを更に含み、

前記オペランドは、第1のオペランド及び第2のオペランドを含み、

前記複数のデータレイアウトの中から一つのオペランド（OP）データレイアウトを決定した場合、

前記第1のオペランドは、前記DRAMバンクの外部から前記IMCモジュールに供給され、

前記第2のオペランドは、前記DRAMセルから前記オペランドレジスタを介して前記IMCモジュールに供給されることを特徴とする方法。

【請求項15】

前記第1のオペランドは、複数の第1のタイルに分割され、

前記第2のオペランドは、複数の第2のタイルに分割され、

各タイルは、複数の値を含み、

前記メモリコントローラは、

前記オペランドレジスタに前記第1のオペランドの第1のタイルを格納し、

前記オペランドレジスタに格納された前記第1のオペランドの第1のタイル、及び前記第2のオペランドの複数の第2のタイルの各々に対して、前記ALUによる演算を実行するように更に構成されることを特徴とする請求項14に記載の方法。

【請求項16】

前記第1のオペランドは、複数の第1のタイルに分割され、

前記第2のオペランドは、複数の第2のタイルに分割され、

各タイルは、複数の値を含み、

前記複数のデータレイアウトの中から同じページ（SR）データレイアウトを決定した場合、

前記メモリコントローラは、前記DRAMセルの同じページに、一つ以上の前記第1のタイル及び1つ以上の前記第2のタイルを格納するように構成されることを特徴とする請求項14に記載の方法。

【請求項17】

前記メモリコントローラは、

前記オペランドレジスタに前記一つ以上の前記第1のタイルの中の一つの第1のタイルを格納し、

10

20

30

40

50

前記オペランドレジスタに格納された前記第1のタイル、及び前記D R A Mセルのアレイの前記第1のタイルと同じページに格納された前記一つ以上の前記第2のタイルのそれに対して、前記A L Uによる演算を実行するように更に構成されることを特徴とする請求項16に記載の方法。

【請求項18】

前記D R A Mバンクの前記I M Cモジュールは、アキュムレータを更に含み、

前記アキュムレータは、累積値を格納するように構成されたアキュムレータレジスタを含み、

前記アキュムレータは、

前記A L Uによって演算された出力を受信し、

前記累積値と前記出力との合計で前記アキュムレータレジスタを更新するように構成され、

前記命令は、前記第1のオペランドと前記第2のオペランドとの内積を計算することを含み、

前記第1のタイルの中の一つの第1のタイルは、行データを格納し、

前記第2のタイルの中の一つの第2のタイルは、列データを含むことを特徴とする請求項17に記載の方法。

【請求項19】

前記第1のタイルは、第1の数の値を有し、

前記第2のタイルは、第2の数の値を有し、

前記D R A Mバンクの前記I M Cモジュールは、出力バッファを含み、

前記出力バッファは、前記第1の数の値と前記第2の数の値との積以上を格納するためのサイズを有し、

前記命令は、前記第1のオペランドと前記第2のオペランドとの外積を計算することを含み、

前記第1のタイルの中の一つの第1のタイルは、行データを格納し、

前記第2のタイルの中の一つの第2のタイルは、列データを含むことを特徴とする請求項17に記載の方法。

【請求項20】

前記第1のタイルは、第1の数の値を有し、

前記第2のタイルは、第2の数の値を有し、

前記D R A Mバンクの前記I M Cモジュールは、出力バッファを含み、

前記出力バッファは、前記第1の数の値及び前記第2の数の値の中の大きい方の値以上を格納するためのサイズを有し、

前記命令は、前記第1のオペランドと前記第2のオペランドとのテンソル積を計算することを含み、

前記第1のタイルの中の一つの第1のタイルは、行データを格納し、

前記第2のタイルの中の一つの第2のタイルは、列データを含むことを特徴とする請求項17に記載の方法。

【請求項21】

前記第1のオペランドは、複数の第1のタイルに分割され、

前記第2のオペランドは、複数の第2のタイルに分割され、

各タイルは、複数の値を含み、

前記複数のデータレイアウトの中から異なるページ(D R)データレイアウトを決定した場合、

前記メモリコントローラは、

前記D R A Mセルのアレイの第1のページに前記第1のタイルのサブセットを格納し、

前記D R A Mセルのアレイの第2のページに前記第2のタイルのサブセットを格納するよう構成されることを特徴とする請求項14に記載の方法。

【請求項22】

10

20

30

40

50

前記メモリコントローラは、

前記オペランドレジスタに前記第1のページから前記第1のオペランドの第1のタイル

を格納し、

前記オペランドレジスタに格納された前記第1のオペランドの第1のタイル、及び前記

第2のページからの前記第2のオペランドの複数の第2のタイルのそれぞれに対して、前

記ALUによる演算を実行するように更に構成されることを特徴とする請求項21に記載

の方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、インメモリコンピューティングに対するデータ配置のためのシステム及び方

法に関する。

【背景技術】

【0002】

高帯域幅メモリ (High Bandwidth Memory; HBM) は、グラフィック処理装置 (GPU) 用高性能メモリとしてしばしば使用される。HBMは、一般的なDRAMに比べて非常に広いバスを有するという利点がある。現在のHBMアーキテクチャは、シリコン貫通電極 (through silicon via; TSV) を使用して接続される複数のスタックDRAMダイ (例えば、ダイス (dice)) と、HBMのバッファ及びGPUのHBMメモリコントローラとして機能するロジックダイとを含む。メモリ内のプロセス (例えば、インメモリ処理 (in-memory processing)) 機能をメモリシステムに追加することによって、さらに性能が向上する。

20

【0003】

上述の内容は、本発明の実施形態の背景に対する理解を深めるためだけのものであり、

従来技術を構成しない情報を含む。

【先行技術文献】

【特許文献】

【0004】

30

【文献】特開2019-075101号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、上記従来技術に鑑みてなされたものであって、本発明の目的は、メモリモジ

ュールの性能を向上させることができる方法、及び性能が向上したメモリモジュールを提

供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するためになされた本発明の一態様によるメモリモジュールは、複数の

ダイナミックランダムアクセスメモリ (DRAM) バンクを含むメモリダイと、メモリコ

ントローラと、を含み、前記DRAMバンクの各々は、複数のページに配列されたDRAM

セルのアレイと、前記複数のページの内の開かれたページの値を格納する行バッファと

、入出力 (IO) モジュールと、インメモリコンピューティング (IMC) モジュールと

、を含み、前記ページの各々は複数の前記DRAMセルを含み、前記DRAMセルの各々

はビット値を格納し、前記IMCモジュールは、前記行バッファ又は前記IOモジュール

からオペランドを受信し、前記オペランド及び複数の算術論理演算から選択された一つの

算術論理演算に基づいて出力を計算するように構成された算術論理ユニット (ALU) と

、前記ALUによって計算された前記出力を格納するように構成された結果レジスタと、

を含み、前記メモリコントローラは、ホストプロセッサから、第1のオペランド、第2の

オペランド、及び命令を受信し、前記命令に基づいて、複数のデータレイアウトから一つの

データレイアウトを決定し、前記一つのデータレイアウトに従って、前記DRAMバン

40

50

クに前記第1のオペランド及び前記第2のオペランドを供給し、前記命令に従って、前記第1のオペランド及び第2のオペランドに対して前記複数の算術論理演算のうち前記一つの算術論理演算を実行するように、前記DRAMバンクの前記IMCモジュールを制御するように構成されたことを特徴とする。

#### 【0007】

前記複数のデータレイアウトは、一つのオペランド(1OP)データレイアウトを含み、前記第1のオペランドは、前記DRAMセルに書き込まれ、前記第2のオペランドは、前記ホストプロセッサから前記DRAMバンクの前記IMCモジュールに直接供給され得る。

#### 【0008】

前記IMCモジュールは、オペランドレジスタをさらに含み、前記メモリコントローラは、さらに、前記オペランドレジスタに前記第1のオペランドの第1のタイルを格納し、前記オペランドレジスタに格納された前記第1のオペランドの第1のタイル、及び前記第2のオペランドの複数の第2のタイルの各々に対して、算術論理演算を実行するように構成され得る。

#### 【0009】

前記第1のオペランドは複数の第1のタイルに分割され、前記第2のオペランドは複数の第2のタイルに分割され、前記タイルの各々は複数の値を含み、前記複数のデータレイアウトは同じ行(SR)データレイアウトを含み、前記メモリコントローラは、前記DRAMセルのアレイの同じページに一つ以上の前記第1のタイル及び一つ以上の前記第2のタイルを格納し得る。

10

#### 【0010】

前記IMCモジュールは、オペランドレジスタをさらに含み、前記メモリコントローラは、さらに、前記オペランドレジスタに前記一つ以上の第1のタイルの内の一つの第1のタイルを格納し、前記オペランドレジスタに格納された前記第1のオペランド、及び前記DRAMセルのアレイの前記第1のタイルと同じページに格納された一つ以上の前記第2のタイルのそれぞれに対して、算術論理演算を実行するように構成され得る。

20

#### 【0011】

前記DRAMバンクの前記IMCモジュールは、アキュムレータ(accumulat or)をさらに含み、前記アキュムレータは、累積値を格納するように構成されたアキュムレータレジスタを含み、前記アキュムレータは、前記ALUによって計算された出力を受信し、累積値と出力との合計で前記アキュムレータレジスタを更新するように構成され、前記命令は、前記第1のオペランドと前記第2のオペランドの内積を計算することを含み、前記第1のタイルの内の前記一つの第1のタイルは行データを格納し、前記第2のタイルの内の一つの第2のタイルは列データを含み得る。

30

#### 【0012】

前記第1のタイルは第1の数の値を有し、前記第2のタイルは第2の数の値を有し、前記DRAMバンクの前記IMCモジュールは、出力バッファを含み、前記出力バッファは、前記第1の数の値と前記第2の数の値の積以上を格納するためのサイズを有し、前記命令は、前記第1のオペランドと前記第2のオペランドの外積を計算することを含み、前記第1のタイルの内の前記一つの第1のタイルは行データを格納し、前記第2のタイルの内の一つ第2のタイルは列データを含み得る。

40

#### 【0013】

前記第1のタイルは第1の数の値を有し、前記第2のタイルは第2の数の値を有し、前記DRAMバンクの前記IMCモジュールは、出力バッファを含み、前記出力バッファは、前記第1の数の値と前記第2の数の値の内の大きい方の値以上を格納するためのサイズを有し、前記命令は、前記第1のオペランドと前記第2のオペランドのテンソル積を計算することを含み、前記第1のタイルの内の前記一つの第1のタイルは行データを格納し、前記第2のタイルの内の一つの第2のタイルは列データを含み得る。

#### 【0014】

50

前記第1のオペランドは複数の第1のタイルに分割され、前記第2のオペランドは複数の第2のタイルに分割され、前記タイルの各々は複数の値を含み、前記複数のデータレイアウトは、異なる行(D R)データレイアウトを含み、前記メモリコントローラは、前記D R A Mセルのアレイの第1のページに前記第1のタイルのサブセットを格納し、前記D R A Mセルのアレイの第2のページに前記第2のタイルのサブセットを格納し得る。

【0015】

前記I M Cモジュールは、オペランドレジスタをさらに含み、前記メモリコントローラは、さらに、前記オペランドレジスタの前記第1のページから前記第1のオペランドの第1のタイルを格納し、前記オペランドレジスタに格納された前記第1のオペランド、及び前記第2のページから前記第2のオペランドの複数の第2のタイルのそれぞれに算術論理演算を実行するように構成されることが好ましい。

10

【0016】

前記D R A Mバンクの各々の前記I M Cモジュールは、前記A L Uによって計算された前記出力をバッファリングするように構成されたバッファをさらに含むことが好ましい。

【0017】

前記バッファは、前記結果レジスタのサイズの4倍以上のサイズを有し得る。

【0018】

前記D R A Mバンクの各々の前記I M Cモジュールは、アキュムレータをさらに含み、前記アキュムレータは、累積値を格納するように構成されたアキュムレータレジスタを含み、前記アキュムレータは、前記A L Uによって計算された前記出力を受信し、前記累積値と前記出力との合計で前記アキュムレータレジスタを更新するように構成されることが好ましい。

20

【0019】

前記メモリモジュールは、シリコン貫通電極によって接続されたメモリダイのスタックを含む高帯域幅メモリ(H B M)モジュールであり、前記メモリダイのスタックは、前記メモリダイを含み得る。

【0020】

上記目的を達成するためになされた本発明の一態様による方法は、インメモリ計算を実行する方法において、メモリモジュールのメモリコントローラによって、第1のオペランド、第2のオペランド、命令を受信する段階と、前記メモリコントローラによって、前記命令に基づいて複数のデータレイアウトから一つのデータレイアウトを決定する段階と、前記データレイアウトに従って、前記メモリモジュールの少なくとも一つのD R A Mバンクに前記第1のオペランド及び前記第2のオペランドを供給する段階と、前記命令に従って、前記第1のオペランド及び前記第2のオペランドに対して複数の算術論理演算の内一つの算術論理演算を実行するように、前記D R A MバンクのI M Cモジュールを制御する段階と、を含み、前記D R A Mバンクの各々は、複数のページに配列されたD R A Mセルのアレイと、前記複数のページの内の開かれたページの値を格納する行バッファと、I Oモジュールと、前記I M Cモジュールと、を含み、前記ページの各々は前記D R A Mセルを含み、前記D R A Mセルの各々はビット値を格納し、前記I M Cモジュールは、前記行バッファ又は前記I Oモジュールからオペランドを受信し、前記オペランド及び複数の算術論理演算から選択された一つの算術論理演算に基づいて出力を計算するように構成されたA L Uと、前記A L Uによって計算された前記出力を格納するように構成された結果レジスタと、を含むことを特徴とする。

30

【0021】

前記複数のデータレイアウトは、一つのオペランド(1 O P)データレイアウトを含み、前記第1のオペランドは、前記D R A Mセルに書き込まれ、前記第2のオペランドは、前記ホストプロセッサから前記D R A Mバンクの前記I M Cモジュールに直接供給され得る。

40

【0022】

前記I M Cモジュールは、オペランドレジスタをさらに含み、前記メモリコントローラ

50

は、さらに、前記オペランドレジスタに前記第1のオペランドの第1のタイルを格納し、前記オペランドレジスタに格納された前記第1のオペランドの第1タイル、及び前記第2のオペランドの複数の第2のタイルの各々に対して、算術論理演算を実行するように構成され得る。

#### 【0023】

前記第1のオペランドは複数の第1のタイルに分割され、前記第2のオペランドは複数の第2のタイルに分割され、前記タイルの各々は複数の値を含み、前記複数のデータレイアウトは、同じ行(SR)データレイアウトを含み、前記メモリコントローラは、前記DRAMセルのアレイの同じページに一つ以上の前記第1のタイル及び1つ以上の前記第2のタイルを格納し得る。

10

#### 【0024】

前記IMCモジュールは、オペランドレジスタをさらに含み、前記メモリコントローラは、さらに、前記オペランドレジスタに前記一つ以上の第1のタイルの内の一つの第1のタイルを格納し、前記オペランドレジスタに格納された前記第1のオペランドと、前記DRAMセルのアレイの前記第1のタイルと同じページに格納された前記一つ以上の第2のタイルのそれぞれに対して、算術論理演算を実行するように構成され得る。

#### 【0025】

前記少なくとも一つのDRAMバンクの前記IMCモジュールは、アキュムレータをさらに含み、前記アキュムレータは、累積値を格納するように構成されたアキュムレータレジスタを含み、前記アキュムレータは、前記ALUによって計算された前記出力を受信し、前記累積値と前記出力との合計で前記アキュムレータレジスタを更新するように構成され、前記命令は、前記第1のオペランドと前記第2のオペランドの内積を計算する段階を含み、前記第1のタイルの内の前記一つの第1のタイルは行データを格納し、前記第2のタイルの内の一つの第2のタイルは列データを含み得る。

20

#### 【0026】

前記第1のタイルは第1の数の値を有し、前記第2のタイルは第2の数の値を有し、前記少なくとも一つのDRAMバンクの前記IMCモジュールは、出力バッファを含み、前記出力バッファは、前記第1の数の値と前記第2の数の値の積以上を格納するためのサイズを有し、前記命令は、前記第1のオペランドと前記第2のオペランドの外積を計算する段階を含み、前記第1のタイルの内の前記一つの第1のタイルは行データを格納し、前記第2のタイルの内の一つの第2のタイルは列データを含み得る。

30

#### 【0027】

前記第1のタイルは第1の数の値を有し、前記第2のタイルは第2の数の値を有し、前記少なくとも一つのDRAMバンクの前記IMCモジュールは、出力バッファを含み、前記出力バッファは、前記第1の数の値と前記第2の数の値の内の大きい方の値以上を格納するためのサイズを有し、前記命令は、前記第1のオペランドと前記第2のオペランドのテンソル積を計算する段階を含み、前記第1のタイルの前記一つの第1のタイルは行データを格納し、前記第2のタイルの内の一つの第2のタイルは列データを含み得る。

#### 【0028】

前記第1のオペランドは複数の第1のタイルに分割され、前記第2のオペランドは複数の第2のタイルに分割され、前記タイルの各々は複数の値を含み、前記複数のデータレイアウトは、異なる行(DR)データレイアウトを含み、前記メモリコントローラは、前記DRAMセルのアレイの第1のページに前記第1のタイルのサブセットを格納し、前記DRAMセルのアレイの第2のページに前記第2のタイルのサブセットを格納し得る。

40

#### 【0029】

前記IMCモジュールは、オペランドレジスタをさらに含み、前記メモリコントローラは、さらに、前記オペランドレジスタの前記第1のページから前記第1のオペランドの第1のタイルを格納し、前記オペランドレジスタに格納された前記第1のオペランド、及び前記第2のページから前記第2のオペランドの複数の第2のタイルのそれぞれに対して、算術論理演算を実行するように構成されることが好ましい。

50

## 【発明の効果】

## 【0030】

本発明によるインメモリコンピューティングに対するデータ配置のための方法及びその方法が適用されたメモリモジュールによれば、メモリモジュールの性能を向上させることができる。

## 【図面の簡単な説明】

## 【0031】

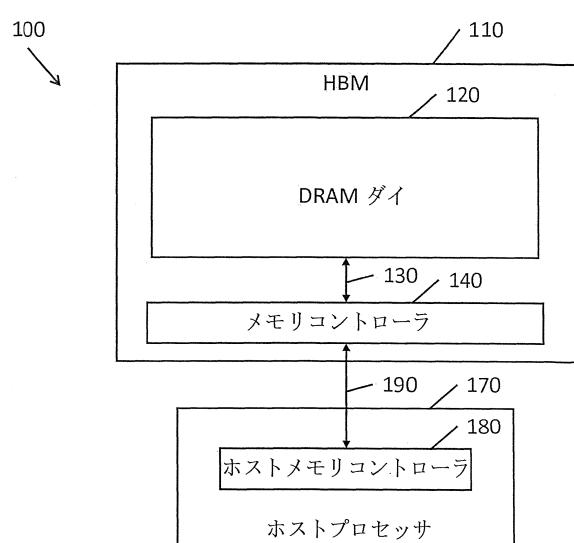

【図1】本発明の一実施形態によるメモリ（例えば、HBM）システムのアーキテクチャを示すブロック図である。

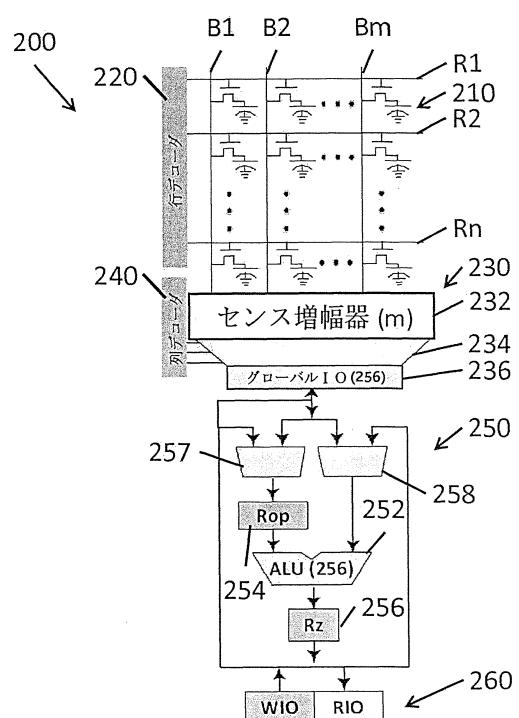

【図2A】本発明の一実施形態による、埋め込み算術論理ユニット（embedded ALU）を有するメモリバンクの概略ブロック図である。

10

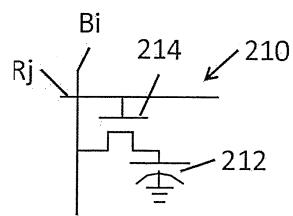

【図2B】本発明の一実施形態によるDRAMセルの例を示す回路図である。

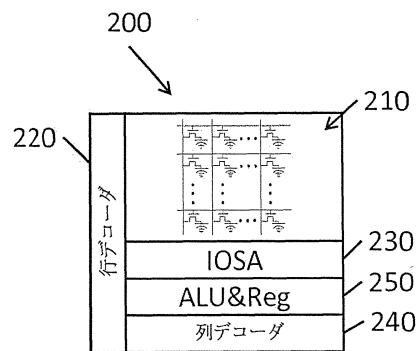

【図2C】DRAMセルのアレイ、行デコーダ、IOSA、IMCモジュール、及び列デコーダを含む、本発明の一実施形態によるDRAMバンクの概略図である。

【図3】本発明の一実施形態によるDRAMブロックのアレイを示す概略図である。

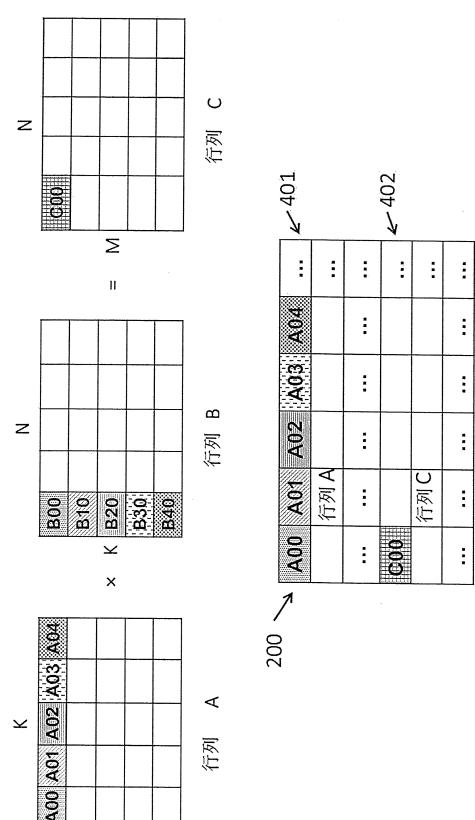

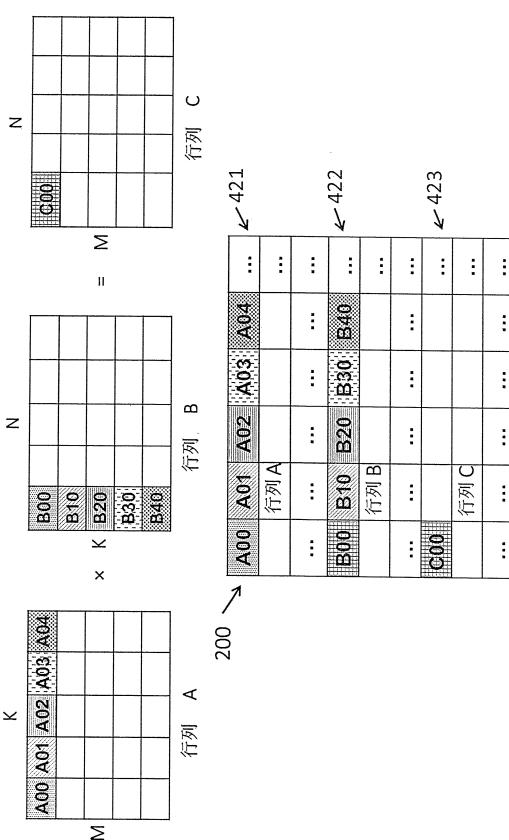

【図4A】第1のオペラント（行列A）がDRAMに格納され、第2のオペラント（行列B）が内蔵されたメモリモジュールの外部からブロードキャストされる場合のGEMMに対するデータの配置を、本発明の一実施形態による統合されたインメモリコンピューティング（IMC）と共に概略的に示す図である。

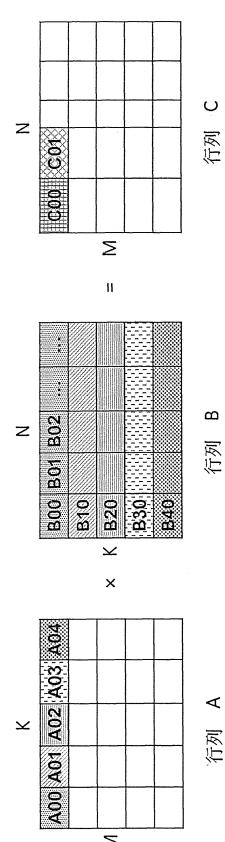

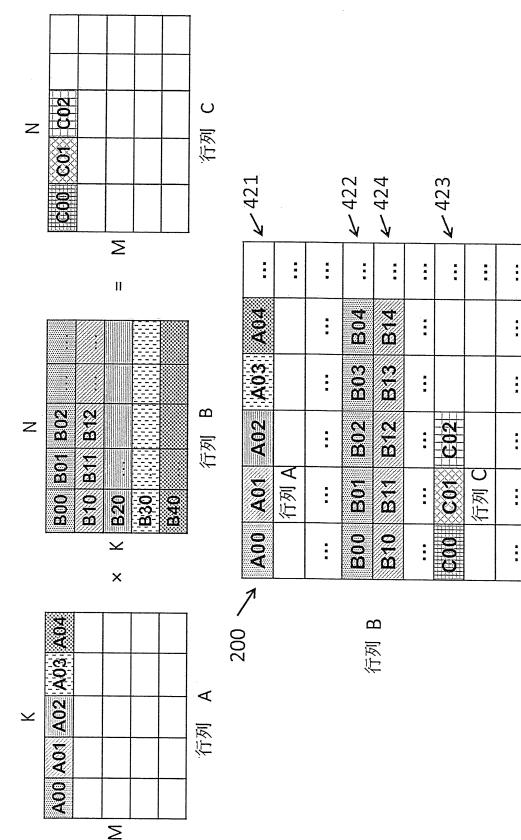

【図4B】双方のオペラント（行列A及び行列B）がメモリモジュールのDRAMの同じページに格納されている場合のGEMMに対するデータの配置を、本発明の一実施形態による統合されたIMCと共に概略的に示す図である。

20

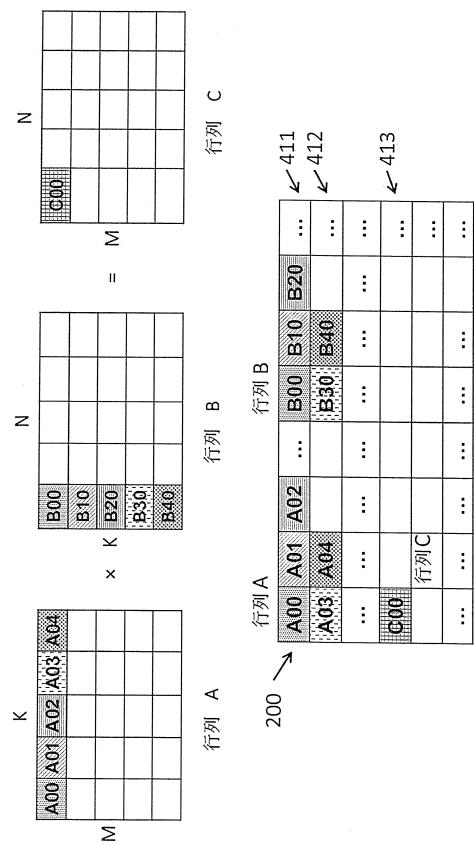

【図4C】双方のオペラント（行列A及び行列B）がメモリモジュールのDRAMの異なるページに格納されている場合のGEMMに対するデータの配置を、本発明の一実施形態による統合されたIMCと共に概略的に示す図である。

【図5A】一つのオペラント（1OP）データレイアウトにおける行列Aの第1の行と行列Bの第1の列との乗算の概略図である。

【図5B】1OPデータレイアウトにおける行列Aの第1の行の第1の値と行列Bの各列の第1の値との乗算をデータの再利用と共に示した概略図である。

【図6A】同じ行（SR）データレイアウトにおける行列Aの第1の行と行列Bの第1の列との乗算の概略図である。

30

【図6B】SRデータレイアウトにおける行列Aの第1の行の第1の値と行列Bの各列の第1の値に対するデータの再利用による乗算の概略図である。

【図7A】異なる行（DR）データレイアウトにおける行列Aの第1の行と行列Bの第1列との乗算の概略図である。

【図7B】DRデータレイアウトにおける行列Bの各列の第1の値と行列Aの第1の行の第2の値により、行列Bの各列の第2の値による行列Aの第1の行の第1の値のデータ再利用による乗算の概略図である。

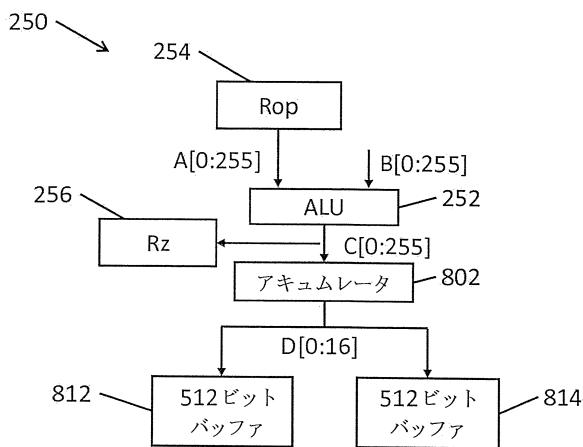

【図8】DRAMバンクのIMCモジュールの概略ブロック図である。

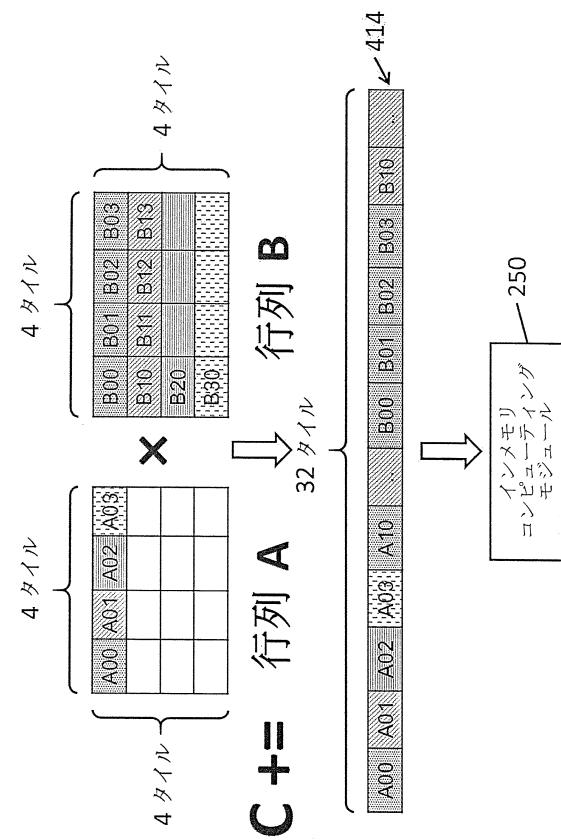

【図9】本発明の一部の実施形態による、同じ行（SR）レイアウトを使用する計算を説明するためのGEMMの一例の概略図である。

40

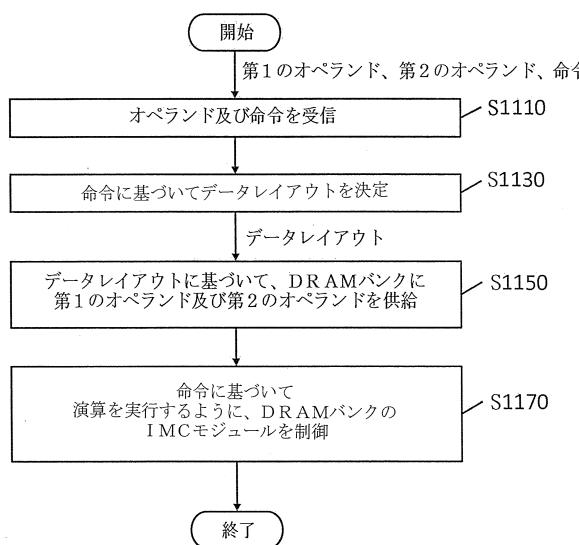

【図10】本発明の実施形態による、IMCモジュールを有するDRAMバンク内のデータの配置を制御するための方法を示すフローチャートである。

## 【発明を実施するための形態】

## 【0032】

本発明の特徴及びそれを達成するための方法は、以下の実施形態の詳細な説明及び図面を参照することにより、容易に理解される。以下、図面を参照しながら実施形態をより詳細に説明するが、図面全体にわたって同じ参照番号は同じ要素を指す。しかし、本発明は、様々な異なる形態で実施することができ、本明細書で説明する実施形態に限定されない。むしろ、これらの実施形態は、本発明が徹底且つ完全なものとなり、本発明の態様及び

50

特徴が当業者に十分に伝わるように例として提供するものである。したがって、本発明の態様及び特徴の完全な理解のために、当業者に不必要的プロセス、要素、及び技術は説明しない。特に記載がない限り、同様の参照番号は、図面及び明細書に記載された説明全体を通じて同様の要素を指すので、その説明は繰り返さない。図面において、要素、層、及び領域の相対的なサイズは、明確にするために誇張されている場合がある。

#### 【 0 0 3 3 】

以下の説明では、説明を目的として、様々な実施形態の完全な理解のために、多数の特定の詳細な説明を提示する。しかし、様々な実施形態は、これらの特定の詳細な説明がなくても実施でき、又は一つ以上の同等の構成で実施してもよい。他方、公知の構造及び装置は、様々な実施形態を曖昧にすることを避けるために、ロック図の形で示す。

10

#### 【 0 0 3 4 】

本明細書で使用される用語は、特定の実施形態を説明するためのものであり、本発明を限定することを意図するものではない。単数形の表現は、文脈がそうでないことを明確に示さない限り、複数形の表現も含む。本明細書で使用される「含む」及び「有する」などの用語は、開示する特徴、数字、ステップ、演算、要素、及び／又は構成要素の存在を特定するが、一つ以上の他の特徴、数字、ステップ、演算、要素、構成要素、及び／又はそれらの組み合わせの存在又は追加を排除するものではない。本明細書で使用される用語「及び／又は」は、一つ以上の関連して挙げられた項目の任意の且つ全ての組み合わせを含む。

#### 【 0 0 3 5 】

本明細書に記載する本発明の実施形態による電子又は電気装置及び／又は任意の他の関連装置又は構成要素は、任意の適切なハードウェア、ファームウェア（例えば、特定用途向け集積回路（A p p l i c a t i o n - S p e c i f i c I n t e g r a t e d C i r c u i t ））、ソフトウェア、又はそれらの組み合わせを利用して実装される。例えば、一部の環境では、これらの装置の様々な構成要素は、一つの集積回路（I C）チップ上に、又は別のI Cチップ上に形成される。また、これらの装置の様々な構成要素は、フレキシブルプリント回路フィルム、テープキャリアパッケージ（T C P）、プリント回路基板（P C B）上に実装されてもよく、又は一つの基板上に形成されてもよい。さらに、これらの装置の様々な構成要素は、コンピュータプログラム命令を実行し、本明細書で説明する様々な機能を行うために他のシステムの構成要素と相互作用する一つ以上のコンピューティングデバイス内における一つ以上のプロセッサ上で実行されるプロセス又はスレッドである。コンピュータプログラム命令は、例えば、ランダムアクセスメモリ（R A M）等の標準的なメモリデバイスを使用してコンピューティングデバイス内に実装されるメモリに格納される。コンピュータプログラム命令はまた、例えば、C D - R O M、フラッシュドライブなどの他の非一時的なコンピュータ読み取り可能媒体に格納される。また、当業者は、本発明の例示的な実施形態の思想及び範囲内で様々なコンピューティングデバイスの機能が単一のコンピューティングデバイスに結合若しくは統合されるか、又は特定のコンピューティングデバイスの機能が一つ以上の他のコンピューティングデバイスにわたって分散されることを認識すべきである。

20

30

#### 【 0 0 3 6 】

特に定義しない限り、本明細書で使用する技術用語又は科学用語を含むすべての用語は、本発明が属する技術分野の通常の知識を有する者が一般に理解するものと同じ意味を有する。また、通常使用される辞書に定義されているような用語は、関連技術及び／又は本明細書の文脈上の意味と一致すると解釈され、本明細書で明らかに定義しない限り、理想的又は過度に公式的な意味に解釈されない。

40

#### 【 0 0 3 7 】

本発明の一部の態様は、一般に、インメモリコンピューティング（i n - m e m o r y c o m p u t e ）の文脈におけるメモリ内のデータ配置の管理に関する。インメモリコンピューティングに関する内容の一例は、メモリを含むD R A M（D y n a m i c R a n d o m A c c e s s M e m o r y ）ダイと、H B Mロジックダイ上のA L U及びメモリ

50

コントローラとを含むHBMシステムであり、ここで、HBMロジックダイ上のALUは、インメモリコンピューティングを実行する。HBMロジックダイのメモリコントローラは、DRAMダイのメモリへのデータの格納、及びDRAMダイからのデータの読み取りを制御する。

#### 【0038】

明確化のため、本明細書で使用する用語「インメモリコンピューティング」は、DRAMダイに格納されたデータを使用して、外部データバスを通過することなく、高帯域幅メモリモジュール等のメモリモジュール内で計算を実行することを意味する。比較コンピュータシステムでは、プロセッサは外部DRAMデータバスを介してメインメモリ（例えば、DRAM）に接続され、メインメモリからのデータへのアクセスは、プロセッサ内のレジスタファイル内のデータ及び/又はプロセッサにより近いハードウェアキャッシュ（例えば、L1キャッシュ、L2キャッシュ）内のデータへのアクセスよりも大幅に遅い（例えば、数十倍遅い）。メモリ又はその近くにさらなるプロセッサ（例えば、「インメモリプロセッサ（in-memory processor）」）を配置することで、外部バスを通過することによって惹起される遅延を回避することができ、これにより、高性能の計算が達成される。

#### 【0039】

本発明の実施形態の態様は、ALU等の計算回路（computational circuitry）をDRAMバンクと同じダイ上に配置する（例えば、それぞれのDRAMバンクのセンス増幅器又は行バッファに直接接続される）ことに関する。

#### 【0040】

DRAMモジュールの設計及び性能特性により、メモリ内のデータの特定の配列は、インメモリコンピューティングの性能に影響を与える。したがって、本発明の実施形態の一部の態様は、メモリモジュール（例えば、HBMメモリモジュール）のDRAMモジュール内にデータを配置するためのシステム及び方法に関し、ここでデータの配置は、IMCモジュールによって実行される計算の特性に基づいて制御される。

#### 【0041】

図1は、本発明の一実施形態によるメモリ（例えば、HBM）システムのアーキテクチャを示すブロック図である。

#### 【0042】

図1を参照すると、本発明の実施形態は、FIM（Function-In-Memory）メモリシステム100のためのシステムを提供する。メモリシステム100（又は、HBMシステム）は、メモリモジュール110（又は、HBMモジュール）に統合されるさらなる（additional）コンピューティングリソースをサポートする。例えば、様々な実施形態において、メモリシステム100は、一部のデータコンピューティング及び移動がメモリ内で実行されるようにし、且つ大容量メモリスクラッチパッド（high-capacity memory scratchpad）を提供する。メモリシステム100は、グラフィックス処理装置（GPU）又は中央処理装置（CPU）等のホストプロセッサ170に接続された少なくとも一つのメモリモジュール110を含む。様々な実施形態において、メモリモジュール110は、内部メモリバス130を介してメモリコントローラ140（例えば、ロジックダイ上）に接続された一つ以上のDRAMダイ120を含む。様々な実施形態において、ホストプロセッサ170は、メモリモジュール110とインターフェースするためのホストメモリコントローラ180（又は、ホストコントローラ）を含む。しかし、本発明の実施形態は、これに限定されるものではない。たとえば、ホストメモリコントローラ180は、ホストプロセッサ170から分離されてもよい（例えば、ホストプロセッサ170とは別のダイ又は同じダイとして）。

#### 【0043】

様々な実施形態によると、メモリコントローラ140は、ホストプロセッサ170からの命令の実行を調整するように構成される。命令は、通常の命令とFIM命令の両方を含む。例えば、通常の命令（例えば、メモリ内機能（function-in-memor

10

20

30

40

50

y ; F I M ) 命令ではなく、伝統的なロード及びストア機能 ) は、ホストメモリコントローラ 180 によって送信され、メモリコントローラ 140 によって受信されて、通常の方法で実行される。例えば、通常の命令は、外部バス 190 を介して受信したデータを D R A M ダイ 120 に格納する命令、及び D R A M ダイ 120 からデータを検索し、外部バス 190 を介してホストプロセッサ 170 にデータを送信する命令を含む。一部の実施形態において、通常の命令及び F I M 命令は、 D R A M ダイの特定の位置 ( 例えば、特定のバンクの特定のページ ) にデータを格納する動作を含む。これらのデータは 2 つの異なるオペランドを含み、ここで、それぞれのオペランドは複数の値 ( 例えば、浮動小数点又は整数値 ) を含み、以下でより詳細に説明するように、これらのオペランドの値は、様々なデータ配置戦略に従って、 D R A M ダイの異なる位置に分散して配置 ( d i s t r i b u t e ) される。 10

#### 【 0044 】

本発明の実施形態の態様は、 I M C ( i n - m e m o r y c o m p u t e ) の使用に関する。いくつかの比較 H B M システムは、 D R A M ダイ 120 の外部 ( 例えば、メモリコントローラ 140 に配置 ) にある A L U を含み、 A L U が外部バス 190 を通過することなく、 1 つ以上の D R A M ダイ 120 に格納されたデータに対する演算 ( o p e r a t i o n ) ( 例えば、算術演算 ( a r i t h m e t i c o p e r a t i o n s ) ) を実行できるように、 D R A M ダイ 120 のメモリバンクによって共有される。例えば、メモリコントローラ 140 は、 D R A M ダイ 120 の異なる部分の間でデータを移動又はコピーするために、データ移動演算 ( 例えば、ロード / ストアペア命令 ( l o a d / s t o r e p a i r i n s t r u c t i o n s ) ) を実行する。例えば、メモリコントローラは、 A L U を利用する計算 F I M 命令 ( 例えば、アトミック命令及び A L U 命令 ) の実行を調整することで、元々は複数の通常命令であった F I M 命令を実行する。別の例として、一部の場合、ホストプロセッサ 170 から受信した F I M 命令は、 I M C が統合されたメモリモジュールに、学習済みの機械学習モデル ( 例えば、ニューラルネットワーク ( n e u r a l n e t w o r k ) ) を使用して、ニューラルネットワークの訓練中に逆伝播 ( b a c k p r o p a g a t i o n ) を実行させるか、又は 2 つの行列を乗算するために、供給された入力に基づいて推論を計算する等の特定の計算を実行させる。このような場合、メモリコントローラ 140 は、受信したデータ ( 例えば、命令のオペランド ) を D R A M バンクの特定のページに格納し、 F I M 命令に関連するデータを格納する D R A M バンクに特定の A L U 演算を提供することによって、これらの命令の実行を調整する。メモリコントローラ 140 は、特定の F I M 命令を実行する際の計算性能を向上させる方法で、受信したデータ ( オペランド ) を D R A M バンクの特定のページに配置する。その結果は、 D R A M ダイ 120 に格納されるか、又は外部バス 190 を介してホストプロセッサ 170 に戻される。 20

#### 【 0045 】

本発明の実施形態の一部の態様は、 I M C モジュールを D R A M ダイ 120 のメモリバンクに統合することによってメモリ境界演算を加速することに關し、これにより、 D R A M ダイ 120 とメモリコントローラ 140 との間で内部メモリバス 130 を通過すること ( t r a v e r s a l ) を避ける。例えば、 I M C モジュールは、データを保持する D R A M バンクと同じ物理的半導体ダイ上にある。それぞれの D R A M バンクは、関連する I M C モジュールを有し、それによって、データが内部メモリバス 130 をメモリコントローラに通過することなく ( 例えば、 D R A M バンクからデータを送信することなく ) 、 D R A M バンクに格納されたデータに対して計算が実行できる。また、上記計算は、 D R A M バンクの I M C モジュール間で並列化 ( p a r a l l e l i z e d a c r o s s ) できる。 30

#### 【 0046 】

本発明の実施形態の態様は高帯域幅メモリに関して説明しているが、実施形態はこれに限定されず、他のタイプの D R A M システムにおいて、 D R A M ダイに I M C モジュールを統合することにも適用される。 50

## 【0047】

図2Aは、本発明の一実施形態による、埋め込み算術論理ユニット(embedded ALU)を有するメモリバンクの概略ブロック図である。図2Aに示すように、DRAMバンク200は、行及び列(又はページ及び列)に配列されたDRAMセル210のアレイを含む。図2Aに例示するように、DRAMバンク200は、n行(又はページ)及びm列に配列されたDRAMセル210を含む。複数のビットラインB1～Bmは列方向に沿って延在し、複数の行イネーブルライン(row enable lines)R1～Rnはアレイの行方向に沿って延在し、ビットラインと交差する。各ビットラインは、対応する列のすべてのセル(DRAMセル210)に接続される(例えば、アレイのi番目の列のすべてのセルは、ビットラインBiに接続される)。同様に、各行イネーブルラインR1～Rnは、対応する行の各DRAMセル210に接続される(例えば、アレイのj番目の行又はページのすべてのセルは、行イネーブルラインRjに接続される)。また、DRAMバンク200のDRAMセル210の行は、DRAMページと呼ばれる。

## 【0048】

図2Bは、本発明の一実施形態によるDRAMセルの例を示す回路図である。それぞれのDRAMセル210は、一般に、データ電圧を格納するためのコンデンサ212(例えば、ビット値、ここで各コンデンサは0ビットを表す電圧又は1ビットを表す電圧を格納する)と、コンデンサ212にデータ電圧を送信するためのスイッチ214とを含むものとしてモデル化される。図2Bに示す特定のDRAMセル210は、アレイのi番目の行及びj番目の列にある。したがって、図2Bに示すDRAMセル210のスイッチ214は、i番目のビットラインBiとコンデンサ212の一方の端子との間に接続され、コンデンサ212の他方の端子は接地に接続される。図2Bに示すように、DRAMセル210のスイッチ214のゲート電極は、j番目の行イネーブルラインRjに接続され、スイッチ214がオンになると、コンデンサ212がビットラインBiに接続される。

## 【0049】

図2Aを再び参照すると、DRAMバンク200は、行イネーブルラインR1～Rnに接続された行デコーダ220を含み、行デコーダ220は、例えば、メモリコントローラ140から供給される行アドレスに対応する行イネーブルラインの特定の一つに、行イネーブル信号を供給するように構成される。DRAMセル210のアレイの特定の行r(又はページ)にデータを書き込むか又は読み取る際、行デコーダ220は、特定の行(又はページ)に対応する行イネーブルラインに行イネーブル信号を供給する。データを書き込む際には、特定の行(又はページ)がイネーブルされている間、書き込まれるデータに対応する電圧がビットラインB1～Bmに供給される。同様に、DRAMセル210のアレイの特定の行(又はページ)からデータを読み取る際、コンデンサ212に格納された電圧に対応する電圧は、ビットラインB1～Bmに沿って送信され、センス増幅器232を含む入出力センス増幅器層230(又はIOSA)によって読み取られる。センス増幅器232の各センス増幅器は、ビットラインの内の対応する一つに接続される(例えば、センス増幅器232は、m個のセンス増幅器を含む)。例えば、一部の実施形態において、DRAMセル210のアレイは、8,192個の列、及び8,192個の対応するセンス増幅器232に接続された8,192個の対応するビットライン(例えば、ビットラインB1～B8192)を含む(例えば、各ページには8,192ビット又は8キロビットのデータを格納できる)。センス増幅器232は、「プリチャージ(precharge)」コマンドによって消去されるまで、現在の行(又はページ)から読み取られたデータを格納するので、センス増幅器232は「行バッファ(row buffer)」と呼ばれる。

## 【0050】

列デコーダ240は、マルチプレクサ234を使用してデータ列のーサブセット(subset)を選択するために使用され、読み取られたデータは、そのデータの計算を実行するために、グローバルIO層236を介してIMCモジュール250に供給される。例えば、一部の実施形態において、列デコーダ240及びマルチプレクサ234は、DRA

10

20

30

40

50

Mセル210の8, 192個の列から256ビット(256b)のデータの選択を可能にする。

#### 【0051】

センス増幅器232に現在格納されているページとは異なるDRAMバンク200のページからデータをロードする場合、「プリチャージ」(PRE)コマンドは現在のページを閉じ、次のアクセスのためにDRAMバンク200を準備するために使用される。次に、「活性化(activate)」(ACT)コマンドを使用して、DRAMバンクの特定の行又はページを開き、その開かれたページのデータをセンス増幅器232に格納する。その後、データがセンス増幅器232から読み取られて(READ)、IMCモジュール250に送信される。

10

#### 【0052】

一方、すでに関いているページからIMCモジュール250にデータをロードする場合には、例えば、列デコーダ240を使用してセンス増幅器232に既に格納されているデータの適切なサブセットを選択することにより(PRE及びACTコマンドは省略してもよい)、READコマンドでデータをロードするのに十分である。

#### 【0053】

様々な実施形態によれば、IMCモジュール250(又はALU&Reg)は、ALU252及び1つ以上のレジスタを含む。図2Aに示す実施形態において、IMCモジュール250は、オペランドレジスタ(Rop)254(又は入力バッファ)及び結果レジスタ(Rz)256を含む。マルチプレクサ257及び258は、(例えば、ALU252に対する第1のオペランド及び第2のオペランドとして)ALU252の2つの入力へのデータの流れを制御するために使用される。例えば、図2Aに示す実施形態において、オペランドレジスタ(Rop)254は、ALU252の第1のオペランド入力に接続され、第1のマルチプレクサ257は、センス増幅器232からグローバルIO層236を介して、又は入出力(IO)モジュール260(又は、書き込み入力/出力及び読み取り入力/出力、又はWIO及びRIO)を介して、外部ソース(例えば、ホストプロセッサ)からのデータを書き込むために、オペランドレジスタ(Rop)254に接続される。図2Aに示す実施形態のように、第2のマルチプレクサ258もまた、グローバルIO層236を介してセンス増幅器232から、又はIOモジュール260を介して外部ソースから、ALU252の第2のオペランド入力に直接データを供給するように構成される。ALU252は、その計算を結果レジスタ(Rz)256に出力し、データは、結果レジスタ(Rz)256からグローバルIO層236を介してDRAMセル210に書き戻されるか、又はIOモジュール260(又は、WIO及びRIO)を介してホストプロセッサ170に送信される。

20

#### 【0054】

一部の実施形態によると、ALU252は、様々な計算演算(例えば、簡単な計算コマンド)を実行するように構成される。例えば、ALU252は、算術演算、ビット単位(bitwise)、シフト演算(shift operations)等を実行するように構成された16ビットALU、32ビットALU、又は64ビットALUである。様々な実施形態において、ALU252は、整数演算(integer operations)、浮動小数点演算(floating point operations)、又はその両方を実行する回路を含む。例えば、ALU252は、ADD(+)、SUBTRACT(-)、MULTIPLY(×)、及びDIVIDE(÷)等の算術演算、AND(&)、OR(|)、XOR(^)、及びNOT(~)演算、並びにテンソル演算(tensor operations)等のビット演算を実行するように構成される。また、一部の実施形態において、ALU252は、单一命令、複数データ(SIMD)、又はデータのベクトルに対する演算を並列に実行するためのベクトル命令を実装する。本発明の実施形態によるALU252によって実装されるベクトル演算の例は、内積(')、外積(⊗)

30

40

50

、整流線形ユニット(ReLU)、平方(v<sub>s</sub>Sqr)、及び平方根(v<sub>s</sub>Sqr<sub>t</sub>)を含む。ALU252は、アトミック及び非アトミック演算に利用される。以下の表1は、本発明の一部の実施形態によるALU252によってサポートされる演算を挙げている。

### 【0055】

【表1】

| ID | 演算                                        | 説明                                   |

|----|-------------------------------------------|--------------------------------------|

| 0  | R <sub>o</sub> p=GIO                      | R <sub>o</sub> pに格納された列読み取りデータ       |

| 1  | R <sub>o</sub> p=WIO                      | R <sub>o</sub> pに格納された列書き込みデータ       |

| 2  | R <sub>o</sub> p=Rz                       | ALU出力RzをR <sub>o</sub> pにコピー         |

| 3  | GIO=Rz                                    | バンクに書き戻す                             |

| 4  | RIO=GIO                                   | DQ出力への通常の読み取り                        |

| 5  | RIO=Rz                                    | RzをDQ出力に駆動                           |

| 6  | Rz=R <sub>o</sub> p (o <sub>p</sub> ) GIO | R <sub>o</sub> p及びバンクからのデータを使用した演算   |

| 7  | Rz=R <sub>o</sub> p (o <sub>p</sub> ) WIO | R <sub>o</sub> p及びブロードキャストデータを使用した演算 |

| 8  | Rz=WIO (o <sub>p</sub> ) GIO              | ブロードキャストデータ及びバンクを使用した演算              |

| 9  | GIO=WIO                                   | DQ入力からの通常の書き込み                       |

10

20

### 【0056】

図2Cは、上述したDRAMセル210のアレイ、行デコーダ220、入出力センス増幅器層(IOSA)230、IMCモジュール(ALU&Reg)250、及び列デコーダ240を含む、本発明の一実施形態によるDRAMバンク200の概略図である。

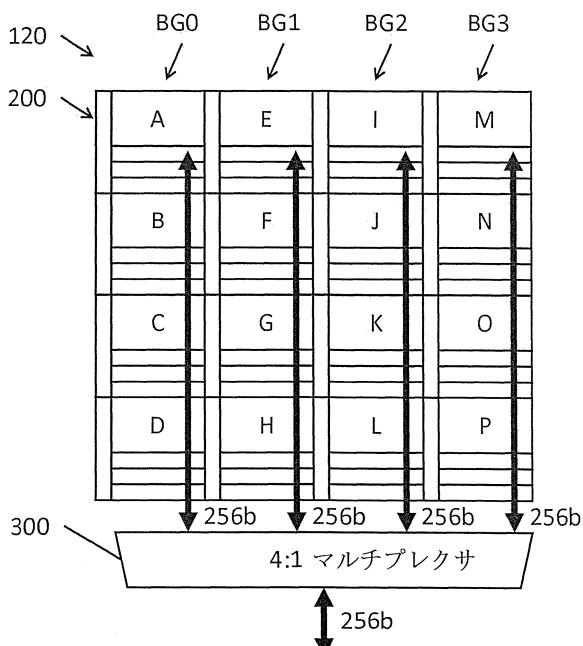

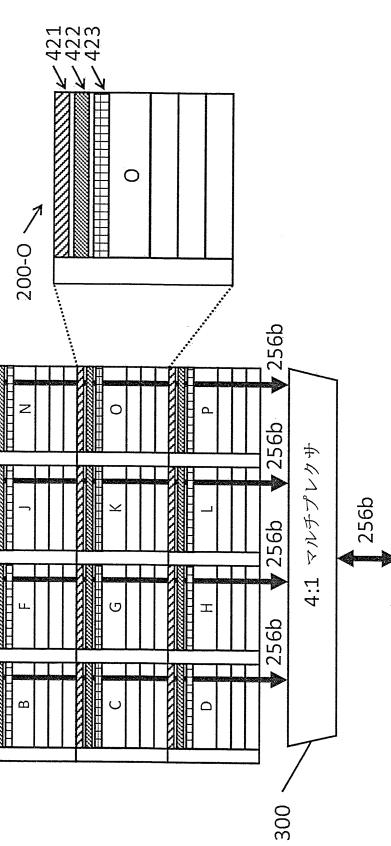

### 【0057】

図3は、本発明の一実施形態によるDRAMブロックのアレイを示す概略図である。図3に示す実施形態のように、16個のDRAMバンク200は、4×4アレイに配列され、DRAMバンクA～Pとしてラベル付けされ、BG0(DRAMバンクA、B、C、及びDを含む)、BG1(DRAMバンクE、F、G、及びHを含む)、BG2(DRAMバンクI、J、K、及びLを含む)、並びにBG3(DRAMバンクM、N、O、及びPを含む)としてラベル付けされた4つのバンクグループに配列される。図2Cに関して上述したように、図3に示す各DRAMバンク200は、DRAMダイ120内で(例えば、外部バスを通過することなく)計算を実行するためのIMCモジュール250を含む。また、図3に示すように、DRAMダイ120は、外部ソースからのデータを(例えば、DRAMダイ120を複数の他のスタック型DRAMダイ120及びメモリコントローラ140に接続するシリコン貫通電極又はTSVを介して)ブロックの4つの列に多重化するように構成されたマルチプレクサ300(例えば、4:1マルチプレクサ)をさらに含む。例えば、マルチプレクサ300は、すべてのDRAMバンク200に、256ビット(256b)データベクトルをブロードキャスト(broadcast)するか、又はDRAMバンク200の特定の列(BG0、BG1、BG2、又はBG3)にデータベクトルを供給するために使用される。

30

40

### 【0058】

DRAMダイ120に統合されたIMCモジュール250等のIMCを含むメモリシステム100は、演算を実行するために、データが外部バス(例えば、バス190)のボトルネックを通過する必要がないので、メモリ境界のホスト演算の性能を加速させる。ただし、IMCは、依然として、ALUパイプライン処理(pipelining)及びDRAMプロセスの形態のコンピューティングオーバーヘッド、並びにデータ配置及びDRAMタイミングの形態のメモリオーバーヘッドに遭遇する。

### 【0059】

したがって、本発明の実施形態の態様は、統合されたIMCモジュール250によって

50

インメモリコンピューティングを実行する際に、DRAMタイミングオーバーヘッドの影響を回避又は減少させるために、DRAM内にデータを配置するシステム及び方法に関する。本発明の実施形態の一部の態様は、改善された性能を達成するためのソフトウェア及びハードウェアの共同設計に関する。

【0060】

様々な実施形態において、メモリコントローラ140は、DRAMダイ120への演算及びDRAMダイ120からの演算を提供し、データの入力及び出力を管理する。したがって、本発明の実施形態の一部の態様は、ホストプロセッサ170によってメモリシステム100のメモリコントローラ140に提供された命令に従って、DRAMダイ120内にデータを配置するように構成されたメモリコントローラ140に関する。例えば、本発明の実施形態の一部の態様は、インメモリコンピューティングと、APIを使用してプログラムのソースコードをコンパイル又は解釈する際に、APIへの呼び出しに従ってデータを配置するようにメモリコントローラ140を制御するためのコマンドを生成するように構成されたコンパイラ（例えば、データコンパイラ）と、を有するHBMと相互作用するアプリケーション・プログラミング・インターフェース（API）を提供することに関する。例えば、APIは、GEMM（General Matrix-Matrix Multiplication）を実行するための関数呼び出し（function call）を提供し、コンパイラは、データに対して実行される演算（例えば、内積、外積、行列乗算など）を含む要素、及びデータのサイズ（例えば、データがメモリのページに適合するか否か）に基づくデータのナイーブな（naive）配置よりも性能が改善する方法で、オペランド行列を表すデータをDRAMダイ120に配置するようにメモリコントローラ140を制御するコマンドのシーケンスを生成する。APIを介してIMCでDRAMを使用するようにソフトウェアを作成する際に、本発明の一部の実施形態によるコンパイラ又はデータコンパイラは、DRAMダイ120の特定の位置にデータを配置し、DRAMダイ120の計算を実行するためのIMCモジュールを制御し、結果を格納するために、ソフトウェアのソースコードの少なくとも一部をメモリコントローラ140によって実行されるコマンドに変換する。

【0061】

一実施形態によると、16レーン（lane）のALUは、半精度浮動小数点（half-precision floating-point）（FP-16）計算で8GFLOPS（ギガ浮動小数点演算/秒）のピーク性能を達成する。（本発明の実施形態によるIMCモジュールの性能をFLOPSに関して本明細書に説明しているが、本発明の実施形態は、浮動小数点演算を実行することに限定されず、様々なデータレイアウトの相対的な性能は、例えば、整数演算の実行する際と似ている。）したがって、第2世代高帯域幅メモリ標準（HBM2）を使用する4つのダイ（4H又は4-Hi）のスタックを使用する、本発明の一実施形態によるIMCの実装は、FP-16計算（ダイあたり256バンク×4ダイのスタック=1,024バンク、各バンクは対応する16レーンのALUを有する）で8TFLOPS（テラ浮動小数点演算/秒）を達成する。

【0062】

TFLOPSで測定されるピーク計算性能は、異なるデータレイアウトシナリオの下で変わる。

一番目の場合（2OPと表記）、メモリモジュール110の外部からの2つのオペランドがインメモリコンピューティングALUに完全に供給され、その結果はバッファリングされて（buffered）完全に累積され、これにより、上述の8TFLOPSのピーク計算性能が得られる。

【0063】

二番目の場合（1OPと表記）、第1のオペランドはHMBの外部からIMCに完全に供給されるが、第2のオペランドはDRAMダイ120の任意の位置から読み取られる。これは、約6.5TFLOPSにピーク計算性能を低下させる。

【0064】

10

20

30

40

50

三番目の場合（DRと表記）、双方のオペランドはDRAMの異なるページに配置され、結果がDRAMに書き戻される。このシナリオでは、約0.8TFLOPSが測定された計算性能である（例えば、2OPの場合よりも1桁遅い）。

#### 【0065】

四番目の場合（SRと表記）で、双方のオペランドはDRAMブロックの同じ行又はページに位置する。これはDRの場合よりも性能が大幅に向上し、約3.3TFLOPSになる。

#### 【0066】

したがって、データの考慮に基づいて、様々なデータレイアウトのトレードオフが行われる。例えば、1OPの場合、第1のオペランドがDRAMにあり、第2のオペランドがHBMの外部からブロードキャストされると、性能が高くなる（上記のように約6.5TFLOPS）が、ホストプロセッサ170にオーバーヘッドが発生し、第2のオペランドをHBMに提供しなければならない。

10

#### 【0067】

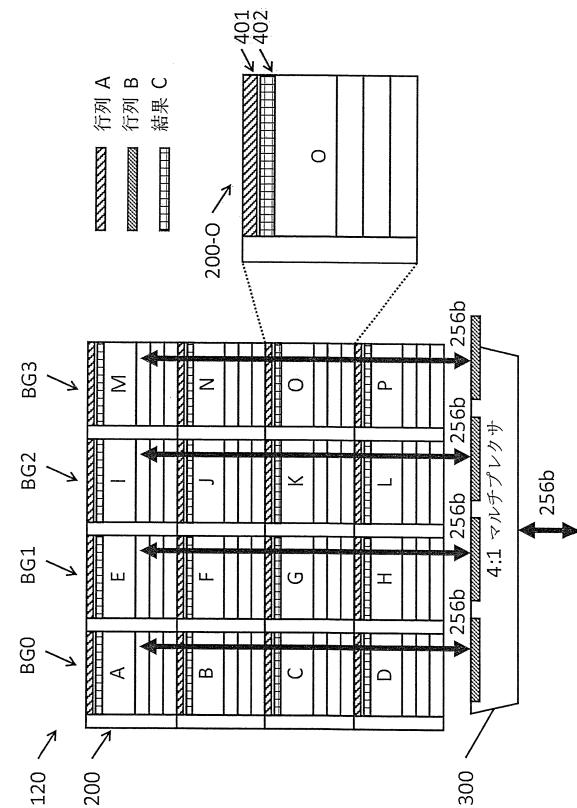

図4Aは、第1のオペランド（行列A）がDRAMに格納され、第2のオペランド（行列B）がメモリモジュールの外部からブロードキャストされる場合のGEMMに対するデータの配置を、本発明の一実施形態による統合されたIMCと共に概略的に示す図である。例示のために、DRAMバンク200-Oをより詳細に示している。図4Aに示すように、第1のオペランド行列Aに関連するデータは、DRAMバンク200-Oの一つのページ401（例えば、第1の行又は第1のページ）に配置され、第2のオペランド行列Bに関連するデータは、（例えば、マルチブレクサ300を介して）DRAMダイ120の外部からブロードキャストされる。計算結果Cは、DRAMバンク200-Oの異なるページ402に配置される。

20

#### 【0068】

双方のオペランドがDRAM内にある場合、双方のオペランドを同じページ又は同じ行（SR）に配置することは、以下で詳細に説明するように、実行する必要があるPRE及びACT演算の数を部分的に減らすことによって、計算性能を向上させる（例えば、約3.3TFLOPS）が、DRAMの正しい部分にデータを配置することに関してより多くの制約を課す。

30

#### 【0069】

図4Bは、双方のオペランド（行列A及び行列B）が、メモリモジュールのDRAMの同じページに格納されている場合のGEMMに対するデータの配置を、本発明の一実施形態による統合されたIMCと共に概略的に示す図である。例示のために、DRAMバンク200-Oをより詳細に示している。図4Bに示すように、第1のオペランド行列A及び第2のオペランドの行列Bに関連するデータは、DRAMバンク200-Oのページ411（例えば、第1の行又は第1のページ）に配置される。より詳細には、ページ411の前半部は第1のオペランド行列Aからのデータで満たされ、ページ411の後半部は第2のオペランド行列Bからのデータで満たされる。行列A及び行列Bが図4Aに関して上述したものと同じサイズと仮定すると、残りのデータを格納するためにさらにページが必要になる。このように、第1のオペランド行列A及び第2のオペランドの行列Bの双方に関連するデータもページ412に配置される。行列乗算の結果Cは、DRAMバンク200のページ413に格納される。

40

#### 【0070】

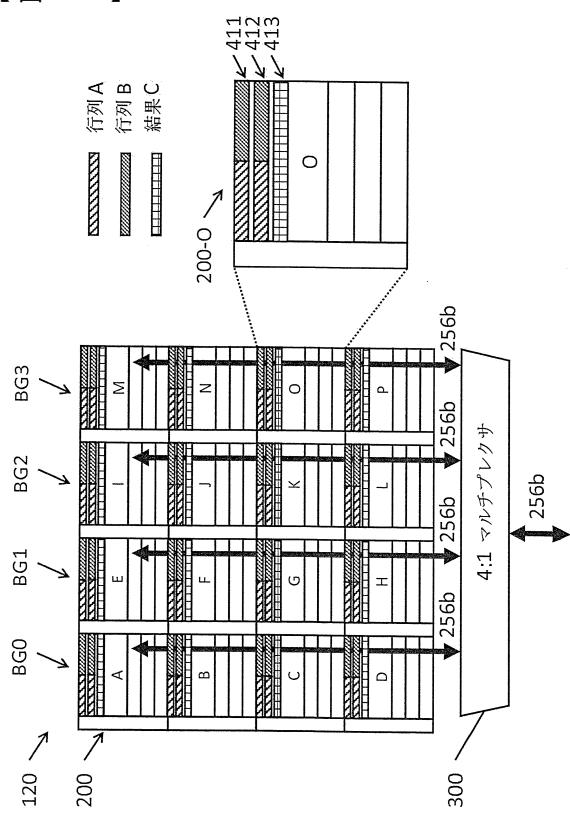

一方、オペランドを異なるページに配置することは、より柔軟で、レイアウトに対する制約を減らす（例えば、固定サイズのメモリのページにきちんと適合しないサイズを有するデータに適合する）が、一般に計算性能が低下する。

#### 【0071】

図4Cは、双方のオペランド（行列A及び行列B）が、メモリモジュールのDRAMの異なるページに格納されている場合のGEMMに対するデータの配置を、本発明の一実施形態による統合されたIMCと共に概略的に示す図である。例示のために、DRAMバン

50

ク 2 0 0 - 0 をより詳細に示している。図 4 C に示すように、第 1 のオペランド行列 A に関連するデータは、ページ 4 2 1 に配置され、第 2 のオペランド行列 B に関連するデータは、ページ 4 2 2 に配置され、結果 C はページ 4 2 3 に配置される。

#### 【 0 0 7 2 】

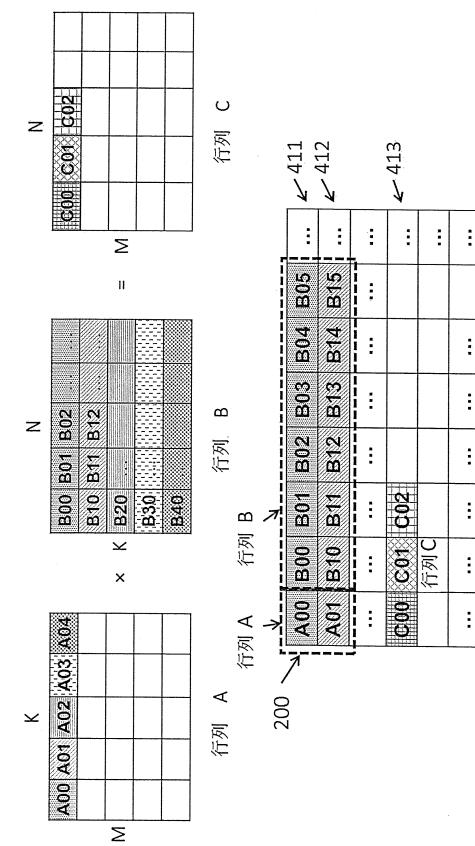

図 4 A、図 4 B、及び図 4 C に示す異なるデータ配置戦略 ( 1 O P 、 S R 、及び D R ) の様々な性能への影響は、以下の図 5 A、図 5 B、図 6 A、図 6 B、図 7 A、及び図 7 B を参照して、より詳細に説明する。例えば、図 5 A に示すように、行列 A は  $M \times K$  行列であり、行列 B は  $K \times N$  行列であるので、行列 A と行列 B の積である行列 C のサイズは、 $M \times N$  である。説明のために、以下の例では  $K = 5$  の場合を説明しているが、本発明の実施形態はそれに限定されない。標準行列乗算に従って、結果行列 C の左上の値  $C_{00}$  は、行列 A ( 各位置  $A_{i,j}$  は、例えば 16 個の半精度浮動小数点値のベクトル又は「タイル」を水平順に示し、図 5 A、図 5 B、図 6 A、図 6 B、図 7 A、及び図 7 B は、 $A_{00}$ 、 $A_{01}$ 、 $A_{02}$ 、 $A_{03}$ 、及び  $A_{04}$  を示す ) の第 1 の行に、行列 B ( 各位置  $B_{i,j}$  は、例えば、16 個の半精度浮動小数点値のベクトル又は「タイル」を垂直順に示す ) の第 1 の列をペアとして乗算して計算される。つまり、 $C_{00}$  は  $A_{00} \cdot B_{00} + A_{01} \cdot B_{10} + A_{02} \cdot B_{20} + A_{03} \cdot B_{30} + A_{04} \cdot B_{40}$  を格納する。図 5 A、図 5 B、図 6 A、図 6 B、図 7 A、及び図 7 B において、シェーディング ( shading ) 処理は共に乗算されるオペランドを識別するために使用する。より詳細には、同じパターンを使用してシェーディング処理された 2 つのオペランドが、図示する計算の一部として共に乗算される。本発明の実施形態の様子は、浮動小数点オペランドに対して浮動小数点演算を実行するように構成された I M C について説明しているが、本発明の実施形態はそれに限定されず、例えば、整数オペランドに対する整数演算を実行するように構成された I M C に適用してもよい。

#### 【 0 0 7 3 】

図 5 A は、一つのオペランド ( 1 O P ) データレイアウトにおける行列 A の第 1 の行と行列 B の第 1 の列との乗算の概略図である。ここで、本発明の一実施形態による一つのオペランドが外部から供給され、一つのオペランドがインメモリコンピューティングで D R A M バンクに格納される。図 5 A に示すように、行列 A の第 1 の行のタイル  $A_{00}$ 、 $A_{01}$ 、 $A_{02}$ 、 $A_{03}$ 、及び  $A_{04}$  は、D R A M バンク 2 0 0 の同じページ 4 0 1 ( 行 ) に格納され、行列 B のベクトル又はタイル  $B_{00}$ 、 $B_{10}$ 、 $B_{20}$ 、 $B_{30}$ 、及び  $B_{40}$  は、外部から供給され、結果 ( 例えば、 $C_{00}$  ) は、D R A M バンク 2 0 0 の別のページ 4 0 2 に格納される。

#### 【 0 0 7 4 】

乗算を計算するプロセスは、D R A M バンク 2 0 0 から値  $A_{00}$  を読み取り、 $A_{00} \cdot B_{00}$  を計算することによって開始する。これには、ページ 4 0 1 を開くことが含まれ、したがって、センス増幅器 2 3 2 を準備するためにプリチャージ ( P R E ) コマンドが必要となり、その後にページ 4 0 1 をセンス増幅器 2 3 2 にロードするための活性化 ( A C T ) コマンド、及びセンス増幅器 2 3 2 から I M C モジュール 2 5 0 に  $A_{00}$  の値をロードするための読み取り ( R E A D ) コマンドが続く。上述のように、 $B_{00}$  は外部から入力として提供されるため、この値の取得に D R A M 演算は必要でない。A L U 2 5 2 は、その後、乗算  $A_{00} \cdot B_{00}$  を計算し、出力バッファ ( 例えば、出力レジスタ R z ) に一時的な結果を格納する。

#### 【 0 0 7 5 】

次に、A L U 2 5 2 は、D R A M から  $A_{01}$  を読み取ることによって乗算  $A_{01} \cdot B_{10}$  を計算する。これはまた、P R E コマンド、A C T コマンド、及び R E A D コマンドが必要である。ベクトル又はタイル  $B_{10}$  は、外部から入力として提供されるため、 $A_{01} \cdot B_{10}$  が計算され、 $A_{00} \cdot B_{00}$  を格納するバッファ ( 例えば、出力レジスタ R z ) の一時的な結果に追加される。このプロセスは、行列 A 及び行列 B の残りの値に対して繰り返される。その結果、それぞれの計算 ( 例えば、タイル  $A_{00}$  及び  $B_{00}$  等の 2 つのオペランドの乗算 ) は、計算ごとに 1 つの P R E 、 1 つの A C T 、及び 1 つの R E A D を必

10

20

30

40

50

要とする。図 8 に関して以下でより詳細に説明するように、一部の実施形態では、IMC は値を格納し、先に格納された値と新たに受信した値の合計 (sum) で格納された値を更新するように構成されるアキュムレータをさらに含む。

#### 【0076】

図 5 B は、1OP データレイアウトにおける行列 A の第 1 の行の第 1 の値と行列 B の各列の第 1 の値との積をデータ再利用と共に示した概略図である。ここで、本明細書の一実施形態によれば、一つのオペラントが外部から供給され、1 つのオペラントがインメモリコンピューティングでDRAM バンクに格納される。図 5 B は、図 5 A に示すものとは異なり、DRAM からロードされたデータは、行列 B の異なる列に対して再利用される（例えば、オペランドレジスタ (Rop) 254 に格納される）。特に、2 つの行列を乗算する際に、行列 A のすべての行の j 番目の要素は、行列 B の j 番目の行のすべての要素と乗算される。したがって、行列 A の各要素を一度ロードし、それを行列 B のすべての列 (N 列) に乗算することにより、DRAM バンク 200 からのデータロードのコストは、N 列にわたって償却 (amortized) される。より詳細には、行列 A 及び行列 B を乗算する場合、従来どおり、タイル A00 は、PRE コマンド、ACT コマンド、及び READ コマンドを使用してDRAM バンク 200 から読み取られ、タイル B00 は、外部から入力として受信される。ALU252 は、C00 の合計の一部を計算するために A00 · B00 を計算する。しかし、DRAM からタイル A01 をロードする代わりに（例えば、別の PRE、ACT、及び READ シーケンスを使用）、C01 に対して計算する乗算の内の一つである A00 · B01 を計算するために、タイル A00 を再利用して（外部から受信された）B01 を乗算する。その結果、各計算には、1/N PRE、1/N ACT が必要であり、計算ごとに 1 つの READ が必要である（行列 A の別の部分をロードするための PRE 及び ACT コマンドが、行列 B の N 列に対して償却されるため）。

10

20

30

40

#### 【0077】

図 6 A は、同じ行 (SR) データレイアウトにおける行列 A の第 1 の行と行列 B の第 1 の列との乗算の概略図である。ここで、本発明の一実施形態によれば、双方のオペラントは、インメモリコンピューティングを有するDRAM バンクの同じページに格納される。図 6 A に示すように、行列 A の第 1 の行のタイル A00、A01、及び A02、並びに行列 B の第 1 の行のタイル B00、B10、及び B20 は、DRAM バンク 200 の同じページ 411 に格納され、行列 A のタイル A03 及び A04、並びに行列 B のタイル B30 及び B40 は、DRAM バンク 200 のページ 412 に格納される。その結果（例えば、C00）は、DRAM バンク 200 のページ 413 に格納される。

#### 【0078】

結果（例えば、内積）を計算するプロセスは、DRAM バンク 200 からタイル A00 を読み取り、A00 · B00 を計算することによって開始する。これには、ページ 411 を開くことが含まれ、したがって、プリチャージ (PRE) コマンドが必要となり、その後に活性化 (ACT) コマンド、及びセンス増幅器 232 から IMC モジュール 250 にタイル A00 をロードするための読み取り (READ) コマンドが続く。タイル B00 は DRAM から読み取る。しかし、タイル B00 が A00 と同じページ 411 にあり、その値は既にセンス増幅器 232 に格納されているので、READ コマンドで十分である（タイル B00 を IMC モジュール 250 に読み取るために、さらに PRE 及び ACT を実行する必要はない）。したがって、タイル A00 及び B00 が読み取られると、ALU252 は A00 · B00 を計算し、一時的な結果をバッファに格納する。同様に、タイル A01 とタイル B10 は、いずれもページ 411 にあり、したがって、ページ 411 が A00 を読み取るために最初に開かれた際に、センス増幅器 232 に予め格納されているため、PRE と ACT なしで A01 · B10 を計算するためのタイル A01 及び B10 の読み取りも同様に、READ コマンドを使用して実行する。そのため、各計算は、計算ごとに 1/r PRE、1/r ACT、及び 2 READ 演算を実行する。ここで、r は、DRAM バンク 200 の同じページに格納されている一致する値のペアの数である。例えば、上述のように、図 6 A は、行列 A の第 1 の行のタイル A00、A01、及び A02 と、行列 B

50

の第1の行のタイルB 0 0、B 1 0、及びB 2 0とが、DRAMバンクのページ4 1 1に格納される場合を示す。したがって、計算A 0 0・B 0 0、A 0 1・B 1 0、及びA 0 2・B 2 0は、ページ4 1 1に3組のタイル（例えば、 $r = 3$ ）が含まれているため、それぞれ1/3 PRE、1/3 ACT、及び2 READコマンドを償却する。A 0 3・B 3 0及びA 0 4・B 4 0を計算する際、ページ4 1 2に2組の値（例えば、 $r = 2$ ）が含まれているため、このような計算は、それぞれ1/2 PRE、1/2 ACT、及び2 READコマンドをそれぞれ償却する。計算ごとに必要なPRE及びACTコマンドの数が減ることにより、全体の計算性能が向上する。

#### 【0079】

図6Bは、SRデータレイアウトにおける行列Aの第1の行の第1の値と行列Bの各列の第1の値に対するデータの再利用による乗算の概略図である。ここで、本発明の一実施形態による双方のオペランドは、インメモリコンピューティングを有するDRAMバンクの同じページに格納される。図5A及び図5Bの配列間の比較と同様の方法で、図6Bに示す計算プロセスは、DRAMからロードされた値が再利用されるという点で図6Aに示すものと異なる。より詳細には、行列の乗算は、第1のオペランドの指定された行の $i$ 番目の要素と第2のオペランドの各列の $i$ 番目の要素との乗算を含むということに基づいて、行列Aと行列Bの要素は、指定された行列Aの行の各要素のデータが、乗算される行列Bの行の値と同じページに配置されるように、DRAMバンク200に配列される。

#### 【0080】

例えば、図6Bに示すように、行列Aに行列Bを乗算すると、行列AのタイルA 0 0は、結果行列Cの第1の行の一部（例えば、C 0 0、C 0 1、C 0 2、C 0 3、C 0 4、C 0 5等の項のいずれか）を計算するプロセスにおいて、行列Bのすべての列の第1のタイル（行列Bの第1の行のすべての要素、例えば、B 0 0、B 0 1、B 0 2、B 0 3、B 0 4、B 0 5、...）に乗算される。同様に、行列Aの値A 0 1に行列Bのすべての列の第2のタイルが乗算される（図6Bに示すように、行列Bの第2の行のすべての要素、例えば、B 1 0、B 1 1、B 1 2、B 1 3、B 1 4、B 1 5、...）。

#### 【0081】

このように、行列Aの少なくとも一つの値は、行列Bの対応値と同じページに格納される。図6Bに示す特定の例において、ページ4 1 1は、行列AからタイルA 0 0、行列BからタイルB 0 0、B 0 1、B 0 2、B 0 3、B 0 4、B 0 5、...を格納し、ページ4 1 2は、行列AからタイルA 0 1、行列BからタイルB 1 0、B 1 1、B 1 2、B 1 3、B 1 4、B 1 5、...を格納する。DRAM内のデータのこのような配列により、DRAMのページが少なくとも $N + 1$ エントリを格納すると仮定すると、各計算は、1/N PREコマンド、1/N ACTコマンド、及び( $N + 1$ )/N READコマンド（PREコマンド及びACTコマンドは、行列BのN列で償却されるため）を実行する。

#### 【0082】

図7Aは、異なる行(DR)データレイアウトにおける行列Aの第1の行と行列Bの第1の列との乗算の概略図である。ここで、オペランドは、本発明の一実施形態によるインメモリコンピューティングでDRAMバンクの異なるページに格納される。図7Aに示すように、行列Aの第1の行のタイルA 0 0、A 0 1、A 0 2、A 0 3、及びA 0 4は、ページ4 2 1に格納される一方、行列Bの第1の列のタイルB 0 0、B 1 0、B 2 0、B 3 0、及びB 4 0は、別のページ4 2 2に格納される。

#### 【0083】

タイルB 0 0がタイルA 0 0とは異なるページ4 2 2（行）にあるため、C 0 0を計算するプロセスは、PRE、ACT、及びREADコマンドのシーケンスを使用して、タイルB 0 0を読み取り、その後に、PRE、ACT、及びREADコマンドのシーケンスを使用して、DRAMバンク200のページ4 2 1（行）からA 0 0を読み取ることによって、A 0 0・B 0 0を計算することから始まる。ALU252は、A 0 0・B 0 0を計算し、その結果を一時的なバッファに格納する。C 0 0計算を継続するために、タイルA 0 1は、ページ4 2 1（行）から読み取られ、ページ4 2 2（行）からB 1 0が読み取られ

10

20

30

40

50

、ここで、それぞれの値は、DRAMバンク200に対するPRE、ACT、及びREADシーケンスの実行を含む。

【0084】

図7Bは、DRデータレイアウトにおける行列Bの各列の第1の値と行列Aの第1の行の第2の値とにより、行列Bの各列の第2の値による行列Aの第1の行の第1の値のデータ再利用による乗算の概略図である。ここで、オペランドは、本発明の一実施例によるインメモリコンピューティングでDRAMバンクの異なるページに格納される。

【0085】

図5Bにおける説明及びTOPにおけるデータ再利用と同様の方法により、行列Bで乗算を実行する際に行列Aから取り出したデータを再利用することで、メモリ演算の数が減る。図7Aにおける説明のように、指定された行列Aの行の各i番目の値は、行列Bのi番目の行の各値と乗算される。したがって、指定された行列Bの行のすべての値がDRAMバンク200の同じページに格納されると、PRE及びACTコマンドの数が減少し、それによって性能が向上する。

【0086】

例えば、行列Aに行列Bを乗算するプロセスは、N個の部分和（例えば、C00、C01、C02、...、C0Nの一部）を計算するために、行列AのタイルA00に行列Bの第1の行のN個のタイル（B00、B01、B02、...、B0N）のそれぞれを乗算することから始まる。このプロセスは、DRAMバンク200からタイルA00をロードすることにより始まる。これには、ページ421（行）を開き、行列AのタイルA00をオペランドレジスタ（Rop）254にロードするため、PREコマンド、ACTコマンド、及びREADコマンドが含まれる。A00をロードした後、行列Bの第1の行のタイルB00、B01、B02、...、B0NがタイルA00に乗算されるようロードされる。図7Bに示すように、行列Bのこれらの値がすべて同じページにある場合（例えば、B00、B01、B02、B03、B04、...は、図7Bに示すDRAMバンク200のページ422にある）、このページにアクセスするために使用されたPRE及びACTコマンドが、そのページに格納されたN個の値で償却される。したがって、行列Aの一つの値に行列Bの一つの行のすべての値を乗算するには、2つのPREコマンド、2つのACTコマンド、及びN+1 READコマンドが必要となり、行のN個の値を償却すると、計算ごとに2/N PREコマンド、2/N ACTコマンド、及び(N+1)/N READコマンドが生成される。上述の例と同様の方法で、DRAMコマンドの数の減少は、全体の計算性能（例えば、行列乗算演算）を向上させる。

【0087】

上述のデータ配置オプションは、サイクルレベル（cycle-level）の高帯域幅メモリ-メモリ内機能（HBM-FIM）シミュレータを使用して実験的にテストし、これはGEMM記録と共にIMC用にカスタマイズされた。実験アーキテクチャには4つの4H HBM2モジュールを含むHBMが含まれており、ここでDRAMのアレイサイズは16,384(16Kib)行×8,192(8Kib)列（例えば、各ページのサイズは8,192b）であり、行バッファのサイズは、8,192ビット(8Kib)である。IMCモジュールは、待ち時間周期を備えた16レーンのFP-16ベクトルユニットと768ビットバッファを含み、パイプライン動作が可能であった。様々な実施形態において、バッファはより小さくてもよく（例えば、256ビットの入力バッファ及び256ビットの出力バッファを含む512ビットのバッファ）、又はより大きくてもよい（例えば、256ビットの入力バッファ及び1,024ビットの出力バッファを備えた1,280ビットのバッファ）。一部の実施形態において、入力バッファは、256ビットよりも大きい（例えば、512ビット）。

【0088】

本発明の実施形態の一部の態様は、DRAMバンク200のレベルでさらなるバッファ及びアキュムレータ（例えば、DRAMバンクでバンクごとに提供されるさらなるハードウェア）を含むことに関する。

10

20

30

40

50

## 【0089】

図8は、DRAMバンクのIMCモジュールの概略ブロック図である。ここで、IMCモジュールは、本発明の一実施形態による結果バッファ、アキュムレータ、及びバッファにさらに接続される。

## 【0090】

図8に示すように、ALU252は、入力オペランドA(図8では256ビットのオペランドA[0:255]と表示)及び入力オペランドB(図8では256ビットのオペランドB[0:255]と表示)を受信する。ALUは、2つの入力オペランド(例えば、加算、乗算、内積、外積など)に対する演算を実行し、結果C(図8では256ビットの結果C[0:255]と表示)を計算する。

10

## 【0091】

図8を参照すると、IMCモジュール250は、ALU252の出力に接続されたアキュムレータ802をさらに含む。例えば、ALU252の出力は、結果レジスタ(Rz)256及びアキュムレータ802の双方に接続され、結果Cが結果レジスタ(Rz)256に格納され、アキュムレータ802に供給される。アキュムレータ802は、累積値(例えば、256ビット値)を格納するアキュムレタレジスタを含む。アキュムレータ802がALU252から新たな結果を受信すると、新たな結果は、アキュムレタレジスタに既に格納されている累積値に追加(例えば、累算)される(例えば、アキュムレータ802のアキュムレタレジスタに格納されている値が更新されるか、又は新たな結果と先にアキュムレータ802に格納されている値の合計として設定される)。一部の実施形態において、アキュムレータ802は、リセットコマンドに応答して、アキュムレタレジスタをリセットする(例えば、アキュムレタレジスタに格納された累積値をゼロに設定する)ように構成される。アキュムレータ802は、行列の乗算を計算する場合(例えば、結果行列の各値が第1のオペランドの行と第2のオペランドの列の内積である場合)等、内積(inner products又はdot products)の計算の際に特に役立つ。図8に示す実施形態において、IMCモジュール250は、512ビットの第1のバッファ812及び512ビットの第2のバッファ814として示される1,024ビットの出力バッファをさらに含む。多数の結果値を格納するさらに大きな出力バッファは、メモリコントローラ140がDRAMバンクの別のページを開いてその結果を格納する前に、一度に多数の結果を計算するために、DRAMバンクを制御できるようにする。例えば、図6Bに示すようにSREデータレイアウトでデータを再利用する場合、結果を格納するためにページを開くには、PRE及びACTコマンドをさらに必要とするオペランドを格納するページ(例えば、図6A及び図6Bに示すページ411)とは異なるDRAMバンク200の別のページ(例えば、図6A及び図6Bに示すページ413)に書き込まれた部分和を計算するために、第1のオペランド行列Aの一つの値に、第2のオペランド行列Bの行に対応する異なる値を乗算する。しかし、出力バッファが大きいほど、演算を完了するのに必要なページ切り替え量が減り(各ページの切り替えにはPRE及びACTが必要なため)、そのため、計算性能が向上する。図8は、アキュムレータ802及びより大きな出力バッファ(812、814)の双方を有するIMCモジュール250を示すが、本発明の実施形態はそれに限定されず、IMCモジュール250がさらなる出力バッファ812及び814なしでアキュムレータ802を含む実施形態、並びにIMCモジュール250がアキュムレータ802なしでさらなる出力バッファ812及び814を含む実施形態を含む。本発明の一部の実施形態において、IMCモジュール250は、(例えば、多数の値が同時に蓄積されるように)並列に配列された多数のアキュムレータ802を含む。本発明の実施形態はさらに、2つの512ビットの出力バッファ812及び814を有する場合に限定されず、512ビットよりも大きいか又は小さい、及び/又は2つ以上の出力バッファ又は2つ未満の出力バッファを含む。IMCモジュール250の様々な部分は、異なる量の待ち時間を持つ。例えば、乗算演算を実行するALU252が4サイクルの待ち時間を導入し、累積演算は1サイクルの待ち時間を含む。

20

## 【0092】

30

40

40

50

本発明の実施形態の態様は、G E M Mを実装することに関して、以下でより詳細に説明する。

#### 【 0 0 9 3 】

図9は、本発明の一部の実施形態による、同じ行(S R)レイアウトを使用する計算を説明するためのG E M Mの一例の概略図である。より具体的には、図9は、行列A及び行列Bの積を示し、行列A及び行列Bの積をアキュムレータ802に現在格納されている値に追加することにより、アキュムレータ(例えば、アキュムレータ802)に格納された結果Cを更新することを示す(結果C+ = 行列A × 行列B)。図9に示す計算では、行列Aの16タイルと行列Bの16タイルが共に乗算され、ここで、各タイルは、16個のF P - 16要素(256ビット)を有する。特定の内部タイルの構成レイアウトは、以下でより詳細に説明するが、G E M Mの全体的な複雑さ(complexity)は、別のレイアウトでも同様である。図9に示すように、同様のパターンでシェーディング処理されたタイルは、共に乗算されたタイルである。上述のように、図9は、同じ行(S R)データレイアウトを示し、ここで、行列A及び行列Bの32個の値すべてが、D R A Mバンク200の同じページ414に格納され、各計算のオペランド(例えば、タイルA00、並びにタイルB00、B01、B02、及びB03)は、すべて同じページ414に格納される。個々の計算の結果は、結果レジスタ(R z)256に蓄積され、結果Cを計算する。

10

#### 【 0 0 9 4 】

タイル - レベル(tile-level)乗算の一つの特定例として、D R A Mバンク200の同じページからロードされた2つのタイルA00及びB00の内積(inner products又はdot products)を計算する際、タイルA00は、行列Bの点線タイルB00である。一部の実施形態において、上述のように、各タイルは、16個のF P - 16要素を含む。例えば、タイルA00は要素a00、a01、...、a15を含み、タイルB00は要素b00、b01、...、b15を含み、タイルA00及びB00の内積は積のペアの合計(= a00 × b00 + a01 × b01 + ... + a15 × b15)である。したがって、2つのタイルの内積(inner products又はdot products)は、単一の要素又は単一の値を生成することから、本発明の実施形態によるI M Cモジュールは、結果を格納するために、より少ないバッファレジスタ(例えば、アキュムレータレジスタ802)で内積を計算する。そのため、アキュムレータレジスタを含む本発明の一部の実施形態によるI M Cモジュールは、内積の計算等、値の累算を含む計算を実行するのに非常に適している。一部の実施形態において、内積の計算に適したアキュムレータを含むI M Cモジュールは、学習済みのニューラルネットワークを使用して推論(又は順方向伝搬)を実行するために使用され、学習済みのニューラルネットワークで第1のオペランドが入力(例えば、以前の層からの活性化)を示し、第2のオペランドは、学習済みのニューラルネットワークの層のニューロンに関連する重みを示す。

20

#### 【 0 0 9 5 】

タイル - レベル乗算の別の例として、D R A Mバンク200の同じページからロードされた2つのタイルの外積を計算する場合、第1のタイルのすべての値は、第2のタイルのすべての値に乗算され、2つのタイルを同時にロードする。例えば、上述のように、各タイルが16個の値を含む場合、2つのタイルの外積は $16 \times 16 = 256$ の出力値を有する。ツリー - 加算器(tree-adder)の累積が不要であり、256個の出力値を並列に計算するため、外積は内積よりも簡単なハードウェアで計算することができる。しかし、外積の計算には、(例えば、外積の結果のすべての値を格納するために)本発明の実施形態によるI M Cモジュール250において多くの出力バッファレジスタ(例えば、出力バッファ812及び814)を必要とする。例えば、各タイルが最大16個のF P - 16値を含むと仮定すると、外積を計算するように構成されたI M Cモジュール250は、256個の値を格納するのに十分な大きさの出力バッファ(例えば、 $256 \times 16$ ビット = 4,096ビットのバッファ)を含む。したがって、出力バッファを含む本発明の一部の実施形態によるI M Cモジュールは、第1および第2のオペランド(上記の例では、

30

40

50

オペランドの各タイルは 16 個の値を含むため、出力バッファには少なくとも 256 個の値が格納される) のタイル内の値の数の積以上のサイズを格納する大きさを有するオペランドの外積を含む計算を実行するのに適する。

【 0096 】

タイル - レベル乗算の第 3 の例として、DRAM バンク 200 の同じページからロードされた 2 つのタイルのテンソル積を計算する場合、2 つのタイルは、行列に配列された値を含む。例えば、各タイルが 16 個の FP - 16 値を含む場合、各タイルは、4 × 4 行列値に配列される。このタイルのテンソル積を計算すると、4 × 4 の結果行列が生成される。例えば、各タイルが最大 16 個の FP - 16 値を含むと仮定すると、16 値の内の 2 つの 4 × 4 タイルのテンソル積を計算するように構成された IMC モジュール 250 は、16 個の値を格納するのに十分な大きさの出力バッファ ( 例えば、16 × 16 ビット = 256 ビットのバッファ ) を有する。したがって、本発明の実施形態による IMC モジュールは、第 1 および第 2 のオペランドの内の大きい方の値の数と同じ値の数を格納するのに十分な大きさの出力バッファを含む計算 ( オペランドのテンソル積を含む ) を実行するのに適する。本発明の実施形態によるテンソル積を実装する IMC モジュールは、内積の計算及び外積の計算に適した IMC モジュールハードウェアに比べて、より簡単なハードウェア及び中間数のバッファレジスタを備えた中間グラウンド ( middle ground ) を示す。

【 0097 】

より詳細には、2 つの 4 × 4 行列 A と B との間でテンソル積を実装することは、64 の乗算演算、48 の加算演算、及び行列 A / 行列 B での転置 ( transpose ) を含む。本発明の一実施形態による 16 レーンの e - ALU 252 を使用する場合、16 個の演算が並列に実行される。これらの  $64 + 48 = 112$  の演算は、7 サイクルの ALU ( 一回のサイクルで乗算を実行すると仮定 ) で実行される。本発明の別の実施形態において、性能を向上させるために、64 レーンの ALU 252 は、2 ~ 3 サイクル又は 4 ~ 6 ナノ秒 ( nanoseconds ) で 2 つの 4 × 4 行列を表す 2 つのタイルのテンソル積の計算に使用される。したがって、ALU 252 でレーンの数を増加させることは、計算間で可能な並列化の量を増加させ、性能を向上させる。

【 0098 】

したがって、本発明の実施形態の態様は、インメモリコンピューティングを備えた DRAM システムにおけるデータ配置のためのシステム及び方法に関する。SR ( 単一ページ ) データレイアウトに関して、内積、外積、及びテンソル積を計算する上記の 3 つの例において、单一の行は、( 行列の ) 列データを有する第 2 のタイルと同じページに ( 行列の ) 行データを有する第 1 のタイルを含む。

【 0099 】

本発明の一部の実施形態によると、メモリモジュール 110 のメモリコントローラ 140 ( 又はクライアント側メモリコントローラ ) は、ホストプロセッサ 170 から受信した命令に従って、ホストプロセッサ 170 から受信したデータ ( オペランド ) の配置を制御する。例えば、命令が内積、外積、又はテンソル積を計算すべきか否かに基づいて、及びオペランドのサイズ ( 例えば、行列の寸法 ( dimensions ) ) に基づいて、メモリコントローラ 140 は、TOP、SR 又は DR データレイアウトを使用し、それに応じてデータを格納するように DRAM バンクを制御する。

【 0100 】

図 10 は、本発明の実施形態による、IMC モジュールを有する DRAM バンク内のデータの配置を制御するための方法を示すフローチャートである。ステップ S1110 において、メモリコントローラ 140 は、オペランド ( 例えば、第 1 のオペランド及び第 2 のオペランド ) と、オペランドに適用される命令 ( 例えば、関数 ) とを受信する。例えば、これらの命令は、内積、外積の計算、学習済みのニューラルネットワーク及び入力ベクトルを使用した推論の実行、ニューラルネットワークの学習のための逆伝搬 { でんぱん } アルゴリズム ( backpropagation algorithm ) のステップの実行

10

20

30

40

50

等を含む。

【0101】

ステップS1130において、メモリコントローラ140は、命令に基づいて、DRAMダイ上のDRAMバンクに一方又は両方のオペランドを格納するために使用するデータレイアウト（例えば、10P、SR、又はDR）を決定する。一部の実施形態において、（例えば、ホストメモリコントローラ180からの）命令は、どのデータレイアウトを使用するかを明示して指定する。一部の実施形態において、実行する計算のタイプ、及びDRAMバンクにおけるそのような計算を加速するためのメモリ又はハードウェア要件に基づいて、レイアウトが選択される（例えば、内積を計算するための命令は、アキュムレータを有するDRAMバンクにデータが配置されるのに対し、外積を計算する命令は、より多くの出力バッファを有するDRAMバンクにデータが配置される）。

10

【0102】

ステップS1150において、メモリコントローラ140は、選択されたデータレイアウトに基づいて、第1のオペランド及び第2のオペランドをDRAMバンクに供給する。一例として、10Pの場合、メモリコントローラ140は、第1のオペランドの少なくとも第1のタイルを格納し、第2のオペランドの第2のタイルをDRAMバンクのIMCモジュールに直接供給するように、DRAMバンク200を制御する。他の例として、SRの場合、メモリコントローラ140は、DRAMバンクの同じ行又は同じページに、第1および第2のオペランドに対応するタイルを格納するように、DRAMバンク200を制御する。

20

【0103】

ステップS1170において、メモリコントローラ140は、入力命令に基づいた演算を実行するように、DRAMバンク200のIMCモジュールを制御する。例えば、学習済みのモデルを使用して推論を実行する命令の場合、演算は、一つのオペランドに基づいて入力ベクトルを用意し、第2のオペランドに格納されたパラメータに基づいて入力ベクトルの値に重みを付けることが含まれる。

【0104】

本明細書では、特定の例示的な実施形態を提示しているが、本発明は、開示された実施形態に限定されず、本発明の思想や技術範囲を逸脱しない範囲内で多様に変更実施することが可能である。

30

【符号の説明】

【0105】

- 100：メモリシステム

- 110：メモリモジュール

- 120：DRAMダイ

- 130：内部メモリバス

- 140：メモリコントローラ

- 170：ホストプロセッサ

- 180：ホストメモリコントローラ

- 190：外部バス

- 200：DRAMバンク

- 210：DRAMセル

- 212：コンデンサ

- 214：スイッチ

- 220：行デコーダ

- 230：入出力センス増幅器層（IOSA）

- 232：センス増幅器

- 234：マルチプレクサ

- 236：グローバルIO層

- 240：列デコーダ

40

50

250 : IMC モジュール (ALU & Reg)

252 : ALU

254 : オペランドレジスタ (Rop)

256 : 結果レジスタ (Rz)

257 : 第1のマルチプレクサ

258 : 第2のマルチプレクサ

260 : 入出力 (IO) モジュール

300 : マルチプレクサ

401, 402, 411, 412, 413, 421, 422, 423 ページ

802 アキュムレータ

812 第1のバッファ

814 第2のバッファ

【図面】

【図1】

【図2 A】

【図 2 B】

【図 2 C】

10

【図 3】

【図 4 A】

20

30

40

50

【図 4 B】

【図 4 C】

10

20

30

40

【図 5 A】

【図 5 B】

50

【図 6 A】

【図 6 B】

【図 7 A】

【図 7 B】

【図 8】

【図 9】

【図 10】

## フロントページの続き

## (51)国際特許分類

H 1 0 B 99/00 (2023.01)

F I

H 1 0 B 12/00 6 8 1 F

H 1 0 B 99/00 4 9 5

ライブ 4 1 9 6

## (72)発明者 皇甫文沁

アメリカ合衆国, 9 5 1 3 1 カリフォルニア州, サンノゼ, ベンダー プレイス 1 6 1 0

## 審査官 北村 学

## (56)参考文献

特開平06-215160 (JP, A)

特開2003-272384 (JP, A)

特開2008-123479 (JP, A)

特開2019-028572 (JP, A)

特開2019-075101 (JP, A)

米国特許第05953738 (US, A)

米国特許出願公開第2017/0255390 (US, A1)

## (58)調査した分野 (Int.Cl., DB名)

G 0 6 F 1 2 / 0 0

G 0 6 F 9 / 3 4

G 0 6 F 1 2 / 0 6

G 1 1 C 5 / 0 4

G 1 1 C 1 1 / 4 0 9 3

H 1 0 B 1 2 / 0 0

H 1 0 B 9 9 / 0 0