(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4449544号

(P4449544)

(45) 発行日 平成22年4月14日(2010.4.14)

(24) 登録日 平成22年2月5日(2010.2.5)

(51) Int.Cl.

F 1

H01G 4/12 (2006.01)

H01G 4/30 (2006.01)H01G 4/12 364

H01G 4/12 352

H01G 4/30 301C

H01G 4/30 311D

H01G 4/30 311F

請求項の数 4 (全 9 頁)

(21) 出願番号

特願2004-117600 (P2004-117600)

(22) 出願日

平成16年4月13日 (2004.4.13)

(65) 公開番号

特開2005-303030 (P2005-303030A)

(43) 公開日

平成17年10月27日 (2005.10.27)

審査請求日

平成19年4月4日 (2007.4.4)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100109667

弁理士 内藤 浩樹

(74) 代理人 100109151

弁理士 永野 大介

(74) 代理人 100120156

弁理士 藤井 兼太郎

(72) 発明者 長井 淳夫

大阪府門真市大字門真1006番地 松下

電子部品株式会社内

(72) 発明者 中村 健吾

大阪府門真市大字門真1006番地 松下

電子部品株式会社内

最終頁に続く

(54) 【発明の名称】 内部電極パターンの形成方法とこれを用いた積層セラミック電子部品の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

積層セラミック電子部品の内部電極パターンの形成方法であって、柱状体の集合によって形成され表面から見た形状がクラックによって微細面積に分割された金属薄膜を第1の支持体上に形成する第1の工程と、第2の支持体上に内部電極の非形成部分に対応する形状に樹脂層を形成する第2の工程と、前記第1の支持体上の金属薄膜と前記第2の支持体上の樹脂層とを金属薄膜と樹脂層とが対向するように重ね合わせて支持体ごと加圧する第3の工程と、第3の工程の加圧後に前記第2の支持体を剥離して前記樹脂層とともに内部電極の非形成部分の金属薄膜を除去する第4の工程を備えた内部電極パターンの形成方法。

## 【請求項 2】

セラミックシートと内部電極が交互に重なるように積層する工程を含むセラミック電子部品の製造方法において、柱状体の集合によって形成され表面から見た形状がクラックによって微細面積に分割された金属薄膜を第1の支持体上に形成する第1の工程と、第2の支持体上に内部電極の非形成部分に対応する形状に樹脂層を形成する第2の工程と、前記第1の支持体上の金属薄膜と前記第2の支持体上の樹脂層とを金属薄膜と樹脂層とが対向するように重ね合わせて支持体ごと加圧する第3の工程と、第3の工程の加圧後に前記第2の支持体を剥離して前記樹脂層とともに内部電極の非形成部分の金属薄膜を除去して内部電極パターンを形成する第4の工程と、セラミックシートと前記内部電極パターンを形成した金属薄膜とを交互に積層して積層体を作製する第5の工程と、前記積層体を切断し焼成する第6の工程とを備えた積層セラミック電子部品の製造方法。

**【請求項 3】**

内部電極パターンを形成した金属薄膜とセラミックシートとを積層する第5の工程は、前記金属薄膜と前記セラミックシートとの界面に第2の樹脂層を介在させつつ積層する請求項2記載の積層セラミック電子部品の製造方法。

**【請求項 4】**

第2の樹脂層にはチタン酸バリウム、酸化マグネシウム、酸化アルミニウムから選ばれた1種類または2種類以上のセラミック粉末が含有されているものを用いる請求項3記載の積層セラミック電子部品の製造方法。

**【発明の詳細な説明】****【技術分野】**

10

**【0001】**

本発明は、例えば積層セラミックコンデンサ等の積層セラミック電子部品に用いられる内部電極パターンの形成方法ならびにこれを用いた積層セラミック電子部品の製造方法に関するものである。

**【背景技術】****【0002】**

従来、積層セラミック電子部品の内部電極として金属薄膜を用いることが種々提案されており、例えば特許文献1には転写基体の一方の面に、剥離層、金属層、接着層が順次積層され、剥離層と接着層が所定の内部電極パターン形状を有する積層セラミックコンデンサの内部電極転写箔が開示されている。

20

**【特許文献1】特開2003-86454号公報****【発明の開示】****【発明が解決しようとする課題】****【0003】**

上記従来の内部電極転写箔は、金属層の上下に設けた剥離層、接着層により連続した金属層の一部を転写するものであるが、積層数が例えば100層以下と比較的少ない場合には精度良く転写できても、数百層にのぼる多積層の場合には、累積された内部電極の有無による段差などのため、セラミックシートへの転写時に内部電極部分以外の不要部分まで転写されたり、あるいは転写が不完全になり所望の形状に転写できない部分が発生するなどの課題があった。

30

**【0004】**

また、あらかじめエッティングやフォトリソグラフィなどの方法により金属薄膜を内部電極形状に形成してから転写する方法もあるが、この場合には多くの工程を必要とし、また高価な設備が必要なため量産性に劣るものであった。

**【0005】**

本発明は、例えば数百層と多積層の積層であっても、内部電極を所望の形状に精度良く転写することのできる内部電極パターンの形成方法と、これを用いた積層セラミック電子部品の製造方法を提供することを目的とするものである。

**【課題を解決するための手段】****【0006】**

40

この目的を達成するために本発明は、積層セラミック電子部品の内部電極パターンの形成方法であって、柱状体の集合によって形成され表面から見た形状がクラックによって微細面積に分割された金属薄膜を第1の支持体上に形成する第1の工程と、第2の支持体上に内部電極の非形成部分に対応する形状に樹脂層を形成する第2の工程と、前記第1の支持体上の金属薄膜と前記第2の支持体上の樹脂層とを金属薄膜と樹脂層とが対向するよう重ね合わせて支持体ごと加圧する第3の工程と、第3の工程の加圧後に前記第2の支持体を剥離して前記樹脂層とともに内部電極の非形成部分の金属薄膜を除去する第4の工程を備えた内部電極パターンの形成方法であり、金属薄膜を所望の形状で精度良く転写することができる。

**【0007】**

50

また、金属薄膜として、柱状体の集合によって形成され表面から見た形状がクラックによって微細面積に分割されているものを用いることにより、転写不要部分や転写不足の部分が発生することをより少なくでき、内部電極パターンがより精度良く形成できるものである。

【0008】

さらに、上記の内部電極パターン形成方法を用いて積層体を作製し、個片に切断し焼成して積層セラミック電子部品を得ることにより、たとえば静電容量のばらつきが少なく、ショート不良の少ない積層セラミック電子部品を作製できるものである。

【発明の効果】

【0009】

10

本発明による内部電極パターンの形成方法は、内部電極非形成部分に対応する樹脂層を用いてこの非形成部分に相当する金属薄膜を除去するという量産性の高い方法により金属薄膜の内部電極パターンを形成し、これを用いて積層セラミック電子部品を作製するので、例えは数百層という多積層の場合でも内部電極の転写を精度良く行うことができ、これを用いた積層セラミック電子部品の特性ばらつきやショート不良の抑制を行うことができる。

【発明を実施するための最良の形態】

【0010】

以下、本発明の一実施の形態について、積層セラミックコンデンサを例に図を参照しながら説明する。

20

【0011】

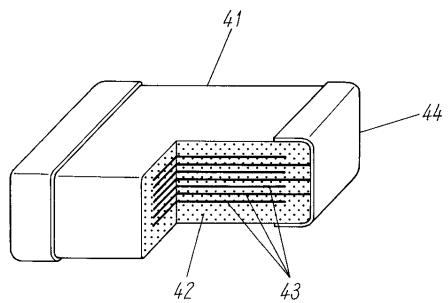

図7は、積層セラミックコンデンサ41の一部切欠斜視図であり、誘電体層42と内部電極43とが交互に積層されて積層体を構成し、内部電極43はその端面が積層体の対向する両端面に交互に露出するよう積層されており、積層体の両端面に形成された一対の外部電極44に交互に接続されている。

【0012】

このような積層セラミックコンデンサの製造方法について、以下に説明する。まず、チタン酸バリウムを主成分とし、これに希土類元素の酸化物や $\text{SiO}_2$ ,  $\text{MgO}$ ,  $\text{MnO}_2$ などの添加物を加えたセラミック原料粉末を混合し、必要に応じて仮焼し粉碎したセラミック粉体を作製する。

30

【0013】

このセラミック粉体と、ポリビニルブチラール樹脂やアクリル樹脂などのバインダー、フタル酸エステルなどの可塑剤、酢酸ブチルなどの溶剤とを混合してセラミックスラリーを作製する。

【0014】

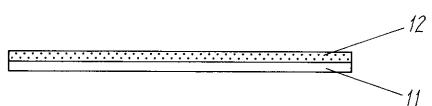

このセラミックスラリーをドクターブレードなどの方法を用いて図1に示すようにポリエチレンテレフタレート(以下PETと略称する)などのフィルム11上に塗工してセラミックシート12を作製する。このセラミックシートは焼成により誘電体層を形成する。

【0015】

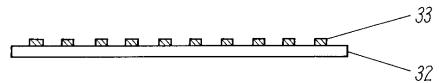

これとは別に、図2に模式的に示す蒸着装置を用いて、PETフィルムやポリイミドフィルムなどの第1の支持体21上にNi金属薄膜22を蒸着により形成する。第1の支持体21は巻出口ロール29から供給され、冷却ドラム28により冷却されながらNi金属薄膜22が蒸着され、Ni金属薄膜22が供給された第1の支持体21は巻取ロール30に巻き取られる。

40

【0016】

なお、図2の蒸着装置の真空槽23は、真空槽23の下部に取り付けられた排気管31より減圧されている。

【0017】

ここで、蒸着金属(Ni)26より蒸発したNi蒸気27によりNi金属薄膜22が形成されると同時に、Ni金属薄膜が成膜される部分に向けてArガス24をガスノズル2

50

5より供給し、真空槽23の真空度はArガス供給下で $8 \times 10^{-2}$ Pa、また支持体21の送り速度は20m/minとした。このように成膜されたNi金属薄膜22の厚みは0.5μmで、その断面の観察結果によるとNi金属薄膜22は縦方向に連続した微細な柱状体の集合によって形成され、またNi金属薄膜22の表面から見た形状はクラックによつて微細面積に分割されている構造となっていた。

【0018】

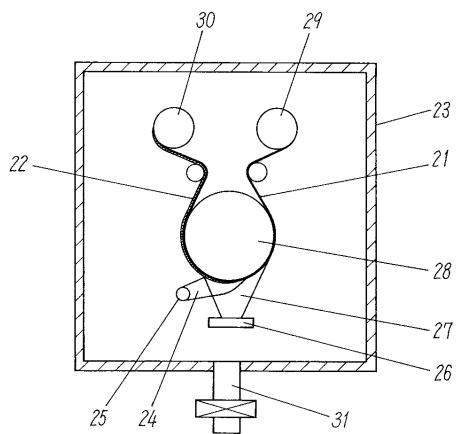

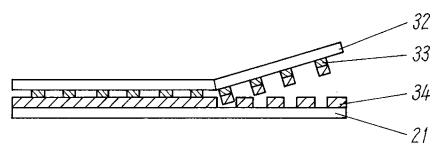

また、ポリビニルブチラール樹脂と可塑剤などを含む樹脂ペーストを作製し、グラビア印刷などの方法を用いて、図3に示すように第2の支持体32上に内部電極非形成部分に対応するパターン形状に第1の樹脂層33を形成した。

【0019】

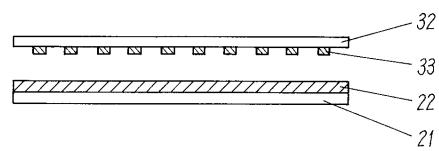

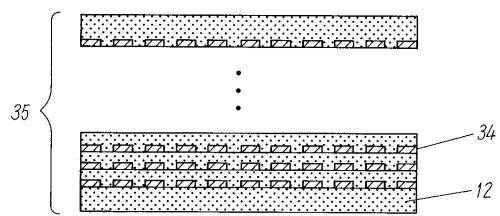

次に、図4に示すように、上記第1の支持体21上に形成したNi金属薄膜22と、第2の支持体32上に形成した内部電極非形成部分に対応するパターン状の樹脂層33とが対向するように重ね合わせ、支持体21, 32側から加圧したのち支持体32を剥離し、図5に示すように内部電極非形成部分に対応するパターン状のNi金属薄膜22を、支持体32上の樹脂層33と共に除去して、内部電極パターン34を作製した。金属薄膜22は、焼成により内部電極となるものである。上記内部電極非形成部分の除去に際して、Ni金属薄膜が断面は縦方向に連続した微細な柱状体の集合によって形成され、またNi金属薄膜の表面から見た形状はクラックによつて微細面積に分割されているため、内部電極非形成部分の除去は容易に行うことができ、また非形成部分を除去した後の内部電極パターンについても除去されずに残った部分や除去されすぎた部分はなく、きれいなパターン形状のものが得られた。

【0020】

このようにして作製した内部電極パターン34と、セラミックシート12とを、別途PETフィルム上に0.01μm~0.5μmの厚みで予め形成した接着層(図示せず)を介して交互に300層積層して図6に示すような積層体35を作製し、焼成後に3.2mm×1.6mmの寸法となるように所定の寸法で切断し、焼成した。

【0021】

この接着層は、ポリビニルブチラール樹脂と可塑剤などの有機物と、比表面積が20m<sup>2</sup>/gのチタン酸バリウムを含むものであり、積層体の焼成過程で誘電体層と内部電極との結合性を高め、デラミネーションなどの構造欠陥の発生を防止できるものである。

【0022】

接着層に含ませるセラミック粉末は、チタン酸バリウム以外に酸化マグネシウム、酸化アルミニウムでも同様の効果が得られ、またこれら3種類のセラミック粉末を組み合わせて用いてもよいが、特にチタン酸バリウムは金属薄膜の表面に形成されたクラックに入り込んで、金属薄膜よりなる内部電極上下の誘電体層を結びつける働きを有し、他の2種類のセラミック粉末より内部構造欠陥を抑制する効果が大きい。さらにチタン酸バリウムは誘電体層の主成分と同じものであるので、接着層に入れる量を多くしても、静電容量等の特性に及ぼす影響が小さい。

【0023】

上記のセラミック粉末はいずれも比表面積が10m<sup>2</sup>/g以上の粉末を用いるのが好ましい。

【0024】

その後、内部電極が露出した両端面に外部電極を形成して、静電容量やショート率測定用の試料(試料番号1)とした。

【0025】

静電容量については、試料100個を20の恒温槽中で周波数1kHz、入力信号レベル1.0Vrmsにて測定し、その最大値と最小値の差Rにより静電容量ばらつきを評価した。

【0026】

ショート率については、上記の静電容量測定後の試料100個について絶縁抵抗計を用

10

20

30

40

50

いて抵抗値を測定し、抵抗値が  $10^3$  以下の個数を百分率で表してショート率とした。

【0027】

また、従来方法による比較例として、特開2003-86454号公報に記載の方法により、P E T フィルム上に内部電極パターン形状に剥離層を形成し、この上に実施の形態1と異なるのはArガスを供給しないこと以外は実施の形態1と同様の方法でNi金属薄膜22を形成した。

【0028】

このNi金属薄膜22の断面構造を観察したところ、Ni蒸着膜の縦方向の形状は連続的な柱状構造ではなく、縦方向に断続的な大きな柱状体からなる構造であり、表面の構造はクラックがほとんどない連続した構造となっていた。

10

【0029】

このNi金属薄膜22上に、内部電極パターン形状の接着層を形成し、実施の形態1と同様にセラミックシートに転写しつつ300層の積層を行った。

【0030】

この積層過程では、内部電極パターンの形成は一部形状が不十分なものとなり、所定の内部電極パターン形状の周囲につながって、非形成部分に至るまで金属薄膜が転写された部分が多く見られた。

【0031】

積層後の積層体35を、上記実施の形態1と同様に焼成後に  $3.2\text{ mm} \times 1.6\text{ mm}$  となるように所定の寸法で切断し、焼成した後、外部電極を形成したものについて、従来方法による比較例の測定用試料（試料番号2）とし、同様の測定を行った。

20

【0032】

上記積層セラミックコンデンサ試料番号1, 2について、静電容量の平均値並びに静電容量のばらつきとショート率を測定した結果をまとめて（表1）に示す。

【0033】

静電容量のばらつきとしては、静電容量の最大値と最小値の差であるR値として表している。

【0034】

【表1】

| 試料番号 | 静電容量 ( $\mu\text{ F}$ ) |     | ショート率<br>(%) |

|------|-------------------------|-----|--------------|

|      | 平均値                     | R値  |              |

| 1    | 10.2                    | 0.5 | 0.1          |

| 2    | 9.8                     | 1.8 | 35           |

30

【0035】

（表1）から明らかなように、本発明の一実施の形態による試料番号1では、静電容量のばらつきを示すR値は  $0.5\mu\text{ F}$  と小さく、ショート率も  $0.1\%$  と小さいのに対して、比較例の試料番号2ではR値が  $1.8\mu\text{ F}$  と、静電容量のばらつきが大きくなっているとともに、ショート率も  $35\%$  と大きくなっている。これは、試料番号2の従来方法による金属薄膜22の転写では、金属薄膜22の表面にクラックがほとんどなく、金属薄膜22が連続した構造として形成されているため、転写を望んでいない部分まで転写されてしまい、これが静電容量のばらつきやショート率の増加につながったものである。

40

【0036】

なお、本実施の形態では内部電極非形成部分に対応するパターン状の樹脂層33を用いて内部電極非形成部分の金属薄膜22を除去することにより金属薄膜22を内部電極形状にパターン化したが、これは内部電極パターン形状に形成した樹脂層を介してセラミックシート上に金属薄膜を内部電極パターン形状に転写した場合、セラミックシートの接着性

50

によっては樹脂層を形成していない部分、つまり内部電極非形成部分までセラミックシート上に転写される場合があるためである。

【0037】

上記のような不具合を避けるために、本発明では予め内部電極形状にパターン化した金属薄膜22をセラミックシート12上に転写するものである。

【0038】

また、本発明の一実施の形態では、P E Tなどのフィルム11上に形成したセラミックシート12を用いたが、これに限定されるものではなく、例えばセラミック粉体と分子量が40,000以上のポリエチレン等を混練した後シート状に成形し、さらに2軸延伸して得られたセラミックシートを用いてもよい。

10

【0039】

この場合には、ポリエチレンを含むセラミックシートは接着性が低いため、上記のように内部電極パターン形状に形成した樹脂層を介して、セラミックシート上に金属薄膜を内部電極パターン形状に転写してもよい。

【産業上の利用可能性】

【0040】

本発明にかかる内部電極パターンの形成方法は、セラミック電子部品の製造方法は、内部電極非形成部分に対応する樹脂層を用いてこの非形成部分に相当する金属薄膜を除去するという量産性の高い方法により金属薄膜の内部電極パターンを形成し、これを用いて積層セラミック電子部品を作製するので、例えば数百層という多積層の場合でも内部電極の転写を精度良く行うことができ、積層セラミック電子部品の製造等に有用である。

20

【図面の簡単な説明】

【0041】

【図1】本発明の一実施の形態におけるフィルム上に形成したセラミックシートの断面図

【図2】同蒸着装置の概略図

【図3】同第2の支持体上に形成した樹脂層の断面図

【図4】同内部電極パターンを形成する方法を説明するための断面図

【図5】同内部電極パターンを形成する方法を説明するための断面図

【図6】同積層体の断面図

【図7】同積層セラミックコンデンサの一部切欠斜視図

30

【符号の説明】

【0042】

11 P E T フィルム

12 セラミックシート

21 第1の支持体

22 金属薄膜

23 真空槽

24 A r ガス

25 ガスノズル

26 蒸着金属

27 N i 蒸気

28 冷却ドラム

29 卷出口ール

30 卷取ロール

31 排気管

32 第2の支持体

33 樹脂層

34 内部電極パターン

35 積層体

41 積層セラミックコンデンサ

40

50

- 4 2 誘電体層

4 3 内部電極

4 4 外部電極

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 辻村 孝彦

大阪府門真市大字門真1006番地 松下電子部品株式会社内

(72)発明者 阿部 冬希

大阪府門真市大字門真1006番地 松下電子部品株式会社内

審査官 酒井 朋広

(56)参考文献 特開2003-086454 (JP, A)

特開2003-347149 (JP, A)

特開平05-214516 (JP, A)

特開2000-228571 (JP, A)

特開平05-132758 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 G 4 / 12

H 01 G 4 / 30