(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6074166号

(P6074166)

(45) 発行日 平成29年2月1日(2017.2.1)

(24) 登録日 平成29年1月13日(2017.1.13)

(51) Int.Cl.

F 1

|                |           |              |         |

|----------------|-----------|--------------|---------|

| G 11 C 11/407  | (2006.01) | G 11 C 11/34 | 3 5 4 D |

| G 11 C 11/405  | (2006.01) | G 11 C 11/34 | 3 5 2 B |

| H 01 L 29/786  | (2006.01) | H 01 L 29/78 | 6 1 3 B |

| H 01 L 21/8242 | (2006.01) | H 01 L 29/78 | 6 1 8 B |

| H 01 L 27/108  | (2006.01) | H 01 L 27/10 | 6 8 1 F |

請求項の数 10 (全 26 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2012-131527 (P2012-131527) |

| (22) 出願日     | 平成24年6月11日 (2012.6.11)       |

| (65) 公開番号    | 特開2013-16246 (P2013-16246A)  |

| (43) 公開日     | 平成25年1月24日 (2013.1.24)       |

| 審査請求日        | 平成27年5月11日 (2015.5.11)       |

| (31) 優先権主張番号 | 特願2011-129728 (P2011-129728) |

| (32) 優先日     | 平成23年6月10日 (2011.6.10)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

| (31) 優先権主張番号 | 特願2011-129757 (P2011-129757) |

| (32) 優先日     | 平成23年6月10日 (2011.6.10)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                     |

|-----------|---------------------|

| (73) 特許権者 | 000153878           |

|           | 株式会社半導体エネルギー研究所     |

|           | 神奈川県厚木市長谷398番地      |

| (72) 発明者  | 竹村 保彦               |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

| 審査官       | 堀田 和義               |

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

列ドライバーと1以上のビット線と1以上のワード線と1以上のメモリセルとビット線制御トランジスタとビット線制御回路とを有し、

前記メモリセルはトランジスタとキャパシタとを有し、

前記ビット線制御トランジスタのチャネル形成領域は、酸化物半導体が用いられ、

前記トランジスタのソースは前記ビット線に接続し、

前記トランジスタのドレインは前記キャパシタの電極の一に接続し、

前記トランジスタのゲートは前記ワード線に接続し、

前記ビット線制御トランジスタのソースは前記ビット線に接続し、

前記ビット線制御トランジスタのドレインは前記列ドライバーに接続し、

前記ビット線制御トランジスタのゲートは前記ビット線制御回路に接続し、

前記ビット線制御回路は独立して電位を発生する手段の負極に接続することを特徴とする半導体装置。

## 【請求項 2】

請求項1において、

前記ビット線には2以上のビット線制御トランジスタが挿入されていることを特徴とする半導体装置。

## 【請求項 3】

請求項1または請求項2において、

10

20

前記ピット線制御トランジスタのゲートは、前記独立して電位を発生する手段の負極と前記ピット線制御回路内のNチャネル型トランジスタを介して接続することを特徴とする半導体装置。

【請求項4】

請求項1乃至請求項3のいずれかにおいて、

前記トランジスタのドレインは別のトランジスタのゲートに接続することを特徴とする半導体装置。

【請求項5】

請求項1乃至請求項4のいずれかにおいて、

前記ピット線の最低電位は、前記ワード線の最低電位より1V以上高いことを特徴とする半導体装置。 10

【請求項6】

請求項1乃至請求項5のいずれかにおいて、

前記ピット線制御回路はインバータを有し、前記インバータの出力は前記ピット線制御トランジスタのゲートに接続することを特徴とする半導体装置。

【請求項7】

請求項1乃至請求項6のいずれかにおいて、

前記ピット線制御トランジスタのゲートの最高電位は、前記ワード線の最高電位よりも1V以上高いことを特徴とする半導体装置。

【請求項8】

20

請求項1乃至請求項7のいずれかにおいて、

前記ピット線制御トランジスタのゲートの最低電位は、他のいずれの部分よりも低いことを特徴とする半導体装置。

【請求項9】

請求項1乃至請求項8のいずれかにおいて、

前記ピット線制御トランジスタのチャネル形成領域は逆導電型を有さない半導体が用いられていることを特徴とする半導体装置。

【請求項10】

請求項1乃至請求項9のいずれかにおいて、

前記ピット線制御トランジスタのチャネル形成領域はバンドギャップが2.5電子ボルト以上の半導体が用いられていることを特徴とする半導体装置。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置(半導体を用いたメモリ装置を含む)に関する。

【背景技術】

【0002】

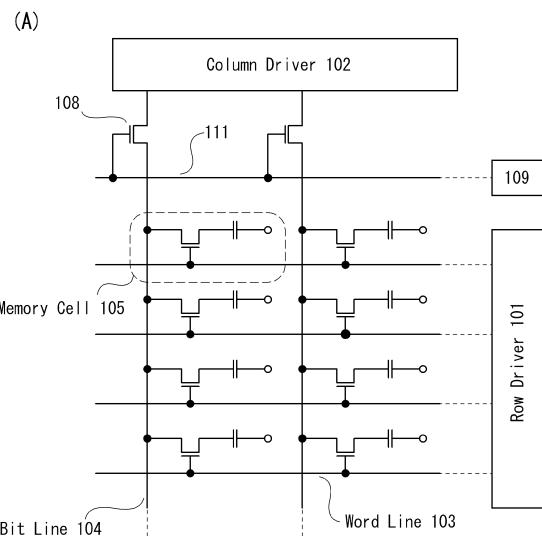

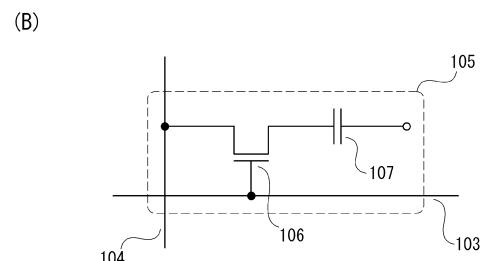

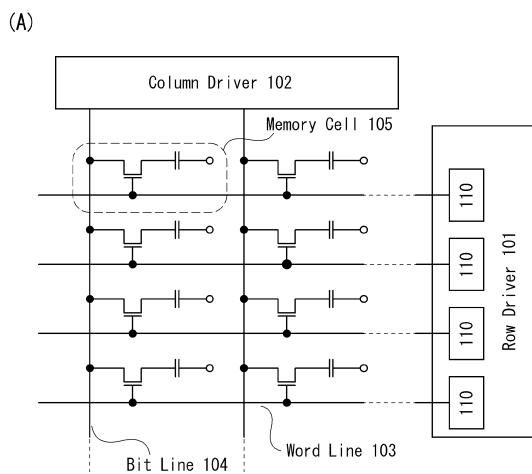

半導体メモリ装置として、ダイナミック・ランダム・アクセス・メモリ(DRAM)が知られている(例えば、特許文献1参照)。DRAMは図2(B)に示すような、セルトランジスタ106とキャパシタ107を有するメモリセル105を、図2(A)に示すようにマトリクス状に配置し、セルトランジスタ106のゲートをワード線103に、ドレンをピット線104に接続したものである。また、複数のワード線を駆動するための行ドライバー101と、複数のピット線を駆動するための列ドライバー102を有する。 40

【0003】

行ドライバー101と列ドライバー102の駆動のために外部から電源が供給される。なお、シリコン半導体を用いたセルトランジスタは、オフ状態でも微小ながらドレン電流(オフ電流)が流れるため、1秒間に数十回、キャパシタに電荷を補充する操作(リフレッシュ)をおこなう必要がある。つまり、DRAMは記憶状態を保持するために外部からの電源供給が不可欠である。

【0004】

50

近年、バンドギャップがシリコン半導体の2倍以上の酸化物半導体を用いたトランジスタのオフ電流が非常に小さいことを利用して、電荷を極めて長期間に保持できることが発見された。例えば、バンドギャップが2.5電子ボルト以上の半導体では、理論上のオフ電流（オフ状態でのドレイン電流）は、 $10^{-26}\text{ A}$ 以下となる。これを利用して、メモリ回路を構成し、不揮発なメモリとして利用することが提唱されている（特許文献2参照乃至特許文献4）。

#### 【0005】

このようなメモリに利用するには、トランジスタのオフ状態での抵抗（オフ抵抗）が十分に高いこと（オフ電流が十分に低いこと）が必要である。例えば、一般的なDRAMで用いられているキャパシタの容量である30fFの容量に電荷を保持して、これを10年維持するには、オフ状態で $1 \times 10^{-22}$ 以上の高い抵抗が必要である。ドレン電圧を+1Vとすれば、オフ電流は $100\text{ yA}$ （ $1 \times 10^{-22}\text{ A}$ ）以下であることが必要である。

10

#### 【0006】

バンドギャップの広い酸化物半導体を用いたトランジスタのサブスレショールド領域でのドレイン電流はサブスレショールド値としきい値とでおおよその値を見積もることができる。室温（27）でのサブスレショールド値の理論上の下限は $60\text{ mV/decade}$ である。

#### 【0007】

例えば、しきい値が+1Vで、サブスレショールド値が $60\text{ mV/decade}$ 、しきい値でのドレイン電流が $1\mu\text{A}$ （ソースの電位 $V_s$ を0V、ドレンの電位を+1Vとする）であれば、ゲートの電位 $V_g$ が+40mVのときドレイン電流は $100\text{ yA}$ となる。ゲートの電位 $V_g$ が0Vであれば、トランジスタのドレイン電流は $100\text{ yA}$ 未満となり、キャパシタの電荷を10年間保持できる。

20

#### 【0008】

なお、保持する期間は10年に限られず、10秒から100年の間で使用する目的に応じて決定でき、そのためにキャパシタの容量やトランジスタのオフ抵抗あるいはオフ電流を設定すればよい。

#### 【0009】

上記は室温でのドレイン電流であるが、実用上はいくつか問題がある。サブスレショールド値は温度に依存し、温度が高くなるとサブスレショールド値は大きくなる。半導体メモリ装置では、高温で保存されることも予想されることから、室温よりも高い温度での保持特性も十分であることが必要である。

30

#### 【0010】

例えば、95でのサブスレショールド値の理論上の下限は $74\text{ mV/decade}$ となる。サブスレショールド値が $74\text{ mV/decade}$ のとき、ドレイン電流が $100\text{ yA}$ となるゲートの電位 $V_g$ の値は-180mVとなる。ゲートの電位 $V_g$ が0Vのとき、ドレイン電流は $10\text{ zA}$ （ $1 \times 10^{-20}\text{ A}$ ）となり、電荷の保持時間は室温のときの1%になる。

#### 【0011】

40

また、トランジスタのサイズが小さくなると短チャネル効果により、サブスレショールド値が上昇する。シリコン半導体はドーピングにより導電型を制御することができる。そのため、例えば、Nチャネル型トランジスタでは、チャネル形成領域のP型のドーパントの濃度を高くして、短チャネル効果を抑制できる。

#### 【0012】

しかしながら、酸化物半導体ではシリコン半導体のようなドーパントの濃度を制御して、導電型を制御することができない。酸化物半導体は、例えば、1つの導電型の強度を変更することはできるが、N型のものをドーピングによりP型に変更すること（逆導電型とすること）はできない。このため、チャネル形成領域を逆の導電型として、短チャネル効果を抑制することができない。

50

**【0013】**

したがって、チャネル長 $100\text{nm}$ 以下ではサブスレショールド値は $100\text{mV}/\text{decade}$ 以上となり、ゲートの電位 $V_g$ を $-0.6\text{V}$ 以下に維持しないと、データが失われる危険がある。さらに、上記では、しきい値を $+1\text{V}$ としたが、しきい値が小さくなれば、室温であっても、また、長チャネルであっても、オフ抵抗を十分に高くするために、ゲートの電位 $V_g$ を $0\text{V}$ 未満とする必要がある。なお、しきい値はゲートに用いる材料の仕事関数によって決定され、しきい値を $+1.5\text{V}$ より大きくすることは困難である。

**【0014】**

このような条件では、半導体メモリ装置の外部からの電源が遮断され、ゲートがソースと同電位（すなわち、 $V_g = 0\text{V}$ ）となるとデータが損なわれる危険がある。なお、電位は相対的なものであるので、以下の説明では外部からの電源が遮断された場合には、多少の時間の経過後、回路の電位は $0\text{V}$ になるとする。10

**【先行技術文献】****【特許文献】****【0015】**

**【特許文献1】**米国特許第4777625号明細書

**【特許文献2】**米国特許出願公開第2011/0101351号明細書

**【特許文献3】**米国特許出願公開第2011/0156027号明細書

**【特許文献4】**米国特許出願公開第2011/0182110号明細書

**【発明の概要】****【発明が解決しようとする課題】****【0016】**

本発明の一は、酸化物半導体のような逆導電型を有さない、バンドギャップが $2.5\text{eV}$ 以上の半導体を用いて形成され、十分な集積度を有し、外部の電源が遮断された状態にあっても必要とする期間、データを保持できるメモリ装置を提供することを課題とする。また、本発明の一は、新規な構造のメモリ装置あるいはその駆動方法を提供することを課題とする。特に消費電力を低減できるメモリ装置あるいはメモリ装置の駆動方法を提供することを課題とする。

**【課題を解決するための手段】****【0017】**

以下、本発明の説明をおこなうが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースとする。すなわち、電位の高低によって、それらを区別しない。したがって、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

**【0018】**

さらに、本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在しているだけのこともある。例えば、トランジスタの回路では、一本の配線が複数のトランジスタのゲートを兼ねている場合もある。その場合、回路図では、一本の配線からゲートに何本もの分岐が生じるように書かれることもある。本明細書では、そのような場合でも、「配線がゲートに接続する」という表現を用いることがある。40

**【0019】**

本発明の一態様は、列ドライバーと1以上のビット線と1以上のワード線と1以上のメモリセルとビット線制御トランジスタとビット線制御回路とを有し、メモリセルはトランジスタとキャパシタとを有し、トランジスタのソースはビット線に接続し、トランジスタのドレインはキャパシタの電極の一に接続し、トランジスタのゲートはワード線に接続し、ビット線制御トランジスタのソースはビット線に接続し、ビット線制御トランジスタのドレインは列ドライバーに接続し、ビット線制御トランジスタのゲートはビット線制御回路に接続し、ビット線制御回路は独立して電位を発生する手段の電極の一に接続することを50

特徴とする半導体メモリ装置である。

【0020】

また、本発明の一態様は、列ドライバーと1以上のビット線と1以上のワード線と1以上のメモリセルとビット線制御トランジスタとビット線制御回路とを有し、メモリセルはトランジスタとキャパシタとを有し、トランジスタのソースはビット線に接続し、トランジスタのドレインはキャパシタの電極の一に接続し、トランジスタのゲートはワード線に接続し、ビット線は列ドライバーに接続し、ビット線は、その一端にビット線制御トランジスタを有し、ビット線制御トランジスタのゲートはビット線制御回路に接続し、ビット線制御回路は独立して電位を発生する手段の電極の一に接続することを特徴とする半導体メモリ装置である。

10

【0021】

また、本発明の一態様は、列ドライバーと1以上のビット線と1以上のワード線と1以上のメモリセルとビット線制御トランジスタとビット線制御回路とを有し、メモリセルはトランジスタとキャパシタとを有し、トランジスタのソースはビット線に接続し、トランジスタのドレインはキャパシタの電極の一に接続し、トランジスタのゲートはワード線に接続し、ビット線は列ドライバーに接続し、ビット線制御トランジスタは、ビット線に直列に挿入されており、ビット線制御トランジスタのゲートはビット線制御回路に接続し、ビット線制御回路は独立して電位を発生する手段の電極の一に接続することを特徴とする半導体メモリ装置である。

20

【0022】

上記において、ビット線には2以上のビット線制御トランジスタが挿入されていてもよい。

また、ビット線制御トランジスタのゲートは、独立して電位を発生する手段の負極とビット線制御回路内のNチャネル型トランジスタを介して接続してもよい。また、メモリセルのトランジスタのドレインは同じメモリセル内の別のトランジスタのゲートに接続してもよい。また、1つ以上のセンスアンプ回路がビット線に挿入されていてもよい。さらに、ビット線制御回路はインバータを有し、前記インバータの出力は前記ビット線制御トランジスタのゲートに接続してもよい。

【0023】

また、ビット線の最低電位は、ワード線の最低電位より1V以上高いことが好ましい。また、ビット線制御トランジスタのゲートの最高電位は、ワード線の最高電位よりも1V以上高いことが好ましい。また、ビット線制御トランジスタの最低電位は、他のいずれの部分よりも低いことが好ましい。

30

【0024】

また、本発明の一態様は、行ドライバーと列ドライバーと1以上のビット線と1以上のワード線と1以上のメモリセルとを有し、メモリセルはトランジスタとキャパシタとを有し、トランジスタのソースはビット線に接続し、トランジスタのドレインはキャパシタの電極の一に接続し、トランジスタのゲートはワード線に接続し、行ドライバーがワード線と接続する部分には独立して電位を発生する手段にソースが接続したトランジスタを有することを特徴とする半導体メモリ装置である。

40

【0025】

また、本発明の一態様は、行ドライバーと列ドライバーと1以上のビット線と1以上のワード線と1以上のメモリセルとを有し、メモリセルはトランジスタとキャパシタとを有し、トランジスタのソースはビット線に接続し、トランジスタのドレインはキャパシタの電極の一に接続し、トランジスタのゲートはワード線に接続し、行ドライバーのトランジスタの一は、ドレインがワード線と接続し、ソースが独立して電位を発生する手段に接続していることを特徴とする半導体メモリ装置である。

【0026】

上記において、行ドライバーのトランジスタの一のソースと独立して電位を発生する手段の間に1つ以上のトランジスタが存在してもよい。また、行ドライバーのトランジスタの

50

一のソースは、独立して電位を発生する手段の負極と接続してもよい。また、メモリセルのトランジスタのドレインは同じメモリセル内の別のトランジスタのゲートに接続してもよい。さらに行ドライバーのトランジスタの一はインバータを構成するトランジスタであってもよい。また、行ドライバーのトランジスタの一はNチャネル型トランジスタであってもよい。

#### 【0027】

また、ビット線の最低電位は、ワード線の最低電位より1V以上高いことが好ましい。また、ワード線の最低電位は、他のいずれの部分よりも低いことが好ましい。

#### 【0028】

独立して電位を発生する手段としては電池やキャパシタを用いることができる。すなわち、それ自体が起電力を有するか、外部からの電気的な作用によらずに一定の電位を維持できるものであればよい。

10

#### 【0029】

なお、以上はメモリセルのトランジスタおよびビット線制御トランジスタがNチャネル型である場合である。メモリセルのトランジスタおよびビット線制御トランジスタがPチャネル型である場合には、上記の電位の関係は反転し、上記で「高い」とされた部分は「低い」と、「低い」とされた部分は「高い」と、「最高」とされた部分は「最低」と、「最低」とされた部分は「最高」と、読み替えればよい。

#### 【発明の効果】

#### 【0030】

20

ビット線制御回路は外部からの電源が遮断された際には、ビット線制御トランジスタのゲートの電位を十分な負の値とするように設計された回路である。負の電位を出力するために、電池やそれに類する電位発生装置（キャパシタ等）を有する。

#### 【0031】

ビット線制御トランジスタは、上記のようにバンドギャップの大きな半導体を用いることにより、オフ電流を十分に小さくできる。そして、そのゲートは、ビット線制御回路に接続し、外部からの電源が遮断された場合には、負の電位となるよう設定されている。そのため、外部からの電源が遮断された際には、そのソースとドレインの間は非常に高い抵抗となる。

#### 【0032】

30

上記の本発明の一態様では、例えば、列ドライバーとビット線の間にビット線制御トランジスタを設けることで、ビット線を浮遊状態とし、その電位を一定に保持できる。そして、ビット線の電位が一定の値であれば、メモリセルのトランジスタのゲートの電位が0Vであっても、ドレン電流を十分に小さくできる。

#### 【0033】

ビット線の電位は、書き込みや読み出しのデータにより変動するが、外部より電源が供給されている状態では電位 $V_1$  ( $> 0$ ) 以上となるようにする。ここでは、電位は $V_1$ であったとする。また、外部より電源が供給されている状態ではビット線制御トランジスタのゲートの電位は、適切な正の値（例えば、 $V_2$  ( $> 0$ )）であるため、ビット線制御トランジスタはオン状態となる。

40

#### 【0034】

ここで、外部からの電源が遮断されたとする。このとき、半導体メモリ装置は、電源の遮断を検知して、まず、ビット線制御トランジスタのゲートの電位を十分な負の値（例えば、 $V_3$  ( $< 0$ )）とする。そのためビット線制御トランジスタはオフ状態となる。半導体メモリ装置の多くの部分の電位が十分に低下してしまうと、列ドライバーの電位も0Vとなるため、ビット線制御トランジスタのソースの電位も0Vとなる。

#### 【0035】

しかしながら、ビット線制御トランジスタは外部電源遮断と同時にオフとなり、ビット線（ビット線制御トランジスタのドレン）の電位は $V_1$ のままであり、そのゲートの電位が十分な負の値となつていれば、ビット線の電位は極めて長期にわたり $V_1$ に近い値に保

50

持できる。

**【0036】**

さて、ビット線にはメモリセル105が接続されている。メモリセルのトランジスタのドレインの電位は書き込まれているデータによって異なるが、外部より電源が供給されている状態では、ビット線の電位が $V_1$ 以上であるので、メモリセルのトランジスタのドレインの電位も $V_1$ 以上である。ここではメモリセルのトランジスタのドレインの電位が $V_4$ ( $V_1$ )であったとする。

**【0037】**

さらに、電源遮断後はビット線の電位は、上記のように $V_1$ であるので、メモリセルのトランジスタのソースの電位は $V_1$ である。一方、外部からの電源の遮断によって、ワード線の電位(メモリセルのトランジスタのゲートの電位)は0Vとなる。この状態でのメモリセルのトランジスタのドレイン電流は、ソースの電位を0Vとした場合のゲートの電位を $-V_1$ とした場合と同等である。すなわち、 $V_1$ を適切な値とすることで、ドレイン電流は非常に小さく、キャパシタの電荷は十分な期間にわたって保持される。

10

**【0038】**

つまり、ビット線にビット線制御トランジスタを挿入すれば、外部からの電源が遮断された状態においてもビット線の電位を十分な期間にわたって適切な正の値に保持でき、その結果、より広範な温度において、さまざまなチャネル長、しきい値のトランジスタをセルトランジスタに用いて作製された半導体メモリ装置でも、十分なデータ保持特性が得られる。

20

**【0039】**

なお、ビット線制御トランジスタはビット線に直列に挿入されるので、オン状態での抵抗は可能な限り低いことが望ましい。そのためには、ビット線制御トランジスタのゲートの電位を高くするとより効果的である。例えば、他のトランジスタのゲートの最高電位(例えば、ワード線の最高電位)よりも1V以上高いことが好ましい。

**【0040】**

また、上記の構成により、外部からの電源が遮断された際にワード線の電位を十分な負の値とすることができます。外部からの電源が遮断された際、列ドライバー内の電位は0Vとなるが、ワード線の電位が十分な負であれば、メモリセルのセルトランジスタのオフ抵抗を十分に高くできる。結果として、電源が遮断された場合でも、より広範な条件(温度、チャネル長、しきい値)のトランジスタをセルトランジスタに用いて作製された半導体メモリ装置でも、十分なデータ保持特性が得られる。

30

**【図面の簡単な説明】**

**【0041】**

【図1】本発明の半導体メモリ装置の例を示す図である。

【図2】従来の半導体メモリ装置の例を示す図である。

【図3】本発明の半導体メモリ装置の例を示す図である。

【図4】本発明の半導体メモリ装置の例を示す図である。

【図5】本発明の半導体メモリ装置の動作例を説明する図である。

【図6】本発明の半導体メモリ装置の作製工程の例を示す図である。

40

【図7】本発明の半導体メモリ装置の作製工程の例を示す図である。

【図8】本発明の半導体メモリ装置の作製工程の例を示す図である。

【図9】本発明の半導体メモリ装置の作製工程の例を示す図である。

【図10】本発明の半導体メモリ装置の作製工程の例を示す図である。

【図11】本発明の半導体メモリ装置の例を示す図である。

【図12】本発明の半導体メモリ装置の例と動作例を示す図である。

【図13】本発明の半導体メモリ装置の例を示す図である。

**【発明を実施するための形態】**

**【0042】**

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異な

50

る態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

#### 【0043】

##### (実施の形態1)

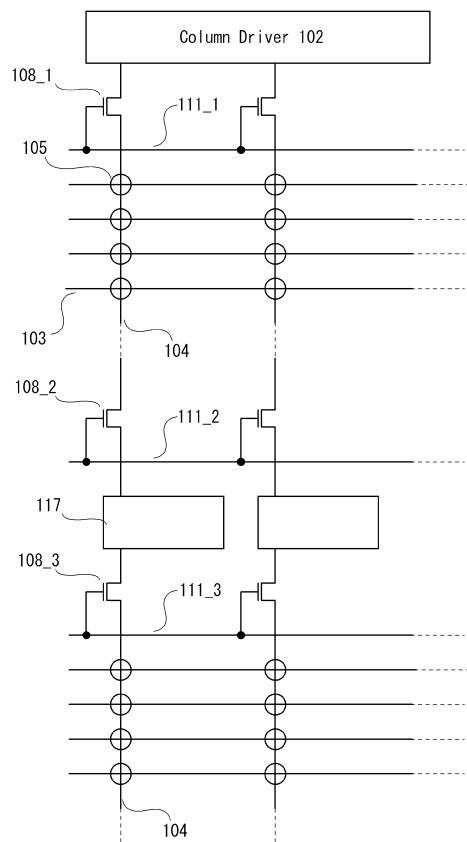

本実施の形態では、図1(A)に示す半導体メモリ装置について説明する。図1(A)に示す半導体メモリ装置は、行ドライバー101、列ドライバー102、行ドライバー101に接続する複数のワード線103、列ドライバー102に(間接的に)接続する複数のビット線104、それぞれのワード線103とビット線104の交点に設けられるメモリセル105を有する。上記の構成は図2に示す従来のDRAMの構成と同様である。

10

#### 【0044】

図1(A)に示す半導体メモリ装置ではそれらに加えて、列ドライバー102とそれぞれのビット線104の間に挿入されたビット線制御トランジスタ108を有する。なお、ビット線制御トランジスタ108はビット線104に挿入されているとも表現できる。

#### 【0045】

あるいは、ビット線制御トランジスタ108のソースが列ドライバー102に接続し、ドレインがビット線104に接続すると表現してもよい。あるいは、列ドライバー102と、列ドライバー102に最も近いメモリセル105の間にビット線制御トランジスタ108が挿入されていると表現してもよい。

#### 【0046】

ビット線制御トランジスタ108のゲートはビット線制御線111に接続する。ビット線制御線111はビット線制御回路109によって電位が設定される。外部より電源が供給されて半導体メモリ装置が使用できる状態にあると判断された場合、ビット線制御回路109は、ビット線制御線111に適切な電位を与えて、ビット線制御トランジスタ108をオンとする。

20

#### 【0047】

また、ビット線の電位は、書き込みや読み出しのデータにより変動するが、外部より電源が供給されている状態では正の電位となるようにする。例えば、+1V以上とする。

#### 【0048】

次に、外部からの電源が遮断されたと検知した場合、あるいは、外部より電源が供給されている状態であっても半導体メモリ装置の使用が終了したという状態を検知した場合には、ビット線制御回路109はビット線制御線111の電位を0V以下の十分な負の電位(例えば、-1V)として、すみやかにビット線制御トランジスタ108をオフとする。

30

#### 【0049】

ビット線制御トランジスタ108がオフとなることにより、ビット線104は列ドライバーから絶縁され、その電位(+1V以上)は保持される。一方、行ドライバの電源電位は0Vとなるので、ワード線103の電位は0Vとなる。その結果、メモリセル105のセルトランジスタ106のゲートの電位はソースの電位よりも十分に低い、という状態となる。そのため、セルトランジスタ106のオフ抵抗は十分に高く、キャパシタ107にある電荷を長期間にわたって保持できる。

40

#### 【0050】

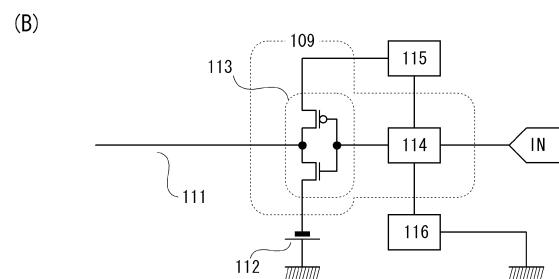

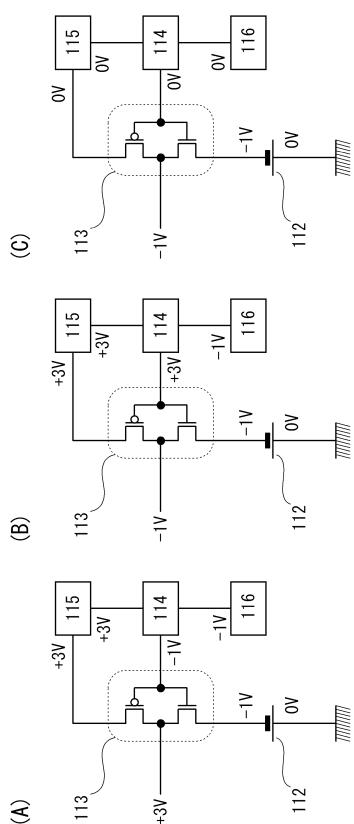

ビット線制御回路109の例を図1(B)に示す。ここに示すビット線制御回路109は、インバータ113と、制御信号発生回路114とを有する。制御信号発生回路114は、高電位電源115、低電位電源116が接続し、入力される信号INにより、それらのいずれかの電位をインバータ113の入力に与える。なお、高電位電源115、低電位電源116は半導体メモリ装置内に別に設けられたものを使用してもよいが、ビット線制御回路109内に設けてもよい。インバータ113のNチャネル型トランジスタのソースは電池112に接続される。以下の説明では、インバータ113のNチャネル型トランジスタのしきい値を+0.5V、Pチャネル型トランジスタのしきい値を-0.5Vとする。

#### 【0051】

50

ビット線制御回路 109 の動作の例について図 5 を用いて説明する。図 5 (A) は外部から電源が供給されている状態である。ここでは、高電位電源 115 の電位を +3V、低電位電源 116 の電位を -1V、電池 112 の負極の電位を -1V、正極の電位を 0V とする。また、制御信号発生回路 114 からは -1V の電位が出力されているため、インバータ 113 の入力電位は -1V、出力電位は +3V となる。したがって、ビット線制御線 111 に接続するビット線制御トランジスタ 108 はオン状態である。

#### 【0052】

何らかの状況の変化（例えば、外部からの電源の遮断や半導体メモリ装置の使用の終了）があった場合には、制御信号発生回路 114 は +3V の電位を出力する（図 5 (B) 参照）。そのため、インバータ 113 の入力電位は +3V、出力電位は -1V となり、ビット線制御線 111 に接続するビット線制御トランジスタ 108 のゲートの電位はソースの電位より 1V も低く、十分なオフ状態となる。

10

#### 【0053】

ビット線制御トランジスタ 108 が十分なオフ状態となると、列ドライバー 102 とビット線 104 は、ビット線制御トランジスタ 108 によって遮断され、ビット線 104 の電位を長期にわたり維持できる。

#### 【0054】

例えば、外部からの電源が遮断された場合には、しばらくすると図 5 (C) に示すように、高電位電源 115 の電位も低電位電源 116 の電位も 0V となり、結果として、制御信号発生回路 114 からの出力電位も 0V となる。しかし、その場合でも、インバータ 113 の出力電位は -1V であるため、ビット線制御トランジスタ 108 は十分なオフ状態を維持できる。

20

#### 【0055】

なお、インバータ 113 は、非動作時であっても、高電位側（高電位電源 115）と低電位側（電池 112）の間で微弱な電流（待機電流）が流れるが、その値は数 pA 以下とできる。本実施の形態では、1つの列ドライバー 102 に1つのインバータ（1つのビット線制御回路 109）を有するので、例えば、10年間の動作を保証するのであれば、0.1 μAh の容量があればよい。

#### 【0056】

なお、ここでは、インバータ 113 の出力の変動に伴って生じる貫通電流を考慮していないが、インバータ 113 の出力の極性は、記憶装置の稼動と非稼動との切り替えによってのみ変動するので、ほとんどの場合、1秒間に1度も変動せず、1時間に一度程度の変動を見込めばよい。したがって、貫通電流はほとんど考慮せずともよい。

30

#### 【0057】

さらに、ビット線制御回路 109 を多く設けて、例えば、1つの半導体メモリ装置に千個のビット線制御回路 109 を有したとしても、0.1 mA h の容量があればよい。この程度の容量の電池は通常の半導体チップに内蔵できる大きさである。なお、現実には、複数のビット線制御線 111 があったとしても、その動作は全て同じとしてよいので、1つの半導体メモリ装置には1つのビット線制御回路 109 を有すれば十分である。

#### 【0058】

40

なお、インバータの出力に接続する配線の電位を変動させるのに要する時間は配線の容量とインバータを構成するトランジスタのチャネル幅に依存する。インバータのトランジスタのチャネル幅が大きいほど、短時間で電位が変動するが、その分、待機電流も増加する。また、配線の容量が大きいほど時間がかかる。

#### 【0059】

複数のビット線制御線 111 を1つのインバータで制御する場合には、インバータに接続する配線の容量が大きく、かつ、インバータのトランジスタのチャネル幅が小さく、速度の低下が問題となるが、ビット線制御線 111 に与える電位の変動に要する時間（上記の例では +2V から -1V へ切り替わる時間）はメモリセルへの書き込み読み出しの時間に比べると百倍以上、場合によって1万倍以上長くても問題がない。そのため、インバータ

50

のトランジスタのチャネル幅が小さくても実用上の問題はない。そのように、チャネル幅の小さなトランジスタを用いると待機電流は十分に小さくできる。

#### 【0060】

##### (実施の形態2)

図3を用いて本実施の形態の半導体メモリ装置を説明する。図3に示される半導体メモリ装置は、ビット線104の途中にセンスアンプ117を有するものである。ビット線104を適切な長さに分割して、読み出しの際に現れるビット線容量（主としてビット線の寄生容量）を小さくし、読み出し精度をあげるためにこのようなセンスアンプ117が導入される。

#### 【0061】

10

このようにビット線104中にセンスアンプ117が挿入されていると、例えば、外部からの電源が遮断された際、ビット線104の電荷はセンスアンプ117を介しても流出することとなる。その結果、外部からの電源が遮断されると、センスアンプに接続するビット線104の電位は0Vとなってしまう。

#### 【0062】

したがって、センスアンプ117を挟んで、ビット線制御トランジスタを設けて、外部からの電源が遮断された際のビット線104からの電荷の流出を防止することが必要となる。

#### 【0063】

20

図3に示される半導体メモリ装置は、列ドライバー102と複数のワード線103と複数のビット線104とそれぞれのワード線103とビット線104の交点に設けられたメモリセル105とを有する。また、ビット線104には、センスアンプ117が挿入されている。

#### 【0064】

さらに、図3に示される半導体メモリ装置は、実施の形態1で示した半導体メモリ装置と同様に列ドライバー102とビット線104の間に挿入されたビット線制御トランジスタ108\_1を有する。ビット線制御トランジスタ108\_1のゲートはビット線制御線111\_1に接続する。ビット線制御線111\_1は実施の形態1のビット線制御回路109のようなビット線制御回路に接続される。

#### 【0065】

30

また、ビット線104に接続するセンスアンプ117と、センスアンプ117に最も近いビット線104に接続するメモリセル105の間にビット線制御トランジスタ108\_2、およびビット線制御トランジスタ108\_3を有する。ビット線制御トランジスタ108\_2、およびビット線制御トランジスタ108\_3のゲートは、それぞれ、ビット線制御線111\_2およびビット線制御線111\_3に接続する。ビット線制御線111\_2、ビット線制御線111\_3はビット線制御回路に接続される。なお、ビット線制御線111\_1、ビット線制御線111\_2、ビット線制御線111\_3は1つのビット線制御回路に接続してもよい。

#### 【0066】

40

このような半導体メモリ装置では、ビット線制御線111\_1乃至ビット線制御線111\_3は実施の形態1で示した場合と同様に状況に応じて電位が変動する。すなわち、半導体メモリ装置が外部より電源が供給されて半導体メモリ装置が使用できる状態にある場合には、ビット線制御線111\_1乃至ビット線制御線111\_3にはビット線制御トランジスタ108\_1乃至ビット線制御トランジスタ108\_3をオンとするような電位が与えられる。

#### 【0067】

また、外部からの電源が遮断された場合、あるいは、外部より電源が供給されている状態であっても半導体メモリ装置の使用が終了した場合には、ビット線制御線111\_1乃至ビット線制御線111\_3にはビット線制御トランジスタ108\_1乃至ビット線制御トランジスタ108\_3をオフとするような電位が与えられる。

50

**【 0 0 6 8 】**

例えば、外部からの電源が遮断された場合には、速やかにビット線制御線 1 1 1\_1 乃至ビット線制御線 1 1 1\_3 は 0 V 以下の十分な負の電位となり、ビット線制御トランジスタ 1 0 8\_1 乃至ビット線制御トランジスタ 1 0 8\_3 をオフとする。この結果、ビット線 1 0 4 は、ビット線制御トランジスタ 1 0 8\_1 乃至ビット線制御トランジスタ 1 0 8\_3 で分離され、列ドライバー 1 0 2、センスアンプ 1 1 7 に接続する部分の電位が 0 V となっても、その他の部分（メモリセル 1 0 5 が接続している部分）の電位は、適切な電位を維持することができる。

**【 0 0 6 9 】**

一方で、ワード線 1 0 3 の電位は 0 V であるので、メモリセルのセルトランジスタは十分に高抵抗であり、キャパシタに蓄積された電荷を長期にわたり維持できる。10

**【 0 0 7 0 】****（実施の形態 3）**

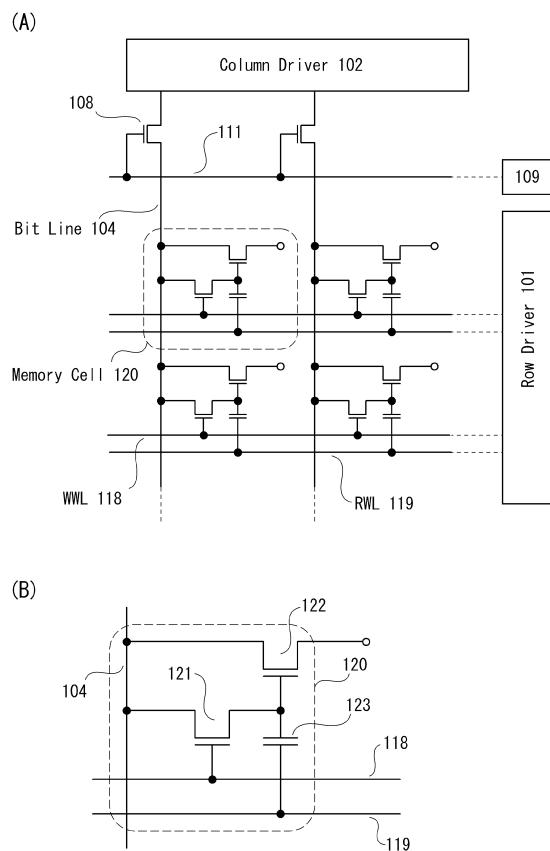

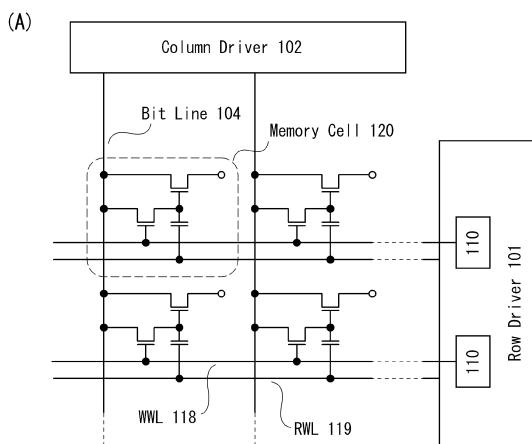

図 4 に示す半導体メモリ装置について説明する。図 4 に示す半導体メモリ装置のメモリセル 1 2 0 の構造は特許文献 4 に記載されているものと同等であり、その動作等については特許文献 4 を参照できる。

**【 0 0 7 1 】**

本実施の形態のメモリセル 1 2 0 は、図 4 (B) に示すように、書き込みトランジスタ 1 2 1 と読み出しトランジスタ 1 2 2 とキャパシタ 1 2 3 を有し、書き込みトランジスタ 1 2 1 のソースと読み出しトランジスタ 1 2 2 のソースはビット線 1 0 4 に接続し、書き込みトランジスタ 1 2 1 のゲートは書き込みワード線 1 1 8 に接続し、書き込みトランジスタ 1 2 1 のドレインと読み出しトランジスタ 1 2 2 のゲートがキャパシタ 1 2 3 の電極の一に接続し、キャパシタ 1 2 3 の電極の他は読み出しワード線 1 1 9 に接続する。20

**【 0 0 7 2 】**

書き込みワード線 1 1 8 と読み出しワード線 1 1 9 の電位は行ドライバー 1 0 1 で制御される。また、ビット線 1 0 4 の電位は列ドライバー 1 0 2 で制御される。

**【 0 0 7 3 】**

このように多くの点で違いが認められるが、実施の形態 1 あるいは実施の形態 2 のメモリセル 1 0 5 と本実施の形態のメモリセル 1 2 0 は、ビット線 1 0 4 に書き込みトランジスタ 1 2 1 (図 1 のメモリセル 1 0 5 のセルトランジスタ 1 0 6 に相当) のソースが接続し、書き込みトランジスタ 1 2 1 のドレインがキャパシタ 1 2 3 の電極の一に接続するという点では同じである。すなわち、データの保存に関しては、書き込みトランジスタ 1 2 1 がオフ状態で高い抵抗を示す必要がある。30

**【 0 0 7 4 】**

したがって、実施の形態 1 および実施の形態 2 で説明したのと同様に、ビット線 1 0 4 の電位を十分に高い値（例えば、+1 V 以上）とし、かつ、列ドライバー 1 0 2 とビット線 1 0 4 の間に挿入されたビット線制御トランジスタ 1 0 8 を設けることで、外部からの電源が遮断された場合でも書き込みトランジスタ 1 2 1 が十分に高い抵抗を実現できるようになる（図 4 (A) 参照）。ビット線制御トランジスタ 1 0 8 のゲートはビット線制御線 1 1 1 に接続する。ビット線制御線 1 1 1 は実施の形態 1 で示したようなビット線制御回路 1 0 9 に接続される。40

**【 0 0 7 5 】**

このような半導体メモリ装置では、ビット線制御線 1 1 1 は実施の形態 1 で示した場合と同様に状況に応じて電位が変動する。すなわち、半導体メモリ装置が外部より電源が供給されて半導体メモリ装置が使用できる状態にある場合には、ビット線制御線 1 1 1 にはビット線制御トランジスタ 1 0 8 をオンとするような電位が与えられる。

**【 0 0 7 6 】**

また、外部からの電源が遮断された場合、あるいは、外部より電源が供給されている状態であっても半導体メモリ装置の使用が終了した場合には、ビット線制御線 1 1 1 にはビット線制御トランジスタ 1 0 8 をオフとするような電位が与えられる。50

**【 0 0 7 7 】**

例えば、外部からの電源が遮断された場合には、ビット線制御線 111 は速やかに 0 V 以下の十分な負の電位（例えば、-1 V）となり、ビット線制御トランジスタ 108 をオフとする。この結果、ビット線 104 の電位は、適切な電位を維持することができる。

**【 0 0 7 8 】**

一方で、書き込みワード線 118 の電位は 0 V であるので、メモリセル 120 の書き込みトランジスタ 121 は十分に高抵抗であり、キャパシタ 123 に蓄積された電荷を長期にわたり維持できる。

**【 0 0 7 9 】**

メモリセル 120 はキャパシタ 123 の容量が小さくても読み出しトランジスタ 122 で信号を増幅してビット線に出力できるという特徴がある。しかし、キャパシタ 123 の容量が小さいということは、書き込みトランジスタ 121 のオフ状態での抵抗が十分に大きくないと必要な時間のデータの保持が困難であるということを意味する。したがって、電源遮断時に、ビット線制御トランジスタ 108 でビット線 104 の電位を適切な正の値を保持し、書き込みトランジスタ 121 のオフ状態での抵抗を高めることは本実施の形態では、特に効果を奏する。10

**【 0 0 8 0 】****( 実施の形態 4 )**

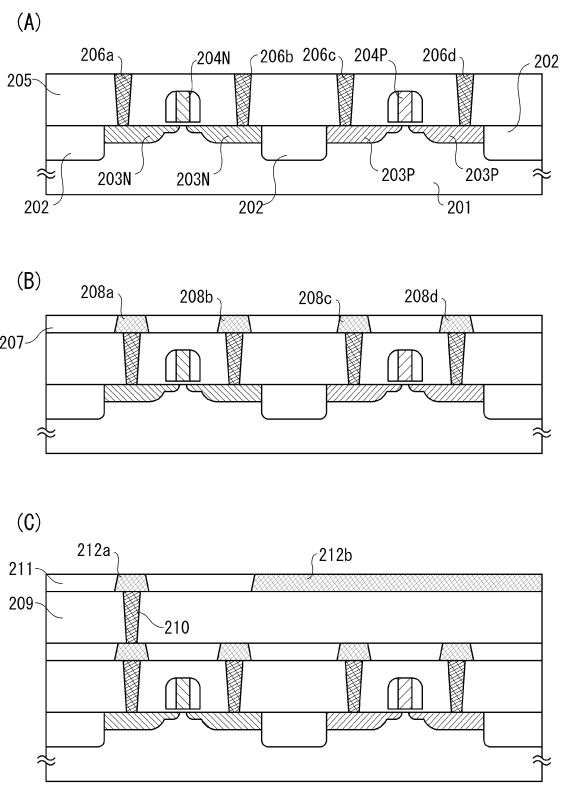

図 6 乃至図 8 を用いて、例えば、図 1 あるいは図 3 に示される半導体メモリ装置の作製工程について簡単に説明する。詳細は公知の半導体集積回路作製技術を参照するとよい。なお、図 6 乃至図 8 は、作製工程を概念的に説明するもので、特定の断面を表すものではない。20

**【 0 0 8 1 】****< 図 6 ( A ) >**

最初に、公知の半導体集積回路作製技術を用いて、半導体等の基板 201 表面に、素子分離絶縁物 202、N 型不純物領域 203N、P 型不純物領域 203P、N チャネル型トランジスタのゲート 204N、P チャネル型トランジスタのゲート 204P、第 1 層間絶縁物 205、第 1 コンタクトプラグ 206a 乃至第 1 コンタクトプラグ 206d 等を形成する。ここで、N チャネル型トランジスタや P チャネル型トランジスタは、半導体メモリ装置の行ドライバーや列ドライバー、ビット線制御回路、センスアンプ等に用いるとよい。30

**【 0 0 8 2 】****< 図 6 ( B ) >**

次に、第 1 層配線 208a 乃至第 1 層配線 208d を形成し、これを第 1 埋め込み絶縁物 207 に埋め込んだ形状とする。これらで図 1 の行ドライバー 101、列ドライバー 102、ビット線制御回路 109 あるいはセンスアンプ 117 等が形成される。

**【 0 0 8 3 】****< 図 6 ( C ) >**

さらに、第 2 層間絶縁物 209、第 2 コンタクトプラグ 210、第 2 埋め込み絶縁物 211、第 2 層配線 212a および第 2 層配線 212b を形成する。なお、第 2 層配線 212a および第 2 層配線 212b を含む層と第 1 層配線 208a 乃至第 1 層配線 208d を含む層の間に 1 層以上の別の配線を含む層を有してもよい。40

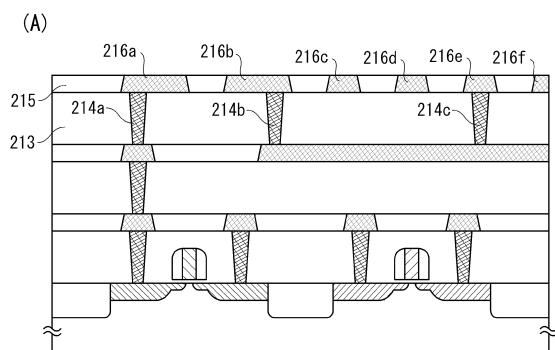

**【 0 0 8 4 】****< 図 7 ( A ) >**

さらに、第 3 層間絶縁物 213、第 3 コンタクトプラグ 214a 乃至第 3 コンタクトプラグ 214c、第 3 埋め込み絶縁物 215、第 3 層配線 216a 乃至第 3 層配線 216f を形成する。なお、第 1 コンタクトプラグ 206a、第 1 層配線 208a、第 2 コンタクトプラグ 210、第 2 層配線 212a、第 2 層配線 212b、第 3 コンタクトプラグ 214a、第 3 コンタクトプラグ 214b、第 3 层配線 216a、第 3 层配線 216b は、図 1 のビット線 104 の一部となる。

**【 0 0 8 5 】**1020304050

<図7(B)>

その後、酸化物半導体層217a、酸化物半導体層217bを形成し、これを覆って、ゲート絶縁物218を形成する。この際、ゲート絶縁物218の物理的な厚さが、酸化物半導体層217a、酸化物半導体層217bの物理的な厚さの2倍以上あると、酸化物半導体層217a、酸化物半導体層217bをゲート絶縁物218で確実に覆うことができ、配線間ショートを防止できるので好ましい。

【0086】

一方、ゲート絶縁物の実効的な厚さ（例えば酸化シリコン換算の厚さ）は酸化物半導体層217a、酸化物半導体層217bの実効的な厚さの1倍以下であることが好ましい。したがって、ゲート絶縁物218には、その誘電率が酸化物半導体層217a、酸化物半導体層217bの誘電率の2倍以上の材料を用いることが好ましい。10

【0087】

例えば、酸化ハフニウム、酸化タンタル、酸化ジルコニウム等の高誘電率材料を用いるとよい。また、酸化バリウム、酸化ストロンチウム、酸化カルシウム、酸化リチウム等、シリコン半導体とシリサイドを形成する材料であるため、シリコン半導体では使用することが避けられてきた材料であっても、酸化物半導体との間では問題が生じないこともあり、誘電率の高い材料であればゲート絶縁物218に用いることができる。

【0088】

さらに、第4層配線219a乃至第4層配線219dを形成する。ここで、第4層配線219aは図1のビット線制御トランジスタ108のゲートあるいはビット線制御線111に相当する。また、第4層配線219b乃至第4層配線219dは、図1のワード線103に相当する。20

【0089】

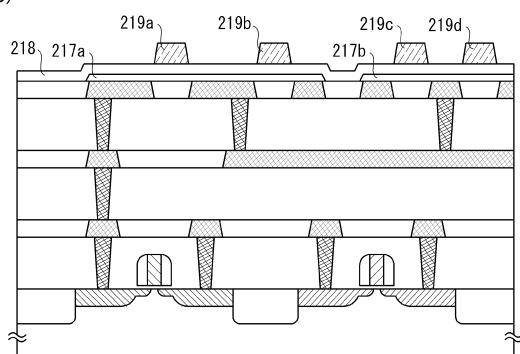

<図8参照>

公知のDRAMの作製技術を用いて、スタック型キャパシタを作製する。すなわち、第4層間絶縁物220、第4コントラクトプラグ221a、第4コントラクトプラグ221b等を形成し、その上に第5層間絶縁物222とキャパシタ電極223a、キャパシタ電極223b等を形成する。さらに、キャパシタ誘電体224とセルプレート225を形成する。このようにして半導体メモリ装置を作製できる。

【0090】

(実施の形態5)

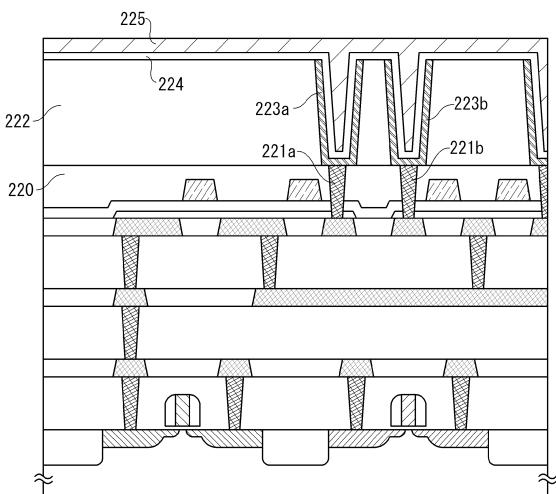

図9および図10を用いて、図4に示される半導体メモリ装置の作製工程について簡単に説明する。詳細は公知の半導体集積回路作製技術や特許文献2を参照するとよい。なお、図9および図10は、作製工程を概念的に説明するもので、特定の断面を表すものではない。

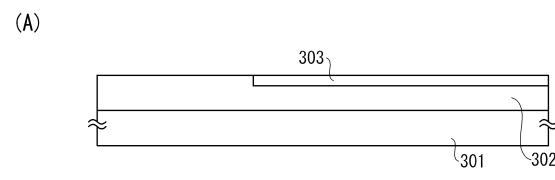

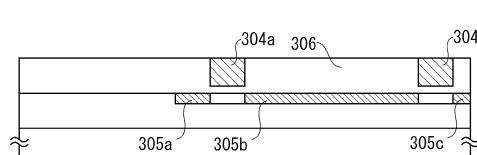

【0091】

<図9(A)>

最初に、公知の半導体集積回路作製技術を用いて、半導体等の基板301表面に、B0X層302、SOI層303を形成する。

【0092】

<図9(B)>

次に、読み出しゲート304aおよび読み出しゲート304bを形成し、これをマスクとして、SOI層303に不純物を注入し、不純物領域305a乃至不純物領域305cを形成する。読み出しゲート304aおよび読み出しゲート304bは図4の読み出しつトランジスタ122のゲートに相当する。さらに、第1層間絶縁物306を形成し、これを平坦化して、読み出しゲート304aおよび読み出しゲート304bの上面を露出させる。

【0093】

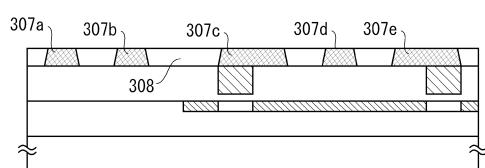

<図9(C)>

第1層配線307a乃至第1層配線307e、第1埋め込み絶縁物308を形成する。

【0094】

50

30

40

50

<図9(D)>

その後、酸化物半導体層309aおよび酸化物半導体層309bを形成し、これを覆って、ゲート絶縁物310を形成する。さらに、第2層配線311a乃至第2層配線311eを形成する。ここで、第2層配線311aは図4のピット線制御トランジスタ108のゲートあるいはピット線制御線111に相当する。また、第2層配線311c、第2層配線311dは図4の書き込みワード線118に相当し、第2層配線311b、第2層配線311eは、図4の読み出しワード線119に相当する。

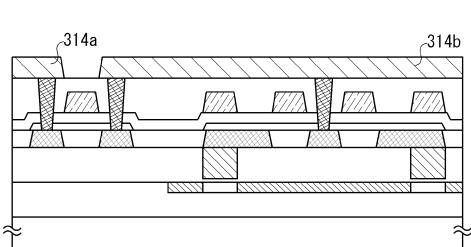

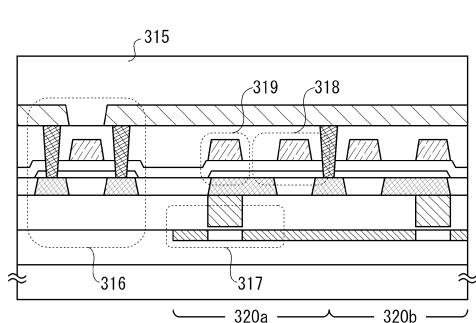

【0095】

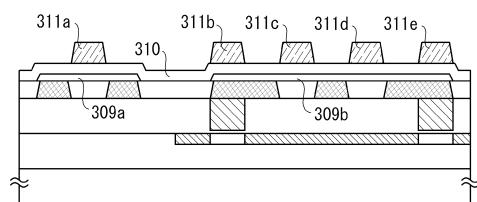

<図10(A)>

平坦な表面を持つ第2層間絶縁物312を形成し、さらに第1層配線307a、第1層配線307b、第1層配線307dに接続するコンタクトプラグ313a、コンタクトプラグ313b、コンタクトプラグ313cを形成する。

10

【0096】

<図10(B)>

第3層配線314aおよび第3層配線314bを形成する。第3層配線314aおよび第3層配線314bは図4(A)のピット線104に相当する。

【0097】

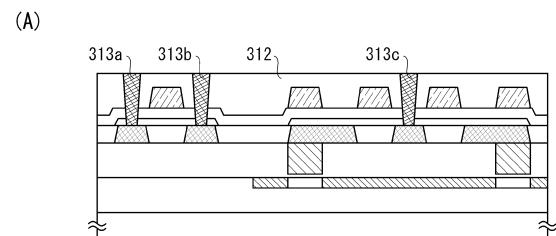

<図10(C)>

第3層間絶縁物315を形成する。さらに別の配線や層間絶縁物等を形成してもよい。以上の工程により、ピット線制御トランジスタ316、読み出しトランジスタ317、書き込みトランジスタ318、キャパシタ319を有する半導体メモリ装置が形成される。ピット線制御トランジスタ316は、図4(A)のピット線制御トランジスタ108に相当する。

20

【0098】

また、読み出しトランジスタ317、書き込みトランジスタ318、キャパシタ319は1つのメモリセルを形成する。読み出しトランジスタ317、書き込みトランジスタ318、キャパシタ319は、それぞれ、図4(B)の読み出しトランジスタ122、書き込みトランジスタ121、キャパシタ123に相当する。

【0099】

なお、図10(C)には、2つのメモリセル(メモリセル320a、メモリセル320b)が示されている。これらのメモリセルは同じピット線に接続するメモリセルである。

30

【0100】

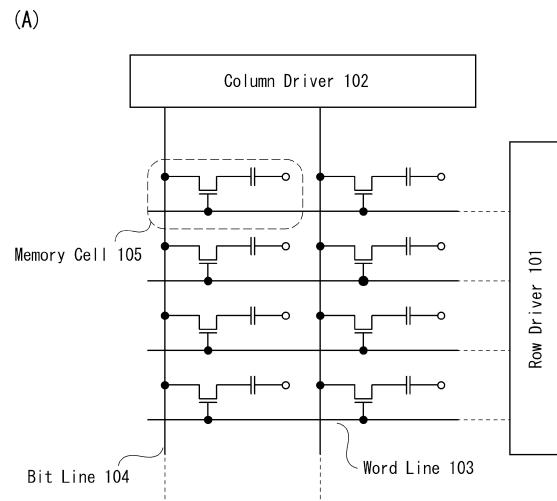

(実施の形態6)

本実施の形態では、図11(A)に示す半導体メモリ装置について説明する。図11(A)に示す半導体メモリ装置は、行ドライバー101、列ドライバー102、行ドライバー101に接続する複数のワード線103、列ドライバー102に接続する複数のピット線104、それぞれのワード線103とピット線104の交点に設けられるメモリセル105を有する。これらの構成は図2に示す従来のDRAMの構成と同様である。

【0101】

図11(A)に示す半導体メモリ装置では行ドライバー101にワード線出力回路110を設ける。ワード線出力回路110はワード線103に接続する。ワード線103はワード線出力回路110によって電位が設定される。ワード線103はメモリセル105が選択された場合には、高い電位となるが、それ以外の場合には低い電位(本実施の形態では十分な負の電位)となる。

40

【0102】

また、外部からの電源が遮断されたと検知した場合は、ワード線出力回路110はワード線103の電位を0V以下の十分な負の電位として、セルトランジスタをオフとする。

【0103】

ワード線出力回路110は、図1(B)に示すピット線制御回路109と同様な構成である。ピット線制御回路109の出力がピット線制御線111に接続されているのに対し、

50

ワード線出力回路 110 の出力はワード線 103 に接続されている。ワード線出力回路 110 の動作はビット線制御回路 109 と同様であり、図 5 を参照できる。

#### 【0104】

本実施の形態では、ワード線出力回路 110 は、1つのワード線 103 に1つ設ける。複数のワード線出力回路 110 と、電池 112、高電位電源 115 の接続関係を図 11 (B) に示す。この結果、電池 112 と高電位電源 115 の間には複数のインバータ 113 が並列に接続される。例えば、1つの半導体メモリ装置に 100 万本のワード線がある場合、電池 112 と高電位電源 115 の間に 100 万のインバータ 113 が並列に接続されることがある。

#### 【0105】

ビット線制御回路 109 と同様に、ワード線出力回路 110 でも非動作時であっても微弱な電流（待機電流）が流れるが、その値は1つのワード線出力回路 110 で数 pA 以下とできる。ただし、上記のように、ワード線出力回路 110 は電池 112 と高電位電源 115 の間に並列に設けられるので、ワード線の数が 100 万本あるとすると、10 年間で必要な電池の容量は 90 mA h 程度となる。

10

#### 【0106】

この点に関しては、ワード線出力回路 110 と高電位電源 115 の間に制御トランジスタ 124 を挿入するとよい。外部からの電源が供給されている状態では、制御トランジスタ 124 はオンであるが、外部からの電源が遮断されると、高電位電源 115 の電位が 0 V となることによりオフとなる。制御トランジスタ 124 は P チャネル型トランジスタを用いることができる。

20

#### 【0107】

ここで、制御トランジスタ 124 に求められるオン抵抗について説明する。制御トランジスタ 124 のオン抵抗が高いと、インバータ 113 の電位が低下するので、オン抵抗は低いことが好ましい。電位の低下は、例えば、高電位電源 115 と低電位電源 116 の電位差の 10 % 以下であることが望ましい。

#### 【0108】

ここで、外部より電源が供給されている状態では、制御トランジスタ 124 を流れる電流はワード線 103 の充放電に使用されるものがほとんどであるので、1つのワード線 103 の寄生容量とメモリ装置の応答速度から制御トランジスタ 124 を流れる電流を見積もることができる。ここで、すべてのワード線 103 の電位が常に変動しているわけではなく、電位が変動するワード線 103 はごく一部であることに注意する必要がある。

30

#### 【0109】

例えば、応答速度が 10 ナノ秒である半導体メモリ装置の場合、1 秒間にワード線 103 の電位の変動は半導体メモリ装置全体で 1 億回おこなわれる。1つのワード線 103 の寄生容量を 40 fF とすると、1 秒間に 4 μC の電荷が制御トランジスタ 124 を通過するので、制御トランジスタ 124 を流れる電流は 4 μA である。

#### 【0110】

この電流による電圧降下が 0.1 V 以下であるためには、制御トランジスタ 124 のオン抵抗は 25 kΩ 以下であればよい。これはインバータ 113 に用いられるものと同じサイズのトランジスタでも実現できるが、チャネル幅を 10 倍としたトランジスタであれば確実に実現できる。また、そのようなトランジスタではオフ抵抗は、インバータ 113 に用いられるトランジスタの 10 分の 1 (約 0.1 T = 1 × 10<sup>-11</sup> Ω) となる。

40

#### 【0111】

以上の議論で、半導体メモリ装置のメモリセル 105 の数（あるいはワード線 103 の数）ではなく、半導体メモリ装置の応答速度と1つのワード線 103 の容量により制御トランジスタ 124 のオン抵抗およびオフ抵抗が決定され、さらには電池 112 の容量が決定されることに注意したい。このことは半導体メモリ装置の応答速度が同じであれば、メモリセルの数が多くても少なくとも、電池 112 に要求される容量は同じであることを意味する。

50

**【0112】**

なお、インバータ113へ供給される電位を安定させるためには、制御トランジスタ124とインバータ113の間に1つの電極を接続するキャパシタ125を設けてよい。キャパシタ125の容量は1 pFより大きく、1 nF未満とするとよい。

**【0113】**

次に、このような制御トランジスタ124の効果について説明する。外部からの電源が遮断されている状態では、インバータは待機状態、制御トランジスタ124はオフ状態である。ここで、1つのインバータ113の待機状態での抵抗を1T<sub>1</sub>、制御トランジスタ124のオフ抵抗を0.1T<sub>1</sub>とする。

**【0114】**

インバータ113はワード線の数だけあり、それぞれ並列に接続されているので、ワード線の数を100万本とすると、インバータ113の合計の抵抗は1M<sub>1</sub>となる。高電位電源115から電池112との間の抵抗はインバータ113の合計の抵抗と制御トランジスタ124のオフ抵抗との合計となり、約0.1T<sub>1</sub>である。すなわち、抵抗のほとんどの部分は、制御トランジスタ124のオフ抵抗で占められる。

**【0115】**

制御トランジスタ124のソースとドレイン間の電位差が1Vであるので、電流は10 pAである。すなわち、10年間に必要な電池の容量は0.9 μAh程度となり、制御トランジスタ124を設けない場合(90 mAh)の10万分の1程度となる。

**【0116】**

なお、半導体回路の微細化にともなって、インバータ113を構成するトランジスタのサイズも極めて小さくなると、短チャネル効果によりオフ抵抗が十分に大きくできず、例えば、1n<sub>1</sub>程度にまで低下してしまうこともある。その場合、ワード線出力回路110全体のオフ抵抗(インバータ113の並列抵抗)は1k<sub>1</sub>まで低下してしまう。

**【0117】**

そのような場合には、制御トランジスタ124を設けることが効果的である。制御トランジスタ124は一つの半導体メモリ装置に少なくとも1つ設ければよいので、微細化は必要とされず、十分なオフ抵抗(0.1T<sub>1</sub>以上)を実現できる。上述の通り、外部からの電源が遮断された状態においては、電池112と高電位電源115との間の抵抗は実質的に制御トランジスタ124のオフ抵抗であるので、インバータ113の並列抵抗がいかに低くても影響しない。

**【0118】**

なお、これとは別に、書き換え読み出しに伴って、ワード線103の電位を変動させることによっても電力が消費される。消費される電力は、ワード線の寄生容量に依存する。1つのワード線103の寄生容量を40 fFとすると、ワード線103が100万本ある半導体メモリ装置では、ワード線全体の寄生容量は40 nFである。したがって、全てのワード線103の電位を+2Vから-1Vに変動させると、0.12 μCの負の電荷が電池112から流出する。

**【0119】**

したがって、全てのワード線の電位を+2Vから-1Vに変動させることを100億回おこなう(1つのワード線にあるメモリセルへの書き込み読み出しを100億回おこなう場合、1つのワード線にメモリセルが千個あるとすれば、1つのメモリセルあたり1000万回の書き込み読み出しをおこなうことに相当する)場合には、1.2 kCの電荷が必要である。これは電池の容量に換算すると330 mAh強であり、上記の10年間の保持のための容量より大きな値となる。

**【0120】**

したがって、電池112は書き込み読み出しの回数を想定した容量を有することが好ましい。あるいは、書き込み読み出し回数が限界に近づいた場合には、書き込み読み出しを制限するか、何らかの警報を発生するような構成とすることが望ましい。このような電池112は、半導体メモリ装置と同じパッケージ内やモジュール内に設けられていてよい。

10

20

30

40

50

**【 0 1 2 1 】**

なお、外部電源から電源が供給されている状態でワード線 103 の電位の変動がない場合、高電位電源 115 から電池 112 の間の抵抗はインバータ 113 の合計の抵抗 (1 M) と制御トランジスタ 124 のオン抵抗 (10 k) との合計となり、外部からの電源が遮断されている状態とは逆にインバータ 113 の合計の抵抗が支配的となり、比較的大きな電流が流れる。

**【 0 1 2 2 】**

半導体メモリ装置に外部より電源が供給されている期間を全体の 10 % とすれば、10 年間に必要な容量は、約 26 mA h である。しかしながら、回路の微細化と共に、インバータ 113 の抵抗が千分の 1 にまで低下した場合には、必要な容量は千倍となる。このような場合には、実施の形態 7 で示すような回路により、外部から電源が供給されている場合には、電池を消耗しないような構成とするとい。

10

**【 0 1 2 3 】**

なお、実施の形態 1 で説明したビット線制御回路 109 の最高出力電位は +3 V であったが、本実施の形態のワード線出力回路 110 はそれより低くできる。

**【 0 1 2 4 】**

例えば、ビット線 104 の電位の変動を 1 V とする場合、実施の形態 1 においては、最低電位が +1 V であるので、最高電位は +2 V となる。一方、ビット線制御トランジスタ 108 をオンとするには、+2 V よりしきい値 (+1 V) だけ高い電位をゲート (ビット線制御線) に与えることが必要であるため、ビット線制御回路 109 の最高出力電位は +3 V となる。

20

**【 0 1 2 5 】**

これに対し、本実施の形態においては、ビット線 104 を列ドライバーから分離する必要はないので、ビット線 104 の最低電位を 0 V とできる。ビット線 104 の電位の変動を 1 V とする場合、最高電位は +1 V となる。そして、セルトランジスタ 106 をオンとする場合には、+1 V よりしきい値 (+1 V) だけ高い電位をゲート (ワード線) に与えることが必要であるため、ワード線出力回路 110 の最高出力電位は +2 V となる。

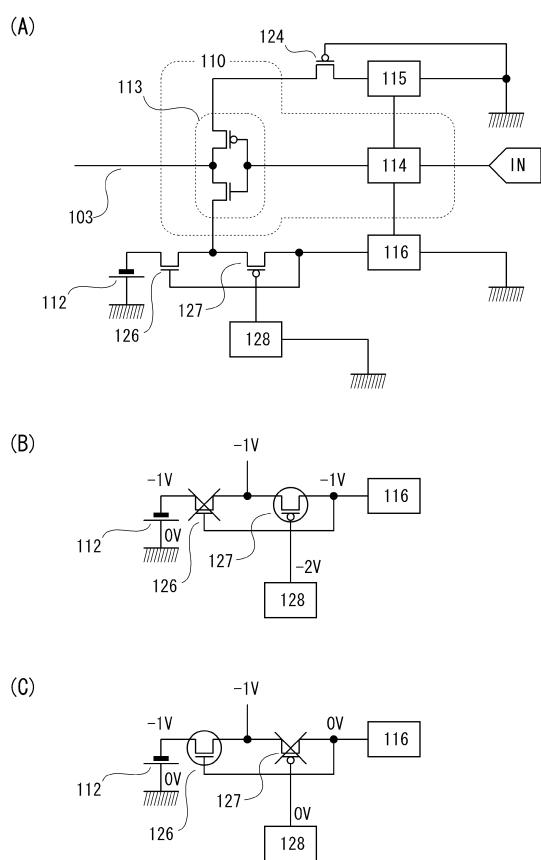

**【 0 1 2 6 】****( 実施の形態 7 )**

本実施の形態では、実施の形態 6 で説明した半導体メモリ装置の他の構成例について説明する。図 12 (A) には、ワード線出力回路 110 とそれに接続する回路や素子の回路例を示す。ここで、ワード線出力回路 110、電池 112、インバータ 113、制御信号発生回路 114、高電位電源 115、低電位電源 116、制御トランジスタ 124 は実施の形態 1 あるいは実施の形態 6 で説明したものと同様のものである。なお、制御トランジスタ 124 は設けなくともよい。

30

**【 0 1 2 7 】**

図 12 (A) に示す回路では、それらに加えて、制御トランジスタ 126、制御トランジスタ 127、超低電位電源 128 を有する。ここでは、制御トランジスタ 126 を N チャネル型、制御トランジスタ 127 を P チャネル型とする。

40

**【 0 1 2 8 】**

なお、実施の形態 6 で制御トランジスタ 124 に対しておこなったものと同様な議論より、制御トランジスタ 127 のオン抵抗 (すなわち、トランジスタのサイズ) も決定でき、例えば、チャネル幅をインバータ 113 に使用しているトランジスタの 10 倍とすればよい。

**【 0 1 2 9 】**

また、制御トランジスタ 126 は、外部からの電源が遮断されている状態においてオンとなることが求められ、オン抵抗はインバータ 113 の並列抵抗よりも十分に小さい (10 分の 1 以下) ことが求められるので、例えば、100 k 以下となるように設計する。これは、制御トランジスタ 124 や制御トランジスタ 127 に比べると十分に大きく、結果として、オフ抵抗も大きく (例えば、1 T 以上) できる。

50

**【 0 1 3 0 】**

なお、微細化の結果、インバータ 113 の並列抵抗が低下した場合には、制御トランジスタ 124、制御トランジスタ 126、制御トランジスタ 127 のオン抵抗もそれに応じて低下することが求められる。

**【 0 1 3 1 】**

制御トランジスタ 126 のドレインは電池 112 の負極に、ソースはインバータ 113 の N チャネル型トランジスタのソースに、ゲートは低電位電源 116 に接続される。また、制御トランジスタ 127 のドレインは低電位電源 116 に、ソースはインバータ 113 の N チャネル型トランジスタのソースに、ゲートは超低電位電源 128 に接続される。また、制御トランジスタ 124 のドレインは高電位電源 115 に、ソースはインバータ 113 の P チャネル型トランジスタのソースに接続され、ゲートは接地される。10

**【 0 1 3 2 】**

なお、制御トランジスタ 126 のゲートあるいは制御トランジスタ 124 のゲートは、上記で示した方法以外にも、他の適切な回路に接続されていてもよい。また、超低電位電源 128 は、外部より電源が供給されている場合には、低電位電源 116 よりも低い電位を出力するものとし、ここでは -2V の電位を出力する。

**【 0 1 3 3 】**

このような回路の動作について説明する。半導体メモリ装置に外部より電源が供給されている場合には、低電位電源 116 の出力電位は -1V、超低電位電源 128 の出力電位は -2V である。したがって、図 12 (B) に示すように、制御トランジスタ 127 はオンとなり、一方、制御トランジスタ 126 はオフとなる。すなわち、ワード線の電位を変動させるための電荷は、低電位電源 116 から供給される。20

**【 0 1 3 4 】**

なお、図 12 (B) には図示されていないが、半導体メモリ装置に外部より電源が供給されている場合には、制御トランジスタ 124 はオンであり、インバータ 113 の P チャネル型トランジスタのソースの電位は +2V である。

**【 0 1 3 5 】**

次に、外部からの電源が途絶すると、図 12 (C) に示すように、低電位電源 116 の出力電位、超低電位電源 128 の出力電位とも 0V となる。したがって、制御トランジスタ 127 はオフとなる。一方、制御トランジスタ 126 はオンとなる。このため、インバータ 113 の N チャネル型トランジスタのソースの電位は、外部からの電源が遮断された状況にあっても -1V が維持される。30

**【 0 1 3 6 】**

なお、実施の形態 6 で説明したように、図 12 (C) には図示されていないが、外部からの電源が遮断された場合には、制御トランジスタ 124 はオフとなる。

**【 0 1 3 7 】**

この状態でも、制御トランジスタ 126 およびインバータ 113 を介して高電位電源 115 ( 外部からの電源が遮断されている状態では電位は 0V ) と電池 112 ( 電位は -1V ) の間に微弱ながら電流が流れ、電池 112 が消耗する。

**【 0 1 3 8 】**

しかしながら、実施の形態 6 の場合と異なり、データの書き込みや読み出しの際には、電池 112 は使用されないので、電池 112 の消耗は実施の形態 6 よりも少ない。また、データの書き込みや読み出しの際には、電池 112 は使用されないので、データの書き込みや読み出しの回数に制約はない。40

**【 0 1 3 9 】**

加えて、外部から電源が供給されている場合には、電池 112 と高電位電源 115 の間の抵抗は、制御トランジスタ 124 のオン抵抗 ( 10k ) と、インバータ 113 の並列抵抗 ( 1M ) と制御トランジスタ 126 のオフ抵抗 ( 1T ) の合計であり、制御トランジスタ 126 のオフ抵抗が支配的である。

**【 0 1 4 0 】**

10

20

30

40

50

回路の微細化の結果、インバータ 113 の並列抵抗が千分の 1 となったとしても、電池 112 と高電位電源 115 間の抵抗はほとんど変化せず、したがって、実施の形態 6 の場合とは異なり、外部から電源が供給されている状態において、電池 112 の消耗はほとんどない。

#### 【 0141 】

制御トランジスタ 124 を設けない場合は 10 年間で必要な電池の容量は 90 mA h 程度である。実施の形態 6 で説明したように、制御トランジスタ 124 を設けるとより消費電力を低減でき、電池 112 に必要な容量を減らすことができる。

#### 【 0142 】

その他に、電池から制御トランジスタ 126 と制御トランジスタ 127 を介して低電位電源 116（外部からの電源が遮断されている状態では電位は 0 V）との間を流れる電流もある。この間の抵抗は、制御トランジスタ 126 のオン抵抗と制御トランジスタ 127 のオフ抵抗との合計であり、制御トランジスタ 127 のオフ抵抗を 0.1 T とすると、約 0.1 T である。この経路を流れる電流は、10 年間で 0.9 μ A h 程度である。

10

#### 【 0143 】

制御トランジスタ 127 を流れる電流と、制御トランジスタ 124 を流れる電流の総計は、10 年間で数 μ A h であり、例えば、半導体メモリ装置の形成されているチップ上に形成された固体電池や電気二重層キャパシタ等を電池 112 として利用できる。

#### 【 0144 】

##### ( 実施の形態 8 )

20

図 13 に示す半導体メモリ装置について説明する。図 13 に示す半導体メモリ装置のメモリセル 120 の構造は実施の形態 3 と同等であり、その動作等については特許文献 4 を参照できる。

#### 【 0145 】

本実施の形態のメモリセル 120 は、図 13 (B) に示すように、書き込みトランジスタ 121 と読み出しトランジスタ 122 とキャパシタ 123 を有し、書き込みトランジスタ 121 のソースと読み出しトランジスタ 122 のソースはビット線 104 に接続し、書き込みトランジスタ 121 のゲートは書き込みワード線 118 に接続し、書き込みトランジスタ 121 のドレインと読み出しトランジスタ 122 のゲートがキャパシタ 123 の電極の一に接続し、キャパシタ 123 の電極の他は読み出しワード線 119 に接続する。

30

#### 【 0146 】

書き込みワード線 118 と読み出しワード線 119 の電位は行ドライバー 101 で制御される。また、ビット線 104 の電位は列ドライバーで制御される。

#### 【 0147 】

このように多くの点で違いが認められるが、実施の形態 6 のメモリセル 105 と本実施の形態のメモリセル 120 は、ビット線 104 に書き込みトランジスタ 121 ( 図 11 (A) のメモリセル 105 のセルトランジスタ 106 に相当 ) のソースが接続し、書き込みトランジスタ 121 のドレインがキャパシタ 123 の電極の一に接続するという点では同じである。すなわち、データの保存に関しては、書き込みトランジスタ 121 がオフ状態で高い抵抗を示す必要がある。

40

#### 【 0148 】

したがって、実施の形態 6 で説明したのと同様に、行ドライバー 101 にワード線出力回路 110 を設けることで、外部からの電源が遮断された場合でも書き込みワード線 118 の電位を十分に低い負に保つようとする ( 図 13 (A) 参照 )。すなわち、外部からの電源が遮断された場合には、書き込みトランジスタ 121 を十分に高い抵抗とするように、書き込みワード線 118 を十分な負の電位とすることができます。

#### 【 0149 】

メモリセル 120 はキャパシタ 123 の容量が小さくても読み出しトランジスタ 122 で信号を增幅してビット線に出力できるという特徴がある。しかし、キャパシタ 123 の容量が小さいということは、書き込みトランジスタ 121 のオフ状態での抵抗が十分に大き

50

くないと必要な時間のデータの保持が困難であるということを意味する。したがって、電源遮断時に、書き込みワード線 118 の電位を十分な負の値とし、書き込みトランジスタ 121 の抵抗を高めることは効果を奏する。

### 【0150】

図13に示すメモリセルでは、書き込みワード線 118 の電位はデータを書き込む場合にのみ変動し、読み出しの際には変動させる必要はない。一般にデータの書き込みよりも読み出しの頻度の方が高いので、実施の形態6で示したメモリセルの場合よりワード線出力回路 110 に接続する電池の容量を小さくできる。なお、ワード線出力回路 110 に実施の形態7で説明した回路(図12(A))を用いてもよい。

### 【符号の説明】

10

### 【0151】

|      |                  |    |

|------|------------------|----|

| 101  | 行ドライバー           |    |

| 102  | 列ドライバー           |    |

| 103  | ワード線             |    |

| 104  | ビット線             |    |

| 105  | メモリセル            |    |

| 106  | セルトランジスタ         |    |

| 107  | キャパシタ            |    |

| 108  | ビット線制御トランジスタ     |    |

| 109  | ビット線制御回路         | 20 |

| 110  | ワード線出力回路         |    |

| 111  | ビット線制御線          |    |

| 112  | 電池               |    |

| 113  | インバータ            |    |

| 114  | 制御信号発生回路         |    |

| 115  | 高電位電源            |    |

| 116  | 低電位電源            |    |

| 117  | センスアンプ           |    |

| 118  | 書き込みワード線         |    |

| 119  | 読み出しワード線         | 30 |

| 120  | メモリセル            |    |

| 121  | 書き込みトランジスタ       |    |

| 122  | 読み出しトランジスタ       |    |

| 123  | キャパシタ            |    |

| 124  | 制御トランジスタ         |    |

| 125  | キャパシタ            |    |

| 126  | 制御トランジスタ         |    |

| 127  | 制御トランジスタ         |    |

| 128  | 超低電位電源           |    |

| 201  | 基板               | 40 |

| 202  | 素子分離絶縁物          |    |

| 203N | N型不純物領域          |    |

| 203P | P型不純物領域          |    |

| 204N | Nチャネル型トランジスタのゲート |    |

| 204P | Pチャネル型トランジスタのゲート |    |

| 205  | 第1層間絶縁物          |    |

| 206a | 第1コントラクトプラグ      |    |

| 206b | 第1コントラクトプラグ      |    |

| 206c | 第1コントラクトプラグ      |    |

| 206d | 第1コントラクトプラグ      | 50 |

|         |              |    |

|---------|--------------|----|

| 2 0 7   | 第 1 埋め込み絶縁物  |    |

| 2 0 8 a | 第 1 層配線      |    |

| 2 0 8 b | 第 1 層配線      |    |

| 2 0 8 c | 第 1 層配線      |    |

| 2 0 8 d | 第 1 层配線      |    |

| 2 0 9   | 第 2 層間絶縁物    |    |

| 2 1 0   | 第 2 コンタクトプラグ |    |

| 2 1 1   | 第 2 埋め込み絶縁物  |    |

| 2 1 2 a | 第 2 層配線      | 10 |

| 2 1 2 b | 第 2 层配線      |    |

| 2 1 3   | 第 3 層間絶縁物    |    |

| 2 1 4 a | 第 3 コンタクトプラグ |    |

| 2 1 4 b | 第 3 コンタクトプラグ |    |

| 2 1 4 c | 第 3 コンタクトプラグ |    |

| 2 1 5   | 第 3 埋め込み絶縁物  |    |

| 2 1 6 a | 第 3 層配線      |    |

| 2 1 6 b | 第 3 层配線      |    |

| 2 1 6 c | 第 3 層配線      |    |

| 2 1 6 d | 第 3 层配線      |    |

| 2 1 6 e | 第 3 層配線      | 20 |

| 2 1 6 f | 第 3 层配線      |    |

| 2 1 7 a | 酸化物半導体層      |    |

| 2 1 7 b | 酸化物半導体層      |    |

| 2 1 8   | ゲート絶縁物       |    |

| 2 1 9 a | 第 4 層配線      |    |

| 2 1 9 b | 第 4 层配線      |    |

| 2 1 9 c | 第 4 層配線      |    |

| 2 1 9 d | 第 4 层配線      |    |

| 2 2 0   | 第 4 層間絶縁物    |    |

| 2 2 1 a | 第 4 コンタクトプラグ | 30 |

| 2 2 1 b | 第 4 コンタクトプラグ |    |

| 2 2 2   | 第 5 層間絶縁物    |    |

| 2 2 3 a | キャパシタ電極      |    |

| 2 2 3 b | キャパシタ電極      |    |

| 2 2 4   | キャパシタ誘電体     |    |

| 2 2 5   | セルプレート       |    |

| 3 0 1   | 基板           |    |

| 3 0 2   | B O X 層      |    |

| 3 0 3   | S O I 層      |    |

| 3 0 4 a | 読み出しゲート      | 40 |

| 3 0 4 b | 読み出しゲート      |    |

| 3 0 5 a | 不純物領域        |    |

| 3 0 5 b | 不純物領域        |    |

| 3 0 5 c | 不純物領域        |    |

| 3 0 6   | 第 1 層間絶縁物    |    |

| 3 0 7 a | 第 1 層配線      |    |

| 3 0 7 b | 第 1 层配線      |    |

| 3 0 7 c | 第 1 层配線      |    |

| 3 0 7 d | 第 1 層配線      |    |

| 3 0 7 e | 第 1 层配線      | 50 |

|         |              |    |

|---------|--------------|----|

| 3 0 8   | 第1埋め込み絶縁物    |    |

| 3 0 9 a | 酸化物半導体層      |    |

| 3 0 9 b | 酸化物半導体層      |    |

| 3 1 0   | ゲート絶縁物       |    |

| 3 1 1 a | 第2層配線        |    |

| 3 1 1 b | 第2層配線        |    |

| 3 1 1 c | 第2層配線        |    |

| 3 1 1 d | 第2層配線        |    |

| 3 1 1 e | 第2層配線        |    |

| 3 1 2   | 第2層間絶縁物      | 10 |

| 3 1 3 a | コントラクトプラグ    |    |

| 3 1 3 b | コントラクトプラグ    |    |

| 3 1 3 c | コントラクトプラグ    |    |

| 3 1 4 a | 第3層配線        |    |

| 3 1 4 b | 第3層配線        |    |

| 3 1 5   | 第3層間絶縁物      |    |

| 3 1 6   | ピット線制御トランジスタ |    |

| 3 1 7   | 読み出しトランジスタ   |    |

| 3 1 8   | 書き込みトランジスタ   |    |

| 3 1 9   | キャパシタ        | 20 |

| 3 2 0 a | メモリセル        |    |

| 3 2 0 b | メモリセル        |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(B)

【図8】

【図9】

(B)

(C)

(D)

【図10】

(B)

(C)

【図11】

【図12】

【図13】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 27/10 3 2 1

(56)参考文献 特開平11-96754 (JP, A)

米国特許第5796650 (US, A)

特開2001-297583 (JP, A)

米国特許第6469952 (US, B1)

特開2013-16247 (JP, A)

米国特許出願公開第2012/0314482 (US, A1)

(58)調査した分野(Int.Cl., DB名)

G 1 1 C 1 1 / 4 0 7

G 1 1 C 1 1 / 4 0 5

H 0 1 L 2 1 / 8 2 4 2

H 0 1 L 2 7 / 1 0 8

H 0 1 L 2 9 / 7 8 6