(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5008223号

(P5008223)

(45) 発行日 平成24年8月22日(2012.8.22)

(24) 登録日 平成24年6月8日(2012.6.8)

(51) Int.Cl.

F 1

|             |              |                  |      |       |       |

|-------------|--------------|------------------|------|-------|-------|

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20  | 623 E |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G02F | 1/133 | 510   |

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G02F | 1/133 | 550   |

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/30  | J     |

|             |              |                  | G09G | 3/36  |       |

請求項の数 6 (全 36 頁)

(21) 出願番号 特願2001-20078 (P2001-20078)

(22) 出願日 平成13年1月29日 (2001.1.29)

(65) 公開番号 特開2001-290457 (P2001-290457A)

(43) 公開日 平成13年10月19日 (2001.10.19)

審査請求日 平成19年12月28日 (2007.12.28)

(31) 優先権主張番号 特願2000-22536 (P2000-22536)

(32) 優先日 平成12年1月31日 (2000.1.31)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 浅見 宗広

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 佐野 潤一

最終頁に続く

(54) 【発明の名称】アクティブマトリクス型表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のソース信号線を駆動するソース信号線駆動回路と、複数のゲート信号線を駆動するゲート信号線駆動回路と、前記複数のソース信号線と前記複数のゲート信号線とが交差する各領域に設けられた複数の画素電極と、前記複数の画素電極をそれぞれ駆動するための複数のスイッチング素子と、を有するアクティブマトリクス型表示装置であって、

前記ソース信号線駆動回路は、複数のD/A変換回路と、複数のソース線選択回路と、を有し、

前記複数のD/A変換回路はデジタル映像信号をアナログ映像信号に変換する機能を有し、

前記複数のD/A変換回路は、階調電源線と電気的に接続され、

前記階調電源線は、RGBに対応した電源電圧を出力するため、基準の電圧の最大値と、基準の電圧の最小値とを供給する機能を有し、前記基準の電圧の最大値は、前記RGBに対応して異なり、

前記複数のD/A変換回路はそれぞれ前記複数のソース線選択回路のいずれか一を介して、前記RGBに対応した3の倍数本の前記ソース信号線に電気的に接続され、

前記デジタル映像信号が前記複数のD/A変換回路に入力するタイミングに同期して、前記複数のソース線選択回路がそれぞれ前記複数のソース信号線のうち前記デジタル映像信号に対応するソース信号線を選択し、前記選択されたソース信号線へ前記複数のD/A変換回路から出力される前記アナログ映像信号が書き込まれ、

第1、第2および第3の期間に分割された1ゲート線選択期間を有し、前記第1の期間には、前記RGBのうち第1の色に対応する前記電源電圧が前記階調電源線に印加され、同時に前記ソース線選択回路はそれぞれ前記第1の色に対応する1本或いは複数本の前記ソース信号線を選択し前記複数のD/A変換回路のいずれか一と電気的に接続させ、

前記第2の期間には、前記RGBのうち第2の色に対応する前記電源電圧が前記階調電源線に印加され、同時に前記ソース線選択回路はそれぞれ前記第2の色に対応する1本或いは複数本の前記ソース信号線を選択し前記複数のD/A変換回路のいずれか一と電気的に接続させ、

前記第3の期間には、前記RGBのうち第3の色に対応する前記電源電圧が前記階調電源線に印加され、同時に前記ソース線選択回路はそれぞれ前記第3の色に対応する1本或いは複数本の前記ソース信号線を選択し前記複数のD/A変換回路のいずれか一と電気的に接続させることを特徴とするアクティブマトリクス型表示装置。

### 【請求項2】

複数のソース信号線を駆動するソース信号線駆動回路と、複数のゲート信号線を駆動するゲート信号線駆動回路と、前記複数のソース信号線と前記複数のゲート信号線とが交差する各領域に設けられた複数の画素電極と、前記複数の画素電極をそれぞれ駆動するための複数のスイッチング素子と、を有するアクティブマトリクス型表示装置であって、

前記ソース信号線駆動回路は、複数のD/A変換回路と、複数のソース線選択回路と、を有し、

前記複数のD/A変換回路はデジタル映像信号をアナログ映像信号に変換する機能を有し、

前記複数のD/A変換回路は、階調電源線と電気的に接続され、前記階調電源線は、RGBに対応した電源電圧を出力するため、基準の電圧の最大値と、基準の電圧の最小値とを供給する機能を有し、前記基準の電圧の最大値は、前記RGBに対応して異なり、

前記複数のD/A変換回路はそれぞれ前記複数のソース線選択回路のいずれか一を介して、前記RGBに対応した3の倍数本の前記ソース信号線に電気的に接続され、

前記デジタル映像信号が前記複数のD/A変換回路に入力するタイミングに同期して、前記複数のソース線選択回路がそれぞれ前記複数のソース信号線のうち前記デジタル映像信号に対応するソース信号線を選択し、前記選択されたソース信号線へ前記複数のD/A変換回路から出力される前記アナログ映像信号が書き込まれ、

第1、第2および第3の期間に分割された1ゲート線選択期間を有し、

前記第1の期間には、前記RGBのうち第1の色に対応する前記電源電圧が前記階調電源線に印加され、同時に前記ソース線選択回路はそれぞれ前記第1の色に対応する1本或いは複数本の前記ソース信号線を選択し前記複数のD/A変換回路のいずれか一と電気的に接続させ、

前記第2の期間には、前記RGBのうち第2の色に対応する前記電源電圧が前記階調電源線に印加され、同時に前記ソース線選択回路はそれぞれ前記第2の色に対応する1本或いは複数本の前記ソース信号線を選択し前記複数のD/A変換回路のいずれか一と電気的に接続させ、

前記第3の期間には、前記RGBのうち第3の色に対応する前記電源電圧が前記階調電源線に印加され、同時に前記ソース線選択回路はそれぞれ前記第3の色に対応する1本或いは複数本の前記ソース信号線を選択し前記複数のD/A変換回路のいずれか一と電気的に接続させ、

前記ソース信号線駆動回路は、前記複数のD/A変換回路とそれ電気的に接続された複数のP/S変換回路を有し、

前記複数のP/S変換回路はそれぞれ前記第1の期間には、前記第1の色に対応するソース信号線に対する映像信号を出力し、

前記第2の期間には、前記第2の色に対応するソース信号線に対する映像信号を出力し

10

20

30

40

50

前記第3の期間には、前記第3の色に対応するソース信号線に対する映像信号を出力することを特徴とするアクティブマトリクス型表示装置。

【請求項3】

請求項1又は請求項2において、

前記ソース信号線駆動回路は、前記複数のD/A変換回路とそれ電気的に接続された複数のP/S変換回路を有し、

前記複数のP/S変換回路へ入力される選択信号によって、前記複数のソース線選択回路が制御されることを特徴とするアクティブマトリクス型表示装置。

【請求項4】

10

請求項3において、

前記複数のソース線選択回路には、前記選択信号と、前記選択信号の反転信号が入力されることを特徴とするアクティブマトリクス型表示装置。

【請求項5】

請求項1乃至請求項4のいずれか一において、

前記1ゲート線選択期間に、前記複数のソース線選択回路はそれ電気的に接続され、

前記複数のD/A変換回路に接続されるソース信号線は、前記RGBについて同色に対応しており、

前記階調電源線には、前記同色に対応したソース信号線に対応する色を表示するための前記電源電圧が印加されることを特徴とするアクティブマトリクス型表示装置。

20

【請求項6】

請求項5において、

前記複数のD/A変換回路はそれぞれ前記複数のソース線選択回路のいずれか一を介して、6以上で3の倍数本の前記ソース信号線に接続され、

前記1ゲート線選択期間における前記複数のD/A変換回路ではそれ電気的に接続され、

前記複数のD/A変換回路に接続されるソース信号線は、前記RGBについて同色に対応した前記ソース信号線が連続して選択されていることを特徴とするアクティブマトリクス型表示装置。

【発明の詳細な説明】

【0001】

30

【発明の属する技術分野】

【0002】

本発明は、マトリクス状に配置されたスイッチング素子と画素により映像などの情報の表示をおこなうカラー画像表示装置（アクティブマトリクス型カラー画像表示装置）、特にデジタル方式の駆動方法およびそれを用いた画像表示装置、電子機器に関する。

【0003】

【従来の技術】

最近安価なガラス基板上に半導体薄膜を形成した半導体装置、例えば薄膜トランジスタ（TFT）を作製する技術が急速に発達してきている。その理由は、アクティブマトリクス型画像表示装置の需要が高まってきたことによる。

40

【0004】

アクティブマトリクス型画像表示装置には、表示素子に液晶を用いるアクティブマトリクス型液晶表示装置やエレクトロルミネッセンス（EL）素子を用いるEL表示装置などがある。以下では、アクティブマトリクス型画像表示装置の代表的な例として、アクティブマトリクス型液晶表示装置を例にとって説明する。

【0005】

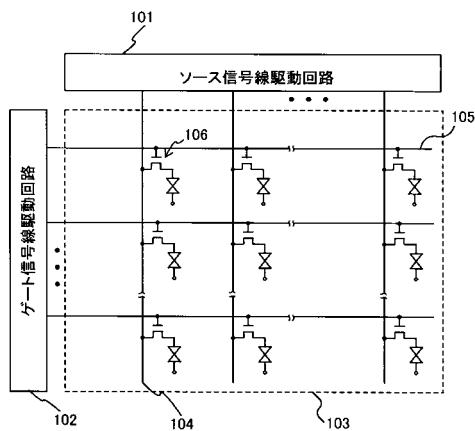

アクティブマトリクス型液晶表示装置は、図30に示すように、ソース信号線駆動回路101と、ゲート信号線駆動回路102と、マトリクス状に配置された画素アレイ部103とを有している。ソース信号線駆動回路101は、クロック信号等のタイミング信号に同期して、入力された映像信号をサンプリングし各ソース信号線104にデータを書き込む

50

。ゲート信号線駆動回路 102 は、クロック信号等のタイミングに同期して、ゲート信号線 105 を順次選択し、画素アレイ部 103 の各画素内にあるスイッチング素子である TFT (画素 TFT) 106 のオン・オフを制御するようになっている。これにより、各ソース信号線 104 に書き込まれたデータが順次各画素に書き込まれることになる。

#### 【0006】

ソース信号線駆動回路の駆動方式としては、アナログ方式とデジタル方式があるが、高精細・高速駆動が可能なデジタル方式のアクティブマトリクス型液晶表示装置が注目されてきている。

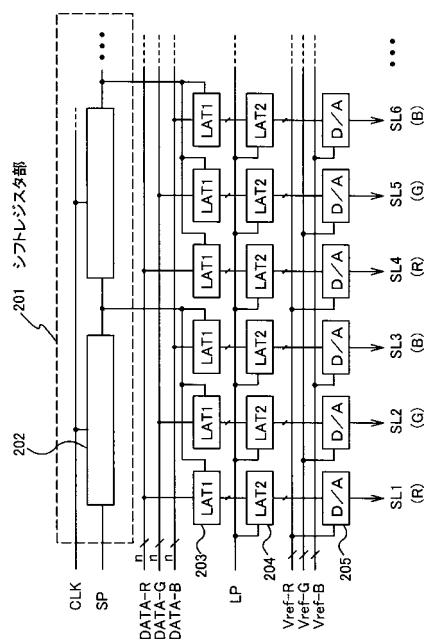

#### 【0007】

従来のデジタル方式のソース信号線駆動回路を図 31 に示す。図 31 において、201 はシフトレジスタ部を示し、フリップフロップ回路などを含むシフトレジスタ基本回路 202 から構成される。シフトレジスタ部 201 へスタートパルス SP が入力されるとクロック信号 CLK に同期してサンプリングパルスが順次ラッチ 1 回路 203 (LAT1) へ送出される。

#### 【0008】

ラッチ 1 回路 203 (LAT1) では、シフトレジスタ部からのサンプリングパルスに同期して、データバスライン (DATA R, DATA G, DATA B) から供給される n ピット (n は自然数) のデジタル映像信号を順次記憶する。

#### 【0009】

一水平画素分の信号が LAT1 部へ書き込まれた後、各ラッチ 1 回路 203 (LAT1) に保持されているデジタル映像信号は、ラッチ信号バスライン (LP) から供給されるラッチパルスに同期してラッチ 2 回路 204 (LAT2) に一斉に転送される。

#### 【0010】

デジタル映像信号がラッチ 2 回路 204 (LAT2) に保持されると、再びスタートパルス (SP) が入力され、次行の画素分のデジタル映像信号が LAT1 部へ新たに書き込まれる。この間、LAT2 部へは、前行の画素分のデジタル映像信号が記憶されておりデジタル / アナログ信号変換回路 (以降、D/A 変換回路と記す) 205 (D/A) によって、デジタル映像信号に対応したアナログ映像信号が各ソース信号線に書き込まれる。図 31 において、Vref-R, Vref-G, Vref-B は、それぞれ R (赤)、G (緑)、B (青) の各色に対応した D/A 変換回路 205 に接続される階調電源線を示す。また、SL1, SL2, … 等は番号付けしたソース信号線を、SL1 等の下に記した R, G, B はそれぞれ赤、緑、青を示し、単板でカラー表示可能な表示装置を想定している。

#### 【0011】

図 31 に示した各 D/A 変換回路 205 はそれぞれ 1 本のソース信号線と接続され、その 1 本のソース信号線にアナログ映像信号を書き込む。しかし、高解像度、高精細の液晶表示装置を作成する場合、大きな面積を占める D/A 変換回路をソース信号線と同数作ることは近年望まれている液晶表示装置の小型化の妨げとなっており、1 つの D/A 変換回路で複数のソース信号線を駆動する方法が特開平 11-167373 で提案されている。

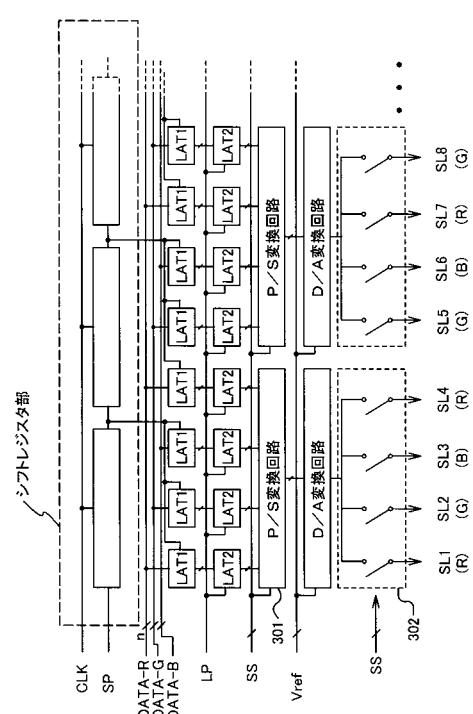

#### 【0012】

1 つの D/A 変換回路で 4 本のソース信号線を駆動するソース信号線駆動回路の構成例を図 32 に示す。図 31 と比較して判るように図 32 にはパラレル / シリアル変換回路 301 (P/S 変換回路)、ソース線選択回路 302 とそれらに入力される選択信号 (SS) が新たに追加されている。このような回路が追加されるにもかかわらず、4 本のソース信号線に 1 つの D/A 変換回路で信号の書き込みができるれば、必要な D/A 変換回路数が 1/4 で済む効果は大きく、ソース信号線駆動回路の占有面積を小さくすることが可能となる。

#### 【0013】

##### 【発明が解決しようとする課題】

図 31 においては、RGB 用に独立な 3 系統の階調電源線がソース信号線駆動回路に供給されている。しかし、図 32 に示したソース信号線駆動回路には、図 31 と異なり 1 系統

10

20

30

40

50

の階調電源線のみが供給されている。一般に、階調電源線の電源電圧が与えられれば、D/A変換回路の出力電圧範囲は一意に決まる。従って、1系統の階調電源線が供給されている図32のソース信号線駆動回路は、各ソース信号線に書き込まれる電圧範囲はRGBの区別なく同じになる。

#### 【0014】

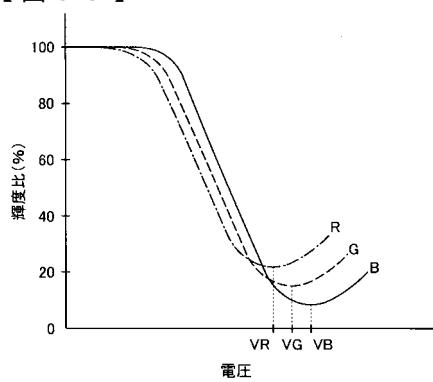

さて、液晶表示装置の輝度比の液晶印加電圧依存性は、RGB各色で全く同じというわけではなく、図33に示す例のように色によって異なる。この例では、輝度比が極小値をとる電圧値がRGBそれぞれに対してVR、(<)VG、(<)VBと異なる。従って、液晶に電圧を印加していったときに階調表現の単調性が失われないためには、液晶に印加できる最大電圧はRGBそれぞれに対してVR、VG、VBとなる。しかし、図32のような1系統の階調電源線しか供給されない場合、前述のように液晶に印加できる電圧範囲はRGBの区別なく一様になるので、図33の輝度比電圧特性を持った液晶に対しては、印加できる最大電圧がVRとなる。この時、GやBが十分に暗の状態にならず、コントラストが低くなるばかりか、正確な色彩の表現性に乏しくなってしまう問題が生じる。10

#### 【0015】

以上の理由から、図31に示したように階調電源線もRGB独立に3系統供給するなどして、液晶の印加電圧をRGB独立に制御できるようにすることが望ましい。

#### 【0016】

しかし、上記の3系統の階調電源線を供給する方法で、1つのD/A変換回路で複数のソース信号線を駆動する場合では、階調電源線の本数が増加するばかりか、それら階調電源線の1つとD/A変換回路との接続切り替えをおこなうスイッチが必要になる。これらは、外部入力ピン数の増加や、階調電源線を配線する領域や上記の追加するスイッチ等による駆動回路の占有面積の増加など新たな問題を生じさせる。これでは、1つのD/A変換回路で複数のソース信号線を駆動し、駆動回路の占有面積を減少させるメリットがなくなってしまう。20

#### 【0017】

そこで本発明は、これらの問題を解決する駆動方法を提供するものである。

#### 【0018】

##### 【課題を解決するための手段】

ソース信号線駆動回路に供給される階調電源線は1系統のみとし、各D/A変換回路はRGBに対応した3本のソース信号線を単位としてその倍数本のソース信号線に対しアナログ映像信号を書き込む。また、1水平書き込み期間内に階調電源線の電源電圧も変化させる。各ソース線選択回路がRGB各色に対応したソース信号線を選択する期間を同期させ、階調電源線に印加する電源電圧は、Rのソース信号線が選択されている期間にはRに対応した電源電圧を、Gのソース信号線が選択されている期間にはGに対応した電源電圧を、Bのソース信号線が選択されている期間にはBに対応した電源電圧をそれぞれ印加する。30

#### 【0019】

こうすることで、外部入力ピン数の増加や、駆動回路の占有面積の増加を招くことなく画素電極の電圧をRGB独立に制御することを可能にする。40

#### 【0020】

##### 【発明の実施の形態】

以下、本発明の実施の形態について、図面を参照しながら説明する。

#### 【0021】

##### 【実施形態】

本実施形態では、1系統の階調電源線がソース信号線駆動回路に供給され、各D/A変換回路がそれぞれRGBに対応する3本のソース信号線を駆動する方法について説明する。

#### 【0022】

また、本実施形態では、RGB各色それぞれ( $n+1$ )ビット( $n$ は自然数)のデジタル映像信号入力に対応する場合を例にとって説明する。50

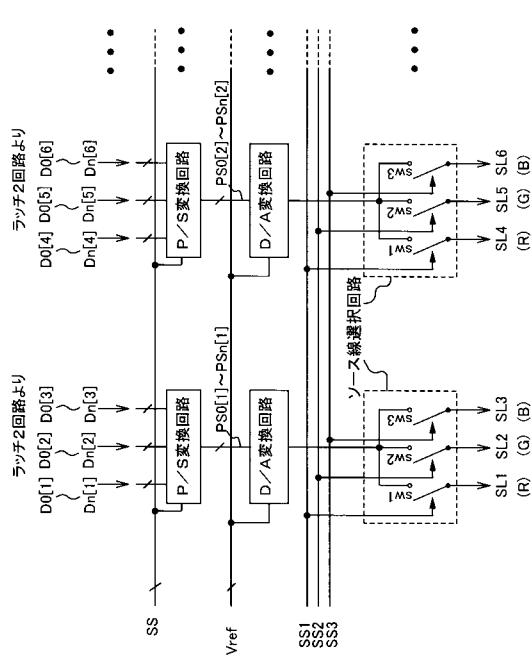

## 【0023】

図1には本実施形態の概略回路図が示されている。図1では、デジタル映像信号を順次サンプリングするためのサンプリングパルスを発生させるシフトレジスタ部、前記サンプリングパルスによりデジタル映像信号をラッチするラッチ1回路部、そして、ラッチパルスの入力により前記ラッチ1回路部に記憶されていたデジタル映像信号を一齊にラッチするラッチ2回路部は図示せず省略した。パラレル/シリアル変換回路(P/S変換回路)は、ラッチ2回路のパラレルな出力データ( $D_0[3k+1] \sim D_n[3k+1]$ 、 $D_0[3k+2] \sim D_n[3k+2]$ 、 $D_0[3k+3] \sim D_n[3k+3]$ (kは0以上の整数))をピット信号毎にまとめシリアルデータに変換する。ここで、 $D_0[3k+1]$ は第( $3k+1$ )ソース信号線に対する最下位(第1)ピット(LSB)のデジタル映像信号を示し、 $D_n[3k+1]$ は同じく第( $3k+1$ )ソース信号線に対する最上位(第( $n+1$ ))ピット(MSB)のデジタル映像信号を示す。以降、表記 $D_1[s]$ は第sソース信号線に対する第( $1+1$ )ピットのデジタル映像信号を示すものとする。また、第( $3k+1$ )ソース信号線はRを、第( $3k+2$ )ソース信号線はGを、第( $3k+3$ )ソース信号線はBをそれぞれ表示するためのソース信号線とする。

## 【0024】

ソース線選択回路は3つのスイッチ $s_w1$ 、 $s_w2$ 、 $s_w3$ から成り、 $s_w1$ がオンすると第( $3k+1$ )番目のソース信号線(Rを担当するソース信号線)が、 $s_w2$ がオンすると第( $3k+2$ )番目のソース信号線(Gを担当するソース信号線)が、 $s_w3$ がオンすると第( $3k+3$ )番目のソース信号線(Bを担当するソース信号線)がそれぞれ各D/A変換回路の出力と接続される。 $SS_1 \sim SS_3$ はそれぞれ $s_w1 \sim s_w3$ のオン・オフを制御する選択信号である。

## 【0025】

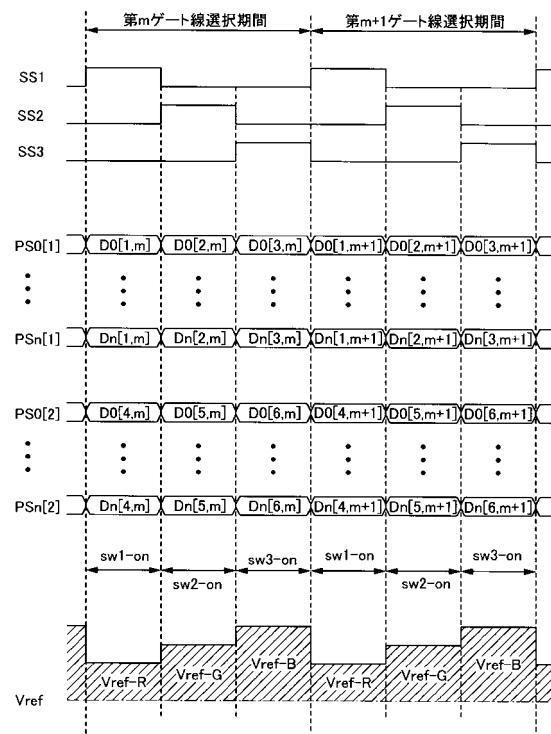

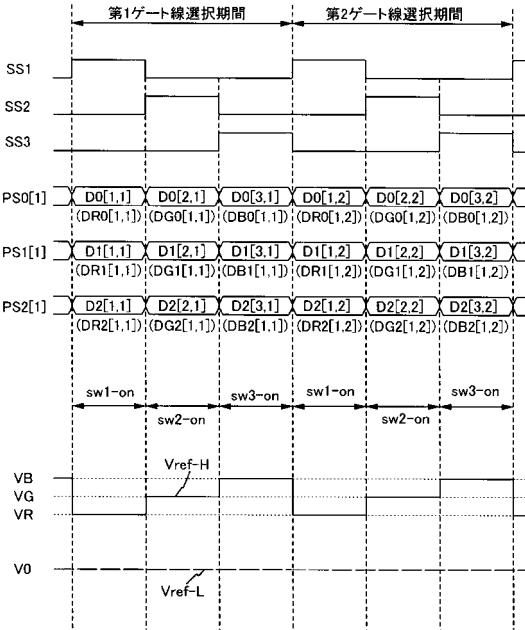

図1の駆動回路に対する信号動作タイミングを図2に示す。1ゲート線選択期間を3つに分割し、第1番目の期間に選択信号 $SS_1$ をHiレベルにし $s_w1$ をオンし、第2番目の期間に選択信号 $SS_2$ をHiレベルにし $s_w2$ をオンし、第3番目の期間に選択信号 $SS_3$ をHiレベルにし $s_w3$ をオンする動作を示す。なお、各P/S変換回路の出力信号( $PS_0[k] \sim PS_n[k]$ )は、上記の選択信号( $SS_1 \sim SS_3$ )と同期させ、1ゲート線選択期間を3分割した、その第1番目の期間には第( $3k+1$ )ソース信号線に対するデジタル映像信号を出力し、第2番目の期間には第( $3k+2$ )ソース信号線に対するデジタル映像信号を出力し、第3番目の期間には第( $3k+3$ )ソース信号線に対するデジタル映像信号を出力するようにP/S変換回路に入力される選択信号 $SS$ により制御する。こうすることで、各ソース信号線に対応したデジタル映像信号が適切なソース信号線の書き込みに反映される。この様子を、図2の $PS_0[1] \sim PS_n[1]$ 、 $PS_0[2] \sim PS_n[2]$ に示した。ここでは、 $PS_1[k]$ は第k段目のP/S変換回路の第( $1+1$ )ピット目の出力信号を示す。従って、 $PS_1[k]$ は、 $D_1[3k-2]$ 、 $D_1[3k-1]$ 、 $D_1[3k]$ のデジタル映像信号から構成される。また、図2において、 $D_1[s, g]$ は第s列第g行の画素に対する第( $1+1$ )ピット目のデジタル映像信号を示し、表記 $D_1[s]$ にあらわにゲート信号線の情報を附加したものである。

## 【0026】

つぎに、階調電源線 $V_{ref}$ への電源電圧の入力方法を図2の $V_{ref}$ に示す。図中、 $V_{ref-R}$ 、 $V_{ref-G}$ 、 $V_{ref-B}$ は、それぞれR、G、Bの各色に対応した階調電源線の電源電圧を印加することを示す。1ゲート線選択期間を3つに分割した第1番目の期間には、ソース線選択回路により第( $3k+1$ )番目のソース信号線(Rを担当するソース信号線)が選択されているので、Rを表示するための電源電圧が階調電源線に印加される。同様に、1ゲート線選択期間を3つに分割した第2、第3番目の期間にはそれぞれG、Bを表示するための電源電圧がそれぞれ階調電源線に印加される。

## 【0027】

以上、本実施形態により、1つのD/A変換回路でRGBの3本のソース信号線を駆動する形態において、1系統のみの階調電源線がソース信号線駆動回路に供給された場合であ

10

20

30

40

50

つても、画素電極の電圧を R G B 独立に制御することが可能となる。なお、本実施形態では、1つの D / A 変換回路で R G B の 3 本のソース信号線を駆動する場合を例に挙げているが、本発明はこれに限定されるものではなく、3 本、6 本、・・・といった 3 の倍数本のソース信号線を1つの D / A 変換回路で駆動する場合にも適用され得る。また、ソース線選択回路がソース信号線を選択する順序は、本実施形態のように R、G、B の順に限定されるものではなく、他の順序でもよい。さらに、本実施形態では、パラレル / シリアル変換回路 ( P / S 変換回路 ) を用いたが、本発明はこの有無に限定されない。すなわち、本発明は D / A 変換回路に 1 ゲート線選択期間、複数のソース信号線に対するデジタル映像信号をシリアル入力するいかなる方法に対しても適用され得る。

【 0 0 2 8 】

10

## 【実施例】

ここで、本発明の実施例について、図面を参照しながら説明する。ただし、本発明は、以下の実施例に限定されるわけではない。

【 0 0 2 9 】

## [ 実施例 1 ]

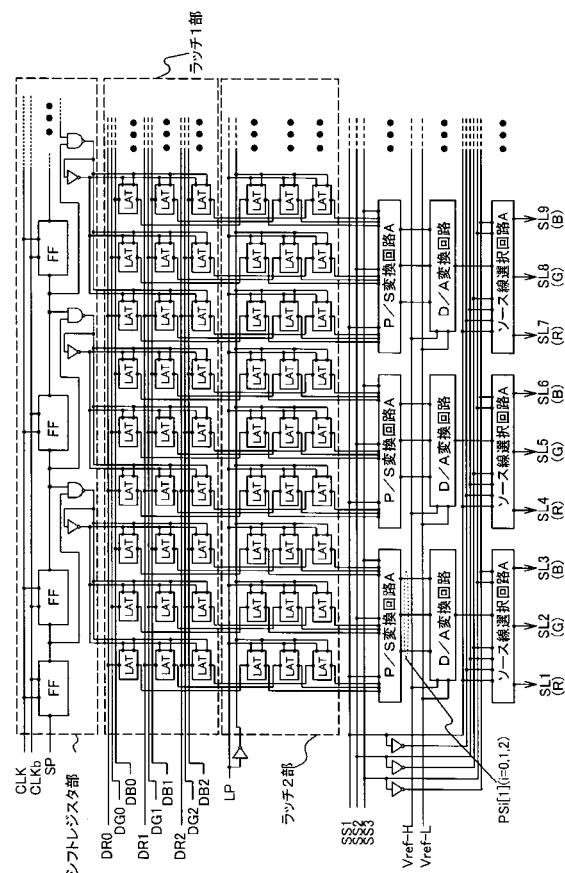

本実施例では、アクティブマトリクス型画像表示装置に本発明を適用した例を示す。アクティブマトリクス型画像表示装置は、従来例で示したようにソース信号線駆動回路、ゲート信号線駆動回路、マトリクス状に配置された画素アレイ部とから構成されている。ゲート信号線駆動回路と画素アレイ部の動作は従来例と同じなので、本実施例ではソース信号線駆動回路について説明する。また、図 3 に示すように、本実施例では、R G B 各色に対するデジタル映像信号は 3 ビットとし、1 つの D / A 変換回路で R G B の 3 本のソース信号線を駆動する場合を例に説明する。

20

【 0 0 3 0 】

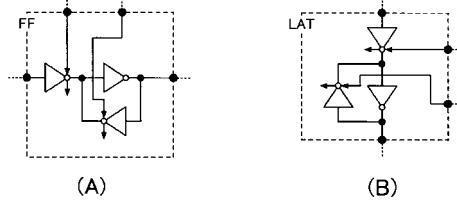

シフトレジスタ部は、フリップフロップ回路 ( F F ) 、 N A N D 回路、およびインバータ回路を有し、クロック信号 ( C L K ) 、前記クロック信号の反転クロック信号 ( C L K b ) およびスタートパルス ( S P ) が入力される。図 4 ( A ) に示すように、フリップフロップ回路 ( F F ) はクロックドインバータ回路、インバータ回路で構成されている。

【 0 0 3 1 】

スタートパルス ( S P ) が入力されると、クロック信号 ( C L K 、 C L K b ) に同期してサンプリングパルスが順次シフトしていく。

30

【 0 0 3 2 】

記憶回路であるラッチ 1 部とラッチ 2 部は、基本ラッチ回路 ( L A T ) から構成されている。基本ラッチ回路を図 4 ( B ) に示す。基本ラッチ回路 ( L A T ) はクロックドインバータ回路とインバータ回路で構成されている。ラッチ 1 部へは R、G、B、各 3 ビットのデジタル映像信号 ( D R 0 、 D R 1 、 D R 2 、 D G 0 、 D G 1 、 D G 2 、 D B 0 、 D B 1 、 D B 2 ) が入力され、シフトレジスタ部からのサンプリングパルスによって、デジタル映像信号をラッチする。ラッチ 2 部は、水平帰線期間に入力されるラッチパルス ( L P ) によって、ラッチ 1 部に保持されていたデジタル映像信号を一斉にラッチすると同時に下流の回路に情報を伝達する。この時、ラッチ 2 部には 1 水平書き込み期間データが保持される。

40

【 0 0 3 3 】

なお、図 4 ( A ) および ( B ) において、各クロックドインバータ回路の P チャネル型トランジスタへのクロック入力端子の接続が省略されているが、実際は N チャネル型トランジスタへのクロック入力端子に入力されている制御信号の反転信号が入力される。また、本実施例ではフリップフロップ回路 ( F F ) と基本ラッチ回路 ( L A T ) は同じ回路構成をしているが、異なる回路構成であってもよい。

【 0 0 3 4 】

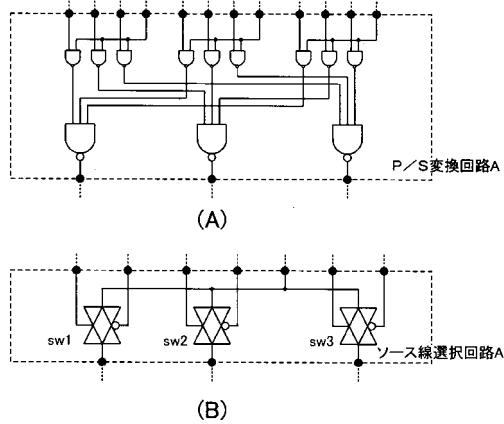

パラレル / シリアル変換回路 ( 図 3 では P / S 変換回路 A とした ) へは、3 ( ビット数 ) × 3 ( R G B で 3 本のソース信号線分 ) のラッチ 2 部に記憶されているデジタル映像信号と、選択信号 ( S S 1 ~ S S 3 ) が入力される。図 5 ( A ) に示すように、P / S 変換回

50

路 A は N A N D 回路から構成されている。

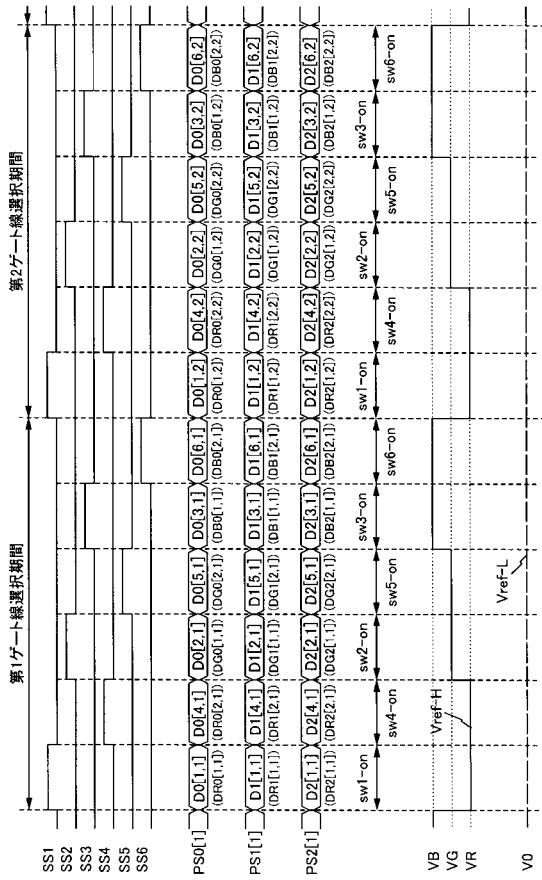

#### 【0035】

図 7 に、第 1 ~ 第 3 ソース信号線 ( S L 1 ~ S L 3 ) に関する P / S 変換回路 A に注目した信号動作タイミングを示す。1 ゲート線選択期間を 3 つに分割し、第 1 番目の期間に選択信号 ( S S 1 ) を H i レベルにし、第 1 ソース信号線 ( S L 1 ) に対するデジタル映像信号を D / A 変換回路に出力する。第 2 番目の期間は、選択信号 ( S S 2 ) を H i レベルにし、第 2 ソース信号線 ( S L 2 ) に対するデジタル映像信号を D / A 変換回路に出力する。第 3 番目の期間は、選択信号 ( S S 3 ) を H i レベルにし、第 3 ソース信号線 ( S L 3 ) に対するデジタル映像信号を D / A 変換回路に出力する。この様子を、図 7 の P S 0 [ 1 ] ~ P S 2 [ 1 ] に示した。ここで、P S 1 [ 1 ] は、第 1 ~ 第 3 ソース信号線 ( S L 1 ~ S L 3 ) に関する P / S 変換回路 A の第 ( 1 + 1 ) ビット目の出力データである。また、前述したように D 1 [ s , g ] は第 s 列第 g 行の画素に対する第 ( 1 + 1 ) ビット目のデジタル映像信号を示している。ここで、R G B で区別した D R 1 、 D G 1 、 D B 1 ( 1 = 0 ~ 2 ) や D 1 [ s ] ( 1 = 0 ~ 2 ) には以下の関係がある。

$$D R 1 [ s ] = D 1 [ 3 s - 2 ] \quad ( 1 = 0 ~ 2 )$$

$$D G 1 [ s ] = D 1 [ 3 s - 1 ] \quad ( 1 = 0 ~ 2 )$$

$$D B 1 [ s ] = D 1 [ 3 s ] \quad ( 1 = 0 ~ 2 )$$

また、 D R 1 [ s ] などの表記にゲート信号線の情報を付加したもの D R 1 [ s , g ] などと表記する。

#### 【0036】

上記と同様な動作は他のソース信号線 ( S L 4 ~ S L 6 、 S L 7 ~ S L 9 、 ...) に関する P / S 変換回路 A でも並行しておこなわれる。

#### 【0037】

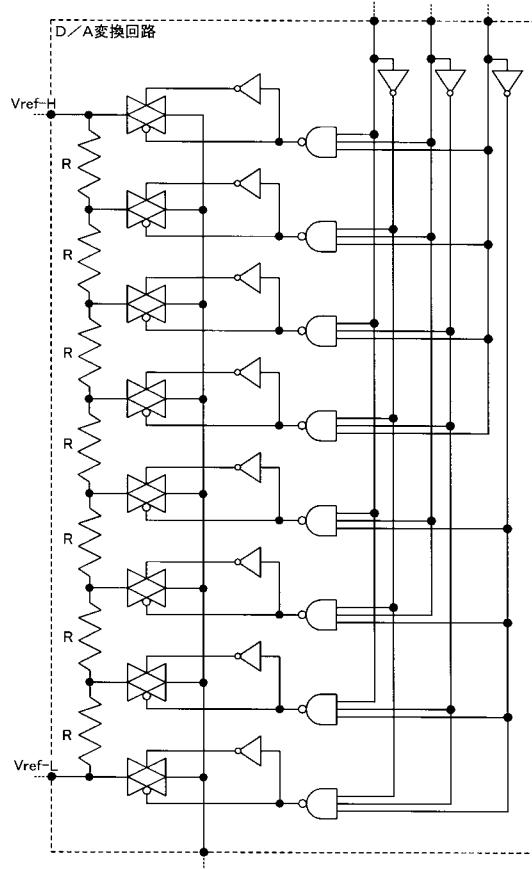

D / A 変換回路の回路構成例を図 6 に示す。図 6 は抵抗ストリング型の D / A 変換回路であり、ある電圧範囲の出力を得るために 2 本の階調電源線を供給する必要がある。図 6 では、これらを V r e f - L 、 V r e f - H と示した。これらの階調電源電圧を抵抗で分圧し、3 ビットのデジタル映像信号に対応した電圧値を出力する。

#### 【0038】

D / A 変換回路の出力は、ソース線選択回路 A を介して適切なソース信号線に接続される。ソース線選択回路 A の回路構成例を図 5 ( B ) に示す。ソース線選択回路 A は 3 つのトランスマッショングート ( スイッチ ) からなり、各ゲートへ選択信号 ( S S 1 ~ S S 3 ) とそれらの反転信号が入力される。図 7 の信号動作タイミングに従えば、1 ゲート線選択期間を 3 つに分割した、第 1 番目の期間にはスイッチ s w 1 をオンし R の第 1 ソース信号線 ( S L 1 ) へ D / A 変換回路の出力を書きこむ。第 2 番目の期間にはスイッチ s w 2 をオンし G の第 2 ソース信号線 ( S L 2 ) へ D / A 変換回路の出力を書きこむ。最後の、第 3 番目の期間にはスイッチ s w 3 をオンし B の第 3 ソース信号線 ( S L 3 ) へ D / A 変換回路の出力を書きこむ。

#### 【0039】

このような書き込みは他のソース信号線に対しても並行しておこなわれる。そして、各ソース信号線に書き込まれたデータは、ゲート信号線駆動回路と画素 T F T との働きにより順次各画素に書き込まれることになる。

#### 【0040】

本実施例では、2 本の階調電源線 V r e f - L 、 V r e f - H のうち、 V r e f - L は R G B 各色について同一電圧として V 0 とし、 V r e f - H は R G B についてそれぞれ V R 、 V G 、 V B とした。1 ゲート線選択期間に階調電源線の電源電圧を変化させる様子は図 7 に示されている。R のソース信号線がソース線選択回路に選択されている期間は、 R に対応する電源電圧が印加され、 G のソース信号線がソース線選択回路に選択されている期間は、 G に対応する電源電圧が印加され、 B のソース信号線がソース線選択回路に選択されている期間は、 B に対応する電源電圧が印加される。

#### 【0041】

10

20

30

40

50

以上の駆動方法により、1つのD/A変換回路で3本のソース信号線を駆動する場合、ソース信号線駆動回路に供給される階調電源線が1系統のみであっても、画素に印加する電圧をRGB独立に制御することができる。

#### 【0042】

なお、本実施例においてソース信号線駆動回路に供給される回路駆動電源は1系統を仮定したが、2系統以上とし必要な部分にレベルシフタ回路を挿入してもよい。また、本実施例では階調電源線Vref-Lの電源電圧はRGBに対して同一としたが、異なっていてもよい。

#### 【0043】

##### [実施例2]

10

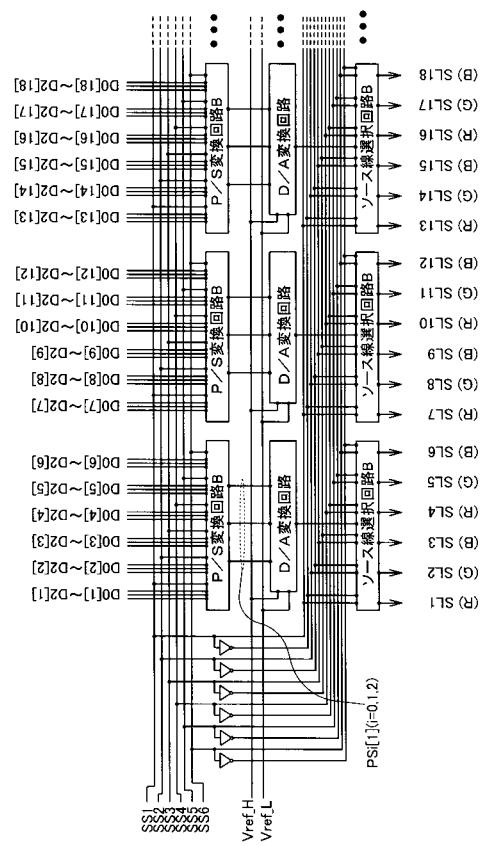

本実施例でも、実施例1と同様にアクティブマトリクス型画像表示装置に本発明を適用した例を示すが、実施例1と異なり1つのD/A変換回路で6本(RGB×2)のソース信号線を駆動する例を説明する。本実施例でも主にソース信号線駆動回路について説明する。シフトレジスタ部、ラッチ1部、ラッチ2部については実施例1と同じとし、以下ではそれらの説明を省略する。本実施例におけるラッチ2回路より下流の回路構成例を図8に示す。また、本実施例でも、RGB各色に対するデジタル映像信号は3ビットとする。

#### 【0044】

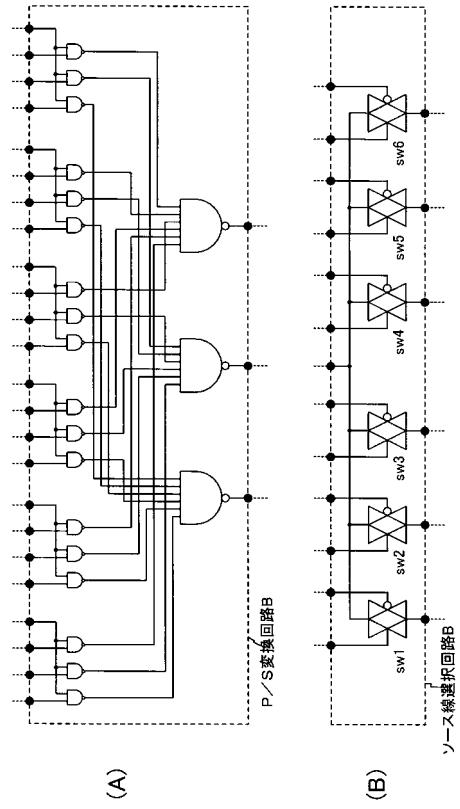

パラレル/シリアル変換回路(図8ではP/S変換回路Bとした)へは、3(ビット数)×6(RGB×2で6本のソース信号線分)のラッチ2部に記憶されているデジタル映像信号と、選択信号(SS1～SS6)が入力される。図9(A)に示すように、P/S変換回路BはNAND回路から構成されている。

20

#### 【0045】

図10に、第1～第6ソース信号線(SL1～SL6)に関わるP/S変換回路Bに注目した信号動作タイミングを示す。1ゲート線選択期間を6つに分割した、それぞれの期間毎に6つの選択信号SS1、SS4、SS2、SS5、SS3、SS6がこの順序でHiレベルになるように入力される。こうしてP/S変換回路Bは、ソース信号線SL1(R)、SL4(R)、SL2(G)、SL5(G)、SL3(B)、SL6(B)に対応するデジタル映像信号をこの順序でD/A変換回路に出力する。この様子を、図10のPS0[1]～PS2[1]に示した。ここで、PS1[1]は、第1～第6ソース信号線(SL1～SL6)に関わるP/S変換回路Bの第(1+1)ビット目の出力データである。また、前述したようにD1[s、g]は第s列第g行の画素に対する第(1+1)ビット目のデジタル映像信号を示している。ここで、RGBで区別したDR1、DG1、DB1(1=0～2)やD1[s](1=0～2)にも以下の関係が成立する。

30

$$DR1[s] = D1[3s - 2] \quad (1 = 0 \sim 2)$$

$$DG1[s] = D1[3s - 1] \quad (1 = 0 \sim 2)$$

$$DB1[s] = D1[3s] \quad (1 = 0 \sim 2)$$

また、DR1[s]などの表記にゲート信号線の情報を附加したものをDR1[s、g]などと表記する。

#### 【0046】

上記と同様な動作は他のソース信号線(SL7～SL12、SL13～SL18、...)に関わるP/S変換回路Bでも並行しておこなわれる。

40

#### 【0047】

D/A変換回路は実施例1と同じで図6に示されるものとする。

#### 【0048】

D/A変換回路の出力は、ソース線選択回路Bを介して適切なソース信号線に接続される。ソース線選択回路Bの回路構成例を図9(B)に示す。ソース線選択回路Bは6つのトランスマッシュゲート(スイッチ)からなり、各ゲートへ選択信号(SS1～SS6)とそれらの反転信号が入力される。図10の信号動作タイミングに従えば、1ゲート線選択期間を6つに分割した、その各期間に6つの選択信号SS1、SS4、SS2、SS5、SS3、SS6がこの順序でHiレベルになる。これにより、ソース線選択回路B内の

50

スイッチは s w 1、s w 4、s w 2、s w 5、s w 3、s w 6 の順にオンし、ソース信号線 S L 1 ( R )、S L 4 ( R )、S L 2 ( G )、S L 5 ( G )、S L 3 ( B )、S L 6 ( B ) をこの順序で D / A 変換回路と接続し各ソース信号線への書き込みをおこなう。

#### 【 0 0 4 9 】

このような書き込みは他のソース信号線に対しても並行しておこなわれる。そして、各ソース信号線に書き込まれたデータは、ゲート信号線駆動回路と画素 T F T との働きにより順次各画素に書き込まれることになる。

#### 【 0 0 5 0 】

本実施例でも、2 本の階調電源線 V r e f - L、V r e f - H のうち、V r e f - L は R G B 各色について同一電圧 V 0 とし、V r e f - H は R G B についてそれぞれ V R、V G 、V B とした。1 ゲート線選択期間に階調電源線の電源電圧を変化させる様子は図 10 に示されている。R のソース信号線がソース線選択回路に選択されている期間は、R に対応する電源電圧が印加され、G のソース信号線がソース線選択回路に選択されている期間は、G に対応する電源電圧が印加され、B のソース信号線がソース線選択回路に選択されている期間は、B に対応する電源電圧が印加される。

#### 【 0 0 5 1 】

本実施例のように、1 ゲート線選択期間内においては、R G B について同色のソース信号線は連続的に D / A 変換回路と接続されることにより、階調電源線に印加する電源電圧を変化させる周期を長くすることができ、回路動作負担の低減につながる。

#### 【 0 0 5 2 】

以上の駆動方法により、1 つの D / A 変換回路で 6 本のソース信号線を駆動する場合、ソース信号線駆動回路に供給される階調電源線が 1 系統のみであっても、画素に印加する電圧を R G B 独立に制御することができる。

#### 【 0 0 5 3 】

なお、本実施例においてソース信号線駆動回路に供給される回路駆動電源は 1 系統を仮定したが、2 系統以上とし必要な部分にレベルシフタ回路を挿入してもよい。また、本実施例では階調電源線 V r e f - L の電源電圧は R G B に対して同一としたが、異なっていてもよい。また、ソース線選択回路のソース信号線を選択する順序は本実施例には限定されない。

#### 【 0 0 5 4 】

#### [ 実施例 3 ]

本実施例では、実施例 1 および実施例 2 をアクティブマトリクス型液晶表示装置に適用した場合の作成方法例として、画素部のスイッチング素子である画素 T F T と、画素部の周辺に設けられる駆動回路（ソース信号線駆動回路、ゲート信号線駆動回路等）の T F T を同一基板上に作製する方法について工程に従って詳細に説明する。但し、説明を簡単にするために、駆動回路部としてはその基本構成回路である C M O S 回路を、画素 T F T 部としては n チャネル型 T F T とを図示することにする。

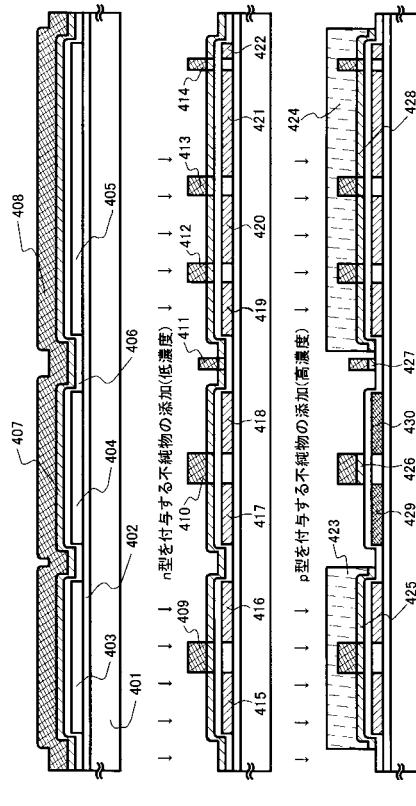

#### 【 0 0 5 5 】

図 11において、基板 4 0 1 には、例えばコーニング社の 1 7 3 7 ガラス基板に代表される無アルカリガラス基板を用いる。T F T が形成される基板 4 0 1 の表面に、下地膜 4 0 2 をプラズマ C V D 法やスパッタ法で形成する。下地膜 4 0 2 は、窒化シリコン膜を 2 5 ~ 1 0 0 n m 、ここでは 5 0 n m の厚さに、酸化シリコン膜を 5 0 ~ 3 0 0 n m 、ここでは 1 5 0 n m の厚さに形成する。また、下地膜 4 0 2 は、窒化シリコン膜や窒化酸化シリコン膜のみを用いても良い。

#### 【 0 0 5 6 】

次に、この下地膜 4 0 2 の上に 5 0 n m の厚さの、非晶質シリコン膜をプラズマ C V D 法で形成する。非晶質シリコン膜は含有水素量にもよるが、好ましくは 4 0 0 ~ 5 5 0 で数時間加熱して脱水素処理を行い、含有水素量を 5 atom% 以下として、結晶化の工程を行うことが望ましい。また、非晶質シリコン膜をスパッタ法や蒸着法などの他の作製方法で形成しても良いが、膜中に含まれる酸素、窒素などの不純物元素を十分低減させておくこ

10

20

30

40

50

とが望ましい。

**【0057】**

ここで、下地膜と非晶質シリコン膜とはいずれもプラズマCVD法で作製されるものであり、このとき下地膜と非晶質シリコン膜を真空中で連続して形成しても良い。下地膜を形成後、一旦大気雰囲気にさらされない工程にすることにより、表面の汚染を防ぐことが可能となり、作製されるTFTの特性バラツキを低減させることができる。

**【0058】**

非晶質シリコン膜を結晶化する工程は、公知のレーザー結晶化技術または熱結晶化の技術を用いれば良い。本実施例では、パルス発振型のKrFエキシマレーザー光を線状に集光して非晶質シリコン膜に照射して結晶質シリコン膜を形成する。

10

**【0059】**

尚、本実施例では半導体層となる結晶質シリコン膜を、非晶質シリコン膜から形成するが、非晶質シリコン膜の代わりに微結晶シリコン膜を用いても構わないし、直接結晶質シリコン膜を成膜しても良い。

**【0060】**

こうして形成された結晶質シリコン膜をパターニングして、島状の半導体層403、404、405を形成する。

**【0061】**

次に、島状の半導体層403、404、405を覆って、酸化シリコンまたは窒化シリコンを主成分とするゲート絶縁膜406を形成する。ゲート絶縁膜406は、プラズマCVD法でN<sub>2</sub>OとSiH<sub>4</sub>を原料とした窒化酸化シリコン膜を10～200nm、好ましくは50～150nmの厚さで形成すれば良い。ここでは100nmの厚さに形成する。

20

**【0062】**

そして、ゲート絶縁膜406の表面に第1のゲート電極となる第1の導電膜407と、第2のゲート電極となる第2の導電膜408とを形成する。第1の導電膜407はSi、Geから選ばれた一種の元素、またはこれらの元素を主成分とする半導体膜で形成すれば良い。また、第1の導電膜407の厚さは5～50nm、好ましくは10～30nmとする必要がある。ここでは、20nmの厚さでSi膜を形成する。

**【0063】**

第1の導電膜407として使用する半導体膜にはn型あるいはp型の導電型を付与する不純物元素が添加されていても良い。この半導体膜の作製法は公知の方法に従えば良く、例えば、減圧CVD法で基板温度を450～500として、ジシラン(Si<sub>2</sub>H<sub>6</sub>)を250SCCM、ヘリウム(He)を300SCCM導入して作製することができる。このとき同時に、Si<sub>2</sub>H<sub>6</sub>に対してPH<sub>3</sub>を0.1～2%混入させてn型の半導体膜を形成しても良い。

30

**【0064】**

第2のゲート電極となる第2の導電膜408は、Ti、Ta、W、Moから選ばれた元素、あるいはこれらの元素を主成分とする化合物で形成すれば良い。これはゲート電極の電気抵抗を下げるために考慮されるものであり、例えば、Mo-W化合物を用いても良い。ここでは、Taを使用し、スパッタ法で、200～1000nm、代表的には400nmの厚さに形成した。(図11(A))

40

**【0065】**

次に公知のパターニング技術を使ってレジストマスクを形成し、第2の導電膜408をエッチングして第2のゲート電極を形成する工程を行う。第2の導電膜408はTa膜で形成されているので、ドライエッチング法によりエッチングを行う。ドライエッチングの条件として、Cl<sub>2</sub>を80SCCM導入して100mTorrで500Wの高周波電力を投入して行う。そして、図11(B)に示すように第2のゲート電極409、410、412、413と、配線411、414を形成する。第2のゲート電極の、チャネル長方向の長さは、CMOS回路を形成する第2のゲート電極409、410で3μmとし、また、画素TFTはマルチゲートの構造となっていて、第2のゲート電極412、413の各々

50

の長さを  $2 \mu m$  とした。

**【0066】**

また、第2の導電膜408はウエットエッティング法で除去することもできる。例えば、Taの場合、フッ酸系のエッティング液で容易に除去することができる。

**【0067】**

また、画素TFTを構成するnチャネル型TFTのドレイン側に保持容量を設ける構造となっている。このとき、第2の導電膜と同じ材料で保持容量の配線電極414が形成される。

**【0068】**

次に、n型を付与する第1の不純物元素を添加する工程を行う。この工程は第2の不純物領域を形成するための工程である。ここでは、フォスフィン( $PH_3$ )を用いたイオンドープ法を行う。この工程では、ゲート絶縁膜406と第1の導電膜407を通してその下の半導体層403、404、405にリンを添加するために、加速電圧は  $80 \text{ keV}$  と高めに設定する。半導体層403、404、405に添加されるリンの濃度は、 $1 \times 10^{16} \sim 1 \times 10^{19} \text{ atoms/cm}^3$  の範囲にするのが好ましく、ここでは  $1 \times 10^{18} \text{ atoms/cm}^3$  とする。そして、半導体層にリンが添加された領域415、416、417、418、419、420、421、422が形成される。(図11(B))

**【0069】**

このとき、第1の導電膜407で、第2のゲート電極409、410、411、412、413、414と重ならない領域にもリンが添加される。この領域のリン濃度は特に規定されるものではないが、第1の導電膜の抵抗率を下げる効果が得られる。

**【0070】**

次に、nチャネル型TFTが形成される領域をレジストマスク423、424で覆って、第1の導電膜407の一部を除去する工程をドライエッティング法で行う。第1の導電膜407はSiであり、ドライエッティングの条件として、 $CF_4$ を50SCCM、 $O_2$ を45SCCM導入し、 $50 \text{ mTorr}$ で  $200 \text{ W}$  の高周波電力を投入して行う。その結果、レジストマスク或いはゲート電極で覆われた、第1の導電膜の一部である425、426、427、428が残る。

**【0071】**

そして、pチャネル型TFTが形成される領域に、p型を付与する第3の不純物元素を添加する工程を行う。ここではジボラン( $B_2H_6$ )を用いてイオンドープ法で添加する。ここでも加速電圧を  $80 \text{ keV}$  として、 $2 \times 10^{20} \text{ atoms/cm}^3$  の濃度にボロンを添加する。そして、図11(C)に示すようにボロンが高濃度に添加された第3の不純物領域429、430が形成される。(図11(C))

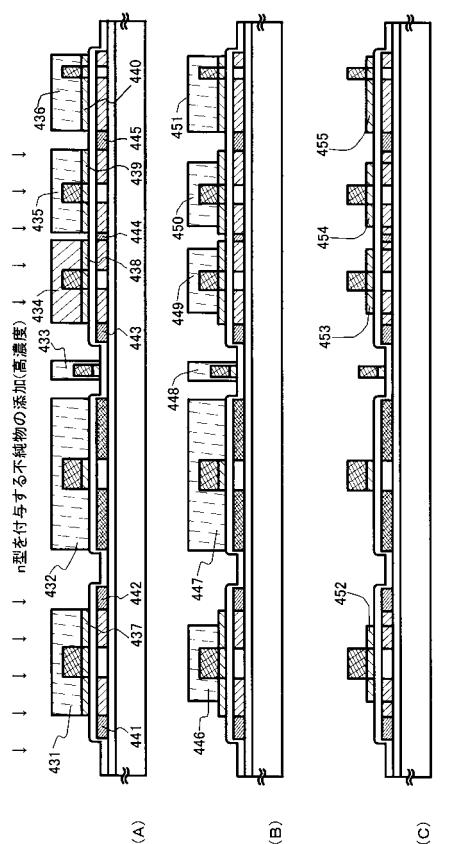

**【0072】**

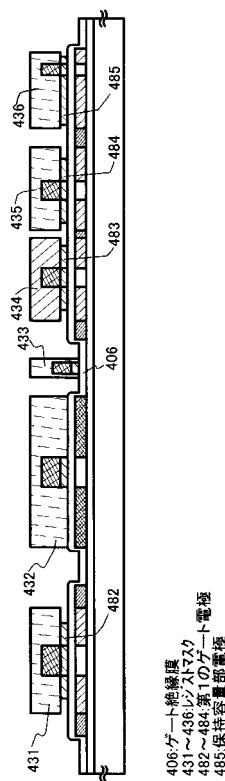

さらに、レジストマスク423、424を完全に除去して、再度レジストマスク431、432、433、434、435、436を形成する。そして、レジストマスク431、434、435、436を用い、第1の導電膜の一部425、428をエッティングし、新たに第1の導電膜の一部437、438、439、440を形成する。(図12(A))

**【0073】**

レジストマスク431は  $9 \mu m$  の長さで、レジストマスク434、435は  $7 \mu m$  の長さで形成する。これにより、n型を付与する第1の不純物添加の工程でリンが添加された半導体層のうち、レジストマスク431、434、435で覆われた下の領域が、第2の不純物領域として次の工程の後確定することになる。

**【0074】**

次に、n型を付与する第2の不純物元素を添加する工程を行う。ここでは、フォスフィン( $PH_3$ )を用いたイオンドープ法で行う。この工程でも、ゲート絶縁膜406を通してその下の半導体層にリンを添加するために、加速電圧は  $80 \text{ keV}$  と高めに設定する。そして、リンが添加された第1の不純物領域441、442、443、444、445が形成される。この領域のリンの濃度はn型を付与する第1の不純物元素を添加する工程と比

10

20

30

40

50

較して高濃度であり、 $1 \times 10^{19} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup>とするのが好ましく、ここでは $1 \times 10^{20}$  atoms/cm<sup>3</sup>とする。（図12（A））

#### 【0075】

さらに、レジストマスク431、432、433、434、435、436を除去して新たにレジストマスク446、447、448、449、450、451を形成する。この工程において、nチャネル型TFTに形成されるレジストマスク446、449、450のチャネル長方向の長さはTFTの構造を決める上で重要である。レジストマスク446、449、450は第1の導電膜437、438、439の一部を除去する目的で設けられるものであり、このレジストマスクの長さにより、第2の不純物領域がゲート電極と重なる領域と、重ならない領域がある範囲で自由に決めることができる。（図12（B））

10

#### 【0076】

そして、レジストマスク446、449、450を使用したエッチングにより、図12（C）に示すように第1のゲート電極452、453、454が形成される。ここで、第1のゲート電極452の、チャネル長方向の長さは6 μm、第1のゲート電極453、454のチャネル長方向の長さは4 μmとした。

#### 【0077】

また、画素部には、保持容量部の電極455が形成される。

#### 【0078】

図12（C）までの工程が終了したら、窒化シリコン膜456、第1の層間絶縁膜457を形成する工程を行う。最初に窒化シリコン膜456を50 nmの厚さに成膜する。窒化シリコン膜456はプラズマCVD法で形成され、SiH<sub>4</sub>を5 SCCM、NH<sub>3</sub>を40 SCCM、N<sub>2</sub>を100 SCCM導入して0.7 Torr、300 Wの高周波電力を投入する。続いて、第1の層間絶縁膜457として酸化シリコン膜を採用し、TEOSを500 SCCM、O<sub>2</sub>を50 SCCM導入し1 Torr、200 Wの高周波電力を投入して950 nmの厚さに成膜する。

20

#### 【0079】

次に、熱処理の工程を行う。熱処理の工程は、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化するために行う必要がある。この工程は、電気加熱炉を用いた熱アニール法や、前述のエキシマレーザーを用いたレーザーハニール法や、ハロゲンランプを用いたラピットサーマルアニール法（RTA法）で行えれば良い。ここでは熱アニール法で活性化の工程を行う。加熱処理は、窒素雰囲気中において300～700、好ましくは350～550、ここでは450、2時間の処理を行う。

30

#### 【0080】

第1の層間絶縁膜457と窒化シリコン膜456には、その後、パターニングでそれぞれのTFTのソース領域と、ドレイン領域に達するコンタクトホール形成のためエッチングされる。そして、ソース電極458、459、460とドレイン電極461、462を形成する。図示していないが、本実施例ではこの電極を、Ti膜を100 nm、Tiを含むAl膜300 nm、Ti膜150 nmをスパッタ法で連続形成した3層構造の電極として用いる。

40

#### 【0081】

そして、ソース電極458、459、460とドレイン電極461、462と、第1の層間絶縁膜457を覆ってパッシベーション膜463を形成する。パッシベーション膜463は、窒化シリコン膜で50 nmの厚さで形成する。さらに、有機樹脂からなる第2の層間絶縁膜464を約1000 nmの厚さに形成する。有機樹脂膜としては、ポリイミド、アクリル、ポリイミドアミド等を使用することができます。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜を用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300で焼成して形成する。

#### 【0082】

50

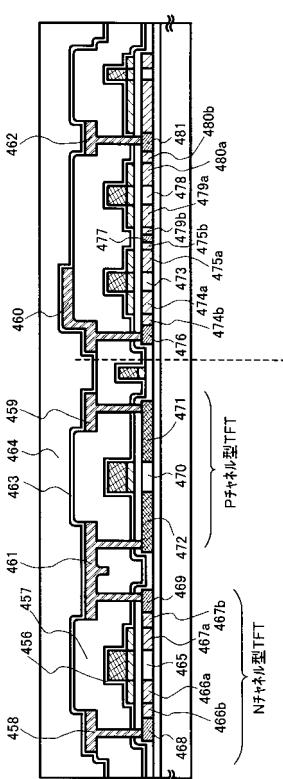

以上の工程で、CMOS回路のnチャネル型TFTにはチャネル形成領域465、第1の不純物領域468、469、第2の不純物領域466、467が形成される。ここで、第2の不純物領域は、ゲート電極と重なる領域(GOLD領域)466a、467aが1.5μmの長さに、ゲート電極と重ならない領域(LDD領域)466b、467bが1.5μmの長さにそれぞれ形成される。第1の不純物領域468はソース領域、第1の不純物領域469はドレイン領域となる。

#### 【0083】

pチャネル型TFTは、同様にクラッド構造のゲート電極が形成され、チャネル形成領域470、第3の不純物領域471、472が形成される。そして、第3の不純物領域471はソース領域、第3の不純物領域472はドレイン領域となる。

10

#### 【0084】

また、画素TFTであるnチャネル型TFTはマルチゲートであり、チャネル形成領域473、478と第1の不純物領域476、477、481と第2の不純物領域474、475、479、480が形成される。ここで第2の不純物領域は、ゲート電極と重なる領域474a、475a、479a、480aと重ならない領域474b、475b、479b、480bとが形成される。

#### 【0085】

こうして図13に示すように、基板401上にCMOS回路と、画素TFTが形成されたアクティブマトリクス基板が作製される。また、画素TFTであるnチャネル型TFTのドレイン側には、保持容量部が同時に形成されている。

20

#### 【0086】

##### [実施例4]

本実施例では、実施例3と同じ工程で図12(A)に示す状態を得た後、他の方法で第1の導電膜の一部を除去する例を、図14を用いて説明する。

#### 【0087】

まず、図12(A)で形成したレジストマスク431、432、433、434、435、436をそのまま使用して、図12(A)の第1の導電膜437、438、439、440の一部をエッチングして除去し、第1の導電膜を図14の482、483、484、485に示すような形状にする。

#### 【0088】

30

ここでのエッチングの工程は、第1のゲート電極がシリコン膜である場合、ドライエッチング法により、SF<sub>6</sub>を40SCCM、O<sub>2</sub>を10SCCM導入して、100mTorr、200Wの高周波電力を印加して行うことができる。

#### 【0089】

このドライエッチングの条件では、下地にあるゲート絶縁膜との選択比は高く、ゲート絶縁膜406はほとんどエッチングされない。

#### 【0090】

ここでは、レジストマスク431は、TFTのチャネル長方向に対して9μm、また、レジストマスク434、435は7μmの長さで形成されている。そして、ドライエッチングにより第1の導電膜を1.5μmずつ除去して、第1のゲート電極482、483、484、485を形成する。

40

#### 【0091】

レジストマスク431、432、433、434、435、436を除去すればTFTに関する部分では、図12(C)の状態になる。以降の工程は実施例3に従えば良く、図13に示すように窒化シリコン膜456、第1の層間絶縁膜457、ソース電極458、459、460、ドレイン電極461、462、パッシベーション膜463、第2の層間絶縁膜464を形成して、図13に示すアクティブマトリクス基板が形成される。

#### 【0092】

##### [実施例5]

本実施例では、実施例3において半導体層として用いる結晶質半導体膜を、触媒元素を用

50

いた熱結晶化法により形成する例を示す。触媒元素を用いる場合、特開平7-130652号公報、特開平8-78329号公報で開示された技術を用いることが望ましい。

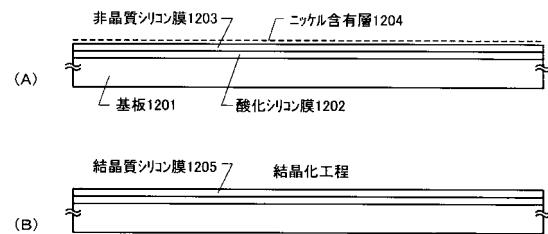

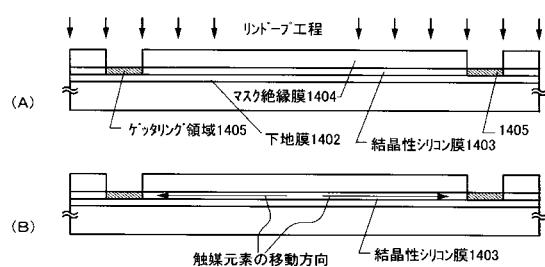

#### 【0093】

ここで、特開平7-130652号公報に開示されている技術を本発明に適用する場合の例を図15に示す。まず基板1201に酸化シリコン膜1202を設け、その上に非晶質シリコン膜1203を形成する。さらに、重量換算で10ppmのニッケルを含む酢酸ニッケル塩溶液を塗布してニッケル含有層1204を形成する。(図15(A))

#### 【0094】

次に、500、1時間の脱水素工程の後、500~650で4~12時間、例えば550、8時間の熱処理を行い、結晶質シリコン膜1205を形成する。こうして得られた結晶質シリコン膜1205は非常に優れた結晶質を有する。(図15(B))

10

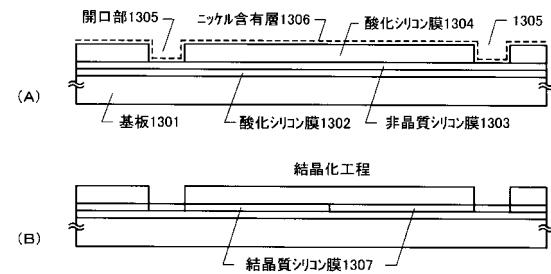

#### 【0095】

また、特開平8-78329号公報で開示された技術は、触媒元素を選択的に添加することによって、非晶質半導体膜の選択的な結晶化を可能としたものである。同技術を本発明に適用した場合について、図16で説明する。

#### 【0096】

まず、ガラス基板1301に酸化シリコン膜1302を設け、その上に非晶質シリコン膜1303、酸化シリコン膜1304を連続的に形成する。この時、酸化シリコン膜1304の厚さは150nmとする。

20

#### 【0097】

次に酸化シリコン膜1304をパターニングして、選択的に開孔部1305を形成し、その後、重量換算で10ppmのニッケルを含む酢酸ニッケル塩溶液を塗布する。これにより、ニッケル含有層1306が形成され、ニッケル含有層1306は開孔部1305の底部のみで非晶質シリコン膜1303と接触する。(図16(A))

#### 【0098】

次に、500~650で4~24時間、例えば570、14時間の熱処理を行い、結晶質シリコン膜1307を形成する。この結晶化の過程では、ニッケルが接した非晶質シリコン膜の部分が最初に結晶化し、そこから横方向へと結晶化が進行する。こうして形成された結晶質シリコン膜1307は棒状または針状の結晶が集合して成り、その各々の結晶は巨視的に見ればある特定の方向性をもって成長しているため、結晶性が揃っているという利点がある。(図16(B))

30

#### 【0099】

尚、上記2つの技術において使用可能な触媒元素は、ニッケル(Ni)の以外にも、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素を用いても良い。

#### 【0100】

以上のような技術を用いて結晶質半導体膜(結晶質シリコン膜や結晶質シリコンゲルマニウム膜などを含む)を形成し、パターニングを行えば、結晶質TFTの半導体層を形成することができる。本実施例の技術を用いて、結晶質半導体膜から作製されたTFTは、優れた特性が得られるが、そのため高い信頼性を要求されていた。しかしながら、本発明のTFT構造を採用することで、本実施例の技術を最大限に生かしたTFTを作製することが可能となった。

40

#### 【0101】

#### [実施例6]

本実施例は、実施例3で用いられる半導体層を形成する方法として、非晶質半導体膜を初期膜として前記触媒元素を用いて結晶質半導体膜を形成した後で、その触媒元素を結晶質半導体膜から除去する工程を行った例を示す。本実施例ではその方法として、特開平10-135468号公報または特開平10-135469号公報に記載された技術を用いる。

#### 【0102】

50

同公報に記載された技術は、非晶質半導体膜の結晶化に用いた触媒元素を結晶化後にリンのゲッタリング作用により除去する技術である。同技術を用いることで、結晶質半導体膜中の触媒元素の濃度を $1 \times 10^{17}$ atms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$ atms/cm<sup>3</sup>にまで低減することができる。

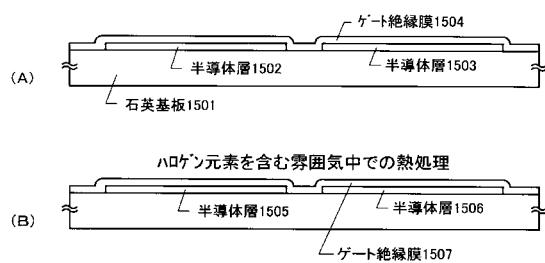

#### 【0103】

本実施例の構成について図17を用いて説明する。ここではコーニング社の1737基板に代表される無アルカリガラス基板を用いる。図17(A)では、実施例5で示した結晶化の技術を用いて、下地膜1402、結晶質シリコン膜1403が形成された状態を示している。そして、結晶質シリコン膜1403の表面にマスク用の酸化シリコン膜1404を150nmの厚さに形成し、さらにパターニングにより開孔部を設け、結晶質シリコン膜を露出させた領域を形成してある。そして、リンを添加する工程を実施して、結晶質シリコン膜にリンが添加された領域1405が設けられている。10

#### 【0104】

この状態で、窒素雰囲気中で550～800、5～24時間、例えば600、12時間の熱処理を行うと、結晶質シリコン膜にリンが添加された領域1405がゲッタリングサイトとして働き、結晶質シリコン膜1403に残存していた触媒元素はリンが添加された領域1405に偏析させることができる。(図17(B))

#### 【0105】

そして、マスク用の酸化シリコン膜1404と、リンが添加された領域1405とをエッチングして除去することにより、結晶化の工程で使用した触媒元素の濃度を $1 \times 10^{17}$ atms/cm<sup>3</sup>以下にまで低減された結晶質シリコン膜を得ることができる。この結晶質シリコン膜はそのまま実施例3で示した本発明のTFTの半導体層として使用することができる。20

#### 【0106】

#### [実施例7]

本実施例では、実施例3で示した本発明のTFTを作製する工程において、半導体層とゲート絶縁膜を形成する他の実施例を示す。本実施例の構成は図18に示されている。

#### 【0107】

ここでは、少なくとも700～1100程度の耐熱性を有する基板が必要であり、石英基板1501が用いられる。そして実施例5及び実施例6で示した技術を用い、結晶質半導体が形成され、これをTFTの半導体層にするために、島状にパターニングして半導体層1502、1503を形成する。そして、半導体層1502、1503を覆って、ゲート絶縁膜1504として酸化シリコンを主成分とする膜を形成する。本実施例では、プラズマCVD法で窒化酸化シリコン膜を70nmの厚さで形成する。(図18(A))30

#### 【0108】

そして、ハロゲン(代表的には塩素)と酸素を含む雰囲気中で熱処理を行う。本実施例では、950、30分とした。尚、処理温度は700～1100の範囲で選択すれば良く、処理時間も10分から8時間の間で選択すれば良い。(図18(B))

#### 【0109】

その結果、本実施例の条件では、半導体層1502、1503とゲート絶縁膜1504との界面で熱酸化膜が形成され、成膜したゲート絶縁膜1504と組み合わされたゲート絶縁膜1507が形成される。また、ハロゲン雰囲気での酸化の過程で、ゲート絶縁膜1504と半導体層1502、1503に含まれる不純物で、特に金属不純物元素はハロゲンと化合物を形成し、気相中に除去することができる。40

#### 【0110】

以上の工程で作製されるゲート絶縁膜1507は、絶縁耐圧が高く半導体層1505、1506とゲート絶縁膜1507の界面は非常に良好なものになる。本発明のTFTの構成を得るためにには、以降の工程は実施例3に従えば良い。

#### 【0111】

#### [実施例8]

本実施例では、実施例5に示す方法で結晶質半導体膜を形成し、実施例3で示す工程でア50

クティブマトリクス基板を作製する方法において、結晶化の工程で使用した触媒元素をゲッタリングにより除去する例を示す。まず、実施例3において、図11(A)で示される半導体層403、404、405は、触媒元素を用いて作製された結晶質シリコン膜であった。このとき、結晶化の工程で用いられた触媒元素が半導体層中に残存するので、ゲッタリングの工程を実施することが望ましい。

#### 【0112】

ここでは、図11(C)に示す工程までそのまま実施し、その後、レジストマスク423、424を除去した。

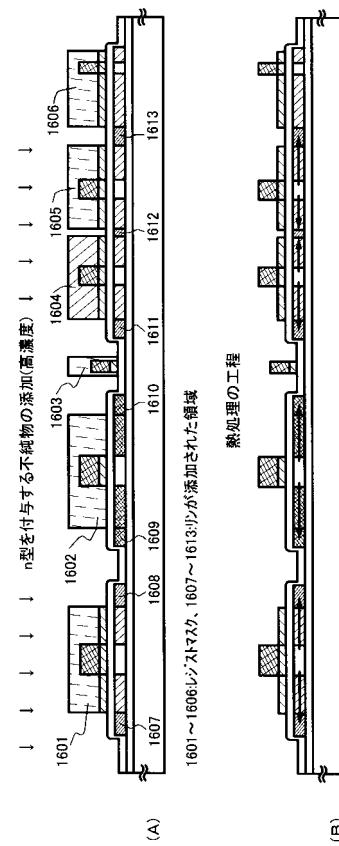

#### 【0113】

そして、図19に示すように、新たなレジストマスク1601、1602、1603、1604、1605、1606を形成する。次に、n型を付与する第2の不純物添加の工程を行う。その結果、半導体層にリンが添加された領域1607、1608、1609、1610、1611、1612、1613が形成される。10

#### 【0114】

ここで、リンが添加された領域1609、1610にはすでにp型を付与する不純物元素であるボロンが添加されているが、このときリン濃度は $1 \times 10^{19} \sim 1 \times 10^{20}$ atoms/cm<sup>3</sup>であり、ボロンに対して1/2程度の濃度で添加されるので、pチャネル型TFTの特性には何ら影響を及ぼさない。

#### 【0115】

この状態で、窒素雰囲気中で400～800、1～24時間、例えば600、12時間の加熱処理の工程を行う。この工程により、添加されたn型及びp型を付与する不純物元素を活性化することができる。さらに、前記リンが添加されている領域がゲッタリングサイトとなり、結晶化の工程の後、残存していた触媒元素を偏析させることができる。その結果、チャネル形成領域から触媒元素を除去することが可能となる。(図19(B))20

#### 【0116】

図19(B)の工程が終了したら、以降の工程は実施例3の工程に従い、図13の状態を形成することにより、アクティブマトリクス基板を作製することができる。

#### 【0117】

#### [実施例9]

本実施例では、実施例3で作製されたアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。30

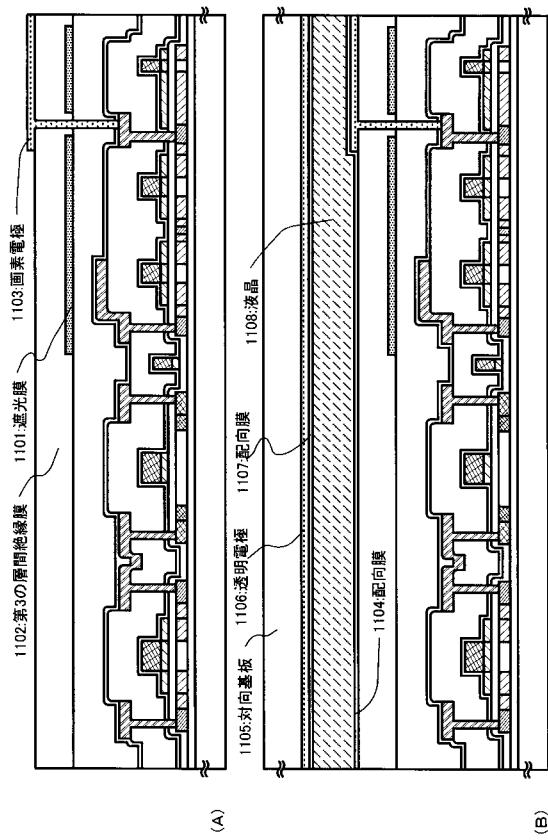

#### 【0118】

図13の状態のアクティブマトリクス基板に対して、図20(A)に示すように遮光膜1101、第3の層間絶縁膜1102を形成する。遮光膜1101は顔料を含む有機樹脂膜や、Ti、Crなどの金属膜を用いると良い。また、第3の層間絶縁膜1102は、ポリイミドなどの有機樹脂膜で形成した。そして、第3の層間絶縁膜1102と第2の層間絶縁膜464、パッシベーション膜463にドレイン電極462に達するコンタクトホールを形成し、画素電極1103を形成する。画素電極1103は、透過型液晶表示装置の場合には透明導電膜を用い、反射型の液晶表示装置の場合には金属膜を用いれば良い。ここでは透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を100nmの厚さにスパッタ法で形成し、画素電極1103を形成する。40

#### 【0119】

次に、図20(B)に示すように、配向膜1104を第3の層間絶縁膜1102と画素電極1103を覆うように形成する。通常液晶表示素子の配向膜にはポリイミド樹脂が多く用いられている。対向側の基板1105には、透明導電膜1106と、配向膜1107とを形成する。配向膜は、形成された後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って平行配向させる役目を果たす。

#### 【0120】

上記の工程を経て、画素TFTと、CMOS回路が形成されたアクティブマトリクス基板と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)など

を介して貼りあわせる。その後、両基板の間に液晶材料1108を注入し、封止剤(図示せず)によって完全に封止する。このようにして図20(B)に示すアクティブマトリクス型液晶表示装置が完成する。

#### 【0121】

なお、上記の行程により作成されるTFTはトップゲート構造であるが、ボトムゲート構造のTFTやその他の構造のTFTに対しても本発明は適用され得る。

#### 【0122】

また、液晶材料の代わりにエレクトロルミネッセンス(EL:Electro Luminescence)材料を用いた自発光型の表示装置であるEL表示装置に対しても本発明は適用され得る。なお、本明細書中では、陽極、有機化合物層及び陰極で形成される素子を発光素子と呼ぶ。

発光素子は、エレクトロルミネッセンス(Electro Luminescence:電場を加えることで発生するルミネッセンス)が得られる有機化合物を含む層(以下、有機化合物層と記す)と、陽極と、陰極とを有する。有機化合物におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)とがあるが、本発明はどちらの発光を用いた発光装置にも適用可能である。

10

#### 【0123】

なお、本明細書では、陽極と陰極の間に設けられた全ての層を有機化合物層と定義する。有機化合物層には具体的に、発光層、正孔注入層、電子注入層、正孔輸送層、電子輸送層等が含まれる。基本的に発光素子は、陽極/発光層/陰極が順に積層された構造を有しており、この構造に加えて、陽極/正孔注入層/発光層/陰極や、陽極/正孔注入層/発光層/電子輸送層/陰極等の順に積層した構造を有していることもある。

20

#### 【0124】

##### [実施例10]

本実施例では、実施例1および実施例2をEL表示装置に適用した場合の作製例について説明する。

#### 【0125】

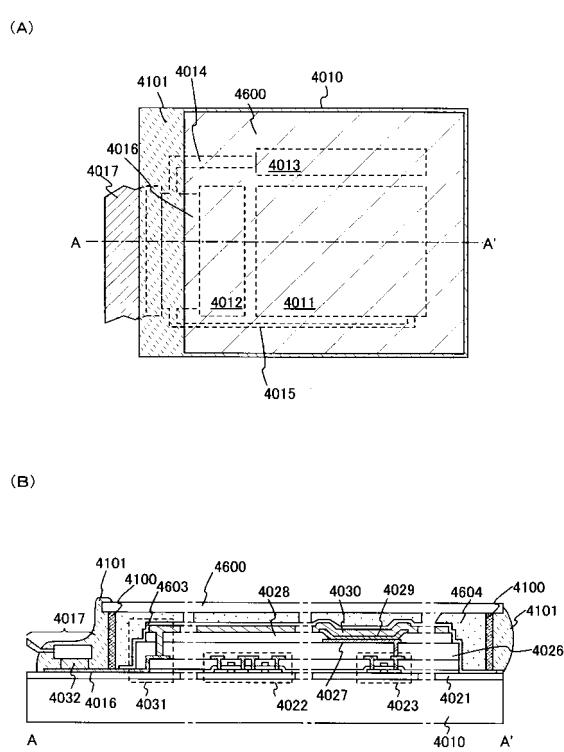

図21(A)は本発明を適用したEL表示装置の上面図であり、図21(B)は図21(A)に示したA-A'で切断したEL表示装置の断面図である。図21(A)において、4010は基板、4011は画素部、4012はソース信号線駆動回路、4013はゲート信号線駆動回路であり、それぞれの駆動回路は配線4014~4016を経てFPC4017に至り、外部機器へと接続される。

30

#### 【0126】

このとき、少なくとも画素部、好ましくは駆動回路及び画素部を囲むようにしてカバー材4600、シーリング材(ハウジング材ともいう)4100、密封材(第2のシーリング材)4101が設けられている。

#### 【0127】

また、図21(B)に示すように、基板4010、下地膜4021の上に駆動回路用TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを組み合わせたCMOS回路を図示している。)4022及び画素部用TFT4023(但し、ここではEL素子への電流を制御するTFTだけ図示している。)が形成されている。これらのTFTは公知の構造(トップゲート構造またはボトムゲート構造)を用いれば良い。

40

#### 【0128】

公知の作製方法を用いて駆動回路用TFT4022、画素部用TFT4023が完成したら、樹脂材料でなる層間絶縁膜(平坦化膜)4026の上に画素部用TFT4023のドレインと電気的に接続する透明導電膜でなる画素電極4027を形成する。透明導電膜としては、酸化インジウムと酸化スズとの化合物(ITOと呼ばれる)または酸化インジウムと酸化亜鉛との化合物を用いることができる。そして、画素電極4027を形成したら、絶縁膜4028を形成し、画素電極4027上に開口部を形成する。

#### 【0129】

次に、EL層4029を形成する。EL層4029は公知のEL材料(正孔注入層、正孔

50

輸送層、発光層、電子輸送層または電子注入層)を自由に組み合わせて積層構造または単層構造とすれば良い。どのような構造とするかは公知の技術を用いれば良い。また、EL材料には低分子系材料と高分子系(ポリマー系)材料がある。低分子系材料を用いる場合は蒸着法を用いるが、高分子系材料を用いる場合には、スピンドルコート法、印刷法またはインクジェット法等の簡易な方法を用いることが可能である。

#### 【0130】

本実施例では、シャドーマスクを用いて蒸着法によりEL層を形成する。シャドーマスクを用いて画素毎に波長の異なる発光が可能な発光層(赤色発光層、緑色発光層及び青色発光層)を形成することで、カラー表示が可能となる。その他にも、色変換層(CCM)とカラーフィルターを組み合わせた方式、白色発光層とカラーフィルターを組み合わせた方式があるがいずれの方法を用いても良い。10

勿論、単色発光のEL表示装置とすることもできる。

#### 【0131】

EL層4029を形成したら、その上に陰極4030を形成する。陰極4030とEL層4029の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中でEL層4029と陰極4030を連続成膜するか、EL層4029を不活性雰囲気で形成し、大気解放しないで陰極4030を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

#### 【0132】

なお、本実施例では陰極4030として、LiF(フッ化リチウム)膜とAl(アルミニウム)膜の積層構造を用いる。具体的にはEL層4029上に蒸着法で1nm厚のLiF(フッ化リチウム)膜を形成し、その上に300nm厚のアルミニウム膜を形成する。勿論、公知の陰極材料であるMgAg電極を用いても良い。そして陰極4030は4031で示される領域において配線4016に接続される。配線4016は陰極4030に所定の電圧を与えるための電源供給線であり、導電性ペースト材料4032を介してFPC4017に接続される。20

#### 【0133】

4031に示された領域において陰極4030と配線4016とを電気的に接続するためには、層間絶縁膜4026及び絶縁膜4028にコンタクトホールを形成する必要がある。これらは層間絶縁膜4026のエッチング時(画素電極用コンタクトホールの形成時)や絶縁膜4028のエッチング時(EL層形成前の開口部の形成時)に形成しておけば良い。また、絶縁膜4028をエッチングする際に、層間絶縁膜4026まで一括でエッチングしても良い。この場合、層間絶縁膜4026と絶縁膜4028が同じ樹脂材料であれば、コンタクトホールの形状を良好なものとすることができます。30

#### 【0134】

このようにして形成されたEL素子の表面を覆って、パッシベーション膜4603、充填材4604、カバー材4600が形成される。

#### 【0135】

さらに、EL素子部を囲むようにして、カバー材4600と基板4010の内側にシーリング材4100が設けられ、さらにシーリング材4100の外側には密封材(第2のシーリング材)4101が形成される。40

#### 【0136】

このとき、この充填材4604は、カバー材4600を接着するための接着剤としても機能する。充填材4604としては、PVC(ポリビニルクロライド)、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材4604の内部に乾燥剤を設けておくと、吸湿効果を保持できるので好ましい。

#### 【0137】

また、充填材4604の中にスペーサーを含有させてもよい。このとき、スペーサーをB50

a O などからなる粒状物質とし、スペーサー自体に吸湿性をもたせてもよい。

【0138】

スペーサーを設けた場合、パッシベーション膜4603はスペーサー圧を緩和することができる。また、パッシベーション膜とは別に、スペーサー圧を緩和する樹脂膜などを設けてもよい。

【0139】

また、カバー材4600としては、ガラス板、アルミニウム板、ステンレス板、F R P (Fiberglass-Reinforced Plastics)板、P V F (ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。なお、充填材4604としてPVBやEVAを用いる場合、数十μmのアルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることが好ましい。

【0140】

但し、EL素子からの発光方向（光の放射方向）によっては、カバー材4600が透光性を有する必要がある。

【0141】

また、配線4016はシーリング材4100および密封材4101と基板4010との隙間を通ってFPC4017に電気的に接続される。なお、ここでは配線4016について説明したが、他の配線4014、4015も同様にしてシーリング材4100および密封材4101の下を通ってFPC4017に電気的に接続される。

【0142】

なお本実施例では、充填材4604を設けてからカバー材4600を接着し、充填材4604の側面（露呈面）を覆うようにシーリング材4100を取り付けているが、カバー材4600及びシーリング材4100を取り付けてから、充填材4604を設けても良い。この場合、基板4010、カバー材4600及びシーリング材4100で形成されている空隙に通じる充填材の注入口を設ける。そして前記空隙を真空状態（ $10^{-2}$  Torr以下）にし、充填材の入っている水槽に注入口を浸してから、空隙の外の気圧を空隙の中の気圧よりも高くして、充填材を空隙の中に充填する。

【0143】

[実施例11]

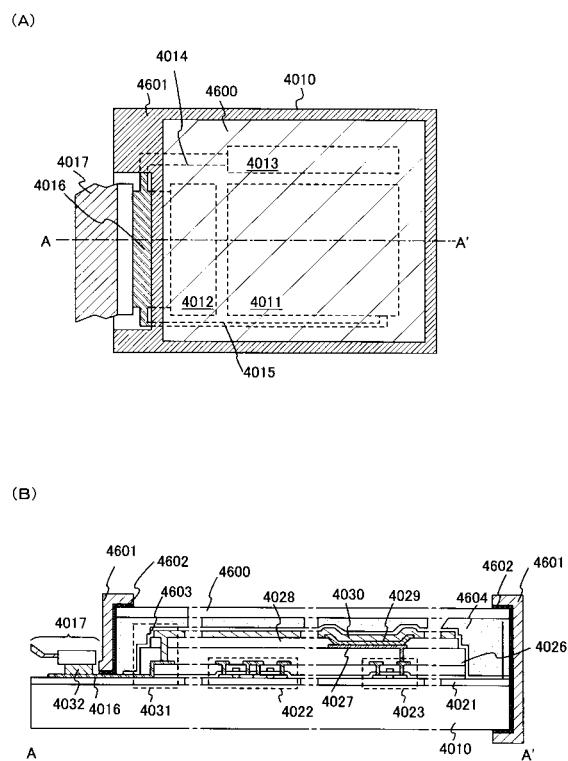

本実施例では、本発明を用いて実施例10とは異なる形態のEL表示装置を作製した例について、図22(A)、図22(B)を用いて説明する。図21(A)、図21(B)と同じ番号のものは同じ部分を指しているので説明は省略する。

【0144】

図22(A)は本実施例のEL表示装置の上面図であり、図22(A)をA-A'で切断した断面図を図22(B)に示す。

【0145】

実施例10に従って、EL素子の表面を覆ってパッシベーション膜4603までを形成する。

【0146】

さらに、EL素子を覆うようにして充填材4604を設ける。この充填材4604は、カバー材4600を接着するための接着剤としても機能する。充填材4604としては、PVC(ポリビニルクロライド)、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。この充填材4604の内部に乾燥剤を設けておくと、吸湿効果を保持できるので好ましい。

【0147】

また、充填材4604の中にスペーサーを含有させてもよい。このとき、スペーサーをB a O などからなる粒状物質とし、スペーサー自体に吸湿性をもたせてもよい。

【0148】

スペーサーを設けた場合、パッシベーション膜4603はスペーサー圧を緩和することが

10

20

30

40

50

できる。また、パッシベーション膜とは別に、スペーサー圧を緩和する樹脂膜などを設けてよい。

#### 【0149】

また、カバー材4600としては、ガラス板、アルミニウム板、ステンレス板、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリルフィルムを用いることができる。なお、充填材4604としてPVFやEVAを用いる場合、数十μmのアルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることが好ましい。

#### 【0150】

但し、EL素子からの発光方向(光の放射方向)によっては、カバー材4600が透光性を有する必要がある。

#### 【0151】

次に、充填材4604を用いてカバー材4600を接着した後、充填材4604の側面(露呈面)を覆うようにフレーム材4601を取り付ける。フレーム材4601はシーリング材(接着剤として機能する)4602によって接着される。このとき、シーリング材4602としては、光硬化性樹脂を用いるのが好ましいが、EL層の耐熱性が許せば熱硬化性樹脂を用いても良い。なお、シーリング材4602はできるだけ水分や酸素を透過しない材料であることが望ましい。また、シーリング材4602の内部に乾燥剤を添加しても良い。

#### 【0152】

また、配線4016はシーリング材4602と基板4010との隙間を通してFPC4017に電気的に接続される。なお、ここでは配線4016について説明したが、他の配線4014、4015も同様にしてシーリング材4602の下を通してFPC4017に電気的に接続される。

#### 【0153】

なお本実施例では、充填材4604を設けてからカバー材4600を接着し、充填材4604の側面(露呈面)を覆うようにフレーム材4601を取り付けているが、カバー材4600及びフレーム材4601を取り付けてから、充填材4604を設けても良い。この場合、基板4010、カバー材4600及びフレーム材4601で形成されている空隙に通じる充填材の注入口を設ける。そして前記空隙を真空状態( $10^{-2}$ Torr以下)にし、充填材の入っている水槽に注入口を浸してから、空隙の外の気圧を空隙の中の気圧よりも高くして、充填材を空隙の中に充填する。

#### 【0154】

##### [実施例12]

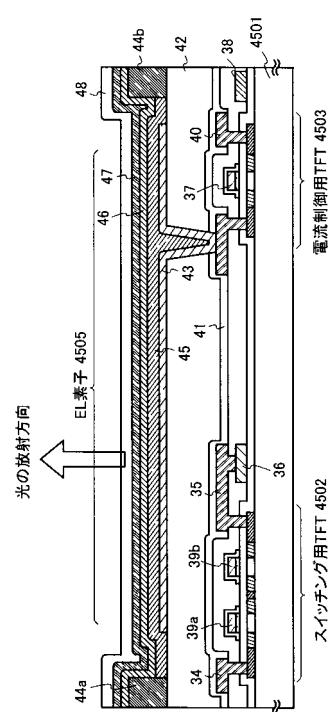

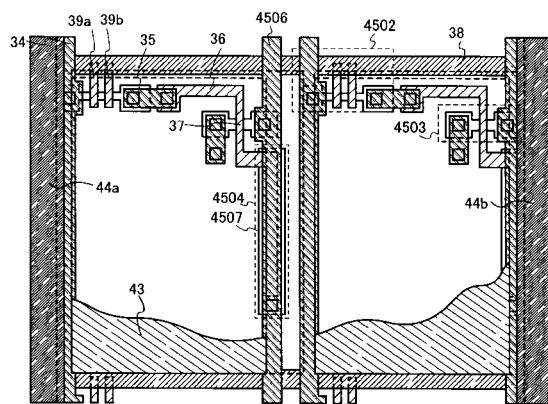

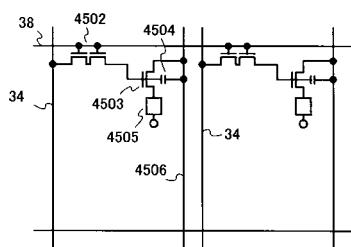

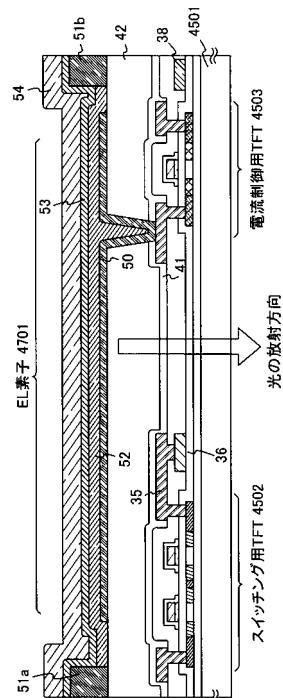

ここでEL表示装置における画素部のさらに詳細な断面構造を図23に、上面構造を図24(A)に、回路図を図24(B)に示す。図23、図24(A)及び図24(B)では共通の符号を用いるので互いに参照すれば良い。

#### 【0155】

図23において、基板4501上に設けられたスイッチング用TFT4502は公知の方法で形成されたnチャネル型TFTを用いる。本実施例ではダブルゲート構造としているが、構造及び作製プロセスに大きな違いはないので説明は省略する。但し、ダブルゲート構造とすることで実質的に二つのTFTが直列された構造となり、オフ電流値を低減することができるという利点がある。なお、本実施例ではダブルゲート構造としているが、シングルゲート構造でも構わないし、トリプルゲート構造やそれ以上のゲート本数を持つマルチゲート構造でも構わない。また、公知の方法で形成されたpチャネル型TFTを用いて形成しても構わない。

#### 【0156】

また、電流制御用TFT4503は公知の方法で形成されたnチャネル型TFTを用いる。スイッチング用TFT4502のソース配線(ソース信号線)は34である。そして、

10

20

30

40

50

スイッチング用 TFT 4502 のドレイン配線である 35 は配線 36 によって電流制御用 TFT のゲート電極 37 に電気的に接続されている。また、38 で示される配線は、スイッチング用 TFT 4502 のゲート電極 39a、39b を電気的に接続するゲート配線（ゲート信号線）である。

#### 【0157】

電流制御用 TFT 4503 は EL 素子を流れる電流量を制御する素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性が高い素子でもある。そのため、電流制御用 TFT 4503 のドレイン側に、ゲート絶縁膜を介してゲート電極に重なるように LDD 領域を設ける構造は極めて有効である。

#### 【0158】

また、本実施例では電流制御用 TFT 4503 をシングルゲート構造で図示しているが、複数の TFT を直列につなげたマルチゲート構造としても良い。さらに、複数の TFT を並列につなげて実質的にチャネル形成領域を複数に分割し、熱の放射を高い効率で行えるようにした構造としても良い。このような構造は熱による劣化対策として有効である。

#### 【0159】

また、図 24 (A) に示すように、電流制御用 TFT 4503 のゲート電極 37 となる配線 36 は 4504 で示される領域で絶縁膜を介して、電流制御用 TFT 4503 のドレイン配線 40 と電気的に接続された電源供給線 4506 と重なる。このとき、4504 で示される領域ではコンデンサが形成され、電流制御用 TFT 4503 のゲート電極 37 にかかる電圧を保持するための保持容量として機能する。保持容量 4504 は、電源供給線 4506 と電気的に接続された半導体膜 4507、ゲート絶縁膜と同一層の絶縁膜（図示せず）及び配線 36 との間で形成される。また、配線 36、第 1 層間絶縁膜と同一の層（図示せず）及び電源供給線 4506 で形成される容量も保持容量として用いることが可能である。なお、電流制御用 TFT のドレインは電源供給線（電源線）4506 に接続され、常に一定の電圧が加えられている。

#### 【0160】

スイッチング用 TFT 4502 及び電流制御用 TFT 4503 の上には第 1 パッシベーション膜 41 が設けられ、その上に樹脂絶縁膜でなる平坦化膜 42 が形成される。平坦化膜 42 を用いて TFT による段差を平坦化することは非常に重要である。後に形成される EL 層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、EL 層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

#### 【0161】

また、43 は反射性の高い導電膜でなる画素電極（EL 素子の陰極）であり、電流制御用 TFT 4503 のドレインに電気的に接続される。画素電極 43 としてはアルミニウム合金膜、銅合金膜または銀合金膜など低抵抗な導電膜またはそれらの積層膜を用いることが好ましい。勿論、他の導電膜との積層構造としても良い。

#### 【0162】

また、絶縁膜（好ましくは樹脂）で形成されたバンク 44a、44b により形成された溝（画素に相当する）の中に発光層 45 が形成される。なお図 24 (A) では、保持容量 4504 の位置を明確にするために一部バンクを省略しており、バンク 44a、44b しか図示していないが、電源供給線 4506 とソース配線（ソース信号線）34 を一部覆うように電源供給線 4506 とソース配線（ソース信号線）34 の間に設けられている。また、ここでは二画素しか図示していないが、R（赤）、G（緑）、B（青）の各色に対応した発光層を作り分けても良い。発光層とする有機 EL 材料としては、共役ポリマー系材料を用いる。代表的なポリマー系材料としては、ポリパラフェニレンビニレン（PPV）系、ポリビニルカルバゾール（PVK）系、ポリフルオレン系などが挙げられる。

#### 【0163】

なお、PPV 系有機 EL 材料としては様々な型のものがあるが、例えば「H. Shenk, H. Becker, O. Gelsen, E. Kluge, W. Kreuder, and H. Spreitzer, "Polymers for Light Emitting Dio

10

20

30

40

50

des", Euro Display, Proceedings, 1999, p. 33-37」や特開平10-92576号公報に記載されたような材料を用いれば良い。

#### 【0164】

具体的な発光層としては、赤色に発光する発光層にはシアノポリフェニレンビニレン、緑色に発光する発光層にはポリフェニレンビニレン、青色に発光する発光層にはポリフェニレンビニレン若しくはポリアルキルフェニレンを用いれば良い。膜厚は30~150nm(好ましくは40~100nm)とすれば良い。

#### 【0165】

但し、以上の例は発光層として用いることのできる有機EL材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせてEL層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。10

#### 【0166】

例えば、本実施例ではポリマー系材料を発光層として用いる例を示したが、低分子系有機EL材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機EL材料や無機材料は公知の材料を用いることができる。

#### 【0167】

本実施例では発光層45の上にPEDOT(ポリチオフェン)またはPAni(ポリアニリン)でなる正孔注入層46を設けた積層構造のEL層としている。そして、正孔注入層46の上には透明導電膜でなる陽極47が設けられる。本実施例の場合、発光層45で生成された光は上面側に向かって(TFTの上方に向かって)放射されるため、陽極は透光性でなければならない。透明導電膜としては酸化インジウムと酸化スズとの化合物や酸化インジウムと酸化亜鉛との化合物を用いることができるが、耐熱性の低い発光層や正孔注入層を形成した後で形成するため、可能な限り低温で成膜できるものが好ましい。20

#### 【0168】

陽極47まで形成された時点でEL素子4505が完成する。なお、ここでいうEL素子4505は、画素電極(陰極)43、発光層45、正孔注入層46及び陽極47で形成されたコンデンサを指す。図24(A)に示すように画素電極43は画素の面積にほぼ一致するため、画素全体がEL素子として機能する。従って、発光の利用効率が非常に高く、明るい画像表示が可能となる。30

#### 【0169】

ところで、本実施例では、陽極47の上にさらに第2パッシベーション膜48を設けている。第2パッシベーション膜48としては窒化珪素膜または窒化酸化珪素膜が好ましい。この目的は、外部とEL素子とを遮断することであり、有機EL材料の酸化による劣化を防ぐ意味と、有機EL材料からの脱ガスを抑える意味との両方を併せ持つ。これによりEL表示装置の信頼性が高められる。

#### 【0170】

以上のように本発明のEL表示装置は図23のような構造の画素からなる画素部を有し、オフ電流値の十分に低いスイッチング用TFTと、ホットキャリア注入に強い電流制御用TFTとを有する。従って、高い信頼性を有し、且つ、良好な画像表示が可能なEL表示装置が得られる。40

#### 【0171】

##### [実施例13]

本実施例では、実施例12に示した画素部において、EL素子4505の構造を反転させた構造について説明する。説明には図25を用いる。なお、図23の構造と異なる点はEL素子の部分と電流制御用TFTだけであるので、その他の説明は省略することとする。

#### 【0172】

図25において、電流制御用TFT4503は公知の方法で形成されたpチャネル型TFTを用いる。

#### 【0173】

10

20

30

40

50

本実施例では、画素電極（陽極）50として透明導電膜を用いる。具体的には酸化インジウムと酸化亜鉛との化合物でなる導電膜を用いる。勿論、酸化インジウムと酸化スズとの化合物でなる導電膜を用いても良い。

#### 【0174】

そして、絶縁膜でなるバンク51a、51bが形成された後、溶液塗布によりポリビニルカルバゾールでなる発光層52が形成される。その上にはカリウムアセチルアセトネット（a c a c Kと表記される）でなる電子注入層53、アルミニウム合金でなる陰極54が形成される。この場合、陰極54がパッシベーション膜としても機能する。こうしてEL素子4701が形成される。

#### 【0175】

本実施例の場合、発光層52で発生した光は、矢印で示されるようにTFTが形成された基板の方に向かって放射される。

#### 【0176】

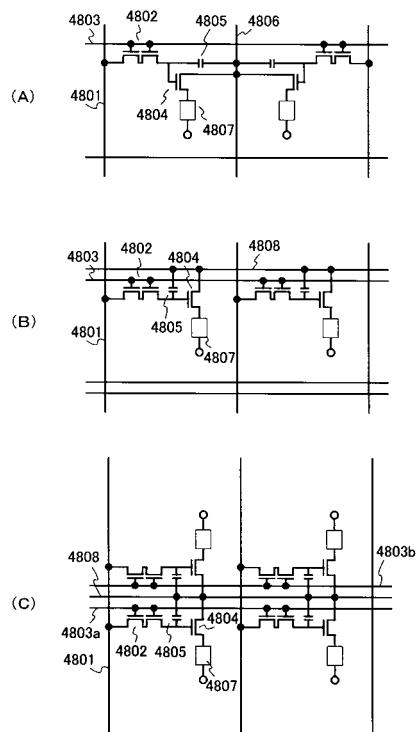

##### [実施例14]

本実施例では、図24（B）に示した回路図とは異なる構造の画素とした場合の例について図26（A）～（C）に示す。なお、本実施例において、4801はスイッチング用TFT4802のソース配線（ソース信号線）、4803はスイッチング用TFT4802のゲート配線（ゲート信号線）、4804は電流制御用TFT、4805は保持容量、4806、4808は電源供給線、4807はEL素子とする。

#### 【0177】

図26（A）は、二つの画素間で電源供給線4806を共通とした場合の例である。即ち、二つの画素が電源供給線4806を中心に線対称となるように形成されている点に特徴がある。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

#### 【0178】

また、図26（B）は、電源供給線4808をゲート配線（ゲート信号線）4803と平行に設けた場合の例である。なお、図26（B）では電源供給線4808とゲート配線（ゲート信号線）4803とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電源供給線4808とゲート配線（ゲート信号線）4803とで専有面積を共有させることができるために、画素部をさらに高精細化することができる。

#### 【0179】

また、図26（C）は、図26（B）の構造と同様に電源供給線4808をゲート配線（ゲート信号線）4803と平行に設け、さらに、二つの画素を電源供給線4808に対し線対称となるように形成する点に特徴がある。また、電源供給線4808をゲート配線（ゲート信号線）4803のいずれか一方と重なるように設けることも有効である。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

#### 【0180】

##### [実施例15]

実施例12に示した図24（A）、図24（B）では電流制御用TFT4503のゲートにかかる電圧を保持するために保持容量4504を設ける構造としているが、保持容量4504を省略することも可能である。実施例12の場合、電流制御用TFT4503のドレン側に、ゲート絶縁膜を介してゲート電極に重なるように設けられたLDD領域を有している。この重なり合った領域には一般的にゲート容量と呼ばれる寄生容量が形成されるが、本実施例ではこの寄生容量を保持容量4504の代わりとして積極的に用いる点に特徴がある。

#### 【0181】

この寄生容量のキャパシタンスは、上記ゲート電極とLDD領域とが重なり合った面積によって変化するため、その重なり合った領域に含まれるLDD領域の長さによって決まる

10

20

30

40

50

。

### 【0182】

また、実施例14に示した図26(A),(B),(C)の構造においても同様に、保持容量4805を省略することは可能である。

### 【0183】

#### [実施例16]

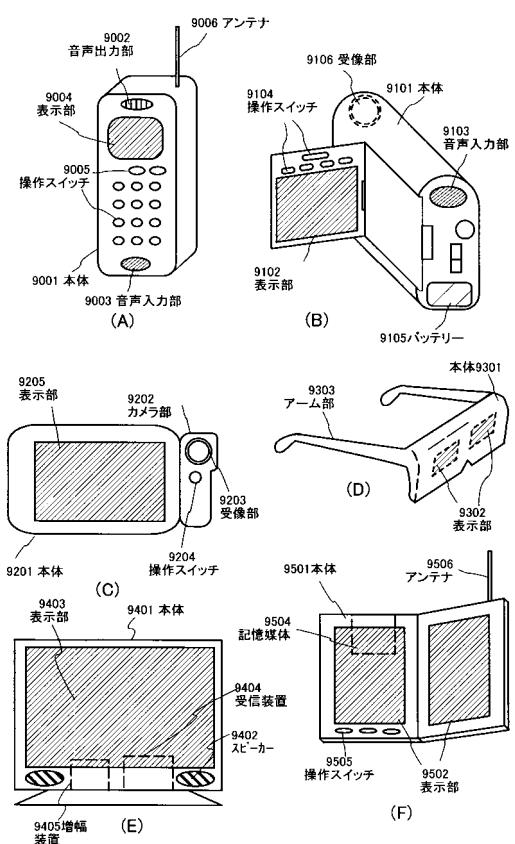

本実施例では、本発明の駆動方法を用いたアクティブマトリクス型液晶表示装置或いはEL表示装置を組み込んだ電子機器について説明する。これらの電子機器には、携帯情報端末(電子手帳、モバイルコンピュータ、携帯電話等)、ビデオカメラ、スチルカメラ、パソコンコンピュータ、テレビ等が挙げられる。それらの一例を図27～図29に示す。

10 ただし、アクティブマトリクス型液晶表示装置については、図27、図28、図29が適用され、EL表示装置については、図27、図28が適用される。

### 【0184】

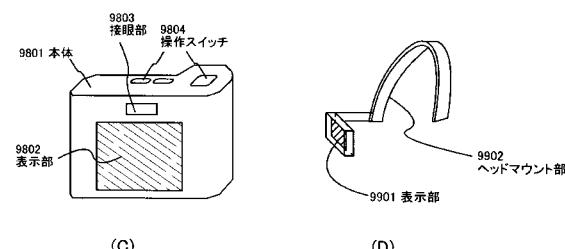

図27(A)は携帯電話であり、本体9001、音声出力部9002、音声入力部9003、表示部9004、操作スイッチ9005、アンテナ9006から構成されている。本発明は表示部9004に適用することができる。

### 【0185】

図27(B)はビデオカメラであり、本体9101、表示部9102、音声入力部9103、操作スイッチ9104、バッテリー9105、受像部9106から成っている。本発明は表示部9102に適用することができる。

20

### 【0186】

図27(C)はパソコンコンピュータの一種であるモバイルコンピュータ或いは携帯型情報端末であり、本体9201、カメラ部9202、受像部9203、操作スイッチ9204、表示部9205で構成されている。本発明は表示部9205に適用することができる。

### 【0187】

図27(D)はヘッドマウントディスプレイ(ゴーグル型ディスプレイ)であり、本体9301、表示部9302、アーム部9303で構成される。本発明は表示部9302に適用することができる。

### 【0188】

図27(E)はテレビであり、本体9401、スピーカー9402、表示部9403、受信装置9404、増幅装置9405等で構成される。本発明は表示部9403に適用することができる。

30

### 【0189】

図27(F)は携帯書籍であり、本体9501、表示部9502、記憶媒体9504、操作スイッチ9505、アンテナ9506から構成されており、ミニディスク(MD)やDVD(Digital Versatile Disc)に記憶されたデータや、アンテナで受信したデータを表示するものである。本発明は表示部9502に適用することができる。

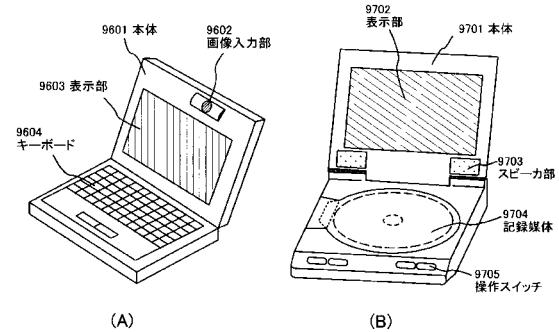

### 【0190】

図28(A)はパソコンコンピュータであり、本体9601、画像入力部9602、表示部9603、キーボード9604で構成される。本発明は表示部9603に適用することができる。

### 【0191】

図28(B)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体9701、表示部9702、スピーカ部9703、記録媒体9704、操作スイッチ9705で構成される。なお、この装置は記録媒体としてDVD、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行なうことができる。本発明は表示部9702に適用することができる。

40

### 【0192】

10

20

30

40

50

図28(C)はデジタルカメラであり、本体9801、表示部9802、接眼部9803、操作スイッチ9804、受像部(図示しない)で構成される。本発明は表示部9802に適用することができる。

**【0193】**

図28(D)は片眼のヘッドマウントディスプレイであり、表示部9901、ヘッドマウント部9902で構成される。本発明は表示部9901に適用することができる。

**【0194】**

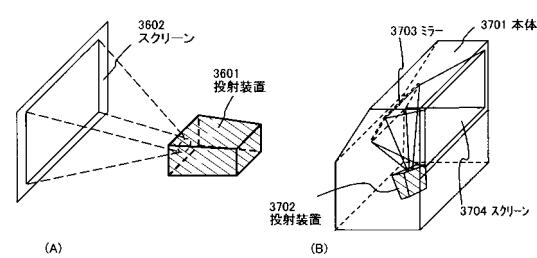

図29(A)はフロント型プロジェクターであり、投射装置3601、スクリーン3602で構成される。

**【0195】**

図29(B)はリア型プロジェクターであり、本体3701、投射装置3702、ミラー3703、スクリーン3704で構成される。

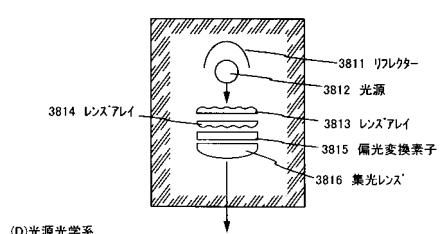

**【0196】**

なお、図29(C)は、図29(A)及び図29(B)中における投射装置3601、3702の構造の一例を示した図である。投射装置3601、3702は、光源光学系3801、ミラー3802、ダイクロイックミラー3803、マイクロレンズアレイ3804、液晶表示部3805、フレネルレンズ3806、投射光学系3807で構成される。投射光学系3807は、投射レンズを含む光学系で構成される。本実施例は単板式の投射装置である。また、図29(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。本発明は液晶表示部3805に適用することができる。

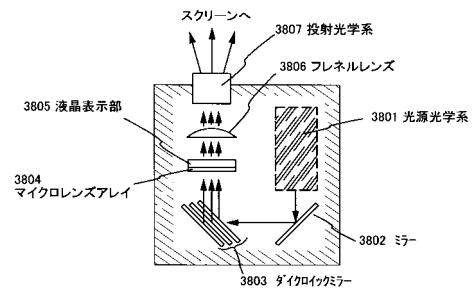

**【0197】**

また、図29(D)は、図29(C)中における光源光学系3801の構造の一例を示した図である。本実施例では、光源光学系3801は、リフレクター3811、光源3812、レンズアレイ3813、3814、偏光変換素子3815、集光レンズ3816で構成される。なお、図29(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

**【0198】**

以上の様に、本発明の適用範囲はきわめて広く、画像表示装置を用いるあらゆる分野の電子機器に適用することが可能である。

**【0199】**

**【発明の効果】**

本発明の駆動方法によると、1つのD/A変換回路で複数のソース信号線を駆動する方法において、外部入力ピン数の増加や、駆動回路の占有面積の増加を招くことなく液晶に印加する電圧をRGB独立に制御することを可能にする。

**【0200】**

また、これによりコントラストの低下を防ぎ、更に、色彩の表現性に優れたクオリティーの高い映像を表示することが可能となる。

**【図面の簡単な説明】**

**【図1】** 本発明の実施形態による駆動回路の概略図である。

**【図2】** 図1の実施形態による動作タイミングの例である。

**【図3】** 実施例1におけるソース信号線駆動回路図である。

**【図4】** 実施例1におけるフリップフロップ回路(FF)と基本ラッチ回路(LAT)の回路図である。

**【図5】** 実施例1におけるP/S変換回路とソース線選択回路の回路図である。

**【図6】** 実施例1におけるD/A変換回路の回路図である。

**【図7】** 実施例1における信号動作タイミングを表す図である。

**【図8】** 実施例2におけるソース信号線駆動回路図である。

**【図9】** 実施例2におけるP/S変換回路とソース線選択回路の回路図である。

10

20

30

40

50

- 【図10】 実施例2における信号動作タイミングを表す図である。

- 【図11】 TFTの作製工程を示す断面図である。

- 【図12】 TFTの作製工程を示す断面図である。

- 【図13】 アクティブマトリクス基板断面図である。

- 【図14】 TFTの作製工程を示す断面図である。

- 【図15】 結晶質シリコン膜の作製工程を示す図である。

- 【図16】 結晶質シリコン膜の作製工程を示す図である。

- 【図17】 結晶質シリコン膜の作製工程を示す図である。

- 【図18】 結晶質シリコン膜の作製工程を示す図である。

- 【図19】 TFTの作製工程を示す断面図である。 10

- 【図20】 液晶表示装置の作製工程を示す断面図である。

- 【図21】 EL表示装置の作製例を示す図である。

- 【図22】 EL表示装置の作製例を示す図である。

- 【図23】 EL表示装置の作製例を示す図である。

- 【図24】 EL表示装置の作製例を示す図である。

- 【図25】 EL表示装置の作製例を示す図である。

- 【図26】 EL表示装置の作製例を示す図である。

- 【図27】 画像表示装置の一例を示す図である。

- 【図28】 画像表示装置の一例を示す図である。

- 【図29】 投影型液晶表示装置の構成を示す図である。 20

- 【図30】 アクティブマトリクス型液晶表示装置の概略図である。

- 【図31】 従来のデジタル方式のソース信号線駆動回路の概略図である。

- 【図32】 1つのD/A変換回路で4本のソース信号線を駆動するソース信号線駆動回路の概略図である。

- 【図33】 液晶表示装置における色別の輝度比 電圧特性の1例である。

#### 【符号の説明】

- 101 ソース信号線駆動回路

102 ゲート信号線駆動回路

103 画素アレイ部

104 各ソース信号線

105 各ゲート信号線

106 各画素のスイッチング素子であるTFT 30

201 シフトレジスタ部

202 シフトレジスタ基本回路

203 ラッチ1回路

204 ラッチ2回路

205 D/A変換回路

301 パラレル/シリアル変換回路

302 ソース線選択回路

【 図 1 】

【 四 2 】

【図3】

【 四 4 】

【 四 5 】

【 図 6 】

【 図 7 】

【 义 8 】

【 図 9 】

【図 10】

【図 11】

401: 基板、402: 下地膜、403: 404: 405: 半導体層、406: ケーブル絶縁膜、407: シリコン膜、408: T膜、

409, 410, 412, 413: リンが付与する不純物の添加(低濃度)、411: 電極、414: 保持容量配線、415～422: リンが付与する不純物領域、

423: 第3の不純物領域、425, 426, 430, 427: 第2の不純物領域、428: 第1の不純物領域、

429, 430: 第3の不純物領域

【図 12】

431～436: ジンスルアブロ、437～440: 第1の導電層、441～445: 第1のゲート電極、446～450: 第1の不純物領域

446～451: ジンスルアブロ、452～456: 第1の導電層、457～460: 第1のゲート電極

【図 13】

CMOS回路

画素ワイヤレス回路

Nチャネル型TFT

Pチャネル型TFT

456: Si膜、457: 第1の層間絶縁膜、458, 459, 460: ソース電極、461, 462: レイテンシ電極、463: ハザードーション電極、

464: 第2の層間絶縁膜、465, 470, 473, 476: フィルタ電極、466a, 466b, 467a, 467b: 第1の不純物領域、468, 476: 第1の不純物領域、

469, 476: 第1の不純物領域(ソース領域)、468, 481: 第3の不純物領域(トライ電極)、471: 第3の不純物領域(ソース領域)、

472: 第3の不純物領域(ソース領域)、473, 476: 第2の不純物領域(トライ電極)、474a, 475a, 475b, 476, 477, 478, 479a, 479b, 480a, 480b: 第2の不純物領域、

477: 第1の不純物領域(ソース領域)

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

(A)

(B)

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図 3 2】

【図 3 3】

---

フロントページの続き

(56)参考文献 特開平11-327518(JP,A)

特開平08-050273(JP,A)

特開平08-263019(JP,A)

特開平09-138670(JP,A)

特開平10-240193(JP,A)

特開2000-020030(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/20

G09G 3/30

G09G 3/36