(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6263538号

(P6263538)

(45) 発行日 平成30年1月17日(2018.1.17)

(24) 登録日 平成29年12月22日(2017.12.22)

(51) Int.Cl.

F 1

G06F 12/08 (2016.01)

H04N 19/433 (2014.01)G06F 12/08 523B

G06F 12/08 559D

H04N 19/433

請求項の数 4 (全 29 頁)

(21) 出願番号 特願2015-531281 (P2015-531281)

(86) (22) 出願日 平成25年9月9日 (2013.9.9)

(65) 公表番号 特表2015-534169 (P2015-534169A)

(43) 公表日 平成27年11月26日 (2015.11.26)

(86) 国際出願番号 PCT/US2013/058765

(87) 国際公開番号 WO2014/039969

(87) 国際公開日 平成26年3月13日 (2014.3.13)

審査請求日 平成28年9月3日 (2016.9.3)

(31) 優先権主張番号 13/606,237

(32) 優先日 平成24年9月7日 (2012.9.7)

(33) 優先権主張国 米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】マルチメディアデータ処理のための方法及びシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

マルチメディアピクセルブロック領域データのフレームについてキャッシュメモリを動作させるプロセスであって、

前記キャッシュメモリを複数のキャッシュバンクに分割することと、

パイプラインスロット内でデータ読み出し及び書き込み動作をスケジューリングすることであって、フロントスロット動作とDMAスロット動作とバックスロット動作とをスケジューリングすることを含む、前記スケジューリングすることと、

前記パイプラインスロットのデータ読み出し及び書き込み動作を連続的に前記キャッシュバンクを介して、前記キャッシュバンク上の複数のバスを介して実行することと、

10

を含み、

前記フロントスロット動作が、メインメモリからフェッチされるべき参照データを決定して前記参照データをフェッチするためにメインメモリフェッチ命令を発生することによりデータを処理することを含み、

前記DMAスロット動作が、前記メインメモリから前記参照データをフェッチして前記フェッチされた参照データをバンク内のピクセルブロック領域に割り当てることによりデータを処理することを含み、

前記バックスロット動作が、マルチメディアデータに関連するデータのフレームを処理するために予想フレームを構成するために前記参照データを読み出すことによりデータを処理することを含む、プロセス。

**【請求項 2】**

請求項 1 に記載のプロセスであって、

前記キャッシュメモリを 3 つのキャッシュバンクの第 1 のキャッシュメモリと 3 つのキャッシュバンクの第 2 のキャッシュメモリとに分割することを更に含む、プロセス。

**【請求項 3】**

請求項 1 に記載のプロセスであって、

前記実行することが、

第 1 のキャッシュバンク上でフロントスロット動作を実行することと、

その後、前記第 1 のキャッシュバンク上で DMA スロット動作を実行する間に第 2 のキャッシュバンク上でフロントスロット動作を実行することと、

その後、前記第 1 のキャッシュバンク上でバックスロット動作を実行する一方で、前記第 2 のキャッシュバンク上で DMA スロット動作を実行する間に第 3 のキャッシュバンク上でフロントスロット動作を実行することと、

その後、前記第 2 のキャッシュバンク上で第 1 のバックスロット動作を実行する間に前記第 3 のキャッシュバンク上で第 1 の DMA スロット動作を実行することと、

その後、前記第 3 のキャッシュバンク上で第 1 のバックスロット動作を実行することと、

、

を含む、プロセス。

**【請求項 4】**

請求項 1 に記載のプロセスであって、

前記実行することが、

第 1 のキャッシュバンク上で第 1 のフロントスロット動作を実行することと、

その後、前記第 1 のキャッシュバンク上で第 1 の DMA スロット動作を実行する間に第 2 のキャッシュバンク上で第 1 のフロントスロット動作を実行することと、

その後、前記第 1 のキャッシュバンク上で第 1 のバックスロット動作を実行する一方で、前記第 2 のキャッシュバンク上で第 1 の DMA スロット動作を実行する間に第 3 のキャッシュメモリ上でフロントスロット動作を実行することと、

その後、前記第 2 のキャッシュバンク上で第 1 のバックスロット動作を実行する間に前記第 3 のキャッシュバンク上で第 1 の DMA スロット動作を実行することと、

その後、前記第 3 のキャッシュバンク上で第 1 のバックスロット動作を実行することと、

、

前記第 1 のキャッシュバンク上で第 2 の DMA スロット動作を実行する前に前記第 1 のキャッシュバンクから全てのデータを削除することと、

を含む、プロセス。

**【発明の詳細な説明】****【技術分野】****【0001】**

本願はデータ処理の分野に関する。

**【背景技術】****【0002】**

例示のシナリオにおいて、マルチメディアデータ処理に関する技術の急速な進歩が、様々なマルチメディアプロセッサのそれぞれの計算能力への需要を増大させる可能性がある。マルチメディアデータ処理は、圧縮目的でのマルチメディアデータの符号化に関与し得る。マルチメディアデータの圧縮は、記憶の間メモリを節約するため、又は伝送の間利用可能な帯域幅を効率良く利用するために実行され得る。マルチメディアデータは、マルチメディアデータの圧縮を達成するのに十分な符号化メカニズムを用いて符号化され得る。マルチメディアデータは、その後、表示 / 閲覧のため圧縮解凍（例えば復号）され得る。

**【0003】**

さらに、例示のシナリオにおいて、様々なビデオコーディングパラダイムが、基準フレームに基づくマルチメディアデータに対応するフレームの符号化、及びそれによる、記憶

10

20

30

40

50

容量の最適化、並びにマルチメディアプロセッサの性能強化も含み得る。例示のシナリオにおいて、マルチメディアデータ処理は、動き補償の実行に関与し得、この処理では、基準フレーム（例えば以前に復号され、メモリ内に記憶されたフレーム）に関連付けられた基準ピクセルが、メモリからフェッチされ、予測フレームを形成するために補間される。予測フレームは、現行フレームに対応する残余サンプルを取得するために現行フレームから差し引かれ得る。その後残余サンプルは、現行フレームの符号化のために符号化され得る。例示のシナリオにおいて、動き補償を実施する一方で、基準ピクセルは（フレームの様々な部分を符号化するために）メモリからランダムにフェッチされ、フェッチされた基準ピクセルの中にかなりの程度の重複が存在する可能性がある。例示のシナリオによれば、基準ピクセルをフェッチすることのランダム性の結果として、メモリ帯域幅消費及び電力損失が増加する可能性がある。

#### 【発明の概要】

##### 【0004】

マルチメディアデータ処理のための方法及びシステムが開示される。一実施形態において、マルチメディアフレームを処理するために、マルチメディアフレームは複数のブロック区画に分割され、各区画は複数のピクセルブロックを含む。一実施形態において、マルチメディアフレームの第1のブロック区画に関連付けられた複数のピクセルブロックについて、第1の基準領域が決定される。一実施形態において、第1の基準領域をメモリからフェッチする前に、第1の基準領域の存在が第1のキャッシュにおいて決定される。第1の基準領域が第1のキャッシュにおいて利用不能であると決定される場合、第1の基準領域の存在が第2のキャッシュにおいてチェックされる。第1の基準領域が第2のキャッシュにおいて利用不能であると決定される場合、第1の基準領域はメモリからフェッチされる。

##### 【0005】

一実施形態において、この方法は、基準データに対応する複数の基準ピクセルブロックをキャッシュするように、第1のキャッシュにおける1つ又は複数のピクセルブロック領域を定義することを含む。複数の基準ピクセルブロックの中からの基準ピクセルブロックが、所定の基準に基づいて、1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に割り当てられる。マルチメディアデータのマルチメディアフレームに関連付けられる複数のピクセルブロックを処理するために基準データの検索を促進するように、基準ピクセルブロックはピクセルブロック領域に基づいてタグに関連付けられる。

##### 【0006】

一実施形態において、基準データの検索は、第1の基準領域に関連付けられるタグ情報を、1つ又は複数のピクセルブロック領域に関連付けられるスパン情報と比較することによって、第1の基準領域を含む可能性がある1つ又は複数のピクセルブロック領域の中からピクセルブロック領域を識別することを含む。さらに、識別された1つ又は複数のピクセルブロック領域において、第1の基準領域に関連付けられる1つ又は複数の基準ピクセルブロックの存在が決定される。一実施形態において、1つ又は複数の基準ピクセルブロックの存在を決定することは、スパン情報と、基準データに関連付けられる基準フレーム内の第1の基準領域の場所とに基づいて、識別された1つ又は複数のピクセルブロック領域の各々内の第1の基準領域のあり得るオフセットを決定することを含む。識別された1つ又は複数のピクセルブロック領域において決定されたあり得るオフセットでの第1の基準領域の存在が、決定されたあり得るオフセットでの各基準ピクセルブロックに関連付けられる複数の利用可能性タグをチェックすることによって決定され得る。

##### 【0007】

一実施形態において、第1の基準領域に関連付けられる1つ又は複数の基準ピクセルブロックの中からの基準ピクセルブロックをメモリからフェッチするための最小細分性は、メモリに関連付けられるプリフェッチバッファにおけるキャッシュの最小細分性とマッチングする。一実施形態において、基準フレーム内の第1の基準領域に関連付けられる1つ又は複数の基準ピクセルブロックに近接し、基準フレーム内に矩形領域を形成する、1つ

10

20

30

40

50

又は複数の追加の基準ピクセルブロックが、共にフェッチされる。一実施形態において、1つ又は複数の追加の基準ピクセルブロック及び第1の基準領域は、基準フレーム内の複数のブロック区画の中からのブロック区画に対応する。一実施形態において、1つ又は複数の追加の基準ピクセルブロック及び第1の基準領域は、基準フレーム内の近接するブロック区画に対応する。

【0008】

一実施形態において、マルチメディアデータを処理するように構成されたシステムが開示される。このシステムは、メモリ、キャッシュユニット、及び処理ユニットを含む。メモリは、基準データに対応する1つ又は複数の基準フレームを記憶するように構成される。キャッシュユニットは、メモリに通信可能に関連付けられ、第1のキャッシュ及び第2のキャッシュを含む。処理ユニットは、メモリ及びキャッシュユニットに通信可能に関連付けられ、基準データに対応する複数の基準ピクセルブロックをキャッシュするように、第1のキャッシュにおける1つ又は複数のピクセルブロック領域を定義するように構成される。処理ユニットはさらに、(1)所定の基準に基づいて、複数の基準ピクセルブロックの中からの基準ピクセルブロックを、1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に割り当てるように、及び、(2)マルチメディアフレームに関連付けられる複数のピクセルブロックを処理するために基準データの検索を促進するように、ピクセルブロック領域に基づいて、基準ピクセルブロックをタグに関連付けるように構成される。

【0009】

一実施形態において、コンピュータ可読媒体が開示され、このコンピュータ可読媒体は、実行されたときにマルチメディアデータ処理のための方法をコンピュータに実行させる、命令セットを記憶する。この方法は、基準データに対応する複数の基準ピクセルブロックをキャッシュするように、第1のキャッシュにおいて1つ又は複数のピクセルブロック領域を定義することを含む。基準データは基準フレームに関連付けられ得る。また、この方法は、複数の基準ピクセルブロックの中からの基準ピクセルブロックを、所定の基準に基づいて、1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に割り当てるなどを含む。また、この方法は、マルチメディアフレームに関連付けられる複数のピクセルブロックを処理するために基準データの検索を促進するように、ピクセルブロック領域に基づいて基準ピクセルブロックをタグに関連付けることを含む。

【図面の簡単な説明】

【0010】

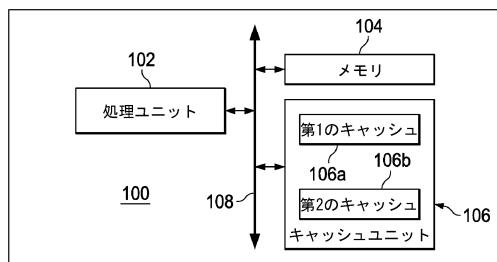

【図1】一実施形態に従った、マルチメディアデータを処理するように構成された例示のシステムのブロック図である。

【0011】

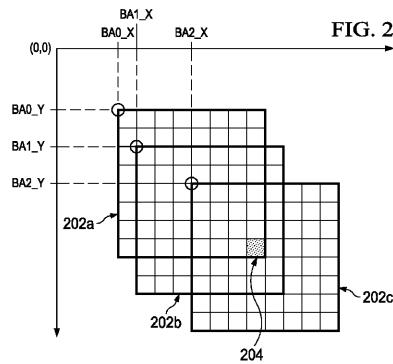

【図2】一実施形態に従った、第1のキャッシュにおいて定義された複数の例示のピクセルブロック領域を示す。

【0012】

【図3A】一実施形態に従った、図1のシステムを用いることなどによる、複数の基準データフェッチ間での重複の例示的活用を示す。

【図3B】一実施形態に従った、図1のシステムを用いることなどによる、複数の基準データフェッチ間での重複の例示的活用を示す。

【図3C】一実施形態に従った、図1のシステムを用いることなどによる、複数の基準データフェッチ間での重複の例示的活用を示す。

【0013】

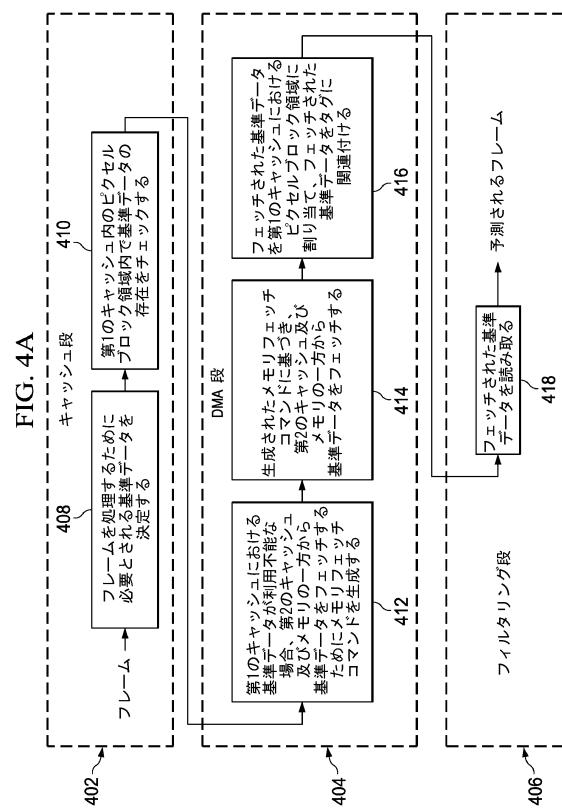

【図4A】一実施形態に従った、マルチメディアデータに関連付けられたマルチメディアフレームの処理を示す例示のプロセスフローの簡略化された概要を示す。

【0014】

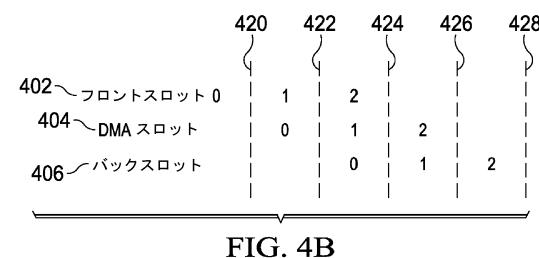

【図4B】一実施形態に従った、マルチメディアフレーム処理の間の、第1のキャッシュに関連付けられた読み取り／書き込み動作の例示のスケジューリングを示す。

10

20

30

40

50

## 【0015】

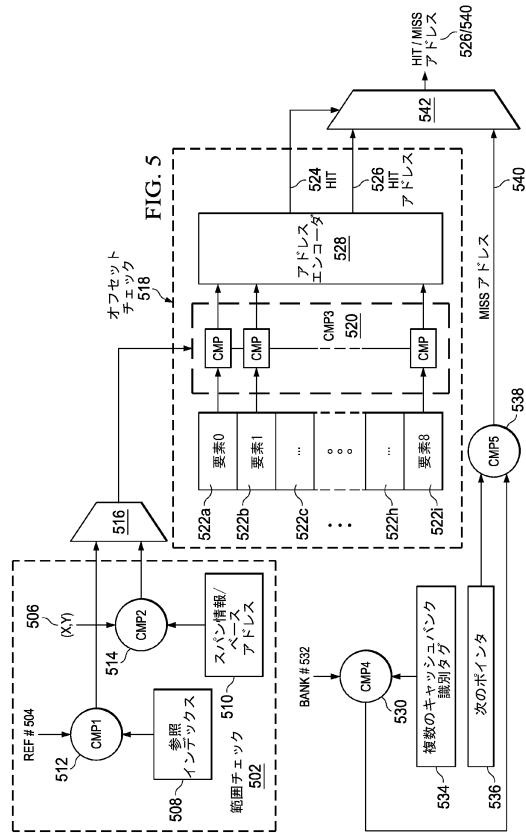

【図5】一実施形態に従って、マルチメディアフレームに関連付けられる複数のピクセルブロックを処理するための基準データの検索の例示のプロセスを示す。

## 【0016】

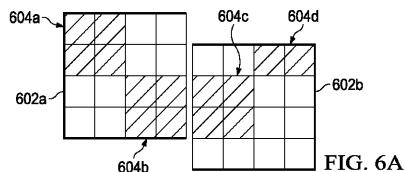

【図6A】一実施形態に従った、基準データに関連付けられる基準フレーム内で互いに近接する基準ピクセルブロックの例示のフェッチを示す。

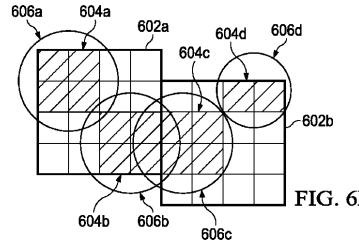

【図6B】一実施形態に従った、基準データに関連付けられる基準フレーム内で互いに近接する基準ピクセルブロックの例示のフェッチを示す。

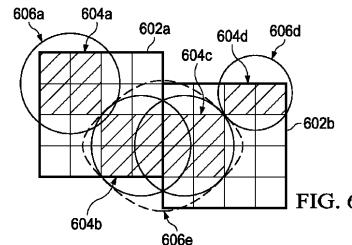

【図6C】一実施形態に従った、基準データに関連付けられる基準フレーム内で互いに近接する基準ピクセルブロックの例示のフェッチを示す。

10

## 【0017】

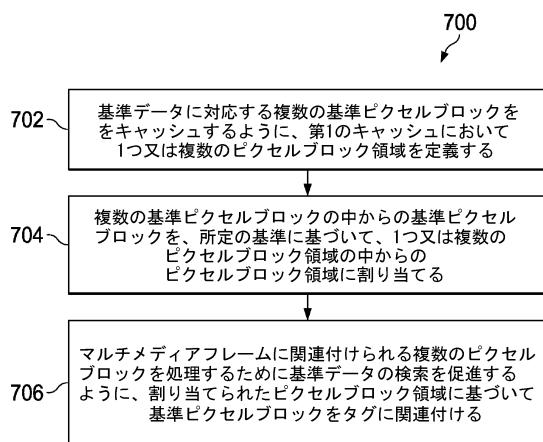

【図7】一実施形態に従った、マルチメディアデータ処理の例示の方法を示すフローチャートである。

## 【0018】

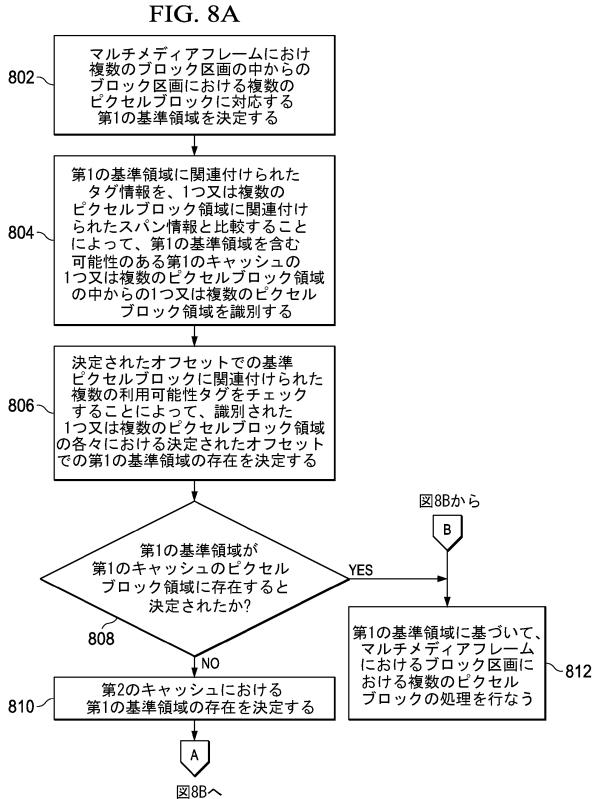

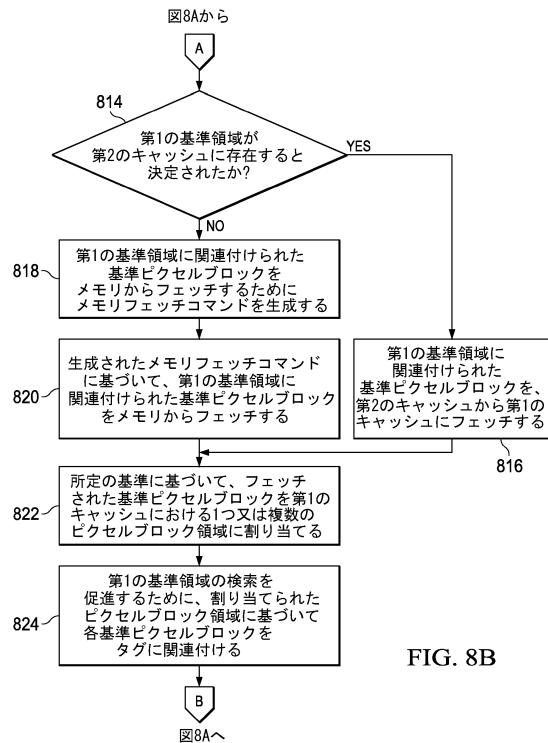

【図8A】一実施形態に従って、マルチメディアフレームの処理を行なうための基準データ検索の例示の方法を示すフローチャートを集合的に示す。

【図8B】一実施形態に従って、マルチメディアフレームの処理を行なうための基準データ検索の例示の方法を示すフローチャートを集合的に示す。

## 【発明を実施するための形態】

## 【0019】

20

例示のシナリオにおいて、マルチメディアデータ処理は、マルチメディアデータに対応するフレームに対して動き補償を行なうことに関与し得る。例示のシナリオにおいて、動き補償を行なう一方で、基準ピクセルが（フレームの様々な部分を符号化するために）メモリからランダムにフェッチされ、フェッチされた基準ピクセルの中にかなりの程度の重複が存在する。例示のシナリオによれば、基準ピクセルをフェッチすることのランダム性の結果として、メモリ帯域幅消費及び電力損失が増加する可能性がある。

## 【0020】

図1は、一実施形態に従ってマルチメディアデータを処理するように構成された例示のシステム100のブロック図である。一実施形態において、システム100は、マルチメディアデータの処理のためのビデオコーデック（例えばビデオエンコーダ／デコーダ）であるように構成される。一実施形態において、システム100はマルチメディアシステム内に含まれるように構成される。一実施形態において、システム100は、マルチメディアシステムの外部にあるように構成され、マルチメディアシステムに通信可能に関連付けられる。マルチメディアシステムの例には、（1）例えば、携帯電話、デジタルビデオカメラ、及びデジタルカムコーダなどのマルチメディアデバイス、（2）例えば、パーソナルコンピュータ、ラップトップ、及び携帯情報端末などのデータ処理デバイス、及び、（3）例えば、セットトップボックス、デジタルビデオディスク（DVD）プレーヤ、及びビデオネットワークサーバなどの家庭用電子機器が含まれ得るが、これらに限定されない。例示のシナリオによれば、システム100は、マルチメディアデータの処理を（順次及び／又はその他の方式で）行なうように、命令セットを実行することが可能な任意の機械であり得る。

30

## 【0021】

マルチメディアデータは、システム100によってメディアキャプチャデバイスから受信され得る。メディアキャプチャデバイスの例は、ビデオカメラ又はカムコーダを含み得る。例えば、メディアキャプチャデバイスは、例えば、スタンドアロンデバイス、又は、スマートフォンなどのモバイルデバイスの一部、或いは、例えば、パーソナルコンピュータ、ラップトップデバイス、又は携帯情報端末（PDA）などのデータ処理デバイスであり得る。マルチメディアデータはまた、システム100によって、スタンドアロンデバイス又はメディアキャプチャデバイスの一部であり得る（例えば、ハードウェア、ソフトウェア、及び／又はファームウェアのいずれかに実装され得る）トランスコーディングシス

40

50

テムから受信され得る。

【0022】

例示のシナリオによれば、マルチメディアデータは、マルチメディアフレーム（以下、同じ意味で「フレーム」と呼ばれる）のシーケンスを含み得、フレームのシーケンスの中からの各フレームは、マルチメディアデータの複数のブロック（例えばマクロブロック）を含み得る。マルチメディアデータの例は、オーディオデータ、ビデオデータ、オーディオビデオ（A/V）データ、イメージデータ、テキストデータ、及びそれらの組み合わせを含み得るが、これらに限定されない。マルチメディアデータの処理の例は、符号化／復号化目的で、マルチメディアデータに対応するフレームに対して動き補償を実施することを含み得る。マルチメディアデータのフレームに対して動き補償を実施することは、基準フレーム（例えば、以前に復号されたフレーム）に関してフレームを符号化／復号化することに関与する。一実施形態において、基準フレームに関連付けられる1つ又は複数の基準ピクセルが、フレームを符号化するために予測フレームを構成するように補間され得る。予測フレームは、フレームに対応する残余サンプルを取得するために、フレームから差し引かれ得る。残余サンプルは、その後、フレームを符号化するために符号化され得る。

【0023】

システム100は、処理ユニット102、メモリ104、キャッシュユニット106、及びバス108を含む。一実施形態において、処理ユニット102は、マルチコアプロセッサ、シングルコアプロセッサ、或いは、1つ又は複数のマルチコアプロセッサ及び1つ又は複数のシングルコアプロセッサの組み合わせとして具現化され得る。例えば、処理ユニット102は、コプロセッサ、マイクロプロセッサ、コントローラ、デジタル信号プロセッサ（DSP）、付属のDSPを備えるか又は備えない処理回路などの、様々な処理デバイス、或いは、例えば、特定用途向け集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）、マイクロコントローラユニット（MCU）、ハードウェアアクセラレータ、専用コンピュータチップなどの集積回路を含む様々な他の処理デバイスのうちの1つ又は複数として具現化され得る。一実施形態において、処理ユニット102はハードコード化された機能性を実行するように構成され得る。一実施形態において、処理ユニット102はソフトウェア命令の執行者として具現化され、命令は、特に、命令が実行されるとき本明細書で説明されるアルゴリズム及び／又は動作を実行するように、処理ユニット102を構成することができる。処理ユニット102は、とりわけ、クロック、算術論理ユニット（ALU）、及び、処理ユニット102の動作をサポートするように構成された論理ゲートを含み得る。一実施形態において、メモリ104はマルチメディアデータを記憶するように構成される。一実施形態において、メモリ104は、マルチメディアデータに関連付けられたマルチメディアフレームを処理するために、基準データを（例えば、複数の基準フレームの形式で）記憶するように構成される。

【0024】

一実施形態において、マルチメディアデータの復号されたフレームが、基準データに対応する基準フレームとしてメモリ104に記憶され得る。メモリ104の例は、ランダムアクセスメモリ（RAM）、デュアルポートRAM、同期ダイナミックRAM（SDRAM）、ダブルデータレートSDRAM（DDRSDRAM）などを含むが、これらに限定されない。一実施形態において、キャッシュユニット106は、メモリ104に記憶された頻繁に用いられる基準データをキャッシュするように構成される。メモリ104に関連付けられる制限された帯域幅及び高いトラフィック条件の結果として、基準データをキャッシュユニット106に記憶することで、システム100に関連付けられた処理性能を向上させる。キャッシュユニット106は、第1のキャッシュ106a及び第2のキャッシュ106bを含む。一実施形態において、第1のキャッシュ106aは、基準データをキャッシュするために実装され得る1つ又は複数のキャッシュバンクを含み得る。より具体的に言えば、第1のキャッシュ106aに関連付けられる記憶スペースが（例えば、物理的区画又は仮想区画に）区分されるものとみなされ得、こうした各区画は、キャッシュバンクと呼ばれ得、基準データをキャッシュするために用いられ得る。キャッシュバンクは

10

20

30

40

50

、本明細書ではさらに図4Bを参照して説明する。一実施形態において、第2のキャッシュ106bは、基準データをキャッシュするために実装され得る1つ又は複数のキャッシュバンクを含み得る。一実施形態において、処理ユニット102、メモリ104、及びキャッシュユニット106は、通信可能に関連付けられ、バス108を介して又は通じて互いに結合又は接続されるように構成される。バス108の例は、データバス、アドレスバス、制御バスなどを含み得るが、これらに限定されない。

#### 【0025】

バス108は、例えば、シリアルバス、双方向バス、又は単方向バスであり得る。マルチメディアデータ処理の場合、マルチメディアデータに対応する各フレームは、複数のピクセルブロックに分割され得る。例えば、フレームは、例えばマクロブロックと呼ばれ得る、複数の $16 \times 16$ ピクセルブロックに分割され得る。こうした各マクロブロックは、例えば、各区画が4つの $4 \times 4$ ピクセルブロックを含み得る4つの区画などの部分にさらに区分され得る。ピクセルブロックのこうした各区画は、本明細書ではブロック区画と呼ばれ得る。上記で説明したように、フレームを処理するために、フレームのブロック区画に関連付けられる複数のピクセルブロックについてなど、フレームの様々な部分について、基準データがフェッチされ得る。一実施形態において、処理ユニット102は、マルチメディアデータのフレームのブロック区画に関連付けられる複数のピクセルブロックを処理するために実装されるべき基準データを決定するように構成される。

#### 【0026】

上記で説明したように、基準データは1つ又は複数の基準フレームの形式でメモリ104に記憶される。1つ又は複数の基準フレームの各々は、1つ又は複数の基準ピクセルブロックを含む。「基準ピクセルブロック」という用語は、例えば、マルチメディアデータのフレームに関連付けられる基準フレーム内の「 $m \times n$ 」ブロックのピクセルを指すものと解釈され得、ここで、 $m$ 及び $n$ は正の整数であることに留意されたい。マルチメディアデータのフレームの各ブロック区画に関連付けられる複数のピクセルブロックを処理するために実装されるべき基準データを決定することは、処理目的で利用され得る基準フレームにおける基準ピクセルブロックを決定することを含み得る。一実施形態において、メモリ104からフェッチされた基準ピクセルブロックは、基準データへの今後のアクセスを容易にするために、キャッシュユニット106に記憶される。

#### 【0027】

一実施形態において、処理ユニット102は、以前にメモリ104からフェッチされた基準データに対応する複数の基準ピクセルブロックをキャッシュするように、キャッシュユニット106に関連付けられる第1のキャッシュ106aにおける1つ又は複数のピクセルブロック領域を定義するように構成される。ピクセルブロック領域は、1つ又は複数の基準ピクセルブロックをキャッシュすることが可能で、第1のキャッシュ106a内の記憶スペースの割り振りとみなされ得る。1つ又は複数のこうした記憶スペースは、メモリ104からフェッチされた複数の基準ピクセルブロックをキャッシュするために、第1のキャッシュ106a内で定義され得る。一実施形態において、第1のキャッシュ106aの1つ又は複数のキャッシュバンクの中からのキャッシュバンクに、ピクセルブロック領域が関連付けられ得る。一実施形態において、定義されるべきピクセルブロック領域の数は、ビデオ圧縮パラダイムに基づいて決定され得る。ビデオ圧縮パラダイムの例は、ビデオコーディング専門家グループ(VCEG)、H.120、H.261、動画像専門家グループ(MPEG)、MPEG-1 Part 2、H.262、又はMPEG-2 Part 2、H.263、MPEG-4 Part 2、H.264、又はMPEG-4 AVC、VC-2(ディラック)、高性能ビデオコーディング(HEVC)などを含むが、これらに限定されない。

#### 【0028】

一実施形態において、各ピクセルブロック領域は、スパン情報、ベースアドレス、キャッシュバンク識別タグ、及び/又は参照インデックスを介して定義される。スパン情報は、各ピクセルブロック領域の長さ方向(例えば高さ)及び幅方向(例えば幅)に沿った寸

10

20

30

40

50

法を示す。ベースアドレスは、基準フレームによって定義されたスペース内で事前に決定された起点からの各ピクセルブロック領域の左上アドレス（例えば、左上ピクセル位置のピクセル座標）から又はこれに関してオフセットされ、基準フレームによって定義されたスペース内のピクセルブロック領域の局所性を示す。各ピクセルブロック領域のベースアドレスは、 $x$  及び  $y$  座標に関して表される。キャッシュバンク識別タグは、各ピクセルブロック領域が関連付けられるキャッシュバンクを示す。参照インデックスは、各ピクセルブロック領域に関連付けられる基準フレームを示す。例えば、メモリ 104 内の基準データが 32 の基準フレームを含み、ピクセルブロック領域が 32 の基準フレームのうちの第 5 の基準フレームに関連付けられる場合、ピクセルブロック領域の参照インデックスは、基準フレーム第 5 番を示し得、ピクセルブロック領域に含まれる基準ピクセルブロックは 10 ここからフェッチされる。

#### 【0029】

一実施形態において、処理ユニット 102 はまた、基準データに対応する複数の基準ピクセルブロックの中からの基準ピクセルブロックを、1 つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に割り当てるよう構成される。一実施形態において、処理ユニット 102 は、所定の基準に基づいて、基準ピクセルブロックをピクセルブロック領域に割り当てる。一実施形態において、所定の基準は、基準フレームによって定義されたスペース内の基準ピクセルブロックの局所性を含むが、これに限定されない。

#### 【0030】

一実施形態において、各基準ピクセルブロックは、マルチメディアデータのフレームに関連付けられる複数のピクセルブロックを処理するために基準データの検索を促進するよう、ピクセルブロック領域に基づいてタグに関連付けられる。一実施形態において、タグは、ピクセルブロック領域内の基準ピクセルブロックの位置の指示を提供するよう構成され得る。一実施形態において、タグは、対応するピクセルブロック領域に関連付けられるベースアドレスからの基準ピクセルブロックのオフセットに基づいて定義され得る。例示の実施形態において、各ピクセルブロック領域の幅及び高さは 32 ピクセル × 32 ピクセルであり、ピクセルブロック領域の細分性は 4 × 4 ピクセルブロックである。したがって、8 つの 4 × 4 基準ピクセルブロックを、 $x$  及び  $y$  方向の各々に沿って含めることができる。各 4 × 4 基準ピクセルブロックは、対応するピクセルブロック領域のベースアドレスからのオフセットに基づいて、タグに関連付けられ得る。 $x$  及び  $y$  方向に沿ったオフセットは各々 3 ビットを利用するため、各タグのサイズは 6 ビットである。タグに基づいて 1 つ又は複数のピクセルブロック領域の各々において 4 × 4 ピクセルブロックを検索することができる。

#### 【0031】

様々な例示のキャッシュ技法において、メモリ内の基準データは、4 × 4 基準ピクセルブロックの形式に編成され、メモリ内の 4 × 4 基準ピクセルブロックの各々は、基準フレームによって定義されたスペース内の  $x$  方向に沿った変位及び  $y$  方向に沿った変位を示すタグに関連付けられる。基準フレームの最大サイズが、1 つ又は複数のマルチメディアコーディングパラダイムに従って 8 K × 8 K ピクセルであると考えると、 $x$  及び  $y$  方向に沿った 4 × 4 基準ピクセルブロックの数は各々 2 K となる。4 × 4 ピクセルブロックは  $x$  及び  $y$  座標に基づいてタグ付けされるため、タグのサイズは  $x$  で 11 ビット、 $y$  で 11 ビット、合計 22 ビットとなる。また、メモリからフェッチされた各 4 × 4 ピクセルブロックは、4 × 4 ピクセルブロックが属する基準フレームに関してタグ付けされる。例えば H.264 などの、マルチメディアコーディングパラダイムのいくつかは、メモリ内に最大 32 までの基準フレームが可能である。32 の基準フレームに基づいてタグ付けすると、タグに 5 ビットを追加することになる。したがって、32 の基準フレームが用いられる場合、各基準ピクセルブロックに対するタグのサイズは 27 ビットであり得る。一実施形態において、良好なキャッシュを行なうために約 288 のタグが用いられる。各タグのサイズは 27 ビットであるため、キャッシュの間 288 の 27 ビット比較が必要である。基準データを決定及びフェッチするために 288 の 27 ビット比較を行なうことで、大量の電力 40 50

が損失することになる。第1のキャッシュ106aにおいてピクセルブロック領域を定義すること、及び、対応するピクセルブロック領域のベースアドレスからのオフセットとして基準ピクセルブロックをタグ付けすることにより、タグのサイズは27ビットから6ビットに減少し、それによって比較コストが低減され、電力消費のかなりの節約につながる。

#### 【0032】

一実施形態において、メモリ104から1つ又は複数の基準ピクセルブロックの各々をフェッチするための最小細分性が、メモリ104の最適な性能のためにメモリ104に関連付けられるプリフェッチバッファにおいてキャッシュするための最小細分性とマッチングする。例えば、プリフェッチバッファにおけるデータ編成がロックベースの場合、基準ピクセルブロックのフェッチはロック単位で整合され、それによって基準データのフェッチが最適化される。同様に、プリフェッチバッファにおけるデータ編成がラインベースである（例えば、基準データフェッチのローが順次フェッチされる）場合、基準ピクセルのフェッチはラインベースの基準データフェッチと整合される。一実施形態において、各ピクセルブロック領域が疎に満たされ、選ばれた少数の基準ピクセルブロックエントリ（要素とも呼ばれる）を含む。一実施形態において、1つ又は複数のピクセルブロック領域の各々が9つの要素を含み、すなわち、各ピクセルブロック領域が9つの基準ピクセルブロックに関連付けられる。一実施形態において、ピクセルブロック領域に関連付けられる各要素には、対応する基準フレーム内のその位置に基づいて、ピクセルブロック領域内の特定の位置が割り当てられる。

10

20

#### 【0033】

一実施形態において、単一の基準フレームに属する基準ピクセルブロックが、1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に割り当てられる。一実施形態において、各ピクセルブロック領域は、第1のキャッシュ106aに関連付けられる1つ又は複数のキャッシュバンクの中からのキャッシュバンク内で定義される。一実施形態において、中で各ピクセルブロック領域が定義されたキャッシュバンクを示すように、各ピクセルブロック領域にキャッシュバンク識別タグが関連付けられる。

#### 【0034】

一実施形態において、第2のキャッシュ106bは、マルチメディアデータの1つ又は複数の後続のブロック区画の処理の間基準データを利用可能とするために、マルチメディアデータに関連付けられる複数のブロック区画の中からの第1のブロック区画に関連付けられる基準データをキャッシュするように編成される。一実施形態において、マルチメディアデータのフレーム内のピクセルブロックは、ラスター走査順に処理される。「ラスター走査順」という用語は、例えば、左から右及び上から下への順を指すものと解釈され得ることに留意されたい。したがって、或るローにおけるピクセルブロックが左から右へと処理された後、マルチメディアデータのフレーム内の後続のローにおけるピクセルブロックが処理される。フレームに関連付けられる1つ又は複数の後続ローの処理の間、1つ又は複数の前のローに関連付けられる基準データは、第1のキャッシュ106aから既に削除されている可能性がある。しかしながら、フレームの近接口におけるピクセルブロックは、基準データフェッチに共通性を有し得る。本明細書で開示される第2のキャッシュ106bは、フレームの近接口に対する基準データフェッチの共通性の活用を可能にする。一実施形態において、第2のキャッシュ106bは、システム100の構成に応じて、フレームのブロック区画の幅と同等の幅方向に沿ったスパンと、長さ方向（例えば高さ）に沿った可変寸法とを有するように定義される。

30

40

#### 【0035】

一実施形態において、基準データに関連付けられる基準ピクセルブロックが第2のキャッシュ106bのスパン内にある場合、メモリ104からフェッチされた基準データは第2のキャッシュ106bにおいてポピュレートされる。一実施形態において、第1のキャッシュ106aにキャッシュされた基準データは、第1のキャッシュ106aにおける基準データの満了時に第2のキャッシュ106bにおいてポピュレートされる。一実施形態

50

において、キャッシュバンクに記憶された基準データのすべて（又は事前に選択された量）がキャッシュバンクから読み取られると、第1のキャッシュ106aにキャッシュされた基準データは一度に1つのキャッシュバンクを満了にする。フレームの後続ローの処理の間、フェッチされた基準ピクセルブロックをキャッシュするために、第2のキャッシュ106b内のスペースの利用可能性が決定される。第2のキャッシュ106b内のスペースが利用可能であると決定された場合、フェッチされた基準ピクセルブロックは第2のキャッシュ106bにおいてポピュレートされる。一実施形態において、第2のキャッシュ106b内のスペースが利用不能であると決定された場合、第2のキャッシュ106bにおける1つ又は複数の以前にキャッシュされた基準ピクセルブロックは削除される。1つ又は複数の以前にキャッシュされた基準ピクセルブロックを削除すると、フェッチされた基準ピクセルブロックをキャッシュするために、第2のキャッシュ106bの起点が、所定のマージンだけシフトされる。起点は、基準データを第2のキャッシュ106bの別のロー内に書き込む一方で、第2のキャッシュ106bのローから基準データを同時に読み取ることを促進するためにシフトされる。一実施形態において、第2のキャッシュ106bはブロックベースで編成され、第2のキャッシュ106bにおいてポピュレートされた基準データは、水平及び／又は垂直方向の変位でタグ付けされる。10

#### 【0036】

一実施形態において、第2のキャッシュ106bはラインベースで編成される。また、一実施形態において、第1のキャッシュ106aに基準データが存在しないと決定された場合、基準データは第2のキャッシュ106bにおいて検索される。第2のキャッシュ106bに基準データが存在すると決定された場合、基準データは、後の基準ピクセルフェッチのために第1のキャッシュ106aのピクセルブロック領域のうちの1つに割り当てられる。しかしながら、一実施形態によれば、基準データが、利用不能である、すなわち第2のキャッシュ106bに存在しない、と決定された場合、基準データはメモリ104からフェッチされる。第2のキャッシュ106bから基準データをフェッチするために用いられる処理サイクルの数（例えば、10処理サイクル）は、メモリ104から基準データをフェッチするために用いられる処理サイクルの数（例えば、100処理サイクル）よりも少ない。一実施形態において、第2のキャッシュ106bは、メモリ104内の各エントリが第2のキャッシュ106bにおける1つの特定位置でキャッシュされるように、「一方向連想（associative）／直接マッピング」される。一実施形態において、基準データの複数の輝度（以下「ルマ」と呼ぶ）成分及び複数のクロミナンス（以下「クロマ」と呼ぶ）成分が、第2のキャッシュ106b及び／又はメモリ104に別々にキャッシュされる。一実施形態において、ルマ成分はメモリ104及び／又は第2のキャッシュ106bにおいて $4 \times 4$ ピクセルブロックとして編成され、クロマ成分は $8 \times 2$ ピクセルブロックとして編成される。2030

#### 【0037】

一実施形態において、処理ユニット102は、基準フレーム内の第1の基準領域に関連付けられた1つ又は複数の基準ピクセルブロックに近接し、基準フレーム内に矩形領域を形成する、1つ又は複数の追加の基準ピクセルブロックをフェッチするように構成される。一実施形態において、この1つ又は複数の追加の基準ピクセルブロック及び第1の基準領域は、基準フレーム内の複数のブロック区画の中からのブロック区画に対応する。一実施形態において、この1つ又は複数の追加の基準ピクセルブロック及び第1の基準領域は、基準フレーム内の近接するブロック区画に対応する。一実施形態において、処理ユニット102は、この1つ又は複数の追加の基準ピクセルブロック及び第1の基準領域に関連付けられた1つ又は複数の基準ピクセルブロックをメモリ104からフェッチするために、メモリフェッチコマンドを生成するように構成される。一実施形態において、処理ユニット102はさらに、生成されたメモリフェッチコマンドに基づいてメモリから1つ又は複数の追加の基準ピクセルブロックと第1の基準領域に関連付けられた1つ又は複数の基準ピクセルブロックとをフェッチするように構成される。40

#### 【0038】

50

一実施形態において、システム 100 はさらに、入力ユニット（例えば画像処理デバイス）、ビデオ表示ユニット（例えば液晶ディスプレイ（LCD）、陰極線管（CRT）など）、カーソル制御デバイス（例えばマウス）、ドライブユニット（例えばディスクドライブ）、信号生成ユニット（例えばスピーカ）、及び／又はネットワークインターフェースユニットなどの構成要素を含む。入力ユニットは、マルチメディアデータの処理のためにマルチメディアデータを処理ユニット 102 に転送するように構成される。ドライブユニットは、本明細書で説明される方法論及び／又は機能のうちの 1 つ又は複数を具現化する 1 つ又は複数の命令セット（例えばソフトウェア）が記憶される機械可読媒体を含む。一実施形態において、ソフトウェアは、メモリ 104 及び処理ユニット 102 も機械可読媒体を構成するように、システム 100 による実行の間、完全又は部分的に、メモリ 104 内及び／又は処理ユニット 102 内にある。ソフトウェアはさらに、ネットワークインターフェースユニットを介してネットワーク上で送信及び／又は受信され得る。

10

#### 【0039】

「機械可読媒体」という用語は、1 つ又は複数の命令セットを記憶する单一媒体及び／又は複数媒体（例えば、集中型及び／又は分散型データベース、及び／又は関連付けられたキャッシュ及びサーバ）を含むものと解釈され得る。また、「機械可読媒体」という用語は、システム 100 による実行のために命令セットを記憶、符号化、及び／又は搬送することが可能であり、様々な実施形態の方法論のうちの任意の 1 つ又は複数をシステム 100 に実行させる、任意の媒体を含むものと解釈され得る。さらに、「機械可読媒体」という用語は、ソリッドステートメモリ、光及び磁気媒体、並びに搬送波信号を含むものと解釈され得るが、これらに限定されるものではない。

20

#### 【0040】

図 2 は、実施形態に従って第 1 のキャッシュ 106a において定義された複数の例示のピクセルブロック領域を示す。図 2 には、第 1 のピクセルブロック領域 202a、第 2 のピクセルブロック領域 202b、及び第 3 のピクセルブロック領域 202c の、3 つのピクセルブロック領域が示されている。複数のこうしたピクセルブロック領域は、第 2 のキャッシュ 106b 及びメモリ 104 の一方からフェッチされた基準ピクセルブロックをキャッシュするために、第 1 のキャッシュ 106a において定義され得ることに留意されたい。図 1 を参照して本明細書で説明されるように、各ピクセルブロック領域は、複数の基準ピクセルブロックをキャッシュすることが可能な第 1 のキャッシュ 106a 内の記憶スペースの割り振りとみなされ得る。一実施形態において、定義されるピクセルブロック領域の数は、ビデオ圧縮パラダイムに基づいて決定される。

30

#### 【0041】

また、図 1 を参照して本明細書で説明するように、各ピクセルブロック領域が、スパン情報、ベースアドレス、及び／又は参照インデックスを介して定義される。一実施形態において、ピクセルブロック領域に対するベースアドレスは、第 1 のキャッシュ 106a によって定義される記憶スペース内の事前に定義された位置（本明細書では「起点」と呼ぶ）からの、ピクセルブロック領域の変位に関して定義され得る。一実施形態において、起点は座標（0, 0）に関連付けられ得、起点からのピクセルブロック領域に対応する左最上ピクセルの変位は、ピクセルブロック領域に対応するベースアドレスを定義するための x 及び y 方向の変位を計算するために測定され得る。図 2 において、第 1 のピクセルブロック領域 202a は、起点（0, 0）からの x 方向に沿った BA0\_X の変位及び y 方向に沿った BA0\_Y の変位に関連付けられるように示され、ベースアドレス（BA0\_X, BA0\_Y）によって定義される。第 2 のピクセルブロック領域 202b は、起点（0, 0）からの x 方向に沿った BA1\_X の変位及び y 方向に沿った BA1\_Y の変位に関連付けられるように示され、ベースアドレス（BA1\_X, BA1\_Y）によって定義される。同様に、第 3 のピクセルブロック領域 202c は、起点（0, 0）からの x 方向に沿った BA2\_X の変位及び y 方向に沿った BA2\_Y の変位に関連付けられるように示され、ベースアドレス（BA2\_X, BA2\_Y）によって定義される。

40

#### 【0042】

50

フレームの複数のピクセルブロックを処理するためにフェッチされた基準データに対応する各基準ピクセルブロックは、1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に割り当てられる。一実施形態において、1つ又は複数の基準ピクセルブロックの各々は、 $4 \times 4$  のピクセルブロックである。一実施形態において、基準データに対応する各基準ピクセルブロックは、所定の基準に基づいてピクセルブロック領域に割り当てられる。一実施形態において、所定の基準は、基準フレーム（例えば、基準ピクセルブロックのフェッチ元であるメモリ104における基準フレーム）によって定義されたスペース内の基準ピクセルブロックの局所性を含むが、これに限定されない。

#### 【0043】

フレームのピクセルブロックを処理するために、ピクセルブロックに対する基準データが決定され、基準データの存在がピクセルブロック領域において検索される。基準データに関連付けられたタグ情報が、(1)スパン情報、及び/又は(2)ピクセルブロック領域のベースアドレスと比較され、基準データに関連付けられた基準ピクセルブロックを含む可能性のある1つ又は複数のピクセルブロック領域が識別される。例えば、基準データに関連付けられ、第3のピクセルブロック領域202cに割り当てられる、基準ピクセルブロック204について考えてみる。基準ピクセルブロック204は、第1のピクセルブロック領域202a、第2のピクセルブロック領域202b、及び第3のピクセルブロック領域202cの各々に共通の領域に配置される。ピクセルブロック領域において基準ピクセルブロック204の検索を行なうと、第1のピクセルブロック領域202a、第2のピクセルブロック領域202b、及び第3のピクセルブロック領域202cが、基準ピクセルブロック204を含む可能性があると決定される。フェッチされるべき基準データに関連付けられたタグ情報が、これら3つのピクセルブロック領域の各々における基準ピクセルブロックのタグと比較され、基準ピクセルブロック204がピクセルブロック領域202cにおいて利用可能であると決定される。

#### 【0044】

基準ピクセルブロックが、第1のキャッシュ106aにおいて定義されたピクセルブロック領域において利用不能であると決定された場合、基準ピクセルブロックが第2のキャッシュ106bにおいて利用可能であるかどうかが決定される。基準ピクセルブロックが第2のキャッシュ106bに存在すると決定された場合、基準ピクセルブロックは第2のキャッシュ106bからフェッチされ、フレームに対応する複数のピクセルブロックを処理するためにピクセルブロック領域にキャッシュされる。基準ピクセルブロックが第2のキャッシュ106bにおいて利用不能であると決定された場合、基準ピクセルブロックはメモリ104からフェッチされる。一実施形態において、キャッシュ動作は約100サイクルで完了するように構成されるため、最適性能を達成するために複数のピクセルブロックが同時に処理される。例示の実施形態において、4つの近接するピクセルブロックのセットが同時に処理される。4つのピクセルブロックは、4つのピクセルブロックに対する基準データフェッチ間の重複を活用するために、同時に処理される。これは、図3A～図3Cを参照して本明細書でさらに説明する。

#### 【0045】

図3A～図3Cは、実施形態に従った、システム100を用いることなどによる、複数の基準データフェッチ間の重複の例示の活用を示す。図1を参照して本明細書で説明するように、マルチメディアフレームが、例えば $16 \times 16$ ピクセルブロックなどの、マクロブロックに分割され、各マクロブロックはさらに細かく区分される。図3Aはマルチメディアフレームに関連付けられるマクロブロック302を示す。マクロブロック302は、第1のブロック区画304a、第2のブロック区画304b、第3のブロック区画304c、及び第4のブロック区画304dなどの、4つの近接するブロック区画にさらに区分される。各ブロック区画は、複数のピクセルブロック（図3Aには図示せず）を含む。一実施形態において、各ブロック区画は4つの $4 \times 4$ ピクセルブロックを含む。図2を参照して本明細書で説明するように、複数のブロック区画の各々に関連付けられるピクセルブロックは、基準ピクセルブロックに対する基準データフェッチ間の重複を活用するために

10

20

30

40

50

、同時に処理される。したがって、各ブロック区画において複数のピクセルブロックを処理するために、基準領域が決定される。基準領域の決定は、本明細書において図3Bを参照して説明する。

#### 【0046】

各ブロック区画において複数のピクセルブロックを処理するために、フェッチされるべき（基準データにおける）基準領域が決定される。図3Bにおいて、基準フレーム306における各ブロック区画に対応するピクセルブロックの局所性に基づいて、第1の基準領域308a、第2の基準領域308b、第3の基準領域308c、及び第4の基準領域308dなどの、（図3Bに点線四角形で示された）4つの基準領域が、4つの区画における複数のピクセルブロックに対応すると決定される。図1を参照して本明細書で説明するように、メモリ104（又はメモリ104に関連付けられるプリフェッチバッファ）におけるデータ編成はブロックベースであるように示されるため、基準ピクセルのフェッチの最小細分性はブロックベースである。したがって、第1のブロック区画に関連付けられたピクセルブロックに対する基準データをフェッチするために、9つの基準ピクセルブロックが、第1の基準領域308aに対応するメモリ104からフェッチされるべきであると決定される。さらに、それぞれ、第2の基準領域308b、第3の基準領域308c、及び第4の基準領域308dに対応するように、9つの基準ピクセルブロック、6つの基準ピクセルブロック、及び9つの基準ピクセルブロックが、メモリ104からフェッチされるべきであると決定される。近接する基準領域に対してフェッチされる基準ピクセルブロックが重複する場合、基準領域のうちの1つに対してフェッチされ、ピクセルブロック領域にキャッシュされた基準ピクセルブロックは、後続のフェッチに利用可能とされ得、利用可能な基準ピクセルブロックは、図3Cを参照して本明細書で説明するように再使用される。

#### 【0047】

図3Cは、ピクセルブロック302の4つの近接するブロック区画に対する複数の基準ピクセルブロックのフェッチを示す。第1のブロック区画304aに関連付けられたピクセルブロックの処理の間、第1のキャッシュ106aにおいて定義されたピクセルブロック領域には基準データが存在しない。したがって、第1のキャッシュ106aのピクセルブロック領域における第1のブロック区画304aに関連付けられたピクセルブロックを処理するために実装されるべき9つの基準ピクセルブロックの存在が決定される。最初に、第1のキャッシュ106aにおいて定義されたピクセルブロック領域には基準データがなく、9つの基準ピクセルブロックは第1のキャッシュ106aにおいて利用不能であると決定され、さらに、9つの基準ピクセルブロックの各々の不在は、第1の基準領域308aにおいて「MISS」として記録される。所望の基準データが第1のキャッシュ106aにおいて利用不能であると決定されるため、9つの基準ピクセルブロックは、メモリ104からフェッチされることになる。4つの処理サイクルのセット（図3Cでは円で表される）が、所望の9つの基準ピクセルブロックをフェッチするために実装され得る。一実施形態において、4つのピクセルブロックが各処理サイクルにおいてフェッチされ、したがって、9つの基準ピクセルブロックに加えていくつかの追加のピクセルブロックがフェッチされる。こうしたピクセルブロックは図3Cでは「関係なし」（又は「N/R」）とマーク付けされる。9つの基準ピクセルブロックは、メモリ104からフェッチされ、第1のキャッシュ106aにおける1つ又は複数のピクセルブロック領域にキャッシュされる。

#### 【0048】

図3Bに示されるように、第1の基準領域308aの右端310aと第2の基準領域308bの左端310bとは3つの共通の四角形ブロック内にあり、このことが第1の基準領域308aと第2の領域308bとの間の重複を生成する。第1のブロック区画304aの処理のための基準データのフェッチの結果として、第2のブロック区画304bに対応するピクセルブロックを処理するために実装されるべき基準ピクセルブロックは、すでにフェッチされ、第1のキャッシュ106aにキャッシュされている。その結果、第2の

10

20

30

40

50

ブロック区画 304b を処理するために実装されるべき 9 つの基準ピクセルブロックの存在をチェックすると、3 つの基準ピクセルブロックが利用可能であると決定され、したがってこれら 3 つのピクセルブロックの存在が「HIT」として記録され、残りの 6 つの基準ピクセルブロックの不在は「MISS」として記録される。これら 6 つの基準ピクセルブロックをフェッチするために、4 つの処理サイクルが実装される。実装された基準データのフェッチの間、6 つの基準ピクセルブロックに加えていくつかの追加の基準ピクセルブロックがフェッチされ得、こうしたピクセルブロックは「N/R」としてマーク付けされる。6 つの基準ピクセルブロックは、メモリ 104 からフェッチされ、第 1 のキャッシュ 106a における 1 つ又は複数のピクセルブロック領域にキャッシュされる。

## 【0049】

10

また第 1 の基準領域 308a の下端 310c と第 3 の基準領域 308c の上端 310d とは 2 つの共通の四角形ブロック内にあり、第 1 の基準領域 308a と第 3 の基準領域 308c との間の重複を生成している。第 1 のブロック区画 304a を処理するための基準データのフェッチの結果として、第 3 のブロック区画 304c に対応するピクセルブロックを処理するために実装されるべき 2 つの基準ピクセルブロックは、すでにフェッチされ、第 1 のキャッシュ 106a にキャッシュされている。第 3 のブロック区画 304c を処理するために実装されるべき 6 つの基準ピクセルブロックの存在をチェックすると、2 つの基準ピクセルブロックが利用可能であると決定され、したがってこれら 2 つのピクセルブロックの存在が「HIT」として記録され、残りの 4 つの基準ピクセルブロックの不在は「MISS」として記録される。これら 4 つの基準ピクセルブロックをフェッチするために、2 つの処理サイクルが実装される。実装された基準データのフェッチの間、これら 4 つの基準ピクセルブロックに加えていくつかの追加の基準ピクセルブロックがフェッチされ得、こうした基準ピクセルブロックは「N/R」としてマーク付けされる。4 つの基準ピクセルブロックは、メモリ 104 からフェッチされ、第 1 のキャッシュ 106a における 1 つ又は複数のピクセルブロック領域にキャッシュされる。

## 【0050】

20

同様に、第 4 の区画 304d に対応するピクセルブロックを処理するために、第 1 のキャッシュ 106a のピクセルブロック領域における 9 つの基準ピクセルブロックの利用可能性がチェックされ、したがって、基準ピクセルブロックは HIT 又は MISS に関連付けられる。MISS と記録されたピクセルブロックは、メモリからフェッチされ、第 1 のキャッシュ 106a のピクセルブロック領域にキャッシュされる。フェッチされた基準データは、フレームの複数のブロック区画におけるピクセルブロックを処理するために用いられる。マルチメディアデータの処理に含まれる様々な段を、本明細書において図 4A を参照して説明する。

## 【0051】

30

図 4A は、一実施形態に従った、システム 100 におけるマルチメディアデータに関連付けられるマルチメディアフレームの処理を示す例示のプロセスフローの簡略化された概要を示す。一実施形態において、マルチメディアフレームの処理は、キャッシュ段 402、直接メモリアクセス (DMA) 段 404、及びフィルタリング段 406 などの、3 段で成される。キャッシュ段 402 において、ステップ 408 で、フレームを処理するために実装されるべき基準データが（例えば、図 1 の処理ユニット 102 によって）決定され、それに続いてステップ 410 で、第 1 のキャッシュ 106a において基準データの存在が（例えば、処理ユニット 102 によって）チェックされる。図 4A において、フレームがキャッシュ段 402 への入力として示されているが、いくつかの実施形態において、（図 3A～図 3C を参照して本明細書で説明するように）フレームはブロックに分割され、さらに各ブロックが区分され、フレームの各ブロック区画内の複数のピクセルブロックについて基準データが決定及びフェッチされる。一実施形態において、フェッチされるべき基準ピクセルブロックのサイズは、フレームの対応するピクセルブロックのサイズよりわずかに大きくなるように決定される。例えば、フレームの 4 × 4 ピクセルブロックの場合、9 × 9 基準ピクセルブロック（各側で 5 つの追加ピクセル、すなわち左に 3 つ及び右に 2

40

50

つの追加ピクセル)が、動き補正の間の補間のために基準フレームからフェッチされるべきであると決定される。同様に、フレームの8×8ピクセルブロックの場合、13×13基準ピクセルブロックが補間のために基準フレームからフェッチされるべきであると決定され得る。

【0052】

図1及び図2を参照して本明細書で説明するように、処理ユニット102は、第1のキャッシュ106aにおいてピクセルブロック領域を定義するように構成され得る。ピクセルブロック領域は、第2のキャッシュ106b及びメモリ104の一方から以前にフェッチされた基準データに対応する複数の基準ピクセルブロックをキャッシュすることができるよう構成される。フレームに対する基準データを決定する際に、基準データを含む可能性のある1つ又は複数のピクセルブロック領域が(例えば、図1の処理ユニット102を用いて)識別される。識別されたピクセルブロック領域における基準データに関連付けられる1つ又は複数の基準ピクセルブロックの存在が、(例えば、図1の処理ユニット102を用いて)決定される。

10

【0053】

DMA段404において、ステップ412で、識別されたピクセルブロック領域における基準データに関連付けられた1つ又は複数の基準ピクセルブロックが利用不能であることが決定されると、第2のキャッシュ106b及びメモリ104の一方から1つ又は複数の基準ピクセルブロックをフェッチするために、1つ又は複数のメモリフェッチコマンドが(例えば、図1の処理ユニット102を用いて)生成される。一実施形態において、ピクセルブロック領域における基準ピクセルブロックの利用不能性が決定されると、第2のキャッシュ106bにおいて基準ピクセルブロックの利用可能性がチェックされる。基準ピクセルブロックが第2のキャッシュ106bにおいて利用可能であると決定された場合、基準ピクセルブロックが、フェッチされ、フレームのピクセルブロックの処理のために第1のキャッシュ106aのピクセルブロック領域にキャッシュされる。基準ピクセルブロックが第2のキャッシュ106bにおいて利用不能であると決定された場合、基準ピクセルブロックはメモリ104からフェッチされなければならない。ステップ414で、基準データは、生成されたメモリフェッチコマンドに基づいてメモリ104から(例えば、図1の処理ユニット102を用いて)フェッチされる。ステップ416で、メモリ104/第2のキャッシュ106bからフェッチされた1つ又は複数の基準ピクセルブロックの各々が、所定の基準に基づいて、第1のキャッシュ106aにおいて定義された1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に(例えば、図1の処理ユニット102を用いて)割り当てられる。一実施形態において、所定の基準は、基準フレーム内の基準ピクセルブロックの局所性、及び基準フレームによって定義されるスペース内のピクセルブロック領域の局所性を含むが、これらに限定されない。割り当てに続き、フレームの後続のピクセルブロックを処理するために基準データの検索を促進するよう、1つ又は複数の基準ピクセルブロックの各々が、ピクセルブロック領域に基づいて(例えば、図1の処理ユニット102を用いて)タグに関連付けられる。

20

【0054】

フィルタリング段406において、ステップ418で、フェッチされ、1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に割り当てられた、(フレームのピクセルブロックに対応する)1つ又は複数の基準ピクセルブロックは、(例えば、図1の処理ユニット102を用いて)読み取られ、予測されるフレームを取得するために処理を受ける。予測されたフレームはその後、マルチメディアデータのフレームの処理(例えば、動き補償に基づく符号化/復号化)に用いられ得る。

30

【0055】

図4Bは、一実施形態に従った、マルチメディアフレームの処理の間の第1のキャッシュ106aに関連付けられる読み取り/書き込み動作の例示のスケジューリングを示す。一実施形態において、第1のキャッシュ106aは、読み取り/書き込み動作のスケジューリングのために複数のキャッシュバンクに分割される。一実施形態において、第1のキ

40

50

ヤッショウ 106a は、例えば、キャッシュバンク 0、キャッシュバンク 1、及びキャッシュバンク 2 の、3 つのキャッシュバンクでパイプライン様式 / 逐次的様式で動作するよう に設計される。図 4B において、キャッシュバンク 0、キャッシュバンク 1、及びキャッシュバンク 2 は、それぞれ、デジット 0、1、及び 2 で表される。パイプライン手法は、所与のキャッシュバンクへの読み取り及び書き込み動作を同時に実施する可能性を排除する。

#### 【0056】

一実施形態において、パイプラインは、システム 100 におけるマルチメディアデータの処理の間関とする様々な段に対応する 3 つのパイプラインスロットを有する。図 4B に示される 3 つのパイプラインスロットは、フロントスロット 402、DMA スロット 404、及びバックスロット 406 である。一実施形態において、フロントスロット 402 は、図 1 のメモリ 104 からフェッチされるべき基準データの決定、及び基準データをフェッチするためのメモリフェッチコマンドの生成を含む処理段に対応し、DMA スロット 404 は、基準データをフェッチすること、及びフェッチされた基準データを第 1 のキャッシュ 106a におけるピクセルブロック領域に割り当てること（図 1 の第 1 のキャッシュ 106a での書き込み動作）を含む処理段に対応し、バックスロット 406 は、マルチメディアデータに関連付けられたフレームの処理のために予測フレームを構成するための（例えば、図 1 の処理ユニット 102 による）基準データの読み取りを含む処理段に対応する。キャッシュバンク（0、1、及び 2）は、パイプラインスロット 402～406 の複数のバス 420～428（点線の垂直コラムで表される）を介して、逐次的、循環的方式でパイプラインスロット（402、404、及び 406）を受ける。

#### 【0057】

図 4B において、パイプラインスロット（402～406）の第 1 のバス 420 で、キャッシュバンク 0 はフロントスロット 402 を受ける。フェッチされるべき（フレームに関連付けられた複数のピクセルブロックに対応する）基準データが決定される。より具体的に言えば、複数のピクセルブロックを処理するために実装されるべき基準データが識別され、第 1 のキャッシュ 106a において及びそれに続いて第 2 のキャッシュ 106b において、基準データの存在がチェックされる。第 1 のキャッシュ 106a 及び第 2 のキャッシュ 106b における基準データの利用不能性が決定されると、基準データはメモリ 104 からフェッチされることになる。メモリ 104 からフェッチされるべき基準データに対応する基準ピクセルブロック（例えば、図 3C で MISS と記録された基準ピクセルブロック）は、キャッシュバンク 0 に割り当てられる。

#### 【0058】

一実施形態において、フェッチされるべき基準ピクセルブロックを収容するためにキャッシュバンク（例えば、キャッシュバンク 0、キャッシュバンク 1、又はキャッシュバンク 2）内のスペースの利用可能性が、フェッチ動作を行なう前にチェックされる。基準ピクセルブロックを収容するのに十分なスペースがキャッシュバンクにおいて利用可能である場合、基準ピクセルブロックは、キャッシュバンクに割り振られ、既にキャッシュバンク内に存在する基準ピクセルブロックのグループと共に処理される。しかしながら、スペースが不十分であると決定された場合、基準ピクセルブロックは次の後続のバスにおいて新しいキャッシュバンクに割り振られる。一実施形態において、最大可能数の基準ピクセルブロックがキャッシュバンクに収容される。一実施形態において、フレームの 4 つのマクロブロックに対応する基準ピクセルブロックが、キャッシュバンクに割り振られる。一実施形態において、フレームのマクロブロックに対応するすべての基準ピクセルブロックが、単一のキャッシュバンクに含められ得る。一実施形態において、マクロブロックに対応するすべての基準ピクセルブロックが 1 つのキャッシュバンクに収容され得ない場合、そのマクロブロックに対応する基準ピクセルブロックは、パイプラインスロット（402～406）の次のバスの間、次のキャッシュバンクに含められる。

#### 【0059】

図 4B に示されるように、第 1 のバス 420 の間、キャッシュバンク 0 はフロントスロット 402 を受ける。

10

20

30

40

50

ット402を受ける。第2のパス422の間、キャッシュバンク1はフロントスロット402を受け、キャッシュバンク0はDMAスロット404を受ける。フロントスロット402の間定義されるすべてのピクセルブロック領域は、キャッシュバンクのキャッシュバンクアドレスに関連付けられるか又はタグ付けされる。一実施形態において、フレームの第1のブロック区画のピクセルブロックに対応する基準ピクセルブロックをキャッシュするために定義されるピクセルブロック領域は、キャッシュバンク0に関連付けられる。フレームの後続のブロック区画に対して定義されるすべてのピクセルブロック領域は、キャッシュバンク1に関連付けられ得る。

#### 【0060】

第3のパス424の間、キャッシュバンク2はフロントスロット402を受け、キャッシュバンク1はDMAスロット404を受け、キャッシュバンク0はバックスロット406(フィルタリング段)を受ける。第4のパス426でキャッシュバンク2がDMAスロット404を受ける前に、キャッシュバンク0に関連付けられたピクセルブロック領域が実装されず、キャッシュバンク1に関連付けられたピクセルブロック領域がキャッシュバンク2を処理するために保持されるため、キャッシュバンク0におけるすべてのピクセルブロック領域は無効化され削除される。例示の実施形態において、キャッシュバンク2は、基準フレーム内のピクセルブロックのローに関連付けられる基準ピクセルブロックに関連付けられたマルチメディアデータを含み得る。キャッシュバンク1は、基準ピクセルブロックのローにおける基準ピクセルブロックの左に1つ又は複数の基準ピクセルブロックが関連付けられたマルチメディアデータを含み得、キャッシュバンク0は、基準フレームにおける基準ピクセルブロックのローの上に位置する最上ローにおける1つ又は複数の基準ピクセルブロックに関連付けられたマルチメディアデータを含み得る。キャッシュバンク1の1つ又は複数の基準ピクセルブロックに関連付けられたマルチメディアデータは、キャッシュバンク2の基準ピクセルブロックを処理する一方で用いられ得るが、キャッシュバンク0の1つ又は複数の基準ピクセルブロックに関連付けられたマルチメディアデータは、キャッシュバンク0の1つ又は複数の基準ピクセルブロックが最上ローに属していることから、キャッシュバンク2の基準ピクセルブロックを処理する一方で用いられ得ない。したがって、マルチメディアデータの処理の間用いられ得る他の追加の基準データを収容するためのスペースを利用可能にするためにキャッシュバンク2を処理する一方で、キャッシュバンク0の1つ又は複数のピクセルブロック領域が無効化及び/又は削除され得る。一実施形態において、第5のパス428の間、キャッシュバンク2はバックスロット406を受ける。一実施形態において、複数のキャッシュバンクが同時にフロントスロット402、DMAスロット404、及び/又はバックスロット406を受ける。

#### 【0061】

図5は、一実施形態に従って、マルチメディアフレームに関連付けられる複数のピクセルブロックを処理するために基準データを検索する例示のプロセスを示す。図3A~図3Cを参照して本明細書で説明するように、マルチメディアフレームのブロック区画に関連付けられるピクセルブロックを処理するために、各ブロック区画について基準領域が決定された後、それらの存在がチェックされる。すなわち、図1の第1のキャッシュ106aにおいて検索される。より具体的に言えば、各基準領域に対応する基準ピクセルブロックの存在が、第1のキャッシュ106aにおける1つ又は複数のピクセルブロック領域においてチェックされる。したがって、基準ピクセルブロックの範囲チェック502が行われ、範囲チェック502では、基準ピクセルブロックを含む可能性のあるピクセルブロック領域を識別するために、基準ピクセルブロックに関連付けられる参照番号(ref#)504及び位置座標(X,Y)506が、それぞれ、各ピクセルブロック領域に関連付けられるタグ情報における参照インデックス508及びスパン情報/ベースアドレス510と比較される。図3A~図3Cを参照して本明細書で説明するように、基準領域はメモリ104に記憶された基準フレーム内で決定され、したがって、基準領域内の基準ピクセルブロックは、基準フレームに対応する参照番号(ref#)504及び基準フレーム内の局所性に対応する位置座標506でタグ付けされる。1つ又は複数のピクセルブロック領域

10

20

30

40

50

の参照番号 (ref #) 504 と参照インデックス 508との比較を行なうために、第1の比較ブロック 512 (図5でCMP1と示される)が用いられる。さらに、位置座標 506 とスパン情報 / ベースアドレス 510との比較を行なうために、第2の比較ブロック 514 (図5でCMP2と示される)が用いられる。

#### 【0062】

一実施形態において、スパン情報は、各ピクセルブロック領域の長さ方向に沿った寸法 (例えば、ピクセルブロック領域の高さ) 及び幅方向に沿った寸法 (例えば、ピクセルブロック領域の幅) を示す。比較の間、

X BA - X 及び < BA - (X + ピクセルブロック領域の幅)、及び

Y BA - Y 及び < BA - (Y + ピクセルブロック領域の高さ)

10

であるかどうかが決定される。ここで、BAは、1つ又は複数のピクセルブロック領域の各々のベースアドレスである。

#### 【0063】

2つの比較ブロック 512 及び 514 の出力に基づき、ブロック 516 で、ピクセルブロック領域が基準ピクセルブロックを含む可能性があると決定される。それに続いて、基準ピクセルブロックを含む可能性があると識別されたピクセルブロック領域内の基準ピクセルブロックの存在を決定するために、オフセットチェック 518 が行われる。オフセットチェック 518 で、基準ピクセルブロックの位置座標 506 (X, Y) に含まれるオフセット情報が、これらのピクセルブロック領域に含まれる要素 (以前にピクセルブロック領域にフェッチ及びキャッシュされた基準ピクセルブロック) のオフセットとマッチングすると決定される。図5において、各ピクセルブロック領域が9つの要素を含むように示されているが、ピクセルブロック領域はこれより多いか又は少ない数の要素を含み得ることに留意されたい。基準ピクセルブロックを含む可能性があるピクセルブロック領域の各々内の要素 522a ~ 522i のタグ情報を、基準ピクセルブロックのオフセット情報と比較するために、第3の比較器ブロック 520 が用いられる。第3の比較器ブロック 520 (図5でCMP3と示される)は、比較を並行して行なうために、ピクセルブロック領域における要素の最大数と同等の多数の比較器 (図5のCMP3 520 内で各々 CMPと示される)を含むように示されている。決定されたあり得るオフセットに1つ又は複数の要素がある場合、その決定されたあり得るオフセットにおける要素に関連付けられる複数の利用可能性タグがチェックされる。一実施形態において、基準ピクセルブロックは、図1のシステム100の設計に従って、単一のピクセルブロック領域内に存在することができる。一実施形態において、基準ピクセルブロックが存在する場合、その要素に関連付けられた複数の利用可能性タグのうちの利用可能性タグが HIT524 とマーク付けされ、存在しない場合、利用可能性タグは MISS とマーク付けされる。利用可能性タグが基準ピクセルブロックの存在を示す場合 (例えば HIT524)、その要素のアドレス (例えば HITアドレス 526) がアドレスエンコーダ 528 を介して符号化される。

20

#### 【0064】

利用可能性タグが基準ブロックの不在を示す場合、第4の比較器ブロック 530 (図5でCMP4と示される)において、現行キャッシュバンク識別タグ 532 を備える1つ又は複数のピクセルブロック領域を決定するために、(図4Bを参照して本明細書で説明するように)現行キャッシュバンク識別タグ 532 (BANK#)を、識別されたピクセルブロック領域に関連付けられた複数のキャッシュバンク識別タグ 534 の各々と比較することによって、バンクチェックが行われる。続いて、現行キャッシュバンク識別タグ 534 を備える決定されたピクセルブロック領域が、識別されたピクセルブロック領域において存在しない基準ピクセルブロックを割り振るためのスペースの利用可能性を有するかどうかがチェックされる。決定されたピクセルブロック領域内の決定されたあり得るオフセットでの要素の不在が、スペースの利用可能性を示し得る。決定されたあり得るオフセットでの要素の不在はまた、次のポインタ 536 の有効性によって示される。次のポインタ 536 は、第5の比較器ブロック 538 (図5でCMP5と示される)で、キャッシュバンクチェックの出力と比較される。キャッシュバンクチェックが出力を生成し、次のポイ

30

40

50

ンタ 5 3 8 が有効である場合、不在要素のアドレス（例えば M I S S アドレス 5 4 0 ）はエンコーダ 5 4 2 を用いて決定される。基準ピクセルブロックはメモリ 1 0 4 又は第 2 のキャッシュ 1 0 6 b から（例えば、図 1 の処理ユニット 1 0 2 を用いて）フェッチされ、識別されたピクセルブロック領域のうちの 1 つに（例えば、図 1 の処理ユニット 1 0 2 を用いて）割り当てられる。現行キャッシュバンク識別タグ 5 3 2 を備える識別されたピクセルブロック領域のいずれも、利用可能なスペースを有さない場合、メモリ 1 0 4 又は第 2 のキャッシュ 1 0 6 b からフェッチされた基準ピクセルブロックを割り当てるために新しいピクセルブロック領域が作成される。

#### 【 0 0 6 5 】

一実施形態において、メモリからフェッチされるべき基準ピクセルブロックを収容するために、キャッシュバンク内のスペースの利用可能性が決定される。スペースの利用可能性を決定すると、基準ピクセルブロックはキャッシュバンクに割り振られる。一実施形態において、メモリ 1 0 4 からのデータフェッチの待ち時間を低減させるために、第 1 の基準領域に対応する基準ピクセルブロックが、単一のメモリフェッチコマンドを用いてメモリ 1 0 4 からフェッチされるように整合される 1 つ又は複数の追加の基準ピクセルブロックと組み合わせてフェッチされる。一実施形態において、基準ピクセルブロック及び 1 つ又は複数の追加の基準ピクセルブロックが基準フレーム内で互いに近接するように、基準ピクセルブロックと共にフェッチされるべき 1 つ又は複数の追加の基準ピクセルブロックが（例えば、図 1 の処理ユニット 1 0 2 を用いて）決定される。また、1 つ又は複数の追加の基準ピクセルブロック及び基準ピクセルブロックが共に基準フレーム内に矩形領域（連続的領域）を形成するように、1 つ又は複数の追加の基準ピクセルブロックが決定される。一実施形態において、1 つ又は複数の追加の基準ピクセルブロック及び基準ピクセルブロックは、フレーム内の複数のブロック区画の中からのブロック区画に対応する。一実施形態において、基準ピクセルブロック及び 1 つ又は複数の追加の基準ピクセルブロックは、基準フレーム内の近接するブロック区画に属し得、基準フレーム内に矩形領域（連続的領域）を共に形成し得る。1 つ又は複数の追加の基準ピクセルブロック及び基準ピクセルブロックは、単一のメモリフェッチコマンドに基づいてメモリ 1 0 4 から共にフェッチされ得る。

#### 【 0 0 6 6 】

一実施形態において、ブロック区画の基準ピクセルブロック及び 1 つ又は複数の追加の基準ピクセルブロックは、フェッチされるように整合される一方で、近接するブロック区画の 1 つ又は複数の基準ピクセルブロックと共にマージされ得る。基準ピクセルブロック、1 つ又は複数の追加の基準ピクセルブロック、及び 1 つ又は複数の基準ピクセルブロックは、矩形（連続的領域）を形成し得、単一のメモリフェッチコマンドに基づいてメモリ 1 0 4 からフェッチされ得る。1 つ又は複数の追加の基準ピクセルブロック及び基準ピクセルブロックは、メモリ 1 0 4 からフェッチされるように整合される一方で、同じ又は異なるキャッシュバンクに割り振られ得る。一実施形態において、割り振られた基準ピクセルブロック及び 1 つ又は複数の追加の基準ピクセルブロックをメモリ 1 0 4 からフェッチするために、キャッシュバンクに対してメモリフェッチコマンドが（例えば、図 1 の処理ユニット 1 0 2 を用いて）作成され得る。割り振られた基準ピクセルブロック及び 1 つ又は複数の追加の基準ピクセルブロックは、作成されたメモリフェッチコマンドに基づいて、メモリ 1 0 4 から（例えば、図 1 の処理ユニット 1 0 2 を用いて）フェッチされ得る。基準ピクセルブロック及び 1 つ又は複数の追加の基準ピクセルブロックはメモリから共にフェッチされるため、メモリから基準データをフェッチするために用いられるタグの総数が削減され得、システム性能仕様への適合を促進する。

#### 【 0 0 6 7 】

一実施形態において、第 1 のキャッシュ 1 0 6 a は、キャッシュユニット 1 0 6 及びシステム 1 0 0 の編成に起因して予測プリフェッチに関与し得ず、第 1 のキャッシュ 1 0 6 a において利用不能な基準ピクセルブロックの各々は、メモリ 1 0 4 から別々にフェッチされることになる。基準ピクセルブロックの各々にタグが割り当てられ得る。いくつかの

10

20

30

40

50

プラットフォーム（例えば、O M A P（商標））において、許容タグの数が制限され、基準ピクセルブロックの各々にタグが割り当てられるため、システム性能仕様を満たすことが困難になる。加えて、基準データフェッチのサイズが、システム 100 における許容最大バーストサイズ内に保たれる。一実施形態において、基準データフェッチのサイズを最大バーストサイズ内に保つために、機能停止論理（break down logic）が実装される。最大バーストサイズは、例えば 8 データ位相を含む。メモリ 104 からの基準データフェッチは、図 6 A～図 6 C でさらに説明する。

【 0068 】

図 6 A～図 6 C は、一実施形態に従った、図 1 のシステム 100 におけるマルチメディアデータに関連付けられた基準フレーム内の互いに近接する基準ピクセルブロックの例示のフェッチを示す。図 6 A は、基準フレームに関連付けられる 2 つの近接するブロック区画 602a 及び 602b を示す。図 6 A に示されるように、2 つの近接するブロック区画 602a 及び 602b の各々が 16 の基準ピクセルブロックを含む。ブロック区画 602a 及び 602b に対応する 1 つ又は複数のピクセルブロックを処理するために基準データの検索を行なうと、基準ピクセルブロックの影付きグループ 604a、604b、604c、及び 604d は、キャッシュユニット 106 において利用不能な基準ピクセルブロックであり、図 1 のメモリ 104 からフェッチされべきと決定される。

【 0069 】

図 6 A に示されるように、基準ピクセルブロックの影付きグループ 604a、604b、及び 604c の各々が 4 つの基準ピクセルブロックを含み、基準ピクセルブロックの影付きグループ 604d は基準ピクセルブロックのペアを含む。基準ピクセルブロックの各影付きグループ 604a、604b、604c、及び 604d における各基準ピクセルブロックに対して基準ピクセルブロックフェッチコマンドを生成する（結果的に、各々、基準ピクセルブロックの影付きグループ 604a、604b、及び 604c を処理するための 4 つの基準ピクセルブロックフェッチコマンドと、基準ピクセルブロックの影付きグループ 604d を処理するための 2 つの基準ピクセルブロックフェッチコマンドとを生成する）代わりに、図 6 B 及び図 6 C を参照して本明細書で説明するように、基準ピクセルブロックフェッチコマンドが組み合わされ得る。

【 0070 】

図 6 B において、ブロック区画における近接するピクセルブロックに対する基準ピクセルブロックフェッチが組み合わされ、それによって、システム容量が最適化され、性能が向上する。例えば、基準ピクセルブロックの影付きグループ 604a、604b、604c、及び 604d の各々に対して、1 つの基準ピクセルブロックフェッチコマンドが生成され得る。基準ピクセルブロックフェッチコマンドは、図 6 B に示されるように、基準ピクセルブロックの影付きグループ 604a、604b、604c、及び 604d における個別の基準ピクセルブロックに対する基準ピクセルブロックフェッチコマンドを組み合わせることによって生成される。例えば、基準ピクセルブロックの影付きグループ 604a をフェッチするために、基準ピクセルブロックフェッチコマンド 606a が用いられ得る。同様に、基準ピクセルブロックの影付きグループ 604b、604c、及び 604d をフェッチするために、基準ピクセルブロックフェッチコマンド 606b、606c、及び 606d が用いられ得る。それによって基準ピクセルブロックフェッチの数が 14 から 4 に削減され、それによってキャッシュ性能が向上する。

【 0071 】

図 6 C において、（ブロック区画 602a 及び 602b などの）近接するブロック区画における近接するピクセルブロックに対する基準ピクセルブロックフェッチが組み合わされる。基準ピクセルブロックフェッチコマンド 606a 及び 606d の生成に加えて、（近接するブロック区画 602a 及び 602b における）近接する基準ピクセルブロックの影付きグループ 604b 及び 604c に対する基準データフェッチが、基準ピクセルブロックの影付きグループ 604b 及び 604c をフェッチするために単一の基準ピクセルブロックフェッチコマンド 606e に組み合わされる。それによって基準ピクセルブロック

10

20

30

40

50

フェッチの数が 14 から 3 に削減され、それによってキャッシュ性能がさらに向上する。

【0072】

図 7 は、一実施形態に従った、マルチメディアデータ処理のための例示の方法 700 を示すフローチャートである。一実施形態において、方法 700 は、図 1 のシステム 100 などのシステムによって実装され得る。フローチャートの動作、及びフローチャートにおける動作の組み合わせは、ハードウェア、ファームウェア、プロセッサ、回路、及び / 又は、1 つ又は複数のコンピュータプログラム命令を含むソフトウェアの実行に関連付けられる他のデバイスなどの、様々な手段によって実装され得る。方法 700 の動作はシステム 100 を用いて説明される。しかしながら、この方法の動作は、任意の他のシステムを用いることによって説明及び / 又は実施され得る。方法 700 は動作 702 で開始される 10。動作 702 で、図 2 を参照して本明細書で説明するピクセルブロック領域などの 1 つ又は複数のピクセルブロック領域が、基準データに対応する複数の基準ピクセルブロックをキャッシュするために、第 1 のキャッシュ ( 例えば、図 1 の第 1 のキャッシュ 106a ) において定義される。一実施形態において、基準データは、メモリ ( 例えば、図 1 のメモリ 104 ) 及び第 2 のキャッシュ ( 例えば、図 1 の第 2 のキャッシュ 106b ) の一方から、フェッチされ得る。一実施形態において、基準データは、メモリに記憶された 1 つ又は複数の基準フレームのうちの基準フレームに対応し得る。

【0073】

図 1 を参照して本明細書で説明するように、各ピクセルブロック領域が、1 つ又は複数の基準ピクセルブロックをキャッシュすることが可能な、第 1 のキャッシュ内の記憶スペースの割り振りとみなされ得る。1 つ又は複数のこうした記憶スペースは、メモリからフェッチされた複数の基準ピクセルブロックをキャッシュするために、第 1 のキャッシュ内で ( 例えば、図 1 の処理ユニット 102 などの処理ユニットを用いて ) 定義され得る。一実施形態において、定義されるべきピクセルブロック領域の数は、ビデオ圧縮パラダイムに基づいて決定され得る。ビデオ圧縮パラダイムの例には、ビデオコーディング専門家グループ ( VCEG ) 、 H.120 、 H.261 、動画像専門家グループ ( MPEG ) 、 MPEG - 1 Part 2 、 H.262 又は MPEG - 2 Part 2 、 H.263 、 MPEG - 4 Part 2 、 H.264 又は MPEG - 4 AVC 、 VVC - 2 ( ディラック ) 、高効率ビデオコーディング ( HEVC ) などが含まれるが、これらに限定されない。 20

【0074】

一実施形態において、各ピクセルブロック領域は、スパン情報、ベースアドレス、キャッシュバンク識別タグ、及び / 又は参照インデックスを介して定義される。スパン情報は、各ピクセルブロック領域の長さ方向 ( 例えば高さ ) 及び幅方向 ( 例えば幅 ) に沿った寸法を示す。ベースアドレスは、基準フレームによって定義されるスペース内の事前に決定された起点からの各ピクセルブロック領域の左上アドレスのオフセットであり、基準フレームによって定義されるスペース内のピクセルブロック領域の局所性を示す。各ピクセルブロック領域のベースアドレスは、 x 及び y 座標に関して表される。キャッシュバンク識別タグは、各ピクセルブロック領域が関連付けられるキャッシュバンクを示す。参照インデックスは、各ピクセルブロック領域に関連付けられる基準フレームを示す。例えば、メモリ 104 における基準データが 32 の基準フレームを含み、ピクセルブロック領域が 32 の基準フレームのうちの基準フレーム # 5 に関連付けられる場合、ピクセルブロック領域の参照インデックスは、ピクセルブロック領域に含まれる基準ピクセルブロックがフェッチされる基準フレームを示し得る。 40

【0075】

動作 704 で、複数の基準ピクセルブロックの中からの基準ピクセルブロックが、所定の基準に基づいて、1 つ又は複数のピクセルブロック領域の中からのピクセルブロック領域に割り当てられる。所定の基準は、基準フレーム内の基準ピクセルブロックの局所性、及び基準フレームによって定義されるスペース内のピクセルブロック領域の局所性を含むが、これらに限定されない。一実施形態において、単一の基準フレームに属する基準ピクセルブロックが、1 つ又は複数のピクセルブロック領域の中からのピクセルブロック領域 50

に割り当てられる。一実施形態において、ピクセルブロック領域が、疎に満たされ、少數基準ピクセルブロックエントリ（要素とも呼ばれる）を含む。一実施形態において、1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域が9つの要素を含む。一実施形態において、ピクセルブロック領域に関連付けられる1つ又は複数の要素の各要素が、対応する基準フレームによって定義されるスペース内の各要素の局所性に基づいて、ピクセルブロック領域内の特定の位置に割り当てられる。一実施形態において、1つ又は複数のピクセルブロック領域の各々がその中に定義されるキャッシュバンクを示すために、キャッシュバンク識別タグが（前述のように）各ピクセルブロック領域に関連付けられる。動作706で、基準ピクセルブロックは、マルチメディアフレームに関連付けられる複数のピクセルブロックを処理するために基準データの検索を促進するように、ピクセルブロック領域に基づいてタグに関連付けられる。マルチメディアフレームの処理のための基準データの検索は、図8A～図8Bで説明する。

#### 【0076】

図8A及び図8Bは、一実施形態に従って、マルチメディアフレームの処理を行なうための基準データ検索の例示の方法800を示すフローチャートを集合的に示す。一実施形態において、システム800は、図1のシステム100などのシステムによって実装され得る。フローチャートの動作、及びフローチャートにおける動作の組み合わせは、ハードウェア、ファームウェア、プロセッサ、回路、及び／又は、1つ又は複数のコンピュータプログラム命令を含むソフトウェアの実行に関連付けられる他のデバイスなどの、様々な手段によって実装され得る。方法800の動作は、システム100を用いて説明される。しかしながら、この方法の動作は、任意の他のシステムを用いることによって説明及び／又は実施され得る。方法800は動作802で開始される。動作802で、マルチメディアフレームにおける複数のブロック区画の中からのブロック区画における複数のピクセルブロックに対応する第1の基準領域が、マルチメディアフレームの処理のために決定される。例えば、マルチメディアフレームの4×4ピクセルブロックの場合、9×9基準領域（各側で5つの追加ピクセル、すなわち、左に3つ及び右に2つの追加ピクセル）が、動き補正の間の補間のために基準フレームからフェッチされると決定される。同様に、フレームの8×8ピクセルブロックの場合、13×13基準領域ブロックが基準フレームからフェッチされるべきであると決定され得る。図3A～図3Cを参照して本明細書で説明するように、第1の基準領域は、メモリ（例えば、図1のメモリ104）に記憶された基準フレーム内で決定され、したがって、第1の基準領域内の基準ピクセルブロックは、基準フレームに対応する参照番号、及び基準フレーム内の局所性に対応する位置座標でタグ付けされる。動作804で、第1の基準領域に関連付けられたタグ情報を、各ピクセルブロック領域に関連付けられたスパン情報を比較することによって、第1の基準領域を含む可能性がある第1のキャッシュ（例えば、図1の第1のキャッシュ106a）の1つ又は複数のピクセルブロック領域の中からのピクセルブロック領域が識別される。第1の基準領域に関連付けられたタグ情報は、参照番号（例えば、図5のref#504）及び位置座標（例えば、図5の(X, Y)506）を含む。スパン情報は、各ピクセルブロック領域の長さ方向に沿った寸法（例えば高さ）及び幅方向に沿った寸法（例えば幅）を示す。比較の間、

X BA - X及び<BA - (X + ピクセルブロック領域の幅)、及び

Y BA - Y及び<BA - (Y + ピクセルブロック領域の高さ)

であるかどうかが決定される。ここで、BAは、1つ又は複数のピクセルブロック領域の各々のベースアドレスであり、(X, Y)は、第1の基準領域に関連付けられた位置座標である。

#### 【0077】

識別されたピクセルブロック領域内の基準ピクセルブロックの存在を決定するために、識別されたピクセルブロック領域についてオフセットチェックが行われる。オフセットチェックの間、識別されたピクセルブロック領域の各々に関連付けられたスパン情報、及び基準フレーム内の第1の基準領域の位置に基づいて、識別されたピクセルブロック領域の

10

20

30

40

50

各々内の第1の基準領域の可能なオフセットが決定される。決定されたあり得るオフセットでの各基準ピクセルブロックに関連付けられる複数の利用可能性タグをチェックすることによって、識別されたピクセルブロック領域の各々における決定されたあり得るオフセットでの第1の基準領域の存在が決定される。動作806で、決定されたあり得るオフセットでの基準ピクセルブロックに関連付けられる複数の利用可能性タグをチェックすることによって、識別されたピクセルブロック領域の各々における決定されたあり得るオフセットでの第1の基準領域の存在が決定される。一実施形態において、基準ピクセルブロックが存在する場合、基準ピクセルブロックに関連付けられる利用可能性タグがHITとしてマーク付けされ、基準ピクセルブロックが存在しない場合、利用可能性タグはMISSとしてマーク付けされる。一実施形態において、利用可能性タグのマーク付けは、図3Cを参照して本明細書で説明するように行われ得る。

10

#### 【0078】

動作808で、第1の基準領域が第1のキャッシュのピクセルブロック領域に存在すると決定されるかどうかが検証される。第1のキャッシュのピクセルブロック領域に第1の基準領域が存在しない場合、動作810で、第2のキャッシュ（例えば、第2のキャッシュ106b）における第1の基準領域の存在が決定される。反対に、第1のキャッシュのピクセルブロック領域に第1の基準領域が存在すると決定されると、動作812が行われる。動作812では、マルチメディアフレームにおけるブロック区画における複数のピクセルブロックが、第1の基準領域に基づいて処理される。マルチメディアフレームの処理の例には、符号化/復号化目的でマルチメディアデータのフレームに対して動き補償を実行することが含まれ得る。動作810で第2のキャッシュにおける第1の基準領域の存在が決定されると、続いて動作814が行われる。動作814では、第1の基準領域が第2のキャッシュ内に存在すると決定されるかどうかが検証される。第1の基準領域が第2のキャッシュ内に存在すると決定された場合、動作816が行われる。動作816では、第1の基準領域に関連付けられた基準ピクセルブロックが、第2のキャッシュから第1のキャッシュにフェッチされる。

20

#### 【0079】

代替として、第1の基準領域が第2のキャッシュに存在しないと決定された場合、動作818で、第1の基準領域に関連付けられた基準ピクセルブロックをメモリからフェッチするために、メモリフェッチコマンドが生成される。一実施形態において、メモリフェッチコマンドは、第1のキャッシュに関連付けられる複数のキャッシュバンクのうちのキャッシュバンクに対して（例えば、図1の処理ユニット102を用いて）生成される。一実施形態において、1つ又は複数の追加の基準ピクセルブロックと、第1の基準領域に関連付けられた1つ又は複数の基準ピクセルブロックとが、基準フレーム内で互いに近接し、基準フレーム内で矩形領域（連続的領域）を形成するように、第1の基準領域と共にフェッチされるべき1つ又は複数の追加の基準ピクセルブロックが決定される。一実施形態において、図6A～図6Cを参照して本明細書で説明するように第1の基準領域及び1つ又は複数の追加の基準ピクセルブロックをフェッチするために、メモリフェッチコマンドが生成される。一実施形態において、1つ又は複数の追加の基準ピクセルブロック及び第1の基準領域は、基準フレーム内の複数のブロック区画の中からのブロック区画に対応する。一実施形態において、1つ又は複数の追加の基準ピクセルブロック及び第1の基準領域は、基準フレーム内の近接するブロック区画に対応する。1つ又は複数の追加の基準ピクセルブロック及び第1の基準領域は、同じ又は異なるキャッシュバンクに関連付けられ得る。

30

#### 【0080】

動作820で、生成されたメモリフェッチコマンドに基づいて、第1の基準領域に関連付けられた基準ピクセルブロックがメモリからフェッチされる。一実施形態において、第1の基準領域は、生成されたメモリフェッチコマンドに基づいて、1つ又は複数の追加の基準ピクセルブロックと共にメモリからフェッチされる。メモリから第1の基準領域の各々をフェッチするための最小細分性が、メモリに関連付けられたプリフェッチバッファの

40

サイズとマッチングする。基準ピクセルブロックは、図 6 A ~ 図 6 C を参照して本明細書で説明するようにメモリからフェッチされ得る。基準ピクセルブロックがメモリ又は第 1 のキャッシュのいずれかからフェッチされると、動作 822 が行われる。

#### 【0081】

動作 822 では、フェッチされた基準ピクセルブロックが、所定の基準に基づいて、第 1 のキャッシュにおける 1 つ又は複数のピクセルブロック領域に割り当てられる。所定の基準は、基準フレームによって定義されたスペース内の基準ピクセルブロックの局所性を含むが、これに限定されない。割り当てられた基準ピクセルブロックに関連付けられるキャッシュバンクが、キャッシュバンクに関連付けられたすべての基準ピクセルブロックがキャッシュバンクから読み取られた時点で満了するように構成される。キャッシュバンクが満了すると、キャッシュバンクに関連付けられた基準ピクセルブロックは、第 1 のキャッシュから削除され、マルチメディアフレームに関連付けられる後続のピクセルブロックを処理するために第 2 のキャッシュに関連付けられたキャッシュバンクに割り当てられる。一実施形態において、フェッチされた 1 つ又は複数の基準ピクセルブロックをキャッシュするために、第 2 のキャッシュ内のスペースの利用可能性が決定される。スペースの利用可能性を決定すると、フェッチされた基準ピクセルブロックは第 2 のキャッシュにキャッシュされる。代替として、スペースの利用不能性を決定すると、第 2 のキャッシュに以前にキャッシュされた 1 つ又は複数の基準ピクセルブロックが削除され、フェッチされた基準ピクセルブロックをキャッシュするために第 2 のキャッシュの起点が所定のマージンだけシフトされる。第 1 のキャッシュに割り当てられた各基準ピクセルブロックが、動作 20 824 を受ける。動作 824 では、マルチメディアフレームの処理の間第 1 の基準領域の検索を促進するように、各基準ピクセルブロックがピクセルブロック領域に基づいてタグに関連付けられる。

#### 【0082】

本明細書で開示された例示の実施形態のうちの 1 つ又は複数の利点が、以下に記載の特許請求の範囲、その解釈又は適用をいかなる方式でも制限することなく、マルチメディアデータに関連付けられる、メモリ帯域幅消費の低減、及びその結果としてのメモリによる電力損失の低減及び再生時間の増加（例えば、再生時間は 3 時間増加する可能性がある）を含む。第 1 のキャッシュにおいてピクセルブロック領域を定義すること、及び、対応するピクセルブロック領域のベースアドレスからのオフセットとして基準ピクセルブロックにタグ付けすることで、タグ付け基準データのサイズが低減し、それによって比較コストが削減され、電力消費のかなりの節約につながる。また、第 2 のキャッシュから基準データをフェッチするために用いられる処理サイクルの数（例えば 10 処理サイクル）は、メモリから基準データをフェッチするために用いられる処理サイクルの数（例えば 100 処理サイクル）より少ないため、第 2 のキャッシュを用いることによって処理サイクルの総数が削減される。また、マルチメディアデータのフレームにおいて近接するピクセルブロックに関連付けられた基準ピクセルブロックをグループ化することによって、バースト当たりのデータ位相の数が、代替のキャッシュパラダイムでは 1 であるのに対して、約 8 まで増加される。バースト当たりのデータ位相が増加することは、相互接続及びメモリインターフェース電力の削減につながる。

#### 【0083】

加えて、基準データフェッチのサイズがメモリのプリフェッチバッファの最大サイズとマッチングするので、プリフェッチバッファと同等のサイズの 1 ピクセルブロック或いは 1 つ又は複数のピクセルブロックをフェッチするために等しい量の電力が損失されるため、システム内で電力が効率的に用いられる。本明細書で開示されるシステムは、効率的なメモリフェッチ動作（例えば DMA）を可能にするために、パイプライン様式で動作するように構成される。図 4 B の詳細な説明で説明された 3 つのキャッシュバンクのパイプライン動作は、コヒーレンシを維持するための複雑な論理を排除し、様々な段の並列及び効率的な動作を可能にする。さらに、本技術において、結合性が高くなることでメモリ仕様が低下している。また、本明細書で開示される方法及びシステムは、毎秒 120 フレーム

10

20

30

40

50

に近いフレームレートの達成を可能にする。

【0084】

本明細書に記載された様々なデバイス、モジュール、分析器、生成器などは、ハードウェア回路（例えば、相補型金属酸化物半導体（C M O S）ベースの論理回路）、ファームウェア、ソフトウェア、並びに／或いは、ハードウェア、ファームウェア、及び／又は（例えば、機械可読媒体において具現化される）ソフトウェアの組み合わせを用いて、可能化及び動作され得る。例えば、様々な電気的構造及び方法は、トランジスタ、論理ゲート、及び電気回路（例えば、特定用途向け集積回路（A S I C）回路、及び／又はデジタル信号プロセッサ（D S P）回路）を用いて具現化され得る。

【0085】

特に、システム100、処理ユニット102、メモリ104、及びキャッシュユニット106は、ソフトウェアを用いて、及び／又は、トランジスタ、論理ゲート、及び電気回路（例えば、A S I C回路などの集積回路）を用いて可能とされ得る。本開示の様々な実施形態は、コンピュータ読み取り可能媒体上に記憶されるか又はその他の方式で具現化された、1つ又は複数のコンピュータプログラムを含み得、コンピュータプログラムは、プロセッサ又はコンピュータに1つ又は複数の動作を行わせるように構成される。コンピュータプログラム又は同様の言語を記憶する、具現化する、又はコンピュータプログラム又は同様の言語で符号化されるコンピュータ可読媒体が、プロセッサ又はコンピュータに1つ又は複数の動作を行わせるように構成された1つ又は複数のソフトウェアプログラムを記憶する有形データ記憶デバイスとして具現化され得る。こうした動作は、例えば、本明細書で説明されるステップ又は動作のいずれかであり得る。また、有形データ記憶デバイスが、1つ又は複数の揮発性メモリデバイス、1つ又は複数の不揮発性メモリデバイス、及び／又は、1つ又は複数の揮発性メモリデバイス及び不揮発性メモリデバイスの組み合わせとして、具現化され得る。

【0086】

また、様々な実施形態において離散型又は分離型として説明及び例示された技法、デバイス、サブシステム、及び方法は、本技術の範囲から逸脱することなく、他のシステム、モジュール、技法、又は方法と組み合わされ得るか又は統合され得る。互いに直接的に結合されるか又は通信しているように図示又は説明される他のアイテムが、そのアイテムがもはや互いに直接的に結合されているとはみなされ得ないが、依然として間接的に結合され得、電気的、機械的、又はその他の方式で互いに通信し得るように、何らかのインターフェース又はデバイスを介して結合され得る。当業者によって確認され得る変更、置換、及び改変の他の例が、本明細書で開示される例示の実施形態を検討した時点又はその後に、本技術の趣旨及び範囲から逸脱することなく成され得る。加えて、例示の目的で、詳細な説明はフレームに関連付けられたピクセルブロックに言及しているが、本明細書で開示される方法及びシステムの範囲は、ピクセルブロックに限定されず、H E V C パラダイムに従ったコーディングユニットを含むように拡張され得る。

【0087】

当業者であれば、本発明の特許請求の範囲内で、例示の実施形態に対してさらなる改変が成され得ること、及び多くの他の実施形態が存在することが理解されよう。

10

20

30

40

【図1】

【図 3 A - 3 C】

FIG. 1

【 図 2 】

【図4A】

【図4B】

### 【図4B】

FIG. 4B

【図5】

【図6 A】

FIG. 6A

【図6 B】

FIG. 6B

【図6 C】

FIG. 6C

【図7】

FIG. 7

【図8 A】

【図 8 B】

---

フロントページの続き

(72)発明者 ヘトゥル サンギヴィ

インド 560097 カルナタカ, バンガロール, ヴィドヤランヤプラ, ナンダナヴァナ

ム レイアウト, 6エイ メイン, サイ ダーサン エイピーティーエス 301

(72)発明者 ムランギ ヴェンカタ ラトゥナ レディ

インド 560043 カルナタカ, バンガロール, カストウリナガール, ファースト メ

イン, フォース クロス 110

(72)発明者 アジト ディーパック グプテ

インド 56008 カルナタカ, バンガロール, コディハリ, セカンド メイン ロード

, アシュウイニ ハイツ 204

(72)発明者 アリンダム バサク

インド 560075 カルナタカ, バンガロール, ニュー ティッパサンドラ, セブンス

クロス, フォース メイン, セカンド フロア 1882

審査官 塚田 肇

(56)参考文献 特開2003-256275(JP, A)

特開2010-102623(JP, A)

特開2007-279829(JP, A)

特表2008-512967(JP, A)

米国特許出願公開第2010/0118043(US, A1)

米国特許出願公開第2007/0176939(US, A1)

特表平4-505818(JP, A)

米国特許出願公開第2011/0320729(US, A1)

米国特許第5960193(US, A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/08

H04N 19/433