【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成18年1月5日(2006.1.5)

【公表番号】特表2004-528719(P2004-528719A)

【公表日】平成16年9月16日(2004.9.16)

【年通号数】公開・登録公報2004-036

【出願番号】特願2002-592201(P2002-592201)

【国際特許分類】

|               |                |                  |

|---------------|----------------|------------------|

| <i>H 01 L</i> | <i>27/06</i>   | <i>(2006.01)</i> |

| <i>H 01 L</i> | <i>29/78</i>   | <i>(2006.01)</i> |

| <i>H 01 L</i> | <i>27/04</i>   | <i>(2006.01)</i> |

| <i>H 01 L</i> | <i>21/8234</i> | <i>(2006.01)</i> |

| <i>H 01 L</i> | <i>21/822</i>  | <i>(2006.01)</i> |

| <i>H 01 L</i> | <i>21/336</i>  | <i>(2006.01)</i> |

| <i>H 01 L</i> | <i>29/866</i>  | <i>(2006.01)</i> |

【F I】

|               |              |                |

|---------------|--------------|----------------|

| <i>H 01 L</i> | <i>27/06</i> | <i>3 1 1 B</i> |

| <i>H 01 L</i> | <i>29/78</i> | <i>6 5 2 B</i> |

| <i>H 01 L</i> | <i>29/78</i> | <i>6 5 3 A</i> |

| <i>H 01 L</i> | <i>29/78</i> | <i>6 5 7 C</i> |

| <i>H 01 L</i> | <i>27/06</i> | <i>1 0 2 A</i> |

| <i>H 01 L</i> | <i>27/04</i> | <i>H</i>       |

| <i>H 01 L</i> | <i>29/78</i> | <i>6 5 8 A</i> |

| <i>H 01 L</i> | <i>29/90</i> | <i>D</i>       |

【手続補正書】

【提出日】平成17年5月18日(2005.5.18)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【発明の詳細な説明】

【発明の名称】静電気放電保護のためのツエナーダイオードを備える二重拡散金属酸化膜半導体トランジスタ

【技術分野】

【0001】

本発明は、一般的には金属酸化膜半導体電界効果トランジスタに関し、特に、トレンチ構造を有する二重拡散金属酸化膜半導体トランジスタに関する。

【背景技術】

【0002】

二重拡散金属酸化膜半導体(Doubled diffused metal-oxide-semiconductor transistor:以下、DMOSという。)トランジスタは、拡散プロセスによってトランジスタ領域を形成した金属酸化膜半導体電界効果トランジスタ(Metal On Semiconductor Field Effect Transistor:以下、MOSFETという。)の一種である。DMOSトランジスタは、通常、電源集積回路用途(power integrated circuit applications)における高電圧回路を実現するためのパワートランジスタとして採用されている。DMOSトランジスタは、低い順電圧降下が要求される場合に、単位面積当たりの電流値をより大きする必要がある。

**【 0 0 0 3 】**

一般的なディスクリート D M O S 回路は、並列に配設された 2 つ以上の個々の D M O S トランジスタセルを備える。各 D M O S トランジスタセルは、同じドレイン接続（基板）を共有し、各 D M O S トランジスタセルの全てのソースは、互いに金属により短絡され、各 D M O S トランジスタセルのゲートは、互いにポリシリコンにより短絡されている。これにより、複数の小さなトランジスタのマトリクスから構成されたディスクリート D M O S 回路であっても、単一の大きなトランジスタとして動作する。ディスクリート D M O S 回路においては、トランジスタマトリクスがゲートによってオンになったとき、単位面積当たりの伝導率を最大にすることが好ましい。

**【 0 0 0 4 】**

代表的な D M O S トランジスタとしては、所謂トレンチ D M O S トランジスタがあり、トレンチ D M O S トランジスタでは、チャネルが垂直に形成され、ゲートは、ソースとドレイン間に延びるトレンチ内に形成されている。トレンチは、内壁が薄膜酸化層で覆われ、ポリシリコンで埋められており、これにより電流が妨害されず、固有のオン抵抗値をより小さくすることができる。D M O S トランジスタの具体例は、米国特許第 5 , 0 7 2 , 2 6 6 号、第 5 , 5 4 1 , 4 2 5 号、第 5 , 8 6 6 , 9 3 1 号にも開示されている。

**【 0 0 0 5 】**

静電気放電（Electrostatic Discharge：以下、E S D という。）は、半導体素子、特に D M O S 構造体にとって重要な問題である。静電気放電からの高電圧過渡信号（high voltage transient signal）は、対象物に一万ボルト以上の電圧をかけることもある。D M O S 素子に固有の問題として、標準的動作のM O S 素子において使用されている比較的薄いゲート誘電体に強い電界が生じることがある。ゲート誘電体は、多くの場合酸化物であり、強い電界が生じると、ゲートに蓄積された電荷が、正常時には絶縁体として動作するゲート酸化層を通り抜け、ゲート誘電体が破壊（rupture）されてしまうことがある。この破壊によって生じる恒久的な損傷の影響は、直ちには現れない。したがって、ゲート酸化層の破壊の可能性は、現実的な信頼度に関わる問題となる。E S D が発生する条件は、多くの作業環境において生じるものであり、市販されている D M O S は、自ら E S D 保護回路（ESD protection systems）を備えているものも多い。この E S D 保護回路は、主機能回路（main functional circuitry）から独立している場合もあり、主機能回路に組み込まれている場合もある。

**【 0 0 0 6 】**

酸化層を破壊する電圧以上の電圧から素子のゲートを保護するために、D M O S 素子のゲートとソース間にツェナーダイオードを接続する手法がある。このような手法及び素子は、例えば、米国特許第 5 , 6 0 2 , 0 4 6 号に開示されている。この手法は、M O S F E T ゲートの E S D 定格（ESD rating）を向上させ、過電圧損傷を回避することに貢献する。

**【 0 0 0 7 】**

この特許文献に開示されている素子の問題は、この素子の製造のためにマスキングプロセスを追加する必要があり、その構造が複雑になり、素子の製造コストが高くなるという点である。

**【 0 0 0 8 】**

したがって、E S D に起因する過電圧保護機構を有するとともに、構造が比較的単純で、安価に製造できるトレンチ D M O S トランジスタの実現が望まれている。

**【 発明の開示 】****【 課題を解決するための手段 】****【 0 0 0 9 】**

本発明は、過電圧保護機構を有する二重拡散金属酸化膜半導体トランジスタを提供する。二重拡散金属酸化膜半導体トランジスタは、第 1 の伝導性タイプを有する基板と、基板上に形成され、第 2 の伝導性タイプを有するボディ領域とを備える。少なくとも 1 つのトレンチは、ボディ領域及び基板に亘って延びる。絶縁層は、トレンチの内壁及びボディ領

域上に形成される。導電性電極は、トレンチ内に蒸着され、トレンチ内の絶縁層に重なる。第1の伝導性タイプを有するソース領域は、トレンチに隣接するボディ領域に形成される。ドーピングされていないポリシリコン層は、絶縁層の一部に重なるよう形成される。第1の伝導性タイプを有する複数のカソード領域は、ドーピングされていないポリシリコン層内に形成される。少なくとも1つのアノード領域は、複数のカソード領域のうち隣接するカソード領域に接する。

#### 【0010】

本発明の一実施例においては、ドーピングされていないポリシリコン層は、ボディ領域から垂直方向に位置する絶縁層の一部に重なる。

#### 【0011】

本発明の他の実施例においては、複数のカソード領域及びアノード領域は、トレンチから垂直方向に位置する絶縁層の一部に設けられる。

#### 【0012】

本発明の他の実施例においては、複数のカソード領域には、ホウ素が打込まれている。

#### 【0013】

本発明の他の実施例においては、ソース領域と、複数のカソード領域とは、同じ蒸着工程で同時に形成される。

#### 【発明を実施するための最良の形態】

#### 【0014】

図1は、DMOS素子のソースとゲート間にツェナーダイオードが設けられた典型的なNチャンネルDMOS素子の等価回路である。ツェナーダイオードは、ゲート-ソース間の電圧が規定の電圧値を超えたとき、降伏する。

#### 【0015】

図2は、従来のトレンチDMOS構造体の具体例を示している。この構造体は、 $n^+$ 基板100を備え、 $n^+$ 基板100上には、 $n$ ドープエピタキシャル層104が成長されている。 $n$ ドープエピタキシャル層104内には、逆の伝導性を有するボディ領域116が形成されている。ボディ領域116の大部分に重なる $n$ ドープエピタキシャル層104は、ソースとして機能する。エピタキシャル層104内には、長方形状のトレンチ124が形成されており、トレンチ124は、構造体の上面において開口しており、トランジスタセルの外周を画定している。トレンチ124の内壁には、ゲート酸化層130が設けられている。トレンチ124には、ポリシリコン、すなわち多結晶シリコンが埋め込まれている。半導体基板100の背面には、ドレイン電極が接続されており、2つのソース領域140及びボディ領域116には、ソース電極が接続されており、トレンチ124に埋め込まれたポリシリコンには、ゲート電極が接続されている。

#### 【0016】

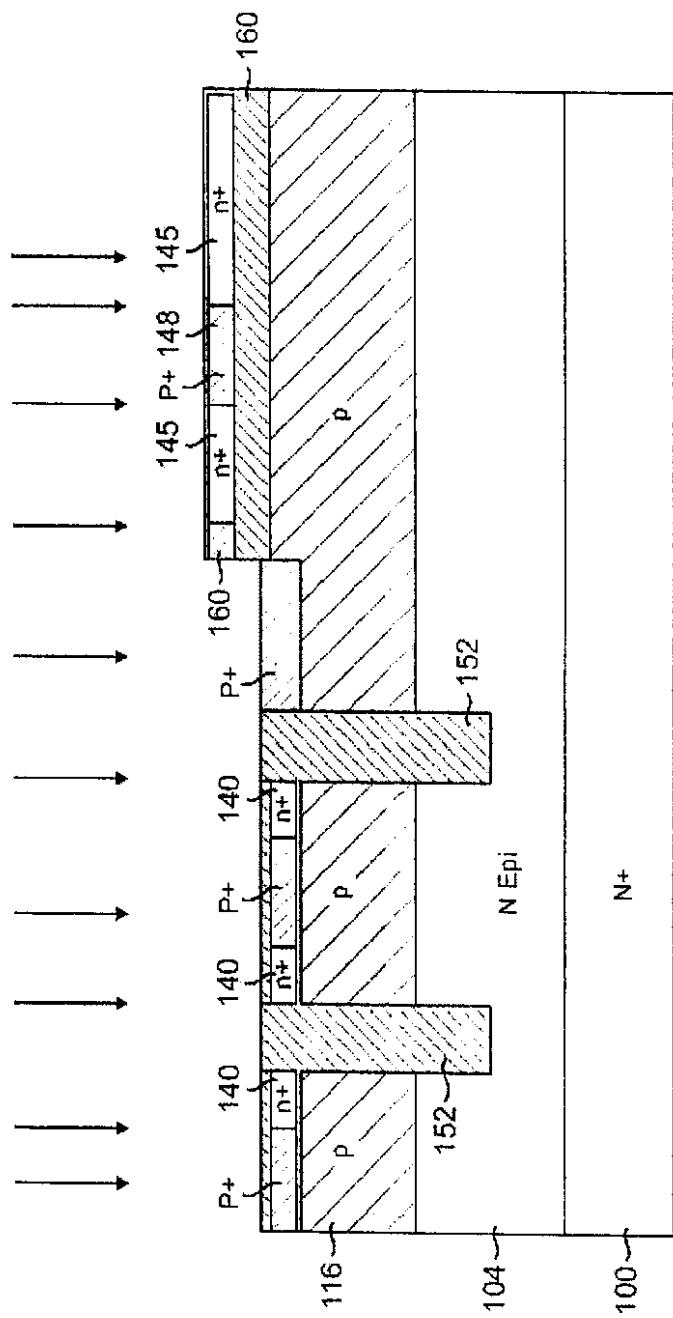

本発明では、新たなマスキングプロセスを追加することを必要とせずに、図2に示すようなトレンチDMOS構造体にツェナーダイオードを組み込む。図11は、本発明に基づいて製造された素子の断面を示している。図11に示す実施例では、ツェナーダイオードは、カソード領域145とアノード領域148から構成されている。後述するように、図11に示す構造は、DMOSトランジスタのソース領域140及びツェナーダイオードの $n^+$ カソード領域145を同じマスキングプロセス及び打込みプロセスで形成できるという利点がある。

#### 【0017】

図3～図12は、本発明に基づくDMOS素子を製造するためのプロセスを説明する図である。図3に示すように、まず、従来と同様の $n^+$ ドープ基板100上に $n$ ドープエピタキシャル層104を成長させる。エピタキシャル層104は、例えば30ボルト素子の場合、5.5ミクロンの厚みに形成するとよい。次に、打込み及び拡散プロセスによって、 $p$ ボディ領域116を形成する。 $p$ ボディ領域116を形成するための打込みプロセスは、基板全体に亘って均一に行うため、マスキングプロセスは不要である。 $p$ ボディ領域116には、 $40 \sim 60\text{ keV}$ で、ドーズ量を約 $5.5 \times 10^{13} / \text{cm}^3$ として、ホウ

素を打ち込む。

【0018】

次に、図4に示すように、エピタキシャル層104の表面を酸化層で覆いマスク層を形成し、このマスク層を従来と同様の手法で露光してパターン化し、マスク部120のみを残す。マスク部120は、トレンチの位置を画定するために用いられる。また、パターン化されたマスク部120は、トレンチ124の側壁を画定する。トレンチ124を、マスク部120の開口部を介して反応性イオンエッティングによって通常1.5～2.5μの深さにドライエッティングする。

【0019】

トレンチ124をエッティングした後、トレンチ124の側壁を平坦化する。最初に、ケミカルドライエッティング(dry chemical etch)により、トレンチ124の側壁から酸化物の薄膜(通常約500～1,000)を取り除き、これにより、反応性イオンエッティングプロセスによって生じる損傷(damage)を除去する。次に、犠牲二酸化シリコン層(sacrificial silicon dioxide layer)(図示せず)をトレンチ124及びマスク部120上に成長させる。緩衝酸化層エッティング(buffer oxide etch)又はHFエッティング(HF etch)によって、犠牲二酸化シリコン層及びマスク部120を除去し、得られるトレンチ124の側壁をできる限り平坦にする。

【0020】

次に、図5に示すように、構造体全体にゲート酸化層130を蒸着させ、このゲート酸化層130がトレンチ120の側壁及びpボディ領域116の表面を覆う。ゲート酸化層130は、通常500～800の厚みに形成される。次に、トレンチ124内にポリシリコン152、すなわち多結晶シリコンを埋め込む。この蒸着の前に、ポリシリコン152は、通常、亜リン酸クロライド(phosphorous chloride)でドーピングされるか、又はヒ素又はリンを打ち込み、これにより、ポリシリコン152の抵抗率を通常20/m以下の範囲に低減する。幾つかの実施例においては、ポリシリコンを2工程のプロセスによって蒸着させてもよい。すなわち、第1の工程において、ドーピングされていないポリシリコンをトレンチの側壁に蒸着させ、続く第2の工程において、ドープされたポリシリコンを蒸着させる。多くの場合、ドーピングされたポリシリコン層の厚みは、ドーピングされていないポリシリコン層の厚みより厚く形成される。例えば、合計の厚みを約8000

として、ドーピングされたポリシリコン層の厚みと、ドーピングされていないポリシリコン層の厚みの比を7:1としてもよい。ドーピングされていないポリシリコン層は、緩衝層として設けられ、ドーパント材料がゲート酸化層を通り抜けて、pボディ領域に侵入することを防止し、パンチスルーエフェクトを更に低減する効果を有している。

【0021】

次に、図7に示すように、ポリシリコン層152をエッティングしてこの厚みを最適化し、pボディ領域116の表面に亘って形成されているゲート酸化層130の一部を露出させる。次に、図8に示すように、ゲート酸化層130及びドーピングされたポリシリコン層152の露出された表面の上に、ドーピングされていないポリシリコン層160を蒸着させる。ドーピングされていないポリシリコン層160は、ツェナーダイオードが形成される領域を画定し、多くの場合、5000～10000の範囲の厚みに形成される。

【0022】

次に、図9に示すように、ドーピングされていないポリシリコン層160をエッチングし、DMOSトランジスタが画定されている領域から完全に取り除く。すなわち、ドーピングされていないポリシリコン層160は、DMOSのトレンチ及びボディ領域に重ならないように取り除かれる。したがって、ドーピングされていないポリシリコン層160は、ツェナーダイオードが形成される領域のみに残る。

【0023】

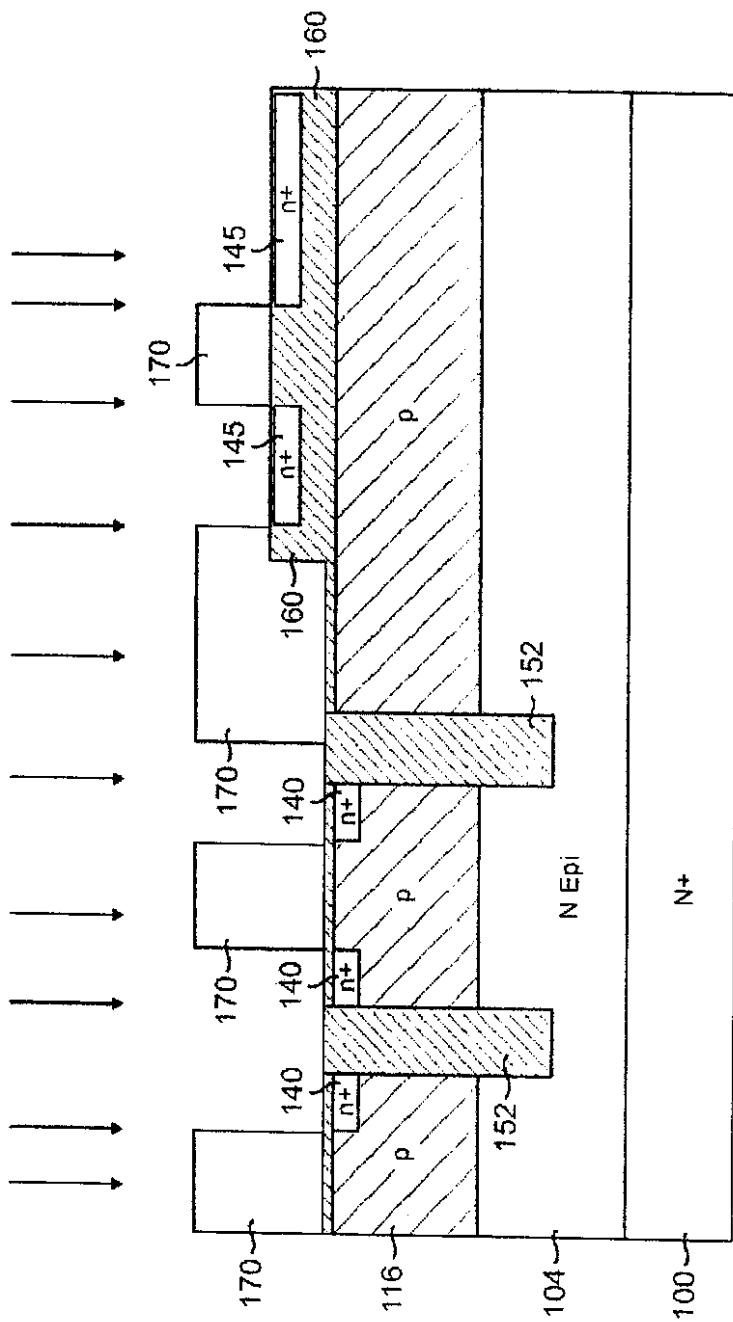

次に、図10に示すように、フォトレジストマスキングプロセスを用いて、パターンを有するマスク層170を形成する。パターンを有するマスク層170は、DMOSトランジスタのソース領域140と、ツェナーダイオードのn<sup>+</sup>カソード領域145とを画定す

る。次に、打込み及び拡散プロセスによって、ソース領域 140 及びカソード領域 145 を形成する。例えば、このソース領域 140 には、80 KeV で、ドーズ量を通常  $8 \times 10^{15} / \text{cm}^2 \sim 1.2 \times 10^{16} / \text{cm}^2$  として、ヒ素を打ち込む。打込みが行われた後、ヒ素が約  $0.5 \mu$  の深さに拡散する。次に、図 11 に示すように、従来と同様の方法でマスク層 170 を取り除き、ツェナーダイオードにおける所望の降伏電圧が実現されるように、カソード領域 145 とアノード領域 148 に中性ホウ素 (neutral boron) を打ち込む。

#### 【0024】

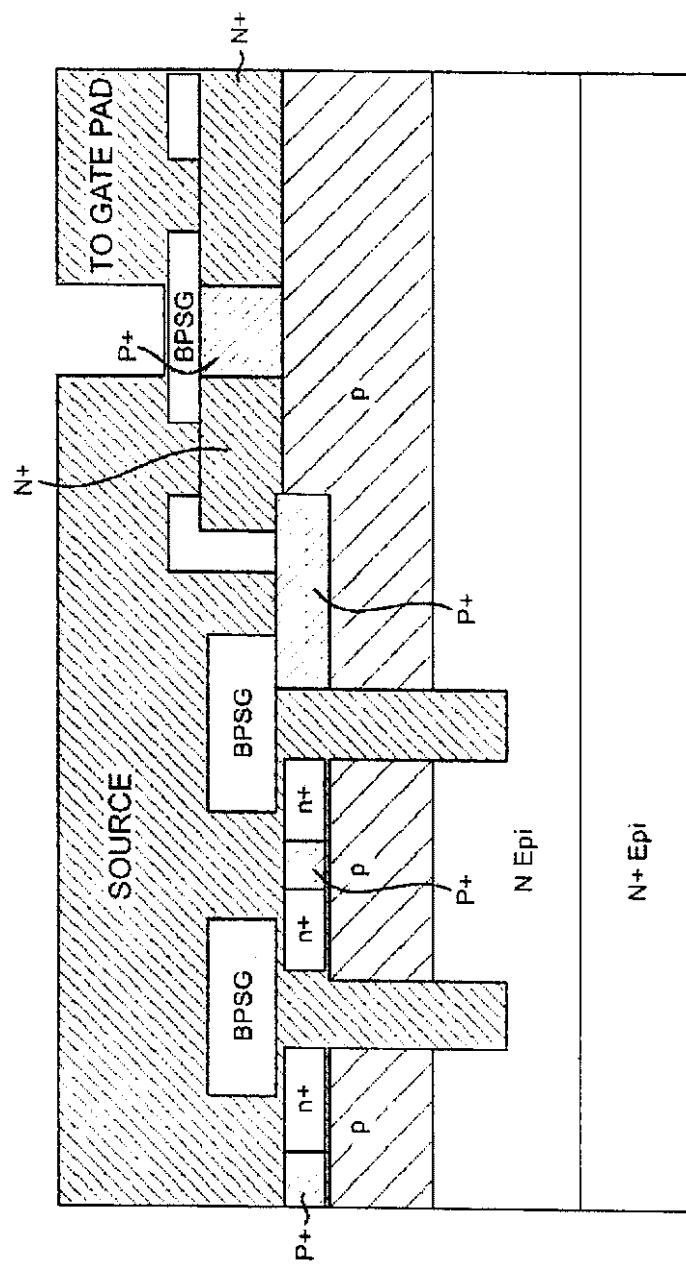

そして、図 12 に示すように、トレンチ DMOS ドラフトは、この構造上に、通常の方法によって BPSG 層を形成し、パターン化してソース及びゲート電極が接続される BPSG 領域を画定することにより、完成する。また、基板の底面には、ドレインコンタクト層を形成する。最後に、パッドマスクを用いて、パッドコンタクトを画定する。

#### 【0025】

以上、様々な実施例を詳細に図示し、説明したが、上述の説明から、本発明に基づくこれらの実施例を修正及び変更することができ、このような修正及び変更は、添付の請求の範囲に基づく本発明の主旨及び範囲から逸脱するものではない。例えば、本発明の製造方法に基づいて、ここで述べた実施例とはそれぞれの半導体領域の伝導性が逆のトレンチ DMOS ドラフト及びツェナーダイオードを製造することもできる。

#### 【図面の簡単な説明】

#### 【0026】

【図 1】DMOS のソースとゲートの間に配設されたツェナーダイオードを備える一般的な N チャンネル DMOS の等価回路を示す回路図である。

#### 【図 2】従来のトレンチ DMOS ドラフト構造体の断面図である。

【図 3】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 4】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 5】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 6】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 7】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 8】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 9】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 10】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 11】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

【図 12】本発明に基づく、過電圧保護機構を有する DMOS ドラフトを製造する製造工程を説明する断面図である。

#### 【手続補正 2】

#### 【補正対象書類名】図面

#### 【補正対象項目名】図 10

#### 【補正方法】変更

#### 【補正の内容】

【図 10】

FIG. 10

【手続補正 3】

【補正対象書類名】図面

【補正対象項目名】図 11

【補正方法】変更

【補正の内容】

【図 11】

FIG. 11

【手続補正 4】

【補正対象書類名】図面

【補正対象項目名】図 1 2

【補正方法】変更

【補正の内容】

【図12】

FIG. 12