(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

(43) International Publication Date

26 May 2005 (26.05.2005)

PCT

(10) International Publication Number

**WO 2005/048342 A1**

(51) International Patent Classification<sup>7</sup>: **H01L 21/768**

(74) Agent: DRAKE, Paul, S.; One AMD Place, Mail Stop 68, P.O. Box 3453, Sunnyvale, CA 94088-3453 (US).

(21) International Application Number:

PCT/US2004/033417

(22) International Filing Date: 8 October 2004 (08.10.2004)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

10/705,631 8 November 2003 (08.11.2003) US

(71) Applicant (for all designated States except US): ADVANCED MICRO DEVICES, INC. [US/US]; One AMD Place, Mail Stop 68, P.O. Box 3453, Sunnyvale, CA 94088-3453 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): HOPPER, Dawn, M. [US/US]; 4327 Verdigris Circle, San Jose, CA 95134 (US). KINOSHITA, Hiroyuki [JP/US]; 1325 Yarmouth Terrace, Sunnyvale, CA 94087 (US). WOO, Christy [US/US]; 10706 Linda Vista Drive, Cupertino, CA 95014 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report

[Continued on next page]

(54) Title: METHOD FOR PREVENTING AN INCREASE IN CONTACT HOLE WIDTH DURING CONTACT FORMATION

(57) **Abstract:** According to one exemplary embodiment, a method for forming a contact over a silicide layer (214) situated in a semiconductor die comprises a step of depositing a barrier layer (202) on sidewalls (206,207) of a contact hole (208) and on a native oxide layer (210) situated at a bottom of the contact hole (208), where the sidewalls (206,207) are defined by the contact hole (208) in a dielectric layer (204). The step of depositing (150) the barrier layer (202) on the sidewalls (206,207) of the contact hole (208) and on the native oxide layer (210) can be optimized such that the barrier layer (202) has a greater thickness at a top of the contact hole (208) than a thickness at the bottom of the contact hole (208). According to this exemplary embodiment, the method further comprises a step of removing (152) a portion (219) of the barrier layer (202) and the native oxide layer (210) situated at the bottom of the contact hole (208) to expose the silicide layer (214).

WO 2005/048342 A1

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**METHOD FOR PREVENTING AN INCREASE IN CONTACT

HOLE WIDTH DURING CONTACT FORMATION**

TECHNICAL FIELD

5 The present invention is generally in the field of semiconductor device fabrication. More particularly, the present invention is in the field of contact formation for semiconductor devices in a semiconductor die.

BACKGROUND ART

10 Contacts are utilized, among other things, to provide connections between a transistor region of a semiconductor die and an interconnect metal layer situated above the transistor region. To achieve high circuit density, these contacts, which generally have a high aspect ratio, must fit within a small area of the semiconductor die without touching or otherwise interfering with each other. As such, it is important to control contact hole width during contact formation to achieve a contact having a sufficiently small width.

15 During a conventional contact fabrication process, a contact hole is typically defined by lithography and etched in an oxide layer, which can be situated, for example, over a transistor region of a semiconductor die. The resulting contact hole can be formed over a silicide layer, which can be connected to, for example, a source or drain area in the transistor region of the semiconductor die. The contact hole is then lined with a barrier layer comprising a metal, such as titanium, and filled with a metal, such as tungsten, to form a contact. However, before the barrier layer can be deposited on the sidewalls of the contact hole and on the silicide 20 layer situated at the bottom of contact hole, a native oxide layer that forms over the silicide layer must first be removed. In the conventional contact fabrication process, the native oxide layer is typically removed by utilizing a sputter etch process comprising argon.

25 However, during the sputter etch process, top corner portions of the oxide layer than defines the contact hole are also etched in addition to the native oxide layer, which causes the top of the contact hole to increase in width. As a result, the contact that is formed after the contact hole has been filled with tungsten has an undesirable increased width compared to the initial width of the patterned contact hole.

Thus, there is a need in the art for a method for forming a contact over a transistor region of a semiconductor die that prevents an undesirable increase in contact hole width during contact formation.

SUMMARY

30 The present invention is directed to method for preventing an increase in contact hole width during

contact formation. The present invention addresses and resolves the need in the art for a method for forming a contact over a transistor region of a semiconductor die that prevents an undesirable increase in contact hole width during contact formation.

According to one exemplary embodiment, a method for forming a contact over a silicide layer situated in a semiconductor die comprises a step of depositing a barrier layer on sidewalls of a contact hole and on a native oxide layer situated at a bottom of the contact hole, where the sidewalls are defined by the contact hole in a dielectric layer. For example, the barrier layer may be titanium/titanium nitride and dielectric layer may be PECVD oxide. The step of depositing the barrier layer on the sidewalls of the contact hole and on the native oxide layer can be optimized such that the barrier layer has a greater thickness at a top of the contact hole than a thickness at the bottom of the contact hole.

According to this exemplary embodiment, the method further comprises a step of removing a portion of the barrier layer and the native oxide layer situated at the bottom of the contact hole to expose the silicide layer. For example, the portion of the barrier layer and the native oxide layer situated at the bottom of the contact hole can be removed by utilizing a sputter etch process. The contact hole comprises an electrical contact width, where the electrical contact width is not increased by the sputter etch process. The dielectric layer comprises top corner regions situated adjacent to the contact hole, where the top corner regions of the dielectric layer are not etch during the step of removing the portion of the barrier layer and the native oxide layer situated at the bottom of the contact hole. Other features and advantages of the present invention will become more readily apparent to those of ordinary skill in the art after reviewing the following detailed description and accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

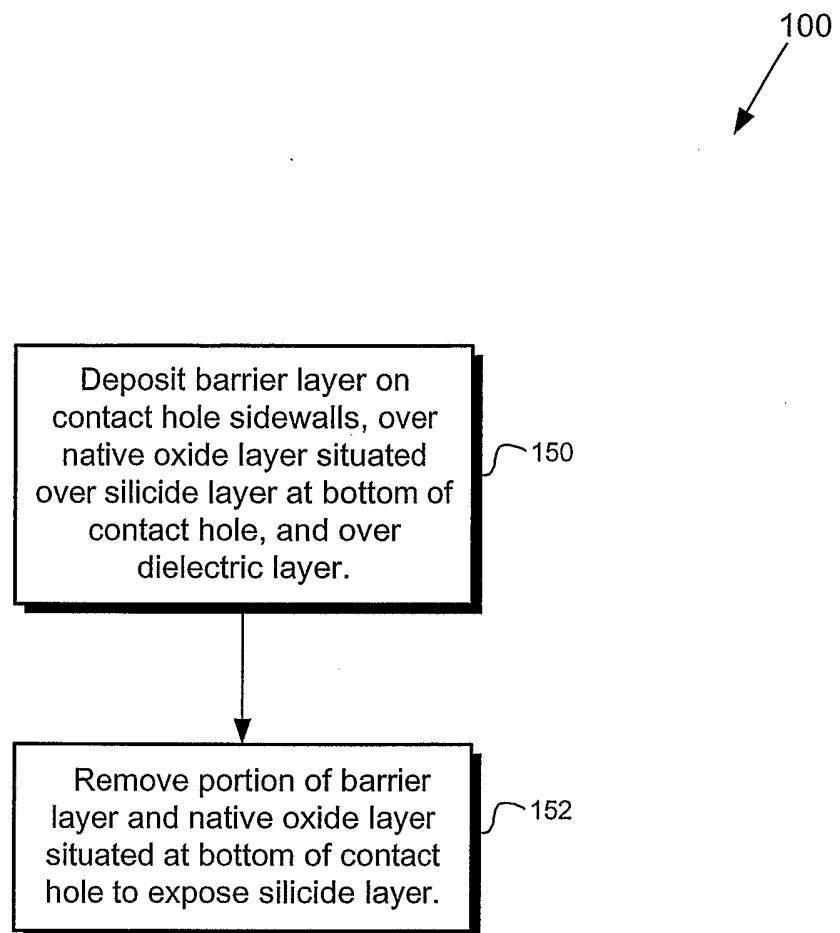

Figure 1 is a flowchart corresponding to exemplary method steps according to one embodiment of the present invention.

Figure 2A illustrates a cross-sectional view of a portion of a wafer processed according to an embodiment of the invention, corresponding to certain steps of the flowchart in Figure 1.

Figure 2B illustrates a cross-sectional view of a portion of a wafer processed according to an embodiment of the invention, corresponding to certain steps of the flowchart in Figure 1.

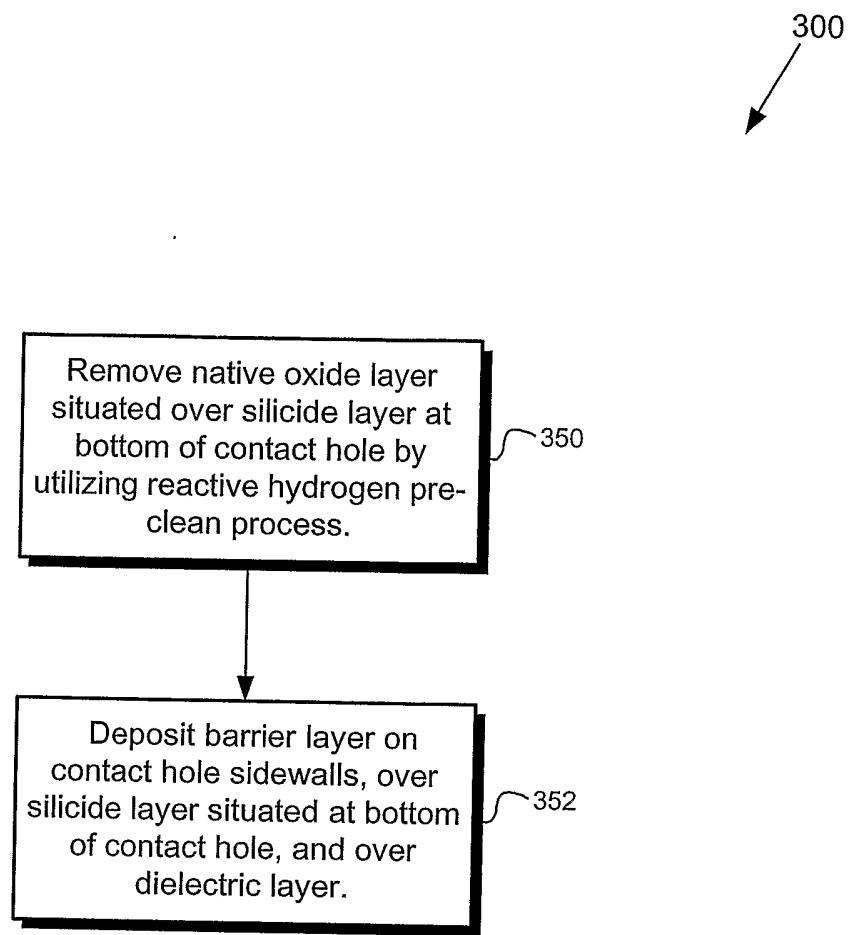

Figure 3 is a flowchart corresponding to exemplary method steps according to one embodiment of the present invention.

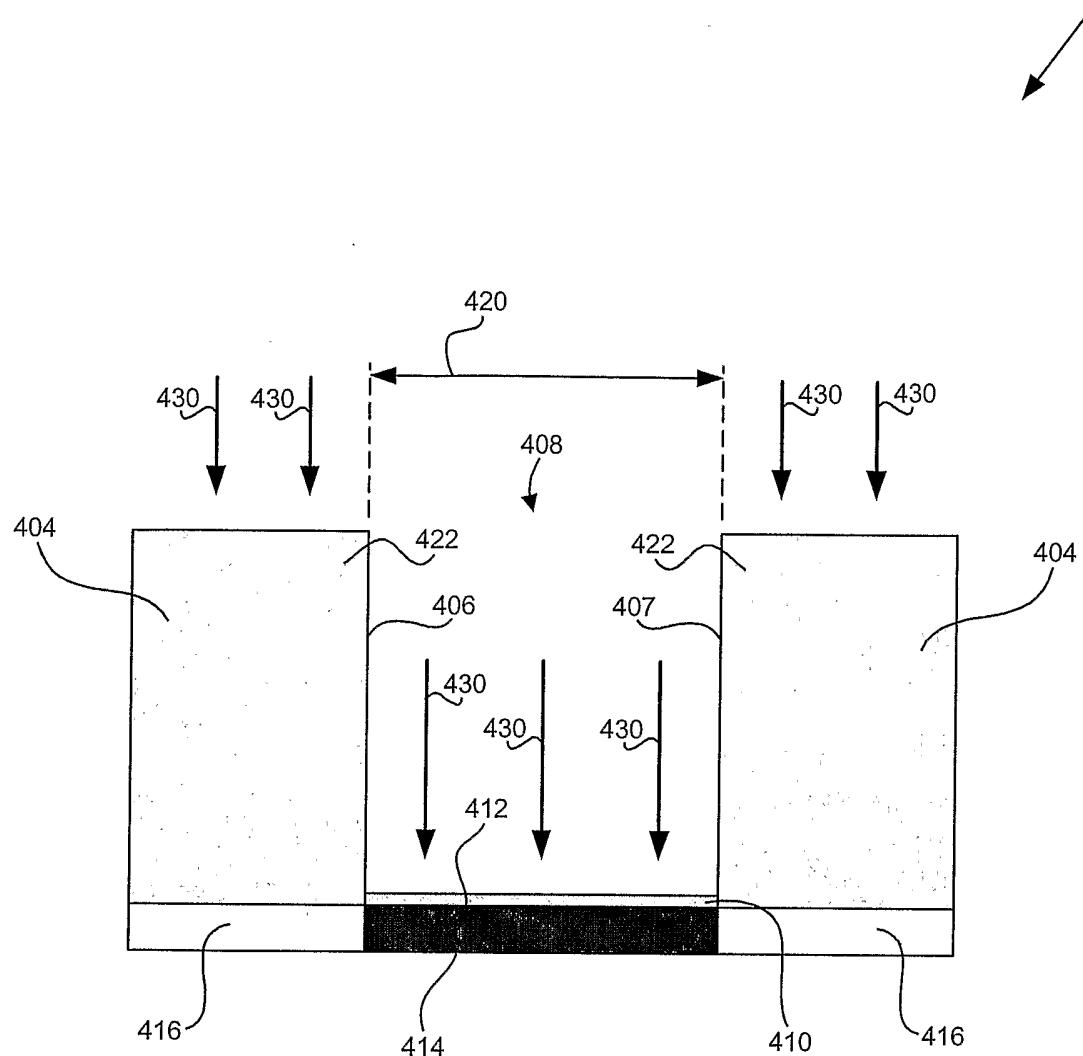

Figure 4A illustrates a cross-sectional view of a portion of a wafer processed according to an embodiment of the invention, corresponding to certain steps of the flowchart in Figure 3.

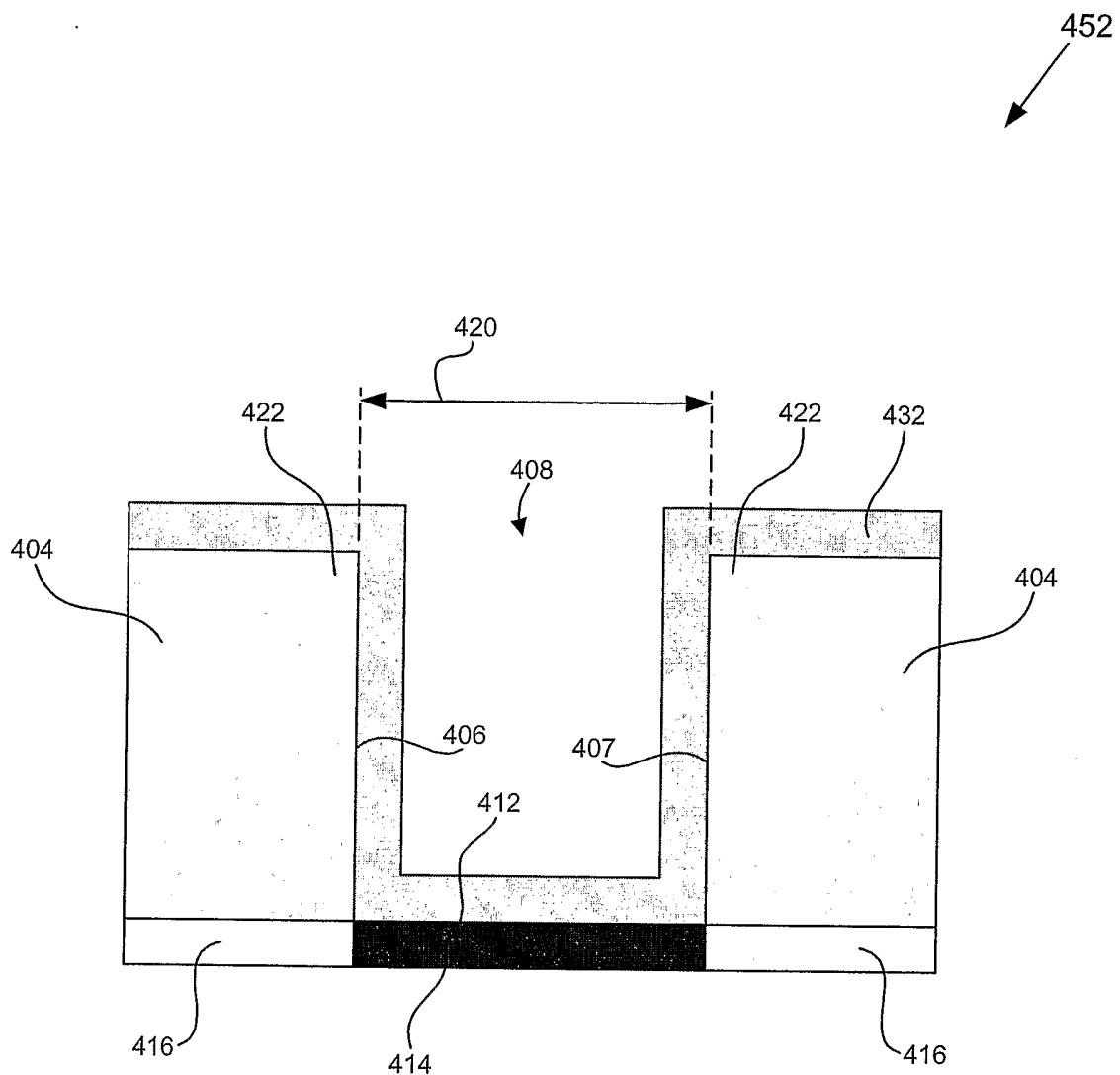

Figure 4B illustrates a cross-sectional view of a portion of a wafer processed according to an embodiment of the invention, corresponding to certain steps of the flowchart in Figure 3.

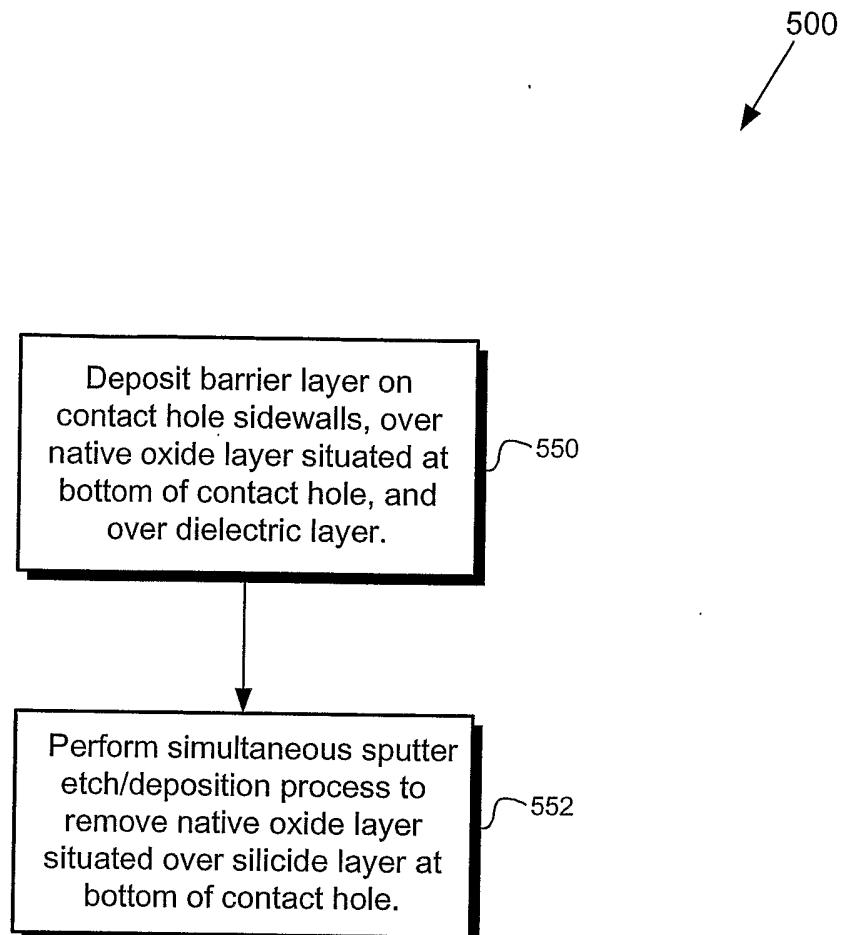

5 Figure 5 is a flowchart corresponding to exemplary method steps according to one embodiment of the present invention.

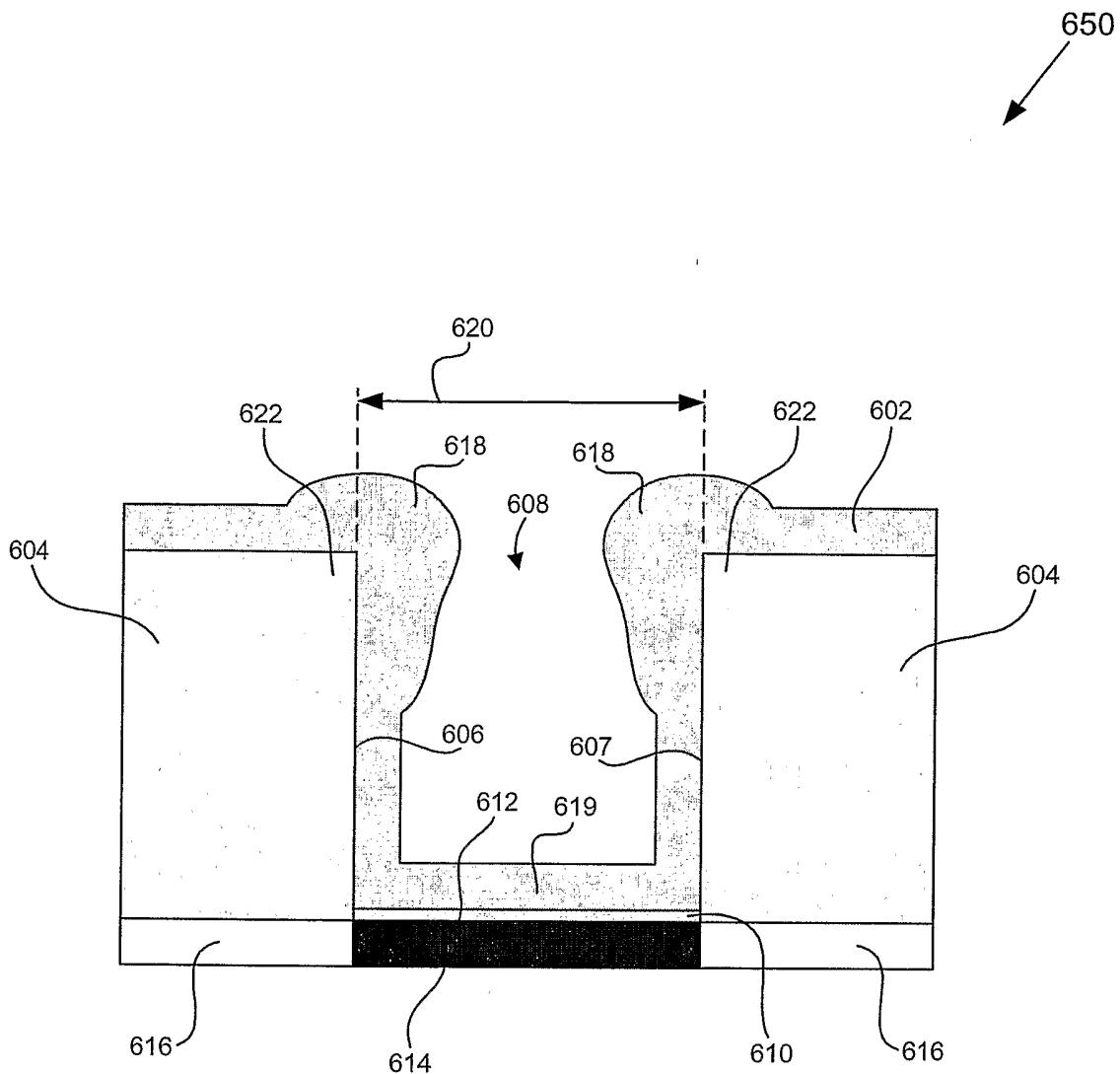

Figure 6A illustrates a cross-sectional view of a portion of a wafer processed according to an embodiment of the invention, corresponding to certain steps of the flowchart in Figure 5.

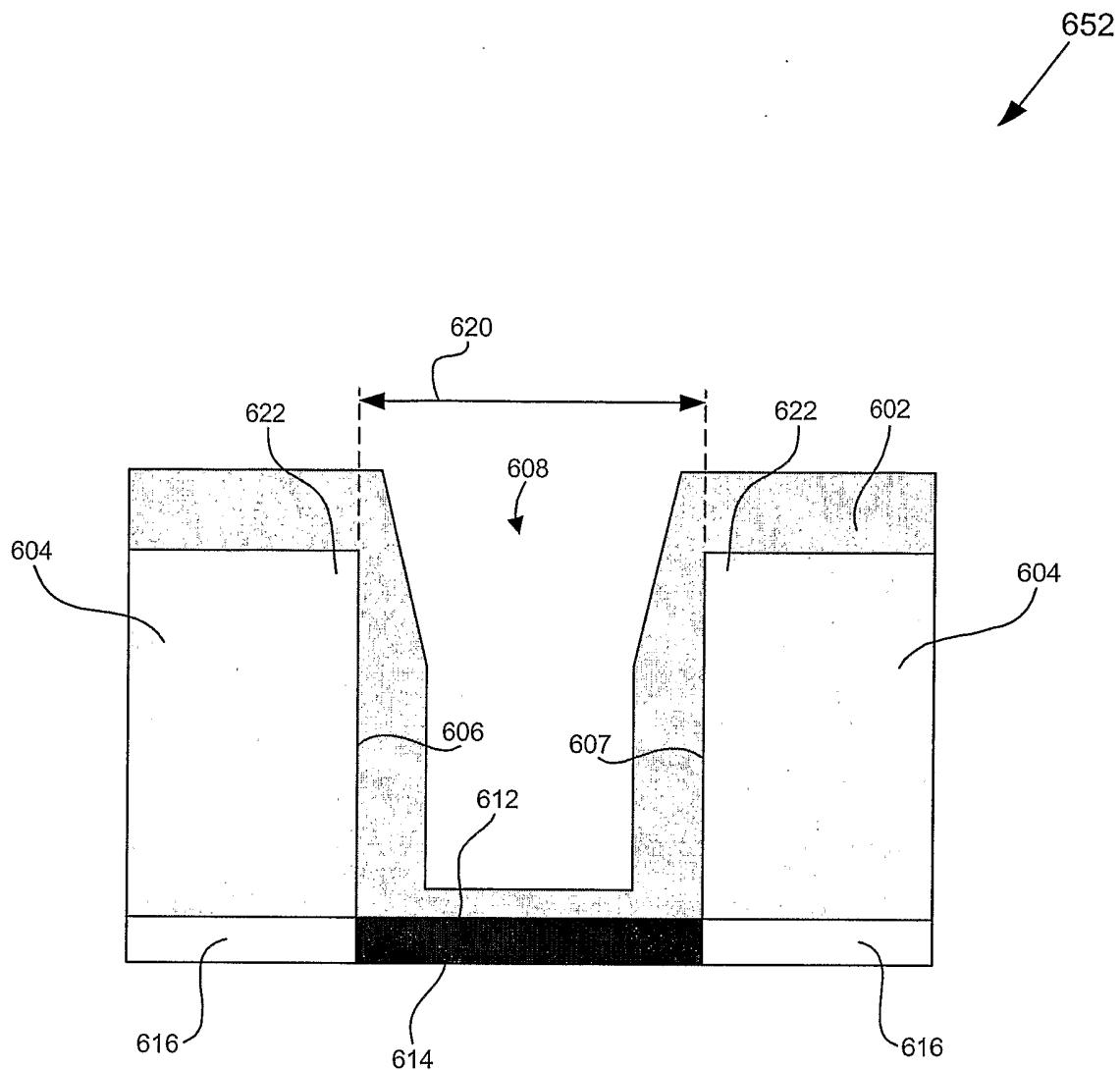

10 Figure 6B illustrates a cross-sectional view of a portion of a wafer processed according to an embodiment of the invention, corresponding to certain steps of the flowchart in Figure 5.

#### DETAILED DESCRIPTION OF THE INVENTION

The present invention is directed to method for preventing increased contact hole width during contact formation in a semiconductor die. The following description contains specific information pertaining to the implementation of the present invention. One skilled in the art will recognize that the present invention 15 may be implemented in a manner different from that specifically discussed in the present application.

Moreover, some of the specific details of the invention are not discussed in order not to obscure the invention.

The drawings in the present application and their accompanying detailed description are directed to merely exemplary embodiments of the invention. To maintain brevity, other embodiments of the present invention are not specifically described in the present application and are not specifically illustrated by the 20 present drawings.

Figure 1 shows a flowchart illustrating an exemplary method for forming a contact over a transistor region in a semiconductor die according to one embodiment of the present invention. Certain details and features have been left out of flowchart 100 that are apparent to a person of ordinary skill in the art. For example, a step may consist of one or more substeps or may involve specialized equipment or materials, as 25 known in the art. Steps 150 and 152 indicated in flowchart 100 are sufficient to describe one embodiment of the present invention, other embodiments of the invention may utilize steps different from those shown in flowchart 100. It is noted that the processing steps shown in flowchart 100 are performed on a wafer, which, prior to step 150, includes a contact hole formed in a dielectric layer and a native oxide layer situated over a silicide layer at the bottom of the contact hole, where the dielectric layer and silicide layer can be situated over

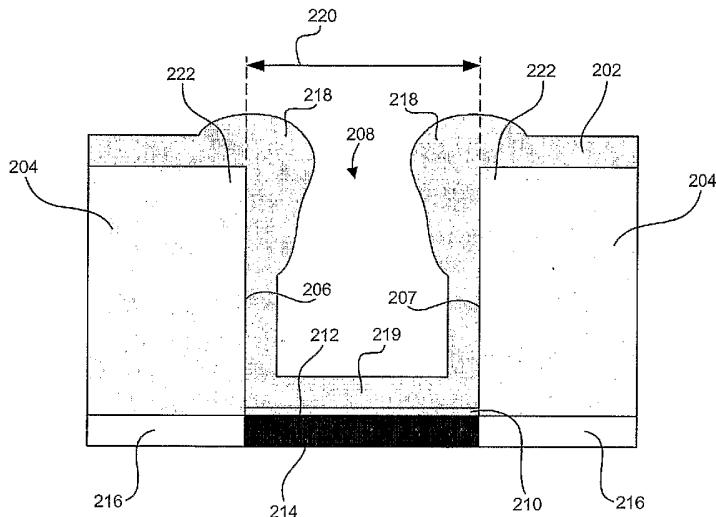

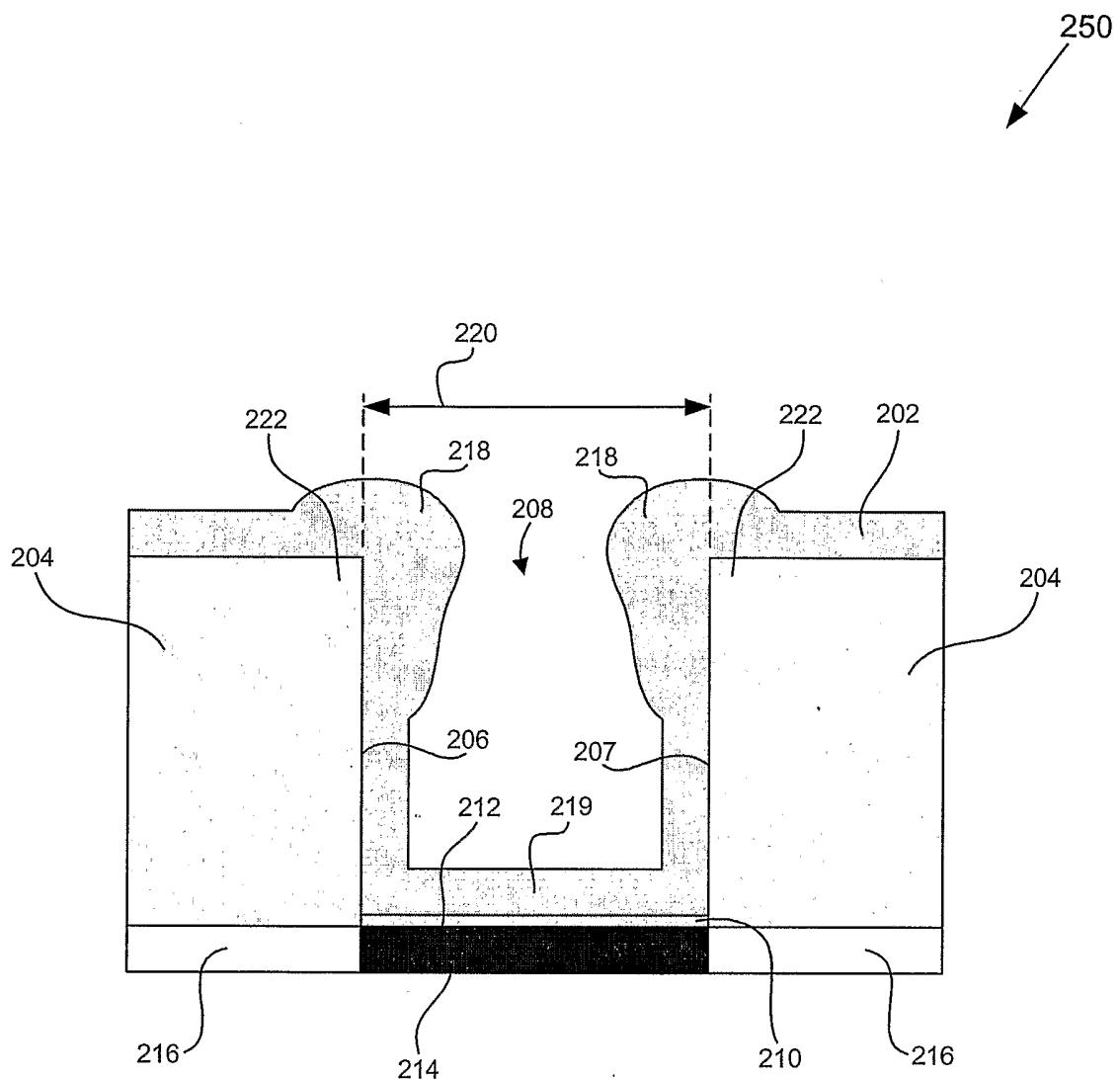

a transistor region of a substrate (not shown in any of the figures). Structures 250 and 252 in Figures 2A and 2B illustrate the result of performing, on a structure including a contact hole formed in a dielectric layer situated over a transistor region of a substrate (not shown in any of the figures) discussed above, steps 150 and 152 of flowchart 100, respectively.

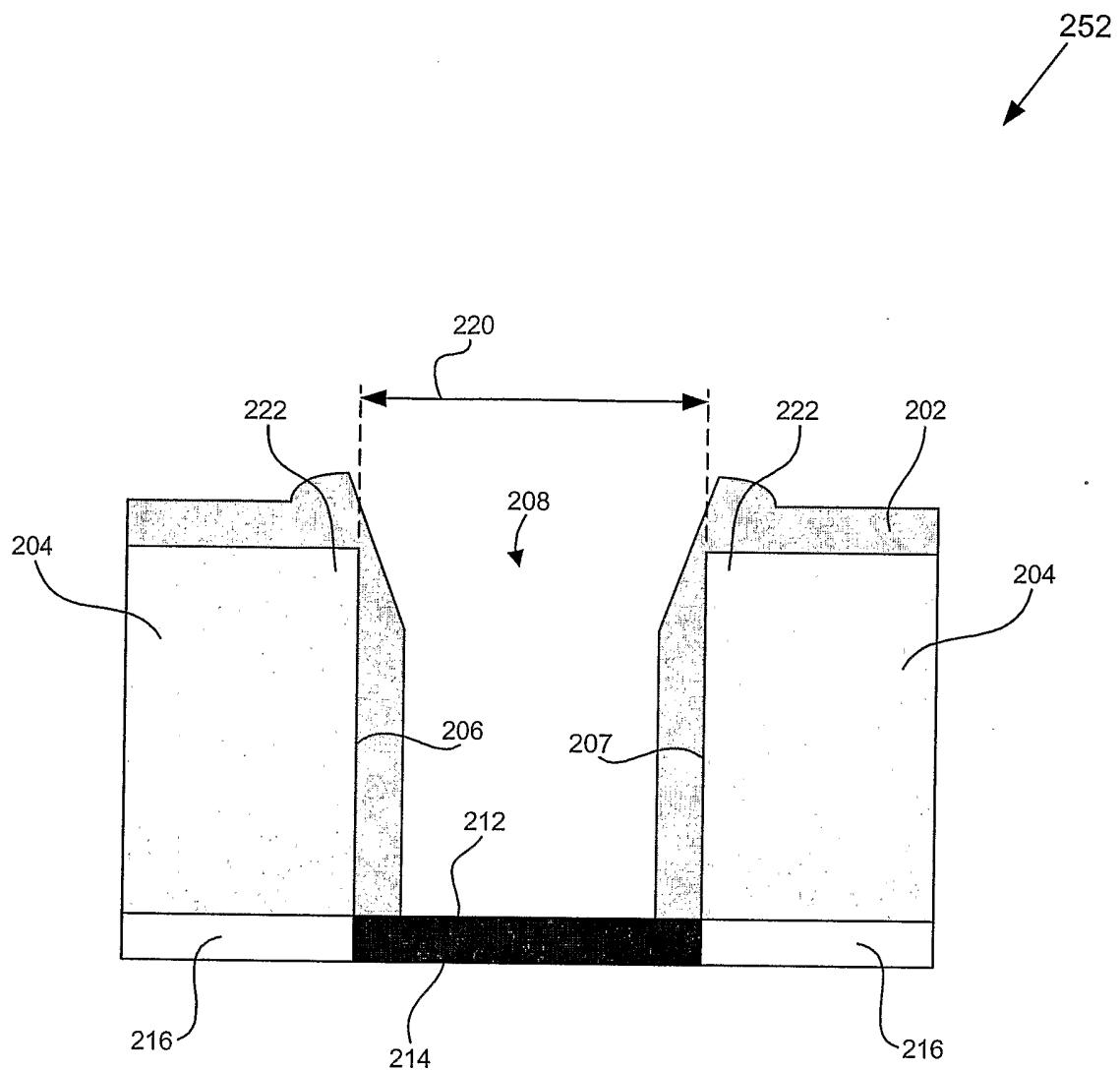

5 Referring now to step 150 in Figure 1 and structure 250 in Figure 2A, at step 150 of flowchart 100, barrier layer 202 is deposited over dielectric layer 204, on sidewalls 206 and 207 of contact hole 208, and over native oxide layer 210 situated at bottom 212 of contact hole 208 and also situated over silicide layer 214. As shown in Figure 2A, dielectric layer 204 is situated over dielectric layer 216, which is situated over a transistor region of a substrate (not shown in Figure 2A). Dielectric layer 204 can comprise silicon dioxide, which can be deposited, for example, in a plasma enhanced chemical vapor deposition (“PECVD”) process. Silicon dioxide deposited in a PECVD process is also referred to as “PECVD oxide” in the present application. Native oxide layer 210 is situated over silicide layer 214 at bottom 212 of contact hole 208 and can comprise thermally grown oxide. By way of example, native oxide layer 210 can have a thickness of between 10.0 Angstroms and 50.0 Angstroms. Barrier layer 202 can be deposited on sidewalls 206 and 207 of contact hole 208, over native oxide layer 210, and over dielectric layer 204 in a manner known in the art and can comprise titanium/titanium nitride (“Ti/TiN”). In other embodiments, barrier layer 202 may comprise a different combination of metals or an appropriate single metal. In the present embodiment, the deposition of barrier layer 202 can be optimized such that portions 218 of barrier layer 202 situated adjacent to top corner regions 222 at the top of contact hole 208 have a greater thickness than portion 219 of barrier layer 202 situated at bottom 212 of contact hole 208. As a result, portions 218 of barrier layer 202 provide sufficient protection for top corner regions 222 of dielectric layer 604 during a subsequent sputter etch process. Contact hole width 220, which is the distance between sidewall 206 and 207 of contact hole 208, is also referred to as “electrical contact width” in the present application. Referring to Figure 2A, the result of step 150 of flowchart 100 is illustrated by structure 250.

Continuing with step 152 in Figure 1 and

20 structure 252 in Figure 2B, at step 152 of flowchart 100, portion 219 of barrier layer 202 and native oxide layer 210 situated at bottom 212 of contact hole 208 are removed to expose silicide layer 214. Portion 219 of barrier layer 202 situated at bottom 212 of contact hole 208 and native oxide layer 210 can be removed by utilizing a sputter etch process, which can comprise argon (“Ar”). The sputter etch process also removes portions of barrier layer 202 situated at the top of sidewalls 206 and 207. However, since portions 218 of

barrier layer 202 (shown in Figure 2A) have sufficient thickness to protect top corner regions 222 of dielectric layer 204, top corner regions 222 are not etched during the sputter etch process. As a result, contact hole width 220 is not increased during the sputter etch process. Contact hole 208 can be filled with a metal such as tungsten in a subsequent step to complete contact formation. Referring to Figure 2B, the result of step 152 of flowchart 100 is illustrated by structure 252.

Thus, in the embodiment of the present invention in Figure 1, by forming barrier layer 202 prior to performing a sputter etch process to remove native oxide layer 210 and optimizing the formation of barrier layer 202, the present invention avoids etching top corner regions 222 of dielectric layer 204. As a result, the present invention advantageously achieves a contact having a contact hole width that is not increased during the contact formation process.

Figure 3 shows a flowchart illustrating an exemplary method for forming a contact over a transistor region of a wafer according to one embodiment of the present invention. Certain details and features have been left out of flowchart 300 that are apparent to a person of ordinary skill in the art. For example, a step may consist of one or more substeps or may involve specialized equipment or materials, as known in the art.

Steps 350 and 352 indicated in flowchart 300 are sufficient to describe one embodiment of the present invention, other embodiments of the invention may utilize steps different from those shown in flowchart 300. It is noted that the processing steps shown in flowchart 300 are performed on a wafer, which, prior to step 350, includes a contact hole formed in a dielectric layer and a native oxide layer situated over a silicide layer at the bottom of the contact hole, where the dielectric layer and silicide layer can be situated over a transistor region of a substrate (not shown in any of the figures). Structures 350 and 352 in Figures 4A and 4B illustrate the result of performing, on a structure including a contact hole formed in a dielectric layer situated over a transistor region of a substrate (not shown in any of the figures) discussed above, steps 350 and 352 of flowchart 300, respectively.

Referring now to step 350 in Figure 3 and structure 450 in Figure 4A, at step 350 of flowchart 300, native oxide layer 410 situated over silicide layer 414 is removed at bottom 412 of contact hole 408 by utilizing reactive hydrogen pre-clean 430. It is noted that although native oxide layer 410 is removed at step 350, native oxide layer 410 is shown in Figure 4A to better illustrate the present embodiment of the invention. In Figure 4A, dielectric layers 404 and 416, sidewalls 406 and 407, contact hole 408, native oxide layer 410, and silicide layer 414 in structure 450 correspond, respectively, to dielectric layers 204 and 216, sidewalls 206

and 207, contact hole 208, native oxide layer 210, and silicide layer 214 in structure 250 in Figure 2A. In the present embodiment, dielectric layer 404 comprises PECVD oxide, which can be hardened in an annealing process after it (i.e. PECVD oxide) has been deposited. Thus, dielectric layer 404 is much harder than native oxide layer 410, which comprises silicon oxide that is thermally grown at room temperature. As a result, 5 when native oxide layer 410 is etched away (i.e. removed) by the reactive hydrogen pre-clean, i.e. reactive hydrogen pre-clean 430, top corner regions 422 of dielectric layer 404, which are situated at the tops of sidewalls 406, are not etched. Thus, contact hole width 420, which is the distance between sidewalls 406 and 407 of contact hole 408, is not increased after performance of reactive hydrogen pre-clean 430. Contact hole width 420 is similar to contact hole width 220 in Figure 2A and is also referred to as "electrical contact width" 10 in the present application. Referring to Figure 4A, the result of step 350 of flowchart 300 is illustrated by structure 450.

Continuing with step 352 in Figure 3 and structure 452 in Figure 4B, at step 352 of flowchart 300, barrier layer 432 is deposited on sidewalls 406 and 407 of contact hole 408, over silicide layer 414 situated at bottom 412 of contact hole 408, and over dielectric layer 404. Barrier layer 432 can be deposited in a manner 15 known in the art and can comprise Ti/TiN. In other embodiments, barrier layer 432 may comprise a different combination of metals or an appropriate single metal. Contact hole 408 can be filled with a metal such as tungsten in a subsequent step to complete contact formation. Referring to Figure 4B, the result of step 352 of flowchart 300 is illustrated by structure 452.

Thus, in the embodiment of the present invention in Figure 3, by utilizing a reactive hydrogen pre- 20 clean process to remove a native oxide layer at the bottom of a contact hole prior to depositing a barrier layer in the contact hole, the present invention advantageously provides a contact having a contact hole width that does not increase during contact formation.

Figure 5 shows a flowchart illustrating an exemplary method for forming a contact over a transistor region of a wafer according to an embodiment of the present invention. Certain details and features have been 25 left out of flowchart 500 that are apparent to a person of ordinary skill in the art. For example, a step may consist of one or more substeps or may involve specialized equipment or materials, as known in the art. Steps 550 and 552 indicated in flowchart 500 are sufficient to describe one embodiment of the present invention, other embodiments of the invention may utilize steps different from those shown in flowchart 500. It is noted that the processing steps shown in flowchart 500 are performed on a wafer, which, prior to step 550, includes

a contact hole formed in a dielectric layer and a native oxide layer situated over a silicide layer at the bottom of the contact hole, where the dielectric layer and silicide layer can be situated over a transistor region of a substrate (not shown in any of the figures). Structures 550 and 552 in Figures 6A and 6B illustrate the result of performing, on a structure including a contact hole formed in a dielectric layer situated over a transistor region of a substrate (not shown in any of the figures) discussed above, steps 550 and 552 of flowchart 500, respectively.

Referring now to step 550 in Figure 5 and structure 450 in Figure 4A, at step 550 of flowchart 500, barrier layer 602 is deposited on sidewalls 606 and 607 of contact hole 608, over native oxide layer 610 situated at bottom 612 of contact hole 608, and over dielectric layer 604, which is situated over dielectric layer 616. Step 550 in Figure 5 corresponds to step 350 in Figure 3. In particular, barrier layer 602, dielectric layers 604 and 616, sidewalls 606 and 607, contact hole 608, native oxide layer 610, bottom 612, silicide layer 614, portions 618, portion 619, contact hole width 620, and top corner regions 622 in structure 650 in Figure 6A correspond, respectively, to barrier layer 202, dielectric layers 204 and 216, sidewalls 206 and 207, contact hole 208, native oxide layer 210, bottom 212, silicide layer 214, portions 218, portion 219, contact hole width 220, and top corner regions 222 in structure 250 in Figure 2A. Thus, similar to contact hole width 220 in Figure 2A, contact hole width 420 is also referred to as "electrical contact width" in the present application. Similar to barrier layer 202 in Figure 2A, the deposition of barrier layer 602 can be optimized in the present embodiment such that portions 618 of barrier layer 602 situated adjacent to top corner portions 222 at the top of contact hole 608 have a greater thickness than portion 619 of barrier layer 602 situated at bottom 612 of contact hole 608. Referring to Figure 6A, the result of step 550 of flowchart 500 is illustrated by structure 650.

Continuing with step 552 in Figure 5 and structure 652 in Figure 6B, at step 552 of flowchart 500, a simultaneous sputter etch/deposition process is performed to remove native oxide layer 610 situated over silicide layer 614 at bottom 612 of contact hole 608. In the simultaneous sputter etch/deposition process, Ar can be utilized for sputter etching and Ti/TiN can be deposited on sidewalls 606 and bottom 612 of contact hole 608, utilizing, for example, a sputter deposition technique. The simultaneous sputter etch/deposition process can utilize an appropriate sputter etch/deposition ratio such that native oxide layer 610 is etched (i.e. removed). By way of example, the ratio of Ar and Ti/TiN molecules can be selected to achieve a sputter etch/deposition ratio of between 1.0 and 2.0. Thus, by utilizing a sputter etch/deposition ratio greater than 1.0,

the present embodiment achieves removal of native oxide layer 610 while protecting top corner regions 622 of dielectric layer 604 by depositing Ti/TiN back onto sidewalls 606 and 607 of contact hole 608. Contact hole 608 can be filled with a metal such as tungsten in a subsequent step to complete contact formation. Referring to Figure 6B, the result of step 552 of flowchart 500 is illustrated by structure 652.

5 Thus, in the embodiment of the present invention in Figure 5, by utilizing a simultaneous sputter etch/deposition process, the present invention achieves removal of a native oxide layer at the bottom of a contact hole situated over a silicide layer while preventing an undesirable increase in contact hole width during contact formation.

10 Thus, as discussed above, in embodiments of the invention in Figures 1, 3, and 5, by appropriately selecting the sequence and techniques for sputter etch and barrier layer deposition processes, the present invention achieves removal of a native oxide layer at the bottom of a contact hole while preventing an undesirable increase in contact hole width during contact formation. In contrast, a conventional contact formation process, which utilizes an Ar sputter etch to remove a native oxide layer prior to barrier layer deposition, results in an undesirable increase in contact hole width.

15 From the above description of exemplary embodiments of the invention it is manifest that various techniques can be used for implementing the concepts of the present invention without departing from its scope. Moreover, while the invention has been described with specific reference to certain embodiments, a person of ordinary skill in the art would recognize that changes could be made in form and detail without departing from the spirit and the scope of the invention. The described exemplary embodiments are to be 20 considered in all respects as illustrative and not restrictive. It should also be understood that the invention is not limited to the particular exemplary embodiments described herein, but is capable of many rearrangements, modifications, and substitutions without departing from the scope of the invention.

Thus, method for preventing an increase in contact hole width during contact formation has been described.

25

CLAIMS

1. A method for forming a contact over a silicide layer (214) situated in a semiconductor die, said method comprising steps of:

5 depositing (150) a barrier layer (202) on sidewalls (206,207) of a contact hole (208) and on a native oxide layer (210) situated at a bottom of said contact hole (208), said sidewalls (206,207) being defined by said contact hole (208) in a dielectric layer (204);

removing (152) a portion (219) of said barrier layer (202) and said native oxide layer (210) situated at said bottom of said contact hole (208) to expose said silicide layer (214).

10 2. The method of claim 1 wherein said step of removing (152) said portion (219) of said barrier layer (202) and said native oxide layer (210) situated at said bottom of said contact hole (208) comprises utilizing a sputter etch process.

15 3. The method of claim 1 wherein said dielectric layer (204) comprises top corner regions (222) situated adjacent to said contact hole (208), wherein said top corner regions (222) of said dielectric layer (204) are not etched during said step of removing (152) said portion (219) of said barrier layer (202) and said native oxide layer (210) situated at said bottom of said contact hole (208).

20 4. The method of claim 2 wherein said contact hole (208) has an electrical contact width (220), wherein said electrical contact width (220) is not increased by said sputter etch process.

5. A method for forming a contact over a silicide layer (414) situated in a semiconductor die, said method comprising steps of:

25 removing (350) a native oxide layer (410) situated over said silicide layer (414) at a bottom of a contact hole (408) by utilizing a reactive hydrogen pre-clean process (430), said sidewalls (406,407) being defined by said contact hole (408) in a dielectric layer (404), said dielectric layer (404) having top corner regions (422) situated adjacent to said contact hole (408);

depositing (352) a barrier layer (432) on said sidewalls (406,407) of said contact hole (408) and over said silicide layer (414).

6. The method of claim 5 wherein said reactive hydrogen pre-clean process (430) does not etch said top corners (422) of said dielectric layer (404).

5 7. The method of claim 5 wherein said contact hole (408) has an electrical contact width (420), wherein said electrical contact width (420) is not increased by said reactive hydrogen pre-clean process (430).

8. A method for forming a contact over a silicide layer (614) situated in a semiconductor die, said method comprising steps of:

10 depositing (550) a barrier layer (602) on sidewalls (606,607) of a contact hole (608) and on a native oxide layer (610) situated at a bottom of said contact hole (608), said sidewalls (606,607) being defined by said contact hole (608) in a dielectric layer (604), said native oxide layer (610) being situated over said silicide layer (614);

15 removing (552) said native oxide layer (610) situated over said silicide layer (614) at said bottom of said contact hole (608) by utilizing a sputter etch/deposition process.

9. The method of claim 8 wherein said step of removing (552) said native oxide layer (610) situated over said silicide layer (614) at said bottom of said contact hole (608) comprises simultaneously sputter etching said barrier layer (602) and said native oxide layer (610) and depositing titanium/titanium nitride on said barrier layer (602).

20 10. The method of claim 8 wherein said contact hole (608) has an electrical contact width (620), wherein said electrical contact width (620) is not increased by said sputter etch/deposition process.

**Fig. 1**

**Fig. 2A**

**Fig. 2B**

**Fig. 3**

**Fig. 4A**

**Fig. 4B**

**Fig. 5**

**Fig. 6A**

**Fig. 6B**

# INTERNATIONAL SEARCH REPORT

In  National Application No

PCT/US2004/033417

## A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 H01L21/768

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, PAJ

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                                      | Relevant to claim No. |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | US 6 498 091 B1 (CHEN LING ET AL)<br>24 December 2002 (2002-12-24)<br>the whole document<br>-----                                                                       | 1-4,8-10              |

| X        | US 6 204 550 B1 (WANG ZHIHAI ET AL)<br>20 March 2001 (2001-03-20)<br>the whole document<br>-----                                                                        | 1-4                   |

| X        | PATENT ABSTRACTS OF JAPAN<br>vol. 018, no. 290 (E-1557),<br>2 June 1994 (1994-06-02)<br>& JP 06 061181 A (SONY CORP),<br>4 March 1994 (1994-03-04)<br>abstract<br>----- | 5-7                   |

| A        | EP 1 233 448 A (TEXAS INSTRUMENTS INC)<br>21 August 2002 (2002-08-21)<br>the whole document<br>-----<br>-/-                                                             | 1-4,8-10              |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the international search

23 February 2005

Date of mailing of the international search report

02/03/2005

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Ploner, G

**INTERNATIONAL SEARCH REPORT**Int'l Application No

PCT/US2004/033417**C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category | Citation of document, with indication, where appropriate, of the relevant passages                  | Relevant to claim No. |

|----------|-----------------------------------------------------------------------------------------------------|-----------------------|

| A        | US 2003/073304 A1 (MAK ALFRED ET AL)<br>17 April 2003 (2003-04-17)<br>the whole document<br>-----   | 5-7                   |

| A        | US 6 511 575 B1 (SHINDO HARUO ET AL)<br>28 January 2003 (2003-01-28)<br>the whole document<br>----- | 5-7                   |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/US2004/033417

| Patent document cited in search report |    | Publication date |                | Patent family member(s)                      |  | Publication date                       |

|----------------------------------------|----|------------------|----------------|----------------------------------------------|--|----------------------------------------|

| US 6498091                             | B1 | 24-12-2002       | TW<br>WO<br>US | 521379 B<br>0239500 A2<br>2003087520 A1      |  | 21-02-2003<br>16-05-2002<br>08-05-2003 |

| US 6204550                             | B1 | 20-03-2001       | US             | 5994211 A                                    |  | 30-11-1999                             |

| JP 06061181                            | A  | 04-03-1994       | NONE           |                                              |  |                                        |

| EP 1233448                             | A  | 21-08-2002       | US<br>EP<br>JP | 2002110999 A1<br>1233448 A2<br>2002289690 A  |  | 15-08-2002<br>21-08-2002<br>04-10-2002 |

| US 2003073304                          | A1 | 17-04-2003       | TW<br>WO       | 559992 B<br>03034481 A1                      |  | 01-11-2003<br>24-04-2003               |

| US 6511575                             | B1 | 28-01-2003       | JP<br>JP<br>JP | 2000150479 A<br>2000311868 A<br>2000311940 A |  | 30-05-2000<br>07-11-2000<br>07-11-2000 |