(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6903398号

(P6903398)

(45) 発行日 令和3年7月14日(2021.7.14)

(24) 登録日 令和3年6月25日(2021.6.25)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G01R 31/00 (2006.01)

G09G 3/20 (2006.01)G09G 3/36

G01R 31/00

G09G 3/20

G09G 3/20

G09G 3/206 1 1 A

6 1 1 F

6 2 3 B

請求項の数 6 (全 14 頁) 最終頁に続く

(21) 出願番号

特願2016-13309 (P2016-13309)

(22) 出願日

平成28年1月27日(2016.1.27)

(65) 公開番号

特開2017-134203 (P2017-134203A)

(43) 公開日

平成29年8月3日(2017.8.3)

審査請求日

平成31年1月10日(2019.1.10)

審判番号

不服2020-8308 (P2020-8308/J1)

審判請求日

令和2年6月16日(2020.6.16)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 田代 智裕

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

合議体

審判長 岡田 吉美

審判官 濱本 穎広

審判官 岸 智史

最終頁に続く

(54) 【発明の名称】 駆動装置および液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

液晶パネルに備えられ、前記液晶パネルの画素領域を駆動する駆動装置であって、外部から入力されたアナログ電源であって、分離された第1のアナログ電源の電位と第2のアナログ電源の電位とを比較して電位差を検出する比較回路と、前記比較回路で検出された前記電位差が予め定められた閾値以上である場合に異常状態であると判定する判定回路と、を備え、

出力アンプと、

P MOSトランジスタおよびN MOSトランジスタと、前記P MOSトランジスタおよび前記N MOSトランジスタが同時にONして大電流が出力されないように設けられた第1の回路および第2の回路とを有し、前記出力アンプから前記画素領域への出力を補助する補助回路と、

一端が前記判定回路に接続され、他端が前記第1の回路を介して前記P MOSトランジスタのゲートに接続され、前記P MOSトランジスタ自体の動作を制御する第1の制御スイッチと、

一端が前記判定回路に接続され、他端が前記第2の回路を介して前記N MOSトランジスタのゲートに接続され、前記N MOSトランジスタ自体の動作を制御する第2の制御スイッチと、

をさらに備え、

10

20

前記判定回路が前記異常状態であると判定した場合において、

前記第1の制御スイッチおよび前記第2の制御スイッチの各々は、前記PMOSトランジスタおよび前記NMOSトランジスタが同時にONしないように制御し、

前記第1のアナログ電源は、前記比較回路、前記補助回路、および前記出力アンプに供給され、

前記第2のアナログ電源は、前記比較回路に供給され、

前記異常状態は、前記PMOSトランジスタおよび前記NMOSトランジスタが同時にONして貫通電流が発生する状態であることを特徴とする、駆動装置。

**【請求項2】**

前記出力アンプから前記画素領域に出力される電流量を制御する電流制御回路をさらに備え、

10

前記電流制御回路は、前記判定回路が前記異常状態であると判定した場合において、前記出力アンプから出力される前記電流量が少なくなるように制御することを特徴とする、請求項1に記載の駆動装置。

**【請求項3】**

前記判定回路は、前記異常状態であると判定した場合において、前記異常状態であることを示す信号を外部に出力することを特徴とする、請求項1または2に記載の駆動装置。

**【請求項4】**

請求項1から3のいずれか1項に記載の駆動装置を備える、液晶表示装置。

**【請求項5】**

20

前記第1のアナログ電源および前記第2のアナログ電源は、FPC(Flexible Printed Circuit)を介して前記駆動装置に供給され、

前記液晶パネルは、前記第1のアナログ電源について前記FPCと接続可能な第1の接続端子と、前記第2のアナログ電源について前記FPCと接続可能な第2の接続端子とを備え、

前記第2の接続端子は、前記FPCの端側部に対応する位置に配置されることを特徴とする、請求項4に記載の液晶表示装置。

**【請求項6】**

前記第2のアナログ電源は、安定化回路を介して前記駆動装置に供給されることを特徴とする、請求項5に記載の液晶表示装置。

30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、液晶パネルの画素領域を駆動する駆動装置、および当該駆動装置を備える液晶表示装置に関する。

**【背景技術】**

**【0002】**

近年、異なるサイズの液晶表示装置で同一部品を使用することによって、同一部品の購入数量を増やしてコスト(部品の単価)を下げる、または開発期間の短縮化および設計リソースの削減のために「プラットフォーム」化するというようなことが行われており、多種多様な液晶パネルに同一部品が共通して使用されるようになってきた。

40

**【0003】**

また、一般的に、液晶表示装置の高解像度化およびサイズの拡大化に伴って、液晶パネルを駆動するドライバーIC(Integrated Circuit)の出力段に接続される負荷は重くなる傾向にあり、ドライバーICは高負荷であっても駆動可能な回路を有している。一例として、高負荷を駆動可能なドライバーICでは、出力アンプの駆動能力だけでは十分な出力(電流)が得られない場合のために、出力アンプの出力をアシスト(補助)するアシスト回路(補助回路)を備えているものがある。

**【0004】**

ところで、液晶表示のアプリケーションによっては低消費電力の要求があり、液晶パネ

50

ルの負荷をできるだけ軽くするような多くの試みがなされており、ソースラインの容量または抵抗を低減した液晶パネル構造がある（例えば、特許文献1, 2参照）。プラットフォーム化と、多種多様な液晶パネルの負荷を駆動することと踏まえて、結果的に高負荷の液晶パネルを駆動することが可能なドライバーICを使用して低負荷の液晶パネルを駆動するケースが出てきている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平5-41651号公報

【特許文献2】特開2001-255857号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来のアシスト回路は、元々想定した高負荷時の動作については問題ないが、低負荷時には条件次第では貫通電流が発生してしまうという問題がある。また、貫通電流は、増加しても表示に影響を及ぼさないため、貫通電流が発生したか否かを製品の状態で簡単にモニタすることができず、液晶パネルが異常状態であるか否かを簡単に知ることができなかつた。

【0007】

本発明は、このような問題を解決するためになされたものであり、アシスト回路に貫通電流を発生させないようにすることが可能な駆動装置および当該駆動装置を備える液晶表示装置を提供することを目的とする。

20

【課題を解決するための手段】

【0008】

上記の課題を解決するために、本発明による駆動装置は、液晶パネルに備えられ、液晶パネルの画素領域を駆動する駆動装置であって、外部から入力されたアナログ電源であって、分離された第1のアナログ電源の電位と第2のアナログ電源の電位とを比較して電位差を検出する比較回路と、比較回路で検出された電位差が予め定められた閾値以上である場合に異常状態であると判定する判定回路とを備え、出力アンプと、PMOSトランジスタおよびNMOSトランジスタと、PMOSトランジスタおよびNMOSトランジスタが同時にONして大電流が出力されないように設けられた第1の回路および第2の回路とを有し、出力アンプから画素領域への出力を補助する補助回路と、一端が判定回路に接続され、他端が第1の回路を介してPMOSトランジスタのゲートに接続され、PMOSトランジスタ自身の動作を制御する第1の制御スイッチと、一端が判定回路に接続され、他端が第2の回路を介してNMOSトランジスタのゲートに接続され、NMOSトランジスタ自身の動作を制御する第2の制御スイッチとをさらに備え、判定回路が異常状態であると判定した場合において、第1の制御スイッチおよび第2の制御スイッチの各々は、PMOSトランジスタおよびNMOSトランジスタが同時にONしないように制御し、第1のアナログ電源は、比較回路、補助回路、および出力アンプに供給され、第2のアナログ電源は、比較回路に供給され、異常状態は、PMOSトランジスタおよびNMOSトランジスタが同時にONして貫通電流が発生する状態である。

30

【発明の効果】

【0009】

本発明によると、駆動装置は、液晶パネルに備えられ、液晶パネルの画素領域を駆動する駆動装置であって、外部から入力されたアナログ電源であって、分離された第1のアナログ電源の電位と第2のアナログ電源の電位とを比較して電位差を検出する比較回路と、比較回路で検出された電位差が予め定められた閾値以上である場合に異常状態であると判定する判定回路とを備え、出力アンプと、PMOSトランジスタおよびNMOSトランジスタと、PMOSトランジスタおよびNMOSトランジスタが同時にONして大電流が出力されないように設けられた第1の回路および第2の回路とを有し、出力アンプから画素

40

50

領域への出力を補助する補助回路と、一端が判定回路に接続され、他端が第1の回路を介して PMOSトランジスタのゲートに接続され、PMOSトランジスタ自体の動作を制御する第1の制御スイッチと、一端が判定回路に接続され、他端が第2の回路を介して NMOSトランジスタのゲートに接続され、NMOSトランジスタ自体の動作を制御する第2の制御スイッチとをさらに備え、判定回路が異常状態であると判定した場合において、第1の制御スイッチおよび第2の制御スイッチの各々は、PMOSトランジスタおよびNMOSトランジスタが同時にONしないように制御し、第1のアナログ電源は、比較回路、補助回路、および出力アンプに供給され、第2のアナログ電源は、比較回路に供給され、異常状態は、PMOSトランジスタおよびNMOSトランジスタが同時にONして貫通電流が発生する状態であるため、アシスト回路に貫通電流を発生させないようにすることが可能となる。

10

【図面の簡単な説明】

【0010】

【図1】本発明の実施の形態1によるソースドライバーICの構成の一例を示す図である。

【図2】一般的なVDDAの接続の一例を示す図である。

【図3】本発明の実施の形態1によるVDDAの接続の一例を示す図である。

【図4】本発明の実施の形態1による比較回路の一例を示す図である。

【図5】本発明の実施の形態1によるソースドライバーICの構成の他の一例を示す図である。

20

【図6】本発明の実施の形態1による液晶表示装置の構成の他の一例を示すブロック図である。

【図7】本発明の実施の形態1による液晶表示装置の構成の他の一例を示すブロック図である。

【図8】本発明の実施の形態2によるVDDAの接続の一例を示す図である。

【図9】本発明の実施の形態3によるVDDAの接続の一例を示す図である。

【図10】水平解像度とソースドライバーICの出力数および使用個数との関係の一例を示す図である。

【図11】一般的な液晶表示装置の構成の一例を示す図である。

【図12】一般的な液晶表示装置の構成の他の一例を示す図である。

30

【図13】一般的な液晶表示装置の構成の一例を示すブロック図である。

【図14】ドライバーICの構成の一例を示す図である。

【図15】電流制御回路の構成の一例を示す図である。

【図16】出力アンプのVDDA波形の一例を示す図である。

【図17】高負荷時および低負荷時のソースドライバーICの書き込みタイミングにおける、出力アンプ電位およびアシスト回路のNMOSトランジスタのゲート部電位の変化の一例を示す図である。

【発明を実施するための形態】

【0011】

本発明の実施の形態について、図面に基づいて以下に説明する。

40

【0012】

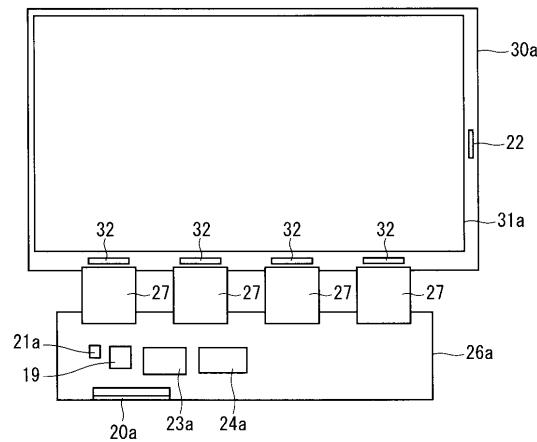

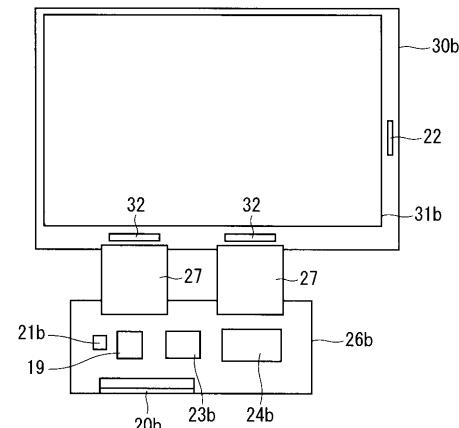

<前提技術>

近年、液晶表示装置のコストを低減するために、ドライバーICの出力チャンネル数を増やすことによってドライバーICの使用個数を減らす動きが活発に行われている(図10参照)。図10の例では、水平解像度とソースドライバーICの出力数および使用個数との関係の一例を示している。TCP(Tape Carrier Package)またはCOF(Chip On Film)は、液晶パネルに貼り付ける側に設ける端子ピッチを容易に小さくできないため、特に中小型の液晶表示装置ではCOG(Chip On Glass)化が盛んになってきている。

【0013】

また、上述の通り、多種多様な液晶パネルに同一部品が共通して使用されるようになつ

50

てきている(図11, 12参照)。なお、図11, 12において、インターフェースコネクタ20a, 20bは、単にインターフェースコネクタ20ともいう。EEPROM21a, 21bは、単にEEPROM21ともいう。電源回路23a, 23bは、単に電源回路23ともいう。階調参照電圧生成回路24a, 24bは、単に階調参照電圧生成回路24ともいう。回路基板26a, 26bは、単に回路基板26ともいう。液晶パネル30a, 30bは単に液晶パネル30ともいう。画素領域31a, 31bは単に画素領域31ともいう。

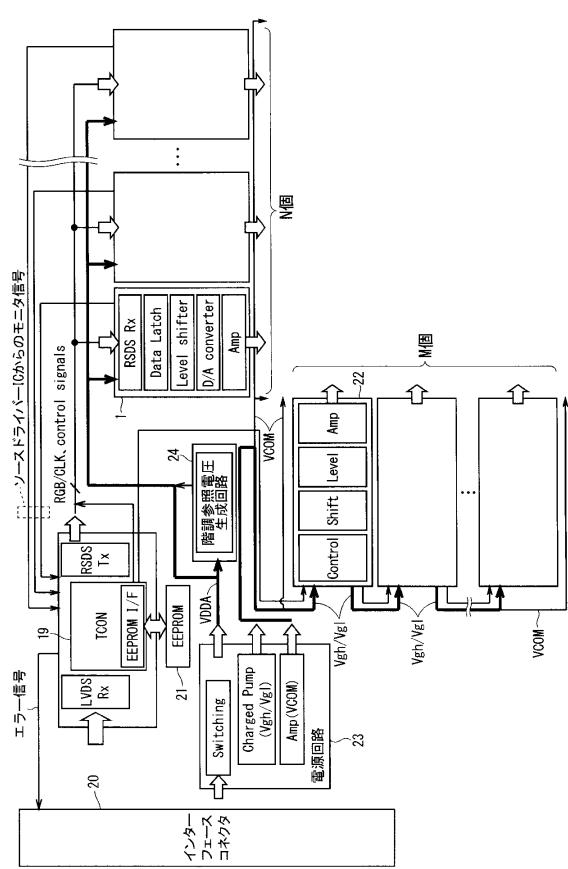

#### 【0014】

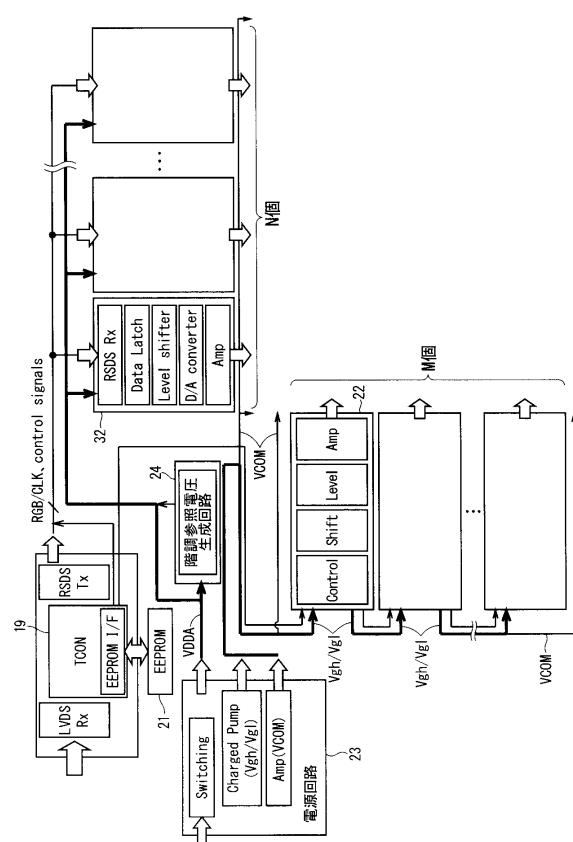

一般的な液晶表示装置では、図13に示すように、タイミングコントローラーであるTCON19、TCON19の設定データを保存しているEEPROM(Electrically Erasable Programmable Read Only Memory、E2PROMともいう)21、ソースドライバー-IC32、ゲートドライバーIC22、電源回路23、および階調参照電圧生成回路24などを備えている。なお、図13において、RSDS Tx/Rxは、mini-LVDS Tx/Rxなど、他のTCON19とソースドライバーIC32との間を接続するインターフェースであってもよい。また、LVDS Rxは、TTLまたはeDPなど、他のシステム側(図示しない外部機器側。当該外部機器から画像データや同期信号等を液晶表示装置に入力する。)とTCON19との間を接続するインターフェースであってもよい。

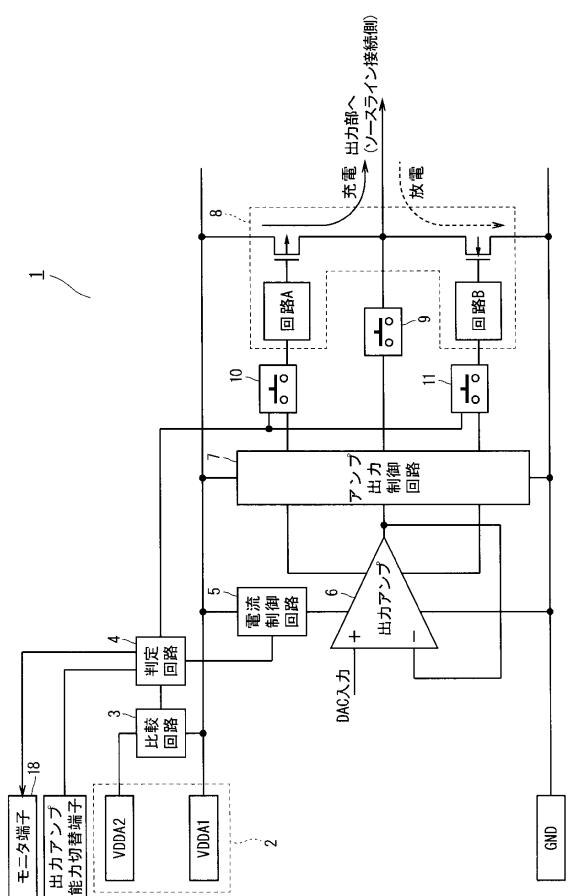

#### 【0015】

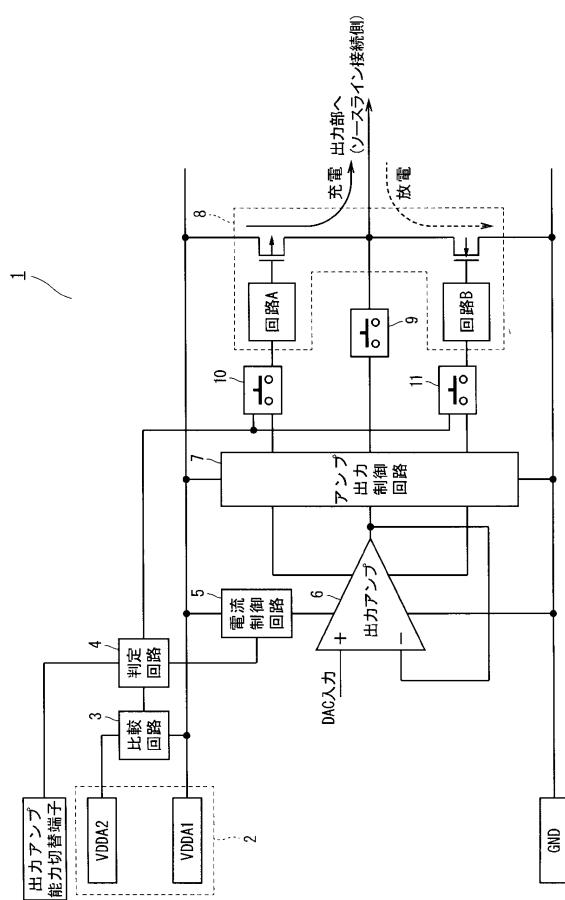

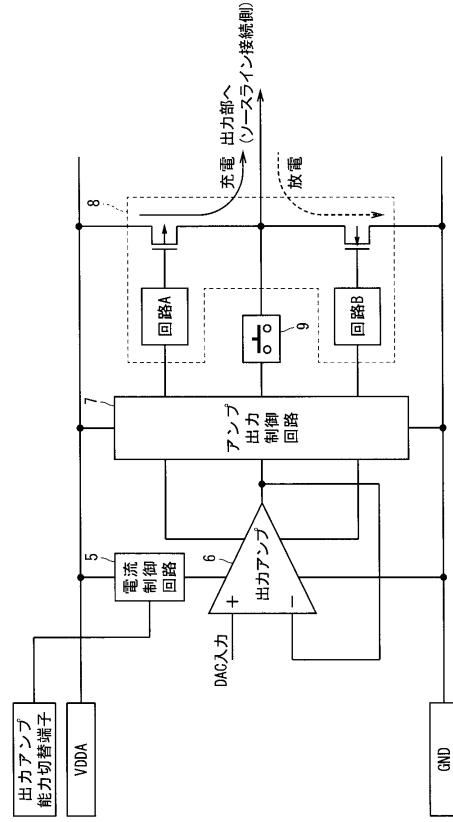

高負荷を駆動可能なドライバーICには、アシスト回路8を備えているものがある(図14参照)。アシスト回路8は、出力アンプ6とは別個の電流源となっており、液晶パネル30の画素領域31への出力を補助する。また、アシスト回路8は、電源側のスイッチであるPMOSトランジスタと、GND側のスイッチであるNMOSトランジスタと、PMOSトランジスタおよびNMOSトランジスタが同時にONして大電流が出力されないような種々の回路(回路A、回路B)を有している。

#### 【0016】

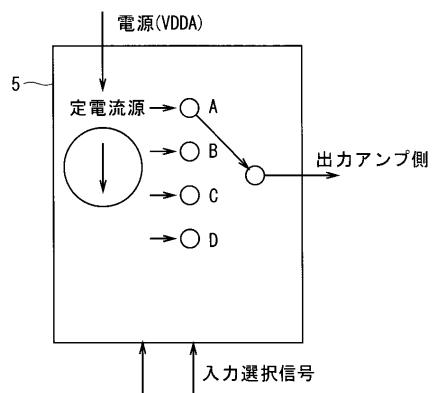

また、高負荷の液晶パネルを駆動することが可能なドライバーICを使用して低負荷の液晶パネルを駆動する場合は、電流制御回路5を用いて、外部から入力された信号(入力選択信号)に基づいて出力アンプ6に入力する電流量を変える方法が一般的に行われている(図15参照)。なお、図15において、出力アンプに入力する電流量は、「A > B > C > D」となっている。電流制御回路5を用いることによって、低負荷の液晶パネルを駆動するときの消費電流が増えないようにしている。

#### 【0017】

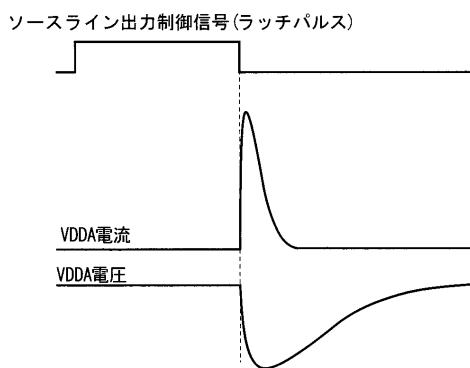

しかし、近年の出力チャンネル数の増加に伴ってドライバーICに内蔵される出力アンプ数も増加傾向にあることと、解像度の増加が要因となって、例えば1水平期間の時間が短くなってきており、液晶駆動のタイミング設定も厳しくなってきている。例えば、図16に示すように、ソースドライバーICは、TCON19からソースドライバーIC32に伝送される制御信号の1つであるラッチパルスの立下り後または少し遅れて、ソースラインに対して一斉に、またはある出力端子ブロック毎に少しづつずらして書き込む動作(一般的には「充電」という)を行う。ある1水平期間にソースラインに書き込んだ電圧から次の1水平期間に書き込むためには電圧値を変えるために一度アンプ側とソースラインを切り離す(Hi-Z状態)必要があり、図14のスイッチ9にて行う。書き込みと同時にVDDA電流(アナログ回路用電流)が一気に増加し、それによってVDDA電圧(アナログ電源用電圧)が一時的に落ち込むが、これらは徐々に回復していく。このような変動は、一般的に負荷変動と呼ばれており、液晶パネルの解像度、サイズ、または構造ごとに変わる。解像度の増加によって1水平期間の時間は短くなるが、ラッチパルスの「H」の期間幅は一定期間設ける必要がある。例えば、ソースドライバーICの全出力をショートし一旦中間電位にしてからソースラインに書き込むチャージシェア機能の場合には、ラッチパルスの「H」幅は1~3μsec程度の時間を確保するのが一般的であり、チャージシェア機能無しの場合においても~1μsec程度は必要である。また、解像度・パネル

10

20

30

40

50

サイズが増えるに従ってソースラインの容量・抵抗成分は一般的に増える傾向であり、負荷変動が回復するまでの時間が不足する状況が起き易くなる。従って、解像度の増加に伴って電源回路23の強化が必要になるが、負荷変動は完全に削減できないためVDDAの電圧レベルとしては変動する機会が増えることになる。

【0018】

アシスト回路8は、元々想定した高負荷時の動作については問題ないが、アンプ出力制御回路7における寄生容量などの作りこみといった条件次第ではNMOStランジスタのゲート部電位が影響を受け、充電するためにON状態のPMOSトランジスタと同時にONして貫通電流が発生してしまう(図17参照)。貫通電流が発生すると、当該貫通電流によって電源およびGNDが揺らされ(電源およびGNDの電位が変動し)、さらに貫通電流が増大するといった悪循環に陥る不具合が生じる。また、アシスト回路8は、ドライバーICに供給される電源ラインのインダクタおよび抵抗成分が多くなってくると、上記の不安定動作がより増幅され、延いてはFPC27(図11, 12参照)からドライバー入力端子(例えば、図14のVDDA端子)までの全体的な抵抗値の変化に弱いものとなる。貫通電流は、増加しても表示に影響を及ぼさないため、貫通電流が発生しているか否かは例えば図3に示すVDDAの出力に対して電流計を設けてモニタするか、電源回路23に入力接続する外付け電源ラインに対して電流計を設けてモニタするしかない。したがって、液晶表示装置の製品状態で簡単にモニタすることができないため、液晶パネルが異常状態であるか否かを簡単に知ることができない。

【0019】

本発明は、このような問題を解決するものであり、以下に詳細に説明する。

【0020】

<実施の形態1>

図1は、本発明の実施の形態1によるソースドライバーIC1の構成の一例を示す図である。なお、ソースドライバーIC1は、図11～13に示すソースドライバー32に代わるものである。

【0021】

図1に示すように、ソースドライバーIC1は、VDDA入力端子2と、比較回路3と、判定回路4と、制御スイッチ10(第1の制御スイッチ)と、制御スイッチ11(第2の制御スイッチ)とを備えることを特徴としている。その他の構成は、図14に示すドライバーICの構成と同様であるため、ここでは詳細な説明を省略する。

【0022】

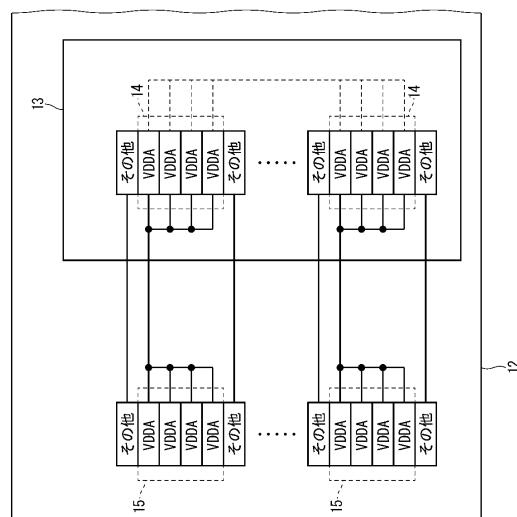

ソースドライバーICには、ロジック用の電源(VDDD)と、アナログ回路用の電源(VDDA)とがある。図2に示すように、一般的なソースドライバーIC13では、同電位の端子同士をまとめて配線している。図2の例では、同電位のVDDA接続端子15をまとめて配線し、ソースドライバーIC13のVDDA入力端子14に接続する場合の一例を示している。VDDA接続端子15は、液晶パネル12の周縁部に配置されており、FPC27に設けられた端子と接続可能となっている。なお、ソースドライバーIC13は、図13のソースドライバーIC32であってもよい。液晶パネル12は、液晶パネル30(図11, 12参照)であってもよい。

【0023】

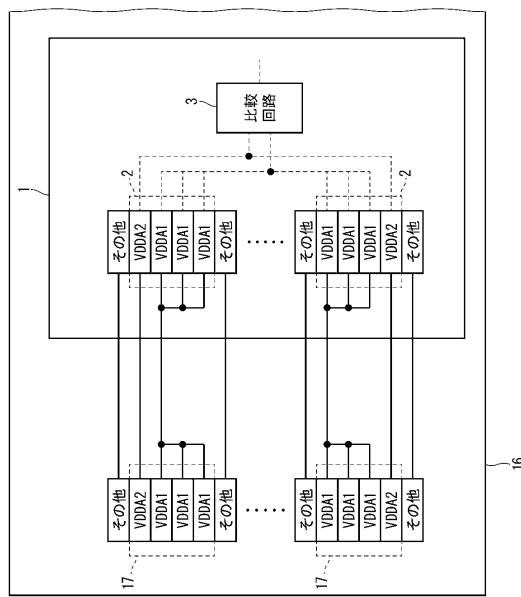

一方、図3に示すように、本実施の形態1では、VDDA接続端子17において外部から入力されたVDDA(アナログ電源)がVDDA1(第1のアナログ電源)の端子とVDDA2(第2のアナログ電源)の端子とに物理的に分離されており、ソースドライバーIC1のVDDA入力端子2においてもVDDA1の端子とVDDA2の端子とに物理的に分離されている。VDDA入力端子2におけるVDDA1の端子およびVDDA2の端子の各々は、比較回路3に接続されている。VDDA接続端子17は、液晶パネル16の周縁部に配置されており、FPC27に設けられたVDDAの端子と接続可能となっている。なお、液晶パネル16は、液晶パネル30(図11, 12参照)であってもよい。

【0024】

10

20

30

40

50

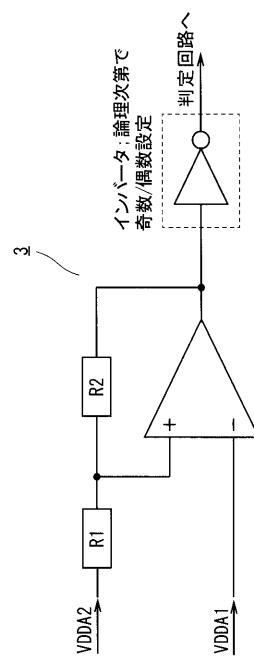

比較回路 3 は、例えば図 4 に示すようなコンパレーターを有しており、VDDA1 の電位とVDDA2 の電位との電位差を検出し、検出した電位差を 2 値論理に変換してから判定回路 4 に出力する。

【0025】

判定回路 4 は、比較回路 3 で検出された電位差が予め定められた閾値以上である場合に異常状態であると判定する。例えば、判定回路 4 は、比較回路 3 から入力された 2 値論理が「H」である場合において異常状態であると判定する。判定回路 4 による判定結果は、電流制御回路 5 に出力される。

【0026】

電流制御回路 5 (図 15 参照) は、判定回路 4 から異常状態である旨の信号 (入力選択信号) が入力されると、出力アンプに入力する電流量が少なくなるように切り替える (例えば、A から D に切り替える)。すなわち、判定回路 4 が異常状態であると判定した場合において、電流制御回路 5 は、出力アンプ 6 から画素領域 31 (図 11, 12 参照) に出力される電流量が少なくなるように制御する。

【0027】

また、判定回路 4 が異常状態であると判定した場合において、制御スイッチ 10, 11 は、判定回路 4 から異常状態である旨の信号が入力されると、アシスト回路 8 が異常に動作しないように、すなわち PMOS トランジスタおよび NMOS トランジスタが同時に ON しないように制御する。

【0028】

なお、判定回路 4 は、異常状態であると判定した場合において、異常状態である旨をシステム側 (図示しない) に出力可能にしてもよい。例えば、図 5 に示すように、ソースドライバー IC 1 にモニタ端子 18 を設け、異常状態である旨の信号 (モニタ信号) を、モニタ端子 18 を介して TCON19 に出力してもよい (図 6 参照)。図 6 において、TCON19 は、ソースドライバー IC 1 から入力されたモニタ信号を認識した後、エラー信号としてインターフェースコネクタ 20 を介してシステム側に出力することができる。

【0029】

また、異常状態である旨をシステム側に出力する他の方法として、図 7 に示すように、異常状態である旨の信号 (モニタ信号) を、モニタ端子 18 を介してインターフェースコネクタ 20 に直接出力するようにしてもよい。この場合、システム側では、異常状態を直接モニタすることができる。

【0030】

以上のことから、本実施の形態 1 によれば、低負荷時のアシスト回路 8 における貫通電流の発生を抑制することができる。従って、VDDA の電流値を下げることができ、液晶表示装置の全体的な消費電力を下げることができる。また、液晶パネルが異常状態であるか否かを簡単にモニタすることができる。近年、車載の機能安全規格である ISO 26262 を意識したシステム構築を行う上でそのリスク管理が問われるが、本実施の形態 1 によれば異常状態 (例えば、断線状態) を監視 (モニタ) することができる。異常状態をシステム側で監視することができる、仮に液晶パネルが異常状態になったとしても表示自体は行うことができるため、液晶パネルの状態を画面に表示してユーザーに知らせることが可能である。そして、液晶パネルが異常状態である場合は、ユーザーに対して異常状態に対する対処を促すことも可能である。

【0031】

<実施の形態 2 >

実施の形態 1 では、図 3 に示す VDDA1 および VDDA2 を電源回路 23 から出力される VDDA に共通して接続する場合について説明した。本発明の実施の形態 2 では、図 8 に示すように、レギュレータ回路などの安定化回路である VDDA2 生成部 29 を備えることを特徴としている。なお、VDDA1 および VDDA2 以外に VDDD 端子や GND 端子、設定端子、何も接続しないダミー端子など他の端子については、「その他」と記載して省略している。構成および動作は、実施の形態 1 と同様であるため、ここでは

10

20

30

40

50

詳細な説明を省略する。

【0032】

図8に示すように、電源回路23のVDDA生成部28から出力されたVDDAは、VDDA1とVDDA2とに分離される。そして、VDDA2に対して安定化回路であるVDDA2生成部29を備え、VDDA2生成部29で生成されたVDDA2は、FPC27を介してソースドライバーIC1のVDDA入力端子2におけるVDDA2の端子に入力される。この場合、VDDA2は、出力アンプ6の電源（電流源）として供給されるVDDA1と完全に分離される。

【0033】

以上のことから、本実施の形態2によれば、VDDA2については、図16に示すような負荷変動を抑制することができる。従って、負荷変動を受けるVDDA1との比較が容易となり、アシスト回路8の不安定な動作をより検出し易くなる。 10

【0034】

<実施の形態3>

本発明の実施の形態3では、図9に示すように、液晶パネル16に設けられたVDDA接続端子17におけるVDDA2の端子をFPC27の端側部に対応する位置に配置することを特徴としている。その他の構成および動作は、実施の形態1または2と同様であるため、ここでは詳細な説明を省略する。

【0035】

図11, 12に示す液晶表示装置に対して振動または衝撃などのストレスが加わると、FPC27の端側部に応力がかかりやすくなり、FPC27の端部（特に、端側部）から断線しやすくなる。図9に示すように、液晶パネル16に設けられたVDDA接続端子17におけるVDDA2の端子（第2の接続端子）をFPC27の端側部に対応する位置に配置した場合において、液晶表示装置に対してストレスが加わると、FPC27の端部の中央側に配置されたVDDA1の端子（第1の接続端子）に接続された配線よりも、端側部に配置されたVDDA2の端子に接続された配線の方が先に断線することになる。断線した配線の抵抗値は大きく上昇する。液晶パネル16の配線抵抗と異方性導電膜（ACF: Anisotropic Conductive Film）の抵抗とを合計すると、電源およびGNDラインは通常10以下程度の抵抗値になることが多い（FPCと回路基板26上の銅配線部分とは、1よりもはるかに小さいレベルの低抵抗であるため、液晶パネル30における配線抵抗のばらつきと比較して無視できるレベルである）。また、完全に断線した場合の抵抗値はMオーダーになるが、断線しかかっている場合の抵抗値は通常時の抵抗値と断線時の抵抗値との間の値となる。 20 30

【0036】

以上のことから、本実施の形態3によれば、VDDA1の配線よりも先にVDDA2の配線が断線するとVDDA2の配線の抵抗値が上昇し、これを比較回路3が検出することができる。また、比較回路3による検出結果に基づいて判定回路4で異常状態を判定し、その結果をシステム側に出力することによって、システム側でVDDA2の断線をモニタすることができるようになる。

【0037】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。また、回路ブロックの一部が他の部品のブロックに移動した形態も可能である。例えば、TCON19がソースドライバーIC内部に踏襲されたTCON内蔵ドライバーICのケースでは、図6, 7のRSDS-Tx/Rx部分は削除される。あるいは電源回路23と階調参照電圧生成回路24が一体となったもの、電源回路23または階調参照電圧生成回路24の一部がソースドライバーIC1、またはゲートドライバーIC22に踏襲された形態も可能である。

【符号の説明】

【0038】

1 ソースドライバーIC、2 VDDA入力端子、3 比較回路、4 判定回路、5

50

電流制御回路、6 出力アンプ、7 アンプ出力制御回路、8 アシスト回路、9 スイッチ、10, 11 制御スイッチ、12 液晶パネル、13 ソースドライバー I C、14 VDDA 入力端子、15 VDDA 接続端子、16 液晶パネル、17 VDDA 接続端子、18 モニタ端子、19 TCON、20 インターフェースコネクタ、21 EEPROM、22 ゲートドライバー I C、23 電源回路、24 階調参照電圧生成回路、25 液晶パネル、26 回路基板、27 FPC、28 VDDA 生成部、29 VDDA 2 生成部、30 液晶パネル、31 画素領域。

【図1】

【図2】

【 四 3 】

【 図 4 】

【図5】

【図6】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(51)Int.Cl.

| F I     |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 7 0 A |

| G 0 9 G | 3/20 | 6 7 0 E |

| G 0 9 G | 3/20 | 6 7 0 M |

(56)参考文献 国際公開第2012/137886 (WO, A1)

米国特許出願公開第2010/0177066 (US, A1)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00-3/38

G01R 31/00